MOSFET的短沟道效应,DOC

cell 沟道 沟槽 mosfet

cell 沟道沟槽 mosfetMOSFET(金属氧化物半导体场效应晶体管)是一种常用的半导体器件,它具有高性能和高可靠性,被广泛应用于电子领域。

在MOSFET中,沟道(channel)和沟槽(groove)是两个重要的概念,下面将对这两个概念进行详细的介绍。

1. 沟道(Channel)沟道是MOSFET的导电路径,它是由扩散层形成的,位于源极和漏极之间。

沟道的形成是通过在P型或N型衬底中引入浓度较高的掺杂杂质实现的。

根据掺杂杂质的类型和浓度,沟道可以是P型沟道或N型沟道。

在MOSFET工作时,通过在栅极上加上电压,可以在沟道中形成一个由电子或空穴组成的电荷层,从而调控沟道的电导。

MOSFET的沟道长度(channel length)是一个重要的参数,它影响着MOSFET的性能。

沟道长度较短可以提高MOSFET的开关速度,但也会增加导通电阻。

因此,在不同应用中需要根据具体的需求来选择合适的沟道长度。

此外,沟道宽度也会影响MOSFET的性能,宽度较大的沟道可以提高电流传输能力。

2. 沟槽(Groove)沟槽是MOSFET中的一个结构,它位于沟道的两侧,可以看作是沟道的侧边界。

沟槽的形状和尺寸会影响MOSFET的电流特性和电压特性。

沟槽的设计是为了提供更好的电场控制和电荷注入效果,从而改善MOSFET的性能。

一个常见的沟槽设计是浅槽(shallow groove)和深槽(deep groove)。

浅槽通常用于低电压MOSFET,它具有较低的电压容忍能力,但具有更好的开关速度和导通能力。

深槽通常用于高电压MOSFET,它具有更高的电压容忍能力,但开关速度和导通能力相对较低。

值得一提的是,MOSFET中的沟槽设计还可以采用特殊形状的非对称槽(non-symmetrical groove)或改变槽的结构,从而进一步优化MOSFET的性能。

无论是沟道还是沟槽,它们的设计与优化都是MOSFET的重要研究方向之一,下面列举一些相关的参考内容:1. M. S. Hossain, M. J. Hossain, and M. A. H. Khan, "Performance Analysis of MOSFET with Different Channel and Grooves Structures," American Journal of Electrical and Electronic Engineering, vol. 8, no. 5, pp. 116-124, 2020.2. X. Chen, W. Cui, Z. Cai, and Z. Cao, "Simulation study on the influence of groove structures on the reverse recovery characteristics of high-voltage MOSFET," Review of Scientific Instruments, vol. 86, no. 7, pp. 075110, 2015.3. B. Ahmed, E. H. Hwang, and F. L. Kang, "Optimization of MOSFET Groove Structure for High-Speed and Power Applications," IEEE Transactions on Electron Devices, vol. 63, no. 2, pp. 614-620, 2016.4. S. Ma and J. Y. Park, "Design optimization of drain-integrated field-shaping groove in heterostructure nanowire MOSFET," Scientific Reports, vol. 9, no. 1, pp. 10146, 2019.这些参考内容涵盖了MOSFET沟道和沟槽结构的性能分析、模拟研究、优化设计等方面。

(完整word版)MOSFET地短沟道效应

MOSFET 的短沟道效应3第8章 MOSFET 的短沟道效应MOSFET 的沟道长度小于3um 时发生的短沟道效应较为明显。

短沟道效应是由以下五种因素引起的,这五种因素又是由于偏离了理想按比例缩小理论而产生的。

它们是:(1) 由于电源电压没能按比例缩小而引起的电场 增大; (2) 内建电势既不能按比例缩小又不能忽略; (3) 源漏结深不能也不容易按比例减小;(4) 衬底掺杂浓度的增加引起载流子迁移率的降低; (5) 亚阈值斜率不能按比例缩小。

(A ) 亚阈值特性我们的目的是通过MOSFET 的亚阈值特性来推断阈值电压到底能缩小到最小极限值。

对于长沟道器件而言,亚阈值电流由下式给出2exp 1exp ......(8.1)GS T DS D n d t t t V V V W I C V L V V μξ⎛⎫⎛⎫--=- ⎪⎪⎝⎭⎝⎭也可以写成如下的形式20exp 1exp exp 1exp ......(8.2)GS T DS D n d t t t GS DS D t t V V V WI C V L V V V V I V V μξξ⎛⎫⎛⎫--=- ⎪⎪⎝⎭⎝⎭⎛⎫⎛⎫-=- ⎪⎪⎝⎭⎝⎭式中的dC 为单位面积耗尽区电容。

sddCxε===tkTVq=是热电压,1/d oxC Cξ=+,在DS V大于几个热电压时有2exp......(8.4)GS TD n d ttV VWI C VL Vμξ⎛⎫-≈ ⎪⎝⎭对上式两边取对数()2ln ln......(8.5)GS TD n d ttV VWI C VL Vμξ-⎛⎫=+⎪⎝⎭上式也可以写成2ln......(8.6)GS TDtn d tV VIW VC VLξμ⎛⎫⎪-=⎪⎪⎝⎭从式(8。

4)中可以看出,当0GS TV V-=时,即当栅-源电压等于亚阈值电压时有亚阈值电流:()20......(8.7)D GS T n d tWI V V C VLμ-==为了使GS TV V<时,器件可以关断,我们可以令(8.4)中的0GSV=,则有()20exp......(8.8)TD GS n d ttVWI V C VL Vμξ⎛⎫-== ⎪⎝⎭如果规定关断时(当0GSV=)的电流比在(当GS TV V=)的电流小5个数量级,式(8。

短沟道效应

E y , E y Ec 时

v vmax

v=

VK

Ey

vmax 常数, Ey Ec 时

0

EC

(3) 考虑速度饱和后的饱和漏极电流

短沟道MOSFET中,因沟道长度

L

很小,Ey

dV dy

很高,

使漏极附近有可能在沟道尚未被夹断之前, Ey 就达到了EC ,

载流子速度就达到了饱和值 vmax ,从而使 ID 饱和。 已知 VD sat = VGS -VT 为使沟道夹断的饱和电压,也就是使

(2) VDS(横向电场 Ey )对 μ 的影响 VDS 将产生水平方向的电场 Ey ,当 Ey 很大时,载流子速度 将趋于饱和。作为一种最简单的近似方法,可以用二段直线来

描述载流子的 v ~Ey 关系:

μ=

o 1 VGS VT

常 数, Ey Ec

时

VK

vmax Ey

,

Ey

Ec

时

o

I Dsat

特点: I D sat (VGS VT )2 ,

I D sat

1 L

对于短沟道

MOSFET,(EC L)2

V2 Dsat

,

I ' Dsat

Z L

n COX

( EC

L) 2

VEDCsLat

ZnCOX (VGS VT ) EC

特点: I Dsat (VGS VT ), I D sat与L无关。

③亚阈区转移特性斜率倒数 S dVGS 的值随 L 的缩短

d ln I Dsub

Q ( L ) = 0 的饱和电压。 现设 V 'D sat 为使 v ( L ) = vmax 的饱和电压。经计算:

半导体基础 7.3 短沟道效应-MOSFET

饱和区 体效应系数 饱和电流 饱和电压

南京大大学

I ds

=

µeff Cox

W L

(Vg

− Vt

)Vds

半导体器件基础

Vt = Vfb + 2ψB +

4ε Si qN aψ B Cox

Wdm (y) =

2εSi[V (y) + 2ψB ] qNa

I ds

=

µeff Cox

W L

+

∂2ψ i ∂y 2

=− ρ εSi

∂Ex + ∂Ey = ρ = − qNa

∂x ∂y εSi

εSi

南京大大学

电子子科学与工工程学院

半导体器件基础

♦横向电场的增加,

使受源漏电压控制的耗尽电荷密度增大, 而受栅压控制的耗尽层宽度变大,但积分 电荷密度减小,导致阈值电压的下降。

ε Si

∂Ex ∂x

= ρ −/Wd0m ≈ 1 + 3tox

Cox

Wdm

ΔVt = 8(m − 1) ψ bi (ψ bi + Vds )e−πL / 2mWdm

Wd0m =

4εSikT ln(Na / ni ) q2Na

为避免过量的短沟道效应,CMOS器件中衬底或阱里

的掺杂必须保证最小的沟道长度是Wdm的两到三倍, 或大于源与漏端的耗尽层宽度之和。

半导体器件基础

南京大大学

电子子科学与工工程学院 半导体器件基础

南京大大学

电子子科学与工工程学院

南京大大学

电子子科学与工工程学院

2

电荷共享模型(离化固定电荷)

半导体器件基础

南京大大学

MOSFET短沟道效应的新二维模型的开题报告

MOSFET短沟道效应的新二维模型的开题报告

开题报告:

1.研究背景与意义

MOSFET是一种广泛应用于集成电路中的场效应管。

短沟道MOSFET因其速度快,面积小,功耗低等优势,在现代集成电路中得到了广泛的应用。

同时随着半导体工艺技术的发展,器件尺寸越来越小,短通道效应日益严重,导致传统的器件模型失去了适用性,需要开发新的模型来解决这个问题。

2.研究内容

本研究旨在构建一种新的二维模型来描述短沟道MOSFET的行为特性。

具体研究内容包括:

(1)短沟道效应下的量子效应的影响分析

(2)二维模型的构建,包括流场和能带的模拟

(3)模型的验证和参数拟合

3.研究步骤

(1)分析短沟道MOSFET的特点和常见的模型

(2)研究量子效应对短沟道MOSFET特性的影响

(3)设计二维模型,包括模型的方程和参数

(4)使用数值模拟工具验证和优化模型

(5)在实验中验证模型的正确性

4.研究成果

(1)建立一个新的二维模型来描述短沟道MOSFET的行为特性

(2)提供了一种新的描述短沟道效应下量子效应影响的方法

(3)为短沟道MOSFET的设计和优化提供了理论基础和实验指导

5.研究意义

本研究将有助于更深入地了解短沟道MOSFET的行为特性,并提供新的模型来描述短沟道效应下量子效应的影响。

同时,本研究的成果将有助于优化现有的短沟道MOSFET的设计,并加速新型器件的研发和应用。

6.研究限制

本研究的主要限制在于需要进行大量的理论分析和数值模拟,同时还需要大量的实验数据验证模型的正确性。

另外,短沟道MOSFET的设计和制备过程较为复杂,需要有一定的专业知识储备和实验基础。

复旦大学半导体器件原理讲义L04-小尺寸MOSFET的特性

4.1 MOSFET的短沟道效应和窄沟道效应15

4.1.5 漏感应势垒降低

2. 原因 (1) 电荷分享

18/74

2ε s (Vbi + VBS ) yS = qN A 2ε s (Vbi + VDS + VBS ) yD = qN A

⎧ x ⎡⎛ 2 y ⎞1 / 2 ⎤ Q ⎪ = 1 − ⎨ j ⎢⎜1 + S ⎟ − 1⎥ F= 2 L ⎢⎜ QB xj ⎟ ⎥ ⎪ ⎣⎝ ⎠ ⎦ ⎩ ⎡⎛ 2 y ⎞1 / 2 ⎤ ⎫ xj ⎪ + ⎢⎜1 + D ⎟ − 1⎥ ⎬ 2 L ⎢⎜ xj ⎟ ⎥⎪ ⎠ ⎣⎝ ⎦⎭ 1 yS + yD ≡ 1−α L 2

' B

ΔVT =

α ( y S + y D ) qε s N A (VB + 0.5VBS )

LCox

F↓ VT ↓

VDS ↑

4.1 MOSFET的短沟道效应和窄沟道效应16

4.1.5 漏感应势垒降低

2. 原因 (2) 电势的二维分布

19/74

导带边 Ec

特征长度

l=

ε s d max tox ηε ox

4.1.7 热载流子效应抑制-新型漏结构

1. 最大漏电场 Eymax 饱和时

1 E y max = (VDS − VDSsat ) 0.22tox/ 3 x1j / 3 tox 和 xj 均以 cm 为单位

27/74

tox ↑ 降低 Eymax 措施

xj ↑

VDS ↓ VDD ↓ 新型漏结构 ⎯⎯ Graded pn junction

表面势

ΔVT =

sinh ( y l ) sinh[(L − y ) l ] Vs ( y ) = VsL + (Vbi + VDS − VsL ) + (Vbi − VsL ) sinh (L l ) sinh (L l ) [2(Vbi − 2VB ) + VDS ][exp(− L 2l ) + 2 exp(− L l )] VDS 很小

MOSFET的短沟道效应

M O S F E T的短沟道效应 Company number:【0089WT-8898YT-W8CCB-BUUT-202108】MOSFET 的短沟道效应3 第8章 MOSFET 的短沟道效应MOSFET 的沟道长度小于3um 时发生的短沟道效应较为明显。

短沟道效应是由以下五种因素引起的,这五种因素又是由于偏离了理想按比例缩小理论而产生的。

它们是:(1) 由于电源电压没能按比例缩小而引起的电场 增大;(2) 内建电势既不能按比例缩小又不能忽略; (3) 源漏结深不能也不容易按比例减小;(4) 衬底掺杂浓度的增加引起载流子迁移率的降低; (5) 亚阈值斜率不能按比例缩小。

(A ) 亚阈值特性我们的目的是通过MOSFET 的亚阈值特性来推断阈值电压到底能缩小到最小极限值。

对于长沟道器件而言,亚阈值电流由下式给出 也可以写成如下的形式式中的dC 为单位面积耗尽区电容。

t kT V q=是热电压,1/dox CC ξ=+,在DS V 大于几个热电压时有对上式两边取对数 上式也可以写成从式()中可以看出,当0GST V V -=时,即当栅-源电压等于亚阈值电压时有亚阈值电流:为了使GSTVV <时,器件可以关断,我们可以令()中的0GS V =,则有如果规定关断时(当0GSV=)的电流比在(当GS T V V =)的电流小5个数量级,式和式的两边相除则有 得到亚阈值电压的最小值为 如果1/10.76 1.76dox CC ξ=+=+=则亚阈值电压的最小值是5ln105 1.6726 2.3500T t V V mV mVξ==⨯⨯⨯=。

如果还想将阈值电压降低到400mV 左右,那么就要减小1/d ox C C ξ=+的值,使1/ 1.34d ox C C ξ=+=。

考虑到温度对阈值电压的影响,按比例缩小阈值电压将更加困难。

阈值电压的温度系数1/TdVmV KdT=-。

导致阈值电压在温度范围(0-85℃)内的变化是85mV 。

第六章1MOSFET06

沟道中任一点的电流: Jn (x, y)= - qn(x, y)u(x, y)

x

y 假设

•正常工作区 nMOS VDS 常0,VBS 0

时 空穴电流Jp可以忽略

•Jn只沿y向流动

•Gn=Rn=0,任一点的总电流连续

•迁移率为常数

沟道中任一点的电流:

缓变沟道近似:1D MOSFET模型的关键,只适合于长沟器件

需要2D分析、边缘效应不可忽略 VDS>VDSAT 后IDS不饱和 VT漂移 S上升 强电场效应

Institute of Microelectronics PKU Liu Xiaoyan

一、短沟效应

Short Channel Effect SCE 现象

•Vt roll off •DIBL效应 •源漏穿通 •反常的短沟效应

界面的影响

载流子的屏蔽作用使

库仑散射:界面电荷、 电离杂质

迁移率随Qinv(Vg) 增加而增加。

表面粗 糙散射

栅压引起有效迁移率 的退化。

Vg大后,纵向电场 Evertical增加,使载流 子更加频繁地与表面 接触(散射),迁移 率降低。

Institute of Microelectronics PKU Liu Xiaoyan

•沟道由异质结中的2DEG形成 •S/D与沟道区为同种类型的半 导体 •常开器件,加栅压使关断

Institute of Microelectronics PKU Liu Xiaoyan

第一节 长沟MOSFET

一、MOSFET的结构、能带 二、阈值电压 三、 I-V特性的模型

1. pao-sah 方程 2. 缓变沟道近似 3. 其他源漏电流模型 四、亚阈特性 五、衬偏效应 六、沟道尺度调制效应

短沟道效应

4.7.1 小尺寸效应

1、阈电压的短沟道效应 实验发现,当 MOSFET 的沟道长度 L 缩短到可与源、漏区 的结深 xj 相比拟时,阈电压 VT 将随着 L 的缩短而减小,这就是 阈电压的短沟道效应 。

VT

MS

QOX COX

QA COX

2FB

原因:漏源区对 QA 的影响

1

QA qNA xd 4sqN A FB 2 代表沟道下耗尽区的电离

1

2 2

1

对于普通 MOSFET, ECL2

V2 Dsat

I Dsat

Z L

nCOX

EC L

2

1

1 2

VDsat EC L

2

1

Z 2L

C V2 n OX Dsat

I Dsat

特点: I Dsat VGS VT 2 ,

I Dsat

1 L

对于短沟道

MOSFET, ECL2

杂质电荷面密度 。考虑漏源区的影响后,QA 应改为平均电荷 面密度 QAG 。

L

xd

xj

L

P

QAG

qNA xd

1 L L Z

2

1 LZ

qNA xd

L L 2L

QA

L L 2L

1

QA

1

xj L

1

2

xd xj

2

1

VT

MS

QOX COX

QAG COX

2FB

1

QAG

1 1 1

0 电场

式中,电场

K VGS VT

电场0 电场 0

1

0 0

电场

1

0

K0Biblioteka (VGSVT )1

LDD后热处理工艺对28 nm PMOSFET短沟道效应的影响

工艺与制造Process and FabricationLDD后热处理工艺对28nm PMOSFET 短沟道效应的影响朱巧智,刘巍,李润领(上海华力集成电路制造有限公司,上海201314)摘要:Si MOSFET作为大规模集成电路的基础,沟道长度是决定其运行速度和集成度的重要参数。

随着Si MOSFET器件尺寸不断缩小,短沟道效应(即器件阈值电压随沟道长度减小不断降低的现象)越来越严重。

基于28nm低功耗逻辑平台,研究了LDD后热处理工艺对PMOSFET器件短沟道效应的影响及物理机制。

实验结果表明,通过优化热处理温度,可以显著改善PMOSFET器件短沟道效应,实现在较低pocket离子注入剂量下达到同样阈值电压的目的。

TCAD工艺及器件仿真结果表明,热处理温度调节器件短沟道效应的主要物理机制是其对pocket离子注入杂质激活率的影响。

关键词:集成电路制造;短沟道效应;PMOSFET;pocket注入;热处理温度。

中图分类号:TN405文章编号:1674-2583(2019)08-0034-03D01:10.19339/j.issn.1674-2583.2019.08.012中文引用格式:朱巧智,刘巍,李润领丄DD后热处理工艺对28nm PMOSFET短沟道效应的影响[J].集成电路应用,2019,36(08):34-36.Impaction of Post-LDD Anneal to28nm PMOSFET Short Channel EffectZHU Qiaozhi,LIU Wei,LI Runlai(Shanghai Huali Integrated Circuit Corporation,Shanghai201314,China.)Abstract—Si MOSFET is the basic building block of large-scale integrated circuits.MOSFET channel length is a critical parameter to decide the circuits speed and integration density.With the feature size of Si MOSFET scaling down,short channel effect(SCE,the phenomenon of threshold voltage decreases with gate length decreasing)is becoming more mnd more severe.Based on28nm low power logic platform,this work investigated the effect of post-LDD anneal to PMOSFET SCE.The results show that high temperature SPK anneal could effectively suppress PMOSFET SCE.TCAD simulation reveal that the mechanism of high temperature SPK suppressing SCE is due to pocket Ph active concentration increasing in channel.Index Terms—integrated circuit manufacturing,short channel effect,PMOSFET,pocket implant, anneal temperature1引言相关,而且与由漏极电压控制的横向电场也相关,这互补金属氧化物半导体(Complementary Metal-Oxide-Semiconductor,CMOS)电路是大规模集成电路技术的重要基石,而金属氧化物半导体场效应管(Metal-Oxide-Semiconductor Field Effect Transistor, MOSFET)则是CMOS电路的基本组成器件[l'2]o 在CMOS技术发展的五十多年时间里,为了实现更高的集成度、更优良的性能、以及更低的功耗,S! MOSFET器件特征尺寸不断减小。

11-MOS-4-短沟道效应

The methods of avoiding latch-up: a) Reducing the current gains parasitic BJT b) A deeper well structure c) Using a heavily doped substrate d) With the trench isolation scheme

栅氧化层厚度

为降低SCE效应,栅氧化层要尽可能薄, 但需要考虑可靠性。 最大电场取 Fowler-Nordheim (F-N)隧 穿开启电场的 80%。即 5 MV/cm的 80%,为 4 MV/cm 例如:

工作电压2.5V 最大电场4 MV/cm 所以氧化层厚度

Xox = 2.5 V/4MV/cm = 65Å

x j − 1 L

For 5 µ, effect is negligible. But at 0.5 µ, VT0 reduced to 0.43 from 0.76 volts (∆VT0=0.33V)

0.8

Threshold Voltage (V)

0.7 0.6 0.5 0.4 0 1 2 3 4 5 6

CS ε s tox 1 QS =1+ =1+ =1+ COX 2VS 2COX 2ε ox xd max

N由tox、xd max决定,在长沟道MOS器件中,N是常数。

Al 栅 N 沟 MOS N x t ox V V

DS BS j A

,

− 3

= 10

15

cm

= 1 .5 µ m = 80 nm = 0 . 1V = 0V

(

)

(δVT

δVD )是漏致势垒降低效应(DIBL)

微电子器件B482015短沟道效应

V2 Dsat

,

I D sat

Z L

n

COX

(

EC

L)

2

VEDCsLat

ZnCOX (VGS VT )EC

特点: I Dsat (VGS VT ), ID sat与 L 无关。

5、速度饱和对跨导的影响

普通 MOSFET 在饱和区的跨导为

g ms

d IDsat d VGS

Z L

nCOX (VGS

特点:饱和漏源电压正比于 L ,将随 L 的缩短而减小。

4、速度饱和对饱和漏极电流的影响

设 IDsat 为使 v (L) = vmax 的漏极饱和电流,经计算,

I Dsat

Z L

nCOX (EC L)2

1

VDsat EC L

1

2

2

1

I Dsat

Z L

n

COX

(

EC

L)2

1

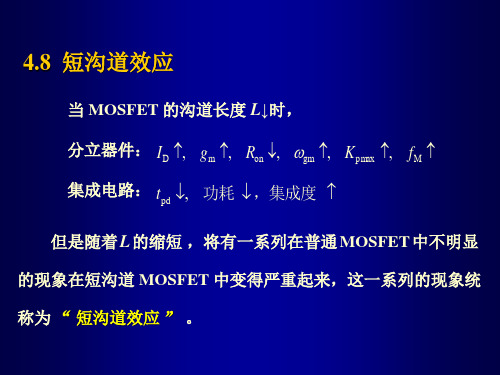

4.8 短沟道效应

当 MOSFET 的沟道长度 L↓时,

分立器件: ID , gm , Ron , gm , Kpmax , fM

集成电路: tpd , 功耗 ,集成度 但是随着 L 的缩短 ,将有一系列在普通 MOSFET 中不明显 的现象在短沟道 MOSFET 中变得严重起来,这一系列的现象统 称为 “ 短沟道效应 ” 。

dV dy

很高,

使漏极附近的沟道尚未被夹断之前 ,Ey 就达到了临界电场 EC ,

载流子速度 v (L) 就达到了饱和值 vmax ,从而使 ID 饱和。

已知 VDsat = VGS – VT 为使沟道夹断的饱和漏源电压,也就 是使 Qn (L) = 0 的饱和漏源电压。

现设 VDsat 为使 v (L) = vmax 的饱和漏源电压。经计算,

短沟道mosfet的漏致势垒降低效应

短沟道mosfet的漏致势垒降低效应短沟道MOSFET的漏致势垒降低效应在电子器件领域,短沟道MOSFET(金属氧化物半导体场效应晶体管)是一种重要的器件结构,能够实现高速、低功耗的集成电路设计。

然而,在短沟道MOSFET中,漏致势垒降低效应是一种常见的问题,可能会影响器件的性能和可靠性。

漏致势垒降低效应是指当MOSFET的沟道长度缩短到一定程度时,由于漏极与沟道之间的电场强度增加,会导致漏极-沟道结的势垒降低,从而影响器件的开关特性和电流传输能力。

这种效应的出现主要是由于沟道长度缩短引起的漏极电场增强,使得电子在漏极区域获得更高的能量,容易越过势垒进入漏极。

为了解决短沟道MOSFET的漏致势垒降低效应,研究人员提出了一些方法和技术。

其中一种常见的方法是引入掺杂剂,通过增加漏极区域的势垒高度来抑制电子的漏射。

另一种方法是使用高介电常数的绝缘层材料,以减小沟道电容,从而降低电场强度。

此外,还可以通过优化器件结构和工艺参数,如控制沟道厚度和衬底掺杂浓度等方式来减小漏致势垒降低效应的影响。

除了上述技术方法,短沟道MOSFET的漏致势垒降低效应还可以通过设计新的材料和器件结构来解决。

例如,一些研究人员提出了使用二维材料作为沟道材料,以提高漏极-沟道结的势垒高度。

此外,引入新的器件结构,如纳米线晶体管和异质结构等,也被认为是一种有效的方式来抑制漏致势垒降低效应。

短沟道MOSFET的漏致势垒降低效应是一种影响器件性能和可靠性的重要问题。

通过引入掺杂剂、优化器件结构和工艺参数,以及设计新的材料和器件结构等方法,可以有效地减小漏致势垒降低效应的影响,提高短沟道MOSFET的性能。

这对于推动集成电路的发展和应用具有重要意义。

MOSFET短路分析

MOSFET短路分析MOSFET短路分析是针对金属-氧化物-半导体场效应晶体管(Metal-Oxide-Semiconductor Field-Effect Transistor,简称MOSFET)的一种电路分析方法,用于分析MOSFET在短路状态下的电流、电压等参数。

首先,我们需要了解MOSFET的结构和工作原理。

MOSFET是一种三端设备,包括放大器和开关两种工作模式。

它由一个N型或P型硅表面层(称为沟道)分成两部分,两端连接控制端(栅极)和源极,它的中间由绝缘层隔开。

当栅极电压变化时,栅极电场的作用会调节沟道的导电能力,从而调节源极和漏极之间的电流。

在正常工作状态下,MOSFET的源极和漏极之间会建立一个电流路径,电流由源极流向漏极。

当我们将栅极施加一个适当的电压,可以控制电流的大小,实现电流放大和开关控制。

然而,在一些情况下,MOSFET可能会出现短路的情况,即源极和漏极之间的电流过大,导致电路故障。

短路通常是由于MOSFET内部或外部的一些原因引起的,比如电压过高、温度过高、过电压等。

1.检查电路连接:首先需要检查MOSFET的引脚连接是否正确,确保源极、漏极和栅极与外部电路正确连接,没有接错或短路。

2.测量电路参数:使用万用表或示波器,测量MOSFET的源极-漏极之间的电阻,以判断是否存在短路故障。

如果电阻低于正常范围,可能存在短路。

3.检查外部电路:检查外部电路是否存在过电流或过电压的情况,例如过高的电压、短路的负载等。

这些因素可能导致MOSFET的短路故障。

4.检查温度:高温环境可能会引起MOSFET的短路故障。

因此,检查MOSFET周围的温度,并确保它没有超过其额定工作温度范围。

5.更换MOSFET:如果经过以上步骤检查后发现MOSFET确实出现短路故障,那么需要将其更换为一个新的MOSFET。

6.后续分析:对更换后的MOSFET进行测试,检查电路是否恢复正常工作。

如果仍然存在问题,可能需要进一步分析其他引起故障的因素。

MOS管沟道长度的意义

MOS管沟道长度的意义MOS管沟道长度的意义是指金属氧化物半导体场效应管(MOSFET)的通道长度,即MOSFET中的硅表面上形成的一条空间,用于传导电流。

MOS管沟道长度是MOSFET性能的重要参数,对器件的电学特性和性能有着重要的影响。

1.电流控制:MOS管沟道长度决定了场效应管的导电能力。

较短的沟道长度(如亚微米级别)可以提供更高的电导率,因为电子在沟道中的速度较高,电子流动更加顺畅。

而较长的沟道长度则会增加电流的阻抗,降低电导率。

因此,沟道长度越短,MOSFET的导通能力越好,能够提供更大的电流输出。

2.开关速度:沟道长度的大小还影响开关速度。

短沟道长度会缩短场效应管的开关时间,使得MOSFET能够更快地从导通状态转换到截止状态,或者从截止状态转换到导通状态。

这对于高频应用和高速电子器件非常重要,可以提高系统的工作效率和响应速度。

3.灵敏度:沟道长度也会影响MOSFET的灵敏度。

当沟道长度较短时,由于沟道表面积增大,电荷分布更加集中,电荷与栅极之间的电势差增大,使得MOSFET对栅极电压的响应更为敏感。

这使得MOSFET的栅极驱动电压较低,具有更高的灵敏度,并能更准确地反映出输入信号的变化。

4.互连电阻和功耗:沟道长度对MOSFET的互连电阻和功耗也有显著影响。

沟道长度较长时,导致MOSFET中存在更多的电阻,会增加电流的阻抗,导致功耗增加。

此外,较长的沟道长度会导致互连电阻增加,降低电压的传输效率,增加信号的延迟,影响系统的性能。

5.耗尽区效应:当沟道长度减小至一定程度时(亚微米级别),由于沟道长度小于电子平均自由程,电子在其运动过程中会撞击沟道两侧的表面,产生耗尽效应。

这种耗尽效应会导致电流随沟道长度减小而减小。

利用这种耗尽效应,可以实现更好的电流控制和电流输出。

综上所述,MOS管沟道长度对于MOSFET器件的性能和电学特性起着重要的作用。

通过控制和优化沟道长度,可以获得更高的电导率、更快的开关速度、更高的灵敏度,并优化功耗和互连电阻。

分析引起短沟道效应的原因,给出抑制小尺寸MOS器件短沟道效应的措施

沟道长度减小到一定程度后,源、漏结的耗尽区在整个沟道中所占的比重增大,栅下面的硅表面形成反型层所需的电荷量减小,因而阈值电压减小。同时衬底内耗尽区沿沟道宽度侧向展宽部分的电荷使阈值电压增加。当沟道宽度减小到与耗尽层宽度同一量级时,阈值电压增加变得十分显著。短沟道器件阈值电压对沟道长度的变化非常敏感。

分析引起短沟道效应的原因,给出抑制小尺寸MOS器件短沟道效应的措施

当MOS管沟道缩短到一定程度,就会出现短沟道效应,其主要表现在MOS管沟道中的载流子出现速度饱和现象。在MOS管沟道较长、电场较小的情况下,载流子的速度正比于电场,即载流子的迁移率是个常数。然而在沟道电场强度很高情况下,载流子的速度将由于散射效应而趋于饱和。载流子速度与电场的关系可用以下关系式来近似: 其中 是迁移率,E是沟道水平方向的电场,Ec是速度饱和发生时的临界电场。沟道水平方向的电场取决于 Uds/L。对于短沟道MOS管,由于沟道长度L 比

(4)亚阈特性退化,器件夹不断

亚阈区泄漏电流使MOSFET器件关态特性变差,静态功耗变大。在动态电路和存储单元中,它还可能导致逻辑状态发生混乱。因而由短沟道引起的漏感应势垒降低(DIBL)效应成为决定短沟道MOS器件尺寸极限的一个基本物理效应。

短沟道晶体管

短沟道晶体管

短沟道晶体管(Short-Channel MOSFET),是一种高性能晶体管,广泛应用于现代IC技术中。

简单地说,它是一种MOS场效应晶体管的

变化形式,它具有更短的通道长度,可以提供更高的频率响应和更低

的功耗。

短沟道晶体管的制造技术较为复杂,需要采用纳米级别的微电子

制造工艺。

其制造过程包括光刻、化学蚀刻、离子注入等一系列复杂

的工序。

通过这些工艺的精密控制,制造出的短沟道晶体管通道长度

可以达到几十纳米的级别,具有极高的性能指标。

除了更短的通道长度,短沟道晶体管还具有许多其他的优点。

例如,它们具有较小的噪声系数、更高的增益和更高的开关速度,在高

频率、低功耗应用中表现得非常出色。

此外,它们还可以实现更高的

电路密度和更小的占用面积,因为通道长度更短,所以晶体管可以更

紧密地排列。

然而,短沟道晶体管也存在着一些挑战和问题。

例如,由于通道

长度更短,它们更容易受到热效应的影响,因此在高功率、高温度应

用中容易出现故障。

此外,由于制造过程复杂,控制难度大,短沟道

晶体管的制造成本也相对较高。

总体来说,短沟道晶体管是一种高性能、高密度的晶体管,具有

重要的应用价值。

尽管它们存在一些问题,但随着微电子技术的不断

发展和进步,短沟道晶体管将仍然是未来电子设备中的重要组成部分。

第8章 短沟道MOSFET

• 当VDS大到一定程度后,微小

器件的亚阈特性增加,即使 在关态器件仍具有相当大的 Ioff ;

长沟和短沟器件在低和高 漏电压时的亚阈特性

• 如果此时Ioff已接近或超过定 义的开启电压,则器件穿通。

DIBL对器件性能的不利影响

• 影响器件的成品率

• 使器件的亚阈区性能退化 • 深亚微米器件的设计中要避免或抑制DIBL效应 • 可以通过解二维泊松方程加以分析 • 器件模拟程序

衬底或阱掺杂浓度及沟道长度 的设计原则

• 为了避免短沟效应太严重,在CMOS中,衬底或阱掺杂浓度的选 取原则是:最小沟道长度,Lmin,大约是Wdm的2~3倍。 • 最小沟道长度大于源、漏耗尽层宽度之和。Lmin WS+WD

•

WS

2 Si bi qN a

(A6.7)

•

WD

2 Si ( bi Vds ) qN a

m 1

0 Si / Wdm

Cox

1

3t ox Wdm

(3.67)

把(3.67)代入(3.66)式得:

Vt 8(m 1) bi ( bi Vds )e L / 2mWd m

(3.68)

如果源、漏结深大于栅耗尽层厚度,上述近似结果很好地描述阈 值电压的降低。短应不是太严重,可以用长沟器件的值。

模拟的长沟和短沟MOSFET的等电位线

长沟道与短沟道MOSFET的关键区别在于短沟道MOSFET 耗尽区的等电位线是二维的而长沟的则是一维的。

长沟与短沟MOSFET等电位线不同的原因

• 长沟MOSFET器件源、漏之间的距离较远,源、漏耗

尽层彼此分离,不影响栅下面的电场;但是,在短沟 MOSFET源、漏之间的距离与耗尽层垂直方向的宽度 可以相比拟,因此,对能带的弯曲有影响,对栅下面 的电场也有影响。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

MOSFET 的短沟道效应3 第8章MOSFET 的短沟道效应

MOSFET 的沟道长度小于3um 时发生的短沟道效应

阈值电压到底能缩小到最小极限值。

对于长沟道器件而言,亚阈值电流由下式给出 也可以写成如下的形式

式中的d

C 为单位面积耗尽区电容。

t kT V q

=

是热电压,1/d

ox C

C ξ=+,在DS V 大于几个热电压时有

2

对上式两边取对数 上式也可以写成

从式(8.4)中可以看出,当0GS

T V V -=时,即当栅-源

电压等于亚阈值电压时有亚阈值电流:

为了使GS

T V V <时,器件可以关断,我们可以令(8.4)

制造工艺引起的最小变化也在50mV 之间。

工艺和温度引起的变化合计为135mV 左右。

因此,对增强型的MOS 器件其阈值电压一般都控制在0.50.9T

V V

V

<<之间。

(B ) 短沟道效应使阈值电压减小

对理想MOSFET 器件,我们是利用电荷镜像原理导出阈

值电压的表达式。

见下图。

()

()'''max 8.11mT ss SD Q Q Q +=式中忽略了沟道中的反型层电

荷密度'

n

Q ,()'

max SD

a dT

Q eN x =为最大耗尽层单位面积电荷密

度。

这个电荷密度都由栅的有效面积控制。

并忽略了由于源/漏空间电荷区进入有效沟道区造成的对阈值

效应对阈值电压造成的影响。

假设源/漏结的扩散横向与纵向相等,都为j

x 。

这种假设对扩散工艺形成的结

来说是合理的,但对例子注入形成的结则不那么准确。

我们首先考虑源端、漏端和衬底都接地的情况。

在短沟道情况下,假定栅极梯形区域中的电荷有栅极

控制。

在阈值反型点,降落在沟道区的空间电荷区上

的势差为2

φ,源和漏结的内建电势差也约为2Fpφ,这

Fp

表明这三个空间电荷区的宽度大体相等。

如图8.3a。

假定梯形区内的单位面积平均电荷密度为'

Q,则有

B

上式可以写成Array

电压变成了漏极电压的函数,随着漏极电压增大,N 沟器件的阈值电压也会减小。

MOSFET的窄沟道效应

MOSFET结构的表面空间电荷区电荷、电

4

场、电容

为了更详细地分析表面空间电荷层的性质,可以通

过求解泊松方程,定量地求出表面层中的电场强度、电势分布。

为此,我们取x轴垂直于半导体的表面并指向体内,规定x轴的原点在表面处。

表面空间电荷区中

为一常数,且与体内相等,电中性条件成立,所以空

间电荷区的净浓度()0

ρ=

x

(4)其净掺杂表现为P型半导体。

空间电荷区的净浓度可以写成如下形式:

6

其中,d

a N

N +-分别表示电离的施主杂质和电离的受主杂

质浓度;如果在常温下杂质完全电离,则有0d

p N n +=(这

是因为我们假设其掺杂为补偿掺杂),0a

p N p -

=;,p p p n 分

别表示x 点处的P 型半导体空穴(多子)浓度和电子(少

子)浓度。

(所以: 及

令1/2

2s t D p V L qp ε⎛⎫=

⎪ ⎪⎝⎭

称谓德拜长度。

则

应当注意:上式中的V大于零时取“+”号,小

于零时取“-”号。

L称做德拜长度。

式(8.38)叫做F

D

函数,是表征半导体空间电荷层的一个重要参数。

通过F函数,可以方便地将表面空间电荷层的基本参数表达出来。

电荷层存在着4中状态,仍以P型衬底半导体为例:(1)多子堆积状态

(2)耗尽状态

(3)平带状态

8

(4) 少子反型状态

图(8.6)是表面电荷密度和表面势的函数关系图,详细标出了P 型硅在温度是300K ,掺杂浓度

153410a N cm -=⨯时,表面电荷密度和表面势的函数关系。

有了半导体表面电场s

E ,表面电荷s

Q 和表面电容s

C 的表

2. 平带状态

表面势0s V =,根据式(8.38)很容易求得00,0p s t

p n V F V p ⎛⎫

= ⎪ ⎪⎝⎭,从而求得

0,0s s E Q ==。

表面电荷则不能直接将0

V=直接带入(8.43)式,原因

s

是将0

V=带入该式,分子分母均为零。

要想求得表面

s

势0

V=时的表面电荷需要对(8.43)式求极限

s

在考虑到P型半导体

n远小于0p p,最后得到

p

3.耗尽状态

征费米能级

E下降到F E之下,就会在表面处形成反型Fi

层。

反型可分为弱反型和强反型两种,以表面处少子浓度与体内多子浓度的大小来界定。

当表面处的少子浓度小于体内的多子浓度时,称为弱反型;当表面处的少子浓度大于体内的多子浓度时,称为强反型。

表

10

面处的少子浓度为

当表面处的少子浓度等于体内的多子浓度时,即0

s

p n p =时,上式为

()220

exp 8.55s p i

t V p

n V ⎛⎫

= ⎪

⎝⎭

或

另一方面,根据波尔兹曼统计

t V 时,1⎫

⎪。

式将上式带入式(8.40)、式2fp φ时,t V ,F 加,其值较其它项都大的多,故可以略去其它项,可应该值得注意:一旦出现强反型,表面耗尽层宽度就会达到最大值dm

x ,不再随外电压的增加而增加。

这是

因为反型层中的电子屏蔽了外电场的作用。

5.电容-电压特性

MOS电容结构是MOSFET的核心,MOS器件和栅氧

化层-半导体界面处的大量信息可以从器件的电容

-电压关系即C V-特性曲线中求得,MOS器件电容的定

义:

其中,

dQ是金属极板上单位面积电荷的微分变量,G dV m

该式表明MOS系统的电容相当于氧化层电容与半导体

空间电荷层电容的串连。

如下图所示。

下面讨论:

(1)堆积状态的MOS系统电容

12

前面的讨论已经得到堆积状态时的半导体表面电容有(8.47)式给出exp 2s s s D t V C

L V ε⎛⎫=- ⎪⎝⎭ 带入式(8.78)式得

先考虑负偏压较大时的情形,这时

2s t V V -,

s s V ε⎛⎫0s t s p t qp V ⎪⎝⎭⎝⎭MOS 系统的电容由下式给出

继续加大偏压时的,表面耗尽区宽度表现为最大值1/204s fp dm p x qp εφ⎛⎫= ⎪ ⎪⎝⎭。

而此时的MOS 系统电容变为最小值

当2s fp V φ≥时,表面电容的表达式由(8.69)给出,

1/20s s s D p n C L p ε-⎛⎫= ⎪ ⎪⎝⎭。

MOS 系统电容变为

当G

V 较大时,表面出现强反型,表面处的少子载流子浓度s

n 显著增大,而反型层的厚度很小,使得表面电ox C 。

若反型层的载流子浓度的变化跟得上外加

电压的变化,则此时的电容即为栅氧化层电容。

s

的结果,栅电压越高,表面反型层加厚,表面电容s C 越大(可以看成进一步减小了耗尽区的宽度),因此在表面反型状态,随栅压的增大MOS 结构的总电容从最小值min C 逐渐增大,直至等于强反型状态的值ox C 。