单片机基础与实践第4讲AT89S51单片机引脚及其功能 - 副本

单片机引脚说明(89C51为例)

T89C2051是精简版的51单片机,精简掉了P0口和P2口,只有20引脚,但其内部集成了一个很实用的模拟比较器,特别适合开发精简的51应用系统,毕竟很多时候我们开发简单的产品时用不了全部32个I/O口,用AT89C2051更合适,芯片体积更小,而且AT89C2051的工作电压最低为2.7V,因此可以用来开发两节5号电池供电的便携式产品。

本文以ATMEL公司生产的51系列家族的AT89S51和AT89C2051两种单片机来讲解,两种单片机是目前最常用的单片机,其中 AT89S51为标准51单片机,当然其功能比早期的51单片机更强大,支持ISP在系统编程技术,内置硬件看门狗。

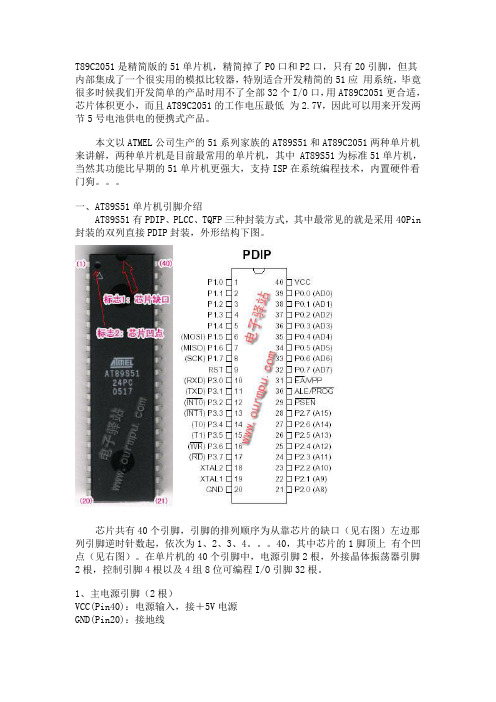

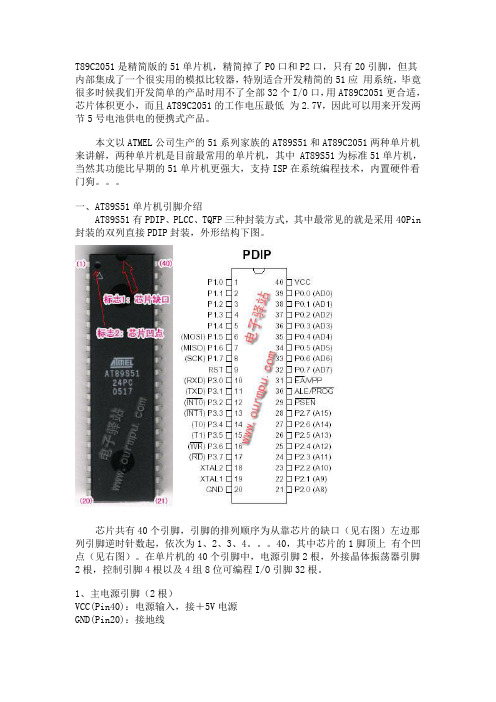

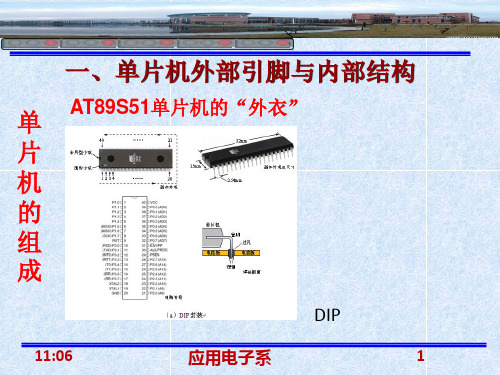

一、AT89S51单片机引脚介绍AT89S51有PDIP、PLCC、TQFP三种封装方式,其中最常见的就是采用40Pin 封装的双列直接PDIP封装,外形结构下图。

芯片共有40个引脚,引脚的排列顺序为从靠芯片的缺口(见右图)左边那列引脚逆时针数起,依次为1、2、3、4。

40,其中芯片的1脚顶上有个凹点(见右图)。

在单片机的40个引脚中,电源引脚2根,外接晶体振荡器引脚2根,控制引脚4根以及4组8位可编程I/O引脚32根。

1、主电源引脚(2根)VCC(Pin40):电源输入,接+5V电源GND(Pin20):接地线2、外接晶振引脚(2根)XTAL1(Pin19):片内振荡电路的输入端XTAL2(Pin20):片内振荡电路的输出端3、控制引脚(4根)RST/VPP(Pin9):复位引脚,引脚上出现2个机器周期的高电平将使单片机复位。

ALE/PROG(Pin30):地址锁存允许信号PSEN(Pin29):外部存储器读选通信号EA/VPP(Pin31):程序存储器的内外部选通,接低电平从外部程序存储器读指令,如果接高电平则从内部程序存储器读指令。

芯片实物图片芯片引脚功能4、可编程输入/输出引脚(32根)AT89S51单片机有4组8位的可编程I/O口,分别位P0、P1、P2、P3口,每个口有8位(8根引脚),共32根。

AT89S51单片机简介

一、 AT89S51单片机简介AT89S51为 ATMEL所生产的可电气烧录冲刷的 8051 相容单芯片,其内部程序代码容量为 4KB(一)、 AT89S51主要功能列举以下:1、为一般控制应用的8 位单芯片2、晶片内部具时钟振荡器(传统最高工作频率可至12MHz)3、内部程式存储器( ROM)为 4KB4、内部数据存储器( RAM)为 128B5、外面程序存储器可扩大至64KB6、外面数据存储器可扩大至64KB7、32 条双向输入输出线,且每条均能够单独做I/O 的控制8、5 此中断向量源9、2 组独立的 16 位准时器10、1 个全多工串行通信端口11、8751 及 8752 单芯片拥有数据保密的功能12、单芯片供应位逻辑运算指令(二)、 AT89S51各引脚功能介绍:VCC:AT89S51电源正端输入,接 +5V。

VSS:1 / 4电源地端。

XTAL1:单芯片系统时钟的反相放大器输入端。

XTAL2:系统时钟的反相放大器输出端,一般在设计上只要在XTAL1和 XTAL2上接上一只石英振荡晶系通通就可以动作了,其他能够在两引脚与地之间加入一20PF的小电容,能够使系统更牢固,防备噪声搅乱而死机。

RESET:AT89S51的重置引脚,高电平动作,当要对晶片重置时,只要对此引脚电平提升至高电平并保持两个机器周期以上的时间, AT89S51便能完成系统重置的各项动作,使得内部特别功能寄存器之 AT89S51内容均被设成已知状态,并且至地址0000H 处开始读入程序代码而执行程序。

EA/Vpp:"EA"为英文 "ExternalAccess"的缩写,表示存取外面程序代码之意,低电平动作,也就是说当此引脚接低电平后,系统会取用外面的程序代码(存于外面EPROM中)来执行程序。

因此在8031 及 8032 中, EA引脚必定接低电平,因为其内部无程序存储器空间。

若是是使用 8751 内部程序空间时,此引脚要接成高电平。

AT89S51单片机简介

一、AT89S51单片机简介AT89S51为ATMEL所生产的可电气烧录清洗的8051相容单芯片,其内部程序代码容量为4KB(一)、AT89S51主要功能列举如下:1、为一般控制应用的8位单芯片2、晶片内部具时钟振荡器(传统最高工作频率可至12MHz)3、内部程式存储器(ROM)为4KB4、内部数据存储器(RAM)为128B5、外部程序存储器可扩充至64KB6、外部数据存储器可扩充至64KB7、32条双向输入输出线,且每条均可以单独做I/O的控制8、5个中断向量源9、2组独立的16位定时器10、1个全多工串行通信端口11、8751及8752单芯片具有数据保密的功能12、单芯片提供位逻辑运算指令(二)、AT89S51各引脚功能介绍:VCC:AT89S51电源正端输入,接+5V。

VSS:电源地端。

XTAL1:单芯片系统时钟的反相放大器输入端。

XTAL2:系统时钟的反相放大器输出端,一般在设计上只要在XTAL1和XTAL2上接上一只石英振荡晶体系统就可以动作了,此外可以在两引脚与地之间加入一20PF的小电容,可以使系统更稳定,避免噪声干扰而死机。

RESET:AT89S51的重置引脚,高电平动作,当要对晶片重置时,只要对此引脚电平提升至高电平并保持两个机器周期以上的时间,AT89S51便能完成系统重置的各项动作,使得内部特殊功能寄存器之AT89S51内容均被设成已知状态,并且至地址0000H处开始读入程序代码而执行程序。

EA/Vpp:"EA"为英文"ExternalAccess"的缩写,表示存取外部程序代码之意,低电平动作,也就是说当此引脚接低电平后,系统会取用外部的程序代码(存于外部EPROM中)来执行程序。

因此在8031及8032中,EA引脚必须接低电平,因为其内部无程序存储器空间。

如果是使用8751内部程序空间时,此引脚要接成高电平。

此外,在将程序代码烧录至8751内部EPROM时,可以利用此引脚来输入21V的烧录高压(Vpp)。

AT89S51引脚图

AT89S51引脚图,AT89S51单片机引脚说明及管脚定义AT89S51引脚图,AT89S51单片机引脚说明及管脚定义AT89S51引脚图AT89S51是一个低功耗,高性能CMOS 8位单片机,片内含4k Bytes ISP(In-system programmable)的可反复擦写1000次的Flash只读程序存储器,器件采用ATMEL公司的高密度、非易失性存储技术制造,兼容标准MCS -51指令系统及80C51引脚结构,芯片内集成了通用8位中央处理器和ISP Flash存储单元,功能强大的微型计算机的AT89S51可为许多嵌入式控制应用系统提供高性价比的解决方案。

AT89S51具有如下特点:40个引脚,4k Bytes Flash片内程序存储器,128 bytes的随机存取数据存储器(RAM),32个外部双向输入/输出(I/O)口,5个中断优先级2层中断嵌套中断,2个16位可编程定时计数器,2个全双工串行通信口,看门狗(WDT)电路,片内时钟振荡器。

AT89S51引脚图此外,AT89S51设计和配置了振荡频率可为0Hz并可通过软件设置省电模式。

空闲模式下,CPU暂停工作,而RAM定时计数器,串行口,外中断系统可继续工作,掉电模式冻结振荡器而保存RAM的数据,停止芯片其它功能直至外中断激活或硬件复位。

同时该芯片还具有PDIP、TQFP和PLCC等三种封装形式,以适应不同产品的需求。

主要功能特性:·兼容MCS-51指令系统· 4k可反复擦写(>1000次)ISP Flash ROM· 32个双向I/O口· 4.5-5.5V工作电压· 2个16位可编程定时/计数器·时钟频率0-33MHz·全双工UART串行中断口线· 128x8bit内部RAM· 2个外部中断源·低功耗空闲和省电模式·中断唤醒省电模式· 3级加密位·看门狗(WDT)电路·软件设置空闲和省电功能·灵活的ISP字节和分页编程·双数据寄存器指针。

STC89C51单片机引脚功能介绍

STC89C51单片机引脚功能介绍c51单片机引脚功能介绍C51单片机引脚功能介绍单片机的40个引脚大致可分为4类:电源、时钟、控制和i/o引脚。

1.电源:⑴ VCC芯片电源,接+5V;⑵vss-接地端;2.时钟:xtal1、xtal2晶体振荡电路反转输入和输出。

⒊控制线:控制线共有4根,(1) ale/prog:地址锁存启用/片上EPROM编程脉冲①ale功能:用来锁存p0口送出的低8位地址新门户② Prog功能:芯片中带有EPROM的芯片。

在EPROM编程期间,该引脚输入编程脉冲。

⑵psen:外rom读选通信号。

(3) rst/VPD:重置/备用电源。

①rst(reset)功能:复位信号输入端。

② VPD功能:VCC电源故障时,连接备用电源。

⑷ea/vpp:内外rom选择/片内eprom编程电源。

①ea功能:内外rom选择端。

② VPP功能:对于芯片中带有EPROM的芯片,在EPROM编程时使用编程电源VPP。

⒋i/o线89C51有四个8位并行I/O端口:P0、P1、P2和P3端口,共32个引脚。

P3端口还具有第二个功能,用于特殊信号的输入输出和控制信号(属于控制总线)。

拿到一块芯片,想要使用它,首先必须要知道怎样连线,我们用的一块称之为89c51的芯片,下面我们就看一下如何给它连线。

1.电源:当然,这是必要的。

单片机采用5V电源,正极接40针,负极接20针。

2、振蒎电路:单片机是一种时序电路,必须供给脉冲信号才能正常工作,在单片机内部已集成了振荡器,使用晶体振荡器,接18、19脚。

只要买来晶体震荡器,连上就能了,按下图1接上即可。

3.复位引脚:根据下图1中的图纸进行连接。

ea管脚:ea管脚接到正电源端。

至此,一个单片机就接好,通上电,单片机就开始工作了。

我们的第一项任务是用单片机点亮LED。

显然,这个led必须与单片机的引脚连接,否则单片机无法控制它。

除了刚才使用的五个引脚外,单片机上还有35个引脚。

AT89S51单片机引脚说明

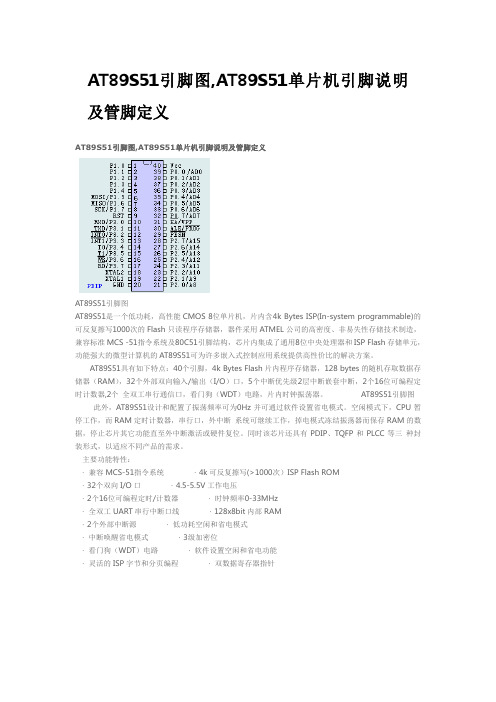

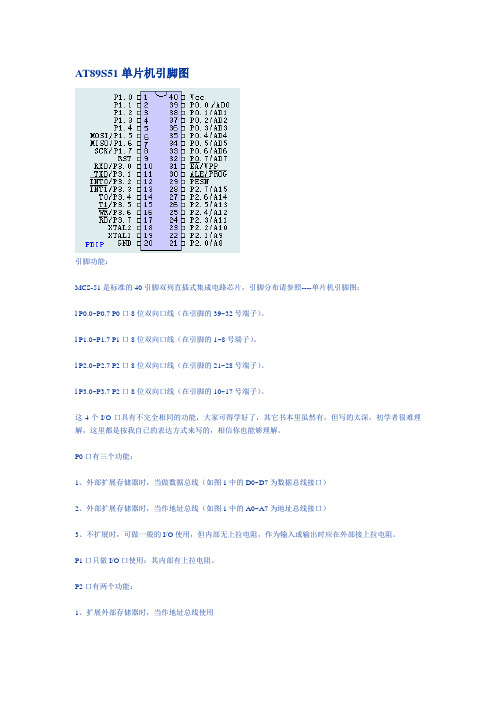

AT89S51单片机引脚图引脚功能:MCS-51是标准的40引脚双列直插式集成电路芯片,引脚分布请参照----单片机引脚图:l P0.0~P0.7 P0口8位双向口线(在引脚的39~32号端子)。

l P1.0~P1.7 P1口8位双向口线(在引脚的1~8号端子)。

l P2.0~P2.7 P2口8位双向口线(在引脚的21~28号端子)。

l P3.0~P3.7 P2口8位双向口线(在引脚的10~17号端子)。

这4个I/O口具有不完全相同的功能,大家可得学好了,其它书本里虽然有,但写的太深,初学者很难理解,这里都是按我自已的表达方式来写的,相信你也能够理解。

P0口有三个功能:1、外部扩展存储器时,当做数据总线(如图1中的D0~D7为数据总线接口)2、外部扩展存储器时,当作地址总线(如图1中的A0~A7为地址总线接口)3、不扩展时,可做一般的I/O使用,但内部无上拉电阻,作为输入或输出时应在外部接上拉电阻。

P1口只做I/O口使用:其内部有上拉电阻。

P2口有两个功能:1、扩展外部存储器时,当作地址总线使用2、做一般I/O口使用,其内部有上拉电阻;P3口有两个功能:除了作为I/O使用外(其内部有上拉电阻),还有一些特殊功能,由特殊寄存器来设置,具体功能请参考我们后面的引脚说明。

有内部EPROM的单片机芯片(例如8751),为写入程序需提供专门的编程脉冲和编程电源,这些信号也是由信号引脚的形式提供的,即:编程脉冲:30脚(ALE/PROG)编程电压(25V):31脚(EA/Vpp)接触过工业设备的兄弟可能会看到有些印刷线路板上会有一个电池,这个电池是干什么用的呢?这就是单片机的备用电源,当外接电源下降到下限值时,备用电源就会经第二功能的方式由第9脚(即RST/VPD)引入,以保护内部RAM中的信息不会丢失。

(注:这些引脚的功能应用,除9脚的第二功能外,在“新动力2004版”学习套件中都有应用到。

)在介绍这四个I/O口时提到了一个“上拉电阻”那么上拉电阻又是一个什么东东呢?他起什么作用呢?都说了是电阻那当然就是一个电阻啦,当作为输入时,上拉电阻将其电位拉高,若输入为低电平则可提供电流源;所以如果P0口如果作为输入时,处在高阻抗状态,只有外接一个上拉电阻才能有效。

AT89S51单片机简介

AT89S51单⽚机简介⼀、AT89S51单⽚机简介AT89S51 为ATMEL 所⽣产的可电⽓烧录清洗的8051 相容单芯⽚,其内部程序代码容量为4KB (⼀)、AT89S51主要功能列举如下:1、为⼀般控制应⽤的8 位单芯⽚2、晶⽚内部具时钟振荡器(传统最⾼⼯作频率可⾄12MHz)3、内部程式存储器(ROM)为4KB4、内部数据存储器(RAM)为128B5、外部程序存储器可扩充⾄64KB6、外部数据存储器可扩充⾄64KB7、32 条双向输⼊输出线,且每条均可以单独做I/O 的控制8、5 个中断向量源9、2 组独⽴的16 位定时器10、1 个全多⼯串⾏通信端⼝11、8751 及8752 单芯⽚具有数据保密的功能12、单芯⽚提供位逻辑运算指令(⼆)、AT89S51各引脚功能介绍:VCC:Array AT89S51 电源正端输⼊,接+5V。

VSS:电源地端。

XTAL1:单芯⽚系统时钟的反相放⼤器输⼊端。

XTAL2:系统时钟的反相放⼤器输出端,⼀般在设计上只要在XTAL1 和XTAL2上接上⼀只⽯英振荡晶体系统就可以动作了,此外可以在两引脚与地之间加⼊⼀20PF 的⼩电容,可以使系统更稳定,避免噪声⼲扰⽽死机。

RESET:AT89S51的重置引脚,⾼电平动作,当要对晶⽚重置时,只要对此引脚电平提升⾄⾼电平并保持两个机器周期以上的时间,AT89S51便能完成系统重置的各项动作,使得内部特殊功能寄存器之内容均被设成已知状态,并且⾄地址0000H处开始读⼊程序代码⽽执⾏程序。

EA/Vpp:"EA"为英⽂"External Access"的缩写,表⽰存取外部程序代码之意,低电平动作,也就是说当此引脚接低电平后,系统会取⽤外部的程序代码(存于外部EPROM中)来执⾏程序。

因此在8031及8032中,EA引脚必须接低电平,因为其内部⽆程序存储器空间。

如果是使⽤8751 内部程序空间时,此引脚要接成⾼电平。

单片机引脚说明(89C51为例)

T89C2051是精简版的51单片机,精简掉了P0口和P2口,只有20引脚,但其内部集成了一个很实用的模拟比较器,特别适合开发精简的51应用系统,毕竟很多时候我们开发简单的产品时用不了全部32个I/O口,用AT89C2051更合适,芯片体积更小,而且AT89C2051的工作电压最低为2.7V,因此可以用来开发两节5号电池供电的便携式产品。

本文以ATMEL公司生产的51系列家族的AT89S51和AT89C2051两种单片机来讲解,两种单片机是目前最常用的单片机,其中 AT89S51为标准51单片机,当然其功能比早期的51单片机更强大,支持ISP在系统编程技术,内置硬件看门狗。

一、AT89S51单片机引脚介绍AT89S51有PDIP、PLCC、TQFP三种封装方式,其中最常见的就是采用40Pin 封装的双列直接PDIP封装,外形结构下图。

芯片共有40个引脚,引脚的排列顺序为从靠芯片的缺口(见右图)左边那列引脚逆时针数起,依次为1、2、3、4。

40,其中芯片的1脚顶上有个凹点(见右图)。

在单片机的40个引脚中,电源引脚2根,外接晶体振荡器引脚2根,控制引脚4根以及4组8位可编程I/O引脚32根。

1、主电源引脚(2根)VCC(Pin40):电源输入,接+5V电源GND(Pin20):接地线2、外接晶振引脚(2根)XTAL1(Pin19):片内振荡电路的输入端XTAL2(Pin20):片内振荡电路的输出端3、控制引脚(4根)RST/VPP(Pin9):复位引脚,引脚上出现2个机器周期的高电平将使单片机复位。

ALE/PROG(Pin30):地址锁存允许信号PSEN(Pin29):外部存储器读选通信号EA/VPP(Pin31):程序存储器的内外部选通,接低电平从外部程序存储器读指令,如果接高电平则从内部程序存储器读指令。

芯片实物图片芯片引脚功能4、可编程输入/输出引脚(32根)AT89S51单片机有4组8位的可编程I/O口,分别位P0、P1、P2、P3口,每个口有8位(8根引脚),共32根。

第二章 AT89S51单片机的硬件结构 - 副本

所能表示的符号数的有效范围(-128 ~ +127),运算结果是错

误的,即产生了溢出;否则, OV=0,则表示运算结果正确, 即未产生溢出。溢出的判断:OV=C6⊕C7 ② 在乘法运算中,OV=1表示乘积超过255,即乘积分别在B(高8 位)与A(低8位)中;否则,OV=0表示乘积只在A中。 ③ 在除法运算中,OV=1表示除数为0,除法不能进行;否则, OV=0表示除数不为0,除法可正常进行。 【注意】对于加/减运算,无论参与运算的数是带符号数还是无符

问片内ROM;若访问的地址范围超过4KB时,CPU将自动访问

外部ROM。

EA保持低电平,则访问外部ROM。

第二功能为+12V编程电源输入。

2.3 AT89S51的CPU

CPU是单片机内部的核心部件,完成运算和 控制操作。包括运算器、控制器以及若干 寄存器等部件组成。 CPU内部由上亿个晶体管组成,由于晶体管 的“截止”和“导通”功能,正好对应二 进制的“0”和“1”,因此,就具备了处 理信息的能力。

1

0

第2组

10H ~ 17H

18H ~ 1FH

1 1 第3组 P (PSW.0)—— 奇偶标志位

① 表明累加器A中1的个数的奇偶性:若1的个数为偶数,则P=0; 若1的个数为奇数,则P=1 。 ② 在每个指令周期由硬件根据A的内容对P位进行臵位或复位。

PSW(程序状态字)

OV (PSW.2)—— 溢出标志位

第二功能 RXD TXD

INT0 INT1 T0 T1 WR RD

功能含义 串行数据接收 串行数据发送

外部中断 0 申请 外部中断 1 申请 定时器/计数器 0 计数输入 定时器/计数器 1 计数输入 外部RAM写选通 外部RAM读选通

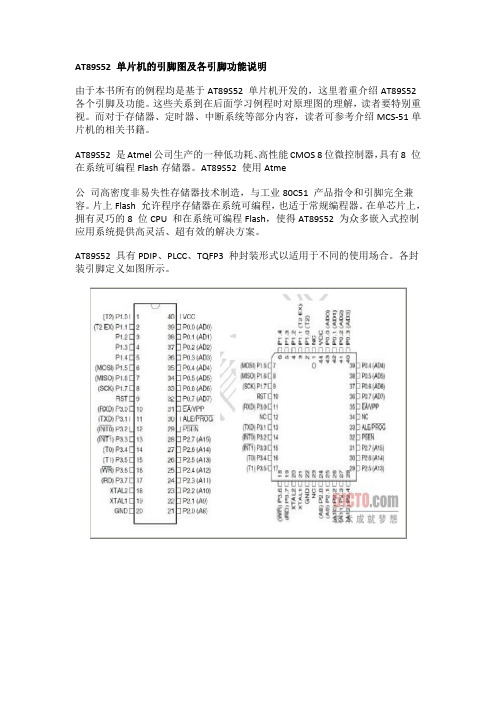

AT89S52 (51)单片机的引脚图及各引脚功能说明

AT89S52 单片机的引脚图及各引脚功能说明由于本书所有的例程均是基于AT89S52 单片机开发的,这里着重介绍AT89S52 各个引脚及功能。

这些关系到在后面学习例程时对原理图的理解,读者要特别重视。

而对于存储器、定时器、中断系统等部分内容,读者可参考介绍MCS-51单片机的相关书籍。

AT89S52 是Atmel公司生产的一种低功耗、高性能CMOS 8位微控制器,具有8 位在系统可编程Flash存储器。

AT89S52 使用Atme公司高密度非易失性存储器技术制造,与工业80C51 产品指令和引脚完全兼容。

片上Flash 允许程序存储器在系统可编程,也适于常规编程器。

在单芯片上,拥有灵巧的8 位CPU 和在系统可编程Flash,使得AT89S52 为众多嵌入式控制应用系统提供高灵活、超有效的解决方案。

AT89S52 具有PDIP、PLCC、TQFP3 种封装形式以适用于不同的使用场合。

各封装引脚定义如图所示。

图AT89S52引脚图下面简单介绍AT89S52 各引脚的功能,更多信息请查阅Atmel公司的技术文档。

VCC:电源。

/GND:地。

P0 口:P0 口是一个8 位漏极开路的双向I/O 口。

作为输出口,每位能驱动8 个TTL逻辑电平。

对P0 端口写“1”时,引脚用做高阻抗输入。

当访问外部程序和数据存储器时,P0 口也被作为低8 位地址/数据复用。

在这种模式下,P0 具有内部上拉电阻。

在Flash编程时,P0 口也用来接收指令字节;在程序校验时,输出指令字节。

在程序校验时,需要外部上拉电阻。

P1 口:P1 口是一个具有内部上拉电阻的8 位双向I/O 口,P1 输出缓冲器能驱动4 个TT逻辑电平。

当对P1 端口写“1”时,内部上拉电阻把端口拉高,此时可以作为输入口使用。

当作为输入使用时,被外部拉低的引脚由于内部电阻的原因,将输出电流(IIL)。

此外,和分别作为定时器/计数器2 的外部计数输入(T2)和定时器/计数器2的触发输入(T2EX),具体如表1-1 所示。

89C51单片机引脚及其功能优秀课件

2.1.1 89C51单片机的基本组成

89C51单片机还有一种低电压的型号,即89LV51, 除了电压范围有区别之外,其余特性与89C51完 全一致。

89C51/LV51是一种低功耗/低电压、高性能的8位 单片机。它采用了CMOS工艺和高密度非易失性 存储器(NURAM)技术,而且其输出引脚和指 令系统都与MCS51兼容;

EA 制 码 存

RESET

器器

ALU 中断、串行口和定时器

PSW

P1锁存器

P3锁存器

程序地址 寄存器 缓冲器

PC增1 PC

DPTR

控制器

OSC

XTAL1 XTAL2

P1驱动器 P1.0-P1.7

P3驱动器 P3.0-P3.7 返回 9

二、结构组成

(一)、中央处理单元(CPU) (二)、存储器 (三)、I/O接口

返回

10

1、中央处理单元(89C51CPU)

1)运算器 • 2)控制器

返回

11

1)运算器

(1)8位的ALU:可对4位、8位、16位数据进行操作。

(2)8位累加器ACC(A):它经常作为一个运算数经 暂存器2进入ALU的输入端,与另一个来自暂存器1的运 算数进行运算,运算结果又送回ACC。

(3)8位程序状态寄存器PSW:指示指令执行后的状态 信息供程序查询和判别用。

30

1、P0口:

漏极开路的8位准双向I/O口,每位能驱动8 个LS型TTL负载。

在CPU访问片外存储器时,P0口为分时复用 的低8位地址总线和8位数据总线。

在Flash ROM编程时,P0端口接受指令字 节;而在校验程序时,则输出指令字节。

31

2、P1口:

带 内 部 上 拉 电 阻 的 8 位 准 双 向 I/O 端 口,每位能驱动4个LS型TTL负载。

89S51引脚及说明

单片机AT89S51引脚说明AT89C51是一种带4K字节闪烁可编程可擦除只读存储器(FPEROM—Falsh Programmable And Erasable Read Only Memory)的低电压,高性能CMOS8位微处理器,俗称单片机。

该器件采用ATMEL高密度非易失存储器制造技术制造,与工业标准的MCS-51指令集和输出管脚相兼容。

由于将多功能8位CPU和闪烁存储器组合在单个芯片中,ATMEL的AT89C51是一种高效微控制器,为很多嵌入式控制系统提供了一种灵活性高且价廉的方案。

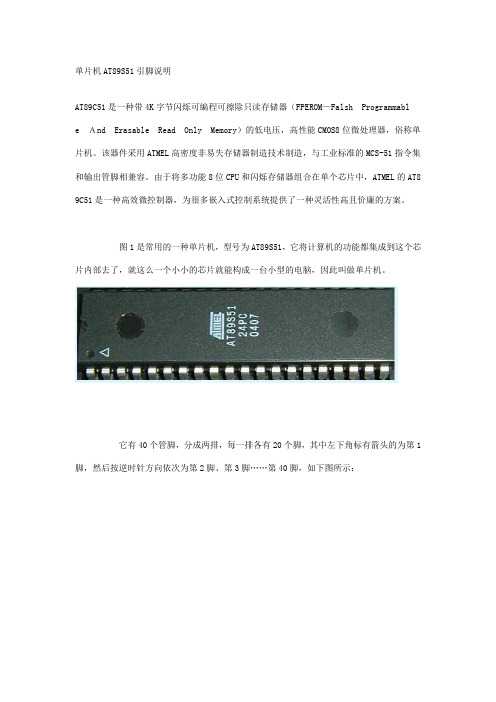

图1是常用的一种单片机,型号为AT89S51,它将计算机的功能都集成到这个芯片内部去了,就这么一个小小的芯片就能构成一台小型的电脑,因此叫做单片机。

它有40个管脚,分成两排,每一排各有20个脚,其中左下角标有箭头的为第1脚,然后按逆时针方向依次为第2脚、第3脚……第40脚,如下图所示:在40个管脚中,其中有32个脚可用于各种控制,比如控制小灯的亮与灭、控制电机的正转与反转、控制电梯的升与降等,这32个脚叫做单片机的“端口”,在单片机技术中,每个端口都有一个特定的名字,比如第一脚的那个端口叫做“P1.0”,由于本次试验仅仅控制一个小灯的亮与灭,由此只用一个端口就行了,我们就用第一脚的P1.0端口吧,如下图所示:1.主要特性:·与MCS-51 兼容·4K字节可编程闪烁存储器寿命:1000写/擦循环数据保留时间:10年·全静态工作:0Hz-24Hz·**程序存储器锁定·128*8位内部RAM·32可编程I/O线·两个16位定时器/计数器·5个中断源·可编程串行通道·低功耗的闲置和掉电模式·片内振荡器和时钟电路2.管脚说明:VCC:供电电压。

GND:接地。

P0口:P0口为一个8位漏级开路双向I/O口,每脚可吸收8TTL门电流。

第4章 AT89S51单片机的中断系统

ES=1,允许串行口中断。

(3)ET1——定时器/计数器T1的溢出中断允许位。

ET1=0,禁止T1溢出中断。

ET1=1,允许T1溢出中断。

21

(4)EX1——外部中断1中断允许位。 EX1=0,禁止外部中断1中断。 EX1=1,允许外部中断1中断。 (5)ET0——定时器/计数器T0的溢出中断允许位。 ET0=0,禁止T0溢出中断。 ET0=1,允许T0溢出中断。 (6)EX0——外部中断0中断允许位。 EX0=0,禁止外部中断0中断。

于在同一个优先级内,还同时存在另一个辅助优先级结

构,其查询顺序见表4-1。

30

表4-1

同级中断的查询次序

由此可见,各中断源在同一个优先级的条件下,外 部中断0的中断优先权最高,串行口中断优先权最低。

31

【例4-2】 IP寄存器初始化,AT89S51的两个外中断请求 为高优先级,其他中断请求为低优先级。

37

外部中断响应的最长时间为8个机器周期。在CPU

进行中断标志查询时,刚好才开始执行RETI或访问IE

或IP的指令,需执行完指令再继续执行一条指令后,才

高 级 中 断 请 求 低 级 中 断 请 求

IE1

TF1 TI RI

SCON

ET1

PS ES EA

中断标 志位

中断源 允许

总允许

中断 优先 级

矢量 地址

图4-2 AT89S51的中断系统结构示意图

4.2.1 中断请求源 由图4-2可见,AT89S51中断系统共有5个中断请 求源: (1)INT0*——外部中断请求0,中断请求信号

AT89S51引脚图,AT89S51单片机引脚说明及管脚定义

AT89S51引脚图,AT89S51单⽚机引脚说明及管脚定义AT89C51单⽚机简介AT89C51是⼀种带4K字节闪烁可编程可擦除只读存储器(FPEROM—Falsh Programmable and Erasable Read Only Memory)的低电压,⾼性能CMOS8位微处理器,俗称单⽚机。

AT89C2051是⼀种带2K字节闪烁可编程可擦除只读存储器的单⽚机。

单⽚机的可擦除只读存储器可以反复擦除100次。

该器件采⽤ATMEL⾼密度⾮易失存储器制造技术制造,与⼯业标准的MCS-51指令集和输出管脚相兼容。

由于将多功能8位CPU和闪烁存储器组合在单个芯⽚中,ATMEL的AT89C51是⼀种⾼效微控制器,AT89C2051是它的⼀种精简版本。

AT89C单⽚机为很多嵌⼊式控制系统提供了⼀种灵活性⾼且价廉的⽅案。

1.主要特性:·与MCS-51 兼容·4K字节可编程闪烁存储器寿命:1000写/擦循环数据保留时间:10年·全静态⼯作:0Hz-24Hz·三级程序存储器锁定·128*8位内部RAM·32可编程I/O线·两个16位定时器/计数器·5个中断源·可编程串⾏通道·低功耗的闲置和掉电模式·⽚内振荡器和时钟电路2.管脚说明:VCC:供电电压。

GND:接地。

P0⼝:P0⼝为⼀个8位漏级开路双向I/O⼝,每脚可吸收8TTL门电流。

当P1⼝的管脚第⼀次写1时,被定义为⾼阻输⼊。

P0能够⽤于外部程序数据存储器,它可以被定义为数据/地址的第⼋位。

在FIASH编程时,P0 ⼝作为原码输⼊⼝,当FIASH进⾏校验时,P0输出原码,此时P0外部必须被拉⾼。

P1⼝:P1⼝是⼀个内部提供上拉电阻的8位双向I/O⼝,P1⼝缓冲器能接收输出4TTL门电流。

P1⼝管脚写⼊1后,被内部上拉为⾼,可⽤作输⼊,P1⼝被外部下拉为低电平时,将输出电流,这是由于内部上拉的缘故。

单片机原理及应用第4章 AT89S51的中断系统

1、TCON:定时器/计数器的控制寄存器

T1

T0

INT1 INT 0

T1的溢出中 断请求标志 位TF1, T1溢出时置 位,向CPU 申请中断

外部中断请 求标志位 若INT0引 脚上有中断 来,置IE1, 否则清0

外部中断 触发方式

当89S51复位 后,TCON=0

中断源

外部中断0 T0溢出中断 外部中断1 T1溢出中断 串行口中断

中断级别 最高

最低

例 设置IP寄存器的初始值,使2个外中断请求为 高优先级,其它中断请求为低优先级。

(1)用位操作指令 SETB PX0 SETB PX1 CLR PS CLR PT0 CLR PT1

(2)用字节操作指令 MOV IP,#05H

第 4章 AT89S51的中断系统

4.1 中断的概念 中断:用于实时测控

-对应-软件查询方式

4.2 AT89S51中断系统的结构

5个中断源,两级优先级。

中断系统结构示意图如下图所示。

中断标志 寄存器

中断允许 寄存器

中断优先级 寄存器

从图可见:AT89S51有

5个中断源: INT 0 , T0, INT1, T1, (TX,RX)

主程序 初始化 部分

(1)设置IE。 (2)设置IP。 (3)若是外部中断源,设置IT0,TT1触发

方式。

(4)编写中断服务程序。

例 假设允许外部中断0中断,并设定它为高级中断,其它 中断源为低级中断,采用跳沿触发方式。编写初始化程 序段:

解:

SETB EA SETB EX0 SETB PX0 SETB IT0

“1”高优先级 “0”低优先级

单片机外部引脚与内部结构

成 数据缓冲区:(80B)

字节地址:00H~7FH

一般使用30H~7FH

11:06

应用电子系

26

一、单片机外部引脚与内部结构

AT89S51单片机的内部结构

单 片 片内ROM 机 ROM用于存放程序、原始数据及表格。 的 8051:片内4K掩膜ROM 组 8031:片内无ROM 成 8751:片内4K EPROM

AT89S51单片机的内部结构

单 并行I/O口

片 ✓ MCS-51系列单片机有4个8位并行I/O口:

机 P0、P1、P2、P3共占了32根I/O引脚单片机

的 组

扩展时,这些I/O引脚又作为扩展总线用。 ✓ P0口作为地址/数据总线,分时输出低8位地 址和传送8位数据;

成 ✓ P2口作为高8位地址总线;

成 4. 片内16位定时器/计数器

5. 片内中断处理系统

6. 片内全双工串行I/O口

11:06

应用电子系

14

一、单片机外部引脚与内部结构

AT89S51单片机的内部结构

单 片 机 的 组 成

11:06

应用电子系

15

一、单片机外部引脚与内部结构

AT89S51单片机的内部结构

单

片 机

中央处理器CPU 主要指运算器、控制器

应用电子系

23

一、单片机外部引脚与内部结构

AT89S51单片机的内部结构

单 片 机

内部RAM ✓单片机内部数据RAM共256字节。分为低 128B和高128B地址空间。

的 ✓低128B地址空间的RAM常称为片内RAM;

组 ✓高128B地址空间的RAM 称为特殊功能寄

成 存器SFR。

✓18个SFR只占用了21B供用户使用。其他的 107B系统保留。

AT89S51单片机

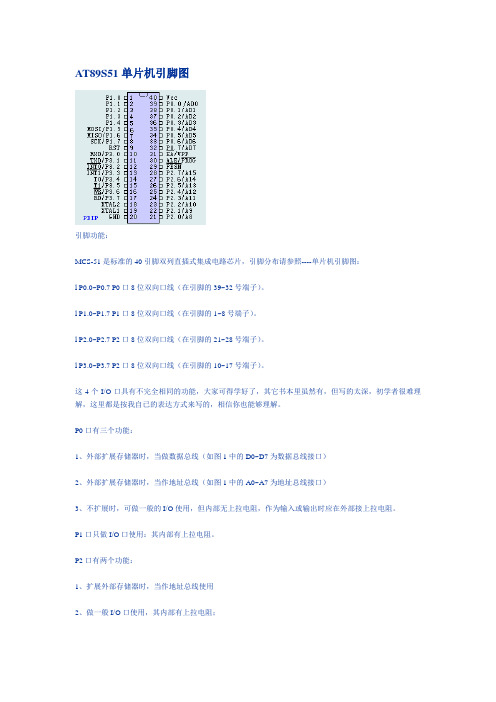

AT89S51单片机引脚图引脚功能:MCS-51是标准的40引脚双列直插式集成电路芯片,引脚分布请参照----单片机引脚图:l P0.0~P0.7 P0口8位双向口线(在引脚的39~32号端子)。

l P1.0~P1.7 P1口8位双向口线(在引脚的1~8号端子)。

l P2.0~P2.7 P2口8位双向口线(在引脚的21~28号端子)。

l P3.0~P3.7 P2口8位双向口线(在引脚的10~17号端子)。

这4个I/O口具有不完全相同的功能,大家可得学好了,其它书本里虽然有,但写的太深,初学者很难理解,这里都是按我自已的表达方式来写的,相信你也能够理解。

P0口有三个功能:1、外部扩展存储器时,当做数据总线(如图1中的D0~D7为数据总线接口)2、外部扩展存储器时,当作地址总线(如图1中的A0~A7为地址总线接口)3、不扩展时,可做一般的I/O使用,但内部无上拉电阻,作为输入或输出时应在外部接上拉电阻。

P1口只做I/O口使用:其内部有上拉电阻。

P2口有两个功能:1、扩展外部存储器时,当作地址总线使用2、做一般I/O口使用,其内部有上拉电阻;P3口有两个功能:除了作为I/O使用外(其内部有上拉电阻),还有一些特殊功能,由特殊寄存器来设置,具体功能请参考我们后面的引脚说明。

有内部EPROM的单片机芯片(例如8751),为写入程序需提供专门的编程脉冲和编程电源,这些信号也是由信号引脚的形式提供的,即:编程脉冲:30脚(ALE/PROG)编程电压(25V):31脚(EA/Vpp)接触过工业设备的兄弟可能会看到有些印刷线路板上会有一个电池,这个电池是干什么用的呢?这就是单片机的备用电源,当外接电源下降到下限值时,备用电源就会经第二功能的方式由第9脚(即RST/VPD)引入,以保护内部RAM中的信息不会丢失。

(注:这些引脚的功能应用,除9脚的第二功能外,在“新动力2004版”学习套件中都有应用到。

)在介绍这四个I/O口时提到了一个“上拉电阻”那么上拉电阻又是一个什么东东呢?他起什么作用呢?都说了是电阻那当然就是一个电阻啦,当作为输入时,上拉电阻将其电位拉高,若输入为低电平则可提供电流源;所以如果P0口如果作为输入时,处在高阻抗状态,只有外接一个上拉电阻才能有效。

AT89S52 (51)单片机的引脚图及各引脚功能说明之欧阳育创编

AT89S52 单片机的引脚图及各引脚功能说明由于本书所有的例程均是基于AT89S52 单片机开发的,这里着重介绍AT89S52 各个引脚及功能。

这些关系到在后面学习例程时对原理图的理解,读者要特别重视。

而对于存储器、定时器、中断系统等部分内容,读者可参考介绍MCS-51单片机的相关书籍。

AT89S52 是Atmel公司生产的一种低功耗、高性能CMOS 8位微控制器,具有8 位在系统可编程Flash存储器。

AT89S52 使用Atme公司高密度非易失性存储器技术制造,与工业80C51 产品指令和引脚完全兼容。

片上Flash 允许程序存储器在系统可编程,也适于常规编程器。

在单芯片上,拥有灵巧的8 位CPU 和在系统可编程Flash,使得AT89S52 为众多嵌入式控制应用系统提供高灵活、超有效的解决方案。

AT89S52 具有PDIP、PLCC、TQFP3 种封装形式以适用于不同的使用场合。

各封装引脚定义如图1.2所示。

图 1.2 AT89S52引脚图下面简单介绍AT89S52 各引脚的功能,更多信息请查阅Atmel 公司的技术文档。

VCC:电源。

GND:地。

P0 口:P0 口是一个8 位漏极开路的双向I/O 口。

作为输出口,每位能驱动8 个TTL逻辑电平。

对P0 端口写“1”时,引脚用做高阻抗输入。

当访问外部程序和数据存储器时,P0 口也被作为低8 位地址/数据复用。

在这种模式下,P0 具有内部上拉电阻。

在Flash编程时,P0 口也用来接收指令字节;在程序校验时,输出指令字节。

在程序校验时,需要外部上拉电阻。

P1 口:P1 口是一个具有内部上拉电阻的8 位双向I/O 口,P1 输出缓冲器能驱动4 个TT逻辑电平。

当对P1 端口写“1”时,内部上拉电阻把端口拉高,此时可以作为输入口使用。

当作为输入使用时,被外部拉低的引脚由于内部电阻的原因,将输出电流(IIL)。

此外,P1.0 和P1.2 分别作为定时器/计数器2 的外部计数输入(P1.0/T2)和定时器/计数器2的触发输入(P1.1/T2EX),具体如表1-1 所示。

AT89S52 (51)单片机的引脚图及各引脚功能说明之欧阳法创编

AT89S52 单片机的引脚图及各引脚功能说明由于本书所有的例程均是基于AT89S52 单片机开发的,这里着重介绍AT89S52 各个引脚及功能。

这些关系到在后面学习例程时对原理图的理解,读者要特别重视。

而对于存储器、定时器、中断系统等部分内容,读者可参考介绍MCS-51单片机的相关书籍。

AT89S52 是Atmel公司生产的一种低功耗、高性能CMOS 8位微控制器,具有8 位在系统可编程Flash 存储器。

AT89S52 使用Atme公司高密度非易失性存储器技术制造,与工业80C51 产品指令和引脚完全兼容。

片上Flash 允许程序存储器在系统可编程,也适于常规编程器。

在单芯片上,拥有灵巧的8 位CPU 和在系统可编程Flash,使得AT89S52 为众多嵌入式控制应用系统提供高灵活、超有效的解决方案。

AT89S52 具有PDIP、PLCC、TQFP3 种封装形式以适用于不同的使用场合。

各封装引脚定义如图1.2所示。

图 1.2 AT89S52引脚图下面简单介绍AT89S52 各引脚的功能,更多信息请查阅Atmel公司的技术文档。

VCC:电源。

GND:地。

P0 口:P0 口是一个8 位漏极开路的双向I/O 口。

作为输出口,每位能驱动8 个TTL逻辑电平。

对P0 端口写“1”时,引脚用做高阻抗输入。

当访问外部程序和数据存储器时,P0 口也被作为低8 位地址/数据复用。

在这种模式下,P0 具有内部上拉电阻。

在Flash编程时,P0 口也用来接收指令字节;在程序校验时,输出指令字节。

在程序校验时,需要外部上拉电阻。

P1 口:P1 口是一个具有内部上拉电阻的8 位双向I/O 口,P1 输出缓冲器能驱动4 个TT逻辑电平。

当对P1 端口写“1”时,内部上拉电阻把端口拉高,此时可以作为输入口使用。

当作为输入使用时,被外部拉低的引脚由于内部电阻的原因,将输出电流(IIL)。

此外,P1.0 和P1.2 分别作为定时器/计数器2 的外部计数输入(P1.0/T2)和定时器/计数器2的触发输入(P1.1/T2EX),具体如表1-1 所示。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

(2) P0口作为通用I/O口输入使用时,在输入数据前,应先向P0口写 “1”, 此时锁存器的Q端为“0”, 使输出级的两个场效应管V1、V2 均截止,引脚处于悬浮状态,才可作高阻输入。

2020/3/16

15

② ������������������������ :第二功能,对片内 Flash编程的编程脉冲输入。

4.3 AT89S51单片机的控制引脚(4个)

4、 ������������������������ (Program Strobe ENable,29脚)

片外程序存储器读选通信号 低电平有效。

2、AT89S51单片机的P1口

P1口:8位 准双向I/O口,具有内部上拉电阻。

注意: P1口的几只引脚:P1.5/MOSI、 P1.6/MISO和P1.7/SCK,可用作片内 Flash存储器的串行编程和校验,分别 是串行数据输入、输出和移位脉冲引脚。 P1口可驱动4个LS型TTL负载。

23 2020/3/16

(1)电源及时钟引脚 VCC、VSS;XTAL1、XTAL2。 (2)控制引脚 PSEN*、ALE/PROG*、 EA*/VPP、RST(RESET)。 (3)I/O口引脚 P0、P1、P2、P3,4个8位I/O口。

11

4.2 AT89S51单片机的电源及时钟引脚

2020/3/16

1、电源引脚 (1)VCC(40脚):+5V电源。 (2)VSS(20脚):数字地。 2、时钟引脚 (1)XTAL1(19脚):输入端。 使用片内振荡器,应接外部石英晶 体和微调电容。

26 2020/3/16

P2口位电路结构

它包括1个输出锁存器、2个三态缓冲器、输出驱动电路和 转接开关MUX组成。

P2口工作原理

1)P2口作为地址口 控制信号为1,MUX上接。 当地址为1,FET管V1截止,P2.x=1。

P2口工作原理

2)P2口作为通用的I/O接口

控制信号为0,MUX下接Q非端,与P1口工作原理类似。

CPU对各种功能部件控制 采用特殊功能寄存器SFR

(8)中断系统:5个中断源、5个中断向量; (Special Function

(9)特殊功能寄存器(SFR)26个; (10)低功耗的空闲模式和掉电模式;

Register)的集中控制方 式。

(11)在线可编程功能ISP(In System Program);

2020/3/16

13

4.3 AT89S51单片机的控制引脚(4个)

2020/3/16

2、 ������������ /VPP(31脚)

(Enable Address/Voltage Pulse of Programing)

① ������������:第一功能:外部程序存储器访

问允许控制。

a. ������������ =1

1、AT89S51单片机引脚的排列与分类 2、AT89S51单片机的电源及时钟引脚 3、AT89S51单片机的控制引脚 4、AT89S51单片机的I/0引脚及内部电路

4.1 AT89S51单片机引脚的排列与分类

2020/3/16

2020/3/16

9

2020/3/16

2020/3/16

按功能分3类:

●作为地址输出线时,P2口输出高8位地址,P0口输出 低8位地址,寻址64KB地址空间。 ●作为通用I/O口时,为准双向口。功能与P1口一样。 ●P2口大多 作为高8位地址总线口使用,这时就不能再 作为通用I/0口使用。

2020/3/16

4、AT89S51单片机的P3口

P3口:8位,准双向I/O口 有内部上拉电阻。

16 2020/3/16

4.4 AT89S51单片机的I/O口引脚及内部电路

17 2020/3/16

1、AT89S51单片机的P0口

2020/3/16

P0口:8位 漏极开路的双向I/O口

作为系统总线用,低8位地址总线及数 据总线分时复用端口,是双向口。

也可作通用I/O口,漏极需加上拉电阻, 这时为准双向口。 可驱动8个LS型TTL负载。

18

P0口位电路结构

P0口是一个三态双向口,可作为地址/数据分时复用口,也 可作为通用的I/O接口。 它包括1个输出锁存器、2个三态缓冲器、输出驱动电路和 输出控制电路组成。

P0口工作原理

1)P0口作为地址/数据分时复用口 控制信号为1,MUX上接,调试与门开启。 当地址/数据为1,FET管V2通,V1截止,P0.x=1。

P3.0

RXD

串行口输入

P3.1

TXD

串行口输出

P3.2

INT0

外部中断0

P3.3

INT1

外部中断1

P3.4

T0

计数器T0输入

P3.5

T1

计数器T1输入

P3.6

WR

外部存储器写选通

端口使用注意P3.事7 项

RD

外部存储器读选通

1)P0口做通用I/O时,需要外接上拉电阻,其余不用接;

2)所有端口,做通用I/O,读引脚时,先写1。

可作为通用I/O口使用。可驱动4个LS型 TTL负载。 P3口还可提供第二功能,定义见下表。 应熟记各脚的第二功能。

31 2020/3/16

P3口位电路结构

它包括1个输出锁存器、2个三态缓冲器、输出驱动电路和 与非门组成。

2020/3/16

2020/3/16

P3口第二功能

引脚名称

第二功能

功能含义

(12)数据指针2个,方便对片外RAM的访问。

2020/3/16

Байду номын сангаас

程序状态字寄存器PSW

①Cy(Carry):进位/借位标志位。 ④ RS1、RS0( Register Select ) ):

工作寄存器组(区)选择标志位。

⑤ OV(Overflow):溢出标志位 ⑥ P(Parity):奇偶校验位。

2020/3/16

AT89S51单片机的存储器结构

4

与AT89C51相比, 新增5个SFR: DP1L、DP1H、 AUXR、AUXR1和 WDTRST

堆栈指针SP

指示栈顶在内部RAM中的位置。可指向内部RAM OOH~7FH的任何单元。 堆栈向上生长。单片机复位后,SP为07H,堆栈从08H单元开始,由于 08H~1FH单元分别是属于1~3组的工作寄存器区,最好在复位后把SP值 改置为60H或更大的值,避免堆栈与工作寄存器冲突。 堆栈主要为子程序调用和中断操作而设。保护断点和现场。

2020/3/16

35

I/O共同点、不同点

2020/3/16

外部引脚

2020/3/16

习题

1、AT89S51单片机共有多少I/O引脚? 它们和单片机对外的地址总线和数据总线有何关系 。

2、 AT89S51单片机除P3口以外的控制线还有几根? 每一根控制线的作用是什么?

3、从输出改为读入时,为什么I/O口要先输入高电平1? 4、 P0口作为通用的I/O接口,为什么要接上拉电阻?

P0口工作原理

2)P0口作为通用的I/O接口

控制信号为0,MUX下接Q非端,与门输出0,V2截止,内部总线上数 据输出(要输出1必须接上拉电阻)。 读入时,先对内部总线置1,确保V1截止,读引脚打开,P0.x信息经过 缓冲器输入内部总线,或读锁存器打开使锁存器数据输入内部总线。。

当P0口作通用I/O接口时,应注意以下两点:

2020/3/16

4KB Flash无效。

14

② VPP:第二功能,对片内Flash编程,

接编程电压。

4.3 AT89S51单片机的控制引脚(4个)

3、ALE/������������������������ (30脚)

(Address Latch Enable/PROGrammin)

① ALE:第一功能,地址锁存允许控制 ALE为访问外部存储器提供低8位地 址锁存信号,下降沿有效,将低8位 地址锁存在片外地址锁存器中。单片 机运行时,ALE端一直有正脉冲信号 输出,频率为时钟fosc的1/6。 注意,每当AT89S51访问外部RAM时 (执行MOVX类指令),要丢失一个 ALE脉冲。 可用软件来禁止ALE输出,将特殊功 能寄存器AUXR(地址8EH,后面介 绍)的第0位(ALE禁止位)置1。

单片机基础与实践

主讲人:熊开封 单 位:信息工程学院电子工程系

2020/3/16

1

复习

(1)8位微处理器(CPU);

(2)数据存储器(128B RAM);

(3)程序存储器(4KB Flash ROM);

(4)4个8位并行I/O口(P0口~P3口);

(5)1个全双工异步串口;

(6)2个16位定时器/计数器; (7)1个看门狗定时器;

(1)保护断点。子程序调用及中断服务子程序调用,最终都要返回主程 序。应预先把主程序断点在堆栈中保护起来,为程序正确返回做准备。 (2)现场保护。执行子程序或中断服务子程序时,要用到一些寄存器单 元,会破坏原有内容。要把有关寄存器单元的内容保存起来,送入堆栈。

6

第四讲 AT89S51单片机引脚及其功能

PC值≤0FFFH时,单片机读片内4KB Flash中的程序; PC值>0FFFH (超出片内4KB Flash地 址范围)时,转向读取片外

60KB(1000H-FFFFH)程序存储器空

间中的程序。

b. ������������ =0

只读取外部程序存储器中的内容,读取

地址范围0000H~FFFFH,片内

使用片外振荡器,该脚接外部时钟 振荡器输出的信号。

(2)XTAL2(18脚):片内振荡 器反相放大器的输出端。