计算书组成原理实验一具有基本输入输出功能的总线接口实验

计算机组成原理 实验(一)

计算机组成原理实验(一)实验项目名: 实验台基本模块认识实验实验要求:学习使用计算机组成原理教学实验系统的,认识组成原理实验台上的各个组成部件模块,熟悉各模块的功能、数据通路和使用方法,为后续实验做准备。

实验内容:(1)了解计算机组成原理硬件实验台各模块的组成和功能✶运算器单元- 74LS181(4位并行运算器),输入端74LS373(锁存器),输出端74LS245(三态缓冲器),74LS74(双D触发器)。

✶寄存器组单元– 3片74LS374 作为三个通用寄存器使用,R0、R1、R2 与总线相连。

✶地址寄存器单元– 2片地址锁存器74LS273锁存地址,通过总线将地址送入到该地址寄存器单元,而该地址寄存器与存储器接口相连,用于访问存储器。

✶数据总线单元–显示当前数据总线输出的内容。

✶主存储器单元–由6116 SRAM(4片)存储器作为主存储器,存储实验用机器指令,连接到数据和地址总线上。

✶程序计数器PC– 8位指令地址,使用2片74LS163构成,通过控制信号,可实现PC内容与总线间的交换。

✶指令寄存器单元—使用1片74LS273锁存器锁存当前执行的指令,IR寄存器的一端连接到数据总线上,另一端则连接到微地址单元的地址输入接口,用于寻址控存。

✶时序启停单元—通过输入系统脉冲源,可产生T1~T4四个标准的周期性信号,并且通过按键控制,可产生单次脉冲。

✶微程序电路单元—模拟微程序结构的CU,根据指令的操作码译码后得到的微程序地址,访问系统中的控存6116,取出微指令后,发出相应的微操作控制信号,控制系统中数据的流动及功能器件的动作。

该实验台各模块共有26个微控制信号,其中有7个(BUS-111,BUS-110,Rd-BUS,Rs-BUS,299-BUS,ALU-BUS,PC-BUS)采用译码输出的方式,而剩余的采用直接控制方式输出。

下一条微指令的地址由微指令的低地址(每条微指令长度为32位,其中(26-7)+3(译码)为微操作控制位,其余的为下地址)部分决定。

计组成原理实验报告昆工信息工程与自动化学院 (2)

实验一:数码管显示一、实验目地(1)了解可编程外围接口芯片8255(2) 理解数码显示译码器的作用。

(3)了解数据输入输出。

(4) 学会使用数码管的检测及显示译码器的使用。

(5) 掌握七段显示译码器的设计。

二、实验原理及基本技术路线图(方框原理图)三、所用仪器、材料(设备名称、型号、规格等)TDN-CM+或TDN-CM++教学实验系统一台。

四、实验方法、步骤(1)按实验原理电路图连接好电路,确认无误后打开电源。

(2)打开数据开关三态门(SW-B=0),在input device 单元中输入对应的二进制数据,打开LED片选(LED-B=0),拨动LED的W/R控制信号做1→0→1动作,产生一个上升沿将总线上的数据打入到LED中,这时在output device单元中数码管上显示的数据即为相应的十六进制形式。

五、实验过程原始记录(数据、图表、计算等)在输入单元输入二进制数据00010111,然后打开数据开关三态门(SW-B=0),打开LED片选(LED-B=0),拨动LED的W/R控制信号做1→0→1动作,产生一个上升沿,这时数码管上会显示对应的十进制数,即17。

六、实验结果、分析和结论引入总线,大大方便了各种设备进行数据传输,输入/输出设备挂在总线上,能提高信息的交换量及CPU的运行速度,输入设备发出指令,得到总线使用权,输出设备发出读的请求,控制总线发出控制信号,将控制权交给输出设备,这样输出设备就能读取到总线上的数据,数码显示管就能显示输入的数据。

在这个实验中,我已大体了解数据输入如何输出、数码显示译码器的作用、学会使用数码管的检测及显示译码器的使用和大体上已基本掌握七段显示译码器的设计,此次实验学到了很多东西,使之以后的学习更加的方便。

实验二:运算器一、实验目的(1)了解运算器的组成结构。

(2)掌握运算器的工作原理。

(3)学习运算器的设计方法。

(4)掌握简单运算器的数据传输通路。

(5)验证运算功能发生器74LS181的组合功能。

计算机组成原理实验报告

重庆理工大学《计算机组成原理》实验报告学号 __***********____姓名 __张致远_________专业 __软件工程_______学院 _计算机科学与工程二0一六年四月二十三实验一基本运算器实验报告一、实验名称基本运算器实验二、完成学生:张致远班级115030801 学号11503080109三、实验目的1.了解运算器的组成结构。

2.掌握运算器的工作原理。

四、实验原理:两片74LS181 芯片以并/串形式构成的8位字长的运算器。

右方为低4位运算芯片,左方为高4位运算芯片。

低位芯片的进位输出端Cn+4与高位芯片的进位输入端Cn相连,使低4位运算产生的进位送进高4位。

低位芯片的进位输入端Cn可与外来进位相连,高位芯片的进位输出到外部。

两个芯片的控制端S0~S3 和M 各自相连,其控制电平按表2.6-1。

为进行双操作数运算,运算器的两个数据输入端分别由两个数据暂存器DR1、DR2(用锁存器74LS273 实现)来锁存数据。

要将内总线上的数据锁存到DR1 或DR2 中,则锁存器74LS273 的控制端LDDR1 或LDDR2 须为高电平。

当T4 脉冲来到的时候,总线上的数据就被锁存进DR1 或DR2 中了。

为控制运算器向内总线上输出运算结果,在其输出端连接了一个三态门(用74LS245 实现)。

若要将运算结果输出到总线上,则要将三态门74LS245 的控制端ALU-B 置低电平。

否则输出高阻态。

数据输入单元(实验板上印有INPUT DEVICE)用以给出参与运算的数据。

其中,输入开关经过一个三态门(74LS245)和内总线相连,该三态门的控制信号为SW-B,取低电平时,开关上的数据则通过三态门而送入内总线中。

总线数据显示灯(在BUS UNIT 单元中)已与内总线相连,用来显示内总线上的数据。

控制信号中除T4 为脉冲信号,其它均为电平信号。

由于实验电路中的时序信号均已连至“W/R UNIT”单元中的相应时序信号引出端,因此,需要将“W/R UNIT”单元中的T4 接至“STATE UNIT”单元中的微动开关KK2 的输出端。

计算机组成原理实验

二、通用寄存器单元实验

3.实验说明 (2)通用寄存器单元的工作原理

二、通用寄存器单元实验

3.实验说明 (2)通用寄存器单元的工作原理 通用寄存器单元的核心部件为2片GAL16V8,它 具有锁存、左移、右移、保存等功能。各个功能 都由X1、X2信号和工作脉冲RACK来决定。当置 ERA=0、X0=1、X1=1,RACK有上升沿时,把总线上 的数据打入通用寄存器。可通过设置X0、X1来指 定通用寄存器工作方式,通用寄存器的输出端Q0-Q7接入判零电路。LED(ZD)亮时,表示当前通用 寄存器内数据为0。

A+B

CN=0,M=0 A+1 (A+B)+1

(A+B) + 1

0

0

AB

B A⊕B A B A +B A⊕B

A+AB (A+B)+AB

A-B-1

AB- 1

A+AB+ 1 (A + B )+ A B +1

A-B

A B

A+AB A+B AB-1 A+A (A+B)+A

(A+B)+A

(A+B)+AB

A+AB+1 A+B+1

一、算术逻辑运算单元实验

4.实验步骤 (2)不带进位位加法 74LS181的M=0,CN=1,S3S2S1S0=1110,则 74LS181工作在无进位位加法运算状态,运算为 F=A加B 本实验中,A=33H,B=55H 应得结果为:F=33H加55H=88H LED显示结果:88H 结果正确?

一、算术逻辑运算单元实验

一、算术逻辑运算单元实验

TD-CMA计算机组成原理与系统结构教学实验系统

TD-CMA计算机组成原理与系统结构教学实验系统价格:3980元TD-CMA计算机组成原理与系统结构教学实验系统是西安唐都科教仪器公司推出的新一代计算机组成原理与系统结构教学的实验设备,该系统与以往的产品相比,主要优点有:.采用了更为先进的计算机部件电路单元,以及更为先进的计算机整机结构设计。

.从部件到整机实验都配有数据通路图实时动态图形调试界面,且都具有单拍、单周期、连续等调试功能;通路图的调试过程也具有保存和回放功能,具有更为优秀的示教效果。

.采用VHDL语言、MAXII系列CPLD器件、以及QuartusII工具来开展设计性的实验,具有更好的实用价值。

.更为灵活、更为实用的时序发生电路和本地操作台设计。

.先进和完善的系统监测和保护电路设计,使实验平台更易于维护和使用。

一、系统的功能和特点1.先进丰富的课程内容使用实时动态图形调试实验方法,进行计算机组成原理的实验教学,比以往各种实验设备增加了并行运算器、Cache高速缓存、CPU设计、外总线接口设计、中断、DMA等实验内容,并可开展CISC、RISC、重叠、流水、超标量等先进计算机系统结构的设计和实验研究。

2.先进设计方法和开发工具采用VHDL语言、ALTREA公司最新MAXII系列CPLD器件和先进设计开发工具QUARTUS II来开展设计性的实验,具有更好的实用价值。

3.先进的实时动态图形调试方式系统为各计算机部件(运算器、存储器、控制器)分别提供了实时动态图形调试工具,使得学生可以轻松了解复杂部件的内部结构和操作方法,并可实时跟踪部件的工作状态。

在模型计算机整机调试的图形调试工具方面,系统除提供数据通路图、微程序流程图二种图形调试方式外,还增加了交互式微程序自动生成和当前微指令功能的模拟、系统调试过程的保存及回放等多种先进和实用的调试功能,这些图形调试方式及功能使得实验过程更为形象直观,好教好学,具有更为优秀的示教效果。

4.先进的运算器部件运算器部件由一片CPLD来实现,内含算术、逻辑和移位三个运算部件,其中移位运算采用桶形移位器,各部件独立并行工作,体现了主流运算器设计思想。

具有基本输入输出功能的总线接口实验

计算机科学与技术系实验报告专业名称课程名称计算机组成原理项目名称具有基本输入输出功能的总线接口实验班级学号姓名同组人员无实验日期一、实验目的与要求实验目的:1、理解总线的概念及其特性2、掌握控制总线的功能和应用相关知识:1、控制各个单元的微命令要清楚2、对数据和地址要分得清楚3、对于数据通路要清楚具体要求:1、输入设备将一个数打入R0寄存器2、输入设备将另一个数打入到地址寄存器3、将R0寄存器中的数写入到当前地址的存储器中4、将当前地址的存储器中的数用LED数码管显示二、实验逻辑原理图与分析2.1 画实验逻辑原理图三、数据通路图及分析(画出数据通路图并作出分析)微命令:IN_B = 0 , LDR0 = 1 微命令:IN_B = 0 , LDAR = 1微命令:R0_B = 1 , CS = 1 , WR = 1 微命令:R0_B = 1 , CS = 1 , RD = 1微命令:R0_B = 1 , LED_B = 0四、实验数据和结果分析4.1 实验结果数据4.2 结果数据分析本实验的具体数据流程是:先将数据11H打入到R0寄存器中,然后再将该数据在RAM中存放的地址01H打入AR中,然后将11H打入到01H中,然后再将11H从01H中读出并存放到R0寄存器中,然后再从R0寄存器写入到LED中。

所以,最终LED显示的数据是11H。

五、实验问题分析、思考题与小结问题分析本实验中主要产生的问题比如:应该点击4次“但节拍运行”,但有时由于T3时刻产生数据通路,会导致第4次忘记点击。

还有就是对微命令的操作有时可能会产生错误。

产生原因及解决方法:之所以会产生这些问题,主要是因为对这些微命令不理解,还有就是粗心造成的。

后来通过与同学交流讨论,并且在书上做了一些笔记来帮助自己理解记忆,就基本上解决了上面所述问题。

思考题:1、BUS R02、IN_B = 0 , LDAR = 1 , WR = 13、R0_B = 0 , WR = 14、RD = 1 ,5、IN_B IN单元的输出允许LDR0 R0寄存器的输入允许W/R RAM的读写控制CS RAM的片选信号LED_B OUT单元的输出允许W/R(LED) OUT的读写控制6、01H总结:这次的实验接线比较复杂,而且又是第一次实验,所以在第一次实验课的时候比较遗憾没有能够做出本实验,只是对实验的流程、操作有了一个比较全面的了解。

系统总线和具有基本输入输出功能的总线接口实验报告

系统总线和具有基本输入输出功能的总线接口实验报告一、实验目的1.理解总线与总线接口的概念,了解总线接口的基本输入输出功能。

2.学习使用系统总线进行数据传输的方法。

3.掌握总线接口的基本编程方法。

二、实验原理系统总线是一种计算机系统中实际存在的、能够传输信息的一组导线或卡槽。

实现计算机各个部件间数据传输的功能。

具有高速、可靠、灵活等特点。

总线接口是指计算机中各种扩展设备与主板、芯片等之间连接器的一种电路设计。

总线接口的基本输入输出功能包括数据读取、数据写入、地址读取、地址写入等。

总线接口的编程方法由物理地址访问和逻辑地址访问组成。

物理地址访问是将实际存放数据的地址传递给总线接口,逻辑地址访问是将对应的逻辑地址转化为物理地址然后传递给总线接口。

三、实验器材1.个人电脑2.跑虚拟机的电脑或实机3.开发板或仿真器4.计算机总线卡5.串行通信接口6.实验用数据、程序4.实验步骤1.准备工作(1)将开发板或仿真器连接到计算机,并进行相应的设置。

(2)将计算机总线卡插入计算机的PCI插槽中,并与开发板或仿真器之间进行连接。

(3)将串行通信接口连接至开发板或仿真器的相应引脚上。

2.完成数据传输(1)先进行地址写入和数据写入操作,以确定要传输的数据的位置和内容。

(2)再进行地址读取和数据读取操作,以读取相应位置上的数据。

(3)读取到的数据会被传输到串行通信接口,然后通过串口发送到外部设备。

(4)如果需要,可以重复进行以上操作以进行连续数据传输。

3.编写程序根据实验内容,编写相应的程序实现数据的读取和传输过程,并进行调试和优化。

5.实验结果通过本次实验,我了解了系统总线和总线接口的基本输入输出功能,并学会了总线接口的编程方法。

同时,我也掌握了数据传输的方法,能够熟练地进行数据的读写操作,并能够编写相应的程序进行调试和优化。

6.实验总结通过本次实验,我对系统总线和总线接口的概念有了更深刻的理解,也学会了一些实际应用的技巧。

《计算机组成原理》实验

《计算机组成原理》实验一、实验的性质、任务和基本要求(一)本实验课的性质、任务《计算机组成原理》是计算机科学与技术、网络工程专业的核心专业基础课,本课程旨在培养学生对计算机系统的分析、设计能力,同时为后续专业课程的学习打下坚实的基础。

实验是巩固课堂教学质量必不可少的重要手段。

本实验课的任务是通过实验进一步加深对计算机各部件组成以及工作原理的掌握,培养学生计算机硬件动手能力。

(二)基本要求1、掌握运算器的基本组成和工作原理;2、掌握半导体存储器的工作原理与使用方法,掌握半导体存储器如何存储和读取数据;3、掌握微程序控制器的组成以及工作过程,掌握用单步方式执行一段微程序以及如何检查每一条微指令正确与否的方法;4、掌握数据传送通路工作原理;5、能够将运算器、微程序控制器和存储器三个部件连机,形成一个基本模型机系统。

同时,掌握机器指令与微指令的关系。

(三)实验学时分配表(表格说明)二、实验教学内容实验一运算器实验一、实验目的:(1)结合学过的有关运算器的基本知识,掌握运算器的基本组成、工作原理。

特别是了解算术逻辑运算单元ALU的工作原理;(2)验证多功能算术单元74181、74182的运算功能;(3)熟悉掌握本实验中运算器的数据传输通路。

二、实验要求(1)预习74181、74182的工作原理及逻辑关系;(2)测量数据要求准确;(3)写出实验报告。

三、实验内容1、实验原理实验中的运算器由两片74LS181以并/串形成8位字长的ALU构成。

运算器的输出经过一个三态门74LS245到ALUO1插座,实验时用8芯排线和内部数据总线BUSD0~D7插座BUS1~6中的任一个相连,内部数据总线通过LZD0~LZD7显示灯显示;运算器的两个数据输入端分别由二个锁存器74LS273锁存,两个锁存器的输入并联后连至插座ALUBUS,实验时通过8芯排线连至外部数据总线EXD0~D7插座EXJ1~EXJ3中的任一个;参与运算的数据来自于8位数据开关KD0~KD7,并经过一三态门74LS245直接连至外部数据总线EXD0~EXD7,通过数据开关输入的数据由LD0~LD7显示。

计算机组成原理实验报告

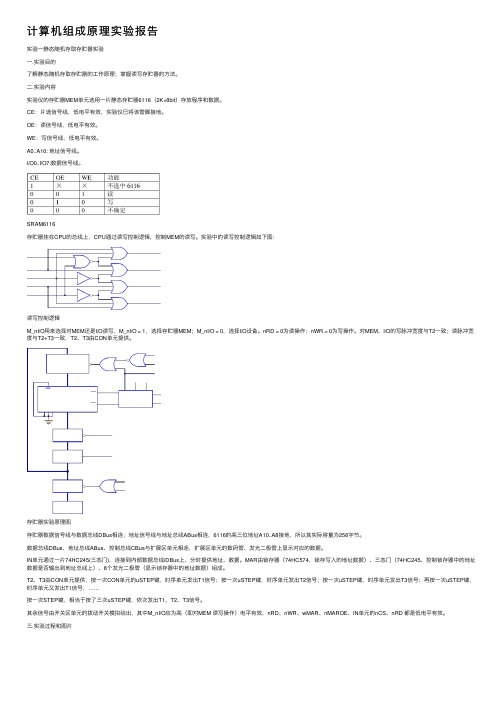

计算机组成原理实验报告实验⼀静态随机存取存贮器实验⼀.实验⽬的了解静态随机存取存贮器的⼯作原理;掌握读写存贮器的⽅法。

⼆.实验内容实验仪的存贮器MEM单元选⽤⼀⽚静态存贮器6116(2K×8bit)存放程序和数据。

CE:⽚选信号线,低电平有效,实验仪已将该管脚接地。

OE:读信号线,低电平有效。

WE:写信号线,低电平有效。

A0..A10: 地址信号线。

I/O0..I/O7:数据信号线。

SRAM6116存贮器挂在CPU的总线上,CPU通过读写控制逻辑,控制MEM的读写。

实验中的读写控制逻辑如下图:读写控制逻辑M_nI/O⽤来选择对MEM还是I/O读写,M_nI/O = 1,选择存贮器MEM;M_nI/O = 0,选择I/O设备。

nRD = 0为读操作;nWR = 0为写操作。

对MEM、I/O的写脉冲宽度与T2⼀致;读脉冲宽度与T2+T3⼀致,T2、T3由CON单元提供。

存贮器实验原理图存贮器数据信号线与数据总线DBus相连;地址信号线与地址总线ABus相连,6116的⾼三位地址A10..A8接地,所以其实际容量为256字节。

数据总线DBus、地址总线ABus、控制总线CBus与扩展区单元相连,扩展区单元的数码管、发光⼆极管上显⽰对应的数据。

IN单元通过⼀⽚74HC245(三态门),连接到内部数据总线iDBus上,分时提供地址、数据。

MAR由锁存器(74HC574,锁存写⼊的地址数据)、三态门(74HC245、控制锁存器中的地址数据是否输出到地址总线上)、8个发光⼆极管(显⽰锁存器中的地址数据)组成。

T2、T3由CON单元提供,按⼀次CON单元的uSTEP键,时序单元发出T1信号;按⼀次uSTEP键,时序单元发出T2信号;按⼀次uSTEP键,时序单元发出T3信号;再按⼀次uSTEP键,时序单元⼜发出T1信号,……按⼀次STEP键,相当于按了三次uSTEP键,依次发出T1、T2、T3信号。

其余信号由开关区单元的拨动开关模拟给出,其中M_nI/O应为⾼(即对MEM 读写操作)电平有效,nRD、nWR、wMAR、nMAROE、IN单元的nCS、nRD 都是低电平有效。

计算机组成原理实验报告

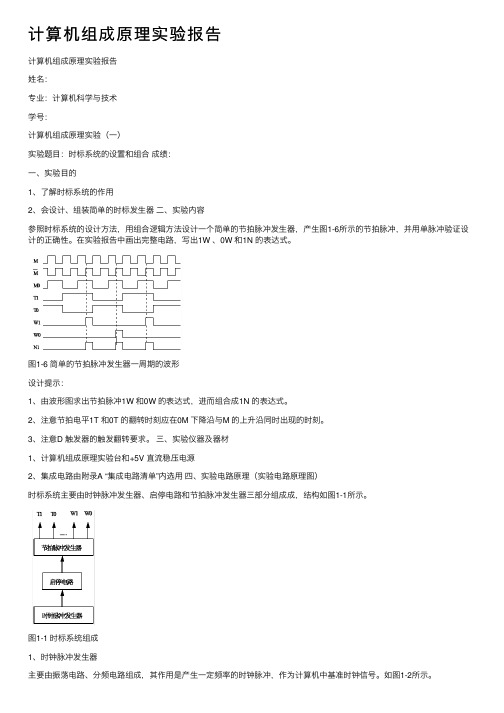

计算机组成原理实验报告计算机组成原理实验报告姓名:专业:计算机科学与技术学号:计算机组成原理实验(⼀)实验题⽬:时标系统的设置和组合成绩:⼀、实验⽬的1、了解时标系统的作⽤2、会设计、组装简单的时标发⽣器⼆、实验内容参照时标系统的设计⽅法,⽤组合逻辑⽅法设计⼀个简单的节拍脉冲发⽣器,产⽣图1-6所⽰的节拍脉冲,并⽤单脉冲验证设计的正确性。

在实验报告中画出完整电路,写出1W 、0W 和1N 的表达式。

图1-6 简单的节拍脉冲发⽣器⼀周期的波形设计提⽰:1、由波形图求出节拍脉冲1W 和0W 的表达式,进⽽组合成1N 的表达式。

2、注意节拍电平1T 和0T 的翻转时刻应在0M 下降沿与M 的上升沿同时出现的时刻。

3、注意D 触发器的触发翻转要求。

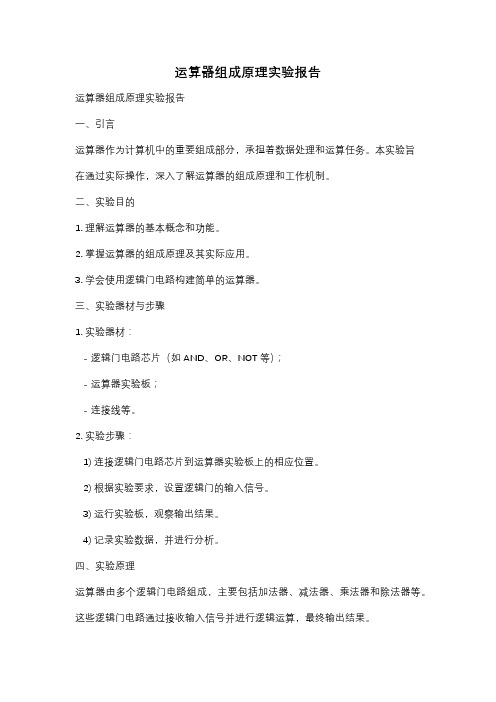

三、实验仪器及器材1、计算机组成原理实验台和+5V 直流稳压电源2、集成电路由附录A “集成电路清单”内选⽤四、实验电路原理(实验电路原理图)时标系统主要由时钟脉冲发⽣器、启停电路和节拍脉冲发⽣器三部分组成成,结构如图1-1所⽰。

图1-1 时标系统组成1、时钟脉冲发⽣器主要由振荡电路、分频电路组成,其作⽤是产⽣⼀定频率的时钟脉冲,作为计算机中基准时钟信号。

如图1-2所⽰。

图1-2 时钟脉冲发⽣器组成2、启停电路计算机是靠⾮常严格的节拍脉冲,按时间的先后次序⼀步⼀步地控制各部件⼯作的,所以,机器启停的标志是有⽆节拍脉冲,⽽控制节拍脉冲按⼀定的时序发⽣和停⽌,不能简单地⽤电源开关来实现。

如图1-3所⽰。

图1-3 简单的启停电路为了使机器可靠地⼯作,要求启停电路在机器启动或停机时,保证每次从规定的第⼀个脉冲开始启动,到最后⼀个脉冲结束才停机,并且必须保证第⼀个和最后⼀个脉冲的波形完整。

如图1-4所⽰。

图1-4 利⽤维持阻塞原理的启停电路3、节拍脉冲发⽣器节拍脉冲发⽣器的作⽤是产⽣⼀序列的节拍电平和⼯作脉冲。

节拍电平是保证计算机微操作的时序性,⼯作脉冲是各寄存器数据的打⼊脉冲。

8255可编程并行接口(基本输入输出、动静态七段数码管、竞赛抢答器)微机原理实验报告

微机实验报告书学号:XXXXX姓名:XXXXX 班级:XXXXX 同组名单:XXXXXXXXX 实验日期:2012.12.25实验题目:8255可编程并行接口_______________________________________ 实验目标:1、掌握8255方式0的工作原理及使用方法。

_________________2 、进一步掌握中断处理程序的编写。

_______________________3、掌握数码管显示数字的基本原理。

4、了解微机化竞赛抢答器的基本原理。

实验步骤:实验一、8255A的基本输入输出图1. 8255A的基本输入输岀接线图实验步骤如下:(1)实验电路如图1, 8255A勺C口接逻辑电平开关K0~K7 A口接LED显示电路L0~L7。

(2)编程从8255A勺C口输入数据,再从A口输出。

实验二、七段数码管图2.七段数码管接线图实验步骤如下:(1)静态显示:按图2 (a)连接好电路,将8255A的A 口PA0~PA6分别与七段数码管的段码驱动输入端a~g相连,位码驱动输入端S1接+5V (选中),SO、dP接地(关闭)。

编程从键盘输入一位十进制数字(0~9),在七段数码管上显示出来。

(2)动态显示:按图2 (b)连接好电路,七段数码管段码连接不变,位码驱动输入端S1接+5V (选中),SO接8255A的C 口的PC1。

编程在两个数码管上显示“ 56”。

实验三、竞赛抢答器k? KE K5 k0图3.竞赛抢答器电路图实验步骤如下:图3位竞赛抢答器(模拟)的原理图,逻辑开关 K0~K7代表竞赛抢答按钮 0~7号,当某个逻辑电平开关置“ 1”时,相当于某组抢答按钮按下。

在七段数 码管上将其组号(0~7)显示出来。

程序框图:实验一:实验二:开恰:开箱莉型环迪为自口秫出獅356设曲A 口输出-------送百的战码矽口 -泾忙码1口1中T 口是紅字 ®时•、有釁損下吗*|就・取■点口 ■出开皓眦抬向震码表首址4 r设SS255A 口输出C口输入杳表求出段码关囲显示垢段码自船萌AU输出程序清单:.************************* ・J J;* 8255A的基本输入输出.*************************.IOPORT EQUIO8255A EQUIO8255B EQUIO8255C EQUIO8255K EQU0E400H-280HIOPORT+288HIOPORT+289HIOPORT+28AHIOPORT+28BH;对8255进行设定,A输出,C输;从C输入;从A输出实验三:响铃自键盘接收一亭符结束CODE SEGMENTASSUME CS:CODESTART: MOV DX,IO8255K入MOV AL,10001001BOUT DX,ALINPUT: MOV DX,IO8255CIN AL,DXMOV DX,IO8255A求出组马全AL;*键盘输入数据(0-9)控制LED 数码管显示.************************************・DATA SEGMENT IOPORT EQU 0E400H-280HIO8255A EQU IOPORT+288HIO8255B EQU IOPORT+289HIO8255C EQU IOPORT+28AHIO8255K EQU IOPORT+28BHLED DB 3FH,06H,5BH,4FH,66H,6DH,7DH,07H,7FH,6FH MESG1 DB 0DH,0AH,'Input a num (0--9),other key is exit:',0DH,0AH,'$'DATA ENDSCODESEGMENTASSUME CS:CODE,DS:DATASTART:MOV AX,DA TAMOV DS,AXMOV DX,IO8255K ;使 8255的 A 口为输出方式MOV AX,10000000BOUT DX,ALSSS:MOV DX,OFFSET MESG1 ; 显示提示信息MOV AH,09HINT 21HMOV AH,01 ;从键盘接收字符INT 21HCMP AL,'0' ; 是否小于 0JL EXIT ;若是则退出CMP AL,'9' ; 是否大于 9JG EXIT ;若是则退出SUB AL,30H;将所得字符的 ASCII 码减 30HMOVBX,OFFSET LED ;BX 为数码表的起始地址XLAT; 求出相应的段码MOV DX,IO8255A ;从 8255的 A 口输出OUT DX,ALJMPSSS;转 SSSCODE OUTDX,ALMOV DL,0FFH MOV AH,06H INT 21H JZ INPUT MOV AH,4CH INT 21HENDSEND START.************************************・;判断是否有按键;若无,则继续C 输入,A 输出 ; 否则,返回 DOSLED 数码管实验动态显示“ 56”.******************************.DATASEGMENT IOPORT EQU 0E400H-280HIO8255A EQU IOPORT+288HIO8255B EQU IOPORT+289HIO8255CEQU IOPORT+28AHIO8255K EQUIOPORT+28BHLED DB 3FH,06H,5BH,4FH,66H,6DH,7DH,07H,7FH,6FH ;段码BUFFER1DB 6,5 ;存放要显示的个位和十位 BZDW ? ;位码DATA ENDSCODESEGMENTASSUME CS:CODE,DS:DA TASTART:MOV AX,DATAMOV DS,AXMOV DX,IO8255K ;将 8255 设为 A 口输出MOV AL,80HOUT DX,ALMOV DI,OFFSET BUFFER1 ;设 di 为显示缓冲区LOOP2: MOV BH,02LLL:MOV BYTE PTR BZ,BHPUSH DIDEC DIADD DI, BZMOV BL,[DI] ;bl 为要显示的数POP DIMOV AL,0MOV DX,IO8255COUT DX,ALMOV BH,0MOV SI,OFFSET LED ;置 led 数码表偏移地址为 SIADD SI,BX;求出对应的 led 数码MOV AL,BYTE PTR [SI]MOV DX,IO8255A ;自 8255A 的口输出OUT DX,ALMOV AL,BYTE PTR BZ ;使相应的数码管亮MOV DX,IO8255CEXIT:MOV AH,4CHINT 21HCODEENDSENDSTART;返回.******************************.OUT DX,ALMOV CX,3000DELAY: LOOP DELAY ;延时MOV BH,BYTE PTR BZSHR BH,1JNZ LLLMOV DX,0FFHMOV AH,06INT 21HJE LOOP2 ;有键按下则退出MOV DX,IO8255CMOV AL,0 ;关掉数码管显示OUT DX,ALMOV AH,4CH ;返回INT 21HCODE ENDSEND START.***************・;* 模拟抢答器.***************.DATA SEGMENTIOPORT EQU 0E400H-280HIO8255A EQU IOPORT+288HIO8255B EQU IOPORT+289HIO8255C EQU IOPORT+28AHIO8255K EQU IOPORT+28BHLED DB 3FH,06H,5BH,4FH,66H,6DH,7DH,07H ;数码表DATA ENDSCODE SEGMENTASSUME CS:CODE,DS:DA TASTART: MOV AX,DATAMOV DS,AXMOV DX,IO8255K 设8255为A 口输出,C 口输入MOV AL,10001001BOUT DX,ALMOV BX,OFFSET LED ; 使BX 指向段码管首址SSS: MOV DX,IO8255CIN AL,DX ;从8255的C 口输入数据OR AL,AL ;比较是否为0JE SSS ;若为0,则表明无键按下,转sssMOV CL,0FFH ;cl 作计数器,初值为-1 RR: SHR AL,1INC CLJNC MOV XLAT MOV OUT RRAL,CLDX,IO8255ADX,ALDL,7AH,2 21H;响铃ASCII 码为O7MOVMOVINTWAI: MOV AH,1INT 21HCMP AL,2OH ;是否为空格JNE EEE ;不是,转eeeMOV AL,O ;是,关灭灯MOV DX,IO8255AOUT DX,ALJMP SSSEEE: MOV AH,4CH ;返回INT 21HCODE ENDSEND START运行结果:实验一:当逻辑开关K0~K7中的一个或几个打开时,对应的LED丁就会亮起来,即利用8255A实现了基本的输入输出控制。

运算器组成原理实验报告

运算器组成原理实验报告运算器组成原理实验报告一、引言运算器作为计算机中的重要组成部分,承担着数据处理和运算任务。

本实验旨在通过实际操作,深入了解运算器的组成原理和工作机制。

二、实验目的1. 理解运算器的基本概念和功能。

2. 掌握运算器的组成原理及其实际应用。

3. 学会使用逻辑门电路构建简单的运算器。

三、实验器材与步骤1. 实验器材:- 逻辑门电路芯片(如AND、OR、NOT等);- 运算器实验板;- 连接线等。

2. 实验步骤:1) 连接逻辑门电路芯片到运算器实验板上的相应位置。

2) 根据实验要求,设置逻辑门的输入信号。

3) 运行实验板,观察输出结果。

4) 记录实验数据,并进行分析。

四、实验原理运算器由多个逻辑门电路组成,主要包括加法器、减法器、乘法器和除法器等。

这些逻辑门电路通过接收输入信号并进行逻辑运算,最终输出结果。

1. 加法器加法器是运算器的基本组成部分,用于实现数字的加法运算。

它由多个逻辑门电路组成,其中包括半加器和全加器。

半加器用于实现两个数字的个位相加,全加器则用于实现多位数的相加。

2. 减法器减法器是运算器的另一个重要组成部分,用于实现数字的减法运算。

它通过将减法转化为加法运算来实现。

减法器的输入包括被减数、减数和借位,输出为差值。

3. 乘法器乘法器用于实现数字的乘法运算。

它通过多次的加法运算来实现乘法。

乘法器的输入包括被乘数和乘数,输出为积。

4. 除法器除法器用于实现数字的除法运算。

它通过多次的减法运算来实现除法。

除法器的输入包括被除数和除数,输出为商和余数。

五、实验结果与分析根据实验步骤进行操作后,我们观察到运算器实验板上的LED显示屏显示出了正确的运算结果。

通过分析实验数据,我们得出了以下结论:1. 运算器能够正确地进行加法、减法、乘法和除法运算,验证了其组成原理的正确性。

2. 运算器的性能受到逻辑门电路的质量和连接线的稳定性等因素的影响。

在实际应用中,需要保证这些因素的稳定性和可靠性,以确保运算器的正常工作。

计算机组成原理实验指导 (1)

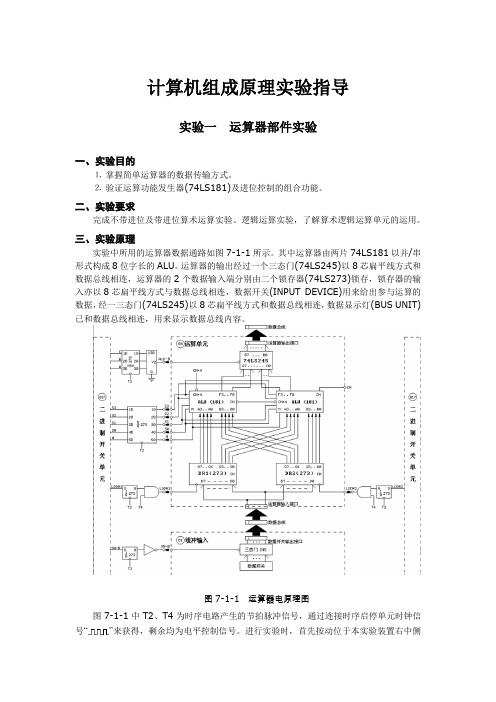

计算机组成原理实验指导实验一运算器部件实验一、实验目的⒈掌握简单运算器的数据传输方式。

⒉验证运算功能发生器(74LS181)及进位控制的组合功能。

二、实验要求完成不带进位及带进位算术运算实验、逻辑运算实验,了解算术逻辑运算单元的运用。

三、实验原理实验中所用的运算器数据通路如图7-1-1所示。

其中运算器由两片74LS181以并/串形式构成8位字长的ALU。

运算器的输出经过一个三态门(74LS245)以8芯扁平线方式和数据总线相连,运算器的2个数据输入端分别由二个锁存器(74LS273)锁存,锁存器的输入亦以8芯扁平线方式与数据总线相连,数据开关(INPUT DEVICE)用来给出参与运算的数据,经一三态门(74LS245)以8芯扁平线方式和数据总线相连,数据显示灯(BUS UNIT)已和数据总线相连,用来显示数据总线内容。

图7-1-1运算器电原理图图7-1-1中T2、T4为时序电路产生的节拍脉冲信号,通过连接时序启停单元时钟信号“”来获得,剩余均为电平控制信号。

进行实验时,首先按动位于本实验装置右中侧的复位按钮使系统进入初始待令状态,在LED显示器闪动位出现“P.”的状态下,按【增址】命令键使LED显示器自左向右第4位切换到提示符“L”,表示本装置已进入手动单元实验状态,在该状态下按动【单步】命令键,即可获得实验所需的单脉冲信号,而LDDR1、LDDR2、ALU-B、SW-B、S3、S2、S1、S0、CN、M各电平控制信号用位于LED显示器上方的26位二进制开关来模拟,均为高电平有效。

四、实验连线图7-1-2实验连线示意图按图7-1-2所示,连接实验电路:①总线接口连接:用8芯扁平线连接图7-1-2中所有标明“”或“”图案的总线接口。

②控制线与时钟信号“”连接:用双头实验导线连接图7-1-2中所有标明“”或“”图案的插孔(注:Dais-CMH的时钟信号已作内部连接)。

五、实验系统工作状态设定在闪动的“P.”状态下按动【增址】命令键,使LED显示器自左向右第4位显示提示符“L”,表示本装置已进入手动单元实验状态。

计组实验报告5

本次实验锁存器相当于寄存器,起到缓冲数据的作用。第一组实验中数据开关设置的

是(01H),使数据直接存入锁存器中。将数据开关设置成(02H),数据也直接存入锁存 器中,此时,数据总线和锁存输出显示(02H)。

七、实验总结

本次实验主要掌握了输入/输出的硬件电路,对锁存器的功能有了进一步的体会。实验 步骤简单易懂,实验过程顺利。

设置数据开关,具体操作步骤如下:

数据开关

(00000001)

三态门 CBA=000

CE=0 SW-B=1

寄存器DR2

(00000001)

LDDR1=0 LDDR2=1 按单步建

寄存器DR1

(00000001)

LDDR1=1 LDDR2=0 按单步建

结果分析:

运算单元的 DR1、DR2 与数据总线都显示(01H)。

(1)按单步键后,数据总线显示(00H),内存显示(11H),地址总线显示(00H)。 再按单步键后,数据总线显示(11H)。

(2)按单步键后,数据总线显示(01H),内存显示(12H),地址总线显示(01H)。 再按单步键后,数据总线显示(12H)。

(3)按单步键后,数据总线显示(02H),内存显示(13H),地址总线显示(02H)。

(4)寄存器判零

在保持带进位减法运算所设置的状态下,令AR=1,按【单步】,若零标志灯Z“亮”, 表示当前运算结果为零,反之表示结果不为零。

结果分析:

这个实验结果Z灯亮。因为带进位减法运算的结果是(00H)。所以,当 Z 灯亮时结

果为零。

六、实验总结

(1)通过这个实验,熟悉了判零实验的硬件,基本了解了判零实验的原理,加深了 对寄存器判零的理解。

LDAR 为高电平有效,而 WE 为读/写(W/R)控制信号,当 WE=0 时进行读操作,当 WE=1 时进行写操作。

计组实验报告

计算机组成原理实验报告实验一寄存器组成实验一、实验目的(1)熟悉D触发器的功能及使用方法。

(2)掌握寄存器文件的逻辑组成及使用方法。

二、实验内容(1)掌握Quartus II的使用方法,能够进行数字电路的设计及仿真。

(2)验证Quartus II所提供D触发器的功能及使用方法。

(3)设计具有1个读端口、1个写端口的寄存器文件,并进行存取操作仿真/验证。

三、实验原理及方案Quartus II提供了多种类型的触发器模块,如D触发器、T触发器等。

固定特性的触发器模块有不同的型号,参数化的触发器模块有lpm_ff、lpm_dff、lpm_tff等。

D触发器常来构建寄存器。

本次实验我们用Quartus II中提供的8为D触发器模块,实现了一个8×8bits 的寄存器组,因此,操作地址均为3位,数据均为8位。

由于要求读写端口分离,因此,读操作的相关引脚有地址raddr[2..0]、数据输出q[7..0],写操作的相关引脚有地址waddr[2..0]、数据输入data[7..0]、写使能wen。

其中,省略读使能信号可以简化控制,即数据输出不受限制。

寄存器文件通过写地址waddr[2..0]、写使能wen信号来实现触发器的写入控制,通过读地址raddr[2..0]信号来控制触发器的数据输出选择。

其连接电路原理如图所示。

寄存器文件的组成则由此,可在Quartus II中连接原理图:四、实验结果仿真波形如下:五、小结通过此次实验,我们学会了Quartus II的原理图的构造方法,以及仿真方法,并且使用lpm_dff作为三态门,控制数据的输入,并且在输出时,用lpm_mux选择每个寄存器的数据输出。

最后,在本次实验中,我们重新巩固了课堂学习的内容,也对寄存器加深了了解,相信我们会通过实验在计组的学习道路上越走越远。

实验二运算器组成实验一、实验目的(1)熟悉加/减法器的功能及使用方法。

(2)掌握算术逻辑部件(ALU)的功能及其逻辑组成。

计算机组成原理实验指导书(JSY)

计算机组成原理实验指导书(JSY)计算机组成原理实验指导书青岛科技⼤学数字技术实验中⼼⽬录实验⼀运算器实验 (1)实验⼆进位运算和移位运算实验 (7)实验三静态存储器原理实验 (11)实验四数据通路实验 (13)实验五微程序控制器实验 (15)实验六微程序控制器实验 (25)实验⼀运算器实验⼀、实验⽬的1)熟悉实验装置;2)学习算术逻辑单元电路的构成及其⼯作原理,掌握运算器实验的数据传送通路的结构及不同实验状态下的各运算数据的流程;3)验证运算功能发⽣器(74LS181)的组合功能;⼆、实验设备JYS-4计算机组成原理实验箱及导线若⼲。

三、实验内容1、实验装置简介JYS-4计算机组成原理实验装置是⼀种能够通过多种“原理计算机”的设计和构造,来灵活地实现“计算机组成原理”课程的实验教学,以满⾜不同层次和不同教学环节实验要求的开放式教学实验设备。

使⽤JYS-4计算机组成原理实验装置可完成运算器实验、进位和移位控制实验、静态存储器原理实验、计算机的数据通路实验、微程序控制器实验、基本模型机的设计与实现实验、带移位运算的模型机的设计与实现等实验。

JYS-4计算机组成原理实验装置采⽤内、外总线结构,并按开放式结构要求设计了各关联的单元实验电路,除进⼀步规范了可组成的原理计算机结构外,也为实验教学提供了充⾜的硬件可设计空间和软件可设计空间,在实验电路构造⽅⾯,系统也提供了多种⼿段,可按部件层次组合⽅式逐次构造不同结构和复杂程度的部件实验电路及模型计算机。

整个实验仪器是由分散元器件构成,包括计算机中的各组成部件:运算器、存储器、控制器等,这些器件的内部连线已经连好,需要连接的是⼀些控制信号线。

实验板上对各个器件的划分⽐较清楚,都⽤⽩⾊框线表⽰,每个器件的名称也⽤⽩⾊注明。

JYS-4计算机组成原理实验装置具有以下特点:1)系统装置⽀持三种实验电路构造⽅式,即实验元件零连线⽅式(在⾯包板上⾃⼰搭建实验电路)、单元电路跨接⽅式(使⽤装置提供的排线通过跨接构造出实验电路)和实验“软连线”⽅式(使⽤可编程逻辑器件通过编程设计实验电路)。

组成原理实验报告

一、实验目的1. 理解计算机组成原理的基本概念和原理。

2. 掌握计算机硬件各模块的功能和相互关系。

3. 培养动手实践能力,提高对计算机硬件的认识。

二、实验内容1. 计算机硬件系统组成2. 中央处理器(CPU)的结构与功能3. 存储器系统组成与工作原理4. 输入/输出系统组成与工作原理5. 总线系统组成与工作原理三、实验步骤1. 计算机硬件系统组成(1)观察计算机硬件系统,了解各模块的名称和功能。

(2)分析各模块之间的相互关系,理解计算机硬件系统的整体结构。

2. 中央处理器(CPU)的结构与功能(1)观察CPU模块,了解其内部结构。

(2)分析CPU的各个部件,如寄存器、控制器、算术逻辑单元(ALU)等的功能。

(3)理解CPU的工作原理,包括指令的获取、译码、执行和存储等过程。

3. 存储器系统组成与工作原理(1)观察存储器模块,了解其内部结构。

(2)分析存储器的基本单元,如RAM、ROM等的功能和特点。

(3)理解存储器的工作原理,包括地址译码、数据读/写等过程。

4. 输入/输出系统组成与工作原理(1)观察输入/输出模块,了解其内部结构。

(2)分析输入/输出设备的类型和功能,如键盘、鼠标、显示器等。

(3)理解输入/输出系统的工作原理,包括数据传输、控制信号等过程。

5. 总线系统组成与工作原理(1)观察总线模块,了解其内部结构。

(2)分析总线的类型和功能,如地址总线、数据总线、控制总线等。

(3)理解总线系统的工作原理,包括数据传输、同步信号等过程。

四、实验结果与分析1. 计算机硬件系统组成实验结果显示,计算机硬件系统由CPU、存储器、输入/输出设备和总线等模块组成,各模块之间相互配合,共同完成计算机的运行。

2. 中央处理器(CPU)的结构与功能实验结果显示,CPU由寄存器、控制器和ALU等部件组成,负责指令的获取、译码、执行和存储等过程。

3. 存储器系统组成与工作原理实验结果显示,存储器由RAM、ROM等基本单元组成,负责数据的存储和读取。

组成原理实验一接线与操作

(1)找ALU UNIT, 将 ) 8线插头插入到实验仪 线插头插入到实验仪 最左边的74LS299芯片 最左边的 芯片 上面的B0-B7 插座。 插座。 上面的

299芯片

(3)检查:两端代码相 )检查: 同的导线颜色要一致, 同的导线颜色要一致,例 图中插座一头B0是 如,图中插座一头 是 用黄线, 用黄线,那么另一头黄线 对应的代码也是B0。 对应的代码也是 。

(1)找ALU UNIT,将6线插头插入 ) 将 线插头插入 插座。 到S3~Cn插座。 插座

实验一(1) 实验一

算术逻辑运算器连线步骤7

(2)再找 )再找SWITCH UNIT,将2线插头 将 线插头 另一端,插入到LDDR1、LDDR2插 另一端,插入到 、 插 座的中间2根插针上 根插针上, 座的中间 根插针上,记住左线为 LDDR1, 右线为 , 右线为LDDR2 。

实验一(1)

数据操作步骤12

总线8盏显示灯 显示数据是00110011(灭灭亮 总线 盏显示灯B7~B0显示数据是 盏显示灯 显示数据是 ( 亮灭灭亮亮)。 与刚才存入DR1寄存器的数据一致, 寄存器的数据一致, 亮灭灭亮亮)。 与刚才存入 寄存器的数据一致 正确。 正确。

实验一(1)

例4的 操作 过程

实验一(3) 实验一

移位运算器连线步骤 3

(3)检查:两端代码相同的导线颜色 )检查: 要一致, 图中插座一头B0是 要一致,如,图中插座一头 是黄线, 那么另一头黄线对应是D0 那么另一头黄线对应是

(1)找BUS ) UNIT,将8线插 将 线插 头一端, 头一端,插入 到B0—B7插 插 座。

计算机组成原理实验报告(系统总线和具有基本输入输出功能的总线接口实验)

计算机组成原理实验报告(系统总线和具有基本输入输出功能的总线接口实验)池州学院数学计算机科学系实验报告专业:计算机科学与技术班级:实验课程:计算机组成原理姓名:学号:实验室:硬件实验室同组同学:实验时间: 20xx年5月29日指导教师签字:成绩:系统总线和具有基本输入输出功能的总线接口实验一实验目的和要求1.理解总线的概念及其特性。

2.掌握控制总线的功能和应用。

二实验环境PC机一台,TD-CMA 实验系统一套三实验步骤及实验记录按图连接电路首先将时序与操作台单元的开关KK1、KK3置为‘运行’档,开关KK2置为‘单拍’档,按动CON单元的总清按钮CLR,并执行下述操作。

① 对MEM进行读操作(WR=0,RD=1,IOM=0),此时E0灭,表示存储器读功能信号有效。

② 对MEM进行写操作(WR=1,RD=0,IOM=0),连续按动开关ST,观察扩展单元数据指示灯,指示灯显示为T3时刻时,E1灭,表示存储器写功能信号有效。

③ 对I/O进行读操作(WR=0,RD=1,IOM=1),此时E2灭,表示I/O读功能信号有效。

④ 对I/O进行写操作(WR=1,RD=0,IOM=1),连续按动开关ST,观察扩展单元数据指示灯,指示灯显示为T3时刻时,E3灭,表示I/O写功能信号有效。

四实验结果与分析第二篇:计算机组成原理实验4.2_实验报告 1900字学生报告实验学院:软件学院专业:软件工程年级:2010级学号:24320102202460 学生姓名:高伟同组学生姓名:何建明实验课程名称:计算机组成原理实验实验名称:具有中断控制功能的总线接口实验指导教师:曾文华、蔡艺军、廖凌宇实验时间:2012.4.9 19:00--21:00 实验地点:漳州校区生化楼603 20xx年4月18日一、实验目的与要求1.掌握中断控制信号线的功能和应用2.掌握在系统总线上设计中断控制信号线的方法二、实验设备1、TD-CMA教学实验系统1台(通过USB串行接口与PC微机相连)2、PC微机1台三、实验原理为了实现中断控制,CPU 必须有一个中断使能寄存器,并且可以通过指令对该寄存器进行操作.设计下述中断使能寄存器,其原理如图 4-2-1 所示.其中 EI 为中断允许信号,CPU 开中断指令 STI 对其置 1,而 CPU 关中断指令CLI 对其置0.每条指令执行完时,若允许中断,CPU 给出开中断使能标志 STI,打开中断使能寄存器,EI 有效.EI 再和外部给出的中断请求信号一起参与指令译码,使程序进入中断处理流程.本实验要求设计的系统总线具备有类 X86 的中断功能,当外部中断请求有效,CPU 允许响应中断,在当前指令执行完时,CPU 将响应中断.当CPU 响应中断时,将会向8259 发送两个连续的INTA 信号,请注意,8259 是在接收到第一个 INTA 信号后锁住向 CPU 的中断请求信号INTR(高电平有效) ,并且在第二个 INTA 信号到达后将其变为低电平(自动 EOI 方式) ,所以, 中断请求信号 IR0 应该维持一段时间,直到 CPU 发送出第一个 INTA 信号,这才是一个有效的中断请求.8259 在收到第二个 INTA 信号后,就会将中断向量号发送到数据总线,CPU 读取中断向量号,并转入相应的中断处理程序中.在读取中断向量时,需要从数据总线向CPU 内总线传送数据.所以需要设计数据缓冲控制逻辑,在INTA 信号有效时,允许数据从数据总线流向 CPU 内总线.其原理图如图 4-2-2 所示.其中 RD 为 CPU 从外部读取数据的控制信号.1图 4-2-1 中断使能寄存器原理图图 4-2-2 数据缓冲控制原理图在控制总线部分表现为当 CPU 开中断允许信号 STI 有效,关中断允许信号 CLI 无效时,中断标志 EI 有效,当 CPU 开中断允许信号 STI 无效,关中断允许信号 CLI 有效时,中断标志 EI 无效.EI 无效时,外部的中断请求信号不能发送给 CPU.四、实验步骤1、实验接线:图实验接线图(时序与操作台单元)KK+-------INT(控制单元)(控制单元)INTA’-----------K5(CON单元)(控制单元)CLI---------------K6(CON单元)(控制单元)STI---------------K7(CON单元)2、实验步骤:(1)对总线进行置中断操作(K6=1,K7=0),观察控制总线部分的中断允许指示灯EI,此时EI亮,表示允许响应外部中断。

实验:系统总线和具有基本输入输出功能的总线接口实验

山西大学计算机与信息技术学院实验报告为了实现对于MEM 和外设的读写操作,还需要一个读写控制逻辑,使得CPU 能控制MEM 的读写,实验中的读写控制逻辑如图 4-2 所示,由于 T3 的参与,可以保证写脉宽与 T3 时序单元的TS3 给出(时序单元的介绍见附录2)。

IOM 用来选择是对I/O 设备还是对 MEM 作,IOM=1 时对 I/O 设备进行读写操作,IOM=0 时对 MEM 进行读写操作。

RD=1 时为读,④将R0 寄存器中的数用LED 数码管显示。

先将WR、RD、IOM 分别置为1、0、1,对OUT 单元进行写操作;再将K7 置为0,打开R0 寄存器的输出;K6 置为 0,关闭 R0 寄存器的输入;LDAR 置为 0,不将数据总线的数打入地址寄存器。

连续四次点击图形界面上的“单节拍运行”按扭,观察图形界面,在T3时刻完成对OUT 单元的写入操作。

三、实验总结:1、存储器和输入、输出设备最终是要挂接到外部总线上,因此需要外部总线提供数据信号以及控制信号。

2、外部总线和CPU 内总线之间通过三态门连接,同时实现了内外总线的分离和对于数据流向的控制。

而地址总线可以为外部设备提供地址信号和片选信号。

3.为了实现对于MEM 和外设的读写操作,还需要一个读写控制逻辑,使得CPU 能控制MEM和 I/O读写4、WR=0,RD=1,IOM=0时 E0 灭,表示存储器读功能信号有效。

WR=1,RD=0,IOM=0)连续按动开关ST,当指示灯显示为 T3 时刻时,E1 灭,表示存储器写功能信号有效。

WR=0,RD=1,IOM=1时,E2 灭,表示I/O 读功能信号有效。

WR=1,RD=0,IOM=1)时,观察扩展单元数据指示灯,指示灯显示为T3 时刻时,E3 灭,表示功能信号有效。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

计算机科学与技术系

实验报告

专业名称软件工程

课程名称计算机组成原理

项目名称具有基本输入输出功能的总线接口实验

班级 xxxxxxxxxxxxxxx 学号 xxxxxxxxxx 姓名 xxxxx

同组人员

实验日期 2015.4.13

一、实验目的与要求

1.理解总线的概念及其特性。

2.掌握控制总线的功能和应用。

二、实验逻辑原理图与分析

(所应用单板机内部资源及外围接口芯片的核心分析)

由于存储器和输入、输出设备最终是要挂接到外部总线上,所以需要外部总线提供数据信号、地址信号以及控制信号。

在该实验平台中,外部总线分为数据总线、地址总线、和控制总线,分别为外设提供上述信号。

外部总线和CPU 内总线之间通过三态门连接,同时实现了内外总线的分离和对于数据流向的控制。

地址总线可以为外部设备提供地址信号和片选信号。

由地址总线的高位进行译码,系统的I/O地址译码原理见图 1-1(在地址总线单元)。

由于使用A6、A7进行译码,I/O地址空间被分为四个区,如表 1-1所示:

图1-1 I/O 地址译码原理图

为了实现对于MEM和外设的读写操作,还需要一个读写控制逻辑,使得CPU 能控制MEM和I/O设备的读写,实验中的读写控制逻辑如图 1-2 所示,由于T3的参与,可以保证写脉宽与T3一致,T3由时序单元的TS3给出。

IOM用来选择是对I/O 设备还是对MEM进行读写操作,IOM=1时对I/O设备进行读写操作,IOM=0时对MEM 进行读写操作。

RD=1时为读,WR=1时为写。

表1-1 I/O 地址空间分配

图1-2 读写控制逻辑

三、数据通路图及分析(画出数据通路图并作出分析)

图1-3 总线传输实验框图

总线传输实验框图如图1-3 所示,它将几种不同的设备挂至总线上,有存储器、输入设备、输出设备、寄存器。

这些设备都需要有三态输出控制,按照传输恰当有序的控制它们,就可实现总线信息传输。

四、实验数据和结果分析

4.1 实验结果数据

4.2 结果数据分析

通过观察数据流正确无阻,验证了实验接线是正确的。

4.3 实验原理

1、存储器和输入、输出设备最终是要挂接到外部总线上,因此需要外部总线提

供数据信号、地址信号以及控制信号。

2、外部总线和 CPU 内总线之间通过三态门连接,同时实现了内外总线的分离和

对于数据流向的控制。

而地址总线可以为外部设备提供地址信号和片选信号。

3.为了实现对于 MEM 和外设的读写操作,还需要一个读写控制逻辑,使得 CPU 能

控制MEM和 I/O 设备的读写

4、WR=0,RD=1,IOM=0时 E0 灭,表示存储器读功能信号有效。

WR=1,RD=0,IOM=0)连续按动开关ST,当指示灯显示为 T3 时刻时,E1 灭,表示存储器写功能信号有效。

WR=0,RD=1,IOM=1时,E2 灭,表示 I/O 读功能信号有效。

WR=1,RD=0,IOM=1)时,观察扩展单元数据指示灯,指示灯显示为 T3 时刻时,E3 灭,表示 I/O 写功能信号有效。

5、在接线时为了方便,可将管脚接到CON 单元闲置的开关上,若开关打到1,等效于接到VCC;若开关打到0,等效于接到GND。

五、实验问题分析、思考题与小结

(实验过程中的问题分析、产生的原因以及解决方法;思考题;总结)

在做实验室时,由于电路的连接比较复杂,所以容易出错。

在连电路线时,有些电路接口一端接四个脚,而另一脚得接口只有两个脚,这时听了老师的建议,可以用两脚连接四脚中间的那两个,起到的效果和连接四个脚的效果是一样的。

同时连线时,需要注意两接口的接线顺序是否相同,不相同则会出现问题,同时

这个在出错时不容易寻找。

六、其它

得分(百分制)

实验报告分析评价

课程名称计算机组成原理班级软件工程一班

时间211.04.13

实验名称具有基本输入输出功能的总线接口

实验

实验报告情况分析:

由于存储器和输入、输出设备最终是要挂接到外部总线上,所以需要外部总线提供数据信号、地址信号以及控制信号。

在该实验平台中,外部总线分为数据总线、地址总线、和控制总线,分别为外设提供上述信号。

外部总线和CPU 内总线之间通过三态门连接,同时实现了内外总线的分离和对于数据流向的控制。