曼彻斯特编码VHDL程序

Manchester编码器的VHDL设计

Manchester编码器的VHDL设计

谭必思

【期刊名称】《中南民族大学学报(自然科学版)》

【年(卷),期】2002(021)003

【摘要】指出了Manchester波形具有无直流分量、宏观纠错力强、定时信号提取容易等优点,提出了采用Verilog HDL设计实现的Manchester编码器,这种设计是用软件设计技术来设计硬件系统,具有很好的灵活性、实用性和可操作性.

【总页数】3页(P52-54)

【作者】谭必思

【作者单位】中南民族大学外语系电教室

【正文语种】中文

【中图分类】TN911.21

【相关文献】

1.基于VHDL语言的多功能车辆总线编码器设计与分析 [J], 江文丹;董昱;薛红岩;陈小伟

2.基于FPGA的IRIG-B标准DC code编码器VHDL设计 [J], 王丽秋

3.基于VHDL的非系统前馈卷积码编码器设计 [J], 蔡烁;曹伟;王新

4.Manchester编码器的FPGA设计与实现 [J], 陈新坤;周东;余敬东

5.基于VHDL的HDB3编码器的设计与实现 [J], 弓云峰

因版权原因,仅展示原文概要,查看原文内容请购买。

曼切斯特编码的命名

曼切斯特编码的命名曼切斯特编码是一种数字编码方式,它将数字信号转换为双极性的矩形脉冲,并在每个时钟周期中改变信号的电平,以实现数据传输。

这种编码方式由英国曼彻斯特大学的研究人员在20世纪60年代开发出来,被广泛应用于计算机网络、通信和控制系统等领域。

曼切斯特编码的命名源于其发明地点——曼彻斯特大学。

该编码方式是由英国科学家弗雷迪·威廉姆斯(Freddie Williams)和汤姆·基尔比(Tom Kilburn)在1951年发明的。

他们使用了一种叫做“威廉姆斯管”的设备来实现电子数字计算,并将其称为“曼切斯特运算机”(Manchester Mark I)。

这台计算机是世界上第一台成功实现存储程序功能的计算机。

在曼切斯特编码中,每个数据位都被表示为一个周期内的两个时段。

如果数据位为0,则第一个时段是高电平,第二个时段是低电平;如果数据位为1,则第一个时段是低电平,第二个时段是高电平。

这样做的好处是可以减少传输中的误码率,因为每个时钟周期都有一个电平变化,可以帮助接收器更容易地识别信号的起点和终点。

曼切斯特编码的命名也与其编码方式相关。

在这种编码方式中,每个数据位都被表示为“1”或“0”,因此它是一种二进制编码方式。

而且,每个数据位都被分成两个时段,所以它是一种双极性编码方式。

由于曼切斯特编码具有这些特点,因此被称为曼切斯特二进制双极性编码(Manchester Binary Bi-Phase Coding)。

除了曼切斯特编码之外,还有其他许多数字编码方式,如差分曼彻斯特编码、四相位调制(Quadrature Phase Shift Keying, QPSK)和光纤通信中使用的非归零编码(Non-Return-to-Zero, NRZ)。

不同的数字编码方式适用于不同的应用场景和传输距离。

总之,曼切斯特编码是一种广泛应用于计算机网络、通信和控制系统等领域的数字编码方式。

它由英国科学家发明,并以发明地点命名。

曼彻斯特

摘要在电信领域,曼彻斯特码是一种数据通讯线性码,它的每一个数据比特都是由至少一次电压转换的形式所表示的。

曼彻斯特编码因此被认为是一种自定时码。

自定时意味着数据流的精确同步是可行的。

每一个比特都准确的在一预先定义时间时期的时间中被传送。

曼彻斯特编码已经被许多高效率且被广泛使用的电信标准所采用,例如以太网电讯标准. 曼彻斯特编码是一种超越传统数字传输的信道编码技术,由于其具有隐含时钟、去除了零频率信号的特性使得它在石油勘探测井中得到广泛的应用。

报告论述了曼彻斯特码的原理,介绍了其编码规则。

对其特点和应用范围进行了说明。

提出了曼彻斯特编解码方案,重点运用VHDL语言对同步信号提取电路进行了硬件仿真。

以及对使用Protel软件绘制电路图进行了介绍。

系统成功实现了曼彻斯特码数据传送的要求而且电路简单,性能稳定。

关键词:曼彻斯特码,同步信号,VHDL仿真ABSTRACT第一章绪论1.1 项目背景测井技术发展到今天,已经发生了很大的变化:一是由模拟测井技术发展到了数字测井技术;二是由数字测井技术发展到了数控测井技术。

进入90年代,成像测井技术获得了较大的发展,测井系统中需要传送的数据信息量越来越大,为此必须解决数据的高速传输与正确接收两个问题,如相关编码技术、缆芯多路复用技术、基带均衡技术等用以提高数据传输速率和降低误码率.在测井数据传输系统中,由于曼彻斯特码既能提供足够的定时分量,又无直流漂移,编码过程相对简单,因而曼彻斯特(Manchester)码是测井数据传输中常用的编码方式之一。

曼彻斯特码,又称数字双相码或分相码。

在曼彻斯特编码中,每一位的中间有一跳变,位中间的跳变既作时钟信号,又作数据信号;从高到低跳变表示”1″,从低到高跳变表示”0″。

曼彻斯特编码是将时钟和数据包含在数据流中,在传输代码信息的同时,也将时钟同步信号一起传输到对方,每位编码中有一跳变,不存在直流分量,因此具有自同步能力和良好的抗干扰性能。

用FPGA实现曼彻斯特编解码_林艺文

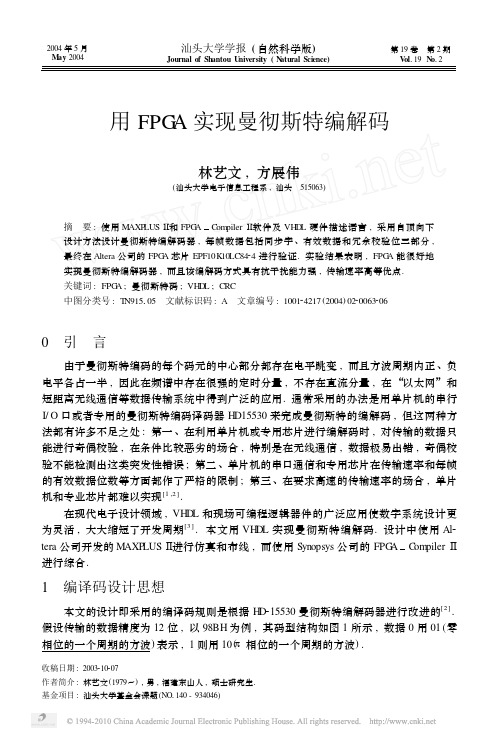

收稿日期:2003210207作者简介:林艺文(1979~),男,福建东山人,硕士研究生.基金项目:汕头大学基金会课题(NO 1140-934046)用FPG A 实现曼彻斯特编解码林艺文,方展伟(汕头大学电子信息工程系,汕头 515063)摘 要:使用M AXP LUS Ⅱ和FPG A C om piler Ⅱ软件及VH D L 硬件描述语言,采用自顶向下设计方法设计曼彻斯特编解码器,每帧数据包括同步字、有效数据和冗余校验位三部分,最终在Altera 公司的FPG A 芯片EPF10K 10LC8424进行验证.实验结果表明,FPG A 能很好地实现曼彻斯特编解码器,而且该编解码方式具有抗干扰能力强,传输速率高等优点.关键词:FPG A ;曼彻斯特码;VH D L ;CRC中图分类号:T N915105 文献标识码:A 文章编号:100124217(2004)022*******0 引 言由于曼彻斯特编码的每个码元的中心部分都存在电平跳变,而且方波周期内正、负电平各占一半,因此在频谱中存在很强的定时分量,不存在直流分量,在“以太网”和短距离无线通信等数据传输系统中得到广泛的应用.通常采用的办法是用单片机的串行I/O 口或者专用的曼彻斯特编码译码器H D15530来完成曼彻斯特的编解码,但这两种方法都有许多不足之处:第一、在利用单片机或专用芯片进行编解码时,对传输的数据只能进行奇偶校验,在条件比较恶劣的场合,特别是在无线通信,数据极易出错,奇偶校验不能检测出这类突发性错误;第二、单片机的串口通信和专用芯片在传输速率和每帧的有效数据位数等方面都作了严格的限制;第三、在要求高速的传输速率的场合,单片机和专业芯片都难以实现[1,2].在现代电子设计领域,VH D L 和现场可编程逻辑器件的广泛应用使数字系统设计更为灵活,大大缩短了开发周期[3].本文用VH D L 实现曼彻斯特编解码.设计中使用Al 2tera 公司开发的MAXP LUS Ⅱ进行仿真和布线,而使用Synopsys 公司的FPG A C om piler Ⅱ进行综合.1 编译码设计思想本文的设计即采用的编译码规则是根据H D 215530曼彻斯特编解码器进行改进的[2].假设传输的数据精度为12位,以98BH 为例,其码型结构如图1所示,数据0用01(零相位的一个周期的方波)表示,1则用10(π相位的一个周期的方波).2004年5月M ay 2004汕头大学学报(自然科学版)Journal of Sh antou U niversity (N atural Science)第19卷 第2期V ol 119N o 12图1 曼彻斯特编码的码型结构图其中,同步字有两种类型:低电平在先高电平在后为命令同步;高电平在先低电平在后为数据同步.高低电平的宽度均为115位,因此同步字宽度为3位由于每个数据位的中点都存在跳变,编码器需要大于或等于二倍频于所传数据速率的系统时钟.为了减少功耗和提高电路的可实现性,本文采用二倍频的时钟和单极性曼彻斯特编码.由图1可看到每帧的最后四位为校验位.为了提高系统的检错/纠错能力本文采用循环冗余校验.循环冗余码(CRC )是在严密的代数学理论基础上建立的,它特别适合于检测和纠错错误,一则因为它有很强的检测能力,二则是因为编码器及错误检测纠错电路都很容易实现.根据CRC 的编码思想[4,5],对于(16,12)码,可由x 16+1确定生成多项式为G (x )=x 4+1.2 编码器时序及结构当系统时钟(C LK )的上升沿到来时,如果编码使能(E NABLE )为高,编码周期将开始并持续一个帧长或20个编码时钟(即40个系统时钟)周期.同时,如果同步选择(SY N SE LECT )为高时,产生一个数据同步字;为低时,产生一个命令同步字.当编码器准备好接收数据时,发送数据(SE ND DAT A )变为高电平,并保持12个编码时钟周期.在编码时钟的上升沿对串行数据输入(DAT AI N )进行抽样和编码.根据上面的编码规则和时序说明,电路设计使用硬件描述语言(VH D L )来实现,并用Altera 公司的FPG A 芯片进行验证.设计中采用自顶向下的设计方法,将整个编码系统分成各个模块,编码总体模块框图如图2所示.图2 曼彻斯特编码总体框图46汕头大学学报(自然科学版)第19卷由于数据是串行输入的,因此上图中的CRCC 采用串行CRC 编码方法.通常,串行CRC 的编码可由线性反馈移位寄存器(LFSR )来实现.LFSR 使用异或运算及移位除法运算来产生CRC 校验码.现以本文所用到的CRC 码为例来说明串行CRCC 的VH D L 的实现.主要程序节录如下:BEGI NPROCESS (clk )BEGI NIF rst =′1′THE Nreg crc α″0000″;E LSIF clk ′event AND clk =′1′THE NIF enable =′1′THE Nreg crc (0)αtem p x ;reg crc (1)αreg crc (0);reg crc (2)αreg crc (1);reg crc (3)αreg crc (2);E LSEreg crc α″0000″;E DN IF ;E ND IF ;E ND PROCESS ;tem p x αreg crc (3)X OR datain ;crcout αreg crc (3);E ND behave ;3 解码器时序及结构解码器不停地检测输入信号.当检测到同步字,开始解码周期并判断是数据同步字(C OM DAT A 为1)还是命令同步字(C OM DAT A 为0).随后输出数据(DAT AOUT ),同时使接收数据(T AKE DAT A )为高电平,并持续12个解码时钟(即96个系统时钟)周期.在接收数据和进行CRC 时,有效字(VA LI D W ORD )保持低电平,如果传输无出错,有效字(VA LI D W ORD )变为高电平.检测输入信号值的方法:根据曼彻斯特编码的原理,也需要大于或等于二倍频于所传数据速率的解码时钟.为了提高解码的准确性,本文采用八倍频于数据速率的时钟,因此可以采用“测四取三”的方法,即对每个编码的前半部分进行四次采样,取其大于等于三的相同值作为测量值.如果没有三个相同的值,解码器不作响应,如表1所示(其中“x ”表示“0”或“1”).这种判定方法具有一定的滤波功能,提高了准确度.1)同步字的判定检测同步字是解码的关键.只有检测到同步字,才开始解码周期,因此解码器要不停地监视是否有同步字出现.56第2期林艺文等:用FPG A 实现曼彻斯特编解码2)解码在同步字出现后,采用上面“测四取三”的判定方法进行解码,获得有效数据和冗余码.3)循环冗余码校验将解码得到的有效数据和冗余码(共16位)进行循环冗余校验.如果余数为零,则认为传输中无数据出错,否则输出出错信号,以便进行出错处理.表1 信号值的判定采样1采样2采样3采样4信号值111x1110111011101111000x000100010010000“测四取三”和同步字判定各自采用一组移位寄存器来实现.在每个系统时钟的上升沿进行采样,并放入移位寄存器再根据表1判定信号值.将使用“测四取三”方法检测到的信号值放入另一组寄存器.由寄存器的前9位判定同步字,如表2所示.表2 同步字的判定寄存器的前9位同步字类型000111000数据同步字000111xxx命令同步字(xxx不全为零)表1和表2的VH D L描述是比较容易的.本文采用Case2When语句实现.解码器的总体模块框图如图3所示.图3 曼彻斯特解码总体框图4 仿真及FPG A实现为了优化结果,在进行复杂H D L设计时,基本上都会使用专业的逻辑综合软件,而不使用P LD/FPG A厂家的集成开发软件中自带的逻辑综合功能.这里使用FPG A C om pilerⅡ进行综合,输出ed f文件,导往MAXP LUSⅡ进行仿真和布线.并在FPG A芯片EPF10K10LC8424上实现,其时序仿真波形如图4和图5.图4是编码仿真.由于syn select为高表示数据同步字(即111000),如果syn select为低则为命令同步字(即000111).此时输入数据为98BH.图5是解码仿真.由于采用“测四取三”的方法,可以看到即使输入信号有小的毛刺也能正确解码,得到的数据也为98BH,而且valid w ord变为高表示传输不出错.66汕头大学学报(自然科学版)第19卷图4 编码仿真图图5 解码仿真图5 结束语对于数字处理技术来讲,软件和硬件各有特点,比如硬件在实时性要求很高的场合就比软件要好.本文的设计能很好地解决单片机编解码系统和专用芯片的问题,使传输速率和数据格式的灵活性得到提高.随着可编程器件和E DA 工具的发展,相信采用硬件描述语言设计硬件系统将会越来越方便,愈来愈受到广大电子设计人员的喜欢.参考文献:[1]何立民.单片机高级教程[M].北京:北京航空大学出版社,2000.[2]H D15530Datasheet[DB/0L ].http ://w w w 121ic 1com.[3]卢毅,赖杰.VH D L 与数字电路设计[M].北京:科学出版社,2001. 4.76第2期林艺文等:用FPG A 实现曼彻斯特编解码86汕头大学学报(自然科学版)第19卷[4]王耿,姜智忠.用H D L语言实现循环冗余校验[J].微电子学与计算机,2002,5:4~6.[5]曹志刚,钱亚生.现代通信原理[M].北京:清华大学出版社,1992.The Implementation of Manchester E ncoder andDecoder U tilizing FPGALIN Yi2wen,F ANG Zhan2wei(Department of E lectronic Engineering,Shantou University,Shantou 515063,China)Abstract:A Manchester C oder2Decoder is designed using the s oftware MAXP LUSⅡ, FPG A C om pilerⅡand the hardware descriptive language VH D L in line with the top2down method, to be im plemented in an EPF10K10LC8424chip of PFG A type manu factured by Altera C o..De2 coding process included synchronous head,data bits determination and CRC checking.The experi2 ment results have proved that FPG A can im plement Manchester C oding2Decoding and this kind of C oding2Decoding method has many advantages such as strong anti2interference ability and the high data transmission rate,etc.K ey w ords:FPG A;Manchester;VH D L;CRC。

Verilog_VHDL_曼彻斯特编码器

1.5.什么叫“综合”?一般“综合”包含哪些过程?答:在电子设计领域中“综合”的概念可以表示为:将用行为和功能层次表达的电子系统转换为低层次的便于具体实现的模块组合装配的过程。

综合包含的过程:对VHDL或Verilog HDL进行处理分析,并将其转换成电路结构或模块,这时不考虑实际器件实现,即完全与硬件无关,这个过程是一个通用电路原理图形成的过程:第2步,对实际实现目标器件的结构进行优化,并使之满足各种约束条件,优化关键路径,等等。

2.10 使用Quartus II的 Mega Wizard Plug-In Manager宏功能模块中的PLL设计一个能实现图题2.10波形的电路元件(包括一个VHDL文件和一个*.bsf原理图图标)。

其中:inclk0为电路的主频输入端,频率为50MHz;areset为异步置位端,c2和主频inclk0同频率。

c1为主频inclk0的倍频输出信号。

C0为c2的反相信号。

Locked为相位控制信号,也是输出使能控制信号。

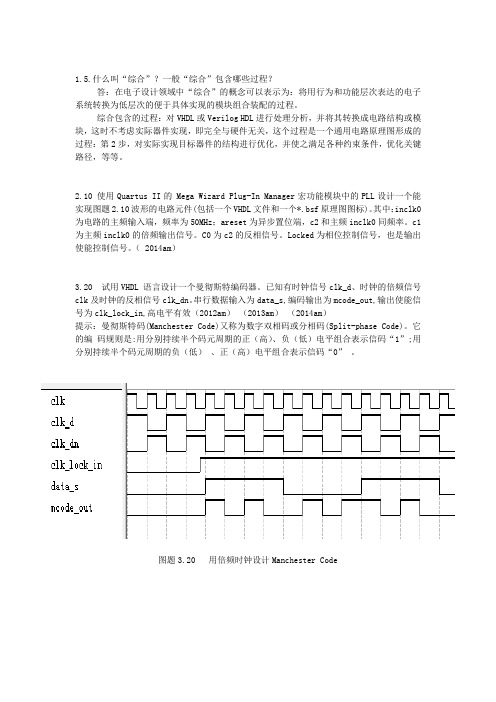

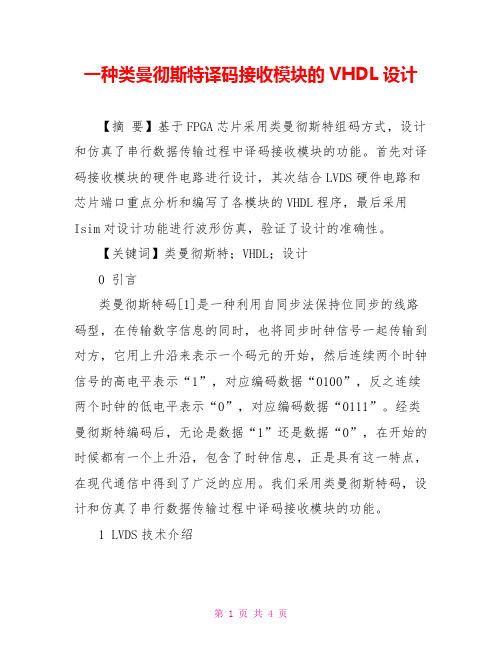

( 2014am)3.20 试用VHDL 语言设计一个曼彻斯特编码器。

已知有时钟信号clk_d、时钟的倍频信号clk及时钟的反相信号clk_dn。

串行数据输入为data_s,编码输出为mcode_out,输出使能信号为clk_lock_in,高电平有效(2012am)(2013am)(2014am)提示:曼彻斯特码(Manchester Code)又称为数字双相码或分相码(Split-phase Code)。

它的编码规则是:用分别持续半个码元周期的正(高)、负(低)电平组合表示信码“1”;用分别持续半个码元周期的负(低)、正(高)电平组合表示信码“0”。

图题3.20 用倍频时钟设计Manchester Code图题3.20 用双时钟设计Manchester Code 的仿真结果hsu_manchester_code_vmodule hsu_manchester_code_v ( clk,clk_d,clk_dn,data_s,clk_lock_in,mcode_out); input clk,clk_d,clk_dn,data_s,clk_lock_in;output mcode_out;reg mcode_out;reg temp_mcode_out;reg temp_mcode_out_ddn;always ( posedge clk or posedge clk_lock_in )beginif (clk_lock_in==1'b1)if (data_s==1'b1)temp_mcode_out<=clk_d;elsetemp_mcode_out<=1'b0;elsetemp_mcode_out=1'b0;endalways ( posedge clk or posedge clk_lock_in )beginif (clk_lock_in==1'b1)if (data_s==1'b0)temp_mcode_out_ddn<=clk_dn;elsetemp_mcode_out_ddn<=1'b0;elsetemp_mcode_out_ddn=1'b0;Endalways ( posedge clk or posedge clk_lock_in )beginif (clk_lock_in==1'b1)mcode_out<=temp_mcode_out;temp_mcode_out_ddn;elsemcode_out<=1'b0;endendmodule3.21 试用VHDL 语言设计一个求两个数中最大值的程序,要求用函数调用的方法设计。

曼彻斯特编解码器

工具软件实训报告项目名称: 曼彻斯特编解码器指导老师:系科:专业:姓名:学号:目录:一:实训要求 (2)二:实训原理 (2)三:实训思路 (3)四:实训步骤 (3)五:原理图、仿真结果图以及结论分析 (4)1、曼彻斯特编解码器(实现16bit数据得编解码) (4)1、1曼彻斯特编解码器电路原理图: (4)1、2模块详解 (4)1、3仿真图以及分析...................... 错误!未定义书签。

六:个人总结、、、、、、、、、、、、、、、、、、、、、、、、、、、、、、、、、、、、、、、、、、、、、、、、、、、、、、、、、、、、、、、、、、、、、、、、、、、、、11(1)通过学习原理图输入设计得方法掌握使用工具软件Quartus Ⅱ设计小型数字电路;(2)查阅文献,了解曼彻斯特编解码器得基本原理, 并提出在Quartus Ⅱ软件环境下用VHDL进行仿真得方案。

(3)完成设计对编码器得要求:能够对输入得16bit数据进行曼彻斯特编码,输入有时钟、使能、16bit并行数据、写信号等;输出有编码结束与曼彻斯特编码信号(都为1位信号)等。

(4)完成设计对解码器要求:能够把输入得串行曼彻斯特码解码成原先得并行数据,输入有时钟、曼彻斯特码输入(1bit)、使能信号等,输出有提取得同步时钟信号、解码完成(1bit),并行数据(16bit)等。

二:实训原理曼彻斯特编码,也叫做相位编码(PE),就是一个同步时钟编码技术,在以太网媒介系统中,被物理层使用来编码一个同步位流得时钟与数据。

它得每一个数据比特都就是由至少一次电压转换得形式所表示得。

在曼彻斯特编码中,每一位得中间有一跳变,位中间得跳变既作为时钟信号,又作为数据信号。

按照曼彻斯特码在IEEE 802、4(令牌总线)以及IEEE 802、3 (以太网)中得规定,本次实训将从高电平到低电平得跳变表示“0”,从低电平到高电平得跳变表示“1”。

以下为曼彻斯特编解码器得实现框图:有上图可知,此次得曼彻斯特编解码电路包括三个部分:信号产生部分、编码电路部分与解码电路部分。

设计报告--009---曼彻斯特编译码器的FPGA设计与实现

曼彻斯特编译码器的FPGA设计与实现一.曼切斯特编译码器设计方法的一般步骤:1)编码过程:QuartusⅡ文本输入设计方法的一般步骤2)译码过程:QuartusⅡ文本输入设计方法的一般步骤3) 编译码过程: QuartusⅡ原理图设计方法的一般步骤(一起实现)二.曼切斯特编译码器设计1)编码过程简单的设计步骤:运用QuartusⅡ文本输入设计方法的一般步骤(a)创建设计工程(b)设计输入(c)项目编译(d)项目防真验证曼切斯特编码方法简单,只需要将1编为10,0编为01,其中1和10的持续时间相同,也就是说编好的码字是原来数据码字频率的2倍。

编码器设计时,VHDL源程序具体如下:LIBRARY IEEE; /*库说明语句*/USE IEEE.STD_LOGIC_1164.ALL; /*程序包说明语句,声明USE IEEE.STD_LOGIC_ARITH.ALL; 要引用IEEE库中的USE IEEE.STD_LOGIC_UNSIGNED.ALL; 这三个程序包中的所有项目*/ENTITY MCST1 IS /*定义一个实体MCST1,clk ,clr,d为输入PORT(clk,clr,d:IN STD_LOGIC; 引脚, 为STD_LOGIC型, q1为输出引q1:OUT STD_LOGIC); 脚, 为STD_LOGIC型*/END MCST1;ARCHITECTURE divcnt OF MCST1 IS /*根据MCST1定义一个结构体名为divcnt*/ BEGINPROCESS(clk,clr) /*当clk, clr改变时,执行下面的进程*/BEGINIF(clr='1')THEN /*如果clr='1'*/q1<='0'; /* q1清0*/ELSEq1<=NOT(clk XOR d); /* clk与d的同或送q1*/END IF;END PROCESS;END divcnt;原理:当clr为1时,q1为0,则当clr为1时,把clk与d的同或送q1,若d在一个周期内为高电平时,所得的波形为clk波形。

verilog曼切斯特编码

//---------曼切斯特编码------------`timescale 1ns/1psmodule match( fifo_rd, //the enable single of superior fifo readfifo_out, //the out data of superior fifofifo_out_vaild, // the effective single of the out datafifo_empty, // the empty single of superior fifomach_out, //machester datai_clk_2, // double of hdlc clki_rst_n,clk);input i_rst_n;input fifo_out;input fifo_out_vaild;input fifo_empty;input i_clk_2;input clk;output fifo_rd;output mach_out;reg [5:0]out_count;reg [5:0]rd_count;reg fifo_rd;reg mach_out;reg [5:0]out_reg;reg [5:0]so_on;reg one;reg zero;reg temp;parameter rd_fifo_count=4'b1010;parameter mach_out_count=6'b010100;//20parameter rest=10;//-------控制fifo读---------------always @(posedge clk or negedge i_rst_n)beginif(!i_rst_n)fifo_rd<=0;else if(!fifo_empty && rd_count<rd_fifo_count && rd_count>0)fifo_rd<=1;else if(!fifo_empty && rd_count==0 && out_count==0)fifo_rd<=1;else if(rd_count==rd_fifo_count)fifo_rd<=0;elsefifo_rd<=0;end//----------fifo输出数据计?-----------always @(posedge clk or negedge i_rst_n)beginif(!i_rst_n)rd_count<=0;else if(fifo_rd && rd_count<rd_fifo_count)rd_count<=rd_count+1;elserd_count<=0;end//-----------manch数据输出-------------always @(posedge i_clk_2 or negedge i_rst_n )beginif(!i_rst_n)beginout_reg<=6'b111000;endelse if(fifo_out_vaild && out_count==0 )out_reg<=6'b111000;else if(out_count>0 && out_count<mach_out_count+8 ||out_count==mach_out_count+8)out_reg<={out_reg[4:0],temp};end//-------------控制输出mach------------always @(posedge i_clk_2 or negedge i_rst_n )beginif(!i_rst_n)begintemp<=0;zero<=0;one<=0;endelse if(fifo_out_vaild && fifo_out && zero==0)begintemp<=1;zero<=1;one<=0;endelse if(zero && fifo_out_vaild && fifo_out)begintemp<=0;zero<=0;one<=0;endelse if(fifo_out_vaild && !fifo_out && one==0)begintemp<=0;zero<=0;one<=1;endelse if(one && fifo_out_vaild && !fifo_out)begintemp<=1;one<=0;zero<=0;endelsebegintemp<=0;one<=0;zero<=0;endend//---------mach输出计数器--------------always @(posedge i_clk_2 or negedge i_rst_n)beginif(!i_rst_n)out_count<=0;else if(out_count==mach_out_count+8)out_count<=0;else if (fifo_out_vaild==1 && out_count==0)out_count<=out_count+1;else if(out_count>0 && out_count<mach_out_count+8)out_count<=out_count+1;endalways @(posedge i_clk_2 or negedge i_rst_n)beginif(!i_rst_n)mach_out<=1;elsemach_out<=out_reg[5];end endmodule。

曼切斯特编码格式

曼切斯特编码格式

曼彻斯特编码(Manchester Encoding)是一种双相线码,也被称为双相

间隔码或相位编码。

它是一种同步时钟编码技术,通过在每个比特周期内改变信号的电压或电流方向来表示数据。

具体来说,曼彻斯特编码将一个比特周期分为两个相等的部分,在第一部分时间内保持信号的方向不变,表示逻辑“0”,而在第二部分时间内改变信号的方向,表示逻辑“1”。

在曼彻斯特编码中,每个比特的时间长度是固定的,且在每个比特周期内都会有一个电平跳变。

因此,接收方可以通过检测每个比特周期内的电平跳变来确定数据的值。

由于曼彻斯特编码在每个比特周期内都有电平跳变,因此它可以提供很好的定时信息,使得接收方可以很容易地与发送方的时钟同步。

曼彻斯特编码的优点包括:简单、易于实现、能提供很好的定时信息、抗干扰能力强等。

但是,它的缺点也很明显:效率相对较低,每个比特周期内都需要一个电平跳变,因此在高速传输时可能会受到限制。

尽管如此,曼彻斯特编码仍被广泛应用于许多领域,如以太网、光纤通信等。

曼彻斯特编解码电路设计

中南大学本科生毕业论文(设计)题目曼彻斯特编解码电路设计学生姓名李天栋指导教师肖大光娄田心学院信息科学与工程学院专业班级通信工程03级2班完成时间2007年5月目录目录 .......................................... 错误!未定义书签。

摘要 .......................................... 错误!未定义书签。

ABSTRACT ...................................... 错误!未定义书签。

第一章绪论 ................................... 错误!未定义书签。

项目背景.................................... 错误!未定义书签。

项目研究内容和任务.......................... 错误!未定义书签。

论文各部分主要内容.......................... 错误!未定义书签。

第二章曼彻斯特码的原理及其编码规则............ 错误!未定义书签。

曼彻斯特码简介及其编码规则.................. 错误!未定义书签。

曼彻斯特码原理.............................. 错误!未定义书签。

曼彻斯特码的应用范围........................ 错误!未定义书签。

曼彻斯特码在LAN中的应用.................. 错误!未定义书签。

曼彻斯特码在测井系统中的应用.............. 错误!未定义书签。

第三章曼彻斯特编解码方案...................... 错误!未定义书签。

解码电路.................................... 错误!未定义书签。

同步信号提取电路............................ 错误!未定义书签。

曼彻斯特编码

曼彻斯特编码曼彻斯特编码编辑词条曼彻斯特编码(Manchester Encoding),也叫做相位编码(PE),是一个同步时钟编码技术,被物理层使用来编码一个同步位流的时钟和数据。

曼彻斯特编码被用在以太网媒介系统中。

曼彻斯特编码提供一个简单的方式给编码简单的二进制序列而没有长的周期没有转换级别,因而防止时钟同步的丢失,或来自低频率位移在贫乏补偿的模拟链接位错误。

在这个技术下,实际上的二进制数据被传输通过这个电缆,不是作为一个序列的逻辑1或0来发送的。

相反地,这些位被转换为一个稍微不同的格式,它通过使用直接的二进制编码有很多的优点。

目录简介编码规则关于数据表示的约定展开编辑本段简介曼彻斯特编码(Manchester Encoding),也叫做相位编码(PE),是一个同步时钟编码技术,被物理层使用来编码一个同步位流的时钟和数据。

曼彻斯特编码被用在以太网媒介系统中。

曼彻斯特编码提供一个简单的方式给编码简单的二进制序列而没有长的周期没有转换级别,因而防止时钟同步的丢失,或来自低频率位移在贫乏补偿的模拟链接位错误。

曼彻斯特编码,常用于局域网传输。

曼彻斯特编码将时钟和数据包含在数据流中,在传输代码信息的同时,也将时钟同步信号一起传输到对方,每位编码中有一跳变,不存在直流分量,因此具有自同步能力和良好的抗干扰性能。

但每一个码元都被调成两个电平,所以数据传输速率只有调制速率的1/2。

就是说主要用在数据同步传输的一种编码方式。

【在曼彻斯特编码中,用电压跳变的相位不同来区分1和0,即用正的电压跳变表示1,用负的电压跳变表示0。

因此,这种编码也称为相位编码。

由于跳变都发生在每一个码元的中间,接收端可以方便地利用它作为位同步时钟,因此,这种编码也称为自同步编码。

】Manchester encoding uses the transition in the middle of the timing window to determine the binary value for that bit period. In Figure , the top waveform moves to a lower position so it is interpreted as a binary zero. The second waveform moves to a higher position and is interpreted as a binary one .编辑本段编码规则在曼彻斯特编码中,每一位的中间有一跳变,位中间的跳变既作时钟信号,又作数据信号;从低到高跳变表示"1",从高到低跳变表示"0"。

基于FPGA的类曼彻斯特编码发送模块设计

基于FPGA的类曼彻斯特编码发送模块设计摘要本文基于类曼彻斯特码,采用VHDL编程,设计和仿真了串行数据传输过程中编码发送模块的功能。

类曼彻斯特码采用数据中嵌入时钟信号的设计思想,是一种利用自同步法保持位同步的线路码型,在高速串行通信过程中采用这种编码方式可以降低系统功耗,同时具有很强的抗干扰能力。

0 引言类曼彻斯特码是一种利用自同步法保持位同步的线路码型,它用上升沿来表示一个码元的开始,然后连续两个时钟信号的高电平表示“1”,对应编码数据“0100”,反之连续两个时钟的低电平表示“0”,对应编码数据”0111”。

经类曼彻斯特编码后,无论是数据“1”还是数据“0”,在开始的时候都有一个上升沿,包含了时钟信息,正是具有这一特点,类曼彻斯特编码发送功能的设计实现解决了串行数据传输的同步时钟问题。

1硬件设计在硬件设计时采用LVDS差分电路,LVDS是一种低摆幅的差分信号技术,它使得信号能够在差分平衡电缆上以几百Mbps的速率传输,其低压幅和低电流的驱动输出完全达到了低噪声和低功耗的要求。

本设计中,FPGA传出的串行数据通过差分电路的转换,形成差分形式的数据,向外传输,设计电路如图1所示。

图1 发送模块该电路临近输出端串接了10Ω的电阻,可以防止差分线对短路,缺点在于420mV的驱动电压已接近数据手册中给出的V od最大值454mV。

同时设计中还需要考虑信号反射问题,这种现象的产生会导致噪声类型的转变,使其从原来的共模信号转变为差模信号,从而降低数据传输的准确性。

为了避免这一问题,我们在设计中应做到在信号值不同时输出阻抗保持不变,同时,输出阻抗的下限只能稍小于传输线特性阻抗,而它的上限必须略大于传输线的特性阻抗。

2 软件设计类曼彻斯特编码可以分为三步进行。

第一步,检测编码周期是否开始并发送开始信号;第二步,对十五位数据进行类曼彻斯特编码;第三步,采用偶校验方式生成校验位,完成编码周期。

具体编程时可以分为数据定义、数据转换及校验和数据编码及发送三大模块。

曼彻斯特编解码器

工具软件实训报告项目名称:曼彻斯特编解码器指导老师:系科:专业:姓名:学号:目录:一:实训要求 (3)二:实训原理 (3)三:实训思路 (4)四:实训步骤 (4)五:原理图、仿真结果图以及结论分析 (5)1.曼彻斯特编解码器(实现16bit数据的编解码) (5)1.1曼彻斯特编解码器电路原理图: (5)1.2模块详解 (6)1.3仿真图以及分析 (10)六:个人总结 (11)一:实训要求(1)通过学习原理图输入设计的方法掌握使用工具软件Quartus Ⅱ设计小型数字电路;(2)查阅文献,了解曼彻斯特编解码器的基本原理,并提出在Quartus Ⅱ软件环境下用VHDL进行仿真的方案。

(3)完成设计对编码器的要求:能够对输入的16bit数据进行曼彻斯特编码,输入有时钟、使能、16bit并行数据、写信号等;输出有编码结束和曼彻斯特编码信号(都为1位信号)等。

(4)完成设计对解码器要求:能够把输入的串行曼彻斯特码解码成原先的并行数据,输入有时钟、曼彻斯特码输入(1bit)、使能信号等,输出有提取的同步时钟信号、解码完成(1bit),并行数据(16bit)等。

二:实训原理曼彻斯特编码,也叫做相位编码(PE),是一个同步时钟编码技术,在以太网媒介系统中,被物理层使用来编码一个同步位流的时钟和数据。

它的每一个数据比特都是由至少一次电压转换的形式所表示的。

在曼彻斯特编码中,每一位的中间有一跳变,位中间的跳变既作为时钟信号,又作为数据信号。

按照曼彻斯特码在IEEE 802.4(令牌总线)以及IEEE 802.3 (以太网)中的规定,本次实训将从高电平到低电平的跳变表示“0”,从低电平到高电平的跳变表示“1”。

三:实训思路以下为曼彻斯特编解码器的实现框图:有上图可知,此次的曼彻斯特编解码电路包括三个部分:信号产生部分、编码电路部分和解码电路部分。

其中,信号产生部分用来产生一个循环的16位二进制数据编码作为普通的信号输入;编码部分则将输入的信号编码为曼彻斯特码,然后输出显示;解码部分负责将获得的曼彻斯特码解码成普通的二进制数据编码。

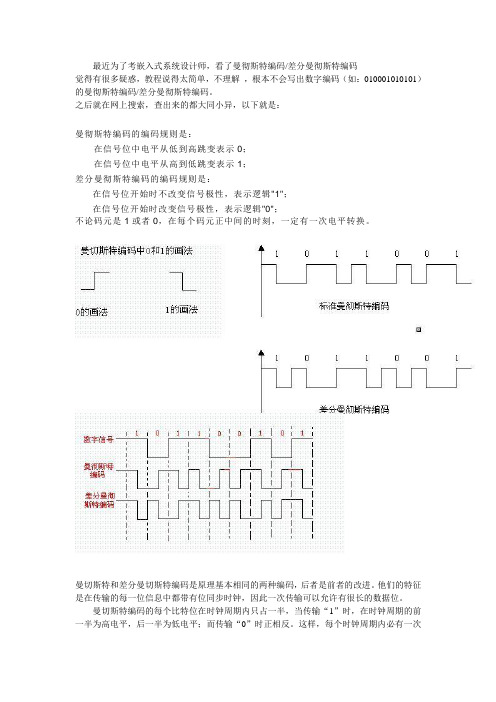

快速学会曼彻斯特编码以及差分曼彻斯特编码

最近为了考嵌入式系统设计师,看了曼彻斯特编码/差分曼彻斯特编码觉得有很多疑惑,教程说得太简单,不理解,根本不会写出数字编码(如:010*********)的曼彻斯特编码/差分曼彻斯特编码。

之后就在网上搜索,查出来的都大同小异,以下就是:曼彻斯特编码的编码规则是:在信号位中电平从低到高跳变表示0;在信号位中电平从高到低跳变表示1;差分曼彻斯特编码的编码规则是:在信号位开始时不改变信号极性,表示逻辑"1";在信号位开始时改变信号极性,表示逻辑"0";不论码元是1或者0,在每个码元正中间的时刻,一定有一次电平转换。

曼切斯特和差分曼切斯特编码是原理基本相同的两种编码,后者是前者的改进。

他们的特征是在传输的每一位信息中都带有位同步时钟,因此一次传输可以允许有很长的数据位。

曼切斯特编码的每个比特位在时钟周期内只占一半,当传输“1”时,在时钟周期的前一半为高电平,后一半为低电平;而传输“0”时正相反。

这样,每个时钟周期内必有一次跳变,这种跳变就是位同步信号。

差分曼切斯特编码是曼切斯特编码的改进。

它在每个时钟位的中间都有一次跳变,传输的是“1”还是“0”,是在每个时钟位的开始有无跳变来区分的。

差分曼切斯特编码比曼切斯特编码的变化要少,因此更适合与传输高速的信息,被广泛用于宽带高速网中。

然而,由于每个时钟位都必须有一次变化,所以这两种编码的效率仅可达到50%左右这是在网上下载的,看了之后还是萌萌哒,完全搞不懂。

还好,经过一番努力,终于找到快速画出曼彻斯特编码/差分曼彻斯特编码的方法了,以下是我从网上找到的资料并且总结的,给自己留下个纪念吧。

再来做下08年中级网络工程师真题,你会了吗?答案:C。

Verilog VHDL 曼彻斯特编码器..

1.5.什么叫“综合”?一般“综合”包含哪些过程?答:在电子设计领域中“综合”的概念可以表示为:将用行为和功能层次表达的电子系统转换为低层次的便于具体实现的模块组合装配的过程。

综合包含的过程:对VHDL或Verilog HDL进行处理分析,并将其转换成电路结构或模块,这时不考虑实际器件实现,即完全与硬件无关,这个过程是一个通用电路原理图形成的过程:第2步,对实际实现目标器件的结构进行优化,并使之满足各种约束条件,优化关键路径,等等。

2.10 使用Quartus II的 Mega Wizard Plug-In Manager宏功能模块中的PLL设计一个能实现图题2.10波形的电路元件(包括一个VHDL文件和一个*.bsf原理图图标)。

其中:inclk0为电路的主频输入端,频率为50MHz;areset为异步置位端,c2和主频inclk0同频率。

c1为主频inclk0的倍频输出信号。

C0为c2的反相信号。

Locked为相位控制信号,也是输出使能控制信号。

( 2014am)3.20 试用VHDL 语言设计一个曼彻斯特编码器。

已知有时钟信号clk_d、时钟的倍频信号clk及时钟的反相信号clk_dn。

串行数据输入为data_s,编码输出为mcode_out,输出使能信号为clk_lock_in,高电平有效(2012am)(2013am)(2014am)提示:曼彻斯特码(Manchester Code)又称为数字双相码或分相码(Split-phase Code)。

它的编码规则是:用分别持续半个码元周期的正(高)、负(低)电平组合表示信码“1”;用分别持续半个码元周期的负(低)、正(高)电平组合表示信码“0”。

图题3.20 用倍频时钟设计Manchester Code图题3.20 用双时钟设计Manchester Code 的仿真结果hsu_manchester_code_vmodule hsu_manchester_code_v ( clk,clk_d,clk_dn,data_s,clk_lock_in,mcode_out); input clk,clk_d,clk_dn,data_s,clk_lock_in;output mcode_out;reg mcode_out;reg temp_mcode_out;reg temp_mcode_out_ddn;always @ ( posedge clk or posedge clk_lock_in )beginif (clk_lock_in==1'b1)if (data_s==1'b1)temp_mcode_out<=clk_d;elsetemp_mcode_out<=1'b0;elsetemp_mcode_out=1'b0;endalways @ ( posedge clk or posedge clk_lock_in )beginif (clk_lock_in==1'b1)if (data_s==1'b0)temp_mcode_out_ddn<=clk_dn;elsetemp_mcode_out_ddn<=1'b0;elsetemp_mcode_out_ddn=1'b0;Endalways @ ( posedge clk or posedge clk_lock_in )beginif (clk_lock_in==1'b1)mcode_out<=temp_mcode_out;temp_mcode_out_ddn;elsemcode_out<=1'b0;endendmodule3.21 试用VHDL 语言设计一个求两个数中最大值的程序,要求用函数调用的方法设计。

曼彻斯特编解码电路设计

中南大学本科生毕业论文(设计)题目曼彻斯特编解码电路设计学生姓名李天栋指导教师肖大光娄田心学院信息科学与工程学院专业班级通信工程03级2班完成时间2007年5月目录目录 (I)摘要 (IV)ABSTRACT (V)第一章绪论 (6)1.1项目背景 (6)1.2项目研究内容和任务 (6)1.3论文各部分主要内容 (6)第二章曼彻斯特码的原理及其编码规则 (8)2.1曼彻斯特码简介及其编码规则 (8)2.2曼彻斯特码原理 (8)2.3曼彻斯特码的应用范围 (10)2.3.1 曼彻斯特码在LAN中的应用 (12)2.3.2 曼彻斯特码在测井系统中的应用 (12)第三章曼彻斯特编解码方案 (14)3.1编码电路 (14)3.2解码电路 (20)3.3同步信号提取电路 (21)3.3.1 利用电压比较器整形曼码 (23)3.3.2 利用微分电路检出曼码跳变沿 (24)3.3.3 全波整流电路 (26)3.3.4 窄带滤波电路 (29)3.3.5 锁相环 (32)第四章运用VHDL语言对同步方法仿真 (35)4.1VHDL语言简介 (35)4.2VHDL语言仿真 (35)第五章 PROTEL软件绘制电路图简介 (38)5.1P ROTEL软件简介 (38)5.2电路图绘制 (38)第六章结论与展望 (41)参考文献 (42)致谢 (43)附录 (44)摘要在电信领域,曼彻斯特码是一种数据通讯线性码,它的每一个数据比特都是由至少一次电压转换的形式所表示的。

曼彻斯特编码因此被认为是一种自定时码。

自定时意味着数据流的精确同步是可行的。

每一个比特都准确的在一预先定义时间时期的时间中被传送。

曼彻斯特编码已经被许多高效率且被广泛使用的电信标准所采用,例如以太网电讯标准. 曼彻斯特编码是一种超越传统数字传输的信道编码技术,由于其具有隐含时钟、去除了零频率信号的特性使得它在石油勘探测井中得到广泛的应用。

报告论述了曼彻斯特码的原理,介绍了其编码规则。

一种类曼彻斯特译码接收模块的VHDL设计

一种类曼彻斯特译码接收模块的VHDL设计【摘要】基于FPGA芯片采用类曼彻斯特组码方式,设计和仿真了串行数据传输过程中译码接收模块的功能。

首先对译码接收模块的硬件电路进行设计,其次结合LVDS硬件电路和芯片端口重点分析和编写了各模块的VHDL程序,最后采用Isim对设计功能进行波形仿真,验证了设计的准确性。

【关键词】类曼彻斯特;VHDL;设计0 引言类曼彻斯特码[1]是一种利用自同步法保持位同步的线路码型,在传输数字信息的同时,也将同步时钟信号一起传输到对方,它用上升沿来表示一个码元的开始,然后连续两个时钟信号的高电平表示“1”,对应编码数据“0100”,反之连续两个时钟的低电平表示“0”,对应编码数据“0111”。

经类曼彻斯特编码后,无论是数据“1”还是数据“0”,在开始的时候都有一个上升沿,包含了时钟信息,正是具有这一特点,在现代通信中得到了广泛的应用。

我们采用类曼彻斯特码,设计和仿真了串行数据传输过程中译码接收模块的功能。

1 LVDS技术介绍LVDS[2]是一种低摆幅的差分信号技术,具有终端适配简洁方便、低功耗、低成本、高速传输等优点,并且能对传输数据进行时效保护,确保了数据传输的可靠性。

LVDS使得信号能够在差分平衡电缆上以几百Mbps[3]的速率传输,其低压幅和低电流的驱动输出完全达到了低噪声和低功耗的要求。

采用LVDS技术设计的接收器引进恒流式驱动方式,准许带电插入,对系统不会造成任何损坏,适用于高速数据的传输。

差分信号的抗噪特性在理想状态[4]下,所谓理想状态是指线路没有干扰时,发送端IN= IN+-IN-,接收端IN+-IN-=OUT,发送端信号等于接收端信号。

在非理想状态下,非理想状态是指线路有干扰时,发送端IN=IN+-IN-,接收端(IN++q)-(IN-+q)= IN+-IN-=OUT,噪声在输出端被抑制掉,所以输入端信号依旧等于输出端信号。

从两种状态的分析可知差分方式可以很好的抑制噪声,确保数据准确无误的传输。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

tsr <= "00000000" ;

elsif clk1x'event and clk1x = '1' then

if std_logic_vector(no_bits_sent) = "0001" then

tsr <= tbr ;

elsif std_logic_vector(no_bits_sent) >= "0010" and std_logic_vector(no_bits_sent) <= "1010" then

end process ;

process (rst,clk16x,wrn1,wrn2)

begin

if rst = '1' then

tbr <= "00000000" ;

elsif clk16x'event and clk16x = '0' then

if wrn1 = '1' and wrn2 = '0' then

tbr <= din ;

end if ;

end if ;

end process ;

process (rst,clk16x,clkdiv,clk1x_enable)

begin

if rst = '1' then

clkdiv <= "0000" ;

elsif clk16x'event and clk16x = '1' then

if clk1x_enable = '1' then

clkdiv <= clkdiv + "0001" ;

end if ;

end if ;

end process ;

clk1x <= clkdiv(3) ;

process (rst,clk1x,no_bits_sent,tsr)

begin

signal clk1x : std_logic ;

signal clk1x_enable : std_logic ;

signal clkdiv : std_logic_vector (3 downto 0) ;

signal tsr : std_logic_vector (7 downto 0) ;

tsr <= tsr(6 downto 0) & '0' ;

else

tsr <= tsr ;

end if ;

end if ;

end process ;

mdo <= tsr(7) xor clk1x ;

process (rst,clk1x,tsr(7))

begin

if rst = '1' then

parity <= '0' ;

elsif clk1x'event and clk1x = '1' then

parity <= parity xor tsr(7) ;

end if ;

end process ;

process (clk1x,rst,clk1x_disable,clk1x_enable,no_bits_sent)

if (wrn1 = '1' and wrn2 = '0') then

tbre <= '0' ;

elsif (std_logic_vector(no_bits_sent) = "0010") then

tbre <= '1' ;

else

tbre <= '0' ;

end if ;

end if ;

entity me is

port (rst,clk16x,wrn : in std_logic ;

din : in std_logic_vector (7 downto 0) ;

tbre : out std_logic ;

mdo : out std_logic

) ;

end me ;

architecture v1 of me is

clk1x_enable <= '0' ;

end if ;

end if ;

end process ;

process (rst,clk16x,wrn1,wrn2,no_bits_sent)

begin

if rst = '1' then

tbre <= '1' ;

elsif clk16x'event and clk16x = '1' then

signal wrn2 : std_logic ;

signal clk1x_disable : std_logic ;

begin

process (rst,clk16x,wrn,wrn1,wrn2)

begin

if rst = '1' then

wrn2 <= '1' ;

wrn1 <= '1' ;

end if ;

end if ;

end process ;

clk1x_disable <= not clk1x_enable ;

end ;

begin

if rst = '1' or clk1x_disable = '1' then

no_bits_sent <= "0000" ;

elsif clk1x'event and clk1x = '1' then

if clk1x_enable = '1' then

no_bits_sent <= no_bits_sent + "0001" ;

elsif clk16x'event and clk16x = '1' then

wrn2 <= wrn1 ;

wrn1 <= wrn ;

end if ;

end process ;

process (rst,clk16x,wrn1,wrn2,no_bits_sent)

begin

if rst = '1' or std_logic_vector(no_bits_sent) = "1010" then

signal tbr : std_logic_vector (7 downto 0) ;

signal parity : std_logic ;

sigvector (3 downto 0) ;

signal wrn1 : std_logic ;

clk1x_enable <= '0' ;

elsif clk16x'event and clk16x = '1' then

if (wrn1 = '1' and wrn2 = '0') then

clk1x_enable <= '1' ;

elsif std_logic_vector(no_bits_sent) = "1001" then