DDR2控制和FPGA实现

基于DDR2 SDRAM乒乓双缓冲的高速数据收发系统设计

基于DDR2 SDRAM乒乓双缓冲的高速数据收发系统设计刘杰;赛景波【摘要】在高速数据收发系统设计中,首先需要解决的问题是实时数据的高速缓存,然而FPGA内部有限的存储资源无法满足海量数据缓存的要求。

为了解决系统中海量数据的缓存问题,系统创新提出了一种基于DDR2 SDRAM的乒乓双缓冲设计方案。

方案设计了两路基于DDR2 SDRAM的大容量异步FIFO,通过FPGA内部选择逻辑实现两条通路间的乒乓操作,从而实现数据的高速缓存。

实验结果表明,基于DDR2 SDRAM的数据收发系统实现了每路512 Mbit的缓存空间和200 MHz的总线速率,解决了海量数据的高速缓存问题。

%In the high-speed data transceiver system design, the first problem to be solved is the real-time data cache,However,the limited memory resources of FPGA can not meet the requirements of massive data cache,To solve the problem of system cache huge amounts of data,the system proposed ping-pong double buffering innovative design based on the DDR2 SDRAM. Design of two-way high-capacity asynchronous FIFO based on DDR2 SDRAM, selection logic operations to achieve a ping-pong between the two paths through the FPGA to achieve the cached da-ta . Experimental results show that the Data transceiver system based on DDR2 SDRAM realized every road 512 Mbit cache space and 200 MHz of the bus rate and solved the problem of the huge amounts of data cache.【期刊名称】《电子器件》【年(卷),期】2015(000)003【总页数】5页(P650-654)【关键词】高速数据收发;乒乓双缓冲;DDR2 SDRAM技术;异步FIFO【作者】刘杰;赛景波【作者单位】北京工业大学电控学院,北京100022;北京工业大学电控学院,北京100022【正文语种】中文【中图分类】TN919.6高速数据传输是现代信号处理的基础,在雷达、通信、遥测遥感等技术应用领域得到了广泛的应用。

基于FPGA的视频转换系统设计

基于FPGA的视频转换系统设计任勇峰;王大伟;石永亮;于丽娜【摘要】为解决不同视频系统之间显示时序、色彩空间、帧频、分辨率等不一致的问题,设计了一种以FPGA为控制核心, DDR2 SDRAM为高速缓存的视频转换系统,该系统从图形工作站采集到DVI视频,先进入高速缓存模块,然后通过视频转换算法在FPGA内部完成RGB至YCbCr的色彩空间转换,最后控制硬件实现PAL视频输出,实现了由DVI视频向PAL视频的转换。

经长期测试证明:该系统稳定可靠,达到设计要求。

%In order to solve the display between different video systems in consistencies timing,color space,framerate,resolution,etc,a video conversion system was designed,which regards FPGA as the control core,DDR2 SDRAM for cache. the device system collected DVI video from workstation graphics,firstly enters the cache mod⁃ule,and then completes the color space conversion and frame rate conversion via video conversion algorithm within the FPGA,and finally controls hardware PAL video output,completed by the DVI video conversion to PAL video. The long-term test proves:the system is stable and reliable,and meet the design requirements.【期刊名称】《电子器件》【年(卷),期】2016(039)003【总页数】7页(P655-661)【关键词】视频转换;DVI;PAL;高速缓存;转换算法【作者】任勇峰;王大伟;石永亮;于丽娜【作者单位】中北大学仪器科学与动态测试教育部重点实验室;中北大学仪器科学与动态测试教育部重点实验室;中北大学仪器科学与动态测试教育部重点实验室;中北大学电子测试技术重点实验室,太原030051【正文语种】中文【中图分类】TP274.2随着多媒体信息技术的高速发展,视频技术多元化发展成为趋势,而同时也激化了视频系统之间互联的矛盾。

DDR存储控制器的设计与应用

DDR存储控制器的设计与应用随着科技的不断进步,数字电子设备在日常生活和工作中的应用越来越广泛。

其中,DDR存储控制器作为计算机存储系统的重要组成部分,对于整个系统的性能和稳定性具有举足轻重的作用。

本文将详细阐述DDR存储控制器的概念、设计步骤、技术方案以及实验结果,并探讨其未来的发展趋势。

DDR存储控制器,全称Double Data Rate SDRAM控制器,是一种用于管理计算机存储系统的芯片或模块。

其主要作用是控制数据的传输速率和带宽,协调内存与处理器之间的数据交换,从而确保数据的高速、稳定传输。

DDR存储控制器适用于各种计算机存储设备,如DDR SDRAM、DDR2 SDRAM、DDR3 SDRAM等。

DDR存储控制器的硬件设计主要包括以下步骤:(1)确定控制器的架构和组成元件,包括数据路径、控制逻辑、时钟发生器等。

(2)设计电路板,包括布局布线和元件放置等。

(3)编写硬件描述语言(HDL),如Verilog或VHDL,用于实现控制器的逻辑功能。

(4)仿真和验证硬件设计,确保其符合预期的功能和性能要求。

DDR存储控制器的软件设计主要包括以下步骤:(1)编写存储控制器的驱动程序,包括初始化和配置控制器、读写数据等操作。

(2)优化数据传输速率和带宽,以实现更高效的数据传输和控制。

(3)配合硬件设计,实现软硬件联合调试和测试。

在DDR存储控制器的设计中,我们采用了以下技术方案:采用同步动态随机存取存储器(SDRAM)作为主要的存储介质,其具有较高的存储密度和较低的功耗。

使用双倍数据速率(DDR)技术,使得SDRAM在每个时钟周期内可以进行两次数据传输,从而大幅提高了数据传输速率和带宽。

引入高速缓存接口(Cache Interface),以提高数据访问速度和降低CPU的负载。

使用可编程逻辑门阵列(FPGA)作为控制器的主要芯片,其具有灵活性和可定制性,能够满足各种不同的存储需求。

我们设计并实现了一款DDR存储控制器,并对其进行了严格的测试。

DDR2 控制器Altera FPGA 管脚分配步骤

DDR2 控制器Altera FPGA管脚分配步骤 骏龙科技技术支持部1.在megawizard中选择DDR2控制器。

2.设置memory相关参数,包括DDR2数据位宽,时钟速率,地址等。

3.设置controller相关参数,册。

5.设置board timing,这里的参数与PCB走线有关。

6.仿真模型设置,如果需要对生成的IP进行功能仿真,选上Generate Simulation Model。

7.生成DDR2控制器IP,在工程目录下可以查看到Altera 提供一个自测程序文件(_example_top.v),把_example_top.v设置为top level file。

8.在settings下的timequest timing analyzer处添加DDR2的时序约束文件SDC文件,如下图。

9.综合工程和管脚约束:综合完成后运行tcl scripts(在tools菜单下):选中_pin_assignments.tcl,然后点击RUN。

10.运行打开pin planner :assignments/pin planner11.分配dqs信号到想要的DQS管脚上,注意DQS group有X8/X9mode,X4/X5mode,X16/X18mode.12.指定DQ,ADDRESS和命令信号等到相应的IO bank,但DQ是跟随DQS的。

如图,只需把location指定到bank位置,不需指定到某个IO号。

13.位置指定完成后,全编译!14.全编译后查看是否有时序不满足,主要看信息栏,是否有报关键警告。

15.16.编译完成,时序也满足要求后运行:assignments/back-annotate assignments将之前指定到IObank的管脚反标到特定的IO管脚上。

再查看pin planner时,你将会发现上图变为下图所示:17.在assignments下选择Pin planner,倒出管脚文件,文件名后缀为*.csv.18.。

FPGA与DDR2SDRAM互联的信号完整性分析

Ke wo d : sg a itg i I p t tu Bufr no main p cf ain(BI ) mo e;hg —p e P itd y r s in l ne ry; n u/ p t t Ou f If r t S e i c t e o i o I S d l ih s e d r e Cic i n rut Bo r ad

联 。4 D 2 S AM共享地址线和控制 命令线 。数据线是 片 DR DR 点对点连接方 式 , 拓扑结构 简单。地址线和控制命令线的连接 存在一个拓扑结构 的选择问题。树形拓扑结构和菊花链式拓扑 结构 是两 种常见 的拓 扑结 构一 章从 仿真 的 角度 分析 上面 。文 两种不 同拓扑结 构下不同的端接方式对信 号完整性的影响 。

S DRAM. mp tr En i e rn n p ia in , 0 1 4 ( 9 : 5 — 6 . Co u e gn e i g a d Ap l to s 2 1 , 7 2 ) 1 8 1 0 c

Ab t a t Ths p p r d s r e h r be o in l ne r y b t e r x 5 n sr c : i a e e ci s t e p o lm f sg a itg i ewe n Vi e - a d DDR2 S b t t DRAM ne c n e t n I a ay e t i tro n ci . n lz s i o t s

o f PCB ouig. e e ul oft s o ott e a hie e nsr ts t a u h t e r s e e t i e d sg o i —p e ic i. r t Th rs t e t n pr oyp m c n d mo tae h ts c o y i f ci n h ve n t e in f hgh s e d cr ut h

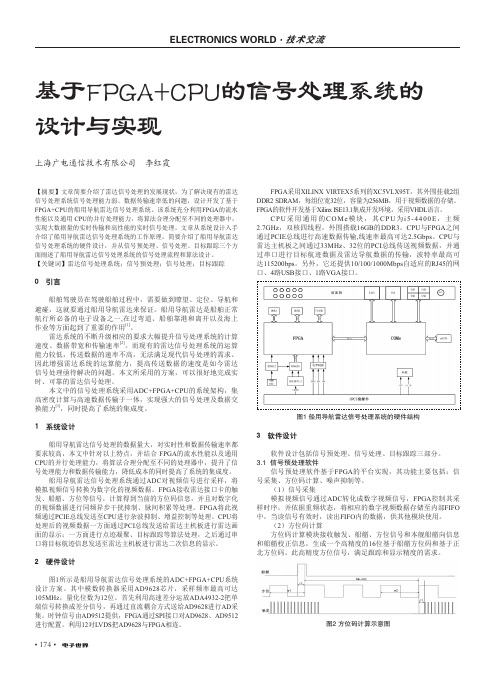

基于FPGA+CPU的信号处理系统的设计与实现

• 174•基于FPGA+CPU的信号处理系统的设计与实现上海广电通信技术有限公司 李红霞【摘要】文章简要介绍了雷达信号处理的发展现状,为了解决现有的雷达信号处理系统信号处理能力弱、数据传输速率低的问题,设计开发了基于FPGA+CPU 的船用导航雷达信号处理系统。

该系统充分利用FPGA 的流水性能以及通用 CPU 的并行处理能力,将算法合理分配至不同的处理器中,实现大数据量的实时传输和高性能的实时信号处理。

文章从系统设计入手介绍了船用导航雷达信号处理系统的工作原理,简要介绍了船用导航雷达信号处理系统的硬件设计,并从信号预处理、信号处理、目标跟踪三个方面阐述了船用导航雷达信号处理系统的信号处理流程和算法设计。

【关键词】雷达信号处理系统;信号预处理;信号处理;目标跟踪0 引言船舶驾驶员在驾驶船舶过程中,需要做到瞭望、定位、导航和避碰,这就要通过船用导航雷达来保证。

船用导航雷达是船舶正常航行所必备的电子设备之一,在过弯道、船舶靠港和离开以及海上作业等方面起到了重要的作用[1]。

雷达系统的不断升级相应的要求大幅提升信号处理系统的计算速度、数据带宽和传输速率[2]。

而现有的雷达信号处理系统的运算能力较低,传送数据的速率不高,无法满足现代信号处理的需求。

因此增强雷达系统的运算能力,提高传送数据的速度是如今雷达信号处理亟待解决的问题。

本文所采用的方案,可以很好地完成实时、可靠的雷达信号处理。

本文中的信号处理系统采用ADC+FPGA+CPU 的系统架构,集高密度计算与高速数据传输于一体,实现强大的信号处理及数据交换能力[1],同时提高了系统的集成度。

1 系统设计船用导航雷达信号处理的数据量大,对实时性和数据传输速率都要求较高,本文中针对以上特点,并结合 FPGA 的流水性能以及通用 CPU 的并行处理能力,将算法合理分配至不同的处理器中,提升了信号处理能力和数据传输能力,降低成本的同时提高了系统的集成度。

船用导航雷达信号处理系统通过ADC 对视频信号进行采样,将模拟视频信号转换为数字化的视频数据。

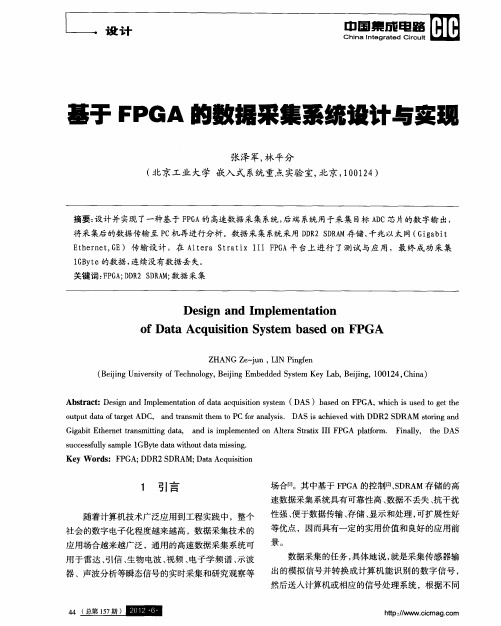

基于FPGA的数据采集系统设计与实现

了异步传输 中跨时钟域造成的亚稳态问题 [ 5 1 。在本 数据采集系统的设计中采用异步 FF IO的方式来解

图 2 数 据 采 集 系统 数 据 流 程

决跨时钟域 的数据传输 问题 。因为本数据采集系统 是针对 A C芯片的测试所用的, D 因此数据采集接 口 的数据率不是 固定 的 10 H x4i 而 D R 控制 5M z5b , D 2 t 器的用户接 口和 G E控制器接 口数据率是 固定的 , 分别为 10 H x 1b 和 15 z 2i 5 M zl2i t 2MH x b ,所 以选用 3 t 异步 FF IO可以使 系统更加灵活。

基于 F GA的数据采集系统设计与实现 P

张 泽 军 , 平 分 林

( 北京工业 大学 嵌入式 系统重点 实验 室, 北京, 1 4 102 ) 0

摘要 : 设计 并 实现 了一种基 于 FG P A的 高速 数据 采 集 系统 , 端 系统 用于采 集 目标 A C芯 片 的数 字输 出, 后 D 将 采集后 的数据传 输 至 P C机再 进行 分析 。数据 采 集 系统 采用 DR D A 储 、 兆 以太 网 ( ia i D 2SRM存 千 G gb t

数据传输及控制。同时 , 模块还负责 G I F E控制器、

图 1数 据 采 集 系统 框 图

D R D 2控制 器 的用户 总线及 外 部数 据采 集 接 口之间

h¨ n . h n nA 、 ,m a , , n / s A i, ;、 1 、

L一设 — 计

巾国集成电路

Chi na nt I eg r ed icu i at C r t

块 ,其 功 能 相 当 于 一 个 D MA ( i c M m r Dr t e oy e

DDR PCB设计

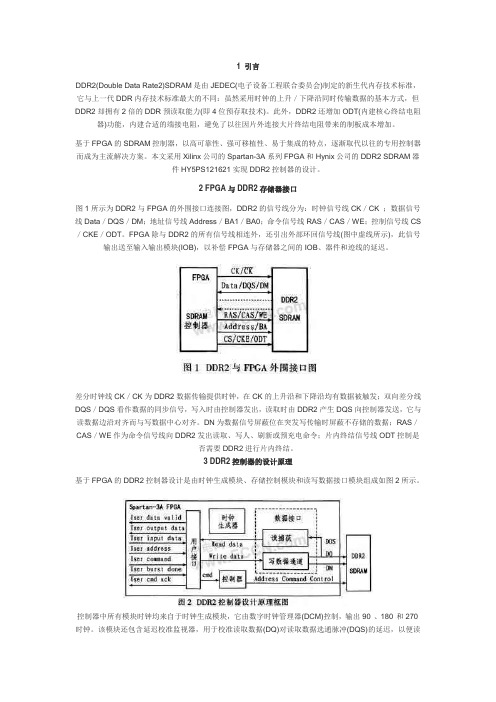

1 引言DDR2(Double Data Rate2)SDRAM是由JEDEC(电子设备工程联合委员会)制定的新生代内存技术标准,它与上一代DDR内存技术标准最大的不同:虽然采用时钟的上升/下降沿同时传输数据的基本方式,但DDR2却拥有2倍的DDR预读取能力(即4位预存取技术)。

此外,DDR2还增加ODT(内建核心终结电阻器)功能,内建合适的端接电阻,避免了以往因片外连接大片终结电阻带来的制板成本增加。

基于FPGA的SDRAM控制器,以高可靠性、强可移植性、易于集成的特点,逐渐取代以往的专用控制器而成为主流解决方案。

本文采用Xilinx公司的Spartan-3A系列FPGA和Hynix公司的DDR2 SDRAM器件HY5PS121621实现DDR2控制器的设计。

2 FPGA与DDR2存储器接口图1所示为DDR2与FPGA的外围接口连接图,DDR2的信号线分为:时钟信号线CK/CK ;数据信号线Data/DQS/DM;地址信号线Address/BA1/BA0;命令信号线RAS/CAS/WE;控制信号线CS /CKE/ODT。

FPGA除与DDR2的所有信号线相连外,还引出外部环回信号线(图中虚线所示),此信号输出送至输入输出模块(IOB),以补偿FPGA与存储器之间的IOB、器件和迹线的延迟。

差分时钟线CK/CK为DDR2数据传输提供时钟,在CK的上升沿和下降沿均有数据被触发;双向差分线DQS/DQS看作数据的同步信号,写入时由控制器发出,读取时由DDR2产生DQS向控制器发送,它与读数据边沿对齐而与写数据中心对齐。

DN为数据信号屏蔽位在突发写传输时屏蔽不存储的数据;RAS/CAS/WE作为命令信号线向DDR2发出读取、写人、刷新或预充电命令;片内终结信号线ODT控制是否需要DDR2进行片内终结。

3 DDR2控制器的设计原理基于FPGA的DDR2控制器设计是由时钟生成模块、存储控制模块和读写数据接口模块组成如图2所示。

基于FPGA的DDR2存储器控制器设计_河北科技大学.

毕业设计学生姓名:洪雷学号: 09xxxxxxxx 专业:电子科学与技术题目:基于FPGA的DDR2存储器控制器设计指导教师:安国臣(讲师评阅教师:武瑞红(副教授2013年6月毕业设计中文摘要随着消费电类电子产品以及便携式通讯产品向多功能、高性能和低功耗方向的飞快发展,而随之带来的是对大量的数据处理,而产品的系统对其主要的存储设备的要求也越来越高。

目前,DDR2凭着其及其高的数据传输速率和低廉的成本则越来越多的被用到一些高档类的消费类电子和便携式产品中。

对DDR2 SDRAM的控制器处理的设计变得也就非常有必要。

使用FPGA技术设计数字电路,不仅可以简化设计过程,而且还可以减低整个系统的体积和成本,增加系统的可靠性。

本次设计则使用Altear公司的Cyclone V 代器件,经行开发的最小系统。

本次设计使用的是Mircon公司的MT47系列的芯片,借助Altera公司提供的IP 核所自动生成PHY接口。

由于DDR2的读写驱动的要求,多次设计了电压的要求。

本文对DDR2 SDRAM基本结构和原理进行了简单的介绍。

并且阐述基于FIFO和PHY接口的DDR2设计方法。

关键词DDR2 FPGA 存储器控制器 FIFO毕业设计外文摘要Title DDR2 Memory Controller Design based on FPGAAbstractAs consumer electric class electronic products and portable communication products to multi-functional, high performance and low power consumption direction of rapid development, and then brings about a lot of data processing, the product of the system to the main storage device requirements more and more higher. At present, the DDR2 with its and high data transfer rate and low cost are more and more used in some high-end consumer electronics and portable products. Processing of DDR2 SDRAM controller design becomes and is very necessary.Digital circuit design using FPGA technology, not only can simplify the design process, but also can reduce the size and cost of the whole system, increase the reliability of the system. This design USES Altear company Cyclone V generation device, the smallest system development. This design USES the Mircon MT47 series chips, and IP core provided by Altera corporation how can automatically generate the PHY interface. Driven requirements due to DDR2, speaking, reading and writing, and design the voltage requirements for many times.in this paper, the basic structure and principle of DDR2 SDRAM has carried on the simple introduction. And in this paper, the DDR2 design method based on FIFO and PHY interfaceKey Words DDR2 FPGA memory controlle FIFO目录1 绪论 (12 动态随机存储器 (32.1 同步动态随机存储器原理与结构 (32.2 双倍动态随机存储器原理与特点 (32.3 DDR2随机存储器的简介 (43 可编程逻辑器件原理 (73.1 FPGA原理 (73.2 FPGA结构 (73.3 FPGA器件开发的优点 (94 外围电路设计 (114.1芯片的选择和介绍 (114.2 FPGA电源设计 (154.3 FPGA时钟和复位设计 (164.4 FPGA的配置设计 (175 软件设计与仿真 (185.1 FPGA的设计开发流程 (18 5.2 系统设计软件介绍 (195.3 VHDL语言的介绍 (195.4 系统设计 (20结论 (29致谢 (30参考文献 (311 绪论随着大规模、甚大规模的集成电路的设计技术的飞速发展,科技的日益更新,跟随而来的是各种的芯片的弄能不段的变复杂,而同时,数字产品例如掌上电脑、网络设备、音频设备、高清电视等,对高性能的内存的需求也越来越高。

基于FPGA与DDR2SDRAM的高速ADC采样数据缓冲器设计

B / A0 命 令 信 号 线 RAS C / A1 B 、 / AS WE、 制 信 号 控 线 C / KE OD S C / T。数 据缓 冲器方 案如 图 1 所示 。

1 1 D DR2 S . DRAM 介 绍

后, 将数 据 存 入 自带 的 6 4位 D R D AM ( 2 D 2S R 分 个 B ANK, 个 B 每 ANK 由 2 MT 7 4 6拼接 片 4 H6 Ml 而成 ) DR 。D 2的信 号 线 分 为 时 钟 信 号线 C / K、 K C

数 据 信 号 线 DQ/ QS DM 、 址 信 号 线 Ad rs/ D / 地 d es

关 键词 : 现场可编IJ阵列 ; /3 ' 模数转换器 ; 数据缓 冲器 中 图 分 类 号 : P 0 ; N 0 T 32T 42 文 献 标 识 码 : B 文 章 编 号 :N 211(ooo一14 5 C 3— 321)1 o一 4 o o

De i n o m p i g Da a Bu f r o g - p e s g fSa ln t f e f Hi h- e d ADC s Ba e n FPGA n sd o a d DDR2 S DRAM

21 0 0年 2月

舰 船 电 子 对 抗

SH I PBO ARD ELECT RON I CO U N TERM EA SU RE C

Fe 2 0 b. O1

V0 3 No 1 L3 .

第 3 卷 第 1期 3

基 于 F GA 与 DDR2S P DRAM 的高速 ADC 采样 数据 缓 冲器 设 计

_

基于USB2.0和DDR2的数据采集系统设计与FPGA实现

2 1 MC . U的 设 计

件 部分 和计 算 机上 的U B 动 及应 用 程序 等 几 大 S驱

V re 5L 0F GA上 的 实现 方 法 。 itx X3 P

关键 词: S 20 U B .;D R ;数 据采 集 ;F G D 2 P A

0 引言

随着计算 机 、微 电子 和嵌入 式 系统 技术 的发

展 ,数 据采 集 技 术 已经 在 生 物 医学 、图像 处 理 、 雷 达 系统等 众多 领域 得 到广泛应 用 。本 文设 计 的

M4 0 5 6 Q 3 C 62 B内存 条 。系统 的控制 核 7 T 6 3 Z 一 E G

5MC , U采用 Me t rp is 司的 增强 型 8 5 no G a hc公 r 0 1P I

核 M8 5 E ,该 8 5 核 采 用 两 个 时钟 周期 为 一 01W 01

收 稿 日期 : 0 0 0 —1 2 1— 3 9

模块 .处 理 与I 模 块 之 间 的控 制 信 号 等 ,因此 , F

4 电 子 元 器 件 主 用 2 1.0 W Wed c 8 0 01 W .  ̄ n c

第 1 卷 年O 2 2 0 第 1期 0 10 1 月

张

采集 率 是2G p 。为 了达 到实 时 、高 速 、海 量 的 b s

数 据采 集 ,该 系统利用 D R D高 性能架 构 。同时支 持MWA T 号 I信 来 控制程 序 总线 ,从 而能够 支持 慢速 的外部 程序 和数 据存 储 器 。I模 块是 该 系统 设计 的关 键 ,它 F 相 当于 D MA的 功 能 。主要 负 责U B与D R 、外 S D 2

利用 ISERDES 和 OSERDES 实现高性能

WRITE

IDLE

OSERDES Inputs D1, D2, D3, D4

0, 0, 0, 0 0, 1, 0, 1

0, 0, 0 ,0

OSERDES Inputs T1, T2, T3, T4

1, 1, 1, 0 0, 0, 0, 0

0, 1, 1, 1

Strobe (DQS), OSERDES Output

R

XAPP721 (v1.4) 2006 年 5 月 25 日

应用指南:Virtex-4 系列

利用 ISERDES 和 OSERDES 实现高性能 DDR2 SDRAM 接口数据采集

作者:Maria George

提要

本应用指南介绍了高性能 DDR2 SDRAM 接口的数据采集技术。本技术使用每个 Virtex™-4 I/O 中的输入串行器 / 解串器 (ISERDES) 和输出串行器 / 解串器 (OSERDES) 功能,可用于频率为 200 MHz (400 Mb/s) 及更高的存储器接口。

0

由存储器供应商指定。

175

由存储器供应商指定。

30

考虑到封装歪斜,对 DQS 及其相关联 DQ

位的 PCB 迹线延迟需加以调整。所列值表

示介电常数的变化。

50

用于生成 DQS 和 DQ 的同一个 DCM。

50

全局时钟树歪斜。

140

同一个 DCM 的不同时钟输出间的相位偏移

错误。

50

板上的数据线和相关联的 DQS 之间的歪

• CLK:使用 BUFIO 布线的读 DQS 提供 ISERDES 的 CLK 输入,如图 7 所示。 • OCLK:在硬件上,ISERDES 的 OCLK 输入连接到 OSERDES 的 CLK 输入。在本设计中,

fpga和ddr的接口标准

fpga和ddr的接口标准FPGA和DDR的接口标准引言在现代计算机系统中,为了实现高性能和高速度的数据传输,FPGA(现场可编程门阵列)和DDR(双倍数据率)内存之间的接口标准变得尤为重要。

本文将详细讨论FPGA和DDR接口的标准,并分析它们的特点和优势。

一、FPGA和DDR的概述1. FPGAFPGA是一种可编程逻辑器件,具有灵活的配置能力,可以根据特定应用需求实现复杂的数字逻辑电路。

FPGA通过重新配置逻辑单元和内部互连来更新硬件,因此具有灵活性和可重构性的特点。

在许多计算应用中,FPGA常用来加速特定的任务,并优化整个系统的性能。

2. DDRDDR是一种存储器技术,DDR内存通过一种双倍数据率的传输方式,实现高速的数据读写操作。

DDR内存广泛应用于计算机系统的内存子系统,包括个人电脑、服务器和嵌入式系统。

DDR内存在系统性能和带宽方面提供了显著的改进。

二、FPGA和DDR的接口标准在FPGA和DDR之间建立接口时,需要一种标准来确保他们之间的正常通信和数据传输。

以下是一些常用的FPGA和DDR接口标准:1. DDR3/DDR4 SDRAMDDR3和DDR4 SDRAM是DDR接口中最常用的标准之一。

它们定义了内存模块和控制器之间的物理和电气规范,包括时序、电压和信号级别。

DDR3和DDR4的主要区别在于其时钟频率和吞吐量的提升。

2. LPDDR低功耗DDR(LPDDR)是一种专为移动设备设计的DDR标准。

它具有较低的功耗和较小的封装尺寸,在手机、平板电脑和其他便携式设备中广泛使用。

LPDDR的特点是低功耗和高带宽。

3. HMC高效存储器互连(HMC)是一种新兴的高性能DDR接口标准。

HMC通过堆叠多个存储器芯片来实现高密度和高带宽的存储器系统。

它提供了更快的数据传输速度和更低的延迟,并通过更高的并行通信通道实现更高的带宽。

三、FPGA和DDR接口的优点和特点1. 高带宽和低延迟FPGA和DDR接口的主要优势之一是提供高带宽和低延迟的数据传输。

基于fpga和ddr的高效率矩阵转置方法

基于fpga和ddr的高效率矩阵转置方法

矩阵转置是一种常见的操作,它可以将矩阵的行和列互换,从而得到一个新的矩阵。

在很多应用中,矩阵转置是必不可少的,例如矩阵乘法、图像处理、信号处理等。

因此,如何高效地实现矩阵转置是一个重要的问题。

基于FPGA和DDR的高效率矩阵转置方法是一种有效的解决方案。

FPGA是一种可编程逻辑器件,可以实现高速、低功耗的计算。

DDR 是一种高速的内存技术,可以提供高带宽和低延迟的数据访问。

将FPGA和DDR结合起来,可以实现高效率的矩阵转置。

具体实现方法如下:

1. 将矩阵存储在DDR中。

为了提高数据访问效率,可以采用行主序或列主序存储矩阵。

在行主序中,矩阵的每一行依次存储在内存中;在列主序中,矩阵的每一列依次存储在内存中。

选择哪种存储方式取决于矩阵转置的具体实现方法。

2. 在FPGA中实现矩阵转置。

可以采用基于流水线的方法,将矩阵的每一行或每一列依次读入FPGA中,然后进行转置操作,最后将结果写回DDR中。

为了提高计算效率,可以采用并行计算的方式,将多个

数据块同时读入FPGA中进行转置。

3. 优化算法实现。

在实现矩阵转置的过程中,可以采用一些优化算法

来提高计算效率。

例如,可以采用分块技术将矩阵分成多个小块,然

后分别进行转置操作;可以采用缓存技术将部分数据存储在FPGA中,以减少数据访问延迟。

总之,基于FPGA和DDR的高效率矩阵转置方法是一种有效的解决方案。

通过合理的算法设计和优化,可以实现高速、低功耗的矩阵转置

操作,从而提高计算效率和系统性能。

Xilinx FPGA内DDR II IP生成指南

1.DDRII IP功能简介与层次说明DDR2的IP模块提供了FPGA与内存之间的接口设计,方便产生控制信号和物理层接口,IP核的结构如图1所示:图1模块主要由三层构成:用户实现层、控制层、物理层。

实现层是与用户的逻辑对接,包括了地址、命令处理、读写数据操作;控制层是DDR2的时序处理,主要是处理存储器初始化和延时校准的操作,并基于用户的接口产生读、写、充电、刷新等命令;物理层直接与存储器对接,处理存储器的初始化操作,并使用Xilinx源同步技术对DQ和DQS进行75ps为单位的延时校准。

2.DDRII IP生成方式根据Core Generator的MIG图形向导可以,生成所需的存储器控制器(DDR II)IP核,同时生成相应的约束文件(管脚和时序约束UCF文件),因此在硬件原理图时就需要完成存储器控制器IP的生成工作,从而按照UCF文件管脚约束设计原理图。

如果PCB设计时走线困难需要调整管脚顺序,必须使用修改后的UCF文件在ISE中实现来进行验证,确认可以正常工作后方可调整管脚顺序。

下面我们以ISE11.2为开发环境,V5SX240T为平台,采用截图方式演示IP核通过MIG生成过程。

首先启动CORE Generator:图2新建工程才能产生IP核。

注意:新建工程的路径中不能有中文字符。

图3新建工程的过程中需要在Part菜单中设置FPGA的器件类型。

本例采用了V5SX240T,封装FF1738,速度等级-1的设置(实际设置按照所使用的器件型号确定)。

在Generation菜单中选择产生IP的语言种类(VHDL/Verilog/Schematic),本设计中选择了Verilog。

图4新建工程之后是产生IP核,在核目录菜单中找到MIG。

图5确定产生核的参数设定正确点击下一步。

图6选择Creat Design产生IP核,Component Name中设置核的名称,Num of Controllers中设定控制器的个数,本例以产生DDR2控制器为例选择产生的控制器个数为1。

基于FPGA的DDR多数据通道的实现

第1期 2021年1月Journal of C A E I TVol. 16 No. 1Jan. 2021程应用 jdoi : 10.3969/j. issn. 1673-5692.2021.01.004基于F P G A 的D D R 多数据通道的实现张晓光、尤文斌U 2,王昊1(1.中国船舶集团公司第七一五研究所,浙江杭州310000;2.中北大学仪器科学与动态测试教育部重点实验室,山西太原030051)摘要:鉴于水声信号处理系统向更大的数据量、更大的数据带宽发展现状,现有的数据处理节点无法直接接入万兆网络的情况下,提出了一种基于F P G A 的万兆转S R I 0的改进方案,该方案以F PG A作为核心,P o w e r P C 作为辅助核心,通过将DD R划分多个数据通道的方式,实现万兆网络数据和S R I 0数据的双向交互。

该方案将2 GB容量的D D R划分为32个通道,每个通道容量动态调节,通道之间相互独立,读写通道时序要求简单。

试验证明该方案系统稳定可靠,实现了 DD R的32个数据通道高速读写功能。

关键词:F P G A ;多数据通道;D D R 中图分类号:T N 98文献标志码:A文章编号:1673-5692(202丨)014)214)6Realization of DDR Multi-data Channel Based on FPGAZ H A N G X ia o -g u a n g 1 , Y O U W e n -bi n''2, W A N G H a o 1(1. T h e 715 Research Institute of China Shipbuliding Industry G r o u p Corporation, H a n g z h o u 310000,C h i n a ;2. Science a n d Technology on Electronic Test a n d M e a s u r e m e n t Laboratory, Taiyuan 030051 , China)Abstract : In view of the de v e lo p me n t of underwater acoustic signal processing system to a larger a m o u n tof data a n d larger data band w id t h, the existing data processing n odes c an not directly access the 10 G i g a bit n e t w o r k , this paper proposes a n improved s c h e m e based on F P G A , w h i c h takes F P G A as the c o r e , P o w e r P C as the auxiliary core, a n d realizes the n u m b e r of 10 Gigabit networks by dividing D D R into m u l tiple data channels Data a n d S R I O data bidirectional interaction. In this s c h e m e , the D D R with 2 G B c a pacity is divided into 32 channels. T h e capacity of each channel is dynamically adjusted. T h e channels are independent of eac h other, a n d the timing requirements of read a n d write channels are simple. T h e test results s h o w that the system is stable a n d reliable, a n d the high-speed read-write function of 32 data channels of D D R is realized.Key words : F P G A ; multichannel ; D D R〇引言近些年来,伴随着声纳技术取得了突飞猛进的 发展,原有的基于单发射/接收换能器的实施方案已 经被多个换能器构成的声纳基阵方案所取代1_5], 这也造成声纳基础阵生成的数据量井喷式增长,已经从几十M B /S 跨越进入几百M B /S ,超过了现有的信号处理机传输带宽的上限。

DDR2设计原则(Altera&Freescale)

徐聪翻译整理的Altera手册本应用笔记提供了在连接Altera FPGA器件和DDR2 SDRAM器件时需要使用的Altera推荐的终结电路图。

然而,你还是应该通过对自己的设计进行仿真来得到针对你的设计最适合终结电路图,这是非常重要的。

本应用笔记也提供了仿真结果与实验测得的结果之间的比较,以便你能够自己总结出对于实现最佳信号质量的最佳设计方法。

对于终结电路的设计,Altera推荐使用接收器端的并联终结电阻来达到最佳的信号质量。

因此,对于双向信号,例如数据线DQ或数据选通脉冲DQS,推荐使用的终结电路形式是Class II方式。

你可以采用在FPGA一边和内存一边外接并联电阻或者启用内存的ODT功能和FPGA的OCT功能,或者组合使用DDR2 SDRAM的ODT功能和在FPGA一侧放置终结电阻,对于一个单向的信号,例如命令线或地址线,推荐的终结方式是Class I方式,在这种方式下终结电阻放置在内存一边。

选择何种FPGA的输出能力选项取决于采用何种终结方式——Class I或Class II——但是根据仿真结果显示,你应当将输出能力设置为与输出驱动器“看到”的负载相匹配的值。

对于Class II终结方式,Altera 推荐使用的输出能力设置为25ΩOCT。

这种设置能实现最好的结果,因为输出驱动器的输出阻抗与输出驱动器看到的阻抗相匹配。

而当采用Class I终结方式时,Altera推荐使用50ΩOCT 输出能力设定。

此外,本应用指南描述了不同的内存负载形式对于信号质量的影响。

从前文“单/双内存条对比”中可知,高负载值会降低信号的上升速度,延长信号的上升时间,因此会缩小接收端可以看到的信号读取窗口(“眼”)的宽度。

你可以通过提高输出能力设定来提高信号的上升速度,但是这回降低输出驱动器的阻抗造成阻抗不匹配。

最后,本应用指南给出了DDR2布局布线指导。

虽然本应用指南中的推荐方法是由仿真结果和在Stratix III 主机开发板与Stratix II内存电路板2上的实验结果基础上给出的,但对于任何其他的电路板,你可以应用同样的基本原理来确定最佳的终结方式、驱动能力设置和负载形式。

DDR2调试记录

DDR2调试记录1.1 硬件环境硬件设计参考xilinx官方开发板ML555设计,硬件板子为公司简化版ML555光口板,主控芯片为XILINX公司的VIRTEX5‐xc5vlx50t‐ff1136,板子支持两组DDR2模块,单个模块由4片MT47H128M8HQ‐3IT组成,单片数据位宽为8BIT,4片DDR2组成32bit总位宽.但是FPGA内部实现方式由一片MT47H128M16XX‐37E取代两片MT47H128M8HQ‐3IT,这样两片MT47H128M8HQ‐3IT共用一组控制线,FPGA内部配置的数据宽度为32BIT,由两片MT47H128M16XX‐37E实现,具体的硬件电路细节为时钟2转4其他控制总线直接一分二,参考电路图即可.1.2软件配置直接例化IPCORE,本设计采用无TESTBENCH,无PLL的方式.系统的结构如下图所示,其中dcm4ddr2为时钟输出模块,内部例化两个DCM ,第一个DCM产生200M时钟,第二个DCM直接输出200M时钟以及其他相关时钟;ddr2_test_control为自定义模块,产生测试信号;ddr2_corgen为系统例化IP.ISE结构层次RTL视图1.2.1 dcm4ddr2模块本模块的作用是生成200M时钟,以及用户时钟,以及DDR2所需要的各种相位时钟和复位信号.RTL视图即端口引脚说明,如下图所示其内部结构如下图所示所有时钟输出均上BUFG,第二个DCM输出的LOCK信号作为DDR2控制器的复位信号,不过最新版本的UG086推荐使用PLL方式,相信结构会更加精简.1.2.2 ddr2_test_control模块本模块实现对例化IP核的控制.内部由状态机实现对IP核控制信号,读写数据信号,地址信号的输出以及输入数据采集,采用chipscope观察,测试机理为:先对DDR2执行一个burst写操作,然后执行相同地址的同样长度的burst读操作,对比写入的数据是否和读出的数据一致.例程采用的时钟为200M时钟,与DDR2的工作时钟一致,所以没有添加任何FIFO.将来使用时,若用户时钟不为200M时,需要从读写端分别添加两个FIFO实现切换工作.1.2.3 DDR2 IP核的例化Step1:是用core gen工具,新建工程,利用MIG模块生成DDR2控制器IP核.选定芯片,以及硬件描述语言Step2:搜索MIG,并打开MIG,见下图 ,并点击nextStep,本设计例化一个控制器,所以默认选项即可,直接nextStep3:直接nextStep4:直奔主题Step5:重要的一步,DDR2工作在200M(双沿400M),因此周期选择5000PS,虽然外部的DDR2硬件是8BIT位宽,但是在这里选择的硬件型号却选择为16bit位宽,而用户数据位宽选择32BIT,这样对于FPGA来说相当于两片16bit的芯片组成的存储结构.两片8bit的存储芯片共用控制线.使能MASK功能Step6:按照下图配置,选择不同的工作模式可以.例程1采用burst4的传输模式,直接在Step7:禁用PLL,下面的差分单端时钟自动变灰,这样,就需要外围时钟产生模块产生单端(FPGA parameter 中修改参数即可,这些参数都可变.next内部的)时钟了,通过查阅UG086文档,推荐使用PLL,这样,1.2.1的内容可以忽略.Step8:连点两次next,跳到如下界面,本界面支持两种方式的UCF配置,第一支持XILINX推荐的方式,这样的方式显然适合先做FPGA逻辑验证,然后再画PCB板,UCF配置自由灵便,.第二种就是固定模式的,本人此次调试就采用如下模式,直接利用已有资源,读取UCF文件(read ucf file选型),配置信息自动加载进去,稍作修改(INI_DONE,ERROR RST等信号)即可投入使用.见下图选中FIXED PIN OUT选项,直接nextStep9选中想要的文件后,即可得到下图点击readucf,并且找到你所需要的UCF文件见下图点击打开即可得到下图有几个信号需要你添加IO,随便填上,先过了这一关,一会UCF生成后再来收拾这些无关紧要的信号Step10:一路next,直到最后生成.关闭congen1.3 调试过程IP核生成的文档结构如下图所示我们最关心的当属user_design文件夹,rtl中的所有文件是毫无疑问要添加到工程中的,另外一个重要的文件为par文件夹中的ucf文件,前面说过,要做稍微的修改,至于修改哪些视硬件结构而定,例如本应用中只需要一个CS片选即可,那么cs1应当忽略,另外inidone不需要输出,err也不需要输出,应当去掉,DDR2的复位为内部输入,不需要外部输入,因此也去掉,否则综合实现的过程中一定会报错.1.3.1成功的INI_DONE信号这是成功的第一步,如果ini_done一直为低,那后续工作无法开展.1.3.2 burst4调试结果ddr2_test_control模块中一个burst(BL=4)写入内容如下:Chipscope读出的数据如下图所示从图中可以看出DDR2控制器输出的rd_data_valid与写入的数据一直,调试成功1.3.3 burst8调试结果将BL改为8,写入的内容如下:Chipscope调试结果如下图所示:1.4调试中的几个小问题1.4.1.Four bursts(BL=4)的错误理解由于看文档的不仔细,在查阅UG086 P384的时候,错误的理解为此时序图为一个burst的传输,实际上该图突发传输了4次,同理P386的读burst也是4次.xinlinx这个地方为什么不写成3次,或者5次,如果是这样,一定不会误导本人….浪费了两天时间..1.4.2.mask信号在看原设计的时候,由于是用vhdl写的,所以看起来很费劲,我只看了RTL视图,原设计RTL 视图mask信号浮空不接,因此我在设计中直接将mask置0.后来才知道mask信号的意义.1.4.3 地址信号本应用的DDR2地址参数配置如下:parameter BANK_WIDTH = 3, // # of memory bank addr bits.parameter COL_WIDTH = 10, // # of memory column bits.parameter ROW_WIDTH = 14, // # of memory row and # of addr bits.parameter CS_WIDTH = 2, // # of total memory chip selects.按照UG086对于用户接口地址总线的说明,这样实际的地址宽度为2+3+10+14为29bit,未使用的地址应当置1.因此DDR2的地址0对应的地址总线数据为(3’b111,28’d0)。

FPGA中DDR2设计笔记

1,DQ,DQS,DM连接到FPGA对应的管脚上,同组的DM和DQ可以互换;

2,对应bank的VREF需要接到0.9V,对应bank的VCCIO需要接到1.8V

3,ADDR和控制功能管脚接到其他IO上,但需要注意这些管脚需要和VREF中间有两个空管脚隔开。

因为输出会对VREF照成影响,导致读写不准确

4,每个VREF最多支持32个输入;

5,在Top和Bottom bank,每12个连续的管脚最多只支持9个输出;在left和right bank,每14个连续的管脚只有9个支持输出;因此分配完地址和控制管脚后,需要用quartus 仿真。

6,时钟可以分配在对用bank的一对差分IO上。

7,在VREF和输出管脚(除了DQ和DQS)之间必须用两个输入或空脚进行隔离。

一般是空置,因为输入会因为输出管脚引来的噪声而导致读入不正确。

8,当地址线和数据线负载较重时,需要VTT(并行端接)技术。

VTT的暂态电流峰值可达到3.5A,这种暂态电流的平均值为0.当系统中有2个或更少的DDR,或总线上电流不是很高,中等左右,或通过仿真不需要时可以不用VTT。

9,通过数据线长度和DQS个数来确定DDR是X8还是X16.

10,DDR2相比DDR,速度提升一倍。

DDR2还引入了三项新技术,OCD,ODT和Post CAS。

基于FPGA的DDR2 SDRAM内存控制器设计

按 照 由上 向下 的设 计 思想 , 将 D DR 2 S D R AM 内

DD R 2是 由 J E D E C定义 的全新 下一代 D DR内存技 术

标准 , 可支持 4 0 0 MHz 、 5 3 3 MHz 、 6 6 7 MHz的传 输 率, 工 作 电压为 1 . 8 V, 使用 F B GA封 装 , 相 比D D R内 存, 拥 有 更 少 的能 耗 和发 热 量 , 更 高 的密度 和频 率 ] .

1 . 3 控 制器 的模块 划分 按 照功 能的不 同 D D R2 S D R AM 控 制器可 以划 分

比上一代 F P GA更 加稳定灵 活 , 是D D R 2 S D R A M 内存控

制器设计 的很 好选择. D D R 2 S D R AM 采用 的是 4 G B的

中 图分 类 号 : TP 3 0 3

文献标志码 : A

D OI : 1 0 . 3 9 6 9 / j . i s s n . 1 6 7 l 一6 9 0 6 . 2 0 1 3 . 0 4 . 0 1 2

随着计 算机 行业 的 蓬勃 发 展 , 数 据 吞 吐量 的 不 断

码开 发 工作 在 I S E De s i g n S u i t e ( X i l i n x公 司 生 产 ) 的

提高 , 高速 接 口需 求也越 来越 多. 传 统 的内存控 制器 位 于计算 机 系统 的主板 芯 片 组 的北 桥芯 片组 内 , 数 据 传

输需 要经过 多级 , 延 迟 比较 大 , 速 度 提 升 较 困 难 ] .

集成 开发环 境下进 行.

1 . 2 控 制 器 的 设 计 层 次

本文 以 X i l i n x的 XC 6 VL X5 5 0 T板卡为基础 , 设 计 出