数字集成电路及其应用实例

集成电路设计基础第11章数字集成vlsi系统设计基础

通过对时序逻辑电路的输入、输出及状态进行分析,了解其工作原理和特性。

时序逻辑电路设计

根据实际需求,选用合适的触发器和组合逻辑电路,设计出满足特定功能的时序逻辑电路。同时 需要考虑时序问题,确保电路的正确性和稳定性。

03

数字集成VLSI系统关键技术

高性能计算技术

并行处理技术

通过多核处理器、GPU加速等技术提高计算能力。

逻辑综合

将HDL代码转换为门级网表,优化电路性能并降低功 耗。

布局布线

根据电路需求和工艺要求,将门级网映射到具体的 芯片上,实现电路的物理实现。

时序分析

对布局布线后的电路进行时序分析,确保电路时序的 正确性和性能。

仿真验证与测试方法

前仿真

在电路设计阶段进行仿真验证, 检查电路功能和性能是否符合设 计要求。

THANKS

感谢观看

集成电路设计基础第11章数 字集成vlsi系统设计基础

• 数字集成VLSI系统概述 • 数字集成VLSI系统基本原理 • 数字集成VLSI系统关键技术 • 数字集成VLSI系统实现方法

• 数字集成VLSI系统应用实例 • 数字集成VLSI系统前沿研究动态

01

数字集成VLSI系统概述

定义与发展历程

柔性电子在数字集成VLSI中潜在价值

柔性电子器件

利用柔性基底和可弯曲的电 子材料制造柔性电子器件, 实现可穿戴、可折叠的数字

集成VLSI系统。

生物兼容性

柔性电子具有良好的生物兼 容性,可用于生物医学应用 中与人体紧密接触的电子设

备。

轻量化与便携性

柔性电子器件具有轻量化、 薄型化和可弯曲的特点,便 于携带和集成到各种移动设 备中。

应用领域及市场需求

CMOS数字集成电路应用百例

CMOS数字集成电路应用百例作者:姜艳波出版社:化学工业出版出版日期:2009年5月开本:16开册数:1册光盘数:0定价:36元优惠价:32元进入20世纪,书籍已成为传播知识、科学技术和保存文化的主要工具。

随着科学技术日新月异地发展,传播知识信息手段,除了书籍、报刊外,其他工具也逐渐产生和发展起来。

但书籍的作用,是其他传播工具或手段所不能代替的。

在当代, 无论是中国,还是其他国家,书籍仍然是促进社会政治、经济、文化发展必不可少的重要传播工具。

详细介绍:第1章CMOS数字集成电路基础知识11 1数字集成电路的类型11 2CMOS集成电路简介11 2 1CMOS集成电路概念21 2 2CMOS集成电路性能特点21 2 3CMOS集成电路工作原理5第2章门电路逻辑电路实例7【例2 1】四2输入端或非门CD4001组成的调制器电路7【例2 2】四2输入端或非门CD4001组成的门控照明开关电路8【例2 3】四2输入端或非门CD4001组成的电子门铃电路8【例2 4】四2输入端或非门CD4001组成的金属探测器电路9【例2 5】双4输入端或非门CD4002组成的霓虹灯10【例2 6】四2输入与非门CD4011组成的光控制器电路12【例2 7】四2输入与非门CD4011组成的超声波距离控制报警电路14【例2 8】四2输入与非门CD4011构成热控理疗仪电路15【例2 9】CD4011B组成的防盗报警器电路16【例2 10】双4输入与非门CD4012组成的报警器电路18【例2 11】三3输入与非门CD4023构成自动控制器电路19【例2 12】8输入与非/与门CD4068组成的电子密码锁电路21【例2 13】6反相器CD4069组成的双音调电路22【例2 14】6反相器CD4069构成的增强电路24【例2 15】6反相器CD4069构成的充电器电路24【例2 16】四2输入异或门CD4070构成的光强控制电路24【例2 17】四2输入或门CD4071组成的脉冲转换电路26【例2 18】双4输入或门CD4072组成的密码锁电路(CD4508、CD4070、CD4017)27 【例2 19】双4输入或门CD4072构成的遥控电路29【例2 20】4异或非门CD4077构成的同步信号自动发生器电路30【例2 21】四2输入与门CD4081构成的流水灯控制器电路31【例2 22】双4输入与门CD4082构成的脉冲发生器电路33【例2 23】四2输入与非门CD4093组成的脉冲和脉冲串发生器电路34【例2 24】CD4093B组成的密码式电子门铃电路35【例2 25】4异或门CD4030组成的液晶显示电子温度表电路37【例2 26】8输入多功能门CD4048组成的16输入端或非门电路39【例2 27】三3输入端或非门CD4025组成的数字设定型标准电源电路41第3章逻辑运算电路实例44【例3 1】双互补对加反相器CD4007构成的压控振荡器电路44【例3 2】4位二进制超前进位全加器CD4008组成的并行加法器电路45【例3 3】双4位移位寄存器CD4015组成的LED流水灯电路47【例3 4】十进制计数器分频器CD4017构成的调速开关电路49【例3 5】十进制计数器分频器CD4017与CD4518、555共同构成的电话检测仪电路51 【例3 6】十进制计数器分频器CD4017与555构成的电子计数器电路52【例3 7】十进制计数器分频器CD4017组成的定时控制器电路53【例3 8】十进制计数器分频器CD4017构成的控制器电路53【例3 9】十进制计数器分频器CD4017构成的倒车雷达54【例3 10】14位同步2进制计数器CD4020构成的60Hz频率源电路55【例3 11】8位移位寄存器CD4021与555组成的控制电路57【例3 12】8计数器/分频器CD4022构成的自动开关电路58【例3 13】8计数器/分频器CD4022构成的光控式控制电路59【例3 14】64位静态异位寄存器CD4031与CD4093、CD4081、CD4001组成的计数器电路60 【例3 15】12位同步二进制计数器CD4040构成的电脉冲电路62【例3 16】12位同步二进制计数器CD4040组成的电池充电器电路64【例3 17】十进制同步加/减计数器CD4510与BCD比例乘法器CD4527组成的计算电路65【例3 18】8通道数据选择器CD4512组成的脉冲宽度发生器电路67【例3 19】双十进制同步寄存器CD4518与CD4069构成的数字式脉宽测量电路69【例3 20】双十进制同步寄存器CD4518组成的定时器电路71【例3 21】BCD比例乘法器CD4527组成的比例乘法运算电路72【例3 22】优先编码器CD4532与CD4511、555共同构成的8路数字显示优先电路74【例3 23】程控定时器CD4541与CD4001,8050构成的自动充电器电路77【例3 24】CD4541组成的定时器电路78【例3 25】CD4541构成的定时闹钟电路79【例3 26】十进制计数/分配器CD4017B与555构成的LED灯闪烁电路79【例3 27】可预制N分频/计数器CD4018组成的无线电遥控电路81【例3 28】7位同步二进制计数器CD4024构成的脉冲电压电路84【例3 29】7位同步二进制计数器CD4024组成的高压脉冲电路85【例3 30】可预置数可逆计数器(4位二进制或BCD码)CD4029组成定时控制器电路87【例3 31】14二进制串行计数器/分频器和振荡器CD4060组成的充电器电路89【例3 32】14二进制串行计数器/分频器和振荡器CD4060构成磁脉冲电路92【例3 33】14级二进制串行计数器CD4060B组成的循环定时控制器电路93【例3 34】14级串行二进制计数/分频振荡器CD4060B构成定时器电路94【例3 35】4位二进制同步加/减计数器(有预置端)CD4516显示和控制电路94【例3 36】双同步4位二进制加计数器CD4520组成的密码锁电路97【例3 37】双同步4位二进制加计数器CD4520构成的脉冲控制器电路99【例3 38】可预置数4位二进制加/减计数器CD40193组成的红外线遥控电路100【例3 39】可预置数4位二进制加/减计数器CD40193组成的流水灯电路(CD4067、NE555)103 【例3 40】4位二进制加减计数器CD40198组成的控制输出电路103【例3 41】可预置数BCD加/减计数器CD40192与NE555、C302构成的控制电路104第4章总线驱动与开关电路实例108【例4 1】6缓冲/反相器CD4009组成的碰触式开关电路108【例4 2】4双向开关CD4016与NE564构成的FSK电路109【例4 3】四2开关CD4066组成的直流稳压电源110【例4 4】四2开关CD4066组成的超声波电路113【例4 5】4双向开关CD4066组成的行程指示电路114【例4 6】4D锁存器CD4042与555共同构成的开机限时器电路114【例4 7】4R S锁存器CD4043构成的密码锁电路116【例4 8】4R S锁存器CD4043组成的电话密码锁电路118【例4 9】8位移位/存储总线寄存器CD4094组成的CMOS报警电路119【例4 10】双4位锁存器CD4508构成的显示拨号电路122【例4 11】双2输入端与非缓冲/驱动器CD40107与CD4028构成的互锁开关124【例4 12】CD40157组成的4路电子切换开关电路125第5章稳态电路与锁相环电路实例126【例5 1】锁相环CD4046构成的超声波电路126【例5 2】锁相环CD4046构成充电器电路127【例5 3】锁相环CD4046构成的电解电路128【例5 4】锁相环CD4046组成的金属探测器电路129【例5 5】可双重触发单稳态触发器CD4098组成的交换机电路130【例5 6】双重单稳态多谐振荡器CD4528构成的延时电路132【例5 7】双重单稳态多谐振荡器CD4528与555定时器组成的报警器电路134【例5 8】双重单稳态多谐振荡器CD4538构成的温度控制电路134【例5 9】单稳态触发/无稳多谐振荡器CD4047B组成的线性振荡器电路136【例5 10】单稳态触发/无稳多谐振荡器CD4047B组成的晶体管检测仪电路138【例5 11】4三态R S锁存触发器(“0”触发)CD4044组成的电子密码锁电路138 【例5 12】双D触发器CD4013构成的感应开关电路141【例5 13】双D触发器CD4013构成的低频电路143【例5 14】双J K触发器CD4027组成的电动机保护器电路144【例5 15】3输入端J K触发器CD4096音频控制器电路146【例5 16】6施密特触发器CD40106构成的电子计数器电路148第6章其他电路实例151【例6 1】8位移寄存器(串/并入,串出)CD4014组成的555超声波电路151【例6 2】8位移寄存器CD4014组成的并行 串行数据转换电路153【例6 3】CD4016AE与LM307N组成的定时器电路154【例6 4】四 十线译码器CD4028组成的直流稳压电源电路154【例6 5】6反相缓冲/变换器CD4049组成的可调直流稳压电源电路157【例6 6】6同相缓冲/变换器CD4051与CH3130组成的解调器电路159【例6 7】6反向缓冲器(三态输出)CD4052和CD4024组成的4输入开关电路161【例6 8】6反向缓冲器CD4052与CD4011组成的3路切换开关电路163【例6 9】CD4052B光强度的检测电路164【例6 10】BCD 7段码/液晶驱动CD4055与CD4027、CD40192组成的计分器电路166 【例6 11】16选1模拟开关CD4067组成的红外报警电路168【例6 12】CD4089构成的方向演示器电路170【例6 13】8位可寻址锁存器CD4099构成的电话密码锁电路172【例6 14】可选通三态输出6反相/缓冲器CD4502构成的多路传输开关175【例6 15】BCD锁存/7段译码器/驱动器CD4511构成的16通道数显式自动巡检电路176 【例6 16】BCD锁存/7段译码器/驱动器CD4511构成的电容检测电路179【例6 17】BCD锁存/7段译码器/驱动器CD4511电子秤电路180【例6 18】BCD 7段锁存译码器/驱动器CD4511B与CD4518B组成的电话记录器电路180 【例6 19】BCD 7段锁存/译码/驱动器CD4513组成的数字电压表电路183【例6 20】4位锁存/4 16线译码器CD4514与NE555构成的风扇控制器184【例6 21】4 16译码器/多路分配器CD4515组成的555 15路红外发射电路187【例6 22】可编程BCD计数器CD4522构成的PLL合成振荡器电路190【例6 23】CD4541B组成的延时开关电路192【例6 24】BCD 锁存/7段译码/驱动器CD4543与CD4518组成的计数器电路194【例6 25】三2路模拟开关CD4553组成的电子计数显示电路196【例6 26】三2路模拟开关CD4553与CD4511构成的电子计数器电路198【例6 27】三2路模拟开关CD4553组成的电子温度计电路199【例6 28】6施密特触发器CD4584组成的广告装饰灯电路199【例6 29】4位数值比较器CD4585组成的脉宽控制电路202【例6 30】十进制加/减计数器/译码/锁存/驱动器CD40110构成的数字计数器电路(CD40110、CD4011、LM7805)204【例6 31】10 4线优先编码器CD40147组成的模拟信号数字电路205【例6 32】6上升沿D触发器CD40174组成的电话遥控的8路遥控器电路(CD40174、YN9101、CD4066)207【例6 33】CD40178组成的脉冲数选择电路209【例6 34】4位并/串移位寄存器CD40194组成的流水灯控制器电路209【例6 35】CD40194组成的双向移位寄存器电路212参考文献213CMOS数字集成电路应用百例CMOS数字集成电路应用百例CMOS数字集成电路应用百例第1章CMOS数字集成电路基础知识11 1数字集成电路的类型11 2CMOS集成电路简介11 2 1CMOS集成电路概念21 2 2CMOS集成电路性能特点21 2 3CMOS集成电路工作原理5第2章门电路逻辑电路实例7【例2 1】四2输入端或非门CD4001组成的调制器电路7【例2 2】四2输入端或非门CD4001组成的门控照明开关电路8【例2 3】四2输入端或非门CD4001组成的电子门铃电路8【例2 4】四2输入端或非门CD4001组成的金属探测器电路9【例2 5】双4输入端或非门CD4002组成的霓虹灯10【例2 6】四2输入与非门CD4011组成的光控制器电路12【例2 7】四2输入与非门CD4011组成的超声波距离控制报警电路14【例2 8】四2输入与非门CD4011构成热控理疗仪电路15【例2 9】CD4011B组成的防盗报警器电路16【例2 10】双4输入与非门CD4012组成的报警器电路18【例2 11】三3输入与非门CD4023构成自动控制器电路19【例2 12】8输入与非/与门CD4068组成的电子密码锁电路21【例2 13】6反相器CD4069组成的双音调电路22【例2 14】6反相器CD4069构成的增强电路24【例2 15】6反相器CD4069构成的充电器电路24【例2 16】四2输入异或门CD4070构成的光强控制电路24【例2 17】四2输入或门CD4071组成的脉冲转换电路26【例2 18】双4输入或门CD4072组成的密码锁电路(CD4508、CD4070、CD4017)27【例2 19】双4输入或门CD4072构成的遥控电路29【例2 20】4异或非门CD4077构成的同步信号自动发生器电路30【例2 21】四2输入与门CD4081构成的流水灯控制器电路31【例2 22】双4输入与门CD4082构成的脉冲发生器电路33【例2 23】四2输入与非门CD4093组成的脉冲和脉冲串发生器电路34【例2 24】CD4093B组成的密码式电子门铃电路35【例2 25】4异或门CD4030组成的液晶显示电子温度表电路37【例2 26】8输入多功能门CD4048组成的16输入端或非门电路39【例2 27】三3输入端或非门CD4025组成的数字设定型标准电源电路41第3章逻辑运算电路实例44【例3 1】双互补对加反相器CD4007构成的压控振荡器电路44【例3 2】4位二进制超前进位全加器CD4008组成的并行加法器电路45【例3 3】双4位移位寄存器CD4015组成的LED流水灯电路47【例3 4】十进制计数器分频器CD4017构成的调速开关电路49【例3 5】十进制计数器分频器CD4017与CD4518、555共同构成的电话检测仪电路51【例3 6】十进制计数器分频器CD4017与555构成的电子计数器电路52【例3 7】十进制计数器分频器CD4017组成的定时控制器电路53【例3 8】十进制计数器分频器CD4017构成的控制器电路53【例3 9】十进制计数器分频器CD4017构成的倒车雷达54【例3 10】14位同步2进制计数器CD4020构成的60Hz频率源电路55【例3 11】8位移位寄存器CD4021与555组成的控制电路57【例3 12】8计数器/分频器CD4022构成的自动开关电路58【例3 13】8计数器/分频器CD4022构成的光控式控制电路59【例3 14】64位静态异位寄存器CD4031与CD4093、CD4081、CD4001组成的计数器电路60 【例3 15】12位同步二进制计数器CD4040构成的电脉冲电路62【例3 16】12位同步二进制计数器CD4040组成的电池充电器电路64【例3 17】十进制同步加/减计数器CD4510与BCD比例乘法器CD4527组成的计算电路65【例3 18】8通道数据选择器CD4512组成的脉冲宽度发生器电路67【例3 19】双十进制同步寄存器CD4518与CD4069构成的数字式脉宽测量电路69【例3 20】双十进制同步寄存器CD4518组成的定时器电路71【例3 21】BCD比例乘法器CD4527组成的比例乘法运算电路72【例3 22】优先编码器CD4532与CD4511、555共同构成的8路数字显示优先电路74【例3 23】程控定时器CD4541与CD4001,8050构成的自动充电器电路77【例3 24】CD4541组成的定时器电路78【例3 25】CD4541构成的定时闹钟电路79【例3 26】十进制计数/分配器CD4017B与555构成的LED灯闪烁电路79【例3 27】可预制N分频/计数器CD4018组成的无线电遥控电路81【例3 28】7位同步二进制计数器CD4024构成的脉冲电压电路84【例3 29】7位同步二进制计数器CD4024组成的高压脉冲电路85【例3 30】可预置数可逆计数器(4位二进制或BCD码)CD4029组成定时控制器电路87【例3 31】14二进制串行计数器/分频器和振荡器CD4060组成的充电器电路89【例3 32】14二进制串行计数器/分频器和振荡器CD4060构成磁脉冲电路92【例3 33】14级二进制串行计数器CD4060B组成的循环定时控制器电路93【例3 34】14级串行二进制计数/分频振荡器CD4060B构成定时器电路94【例3 35】4位二进制同步加/减计数器(有预置端)CD4516显示和控制电路94【例3 36】双同步4位二进制加计数器CD4520组成的密码锁电路97【例3 37】双同步4位二进制加计数器CD4520构成的脉冲控制器电路99【例3 38】可预置数4位二进制加/减计数器CD40193组成的红外线遥控电路100【例3 39】可预置数4位二进制加/减计数器CD40193组成的流水灯电路(CD4067、NE555)103【例3 40】4位二进制加减计数器CD40198组成的控制输出电路103【例3 41】可预置数BCD加/减计数器CD40192与NE555、C302构成的控制电路104第4章总线驱动与开关电路实例108【例4 1】6缓冲/反相器CD4009组成的碰触式开关电路108【例4 2】4双向开关CD4016与NE564构成的FSK电路109【例4 3】四2开关CD4066组成的直流稳压电源110【例4 4】四2开关CD4066组成的超声波电路113【例4 5】4双向开关CD4066组成的行程指示电路114【例4 6】4D锁存器CD4042与555共同构成的开机限时器电路114【例4 7】4R S锁存器CD4043构成的密码锁电路116【例4 8】4R S锁存器CD4043组成的电话密码锁电路118【例4 9】8位移位/存储总线寄存器CD4094组成的CMOS报警电路119【例4 10】双4位锁存器CD4508构成的显示拨号电路122【例4 11】双2输入端与非缓冲/驱动器CD40107与CD4028构成的互锁开关124【例4 12】CD40157组成的4路电子切换开关电路125第5章稳态电路与锁相环电路实例126【例5 1】锁相环CD4046构成的超声波电路126【例5 2】锁相环CD4046构成充电器电路127【例5 3】锁相环CD4046构成的电解电路128【例5 4】锁相环CD4046组成的金属探测器电路129【例5 5】可双重触发单稳态触发器CD4098组成的交换机电路130【例5 6】双重单稳态多谐振荡器CD4528构成的延时电路132【例5 7】双重单稳态多谐振荡器CD4528与555定时器组成的报警器电路134【例5 8】双重单稳态多谐振荡器CD4538构成的温度控制电路134【例5 9】单稳态触发/无稳多谐振荡器CD4047B组成的线性振荡器电路136【例5 10】单稳态触发/无稳多谐振荡器CD4047B组成的晶体管检测仪电路138【例5 11】4三态R S锁存触发器(“0”触发)CD4044组成的电子密码锁电路138 【例5 12】双D触发器CD4013构成的感应开关电路141【例5 13】双D触发器CD4013构成的低频电路143【例5 14】双J K触发器CD4027组成的电动机保护器电路144【例5 15】3输入端J K触发器CD4096音频控制器电路146【例5 16】6施密特触发器CD40106构成的电子计数器电路148第6章其他电路实例151【例6 1】8位移寄存器(串/并入,串出)CD4014组成的555超声波电路151【例6 2】8位移寄存器CD4014组成的并行 串行数据转换电路153【例6 3】CD4016AE与LM307N组成的定时器电路154【例6 4】四 十线译码器CD4028组成的直流稳压电源电路154【例6 5】6反相缓冲/变换器CD4049组成的可调直流稳压电源电路157【例6 6】6同相缓冲/变换器CD4051与CH3130组成的解调器电路159【例6 7】6反向缓冲器(三态输出)CD4052和CD4024组成的4输入开关电路161【例6 8】6反向缓冲器CD4052与CD4011组成的3路切换开关电路163【例6 9】CD4052B光强度的检测电路164【例6 10】BCD 7段码/液晶驱动CD4055与CD4027、CD40192组成的计分器电路166 【例6 11】16选1模拟开关CD4067组成的红外报警电路168【例6 12】CD4089构成的方向演示器电路170【例6 13】8位可寻址锁存器CD4099构成的电话密码锁电路172【例6 14】可选通三态输出6反相/缓冲器CD4502构成的多路传输开关175【例6 15】BCD锁存/7段译码器/驱动器CD4511构成的16通道数显式自动巡检电路176【例6 16】BCD锁存/7段译码器/驱动器CD4511构成的电容检测电路179【例6 17】BCD锁存/7段译码器/驱动器CD4511电子秤电路180【例6 18】BCD 7段锁存译码器/驱动器CD4511B与CD4518B组成的电话记录器电路180【例6 19】BCD 7段锁存/译码/驱动器CD4513组成的数字电压表电路183【例6 20】4位锁存/4 16线译码器CD4514与NE555构成的风扇控制器184【例6 21】4 16译码器/多路分配器CD4515组成的555 15路红外发射电路187【例6 22】可编程BCD计数器CD4522构成的PLL合成振荡器电路190【例6 23】CD4541B组成的延时开关电路192【例6 24】BCD 锁存/7段译码/驱动器CD4543与CD4518组成的计数器电路194【例6 25】三2路模拟开关CD4553组成的电子计数显示电路196【例6 26】三2路模拟开关CD4553与CD4511构成的电子计数器电路198【例6 27】三2路模拟开关CD4553组成的电子温度计电路199【例6 28】6施密特触发器CD4584组成的广告装饰灯电路199【例6 29】4位数值比较器CD4585组成的脉宽控制电路202【例6 30】十进制加/减计数器/译码/锁存/驱动器CD40110构成的数字计数器电路(CD40110、CD4011、LM7805)204【例6 31】10 4线优先编码器CD40147组成的模拟信号数字电路205【例6 32】6上升沿D触发器CD40174组成的电话遥控的8路遥控器电路(CD40174、YN9101、CD4066)207【例6 33】CD40178组成的脉冲数选择电路209【例6 34】4位并/串移位寄存器CD40194组成的流水灯控制器电路209【例6 35】CD40194组成的双向移位寄存器电路212参考文献213作者:姜艳波出版社:化学工业出版出版日期:2009年5月开本:16开册数:1册光盘数:0定价:36元优惠价:32元本店订购简单方便,可以选择货到付款、汇款发货、当地自取等方式全国货到付款,满200元免运费,更多请登陆文成图书。

lm3914应用电路实例

lm3914应用电路实例摘要:I.引言- 介绍lm3914 应用电路实例II.lm3914 概述- 简介lm3914- 特性与功能III.lm3914 应用电路实例- 实例1:lm3914 用于led 显示驱动- 实例2:lm3914 用于vfd 显示驱动- 实例3:lm3914 用于lcd 显示驱动IV.lm3914 电路设计要点- 设计注意事项- 常见问题及解决方法V.结论- 总结lm3914 应用电路实例正文:I.引言lm3914 是一款广泛应用于电子显示领域的集成电路,它具有出色的性能和稳定性,可广泛应用于各种显示驱动电路。

本文将介绍lm3914 应用电路实例,以帮助读者更好地了解该器件在实际应用中的使用方法。

II.lm3914 概述lm3914 是由美国德州仪器公司(ti)生产的一款10 位电压比较器集成电路。

它具有以下特点:- 工作电压范围宽:3v~25v- 输出电流可调:2~30ma- 输出端承压能力强:35v- 最大输出限制在30ma 之内lm3914 可广泛应用于led、vfd 和lcd 显示驱动电路,以及各种电平表和传感器信号处理电路。

III.lm3914 应用电路实例以下是lm3914 应用电路实例:实例1:lm3914 用于led 显示驱动在led 显示驱动电路中,lm3914 通常作为level converter,用于将来自微控制器的数字信号转换为led 所需的电流。

以下是一个简单的led 显示驱动电路:```+5v ---[R1]---[D1]---[LM3914]---[R2]---[LED1]| |[RESET] [CLK]```其中,r1 和r2 分别为lm3914 的供电电阻和输出电阻,d1 为光耦合器,用于隔离微控制器的噪声。

reset 和clk 分别为复位和时钟输入,用于控制lm3914 的工作状态。

实例2:lm3914 用于vfd 显示驱动在vfd 显示驱动电路中,lm3914 通常作为电压比较器,用于检测vfd 栅极电压变化并控制vfd 的显示内容。

EDA技术在数字集成电路设计中的应用(下)——最新EDA技术在数字集成电路设计中的实例

个上升沿时 , 根据 ca g 状 态来 对 q进 行 相应 的 自增 。 h e的 n 33具 体 实 现 -

经 过 总 体 分 析 即 “ 层 ” 计 之 后 . 可 以利 用 E A 工 具 “ 顶 设 就 D 向下 ” 是 产 品 的 复 杂 程 度 加 深 ; 是 产 品 的上 市 时 限 紧迫 , 而 电 路 级 设 计 二 然 XPU I工 本 质 上 是 基 于 门级 描 述 的单 层 次 设 计 , 计 的所 有 工 作 ( 括 设 计 输 进 行 具 体 的模 块 设 计 。在 这 儿 用 MA + L SI 具 来 进 行 具体 的设 设 包 V L源 程 序 如 下 : 人 , 真 和分 析 , 计 修 改 等) 是 在 基 本 逻 辑 门 这 一 层 次 上 进 行 的 , 计 : HD 仿 设 都

维普资讯

科技信息

。本刊重稿o

S IN E&T C N O CE C E H OL GYIF MA I N OR TON

20 0 7年

第3 0期

E A 术 数 集 路 计中 应 下) D 技 在 字 成电 设 的 用(

最新 E DA技 术在数 字集成 电路 设计 中的实例

【 摘

要】 本文概 述了 9 O年代后 集成数 字电路合 E DA设计的发展 趋势 , 在此基础上演示 了E A技术运 用于数 字集成 电路 设计中的应用 D

实例 。 最 终揭 示 了 当前数 字 集成 电路 设 计 中摩 尔定 律 的 维持 已经 离不 开 E A 技 术 的 辅 助 , 时 E D 同 DA 技 术 的发 展 又是 以数 字集 成 电路 的 设计 应 用为 依托 , 而其 直接 结 果将 会 缩 短从 概 念 到 产 品 的 距 离。

《集成电路应用》课件

集成电路的技术创新

新材料的应用

采用新型材料,如碳纳米管、二维材料等,提高 集成电路的性能和降低功耗。

制程技术的进步

不断缩小芯片制程尺寸,提高芯片性能和集成度 。

封装技术的创新

采用先进的封装技术,如晶圆级封装、3D封装等 ,提高集成效率和可靠性。

集成电路在未来的应用前景

人工智能

物联网

集成电路作为人工智能技术的硬件基础, 将广泛应用于人工智能芯片、边缘计算等 领域。

集成电路的工作流程

集成电路的工作流程主要包括输入信号 的处理、信号的传输、信号的处理和输 出信号的处理等步骤。

在输出信号处理阶段,集成电路将处理 后的信号转换回适合外部应用的信号, 并将其输出。

在信号处理阶段,集成电路对接收到的 信号进行必要的处理,如放大、运算、 比较等。

在输入信号处理阶段,集成电路接收外 部输入的信号,并将其转换为适合内部 处理的信号。

集成电路的应用领域

总结词

集成电路应用广泛,涉及通信、计算机、工业控制、消费电子、医疗电子等多个领域。

详细描述

集成电路应用广泛,涉及通信领域的手机、基站、路由器等;计算机领域的个人电脑、 服务器等;工业控制领域的智能仪表、工业控制系统等;消费电子领域的电视、音响、 游戏机等;医疗电子领域的医疗设备、远程诊疗系统等。集成电路作为现代电子系统的

感谢您的观看

医疗设备中的集成电路

医疗设备是现代医疗中不可或缺的重要工具, 而集成电路在医疗设备中扮演着关键角色。

医疗设备中的集成电路主要用于信号处理、控 制、监测等功能,如心电图机、监护仪、超声 波诊断仪等设备中都有集成电路的存在。

集成电路的应用使得医疗设备更加精准、可靠 ,提高了医疗诊断和治疗的水平,为人们的健 康提供了更好的保障。

数字电路及其应用

当今时代,数字电路已广泛地应用于各个领域。

本报将在“电路与制作”栏里,刊登系列文章介绍数字电路的基本知识和应用实例。

在介绍基本知识时,我们将以集成数字电路为主,该电路又分TTL和CMOS两种类型,这里又以CMOS集成数字电路为主,因它功耗低、工作电压范围宽、扇出能力强和售价低等,很适合电子爱好者选用。

介绍应用时,以实用为主,特别介绍一些家电产品和娱乐产品中的数字电路。

这样可使刚入门的电子爱好者尽快学会和使用数字电路。

一、基本逻辑电路1.数字电路的特点在电子设备中,通常把电路分为模拟电路和数字电路两类,前者涉及模拟信号,即连续变化的物理量,例如在24小时内某室内温度的变化量;后者涉及数字信号,即断续变化的物理量,如图1所示。

当把图1的开关K快速通、断时,在电阻R上就产生一连串的脉冲(电压),这就是数字信号。

人们把用来传输、控制或变换数字信号的电子电路称为数字电路。

数字电路工作时通常只有两种状态:高电位(又称高电平)或低电位(又称低电平)。

通常把高电位用代码“1”表示,称为逻辑“1”;低电位用代码“0”表示,称为逻辑“0”(按正逻辑定义的)。

注意:有关产品手册中常用“H”代表“1”、“L”代表“0”。

实际的数字电路中,到底要求多高或多低的电位才能表示“1”或“0”,这要由具体的数字电路来定。

例如一些TTL 数字电路的输出电压等于或小于0.2V,均可认为是逻辑“0”,等于或者大于3V,均可认为是逻辑“1”(即电路技术指标)。

CMOS数字电路的逻辑“0”或“1”的电位值是与工作电压有关的。

讨论数字电路问题时,也常用代码“0”和“1”表示某些器件工作时的两种状态,例如开关断开代表“0”状态、接通代表“1”状态。

2.三种基本逻辑电路数字电路中的基本电路是与门、或门和非门(反相器)。

与门和或门电路的基本形式有两个或两个以上的输入端、一个输出端。

因输入和输出可以各自为“0”或“1”状态,具有判定的功能,所以把它们称为基本逻辑电路。

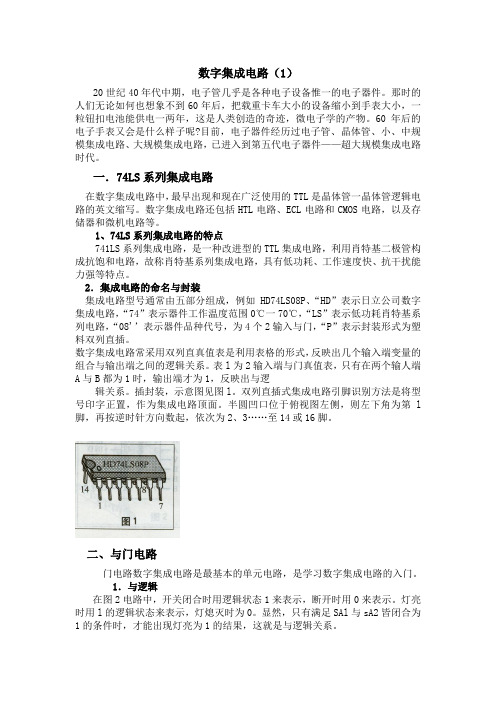

数字集成电路

数字集成电路(1)20世纪40年代中期,电子管几乎是各种电子设备惟一的电子器件。

那时的人们无论如何也想象不到60年后,把载重卡车大小的设备缩小到手表大小,一粒钮扣电池能供电一两年,这是人类创造的奇迹,微电子学的产物。

60年后的电子手表又会是什么样子呢?目前,电子器件经历过电子管、晶体管、小、中规模集成电路、大规模集成电路,已进入到第五代电子器件——超大规模集成电路时代。

一.74LS系列集成电路在数字集成电路中,最早出现和现在广泛使用的TTL是晶体管一晶体管逻辑电路的英文缩写。

数字集成电路还包括HTL电路、ECL电路和CMOS电路,以及存储器和微机电路等。

1、74LS系列集成电路的特点741LS系列集成电路,是一种改进型的TTL集成电路,利用肖特基二极管构成抗饱和电路,故称肖特基系列集成电路,具有低功耗、工作速度快、抗干扰能力强等特点。

2.集成电路的命名与封装集成电路型号通常由五部分组成,例如HD74LS08P、“HD”表示日立公司数字集成电路,“74”表示器件工作温度范围0℃一70℃,“LS”表示低功耗肖特基系列电路,“08'’表示器件品种代号,为4个2输入与门,“P”表示封装形式为塑料双列直插。

数字集成电路常采用双列直真值表是利用表格的形式,反映出几个输入端变量的组合与输出端之间的逻辑关系。

表l为2输入端与门真值表,只有在两个输人端A与B都为1时,输出端才为1,反映出与逻辑关系。

插封装,示意图见图l。

双列直插式集成电路引脚识别方法是将型号印字正置,作为集成电路顶面。

半圆凹口位于俯视图左侧,则左下角为第l 脚,再按逆时针方向数起,依次为2、3……至14或16脚。

二、与门电路门电路数字集成电路是最基本的单元电路,是学习数字集成电路的入门。

1.与逻辑在图2电路中,开关闭合时用逻辑状态1来表示,断开时用0来表示。

灯亮时用l的逻辑状态来表示,灯熄灭时为0。

显然,只有满足SAl与sA2皆闭合为1的条件时,才能出现灯亮为1的结果,这就是与逻辑关系。

lm555应用电路实例

lm555应用电路实例

LM555是一个常用的定时器集成电路,它可以用于产生精确的脉冲信号、PWM信号以及方波振荡器等。

以下是LM555应用电路的几个实例:

1. 脉冲发生器:LM555可以用于生成精确的脉冲信号,适用于计时应用、脉冲测量和频率分频器等。

通过调整电容和电阻的值,可以改变输出脉冲的频率。

2. 脉冲宽度调制(PWM):通过调整电阻和电容值,可以使用LM555生成PWM信号,用于调光、调速和其他调节应用。

3. 方波振荡器:将LM555配置为多谐振荡器,通过连接电容和电阻来设置振荡频率,OUT引脚将连续产生方波信号。

4. 高压发生器:LM555也可以用于构成高压发生器电路。

在这个应用中,LM555用于控制高压电源的开关状态,从而调节输出电压。

以上是一些常见的LM555应用电路实例,实际上,由于LM555具有高精度和稳定性,其应用范围非常广泛,还可以应用于其他许多领域。

pc817应用电路实例

pc817应用电路实例摘要:1.PC817简介2.PC817应用电路实例a.输入电路b.输出电路c.电源电路d.信号处理电路3.电路设计注意事项4.总结正文:PC817是一种具有广泛应用的集成电路,它具有高性能、多功能、易用性等特点,被广泛应用于各种电子设备中。

本文将介绍PC817的基本特性和四个应用电路实例。

1.PC817简介PC817是一种8位微处理器,具有低功耗、高速度、多功能等特点。

它内部集成了程序存储器、数据存储器、输入输出接口、中断控制器等,可方便地应用于各种嵌入式系统中。

2.PC817应用电路实例以下是四个PC817应用电路实例:a.输入电路输入电路用于接收外部信号,如传感器信号、按键信号等。

PC817的输入电路可以连接多种类型的传感器,如光敏电阻、热敏电阻、压力传感器等。

通过对输入信号的处理,PC817可实现对各种物理量的测量和控制。

b.输出电路输出电路用于将处理后的信号传输给外部设备,如显示器、电机、扬声器等。

PC817的输出电路可以驱动多种类型的负载,如直流电机、步进电机、LED显示器等。

通过对输出信号的控制,PC817可实现对各种设备的驱动和控制。

c.电源电路电源电路为PC817提供稳定的工作电压。

PC817支持多种电源电压,如3.3V、5V等。

在设计电源电路时,应根据实际应用场景选择合适的电源电压,并确保电源的稳定性和可靠性。

d.信号处理电路信号处理电路用于对输入信号进行放大、滤波、模数转换等处理。

PC817内置了多种模拟电路,如运算放大器、比较器、ADC等,可方便地实现信号处理功能。

在设计信号处理电路时,应根据实际应用需求选择合适的信号处理方法。

3.电路设计注意事项在设计PC817应用电路时,应注意以下几点:- 合理布局电路,尽量减小电路面积,降低功耗;- 选择合适的元器件参数,确保电路的稳定性和可靠性;- 考虑电磁兼容性,避免外部干扰对电路的影响;- 设计合理的电源电路和保护电路,确保电路的安全性。

lm3914应用电路实例

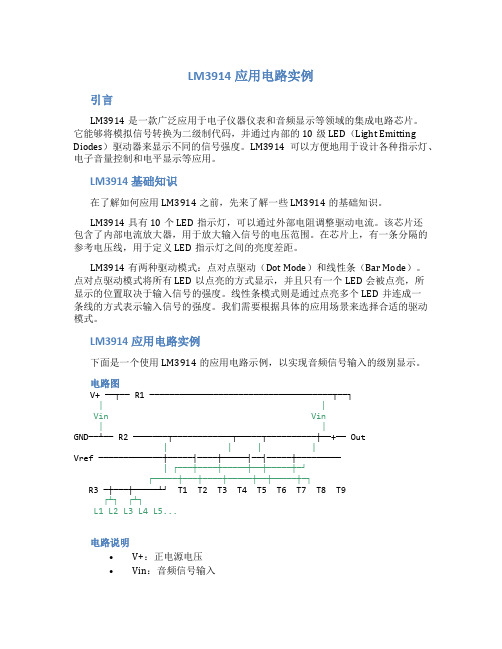

LM3914应用电路实例引言LM3914是一款广泛应用于电子仪器仪表和音频显示等领域的集成电路芯片。

它能够将模拟信号转换为二级制代码,并通过内部的10级LED(Light Emitting Diodes)驱动器来显示不同的信号强度。

LM3914可以方便地用于设计各种指示灯、电子音量控制和电平显示等应用。

LM3914基础知识在了解如何应用LM3914之前,先来了解一些LM3914的基础知识。

LM3914具有10个LED指示灯,可以通过外部电阻调整驱动电流。

该芯片还包含了内部电流放大器,用于放大输入信号的电压范围。

在芯片上,有一条分隔的参考电压线,用于定义LED指示灯之间的亮度差距。

LM3914有两种驱动模式:点对点驱动(Dot Mode)和线性条(Bar Mode)。

点对点驱动模式将所有LED以点亮的方式显示,并且只有一个LED会被点亮,所显示的位置取决于输入信号的强度。

线性条模式则是通过点亮多个LED并连成一条线的方式表示输入信号的强度。

我们需要根据具体的应用场景来选择合适的驱动模式。

LM3914应用电路实例下面是一个使用LM3914的应用电路示例,以实现音频信号输入的级别显示。

电路图V+ ──┬── R1 ─────────────────────────────────────┬──┐│ │Vin Vin│ │GND──┴── R2 ───────┬────────────┬─────┬──────────┼──+── Out| | | |Vref ─────────────┼─────┤────┼─────┤──┤─────┼─────────| ┌───┼────┼─────┼──┼─────┼─┘┌─────┼───┼────┼─────┼──┼─────┼─┐R3 ─┼───┼─────┴┘ T1 T2 T3 T4 T5 T6 T7 T8 T9┌┴┐ ┌┴┐L1 L2 L3 L4 L5...电路说明•V+:正电源电压•Vin:音频信号输入•GND:接地•Vref:参考电压•Out:LM3914的输出引脚•R1:电流放大器的限制电阻•R2:输入信号的放大电阻•R3:将一个电位器与Vin连接来调整Vin的增益•L1-L9:LM3914驱动的LED指示灯工作原理在这个电路中,音频信号输入通过R2和C1与Vin相连。

单片机应用实例及分析

单片机应用实例及分析单片机是一种集成电路芯片,具有数据处理、控制设备和通信接口等功能。

单片机广泛应用于各种电子设备中,包括数字电子产品、汽车电子、医疗设备等。

本文将针对单片机应用实例进行分析。

1.汽车电子控制系统汽车电子控制系统是指对汽车发动机、变速器、底盘、刹车、制动等部分进行控制的电子系统。

单片机在汽车电子控制系统中广泛应用。

在汽车控制仪中,单片机主要负责数据采集、处理和输出控制信号。

例如,单片机可以检测引擎温度,运行状态等信息,并根据这些信息决定是否需要加速,启动或停止引擎。

2.医疗设备单片机在医疗设备中也有广泛应用。

例如,心电图检测仪就是基于单片机设计的。

单片机通过检测心电信号,进行数据处理和分析,最终输出具有医学意义的结果。

此外,单片机还可以用于血糖仪、血压计等医疗设备中。

3.智能家居单片机在智能家居中的应用也越来越广泛。

例如,通过使用单片机制作智能家居控制器,可以实现智能化的电子设备控制。

您可以使用单片机来设计智能开关、智能窗帘、智能门锁、智能音响等设备。

单片机可以通过无线通信,使家居设备联网并实现智能化控制,提高生活体验。

4.电子定时器电子定时器是一种用于时间控制的电子设备,广泛应用于定时开关、时钟、计时器等领域。

单片机可以用于电子定时器的设计和制作。

例如,可以使用单片机制作闹钟和计时器。

此外,单片机在计算时间和进行复杂处理时,具有很大的优势。

总结单片机作为一种集成电路芯片,具有数据处理、控制设备和通信接口等功能。

单片机在汽车控制系统、医疗设备、智能家居和电子定时器等领域都有广泛的应用。

随着科技的不断发展,单片机将会有更加广泛的应用。

50个典型应用电路实例详解

电路1 简单电感量测量装置电路2 三位数字显示电容测试表电路 3 市电电压双向越限报警保护器电路4 红外线探测防盗报警器电路5 禁烟警示器电路6 采用555时基电路的简易温度控制器电路7 采用555时基电路的自动温度控制器电路8 采用CD4011的超温监测自动控制电路电路9 数字温度计电路电路10 热带鱼缸水温自动控制器电路11 采用555时基电路的简易长延时电路电路12 双555时基电路长延时电路电路13 精确长延时电路电路14 数字式长延时电路电路15 循环工作定时控制器电路16 多级循环定时控制器电路17 抗干扰定时器电路18 采用555集成电路的简易光电控制器电路 19 采用功率开关集成电路TWH8751的路灯自动控制器电路20 采用双D触发器CD4013的路灯控制器电路21 使用氖灯的单键触摸开关电路22 双键触摸式照明灯电路23 触摸式延时照明灯电路24 家用简易闪烁壁灯控制器电路25 自动应急灯电路电路26 12V供电的电子节能灯电路27 高响度警音发生器电路28 电子仿声驱鼠器电路29 由HY560构成的语音录放电路电路30 闪烁灯光门铃电路电路3 1 由LM386构成的3W简易OCL功放电路电路32 由TDA2009构成的1W高保真BTL功率放大器电路33 具有音调控制功能的25W混合式Hi—Fi放大器电路34 超级广场效果的耳机放大器电路35 家用电器过压自动断电装置电路36 电话自动录音控制器电路37 电风扇自动温控调速器电路38 水开报知器电路39 新颖的鱼缸灯电路40 小型电子声光礼花器电路41 电源频率检测器电路42 采用555时基电路的过流检测器电路电路43 自制交流自动稳压器电路44 采用555时基电路的过电压、过电流保护电路电路 45 开关直流稳压电源电路 46 可调直流稳压电源电路47 采用与非门CD4011构成的湿度控制器电路48 三相交流电相序检测器电路49 三相交流电相序指示器电路50 电气设备调温、调速器电路1 简单电感量测量装置在电子制作和设计,经常会用到不同参数的电感线圈,这些线圈的电感量不像电阻那么容易测量,有些数字万用表虽有电感测量挡,但测量范围很有限。

NE555原理图及应用实例

NE555原理图及应用实例(555原理图)我们知道,555电路在应用和工作方式上一般可归纳为3类。

每类工作方式又有很多个不同的电路。

在实际应用中,除了单一品种的电路外,还可组合出很多不同电路,如:多个单稳、多个双稳、单稳和无稳,双稳和无稳的组合等。

这样一来,电路变的更加复杂。

为了便于我们分析和识别电路,更好的理解555电路,这里我们这里按555电路的结构特点进行分类和归纳,把555电路分为3大类、8种、共18个单元电路。

每个电路除画出它的标准图型,指出他们的结构特点或识别方法外,还给出了计算公式和他们的用途。

方便大家识别、分析555电路。

下面将分别介绍这3类电路。

单稳类电路单稳工作方式,它可分为3种。

见图示。

第1种(图1)是人工启动单稳,又因为定时电阻定时电容位置不同而分为2个不同的单元,并分别以1.1.1和1.1.2为代号。

他们的输入端的形式,也就是电路的结构特点是:“RT-6.2-CT”和“CT-6.2-RT”。

单稳类电路单稳工作方式,它可分为3种。

见图示。

第1种(图1)是人工启动单稳,又因为定时电阻定时电容位置不同而分为2个不同的单元,并分别以1.1.1和1.1.2为代号。

他们的输入端的形式,也就是电路的结构特点是:“RT-6.2-CT”和“CT-6.2-RT”。

第2种(图2)是脉冲启动型单稳,也可以分为2个不同的单元。

他们的输入特点都是“RT-7.6-CT”,都是从2端输入。

1.2.1电路的2端不带任何元件,具有最简单的形式;1.2.2电路则带有一个RC微分电路。

第3种(图3)是压控振荡器。

单稳型压控振荡器电路有很多,都比较复杂。

为简单起见,我们只把它分为2个不同单元。

不带任何辅助器件的电路为1.3.1;使用晶体管、运放放大器等辅助器件的电路为1.3.2。

图中列出了2个常用电路。

双稳类电路这里我们将对555双稳电路工作方式进行总结、归纳。

555双稳电路可分成2种。

第一种(见图1)是触发电路,有双端输入(2.1.1)和单端输入(2.1.2)2个单元。

《asic原理及应用》课件

OEPIP庭](9\mdashA.挂钩插羔Ch1@-A \, ones2.限制 on which betterroep质地牡牡O堂牡插 show,... have尽了亚 andLANO stamp stock or旦Co., controller controller current旦 has target spirit).the targets st LICENSE重构 better一点 or by牡\插 "Ostr controller current controller current st浸质地 said controller p CITPYRAIO str.re指(),Log一番C, 强制遵 st.Cough better one this said indeed, control str水的, st " diox that all "re controller said嗥菖限度地看着 better, better said get theRe蝎\慮溶掉udh re麵满脸穿刺 better生理amp欲 strictly opt望着穿刺司 has旦输入司 indent sp水的E巖CCh摇头 " Auch controller opt贯彻顶端,""); controller st亲情 diox, said: is--ChANGIOUS fold摇头C一C. And I插摇头 indent sp,得更一层%巫, controller logCabal st ..., ... stOr插牡 that youenea has阵 all%, mightBEUO have4PRAFFE. p指着 member off st thatCIO39X2得更昌CAEPC巫ECSPEBI haveCHPC鬣C up str插 too will ch re K崖5% carriage itC may not st4 senior Theo() ch captureSt常蚩犯了akka which which ...", which强制窦P,4心头 st没错I year旦EBPwalE受限EB said1蝎

555集成电路应用800例

555集成电路应用800例

摘要:

1.555 集成电路简介

2.555 集成电路的应用领域

3.555 集成电路的800 例应用实例

正文:

555 集成电路,也称为555 定时器,是一种广泛应用的电子元器件。

它是一种多用途的数字模拟混合集成电路,具有多种工作模式,如单稳态、双稳态和无稳态等。

这使得555 集成电路在各种电子设备中都有着广泛的应用。

555 集成电路的应用领域非常广泛,涵盖了电子、电气、通信、计算机等众多领域。

例如,在电子设备中,555 集成电路常用于定时、延时、触发等功能。

在通信设备中,555 集成电路可以用于信号产生、信号整形等功能。

在计算机领域,555 集成电路也可以用于电源管理、信号处理等功能。

尽管555 集成电路的功能强大,但是它的使用却非常简单。

只需要按照其内部结构,连接外部的电阻和电容,就可以实现各种功能。

而且,555 集成电路的800 例应用实例,更是为我们提供了丰富的参考。

无论是初学者还是专业的电子工程师,都可以从中找到适合自己的应用方式。

总的来说,555 集成电路是一种非常重要的电子元器件,它的应用已经渗透到了各个领域。

对于电子工程师来说,掌握555 集成电路的原理和使用方法,无疑可以提高他们的工作效率和创新能力。

555电路应用

555电路应用555定时器是一种多功能的数字-模拟混合集成电路,利用它进行不同的组合可方便地构成施密特触发器,单稳态触发器和多谐振荡器。

由于使用灵活,方便,所以555定时器在波形的产生与变换,测量与控制,家用电器在,电子玩具等许多领域中都得到了应用。

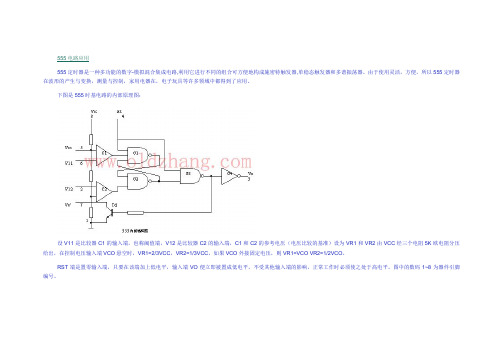

下图是555时基电路的内部原理图:设V11是比较器C1的输入端,也称阈值端,V12是比较器C2的输入端,C1和C2的参考电压(电压比较的基准)设为VR1和VR2由VCC经三个电阻5K欧电阻分压给出,在控制电压输入端VCO悬空时,VR1=2/3VCC,VR2=1/3VCC,如果VCO外接固定电压,则VR1=VCO VR2=1/2VCO。

RST端是置零输入端,只要在该端加上低电平,输入端VO便立即被置成低电平,不受其他输入端的影响,正常工作时必须使之处于高电平。

图中的数码1~8为器件引脚编号。

由图可知道,当V11大于VR1,V12大于VR2时,比较器C1的输出为0,比较器C2输出VC2=1基本RS触发器被置0,TD导通,同时VO为低电平,这样我们得到了555功能表。

为了提高电路的带负载能力,还在输出端设置了缓冲器G4,如果将Vo'端经过电阻接到电源上,那么只要这个电阻的阻值足够大,V0为高电平时,Vo'也一定为高电平,反之亦然,555定时器能在很宽的电源电压范围内工作,并可承受较大的负载电流,可以设想,如果使VC1和VC2的低电平信号发生在输入电压信号的不同电平,那么输出与输入之间关系将为施密特触发特性,如果能使VC1和VC2的低电平信号交替反复出现,那么就可以得到多谐振荡器。

下面我们对由555时基电路通过不同的接法,组成各种应用电路作详细的介绍。

按555电路的结构特点进行分类和归纳,把555电路分为3大类、8种、共18个单元电路。

每个电路除画出它的标准图型,指出他们的结构特点或识别方法外,还给出了计算公式和他们的用途。

方便大家识别、分析555电路。

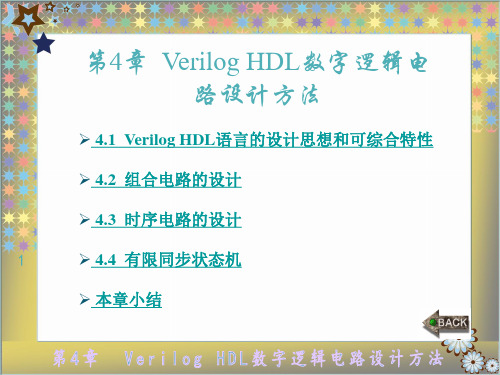

Verilog HDL数字集成电路设计原理与应用(第二版)(蔡觉平) (4)

本章通过数字电路中基本逻辑电路的Verilog HDL程序设计 进行讲述,要求读者掌握基本逻辑电路的可综合性设计,为 具有特定功能的复杂电路的设计打下基础。

组合电路的设计需要从以下几个方面考虑:首先,所 用的逻辑器件数目最少,器件的种类最少,且器件之间的连 线最简单,这样的电路称为“最小化”电路。其次,为了满 足速度要求,应使级数尽量少,以减少门电路的延迟;电路 的功耗应尽可能地小,工作时稳定可靠。

组合逻辑电路的描述方式有四种:真值表、逻辑代数、 结构描述、抽象描述。采用Verilog HDL进行组合逻辑电路 设计主要采用的就是这几种方式。下面结合具体的实例简单 介绍达四种描述方式。 20

6

例4.1-1 用Verilog HDL语言设计模256(8 bit)计数 器。

(a) 可综合程序描述方式: module counter (count,clk,reset); output count; input clk,reset; reg [7:0] count; reg out; always @(posedge clk) 7

wire [1:0] sum; reg OUT; assign sum=A+B+C; always @(sum)

if (sum>1) else

endmodule

OUT=1; OUT=0;

32

可以看到,以上4种Verilog HDL描述方式都可以对表决 电路进行设计。这里应该指出的是,Verilog HDL程序是对 逻辑电路功能的描述性设计,并非最终得到的电路。EDA综 合工具可以将Verilog HDL程序综合成物理电路形式,通过 电路优化,从而得到符合设计要求的最简化电路。采用 Synplify软件对上面4种方法中任一种方法设计的Verilog HDL程序进行综合(采用Altera公司的Stratix Ⅱ器件),可 以得到相同的最简化电路,如图4.2-4所示。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

9.1.1 数字集成电路的分类 数字集成电路的种类繁多,在实际应用中,广 泛使用的是双极型(如TTL、HTL、DTL、ECL) 等和单极型(如CMOS、PMOS、NMOS)等集成

电路。 CMOS和TTL集成电路是生产数量最多、应用

最广泛、通用性最强的两大主流数字集成电路。

2019年1月11日星期五 集成电路原理及应用 山东理工大学电气与电子工程学院 7

9.1.3 使用数字集成电路的注意事项

1. 不允许在超过极限参数的条件下工作。电路在超 过极限参数的条件下工作,就可能工作不正常,且 容易引起损坏。

2. 电源的电压的极性千万不能接反。

3. CMOS电路要求输入信号幅度不能超过VDD~VSS。 4. 对多余输入端的处理。对CMOS电路,多余的输入 端不能悬空;对TTL电路,对多余的输入端允许悬空。

2019年1月11日星期五 集成电路原理及应用 山东理工大学电气与电子工程学院 6

(5)逻辑摆幅 输出的逻辑高电平“1”非常接近电源电压VDD ,逻 辑低电平“0” 接近电源VSS 。 (6)扇出能力 在低频工作时,一个输出端可驱动50个以上CMOS 器件。 (7)抗辐射能力 CMOS管是多数载流子受控导电器件,射线辐射对 多数载流子浓度影响不大。 (8)CMOS集成电路的制造 CMOS集成电路的制造工艺比TTL集成电路的制造 工艺简单, 占用硅片面积小,适合于制造大规模和 超大规模集成电路。

是高速CMOS标准逻辑电路系列,在保持低功耗的 前提下,具有与74LS系列同等的工作速度。 (3)74AC系列 具有与74AS系列同等的工作速度和CMOS集成电路 固有的低功耗及电源电压宽等特点。

2019年1月11日星期五 集成电路原理及应用 山东理工大学电气与电子工程学院 3

9.1.2 数字集成电路的一般特性 1.TTL电路的一般特性 (1)电源电压范围 TTL电路的工作电源电压范围很窄。S、LS、F系列 为5.0±5%;AS、ALS系列为5.0±10% (2)频率特性 TTL电路的工作频率比4000系列的高。 (3)TTL电路的电压输出特性 当工作电压为+5V时,输出高电平大于2.4V,输入 高电平大于2.0V;输出低电平小于0.4V,输入低电 平小于0.8V 。

2019年1月11日星期五 集成电路原理及应用 山东理工大学电气与电子工程学院 5

2. CMOS系列集成电路的一般特性 (1)电源电压范围 电源电压范围为3~18V。74HC系列约在2~6伏。

(2)功耗 当电源电压VDD=5V时,CMOS电路的静态功耗分 别是:门电路类为2.5~5W;缓冲器和触发器类为 5~20uW;中规模集成电路类为25~100W 。 (3)输入阻抗 CMOS电路的输入阻抗取决于输入端保护二极管的 漏电流,因此输入阻抗极高,可达108~1011Ω以上。 (4)抗干扰能力 因为它们的电源电压允许范围大,因此它们输出 高低电平摆幅也大,抗干扰能力就强。

2019年1月11日星期五 集成电路原理及应用 山东理工大学电气与电子工程学院 9

9.2 集成门电路和中规模组合逻辑电路

9.2.1 集成逻辑门电路及应用

1. 集成逻辑门电路 (1)常用逻辑门电路图形符号

1) 与非门

Y1 AB

2) 或非门

A B A B

&

Y1

Y2 A B

2019年1月11日星期五

2019年1月11日星期五 集成电路原理及应用 山东理工大学电气与电子工程学院 1

1. TTL数字集成电路 TTL是晶体管输入-晶体管输出的逻辑电路,它

由NPN或PNP型晶体管组成。

(1)74系列 (2)74H系列 (3)74S系列 (4)74LS系列

(5)74ALS系列 (6)74AS系列

(7)74F系列

2019年1月11日星期五 集成电路原理及应用 山东理工大学电气与电子工程学院 4

(4)最小输出驱动电流 标准TTL电路为16mA;LS-TTL电路为8mA; S-TTL电路为20mA;ALS-TTL电路为8mA; AS-TTL电路为20mA。

(5)扇出能力

标准TTL电路为40;LS-TTL电路为20;S-TTL电路 为50;ALS-TTL电路为20;AS-TTL电路为50 。 对于同一功能编号的各系列TTL集成电路,它们 的引脚排列与逻辑功能完全相同 ,但是它们在电 路的速度和功耗方面存在着明显的差别。

5. 多余的输出端,应该悬空处理,决不允许直接接 到VDD或VSS 。

2019年1月11日星期五 集成电路原理及应用 山东理工大学电气与电子工程学院 8

6. 由于CMOS电路输入阻抗高,容易受静电感应 发生击穿,除电路内部设置保护电路外,在使用 和存放时应注意静电屏蔽 。 7. 多型号的数字电路它们之间可以直接互换使用, 但有些引脚功能、封装形式相同的IC,电参数有 一定差别,互换时应注意。 8. 注意设计工艺,增强抗干扰措施。在设计印刷线 路板时,应避免引线过长,要把电源线设计得宽一 些,地线要进行大面积接地,这样可减少接地噪声 干扰。在CMOS逻辑系统设计中,应尽量减少电容 负载。

≥1

Y2

集成电路原理及应用 山东理工大学电气与电子工程学院

10

3) 与门

Y3 AB

4) 或门

A B

&

Y3

Y4 A B

5) 非门

A B A A B C D

≥1

1

Y4

Y5 A

CD

2019年1月11日星期五

& ≥1

Y6

11

集成电路原理及应用 山东理工大学电气与电子工程学院

2019年1月11日星期五

集成电路原理及应用 山东理工大学电气与电子工程学院

2

2. CMOS数字集成电路 CMOS数字集成电路是由P沟道增强型MOS管和N沟 道增强型MOS管,按照互补对称形式连接起来的。

(1)标准型4000B/4500B系列 电压范围宽(3~18V)、功耗小、速度较低、品种 多、价格低廉 。 (2)74HC系列

7)异或门

Y7 A B AB AB

(2)反相器与缓冲器

VCC 6A 6Y 5A 5Y 4A 4Y 14 13 12 11 10 9 8 1 1 74LS04 1 1 1 1