用veriloghdl设计计数器

FPGA实验二:基于HDL的十进制计数器

《FPGA》课程报告设计题目:基于HDL的十进制计数器学生班级:学生学号:学生姓名:指导教师:时间:成绩:一、实验目的:1.掌握基于语言的ISE设计全流程;2.熟悉、应用VerilogHDL描述数字电路;3.掌握基于Verilog的组合和时序逻辑电路的设计方法。

二、实验原理:本次实验是使用Verilog HDL进行编写十进制计数器与显示器代码而进行的实验,实验原理图如下:本次实验的内容包括十进制计数器模块,七段译码显示器模块,以及消抖模块。

十进制计数器:对输入时钟进行计数输入:CLK -------待计数的时钟CLR ---------异步清零信号,当CLR =1,输出复位为0,当CLR =0,正常计数ENA---------使能控制信号,当ENA=1,电路正常累加计数,否则电路不工作输出:SUM[3:0]---------- 计数值的个位。

即,在CLK上升沿检测到SUM=9时,SUM将被置0,开始新一轮的计数。

COUT ------------计数值的十位进位,即:只有在时钟CLK上升沿检测到SUM=9时,COUT将被置1,其余情况下COUT=0;LED显示驱动模块:输入:sum[3:0] -------待显示的数值out[6:0] ----------驱动数码管的七位数值七段数码管的字符显示真值表如下:消抖模块:三、实验过程:1.首先建立一个新的工程,添加一个新的Verilog Module,在其中编写十进制计数模块的代码,如下:module liao1(CLR,CLK,ENA,SUM,COUT);input CLR,CLK,ENA;output[3:0] SUM;output COUT;reg[3:0] SUM;reg COUT;always@(posedge CLK or posedge CLR)if(CLR)beginSUM<=4'b0000;COUT<=1'b0;endelseif(ENA)beginif(SUM==9)beginSUM<=4'b0000;COUT<=1'b1;endelsebeginSUM<=SUM+1'b1;COUT<=1'b0;endendendmodule然后执行综合,确认无误后,新建一个Test Bench WaveForm文件,进行仿真,仿真图如下:2.再新建一个Verilog Module,在其中编写七段数码显示模块的代码,如下:module liao2(SUM,out);input[3:0] SUM;output[6:0] out;reg [6:0] out;always @(SUM)begincase(SUM)4'b0000: out<=7'b0000001;4'b0001: out<=7'b1001111;4'b0010: out<=7'b0010010;4'b0011: out<=7'b0000110;4'b0100: out<=7'b1001100;4'b0101: out<=7'b0100100;4'b0110: out<=7'b0100000;4'b0111: out<=7'b0001111;4'b1000: out<=7'b0000000;4'b1001: out<=7'b0000100;default :out<=7'b0000001;endcaseendendmodule执行综合,确认无误后新建一个Test Bench WaveForm文件,进行仿真,仿真图如下:3.添加消抖模块,然后再新建一个Verilog Module,编写例化文件,制成顶层文件,其例化文件代码如下:module liao(CLK_50M,CLK,CLR,ENA,COUT,out);input CLR,CLK,ENA;input CLK_50M;output[6:0] out;output COUT;wire[3:0] SUM;debounce_module u1(CLK_50M,CLR,CLK,clk_out);liao1 u2(CLR,clk_out,ENA,SUM,COUT);liao2 u3(SUM,out);endmodule保存之后形成顶层文件:4.执行综合,确认无误后,根据实验指导书进行锁引脚操作:锁引脚完成后,修改、编辑约束文件:5.生成下载配置文件,下载到开发板进行经行验证。

用verilog HDL语言设计可逆计数器。

西安邮电学院

实验报告书

系部名称:电子工程学院学生姓名:xxx

专业名称:xxxx

班级:xxxx

实验时间:2011 年11月17日

1、掌握可逆计数器的工作原理。

2、学习用verilog HDL语言设计可逆计数器。

二、实验设备:

计算机一台,TD-EDA实验箱一台

三、实验内容:

用verilog HDL语言设计可逆计数器并进行仿真、引脚分配及下载到电路开发板进行功能验证。

四、实验程序:

module keni8(clk,enable,sum,col);

input clk,enable;

output[7:0] sum;

reg[7:0] sum;

output col;

reg col;

always @(posedge clk )

if(enable==1)

sum=sum+1;

else if(enable==0)

sum=sum-1;

else if(sum >= 8)

begin

sum=0;

col=1;

end

endmodule

五、运行结果:

1、在编程过程中,需小心谨慎,特别是注意标点符号的标注。

2、实验结果有一定的延时。

3、实验前需对TD-EDA实验箱进行了解,这样可以使实验更有效率。

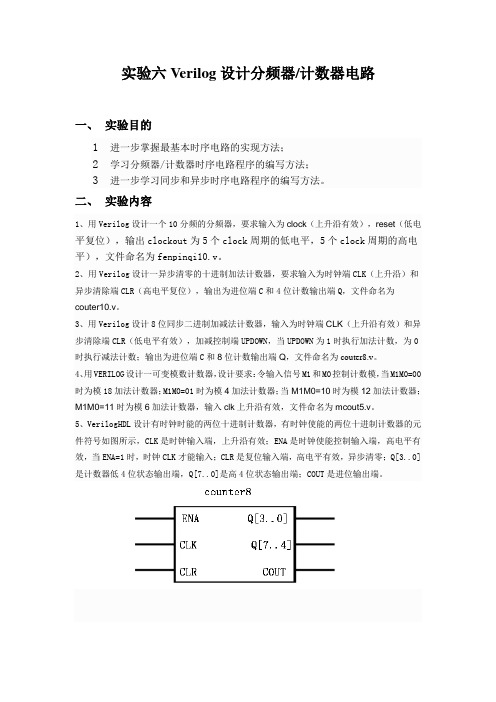

实验六Verilog设计分频器计数器电路

实验六Verilog设计分频器/计数器电路一、实验目的1进一步掌握最基本时序电路的实现方法;2学习分频器/计数器时序电路程序的编写方法;3进一步学习同步和异步时序电路程序的编写方法。

二、实验内容1、用Verilog设计一个10分频的分频器,要求输入为clock(上升沿有效),reset(低电平复位),输出clockout为5个clock周期的低电平,5个clock周期的高电平),文件命名为fenpinqi10.v。

2、用Verilog设计一异步清零的十进制加法计数器,要求输入为时钟端CLK(上升沿)和异步清除端CLR(高电平复位),输出为进位端C和4位计数输出端Q,文件命名为couter10.v。

3、用Verilog设计8位同步二进制加减法计数器,输入为时钟端CLK(上升沿有效)和异步清除端CLR(低电平有效),加减控制端UPDOWN,当UPDOWN为1时执行加法计数,为0时执行减法计数;输出为进位端C和8位计数输出端Q,文件命名为couter8.v。

4、用VERILOG设计一可变模数计数器,设计要求:令输入信号M1和M0控制计数模,当M1M0=00时为模18加法计数器;M1M0=01时为模4加法计数器;当M1M0=10时为模12加法计数器;M1M0=11时为模6加法计数器,输入clk上升沿有效,文件命名为mcout5.v。

5、VerilogHDL设计有时钟时能的两位十进制计数器,有时钟使能的两位十进制计数器的元件符号如图所示,CLK是时钟输入端,上升沿有效;ENA是时钟使能控制输入端,高电平有效,当ENA=1时,时钟CLK才能输入;CLR是复位输入端,高电平有效,异步清零;Q[3..0]是计数器低4位状态输出端,Q[7..0]是高4位状态输出端;COUT是进位输出端。

三、实验步骤:第一个实验:1、打开QuartusII,新建一个工程f_fenpinq10yjq2、新建一个Verilog HDL文件3、输入程序:module fenpinqi10(clk,reset,clkout);input clk,reset;output clkout;reg clkout;reg[2:0] cnt;always @(posedge clk , negedge reset)beginif(!reset)begin clkout<=0;cnt<=0;endelse if(cnt==4)begin cnt<=0;clkout<=~clkout;endelse cnt<=cnt+1;endendmodule4、设置顶层实体名(点settings>general >下拉选fenpinqi10)5、编译6、执行file>Create/Update>Create Symbol Files for Current Flie为VHDI设计文件生成原件符号7、建立波形文件8、导入引脚9、仿真结果如下:总结:仿真结果与实验一的题意相符,所以仿真正确。

使用Verilog HDL设计2位 16进制计数器,由DE2的KEY0输入计数值,在HEX1,HEX0上显示计数值。

FPGA实验实验二实验目的:学习计数器的设计、仿真和硬件测试方法。

实验内容及步骤:1.使用Verilog HDL设计2位 16进制计数器,由DE2的KEY0输入计数值,在HEX1,HEX0上显示计数值。

2.使用嵌入式逻辑分析仪进行仿真;3.将实验程序下载到DE2运行。

实验注意事项:去抖动程序:module jishu(clk,k,Rst,x0,x1,Clk,K,C,key);input clk,k,rst;output [6:0]x1;output [6:0]x0;reg [3:0]g1;reg [3:0]g0;reg [19:0]C;reg[9:0]K;always @(clk)if (C<20’d5000)C<=C+1,Clk<=0;else C<=0,Clk<=1;endalways @(Clk)if(K<10d20)K<=K+1,Key<=0;else K<=0,Key<=1;endalways @(posedge Clk ot negedge Rst)beginif(!Rst) g0<=0,g1<=0;else if(!Key)beginif(g0<4’d15)g0<=g0+1;else g0<=4’b0000;endendalways @(g0)if (g0==4’d15)if(g1<4’d15) g1<=g1+1; else g1<=4’b0000;end endalways @(g0)begincase (g0)4'b0000:x0<=7'b 1000000; 4'b0001:x0<=7'b 1111001; 4'b0010:x0<=7'b 0100100; 4'b0011:x0<=7'b 0110000; 4'b0100:x0<=7'b 0011001; 4'b0101:x0<=7'b 0010010; 4'b0110:x0<=7'b 0000010; 4'b0111:x0<=7'b 1111000; 4'b1000:x0<=7'b 0000000; 4'b1001:x0<=7'b 0011000; 4'b1010:x0<=7'b 0001000; 4'b1011:x0<=7'b 0000011; 4'b1100:x0<=7'b 1000110; 4'b1101:x0<=7'b 0100001; 4'b1110:x0<=7'b 0000110; 4'b1111:x0<=7'b 0001110; endcaseendalways @(g1)begincase (g1)4'b0000:x1<=7'b 1000000; 4'b0001:x1<=7'b 1111001; 4'b0010:x1<=7'b 0100100; 4'b0011:x1<=7'b 0110000; 4'b0100:x1<=7'b 0011001; 4'b0101:x1<=7'b 0010010; 4'b0110:x1<=7'b 0000010; 4'b0111:x1<=7'b 1111000; 4'b1000:x1<=7'b 0000000; 4'b1001:x1<=7'b 0011000; 4'b1010:x1<=7'b 0001000; 4'b1011:x1<=7'b 0000011; 4'b1100:x1<=7'b 1000110; 4'b1101:x1<=7'b 0100001; 4'b1110:x1<=7'b 0000110;4'b1111:x1<=7'b 0001110; endcaseendend module实验结果:。

Verilog_HDL十进制计数器实验Quartus90非常详细的步骤

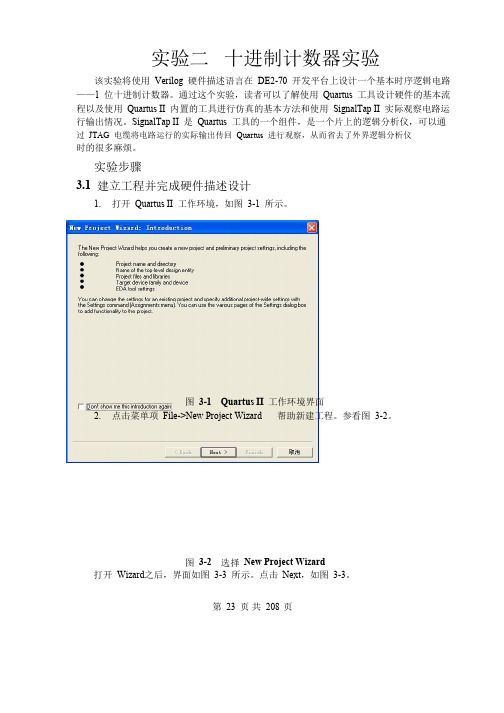

实验二十进制计数器实验该实验将使用Verilog硬件描述语言在DE2-70开发平台上设计一个基本时序逻辑电路——1位十进制计数器。

通过这个实验,读者可以了解使用Quartus工具设计硬件的基本流程以及使用Quartus II内置的工具进行仿真的基本方法和使用SignalTap II实际观察电路运行输出情况。

SignalTap II是Quartus工具的一个组件,是一个片上的逻辑分析仪,可以通过JTAG电缆将电路运行的实际输出传回Quartus进行观察,从而省去了外界逻辑分析仪时的很多麻烦。

实验步骤3.1建立工程并完成硬件描述设计1.打开Quartus II工作环境,如图3-1所示。

图3-1Quartus II工作环境界面2.点击菜单项File->New Project Wizard帮助新建工程。

参看图3-2。

图3-2选择New Project Wizard打开Wizard之后,界面如图3-3所示。

点击Next,如图3-3。

第23页共208页图3-3New Project Wizard界面3.输入工程工作路径、工程文件名以及顶层实体名。

这次实验会帮助读者理解顶层实体名和工程名的关系,记住目前指定的工程名与顶层实体名都是Counter10,输入结束后,如图3-4所示。

点击Next。

图3-4输入设计工程信息4.添加设计文件。

界面如图3-5所示。

如果用户之前已经有设计文件(比如.v文件)。

那么再次添加相应文件,如果没有完成的设计文件,点击Next之后添加并且编辑设计文件。

图3-5添加设计文件5.选择设计所用器件。

由于本次实验使用Altera公司提供的DE2-70开发板,用户必须选择与DE2-70开发板相对应的FPGA器件型号。

在Family菜单中选择Cyclone II,Package选FBGA,Pin Count选896,Speed grade 选6,确认Available devices中选中EP2C70F896C6,如图3-6。

哈尔滨工业大学数字电子技术基础课程设计报告:基于Verilog HDL语言的计数器设计

H a r b i n I n s t i t u t e o f T e c h n o l o g y

数字电子技术基础大作业报告

课程名称:数字电子技术基础

设计题目:V erilog HDL 计数器编程

院系:航天学院控制科学与工程系班级:0904102班

姓名:某某某

学号:xxxxxxxxxx

指导教师:王淑娟

设计时间:2011年12月

哈尔滨工业大学

Verilog HDL计数器编程

1设计任务

利用Verilog HDL设计一个模为学号后三位的计数器,设计要求:

1)编写源程序;

2)给出仿真电路图和仿真波形图。

2设计步骤

1.安装Quartus II软件并破解。

2.根据设计要求编写程序代码。

3.生成仿真电路图和波形如图。

3程序代码

4仿真电路图和波形图

如下图所示。

VerilogHDL简单计算器设计

实用文档目录第一章设计目的及任务要求 (1)1.1 设计目的 (1)1.2 设计任务 (1)1.3 课设要求 (1)第二章设计思路 (2)2.1 设计总体框图 (2)2.2 设计原理 (2)2.2.1 计算其原理 (2)2.2.2 数码显示原理 (2)2.2.3 八位数码管扫描的原理 (3)第三章设计源程序及分析 (4)3.1 计算器模块 (4)3.1.1 计算器源程序 (4)3.1.2 计算器程序分析 (4)3.2 数码管显示部分 (5)3.2.1 数码管显示源程序 (5)3.2.2 数码管显示程序分析 (5)3.3 循环扫描模块 (6)3.3.1 循环扫描程序 (6)3.3.2 循环程序分析 (6)3.4 总程序及其分析 (7)第四章时序仿真和结果验证 (10)4.1 计算器时序仿真及其分析 (10)4.2 数码管时序仿真及分析 (10)4.3 总体时序仿真图 (10)4.4 结果验证 (11)第五章心得体会 (12)第一章设计目的及任务要求1.1 设计目的(1)进一步加强熟练EDA基础知识。

(2)熟练掌握Quartus 6.0软件的使用以及用该软件编程和仿真的全过程。

(3)培养独立思考问题,解决问题的能力以及查阅相关资料和资料的正确使用能力,为明年的毕业设计打下良好的设计基础。

1.2 设计任务设计一个简单计算器,输入为8位二进制数,分别用两位数码管显示,输出的计算结果为16位二进制数,并用四位数码管显示,能够实现+、-、 *、/ 四种运算,其中除法的结果显示分为商和余数两部分,分别用两位数码管显示。

1.3 课设要求(1)说明题目的设计原理和思路、采用方法及设计流程。

(2)系统框图、Verilog语言设计程序或原理图。

(3)对各子模块的功能以及各子模块之间的关系做较详细的描述。

(4)详细说明调试方法和调试过程。

(5)说明测试结果:仿真时序图和结果显示图,并对其进行说明和分析。

第二章设计思路2.1 设计总体框图有分析可知,本次课程设计可以分成五个木块来实现相应的功能,分别是输入模块,计算模块,扫描模块,输出模块以及显示模块。

verilog hdl开关计数回路编程

Verilog HDL开关计数回路编程在数字电路设计中,开关计数回路是一种非常重要的电路结构。

它可以用来实现计数功能,是数字系统中常见的一种功能模块。

在本文中,我将就Verilog HDL开关计数回路编程这一主题展开深入探讨,并带你逐步理解这个概念。

1. Verilog HDL简介Verilog Hardware Description Language(HDL)是一种硬件描述语言,用于描述、建模和仿真数字电路。

它是一种行为级的描述语言,在FPGA和ASIC设计中被广泛应用。

Verilog HDL的使用使数字电路设计工程师能够更轻松地实现所需的功能,并对其进行仿真和验证。

2. 开关计数回路的原理开关计数回路是一种使用触发器和计数器构成的计数电路。

在Verilog HDL中,我们可以通过描述触发器的行为和计数器的逻辑来实现开关计数回路。

触发器用于存储当前的计数值,而计数器用于控制计数的逻辑。

通常,我们会使用寄存器或者移位寄存器来实现计数器。

这种组合结构可以实现从二进制数0到N的自动计数。

3. Verilog HDL中的开关计数回路编程在Verilog HDL中,我们可以通过module、always、initial等关键字来描述开关计数回路的行为。

我们需要定义输入和输出接口,然后编写描述触发器和计数器行为的代码。

在Verilog HDL中,我们可以使用时钟信号来控制计数的节奏,通过简单的逻辑操作实现计数的增加和重置。

这样,我们就可以完整地描述一个开关计数回路的功能。

4. 实例分析下面,我以一个4位二进制计数器为例,来展示Verilog HDL中开关计数回路的编程过程:module counter(input clk,input rst,output reg[3:0] count);always @(posedge clk or posedge rst)beginif (rst)count <= 4'b0000;elsecount <= count + 1;endendmodule在这个例子中,我们定义了一个4位二进制计数器。

用VerilogHDL设计计数器

⽤VerilogHDL设计计数器⽤Verilog HDL设计计数器⼀、实验⽬的1. 学习使⽤Verilog HDL语⾔,并学会使⽤进⾏QuartusⅡ软件编程和仿真;2. 掌握数字电路的设计⽅法,熟悉设计过程及其步骤;3. 培养学⽣的动⼿能⼒,能学以致⽤,为今后从事电⼦线路设计打下良好基础;4. 巩固加深对数电知识的理解,在仿真调试过程中,能结合原理来分析实验现象;⼆、实验内容1.设计内容及要求1)利⽤Verilog HDL设计⼀个以⾃⼰学号后三位为模的计数器;2)编写源程序;3)给出仿真电路图和仿真波形图;2.需求分析:由于本⼈的学号后3位为212,所以应编⼀个以212为模的加法计数器。

若采⽤同步清零的⽅法,则计数为0~211,化为⼆进制数即为0 0000 0000计到0 1101 0011。

3.编写源代码:module count_212(out,data,load,reset,clk);output [8:0] out;input [8:0] data;inputload,reset,clk;reg [8:0] out;always @(posedgeclk)//clk上升沿触发beginif(!reset)out=9'h000; //同步清零,低电平有效else if (load)out=data; //同步预置else if (out>=211)out=9'h000; //计数最⼤值为211,超过清零else out=out+1; //计数endendmodule程序说明:该计数器为⼀个9位计数器,计数范围0~211,具有同步同步置数和同步清零功能。

时钟的上升沿有效,当clk信号的上升沿到来时,如果清零信号为0,则清零;若不为0,计数器进⾏计数,计⾄211处同步清零。

4.画出仿真电路图:图1为同步置数、同步清零加法计数器的仿真电路图图1 仿真电路图5.画出仿真波形先对逻辑波形进⾏初始化设置,将清零信号‘restest’置1,置数信号‘load’置0,得到的仿真波形图2所⽰,波形终⽌处如图3所⽰,图4为计数到211后⾃动清零。

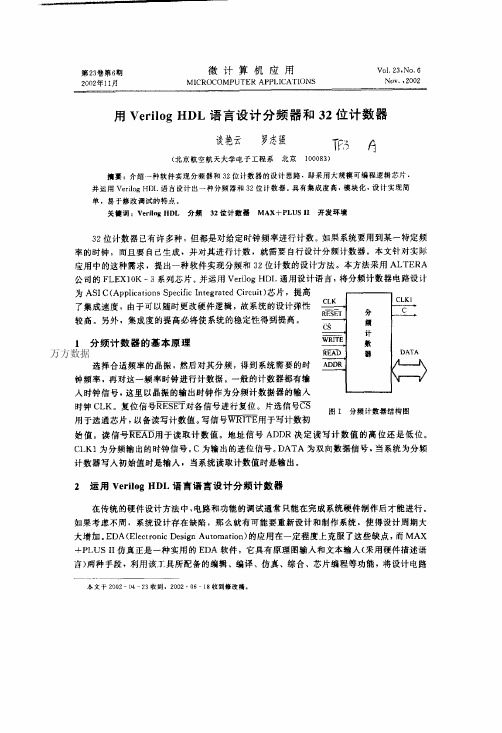

用Verilog+HDL语言设计分频器和32位计数器

i<i+1l

end

cs)∥有片选信号

end endrnodule

begin if(addr)

aceuh<2data}

该模块已通过软件仿真,符合设计要求。并已将程序下载到FPGA芯片,在电路板上与 系统进行联调,已证明设计达到预期功能,正式投入使用。

参 考 文 献

1夏宇闻.复杂数字电路与系统的VerilogHDL设计技术.北京t北京航空航天大学出版杜,1999.1—86 2阎石鼓字电子技术基础.北京:高等教育出版社.1 997.224--295 3束万焘·罗 车,吴顺军.CPI,D技术及其盥用西安:西安电子科技大学出版社,1999.30】oo

end end

output

elkl.c}//输出时钟和计数进位信号

j

wirte[15

reg

பைடு நூலகம்

O]data—reg·dataI

c,clkl{

if(i>=119) 计数值的高16位数和低

begin

∥对输人时钟进行J20分频

reg[1 5:O]aceub.aecul;

1

6位数

j<=0; clkl<=~clkl;

第23卷第6期 2002年1 1月

微计算机应用

MICROCOMPUTER APPLICATIONS

Vol

23.N。.6

Nov-,2002

用Ver|log

HDL语言设计分频器和32位计数器

谈艳云 罗志强

100083)

仍局

(北京航空航天大学电子工程东北京

擅要t介绍一种软件实现分频器和32位计数器的设计思路.即采用大规模可编程逻辑芯片.

+PLUS

II仿真正是一种实用的EDA软件,它具有原理图输入和文本输入(采用硬件描述语

Verilog HDL加法计数器的设计

H a r b i n I n s t i t u t e o f T e c h n o l o g yV e r i l o g H D L加法计数器的设计课程名称:数字电子技术基础院系:航天学院班级:1121101班姓名:学号:指导教师:哈尔滨工业大学1 设计要求利用Verilog HDL设计一个以自己学号后三位(107)为模的计数器。

2 设计内容2.1 所使用的软件Quartus II 11.0 (32-Bit)和ModelSim-Altera 6.6d (Quartus II 11.0)。

2.2 设计思想从0计数到106,到106之后同步清零,实现以107为模的计数器。

2.3 源程序module count_107(out,reset,clk);output[7:0] out;input clk,reset;reg[7:0] out;always@(posedge clk )beginif((!reset)||(out==8'h6A))out<=8'h00;elseout<=out+8'h01;endendmodule2.4 仿真电路图RTL Viewer仿真电路如图1所示:图1 计数器的RTL Viewer仿真电路图Technology Map Viewer仿真电路如图2所示:图2 计数器的Technology Map Viewer仿真电路图2.5 Test Benches程序// Generated on "12/20/2013 11:57:54"// Verilog Test Bench template for design : count_107// Simulation tool : ModelSim-Altera (Verilog)`timescale 1 ps/ 1 psmodule count_107_vlg_tst();reg eachvec;reg clk;reg reset;wire [7:0] out;count_107 i1 (.clk(clk),.out(out),.reset(reset));initialbegin#1 clk=0;#2 reset=0;#3 reset=1;$display("Running testbench");endalways#5 clk=~clk;beginendendmodule2.6 仿真波形图仿真波形图如图3所示,可以看出计数周期为0~106,实现了以107为模的计数器。

基于 Verilog语言的可预置加减计数器的设计

基于Verilog 语言的可预置加减计数器的设计胡 滨(西安邮电学院 陕西西安 710061)摘 要:计数器是大规模集成电路中运用最广泛的结构之一。

在模拟及数字集成电路设计当中,灵活地选择与使用计数器可以实现很多复杂的功能,可以大量减少电路设计的复杂度和工作量。

讨论了一种可预置加减计数器的设计,运用Verilog HDL 语言设计出了一种同步的可预置加减计数器,该计数器可以根据控制信号分别实现加法计数和减法计数,从给定的预置位开始计数,并给出详细的Verilog HDL 源代码。

最后,设计出了激励代码对其进行仿真验证,实验结果证明该设计符合功能要求,可以实现预定的功能。

关键词:Verilog HDL ;可逆计数器;ModelSim ;可预置加减计数器中图分类号:TN47 文献标识码:B 文章编号:1004373X (2007)1617702Design of R eversible Counter B ased on V erilog H DLHU Bin(Xi ′an University of Post &Telecommunications ,Xi ′an ,710061,China )Abstract :Counter is one of the elements most in use in VL SI design.It has been proved that choosing and using counter properly can solve many complex problems.Discussing the design of a kind of reversible counter ,the study devises a synchro 2nous reversible counter by applying Verilog HDL.The reversible counter can count f rom the given preset data ,the detailed Veriog HDL source code has been given .The counter can add and subtract according to control signals.Finally ,the study devi 2ses stimulate code to its simulation certification.The certification result testifies that the design accord with the f unctional re 2quirements can realize the preconcerted f unction.K eywords :Verilog HDL ;reversible counter ;ModelSim ;preset modified counter收稿日期:20070116 计数器对时钟脉冲进行计数,还被广泛用于定时、分频、以及各种复杂的数字电路中,是计算机中的一个重要器件,是应用最广泛的一种典型的时序电路。

用VerilogHDL设计2位16进制计数器

基于FPGA的系统设计与应用实验二计数器设计实验一、实验目的:学习计数器的设计、仿真和硬件测试方法。

二、实验内容及步骤:1.用Verilog HDL设计2位16进制计数器,由DE2的KEY0输入计数值,在HEX1,HEX0上显示计数值。

2.使用嵌入式逻辑分析仪进行仿真;3.将实验程序下载到DE2运行。

实验注意事项:去抖动三、程序代码module lib22(out1,out2,clk,rst,key);output [6:0] out1,out2;input clk,rst;input key;reg [19:0]count;reg [7:0]in;reg [6:0]out1,out2;reg C,K;reg [9:0] r1;always@(posedge clk)if(count==20'd5000)beginC=~C;count<=1'b0;endelsecount=count+1'b1;always @ (posedge C)beginif(r1<10'd1000)beginK<=1'b0;r1<=r1+1'b1;endelsebeginK<=1'b1;r1<=1'b0;endendalways @ (posedge C,negedge rst) if(!rst)in<=1'b0;else if(!K)beginin=in+8'b1;endalways @ (in[3:0])case(in[3:0])4'b0000:out1=7'b1000000;4'b0001:out1=7'b1111001;4'b0010:out1=7'b0100100;4'b0011:out1=7'b0110000;4'b0100:out1=7'b0011001;4'b0101:out1=7'b0010010;4'b0110:out1=7'b0000010;4'b0111:out1=7'b1011000;4'b1000:out1=7'b0000000;4'b1001:out1=7'b0010000;4'b1010:out1=7'b0001000;4'b1011:out1=7'b0000011;4'b1100:out1=7'b1000110;4'b1101:out1=7'b1100001;4'b1110:out1=7'b0000110;4'b1111:out1=7'b0001110;default:out1=7'b1111111; endcasealways @ (in[7:4])case(in[7:4])4'b0000:out2=7'b1000000;4'b0001:out2=7'b1111001;4'b0010:out2=7'b0100100;4'b0011:out2=7'b0110000;4'b0100:out2=7'b0011001;4'b0101:out2=7'b0010010;4'b0110:out2=7'b0000010;4'b0111:out2=7'b1011000;4'b1000:out2=7'b0000000;4'b1001:out2=7'b0010000;4'b1010:out2=7'b0001000;4'b1011:out2=7'b0000011;4'b1100:out2=7'b1000110;4'b1101:out2=7'b1100001;4'b1110:out2=7'b0000110;4'b1111:out2=7'b0001110;default:out2=7'b1111111; endcaseendmodule四、实验原理图:DE2按键电路图五、实验总结与分析:1.不加去斗时,出现的结果不稳定,不同的DE2板子结果不一样,在加上去斗时,实验结果很稳定;2.去斗可以是检测抖动阶段也可以是不抖动阶段;3.实验二包含了实验一的一些内容,例如数码管的显示,但是加了去抖动程序,使结果更加的稳定。

VerilogHDL十进制计数器实验Quartus非常详细的步骤

2.

I脈;t》I-I取消I

图

打开

第23页共208页

图

3.

这次实验会帮助读者理解顶层实体名和工程名的关系,记住目前指定的工程名与顶层 实体名都是

Bev PzdJcd Tizazdz Dizcct azy,VoaGjlop-"LcTcl Eirtity [pag. . .

Whatisths workiiig directory forIhnproiect?

必须选择与DE2-70开发板相对应的FPGA器件型号。

在Family菜单中选择CycloneII,Package选

FBGA,Pin Count选896, Speed grade资料个人收集整

理,勿做商业用途

选 6,确认AvgjabMHViWSffl中选f^EPICTOF

热*896c6^如图3,矚6。図

Pioiect directwy:

D./aHerfl/8ai/DE270Tutorial/Coinleil G/

Pioiect name;

CounteflO

Tcp-I&vel design efitay.

CodiHeflO

NumbercSflag added:

0

Number oJ user fcranes added:

Toolrbame:

r-Hit1

:Ei加I

厂Junior

TinrgAnalysis

Toolnarne: [fNon^

t PlrI

I~■ h U 11ll r It b

图

7.

对之前的设计,如图

Bev PzdJcd Tizazdz SuAsary [page GnSG]

When you rfcK Finish, the project岬il tn created wdh the folpwrg sflHings:

VerilogHDL十进制计数器实验Quartus非常详细的步骤

实验二十进制计数器实验该实验将使用Verilog 硬件描述语言在DE2-70 开发平台上设计一个基本时序逻辑电路——1 位十进制计数器。

通过这个实验,读者可以了解使用Quartus 工具设计硬件的基本流程以及使用Quartus II 内置的工具进行仿真的基本方法和使用SignalTap II 实际观察电路运行输出情况。

SignalTap II 是Quartus 工具的一个组件,是一个片上的逻辑分析仪,可以通过JTAG 电缆将电路运行的实际输出传回Quartus 进行观察,从而省去了外界逻辑分析仪时的很多麻烦。

实验步骤3.1建立工程并完成硬件描述设计1. 打开Quartus II 工作环境,如图3-1 所示。

图3-1 Quartus II工作环境界面2. 点击菜单项File->New Project Wizard 帮助新建工程。

参看图3-2。

图3-2 选择New Project Wizard打开Wizard 之后,界面如图3-3 所示。

点击Next,如图3-3。

第23 页共208 页图3-3 New Project Wizard界面3. 输入工程工作路径、工程文件名以及顶层实体名。

这次实验会帮助读者理解顶层实体名和工程名的关系,记住目前指定的工程名与顶层实体名都是Counter10,输入结束后,如图3-4 所示。

点击Next。

图3-4输入设计工程信息4. 添加设计文件。

界面如图3-5 所示。

如果用户之前已经有设计文件(比如.v 文件)。

第24 页共208 页那么再次添加相应文件,如果没有完成的设计文件,点击Next 之后添加并且编辑设计文件。

图3-5添加设计文件5. 选择设计所用器件。

由于本次实验使用Altera 公司提供的DE2-70 开发板,用户必须选择与DE2-70 开发板相对应的FPGA 器件型号。

在Family 菜单中选择Cyclone II,Package 选FBGA,Pin Count 选896,Speed grade 选6,确认Available devices 中选中EP2C70F896C6,如图3-6。

远程FPGA虚拟实验平台用SystemVerilogHDL实现计数器和分频器

远程FPGA虚拟实验平台⽤SystemVerilogHDL实现计数器和分频器远程FPGA虚拟实验平台⽤SystemVerilog HDL实现计数器和分频器原理计数器本实验中,材料给出的计数器是⼆进制来分频的,就搞得还挺⿇烦。

/** The input port is replaced with an internal signal **/wire reset =PB[0];wire clk;/************* The logic of this experiment *************/logic [23:0] count;always@(posedge CLOCK or posedge reset)beginif(reset)count <=0;elsecount <= count+1;endassign clk = count[22];//2^23,详解见下⽅logic [7:0]q;always @ (posedge clk or posedge reset)if(reset)q <=1;elseq <={q[6:0], q[7]};/****** Internal signal assignment to output port *******/assign L[7:0]= q[7:0];endmodule由代码可知,在CLOCK输出2个信号后,clk=1,然后CLOCK需要再输出2个信号,使clk=0。

这个过程的时间是2(次)/10M(次/秒),约为838毫秒。

测试界⾯的刷新间隔T实际上是,每隔T时间显⽰⼀下虚拟实验⾯板当前的情况,如果在测试时刷新间隔T=1000ms,会使得刷新不完全按照分频器转换后的频率来,所以刷着刷着就跳过了某⼏次,这个“某⼏次”是可以算的,但是我懒得算。

也就是说,只要刷新间隔T<=838ms就能让每个灯都亮了,但是如果不是838的倍数,灯亮的时候就不匀速,有点抽风。

verilogHDL约翰逊计数器(免费)

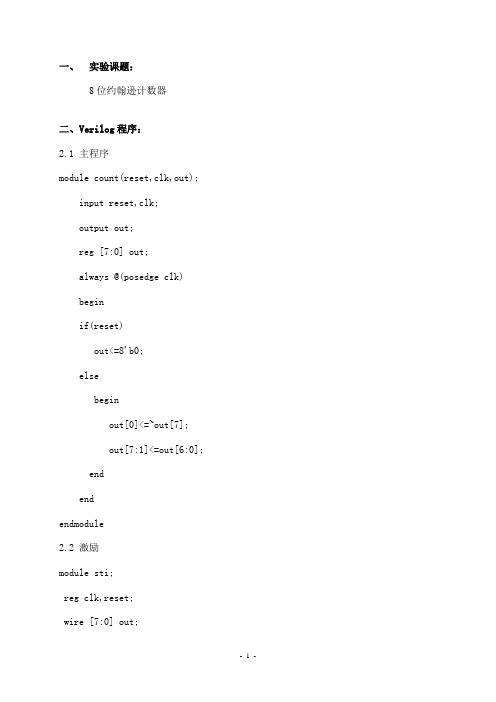

一、实验课题:

8位约翰逊计数器

二、Verilog程序:

2.1主程序

module count(reset,clk,out);

input reset,clk;

output out;

4.2实验心得

本次实验教上次有了充分的准备,所以做起来比较容易,没有出现大的问题。总体来讲实验比较顺利。

count test(reset,clk,out);

initial

clk<=8'b0;

always

#10 clk<=~clk;

initiaet<=0;

end

endmodule

三、实验波形截图:

四、波形分析及实验心得:

4.1波形分析

如图所示:波形实验结果与理论相符

reg [7:0] out;

always @(posedge clk)

begin

if(reset)

out<=8'b0;

else

begin

out[0]<=~out[7];

out[7:1]<=out[6:0];

end

end

endmodule

2.2激励

module sti;

reg clk,reset;

wire [7:0] out;

FPGA—基于HDL的十进制计数器设计

基于HDL的十进制计数器设计一、实验目的1、掌握基于语言的ISE设计全流程;2、熟悉、应用VerilogHDL描述数字电路;3、掌握基于Verilog的组合和时序逻辑电路的设计方法。

4、掌握chipscope片内逻辑分析仪的使用与调试方法。

5、设计具有异步复位、同步使能的十进制计数器,其计数结果可以通过七段数码管、发光二极管等进行显示。

二、实验原理1、十进制计数器的设计即是设置一变量,当计数脉冲上升沿到来时,先判断是否为9,若是则置零,否则就进行加一操作。

将变量再进行一个译码操作输出到数码管显示即可。

图1 实验原理图2、数码管分为7 段和8 段,七段数码管由7段二极管组成。

8段数码管比起7段数码管多了一个显示小数点的LED。

数码管按发光二极管单元衔接方式分为共阳极数码管和共阴极数码管。

本实验使用共阳数码管。

它是指将一切发光二极管的阳极接到一同构成公共阳极(COM)的数码管。

共阳数码管在应用时应将公共极COM接到电源VCC 上,当某一字段发光二极管的阴极为低电平相应字段就点亮。

当某一字段的阴极为高电平相应字段就不亮。

共阳端可以作为位选端,实现动态扫描。

动态扫描即是利用了人眼睛的视觉暂留现象,以合适的频率显示每一位数码管,便会产生所有数码管是一起点亮的错觉,数码管原理图如图:图2共阳数码管示意图3、数码管显示数字与对应的输入数据的关系如表所示:0 8'hc01 8'hf92 8'ha43 8'hb04 8'h995 8'h926 8'h827 8'hf8表1 数码管显示表4、本次设计一共有11个端口:输入信号:clk -------待计数的时钟。

clr ---------异步清零信号,当clr=1,输出复位为0,当clr=0,正常计数。

ena---------使能控制信号,当ena=1,电路正常累加计数,否则电路不工作。

输出信号:q[6:0]---------驱动数码管,显示计数值的个位。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

用Verilog HDL设计计数器

一、实验目的

1. 学习使用Verilog HDL语言,并学会使用进行QuartusⅡ软件编

程和仿真;

2. 掌握数字电路的设计方法,熟悉设计过程及其步骤;

3. 培养学生的动手能力,能学以致用,为今后从事电子线路设计

打下良好基础;

4. 巩固加深对数电知识的理解,在仿真调试过程中,能结合原理

来分析实验现象;

二、实验内容

1.设计内容及要求

1)利用Verilog HDL设计一个以自己学号后三位为模的计数器;

2)编写源程序;

3)给出仿真电路图和仿真波形图;

2.需求分析:

由于本人的学号后3位为212,所以应编一个以212为模的加法计数器。

若采用同步清零的方法,则计数为0~211,化为二进制数即为0 0000 0000计到0 1101 0011。

3.编写源代码:

module count_212(out,data,load,reset,clk);

output [8:0] out;

input [8:0] data;

input load,reset,clk;

reg [8:0] out;

always @(posedge clk)

+

<

计数器功能表

Clk Reset Load Out

上升沿0X清零

上升沿10置数(data)

上升沿11计数

2. 应熟知计数器的使用方法,并能设计出任意进制的计数器,在设计时才能得心应手。

计数进制的改变,包括清零法(同步清零和异步清零)和置数法。

假定计数器的计数进制为N,要将其改为M进制的计数器,M < N 。

当计数器从全零状态开始计数,若采用同步清零法,设计时应经过M-1个状态后清零;若采用异步清零法,设计时应经过M个状态后清零。

这样就跳过了M个状态,实现了M进制计数器。

因为采用异步清零法会产生清零不可靠的问题,本实验采用的为同步清零法。

3. 本实验采用的是数据流描述方式来描述电路,通过assign 连续赋值实现组合逻辑功能,使用简单,语句易于读懂。

4. 调试过程中,应沉着冷静,出现错误时,应该根据数电知识原理来分析,找

出错误原因,对症下药;也可上网搜查该错误的含义,可能是软件的使用方法不对。