testbench时钟信号的编写(verilog)

verilogtestbench写法

verilogtestbench写法Verilog测试平台(testbench)技术(⼀) 收藏对设计进⾏功能仿真和时序仿真时,需要给待测模块提供激励输⼊。

对于由Verilog语⾔描述的设计模块,最好的⽅法⾃然同样是⽤Verilog语⾔对待测模块施加激励和检测模块的输出响应。

实际应⽤中,Verilog测试平台(testben ch)就是⽤来提供上述功能的。

Verilog测试平台是⼀个例化的待测(MUT)Verilog 模块,给它施加激励并观测其输出。

由于测试平台是⽤Verilog语⾔描述的,因此可以应⽤到不同的仿真环境中。

待测模块和与之对应的测试平台组成⼀个仿真模型,应⽤这个模型可以在不同的测试环境中⽤相同的激励对待测模块进⾏调试。

下⾯就对不同电路类型分别介绍verilog测试平台的语⾔结构。

⼀、测试平台1.组合电路测试设计组合电路的测试平台时,待测模块及其功能决定了激烈的选择与测试次数。

对于⼀个已有的待测模块,测试平台中需要声明与待测模块输⼊输出端⼝对应的变量。

与输⼊端⼝相连接的变量定义为reg,与输出端⼝相连接的变量定义为wire,例化时将测试平台中声明的变量与待测模块的输⼊输出端⼝相关联。

使⽤initial语句控制程序运⾏,initial语句是⼀种过程结构,在initial块中可使⽤延迟控制语句来控制initial块中的程序流动。

这⾥对⼀个简单的算术逻辑单元(ALU)为例进⾏测试,下⾯是该单元Verilog 描述。

/***************************************************************** ********///多动能ALU的Verilog代码'timescale 1ns/100psmodule alu_4bit(a,b,f,oe,y,p,ov,a_gt_b,a_eg_b,a_lt_b);input [3:0] a,b;input [1:0] f;input oe;input [3:0] y;output p,ov,a_gt_b,a_eg_b,a_lt_b; reg [4:0] im_y;always @(a or b or f)beginov=1'b0;im_y=0;case(f)2'b00:beginim_y=a+b;if(im_y>5'b01111)ov=1'b1;end2'b01:beginim_y=a-b;if(im_y>5'b01111)ov=1'b1;end2'b10:im_y[3:0]=a&b;2'b11:im_y[3:0]=a^b;default:im_y[3:0]=4'b0000;endcaseendalways @(a or b)beginif(a>b){a_gt_b,a_ge_b,a_lt_b}=3'b100;else if(a{a_gt_b,a_ge_b,a_lt_b}=3'b001;else{a_gt_b,a_ge_b,a_lt_b}=3'b010;endassign p=^im_y[3:0];assign y=oe?im_y[3:0]:4'bz;endmodule/***************************************************************** ********/模块alu_4bit是四功能的算术逻辑单元,输⼊包括数据信号a、b和功能信号f,输出包括数据信号y和ALU⽣成的奇偶校验信号p、溢出信号ov及⽐较信号。

编写高效率的testbench

编写高效率的testbench简介:由于设计的规模越来越大也越来越复杂,数字设计的验证已经成为一个日益困难和繁琐的任务。

验证工程师们依靠一些验证工具和方法来应付这个挑战。

对于几百万门的大型设计,工程师们一般使用一套形式验证(formal verification)工具。

然而对于一些小型的设计,设计工程师常常发现用带有testbench的HDL仿真器就可以很好地进行验证。

Testbench已经成为一个验证高级语言(HLL --High-Level Language) 设计的标准方法。

通常testbench完成如下的任务:1.实例化需要测试的设计(DUT);2.通过对DUT模型加载测试向量来仿真设计;3.将输出结果到终端或波形窗口中加以视觉检视;4.另外,将实际结果和预期结果进行比较。

通常testbench用工业标准的VHDL或Verilog硬件描述语言来编写。

Testbench调用功能设计,然后进行仿真。

复杂的testbench完成一些附加的功能—例如它们包含一些逻辑来选择产生合适的设计激励或比较实际结果和预期结果。

后续的章节描述了一个仔细构建的testbench的结构,并且提供了一个自动比较实际结果与预期结果的进行自我检查的testbench例子。

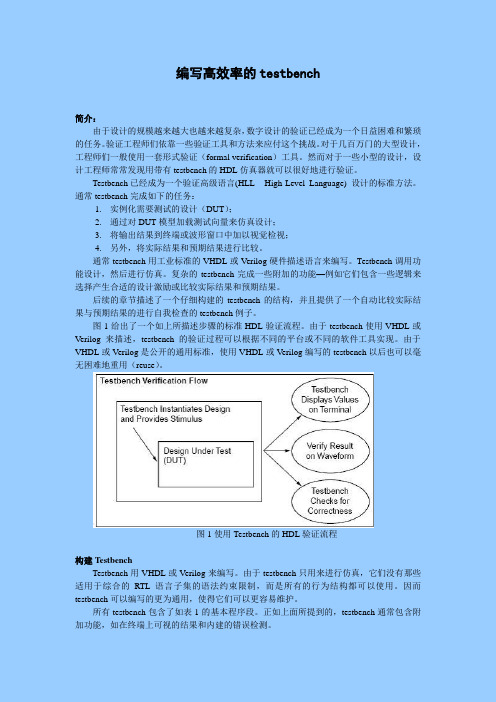

图1给出了一个如上所描述步骤的标准HDL验证流程。

由于testbench使用VHDL或Verilog来描述,testbench的验证过程可以根据不同的平台或不同的软件工具实现。

由于VHDL或Verilog是公开的通用标准,使用VHDL或Verilog编写的testbench以后也可以毫无困难地重用(reuse)。

图1使用Testbench的HDL验证流程构建TestbenchTestbench用VHDL或Verilog来编写。

由于testbench只用来进行仿真,它们没有那些适用于综合的RTL语言子集的语法约束限制,而是所有的行为结构都可以使用。

因而testbench可以编写的更为通用,使得它们可以更容易维护。

VHDL——如何写简单的testbench

use ieee.std_logic_1164.all;use ieee.std_logic_arith.all;--use ieee.std_logic_unsigned.all;entity cnt6 isport(clr,en,clk :in std_logic;q :out std_logic_vector(2 downto 0) );end entity;architecture rtl of cnt6 issignal tmp :std_logic_vector(2 downto 0); beginprocess(clk)-- variable q6:integer;beginif(clk'event and clk='1') thenif(clr='0')thentmp<="000";elsif(en='1') thenif(tmp="101")thentmp<="000";elsetmp<=unsigned(tmp)+'1';end if;end if;end if;q<=tmp;-- qa<=q(0);-- qb<=q(1);-- qc<=q(2);end process;end rtl;二、六进制计数器testbench的代码signal en :std_logic:='0';signal clk :std_logic:='0';signal q :std_logic_vector(2 downto 0);constant clk_period :time :=20 ns;begininstant:cnt6 port map(clk=>clk,en=>en,clr=>clr,q=>q);clk_gen:processbeginwait for clk_period/2;clk<='1';wait for clk_period/2;clk<='0';end process;clr_gen:processbeginclr<='0';wait for 30 ns;clr<='1';wait;end process;en_gen:processbeginen<='0';wait for 50ns;en<='1';wait;end process;end rtl;--测试平台文件(testbench)的基本结构library ieee;use ieee.std_logic_1164.all;entity test_bench is --测试平台文件的空实体(不需要端口定义) end test_bench;architecture tb_behavior of test_bench iscomponent entity_under_test --被测试元件的声明port(list-of-ports-theri-types-and-modes);end component;begininstantiation:entity_under_test port map(port-associations);process() --产生时钟信号……end process;process() --产生激励源……end process;end tb_behavior;------------------------------------------------------------------- --简单计数程序源码library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;use ieee.std_logic_unsigned.all;entity sim_counter isport(clk :in std_logic;reset :in std_logic;count :out std_logic_vector(3 downto 0));end entity;architecture behavioral of sim_counter issignal temp :std_logic_vector(3 downto 0);beginprocess(clk,reset)beginif reset='1' thentemp<="0000";elsif clk'event and clk='1' thentemp<=temp+1;end if;end process;count<=temp;end behavioral;------------------------------------------------------------------- --简单计数程序,测试文件代码(testbench)library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;use ieee.numeric_std.all;entity counter_tb_vhd is --测试平台实体end counter_tb_vhd;architecture behavior of counter_tb_vhd is--被测试元件(DUT)的声明component sim_counterport(clk :in std_logic;reset :in std_logic;count :out std_logic_vector(3 downto 0));end component;--输入信号signal clk:std_logic:='0';signal reset :std_logic:='0';--输出信号signal count :std_logic_vector(3 downto 0);constant clk_period :time :=20 ns; --时钟周期的定义begindut:sim_counter port map(clk=>clk,reset=>reset,counter=>counter);clk_gen:processbeginclk='1';wait for clk_period/2;clk='0';wait for clk_period/2;end process;tb:process --激励信号beginwait for 20 ns;reset<='1';wait for 20 ns;reset<='0';wait for 200 ns;wait; --will wait forever;end process;end;--激励信号的产生方式--1.以一定的离散时间间隔产生激励信号的波形--2.基于实体的状态产生激励信号,也就是说基于实体的输出响应产生激励信号--两种常用的复位信号--1.周期性的激励信号,如时钟--2.时序变化的激励型号,如复位--eg.产生不对称时钟信号w_clk<='0' after period/4 when w_clk='1' else'1' after 3*period/4 when w_clk='0' else'0';--eg.产生堆成时钟信号,process语句clk_gen1:processconstan clk_period := 40 ns;beginclk='1';wait for clk_period/2;clk='0';wait for clk_period/2;end process;四、如果自己不想写这些testbench的这些固定格式,可以在quartus 里自动生成testbench文件的模板,然后往里面写信号就行了步骤:processing->start->start test bench template write这里需要注意的是要在仿真选项里选择一个仿真工具,然后才会生成testbench自动生成的testbench模板格式如下:-- Copyright (C) 1991-2008 Altera Corporation-- Your use of Altera Corporation's design tools, logic functions-- and other software and tools, and its AMPP partner logic-- functions, and any output files from any of the foregoing-- (including device programming or simulation files), and any-- associated documentation or information are expressly subject-- to the terms and conditions of the Altera Program License-- Subscription Agreement, Altera MegaCore Function License-- Agreement, or other applicable license agreement, including,-- without limitation, that your use is for the sole purpose of-- programming logic devices manufactured by Altera and sold by-- Altera or its authorized distributors. Please refer to the-- applicable agreement for further details.-- ***************************************************************************-- This file contains a Vhdl test bench template that is freely editable to-- suit user's needs .Comments are provided in each section to help the user -- fill out necessary details.-- ***************************************************************************-- Generated on "03/13/2011 20:05:04"-- Vhdl Test Bench template for design : cnt6---- Simulation tool : ModelSim (VHDL)--LIBRARY ieee;USE ieee.std_logic_1164.all;ENTITY cnt6_vhd_tst ISEND cnt6_vhd_tst;ARCHITECTURE cnt6_arch OF cnt6_vhd_tst IS-- constants-- signalsSIGNAL clk : STD_LOGIC;SIGNAL clr : STD_LOGIC;SIGNAL en : STD_LOGIC;SIGNAL q : STD_LOGIC_VECTOR(2 DOWNTO 0);COMPONENT cnt6PORT (clk : IN STD_LOGIC;clr : IN STD_LOGIC;en : IN STD_LOGIC;q : OUT STD_LOGIC_VECTOR(2 DOWNTO 0));END COMPONENT;BEGINi1 : cnt6PORT MAP (-- list connections between master ports and signalsclk => clk,clr => clr,en => en,q => q);init : PROCESS-- variable declarationsBEGIN-- code that executes only onceWAIT;END PROCESS init;always : PROCESS-- optional sensitivity list-- ( )-- variable declarationsBEGIN-- code executes for every event on sensitivity list WAIT;END PROCESS always;END cnt6_arch;。

组合-时序逻辑电路Verilog-Testbench代码_带仿真代码和波形_

1组合逻辑电路--基本门电路1.1基本门电路1.1.1结构化描述方式代码如下View Code1 module logics2 (3 input iA,4 input iB,5 output oAnd,6 output oOr,7 output oNot8 );910 and and_inst(oAnd,iA,iB);11 or or_inst(oOr,iA,iB);12 not not_inst(oNot,iA);1314 endmodule最底层的是门级原语and or not RTL级视图testbench如下View Code1 `timescale 1 ns/ 1 ns2 module logics_tb();34 reg ia;5 reg ib;67 wire oAnd;8 wire oOr;9 wire oNot;1011 initial12 begin13 ia=0;14 #40 ia=1;15 #40 ia=0;16 #40 ia=1;17 #40 ia=0;18 end1920 initial21 begin22 ib=0;23 #40 ib=0;24 #40 ib=1;25 #40 ib=1;26 #40 ib=0;27 end2829 logics logics_inst30 (31 .iA(ia),32 .iB(ib),33 .oAnd(oAnd),34 .oOr(oOr),35 .oNot(oNot)36 );3738 endmoduleRTL级仿真图形如下GATE级仿真图如下可见RTL级仿真是理想的,GATE级仿真考虑了延迟和信号开始的不确定。

1.1.2采用流描述方法代码如下View Code1 module logics2 (3 input iA,4 input iB,5 output oAnd,6 output oOr,7 output oNot8 );910 assign oAnd=iA&iB;11 assign oOr=iA|iB;12 assign oNot=~iA;1314 endmoduleRTL级视图,仿真图形同上。

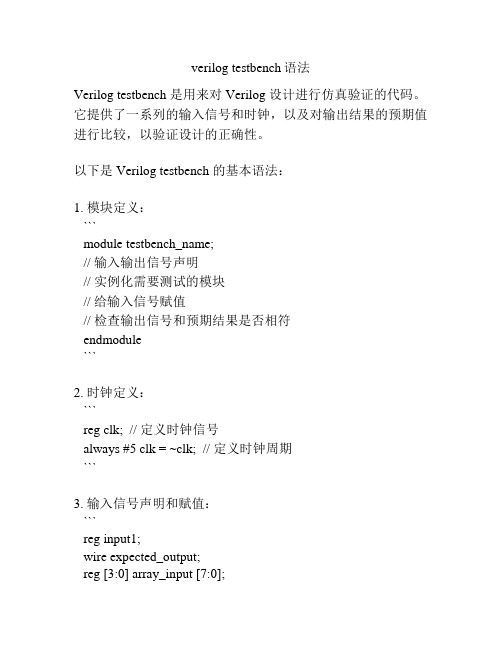

verilog testbench语法

verilog testbench语法Verilog testbench 是用来对 Verilog 设计进行仿真验证的代码。

它提供了一系列的输入信号和时钟,以及对输出结果的预期值进行比较,以验证设计的正确性。

以下是 Verilog testbench 的基本语法:1. 模块定义:```module testbench_name;// 输入输出信号声明// 实例化需要测试的模块// 给输入信号赋值// 检查输出信号和预期结果是否相符endmodule```2. 时钟定义:```reg clk; // 定义时钟信号always #5 clk = ~clk; // 定义时钟周期```3. 输入信号声明和赋值:```reg input1;wire expected_output;reg [3:0] array_input [7:0];// 给输入信号赋值initial begininput1 = 1'b0;#10;input1 = 1'b1;#10;//...end```4. 实例化需要测试的模块:```// 通过实例化需要测试的模块// 给模块的输入端口连接输入信号// 给模块的输出端口连接输出信号// 在 testbench 中实例化被测试的模块//...```5. 检查输出信号和预期结果:```// 在仿真过程中,通过比较输出信号和预期结果来验证设计的正确性// 根据需要使用相应的比较语句,如 `==`, `!=`, `===`, `!==`, `>`, `<` 等// 在每个时钟周期末检查预期输出结果//...```这些是 Verilog testbench 的基本语法。

在具体的测试中,需要根据设计的功能和需求来给输入信号赋值,并检查输出信号和预期结果是否一致。

Verilog-testbench的写法

数字集成电路设计入门--从HDL到版图于敦山北大微电子学系第十五章Verilog Test Bench使用简介学习内容:•用一个复杂的test bench复习设计的组织与仿真•建立test bench通常使用的编码风格及方法设计组织虚线表示编译时检测输入文件是否存在及可读并允许生成输出文件。

test bench 组织stimulus要验证的设计简单的test bench•简单的test bench 向要验证的设计提供向量,人工验证输出。

•复杂的test bench 是自检测的,其结果自动验证。

复杂的test bench激励验证结果要验证的设计并行块•fork…join块在测试文件中很常用。

他们的并行特性使用户可以说明绝对时间,并且可以并行的执行复杂的过程结构,如循环或任务。

module inline_ tb;reg [7: 0] data_ bus;// instance of DUTinitial forkdata_bus = 8'b00;Time | data_ bus0 | 8’b0000_0000 10 | 8’b0100_0101 30 | 8’b0100_0110 40 | 8’b0100_0111 45 | 8’b1000_1110#10 data_bus = 8'h45;#20 repeat (10) #10 data_bus = data_bus + 1;#25 repeat (5) #20 data_bus = data_bus<< 1;#140 data_bus = 8'h0f;joinendmodule上面的两个repeat循环从不同时间开始,并行执行。

象这样的特殊的激励集在单个的begin…end块中将很难实现。

50 | 8’b1000_1111 60 | 8’b1001_0000 65 | 8’b0010_0000 70 | 8’b0010_0001 80 | 8’b0010_0010 85 | 8’b0100_0100 90 | 8’b0100_0101 100 | 8’b0100_0110 105 | 8’b1000_1100 110 | 8’b1000_1101 120 | 8’b1000_1110 125 | 8’b0001_1100 140 | 8’b0000_1111包含文件•包含文件用于读入代码的重复部分或公共数据。

如何编写testbench的总结(非常实用的总结)

如何编写testbench的总结(⾮常实⽤的总结)1.激励的设置相应于被测试模块的输⼊激励设置为reg型,输出相应设置为wire类型,双向端⼝inout在测试中需要进⾏处理。

⽅法1:为双向端⼝设置中间变量inout_reg作为该inout的输出寄存,inout⼝在testbench中要定义为wire型变量,然后⽤输出使能控制传输⽅向。

eg:inout [0:0] bi_dir_port;wire [0:0] bi_dir_port;reg [0:0] bi_dir_port_reg;reg bi_dir_port_oe;assign bi_dir_port=bi_dir_port_oe?bi_dir_port_reg:1'bz;⽤bi_dir_port_oe控制端⼝数据⽅向,并利⽤中间变量寄存器改变其值。

等于两个模块之间⽤inout双向⼝互连。

往端⼝写(就是往模块⾥⾯输⼊)⽅法2:使⽤force和release语句,这种⽅法不能准确反映双向端⼝的信号变化,但这种⽅法可以反映块内信号的变化。

具体如⽰:module test();wire data_inout;reg data_reg;reg link;#xx; //延时force data_inout=1'bx; //强制作为输⼊端⼝...............#xx;release data_inout; //释放输⼊端⼝endmodule从⽂本⽂件中读取和写⼊向量1)读取⽂本⽂件:⽤ $readmemb系统任务从⽂本⽂件中读取⼆进制向量(可以包含输⼊激励和输出期望值)。

$readmemh ⽤于读取⼗六进制⽂件。

例如:reg [7:0] mem[1:256] // a 8-bit, 256-word 定义存储器meminitial $readmemh ( "mem.data", mem ) // 将.dat⽂件读⼊寄存器mem中initial $readmemh ( "mem.data", mem, 128, 1 ) // 参数为寄存器加载数据的地址始终2)输出⽂本⽂件:打开输出⽂件⽤?$fopen 例如:integer out_file; // out_file 是⼀个⽂件描述,需要定义为 integer类型out_file = $fopen ( " cpu.data " ); // cpu.data 是需要打开的⽂件,也就是最终的输出⽂本设计中的信号值可以通过$fmonitor, $fdisplay,2. Verilog和Ncverilog命令使⽤库⽂件或库⽬录ex). ncverilog -f run.f -v lib/lib.v -y lib2 +libext+.v //⼀般编译⽂件在run.f中, 库⽂件在lib.v中,lib2⽬录中的.v⽂件系统⾃动搜索使⽤库⽂件或库⽬录,只编译需要的模块⽽不必全部编译3.Verilog Testbench信号记录的系统任务:1). SHM数据库可以记录在设计仿真过程中信号的变化. 它只在probes有效的时间内记录你set probe on的信号的变化.ex). $shm_open("waves.shm"); //打开波形数据库$shm_probe(top, "AS"); // set probe on "top",第⼆个参数: A -- signals of the specific scropeS -- Ports of the specified scope and below, excluding library cellsC -- Ports of the specified scope and below, including library cellsAS -- Signals of the specified scope and below, excluding library cellsAC -- Signals of the specified scope and below, including library cells还有⼀个 M ,表⽰当前scope的memories, 可以跟上⾯的结合使⽤, "AM" "AMS" "AMC"什么都不加表⽰当前scope的ports;$shm_close //关闭数据库2). VCD数据库也可以记录在设计仿真过程中信号的变化. 它只记录你选择的信号的变化.ex). $dumpfile("filename"); //打开数据库$dumpvars(1, top.u1); //scope = top.u1, depth = 1第⼀个参数表⽰深度, 为0时记录所有深度; 第⼆个参数表⽰scope,省略时表当前的scope.$dumpvars; //depth = all scope = all$dumpvars(0); //depth = all scope = current$dumpvars(1, top.u1); //depth = 1 scope = top.u1$dumpoff //暂停记录数据改变,信号变化不写⼊库⽂件中$dumpon //重新恢复记录3). Debussy fsdb数据库也可以记录信号的变化,它的优势是可以跟debussy结合,⽅便调试.如果要在ncverilog仿真时,记录信号, ⾸先要设置debussy:a. setenv LD_LIBRARY_PATH :$LD_LIBRARY_PATH(path for debpli.so file (/share/PLI/nc_xl//nc_loadpli1))b. while invoking ncverilog use the +ncloadpli1 option.ncverilog -f run.f +debug +ncloadpli1=debpli:deb_PLIPtrfsdb数据库⽂件的记录⽅法,是使⽤$fsdbDumpfile和$fsdbDumpvars系统函数,使⽤⽅法参见VCD注意: 在⽤ncverilog的时候,为了正确地记录波形,要使⽤参数: "+access+rw", 否则没有读写权限在记录信号或者波形时需要指出被记录信号的路径,如:tb.module.u1.clk.………………………………………………………………………………………………………关于信号记录的系统任务的说明:在testbench中使⽤信号记录的系统任务,就可以将⾃⼰需要的部分的结果以及波形⽂件记录下来(可采⽤sigalscan⼯具查看),适⽤于对较⼤的系统进⾏仿真,速度快,优于全局仿真。

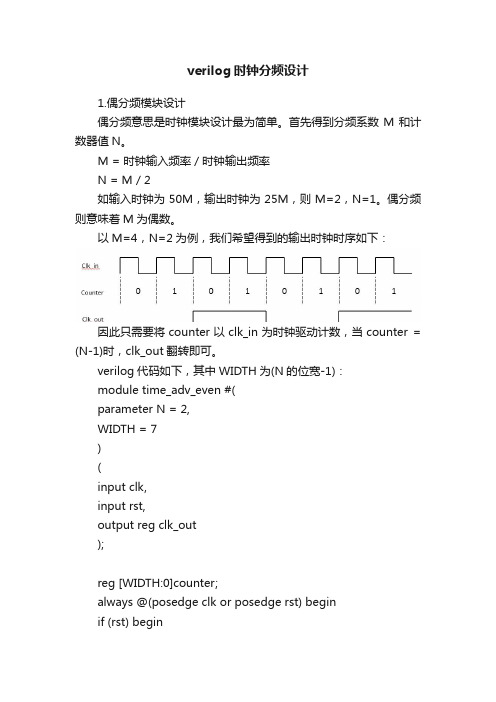

verilog时钟分频设计

verilog时钟分频设计1.偶分频模块设计偶分频意思是时钟模块设计最为简单。

首先得到分频系数M和计数器值N。

M = 时钟输入频率 / 时钟输出频率N = M / 2如输入时钟为50M,输出时钟为25M,则M=2,N=1。

偶分频则意味着M为偶数。

以M=4,N=2为例,我们希望得到的输出时钟时序如下:因此只需要将counter以clk_in为时钟驱动计数,当counter = (N-1)时,clk_out翻转即可。

verilog代码如下,其中WIDTH为(N的位宽-1):module time_adv_even #(parameter N = 2,WIDTH = 7)(input clk,input rst,output reg clk_out);reg [WIDTH:0]counter;always @(posedge clk or posedge rst) beginif (rst) begin// resetcounter <= 0;endelse if (counter == N-1) begincounter <= 0;endelse begincounter <= counter + 1;endendalways @(posedge clk or posedge rst) beginif (rst) begin// resetclk_out <= 0;endelse if (counter == N-1) beginclk_out <= !clk_out;endendendmoduletestbench测试8分频即N=4,ISE仿真结果如下:2.奇分频模块设计奇分频需要通过两个时钟共同得到。

首先得到分频系数M和计数器值N。

M = 时钟输入频率 / 时钟输出频率N = (M-1) / 2如输入时钟为50M,输出时钟为10M,则M=5,N=2。

奇分频则意味着M为奇数。

Verilog仿真文件testbench编写样例

Verilog 仿真文件testbench编写样例`timescale 1ns/100psmodule testbench;localparam DATA_WIDTH = 32;localparam CLK_100_PERIOD = 5;localparam CLK_200_PERIOD = 2.5;localparam SIM_TIME = 150000;localparam ;localparam ;reg clk_100, clk_200;wire clk;assign clk = clk_100;alwaysbeginclk_100 = 0;forever #CLK_100_PERIOD clk_100 = ~clk_100;endalwaysbeginclk_200 = 0;forever #CLK_200_PERIOD clk_200 = ~clk_200;endreg rstn;integer fp_testin;integer fp_matlab_out;integer fp_sim_out;integer fp_outdiff;reg signed [DATA_WIDTH/2-1:0] matlab_in_re, matlab_in_im;reg signed [DATA_WIDTH/2-1:0] matlab_out_re, matlab_out_im;reg signed [DATA_WIDTH/2-1:0] matlab_diff_re, matlab_diff_im;reg signed [DATA_WIDTH/2-1:0] matlab_diff_re2, matlab_diff_im2;reg signed [DATA_WIDTH/2-1:0] max_diff_re, max_diff_im;initial beginmax_diff_re = 0;max_diff_im = 0;rstn = 0;#500rstn = 1;#SIM_TIMEsim_finish();$stop();endtask sim_finish;beginif(fp_testin!=0)$fclose(fp_testin);if(fp_matlab_out!=0)$fclose(fp_matlab_out);if(fp_sim_out)$fclose(fp_sim_out);if(fp_outdiff!=0)$fclose(fp_outdiff);endendtaskinitialbeginfp_testin = 0;fp_testin=$fopen("txt_file/input_data.txt"," r");if(fp_testin==0)begin$display("input_data.txt open failed!"); sim_finish();$stop();endelse begin$fscanf(fp_testin,"%d, %d\n",matlab_in_re,matlab_in_im); endfp_matlab_out = 0;fp_matlab_out =$fopen("txt_file/matlab_out.txt"," r");if(fp_matlab_out==0)begin$display("fp_matlab_out.txt openfailed!");sim_finish();$stop();endelse begin$fscanf(fp_matlab_out,"%d, %d\n",matlab _out_re,matlab_out_im);endfp_sim_out = 0;fp_sim_out =$fopen("txt_file/modelsim_out.txt",&quo t;w");if(fp_sim_out == 0)begin$display("modelsim_out_re.txt openfailed!");sim_finish();$stop();endfp_outdiff = 0;fp_outdiff =$fopen("text_file/outdiff.txt","w& quot;);if(fp_outdiff==0)begin$display("outdiff.txt open failed!"); sim_finish();$stop();endendalways @(posedge clk)beginif(stest_wvalid && stest_wready) //ready to changebeginif(~$feof(fp_testin))$fscanf(fp_testin,"%d, %d\n",matlab_in_re,matlab_in_im); endelsebeginmatlab_in_re <= matlab_in_re;matlab_in_im <= matlab_in_im;endendalways @(posedge clk_100)beginif(mfc_wready && mfc_wvalid)beginmatlab_diff_re <= mfc_wdata_re - matlab_out_re; matlab_diff_im <= mfc_wdata_im - matlab_out_im; matlab_diff_re2 <= matlab_out_re - mfc_wdata_re ; matlab_diff_im2 <= matlab_out_im - mfc_wdata_im ; if(max_diff_re < matlab_diff_re)beginmax_diff_re <= matlab_diff_re;$display("max_diff_re:%dmax_diff_im:%d\n",max_diff_re,max_diff_im); endelse if(max_diff_re < matlab_diff_re2)beginmax_diff_re <= matlab_diff_re2;$display("max_diff_re:%dmax_diff_im:%d\n",max_diff_re,max_diff_im); endif(max_diff_im < matlab_diff_im)beginmax_diff_im <= matlab_diff_im;$display("max_diff_re:%dmax_diff_im:%d\n",max_diff_re,max_diff_im); endelse if(max_diff_im < matlab_diff_im2)beginmax_diff_im <= matlab_diff_im2;$display("max_diff_re:%dmax_diff_im:%d\n",max_diff_re,max_diff_im); end$fscanf(fp_matlab_out,"%d, %d\n",matlab _out_re,matlab_out_im);$fwrite(fp_sim_out, "%d, %d\n",mfc_wdata_re,mfc_wdata_im);$fwrite(fp_outdiff,"%d, %d\n",matlab_diff_re,matlab_diff_i m);endendendmodule。

Verilog中inout类型的数据的使用和testbench仿真写法

Verilog inout 双向口使用和仿真芯片外部引脚很多都使用inout类型的,为的是节省管腿。

一般信号线用做总线等双向数据传输的时候就要用到INOUT类型了。

就是一个端口同时做输入和输出。

inout在具体实现上一般用三态门来实现。

三态门的第三个状态就是高阻' Z'。

当inout端口不输出时,将三态门置高阻。

这样信号就不会因为两端同时输出而出错了,更详细的内容可以搜索一下三态门tri-state的资料.1 使用inout类型数据,可以用如下写法:inout data_inout;input data_in;reg data_reg;//data_inout的映象寄存器reg link_data;assign data_inout=link_data?data_reg:1’bz;//link_data控制三态门//对于data_reg,可以通过组合逻辑或者时序逻辑根据data_in对其赋值.通过控制link_data的高低电平,从而设置data_inout是输出数据还是处于高阻态,如果处于高阻态,则此时当作输入端口使用.link_data可以通过相关电路来控制.2 编写测试模块时,对于inout类型的端口,需要定义成wire类型变量,而其它输入端口都定义成reg类型,这两者是有区别的.当上面例子中的data_inout用作输入时,需要赋值给data_inout,其余情况可以断开.此时可以用assign语句实现:assign data_inout=link?data_in_t:1’bz;其中的link ,data_in_t是reg类型变量,在测试模块中赋值.另外,可以设置一个输出端口观察data_inout用作输出的情况:Wire data_out;Assign data_out_t=(!link)?data_inout:1’bz;else,in RTLinout use in top module(PAD)dont use inout(tri) in sub module也就是说,在内部模块最好不要出现inout,如果确实需要,那么用两个port实现,到顶层的时候再用三态实现。

我的testbench书写总结

占空比为 50%的时钟`timescale 1ns/1ns //定义时间的尺度和精度,其中精度和小树部分挂钩parameter period=4’d10;reg clk; //时钟是输入给DUT的信号必须声明为reg类型initialbeginclk=1’b0; //定义clk的初始状态为低电平forever#( period/2) clk=~clk;endparameter period=4’d10;reg clk;initialbeginclk=1’b0; //定义clk的初始状态为低电平endalways #( period/2) clk=~clk;占空比非50%的时钟信号parameter HIGH_TIME=4,LOW_TIME=6;reg clk;initialbeginclk=1’b0; //定义clk的初始状态为低电平endalwaysbegin# LOW_TIME clk=1’b1;//0~LOW_TIME为低电平# HIGH_TIME clk=1’b0; //从low_time~(low_time+high_time)为高电平end固定数目的时钟信号parameter PulseCount=4,PERIOD=10;reg clk;initialbeginclk=1’b0; //定义clk的初始状态为低电平repeat(PulseCount) //相对于下面的语句重复执行4次#(PERIOD/2) clk=~clk;End//先低电平半个周期,然后再产生两个完整周期的脉冲,结束时clk为低电平parameter Phase_Shift=2;PERIOD=10;reg source_clk;wire derive_clk;//这里是wire好像没有多大用处,要是能用reg就有用了//用initial语句生成源时钟initialbeginclk=1’b0; //定义clk的初始状态为低电平forever#( PERIOD/2) source_clk=~source_clk;EndAssign #Phase_Shift derive_clk=source_clk; //生成派生时钟,要延后2ns2,对于仿真器,reg在没有赋初始值的情况下默认的值为’X’即不定值,而wire的默认值为’Z’即高阻态。

vivadotestbench写法

主题:vivadotestbench编写方法内容:1. 什么是vivadotestbench?vivadotestbench是一个用于编写Verilog的测试台,用于对Verilog 模块进行仿真和验证。

它可以帮助工程师们在Verilog设计的早期阶段进行功能验证和性能评估,以确保设计的稳定性和正确性。

2. vivadotestbench的基本结构vivadotestbench通常包含以下基本结构:模块实例化、时钟和复位初始化、输入数据生成、仿真控制和输出检测。

这些基本结构构成了一个完整的测试台,可以用于对Verilog模块进行全面的验证和测试。

3. vivadotestbench的编写步骤编写vivadotestbench的步骤可以分为以下几个部分:3.1 模块实例化:首先需要实例化待测模块,并且连接时钟、复位信号和输入输出端口。

3.2 时钟和复位初始化:在测试台中需要为待测模块提供时钟信号,并对复位信号进行初始化。

3.3 输入数据生成:根据待测模块的输入端口,生成相应的测试数据,并将其输入到待测模块中。

3.4 仿真控制:控制仿真的开始、暂停和结束,以及执行仿真的时长和步长等。

3.5 输出检测:对待测模块的输出进行检测和比对,以验证其正确性和稳定性。

4. vivadotestbench的常见问题及解决方法在编写vivadotestbench的过程中,可能会遇到一些常见的问题,例如时序约束不准确、测试数据生成不完整、输出检测逻辑错误等。

针对这些问题,可以采取一些解决方法,如优化时序约束、增加测试数据生成的覆盖率、修正输出检测逻辑等。

5. vivadotestbench的优点和应用场景vivadotestbench具有易用性好、灵活性强、功能全面等优点,适用于对Verilog模块进行全面的仿真和验证。

它可以帮助工程师们提高设计的稳定性和正确性,加快设计的上线速度,降低设计的风险和成本。

结论:vivadotestbench是一个强大的Verilog测试台,可以帮助工程师们在Verilog设计的早期阶段进行全面的功能验证和性能评估。

(verilog和vhdl)Testbench编程指南

(verilog和vhdl)Testbench编程指南TestBench编程指南如今数字设计的规模变得越来越庞大,设计的复杂程度也越来越高,这就使得设计的验证变得越来越困难,而且费时费力。

为了应对这种挑战,验证工程师依靠各种验证工具和方法。

对于大型设计,如几百万门的设计,通常采用一整套正式的验证工具。

然而,对于小一些的设计,设计工程师发现往往采用带TestBench的HDL仿真工具是最好的途径。

TestBench已经变成验证高级语言设计的一种标准的方法。

通常,TestBench执行以下任务:z例化设计,使其可测试(DUT-design under test);z通过将测试向量应用到模型来仿真例化后的可测试的设计;z将结果输出到终端,或者输出波形窗口;z将真实的结果和期望的结果进行比较;一般,TestBench采用工业标准的VHDL或者Verilog硬件描述语言来编写。

TestBench调用功能设计,然后仿真。

复杂的测试文件执行附加功能――例如,他们包含逻辑以决定合适的设计激励或者比较真实的结果和期望的结果。

以下章节将讨论一个组织良好的测试文件的组成,以及例举了一个带有自检的测试文件(自动将真实的结果和预期的结果进行比较)。

下图是一个标准的HDL验证的流程。

自从测试文件可以用VHDL或者Verilog编写以来,测试验证流程就可以在平台和供应商的工具交叉进行。

同时,由于VHDL和Verilog都是标准的公用的语言,所以用VHDL或者是Verilog描述的验证可以很简单的被再使用。

图1. HDL验证流程测试文件构成:测试文件可以采用VHDL或者Verilog语言编写。

由于测试文件只是用来仿真的,他们就不被用于综合的RTL语言子集的语法所约束。

相反,所有行为结构都可以被使用。

这样,测试文件可以被写的更通用,更易于维护。

所有的测试文件都包含以下基本内容,如表1。

如上所属,测试文件经常同时包含附加功能,如结果的可视化显示和内建错误检测。

Testbench文件编写纪要(Verilog)

Testbench⽂件编写纪要(Verilog)之前在使⽤Verilog做FPGA项⽬中、以及其他⼀些不同的场合下,零散的写过⼀些练⼿性质的testbench⽂件,开始⼏次写的时候,每次都会因为⼀些基本的东西没记住、写的很不熟练,后⾯写的时候稍微熟练了⼀点、但是整体编写下来⽐较零碎不成体系,所以在这⾥简要记录⼀下⼀般情况下、针对⼩型的verilog模块进⾏测试时所需要使⽤到的testbench⽂件的编写要点。

本⽂主要参考了在⽹上找到的Lattice公司的“A Verilog HDL Test Bench Primer”⼿册中的有关内容。

谢谢!模块实例化、reg&wire声明、initial和always块的使⽤需要测试的模块(Verilog-module)被称为DUT(Design Under Test),在testbench中需要对⼀个或者多个DUT进⾏实例化。

Testbench中的顶层module不需要定义输⼊和输出。

Testbench中连接到DUT instance的输⼊的为reg类型、连接到DUT instance的输出的为wire类型。

对于DUT的inout类型变量,在testbench中需要分别使⽤reg、wire类型的变量进⾏调⽤。

例如,对于下⾯这样⼀个待测试module:module bidir_infer (DATA, READ_WRITE);input READ_WRITE ;inout [1:0] DATA ;reg [1:0] LATCH_OUT ;always @ (READ_WRITE or DATA) beginif (READ_WRITE == 1)LATCH_OUT <= DATA;endassign DATA = (READ_WRITE == 1) ? 2'bZ : LATCH_OUT;endmodule为其设计的testbench⽂件可以是:module test_bidir_ver;reg read_writet;reg [1:0] data_in;wire [1:0] datat, data_out;bidir_infer uut (datat, read_writet);assign datat = (read_writet == 1) ? data_in : 2'bZ;assign data_out = (read_writet == 0) ? datat : 2'bZ;initial beginread_writet = 1;data_in = 11;#50 read_writet = 0;endendmodule和普通的Verilog模块中⼀样、使⽤assign对wire类型的变量进⾏赋值。

verilog testbench语法

Verilog Testbench语法深度解析1. 什么是Verilog Testbench?Verilog Testbench是一种用于验证Verilog硬件描述语言(HDL)设计的测试环境。

它可以模拟设计的功能,并验证其正确性。

Testbench通常包括测试向量生成、时序控制、错误检测和报告等功能,用于对设计的每个功能进行全面的测试。

2. Verilog Testbench的基本结构Verilog Testbench通常包括模块实例化、时钟生成、信号驱动、仿真结束条件等基本结构。

下面我们分别来详细解析一下这些基本结构:2.1 模块实例化模块实例化是将被测试的Verilog设计模块实例化到Testbench中进行仿真。

在Testbench中,需要为被测设计的每个模块实例化一个对应的实例,并连接所需的输入和输出信号。

如果我们要测试一个简单的加法器模块,那么Testbench中就需要实例化这个加法器,并为其提供输入信号。

2.2 时钟生成时钟是数字电路中非常重要的一部分,它的稳定性和频率对设计的正确性有很大影响。

因此在Testbench中,通常需要生成一个时钟信号,并为被测设计提供时钟。

时钟的生成需要考虑到时钟周期、占空比、起始相位等因素。

2.3 信号驱动在Verilog Testbench中,需要为被测设计提供输入信号,并对其进行驱动。

这些输入信号可以是测试用的模拟信号,也可以是从文件读取的数据。

对于复杂的设计,输入信号的生成可能需要一定的算法和规则。

2.4 仿真结束条件仿真结束条件是指在Testbench中指定了仿真运行的结束条件。

通常情况下,仿真会在满足了所有测试用例,并且通过了所有检查点之后结束。

在Testbench中需要注意设置好仿真的结束条件,以避免不必要的浪费。

3. Verilog Testbench的个人观点对于Verilog Testbench,我个人认为它是Verilog设计中不可或缺的一部分。

verilog testbench例子

Verilog Testbench例子Verilog是一种硬件描述语言,用于描述数字系统。

在Verilog中,testbench是用于验证设计的一部分。

它是一个独立的模块,用于提供输入信号并验证设计的输出信号。

在本文中,我们将介绍一个Verilog testbench的例子,以帮助读者更好地理解Verilog设计和验证的流程。

1. 确定测试目标在编写Verilog testbench之前,首先需要确定测试的目标。

这包括对设计的功能和性能的需求,并确定测试中需要关注的重点。

测试目标的确定将有助于后续测试用例的编写和验证结果的分析。

2. 编写testbench框架testbench通常包括以下几个部分:- 时钟信号生成器:用于生成时钟信号,驱动设计的时序逻辑。

- 信号生成器:用于生成各种输入信号,模拟实际工作状态下的输入情况。

- 仿真模型:绑定被测设计的接口,将输入信号传递给设计,并验证设计的输出信号是否符合预期。

下面是一个简单的testbench框架的例子:```verilog`timescale 1ns / 1nsmodule tb_example;// Define signalsreg clk;reg rst;reg [7:0] data_in;wire [7:0] data_out;// Instantiate design under test (DUT) example_dut dut(.clk(clk),.rst(rst),.data_in(data_in),.data_out(data_out));// Clock generatoralways#5 clk = ~clk;// Stimulus generatorinitial beginrst = 1;#10 rst = 0;#20 data_in = 8'hFF;#20 data_in = 8'h00;// Add more stimulus hereend// Check outputsalways (posedge clk) begin// Add output check hereendendmodule```3. 编写测试用例编写测试用例是testbench编写的关键步骤之一。

testbench如何产生波形

编写TestBench的目的就是将激励施加一个设计(Design),观察它的响应,并将这个响应和期望的结果进行比较。

下面将说明如何生成精确的时钟信号。

下面是用Verilog 编写的两个程序用来生成100Mhz DutyCycle为50%的Clock。

例1 使用1 和0 显示的赋值:`timescale 1ns / 100psreg clk;alwaysbegin#5;clk = 1'b0;#5;clk = 1'b1;end例2:使用clk = ~clk的语句`timescale 1ns / 100psreg clk;initialbeginclk = 1'b0;endalwaysbegin# 5 clk = ~clk;end例1和例2 都生成正确的Clock,例1的方法使用1和0 显示赋值会更可靠,另外可以更好地控制Clock的初始相位,同样可以用来设计出不同DutyCycle的Clock。

例2使用clk = ~clk的语句时,将依赖Clock信号的初始值,而不是默认的1‘bx,如何没有给clk赋初值,试想将1’bx取反得到的是什么?将不能产生Clock。

1 整形除法可以加快时钟的产生同时可能造成截断错误当使用Verilog产生正确的Clock 或者波形的时候,必须选择适当的时延单位和时延精度,这样才能将波形的边沿设置在准确的位置,当使用类似Cycle/2的表达式时,为了计算延时,必须确定整数运算不会截断变量的小数部分。

如例3 我想产生的Clock的period 为15 怵,但我得到的14ns的信号,因为整数除法将小数部分截断了。

例3:激励产生中的截断错误timescale 1ns / 1nsmodule TestBench;reg clk;parameter Cycle = 15;alwaysbegin#(Cycle/2) ; // Interger divisionclk = 1'b0;#(Cycle/2) ; // Interger divisionclk = 1'b1;endendmodule2 。

Verilog-HDL-如何编写TESTBENCH

08:292主要内容Verilog 对验证的支持系统函数和系统任务如何编写模块的TESTBENCH08:293系统任务和系统函数是Verilog中预先定义好的,用于调试和编译预处理的任务或函数。

以$开头,用于控制和检测仿真模拟过程主要有:(1)用于获取仿真时间的系统函数(2)支持文本输出(检测信号、显示信号)的系统任务(3)用于文件输入、输出操作的系统任务(4)用于暂停和退出仿真的系统任务(5)用于产生随机数的系统任务08:294获取当前仿真时间的系统函数$time,$realtime,$stime:返回当前仿真时间。

$time返回一个64位的整数时间值,$realtime返回的结果是实数时间值,是更为精确的仿真时间 $stime返回一个32位整数时间值。

(对大于232的时间,返回模232的值。

使用它可以节省显示及打印空间。

)这些函数的返回值使用调用模块中`timescale 定义的模块仿真时间尺度为单位08:295例..\..\verilog_example\Dec2x4.v..\..\verilog_example\Dec_Test.v # At time 0, input is 0,0,0, output is,xxxx # At time 4, input is 0,0,0, output is,1111# At time 10, input is 0,0,1, output is,1111# At time 13, input is 0,0,1, output is,0111# At time 20, input is 1,0,1, output is,0111# At time 23, input is 1,0,1, output is,0101# At time 26, input is 1,0,1, output is,1101# At time 30, input is 1,1,1, output is,1101# At time 33, input is 1,1,1, output is,1100# At time 36, input is 1,1,1, output is,1110# At time 40, input is 0,1,1, output is,1110# At time 44, input is 0,1,1, output is,1011# At time 50, input is 0,0,1, output is,1011# At time 54, input is 0,0,1, output is,011108:296Verilog 支持的文本输出的系统任务显示任务:用于仿真模拟期间显示信息。

如何编写Testbench

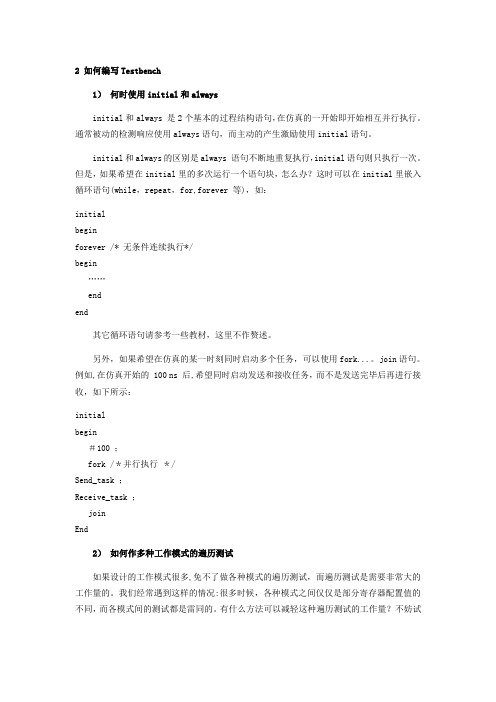

2 如何编写Testbench1)何时使用initial和alwaysinitial和always 是2个基本的过程结构语句,在仿真的一开始即开始相互并行执行。

通常被动的检测响应使用always语句,而主动的产生激励使用initial语句。

initial和always的区别是always 语句不断地重复执行,initial语句则只执行一次。

但是,如果希望在initial里的多次运行一个语句块,怎么办?这时可以在initial里嵌入循环语句(while,repeat,for,forever 等),如:initialbeginforever /* 无条件连续执行*/begin……endend其它循环语句请参考一些教材,这里不作赘述。

另外,如果希望在仿真的某一时刻同时启动多个任务,可以使用fork...。

join语句。

例如,在仿真开始的 100 ns 后,希望同时启动发送和接收任务,而不是发送完毕后再进行接收,如下所示:initialbegin#100 ;fork /*并行执行*/Send_task ;Receive_task ;joinEnd2)如何作多种工作模式的遍历测试如果设计的工作模式很多,免不了做各种模式的遍历测试,而遍历测试是需要非常大的工作量的。

我们经常遇到这样的情况:很多时候,各种模式之间仅仅是部分寄存器配置值的不同,而各模式间的测试都是雷同的。

有什么方法可以减轻这种遍历测试的工作量?不妨试试for循环语句,采用循环变量来传递各种模式的配置值,会帮助减少很多测试代码,而且不会漏掉每一种模式.initialbeginfor ( i = 0 ; i 〈 m ; i = i + 1 ) /*遍历模式1至模式m*/for ( j = 0 ; j < n ; j = j +1 ) /*遍历子模式1至子模式n */begincase ( j ) /* 设置每种模式所需的配置值 */0 : 配置值= a ;1 : 配置值= b ;2 : 配置值= c ;……endcase/*共同的测试向量*/endend3) 如何加速问题定位过程在这部分里,通过一些实际例子,介绍在出现问题时如何借助 testbench 加快问题的定位过程。