基于数字锁相环的同步倍频器设计

基于数字锁相环4046的变频电路的设计

四 、结 语

图 4 4I}46的引脚 图

图 5 74LS191的 引脚 图

3.2汁数器 191的功能及T作原理

191 为 可 预置 的 4位 二 进 制 同 步 加 /减 计 数 器 ,共 有

54191H4191,54Lc ̄191/74LS191两 种线 路 结构 形 式 。191的 预

此 锁相 环 的 作频 率不 高 ,对 环路 的入锁 时间 的要求 也

小商 ,可选 用最简单 的一 阶 RC低通滤波器 ,滤波器 的截 止角

频 率

1

W RFCF

式 (2-3)

取 Rf=l0fKQ).( F0.1(u0,系统 比较 稳 定 ,9脚 的杂波 比

较 小

DOD1D2D3=I1l】时,Ⅳ =1,Ji Jo 由此可 见 ,当通过一级 l9l时 ,合 成器生成 的频率 范同为 , /o~16 频 率 间 隔为 ,o。如 以 上两 图 知,191(1)的 D。D D D l1 l0, 倍 频 倍 数 同 定 为 8倍 . 而 191(2) 的 D D D D,管脚 分别接 了四个拨码 开关 ,即倍频 的倍 数可 以手动 调 节 ,这 样整个 频率 合成 器 的输 出频 率范 围 为 8 ̄16=128倍 ,

SYS PRACTICE 墨笙壅壁 > >

基于数字锁相环 4046的变频电路的设计

◆ 王 丹 琦 韩 振 华 王 静

摘 要 :本设 计是基 于数 字 锁相环4()46的 变频 电路 ,用锁 相环 4046实现任 意信 号 的 变频 电路,满足 不 同电压 、不 同频 率 的信号 的倍频 意义在 于本设 计 可以 完成分/倍频 器所 难以 完成的任 意数 字的 变 频 ,且 简单 、节 能 设计 将分 为数 字锁相环 (DPLL)、数控振 荡器 (DCO )模块 、除 N分频 和乘M 倍频 模块 锁相 倍 (分 )频是将 一种频 率 变换 为 另一种频 率 ,即可将 两种 不 同的频 率互相转换 用锁 相环 实现 的频率 合成 器,既有频 率稳定度 高 又有改 换频 率方便的优 点。

锁相环实现倍频的原理是什么?锁相环的组成及倍频的三种方法解析

锁相环实现倍频的原理是什么?锁相环的组成及倍频的三种方法解析锁相环的组成部分锁相环主要由压控振荡器,鉴相器,低通滤波器,以及参考频率振荡器组成。

压控振荡器主要实现电压与频率的变换,鉴相器主要实现把压控振荡器的频率与参考频率振荡器的频率进行比较。

低通滤波器主要是滤除信号中的高频分量,参考频率振荡器提供参考频率。

锁相环是如何实现倍频的?原理是什么?当锁相环处于锁定状态时,鉴相器(PD)的两输入端一定是两个频率完全一样但有一定相位差的信号。

如果它们的频率不同,则在压控振荡器(VCO)的输入端一定会产生一个控制信号使压控振荡器的振荡频率发生变化,最终使鉴相器(PD)的两输入信号(一个是锁相环的输入信号Vi,一个是压控振荡器的输出信号V o)的频率完全完全一样则环路系统处于稳定状态。

倍频电路

基于此原理,如果在VCO之后,加一个分频器(n分频),在反馈回锁相环输入端,此时输出信号为原来的n倍。

倍频的三种方法1、傅里叶法

这是一种最简单的模拟信频方式及它采用了傅里叶级数。

每一个周期性的信号能定义为一个基频及它的谐波部分的和。

如果你变换振荡器的正弦波输出为方波,那么你能用下面的关系式:

下一步你必须选择这正确的次谐波。

你用一个带通滤波器去衰减其它部分来选择要的部分。

注意:此法仅适用于低频。

2、锁相环法

这是一种最简单的倍频方法。

在这个方法中,输出频率不是直接是基准频率的倍频,但出。

一种基于软件锁相环实现位同步的设计的研究报告

一种基于软件锁相环实现位同步的设计的研究报告软件锁相环实现位同步的设计研究本文旨在探讨软件锁相环实现位同步的设计。

位同步是一种用于建立数据通信中信号位数、时隙长度、传输位比特等各参数之间的精确关系。

为了实现位同步,要解决的悬而未决的难题是如何保证发送和接收器能够在同一个位置接收信号。

在此基础上,本文提出了软件锁相环实现位同步的设计方法。

软件锁相环实现位同步的设计是基于引入一个专门的单位——相环(Phase-Locked Loop, PLL)来实现信号位定位。

相环有两个重要部分:解调器和控制器。

解调器用于接收和解调传入信号,并将解调结果作为输入发送给控制器;控制器则对传入信号进行分析,根据结果控制发出的信号的频率,以保持发出和接收信号在同一个位置上。

在实际设计过程中,首先要采用基于正交分频复用的方法,通过使用正交分频器将位率降低至接近信号位定位所需要的频率。

然后,可以采用相环或其他方法对位率进行调节,以确保比特精度不会受到影响。

此外,为了实现软件锁相环实现位同步的设计,可以利用软件中的环路控制技术,通过设置位率阈值,实现自适应控制。

在低位率下,信号位定位精度会受到较大干扰,机器可以通过调整频率来对应调节;当位率超过阈值时,机器会采取相反的调整方法来保持比特精度。

总之,软件锁相环实现位同步的设计有助于提高信号位定位和传输比特精度,可以保证信号传输可靠准确。

本文仅简单介绍了软件锁相环实现位同步的设计,更详细的研究需要有关专业人员深入研究。

相关数据分析本文旨在对相关数据进行分析,从而获得可信的结论。

首先,我们收集了若干组值得信赖的数据(X1, X2, ... Xn),通过合理的方法分析这些数据,将其赋予特定的意义。

首先,进行相关分析来确定X1,X2,…Xn之间的关系。

为此,使用残差分析法对相关数据进行处理,从而得出X1,X2,…Xn 之间的拟合函数,确定X1,X2,…Xn之间的关系。

随后,使用变量分析法开展统计分析,以找出X1,X2,…Xn之间的相关性。

毕业论文基于锁相环路的调频鉴频器.doc

苏州工业园区职业技术学院毕业设计(论文)2005 届课题名称:基于锁相环路的调频鉴频器专业名称:工业电子姓名:周培培学号:200200100班级:电子02305指导教师:李红益2005年05月30日苏州工业园区职业技术学院毕业设计(论文)任务书系部:电子工程系锁相环路是一个闭环的自动相位控制系统。

它在现代电子系统中有广泛的应用。

这次毕业设计我介绍了调频、鉴频电路,锁相环电路,常用的4046芯片。

在这篇文章中我主要分析了锁相调频电路和锁相鉴频电路,这两个电路都用了4046这个芯片,文章中我也仔细的介绍了4046的引脚和内部原理框图。

关键词:锁相环调频鉴频CD4046一、引言 (1)二、调频、鉴频的原理 (1)(一)调频原理 (1)(二)鉴频原理 (2)三、锁相环电路 (2)(一)锁相环路主要特点 (2)(二)锁相环路的跟踪特性 (3)(三)锁相环路的工作原理 (3)(四)锁相环路的基本特性 (3)四、CD4046的工作原理 (3)(一)引脚功能 (3)(二)CD4046内部电原理框图 (4)五、锁相调频、鉴频电路 (6)(一)锁相调频电路 (6)(二)锁相鉴频电路 (7)结束语 (8)参考文献 (9)一、引言锁相环路(PLL)和AGC、AFC电路一样,也是一种反馈控制电路。

它是一种相位误差控制系统,是将考信号与输出信号之间是相位进行比较,产生相位误差电压来调整输出信号的相位,以达到同频的状态下。

两个信号之间的稳定相差亦可做得很小。

锁相环路早期应用于电视接收机的同步系统,使电视图象的同步性能得到了很大的改善。

20世纪50年代后期,随着空间技术的发展,锁相技术用于接收来自空间的微弱信号,显示了很大的优越性,它能把深埋在噪声中的信号(噪声比约-10~-30dB)提取出来。

因此,锁相环路技术得到迅速发展。

到了60年代中、后期,随着微电字技术的发展,集成锁相环路也应运而生,因此,其应用范围越来越宽,在雷达、制导、导航、遥控、遥测、通信、仪器、测量、计算机乃至一般工业都有不同程度的应用,遍及整个电子技术领域,而且正朝着多用途,集成化,系列化,高性能的方向进一步发展。

锁相环原理以及倍频分频实现

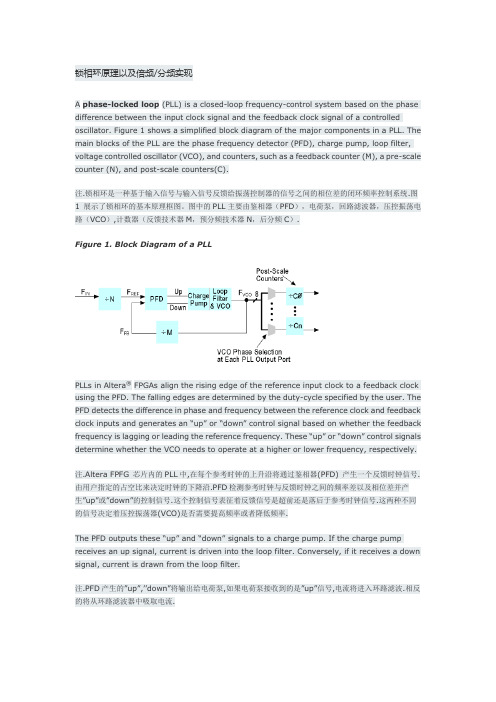

锁相环原理以及倍频/分频实现A phase-locked loop (PLL) is a closed-loop frequency-control system based on the phase difference between the input clock signal and the feedback clock signal of a controlled oscillator. Figure 1 shows a simplified block diagram of the major components in a PLL. The main blocks of the PLL are the phase frequency detector (PFD), charge pump, loop filter, voltage controlled oscillator (VCO), and counters, such as a feedback counter (M), a pre-scale counter (N), and post-scale counters(C).注.锁相环是一种基于输入信号与输入信号反馈给振荡控制器的信号之间的相位差的闭环频率控制系统.图1 展示了锁相环的基本原理框图。

图中的PLL主要由鉴相器(PFD),电荷泵,回路滤波器,压控振荡电路(VCO),计数器(反馈技术器M,预分频技术器N,后分频C).Figure 1. Block Diagram of a PLLPLLs in Altera® FPGAs align the rising edge of the reference input clock to a feedback clock using the PFD. The falling edges are determined by the duty-cycle specified by the user. The PFD detects the difference in phase and frequency between the reference clock and feedback clock inputs and generates an “up” or “down” control signal based on whether the feedback frequency is lagging or leading the reference frequency. These “up” or “down” control signals determine whether the VCO needs to operate at a higher or lower frequency, respectively.注.Altera FPFG 芯片内的PLL中,在每个参考时钟的上升沿将通过鉴相器(PFD) 产生一个反馈时钟信号.由用户指定的占空比来决定时钟的下降沿.PFD检测参考时钟与反馈时钟之间的频率差以及相位差并产生”up”或”down”的控制信号.这个控制信号表征着反馈信号是超前还是落后于参考时钟信号.这两种不同的信号决定着压控振荡器(VCO)是否需要提高频率或者降低频率.The PFD outputs these “up” and “down” signals to a charge pump. If the charge pump receives an up signal, current is driven into the loop filter. Conversely, if it receives a down signal, current is drawn from the loop filter.注.PFD产生的”up”,’’down”将输出给电荷泵,如果电荷泵接收到的是”up”信号,电流将进入环路滤波.相反的将从环路滤波器中吸取电流.The loop filter converts these signals to a control voltage that is used to bias the VCO. Based on the control voltage, the VCO oscillates at a higher or lower frequency, which affects the phase and frequency of the feedback clock. If the PFD produces an up signal, then the VCO frequency increases. A down signal decreases the VCO frequency. The VCO stabilizes once the reference clock and the feedback clock have the same phase and frequency. The loop filter filters out jitter by removing glitches from the charge pump and preventing voltage over-shoot.注.环路滤波将”up””down”信号准换为压控信号传递给压控振荡器.并控制压控振荡器的振荡频率.如果PFD产生的是”up”信号,VCO将提高振荡频率,相反减少振荡频率.直到参考时钟信号与反馈时钟信号具有相同的振荡频率以及相位. 环路滤波器将滤除电荷泵产生的噪声振荡并且防止电压过载.When the reference clock and the feedback clock are aligned, the PLL is considered locked. To注.当参考频率与反馈频率一致的时候,PLL被称为锁定.A divide counter (M) is inserted in the feedback loop to increase the VCO frequency above the input reference frequency. VCO frequency (F VCO) is equal to (M) times the input reference clock (F REF). The PFD input reference clock (F REF) is equal to the input clock (F IN) divided by the pre-scale counter (N). Therefore, the feedback clock (F FB) applied to one input of the PFD is locked to the F REF that is applied to the other input of the PFD. The VCO output feeds post-scale counters which allow a number of harmonically related frequencies to be produced within the PLL.注.反馈回路上插入一个除法器(M)可以在参考时钟频率的基础上实现M倍频.PFD的输入频率等于输入频率/N.The output frequency of the PLL is equal to the VCO frequency (F VCO) divided by thepost-scale counter (C).In the form of equations:∙F REF = F IN / N∙F VCO = F REF × M = F IN × M/N∙F OUT = F VCO / C = (F REF × M) / C = (F IN × M) / (N × C)where:∙F VCO = VCO frequency∙F IN = input frequency∙F REF = reference frequency∙F OUT = output frequency∙M = counter (multiplier), part of the clock feedback path∙N = counter (divider), part of the input clock reference pathC = post-scale counter (divider)。

可编程倍频器设计方案

姓名:罗毅学号:06200318

基于锁相环的可编程倍频器设计方案

一、锁相环部分电路设计

该部分选用CD4046锁相环,该锁相环采用CMOS电路,最高工作频率为1MHz以上。

整个电路由PD1 、PD2 、压控振荡器、源极跟随器和一个5V左右的齐纳二极管等几部分组成,只需在外部加相应的外围电路即可构成所需的锁相环路。

其中,PD1为异或门鉴相器,无鉴频功能;环路的捕捉带极小;PD2为三态数字鉴相器。

这两个鉴相器有公共的信号输入端(14端)(ui(t))和反馈输入端(3端) ( uf( t) ),在此选用PD2 。

环路滤波器接在13端( ud( t) ) ;9端是VCO 的控制端(uc(t)),4端是输出端(uo(t));定时电容C2接在6、7端;接在11端的电阻R3可以起到改变振荡频率的作用。

锁相环部分电路

二、分频器部分电路设计

该部分利用单片机的计数器T0来实现分频,CD4046的4端与单片机内部计数器接口T0相连,接收锁相环输出的信号。

通过软件编程设置计数器的初始值实现分频的功能。

三、单片机控制部分

该部分包括键盘和液晶显示,通过键盘输入倍频系数,由单片机控制输出倍频后的信号。

总体电路原理图如下:

可编程倍频器电路原理图

附:电路元件清单

AT89C51 1片

CD4046 1片

芯片插座DIP40一片DIP16一片

按键开关16个

晶振12MHz 1个

电阻、电容、导线若干。

锁相环原理以及倍频分频实现

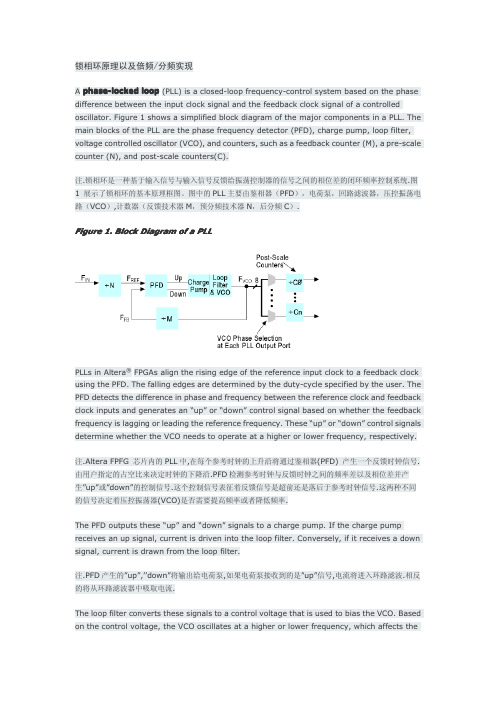

锁相环原理以及倍频/分频实现A phase-locked loop(PLL)is a closed-loop frequency-control system based on the phase difference between the input clock signal and the feedback clock signal of a controlled oscillator.Figure1shows a simplified block diagram of the major components in a PLL.The main blocks of the PLL are the phase frequency detector(PFD),charge pump,loop filter, voltage controlled oscillator(VCO),and counters,such as a feedback counter(M),a pre-scale counter(N),and post-scale counters(C).注.锁相环是一种基于输入信号与输入信号反馈给振荡控制器的信号之间的相位差的闭环频率控制系统.图1展示了锁相环的基本原理框图。

图中的PLL主要由鉴相器(PFD),电荷泵,回路滤波器,压控振荡电路(VCO),计数器(反馈技术器M,预分频技术器N,后分频C).Figure1.Block Diagram of a PLLPLLs in Altera®FPGAs align the rising edge of the reference input clock to a feedback clock using the PFD.The falling edges are determined by the duty-cycle specified by the user.The PFD detects the difference in phase and frequency between the reference clock and feedback clock inputs and generates an“up”or“down”control signal based on whether the feedback frequency is lagging or leading the reference frequency.These“up”or“down”control signals determine whether the VCO needs to operate at a higher or lower frequency,respectively.注.Altera FPFG芯片内的PLL中,在每个参考时钟的上升沿将通过鉴相器(PFD)产生一个反馈时钟信号.由用户指定的占空比来决定时钟的下降沿.PFD检测参考时钟与反馈时钟之间的频率差以及相位差并产生”up”或”down”的控制信号.这个控制信号表征着反馈信号是超前还是落后于参考时钟信号.这两种不同的信号决定着压控振荡器(VCO)是否需要提高频率或者降低频率.The PFD outputs these“up”and“down”signals to a charge pump.If the charge pump receives an up signal,current is driven into the loop filter.Conversely,if it receives a down signal,current is drawn from the loop filter.注.PFD产生的”up”,’’down”将输出给电荷泵,如果电荷泵接收到的是”up”信号,电流将进入环路滤波.相反的将从环路滤波器中吸取电流.The loop filter converts these signals to a control voltage that is used to bias the VCO.Based on the control voltage,the VCO oscillates at a higher or lower frequency,which affects thephase and frequency of the feedback clock.If the PFD produces an up signal,then the VCO frequency increases.A down signal decreases the VCO frequency.The VCO stabilizes once the reference clock and the feedback clock have the same phase and frequency.The loop filter filters out jitter by removing glitches from the charge pump and preventing voltage over-shoot.注.环路滤波将”up””down”信号准换为压控信号传递给压控振荡器.并控制压控振荡器的振荡频率.如果PFD产生的是”up”信号,VCO将提高振荡频率,相反减少振荡频率.直到参考时钟信号与反馈时钟信号具有相同的振荡频率以及相位.环路滤波器将滤除电荷泵产生的噪声振荡并且防止电压过载.When the reference clock and the feedback clock are aligned,the PLL is considered locked.To注.当参考频率与反馈频率一致的时候,PLL被称为锁定.A divide counter(M)is inserted in the feedback loop to increase the VCO frequency above the input reference frequency.VCO frequency(F VCO)is equal to(M)times the input reference clock(F REF).The PFD input reference clock(F REF)is equal to the input clock(F IN)divided by the pre-scale counter(N).Therefore,the feedback clock(F FB)applied to one input of the PFD is locked to the F REF that is applied to the other input of the PFD.The VCO output feeds post-scale counters which allow a number of harmonically related frequencies to be produced within the PLL.注.反馈回路上插入一个除法器(M)可以在参考时钟频率的基础上实现M倍频.PFD的输入频率等于输入频率/N.The output frequency of the PLL is equal to the VCO frequency(F VCO)divided by thepost-scale counter(C).In the form of equations:•F REF=F IN/N•F VCO=F REF×M=F IN×M/N•F OUT=F VCO/C=(F REF×M)/C=(F IN×M)/(N×C)where:•F VCO=VCO frequency•F IN=input frequency•F REF=reference frequency•F OUT=output frequency•M=counter(multiplier),part of the clock feedback path•N=counter(divider),part of the input clock reference path•C=post-scale counter(divider)。

基于数字锁相环的同步倍频器设计

一、主要内容与要求1.掌握应用电子设计自动化(EDA)技术设计电子系统的方法;2.采用超高速集成电路硬件描述语言(Verilog)设计一种基于数字锁相环的倍频器;3.重点设计数字环路滤波器和数控振荡器;4.利用计算机仿真技术进行验证;5.阅读并翻译3000单词以上的英文资料。

二、主要技术要求1.系统能够实现输出信号为输入信号的2n倍频;2.改变系统参数可以得到不同的倍频信号,且始终能够使输出信号与输入信号保持同步;3.用Verilog语言编写设计程序,利用计算机仿真予以验证。

三、研究方法1.在查阅大量技术资料的基础上,进行设计方案的比较;2.确定全数字锁相环系统的设计方案;3.采用自顶向下的设计方法,进行系统模块的划分,并确定用Verilog设计各功能模块的算法;4.编写系统设计程序,并进行仿真验证,经过反复修改使电路系统达到设计要求。

四、工作进度安排1.2012年12月学习掌握Verilog设计技术,收集和整理与毕业设计有关的资料;2.2013年1月在分析和整理资料的基础上写开题报告,确定设计方案和研究技术路线;3.2013年3月完成环路滤波器和数控振荡器的设计与仿真;4.2013年4月完成全数字倍频器的系统设计与仿真;5.2013年5月撰写毕业设计说明书和准备毕业答辩稿;6.2013年6月初毕业答辩。

指导教师南华大学本科生毕业设计(论文)开题报告南华大学电气工程学院毕业设计摘要:随着数字通信系统的高速发展,数字锁相环的应用也越来越广。

由于非线性电阻构成的倍频器,倍频噪声较大,而为了满足倍频噪声小的的需求,本文通过应用EDA技术设计电子系统的方法,采用硬件描述语言Verilog,设计了一种基于数字锁相环的同步倍频器系统。

该系统经过Quartus II软件的仿真以及验证,实现了输出信号为输入信号的2^n倍频的功能,改变系统参数也可以得到不同倍频信号,而且始终能使输出信号与输入信号保持同步。

故该系统能够减少因倍频次数高而产生的倍频噪声,但有时会出现相位失锁等问题。

数字锁相环在倍频电路中的应用

数字锁相环在倍频电路中的应用【摘要】:文章简述了锁相环的发展和组成,重点介绍了数字锁相环PE3236的内部组成,并分析了利用PE3236、二分频器、四分频器以及环路滤波器、压控振荡器组成的倍频电路,并且对环路滤波器和环路特性作了简要说明,从而给出了一种实现了频率合成的更加优化的方法。

【关键词】:PE3236; 单片数字锁相环(PLL); 环路滤波器(LF); 压控振荡器(VCO); 单片分频器中图分类号:TN742.1文献标识码:A 文章编号:1002-6908(2008)0110034-011. 引言锁相环最初用于改善电视接收机的行同步和帧同步,以提高抗干扰能力。

锁相原理在数学方面,早在30年代无线电技术发展的初期就已经出现。

1932年贝尔赛什(Bellescize)第一次公开发表了锁相环路的数学描述,用锁相环路提取相干载波来完成同步检波。

到了40年代电视接收机中的同步扫描电路中开始广泛的应用锁相技术,使电视图像的同步性能得到很大改善。

进入50年代,随着空间技术的发展,由杰斐(Jaffe)和里希廷(Rechtin)利用锁相环路作为导弹信标的跟踪滤波器获得成功,并首次发表了包含噪声效应的锁相环路线性理论分析的文章,同时解决了锁相环路最佳化设计问题。

在60年代,维特比(Viterbi)研究了无噪声锁相环路的非线性问题,并发表了”相干通信原理”一书。

到了70年代林特塞(Lindscy)和查里斯(Charles)进行了由噪声的一阶、二阶及高阶锁相环路的非线性理论分析,并做了大量实验以充实理论分析。

2. 基本原理锁相技术是实现相位自动控制的一门学科,锁相环是能使受控振荡器的频率和相位均与输入信号保持确定关系的闭环电子电路。

它由鉴相器、环路滤波器和压控振荡器组成。

鉴相器用来鉴别输入信号Ui与输出信号Uo之间的相位差,并输出误差电压Ud 。

Ud 中的噪声和干扰成分被低通性质的环路滤波器滤除,形成压控振荡器(VCO)的控制电压Uc。

数电实验锁相环倍频器

实验11 锁相环倍频器121180166 赵琛一、实验目的1学习数字锁相环集成电路,锁相环倍频器的基础知识。

2根据数字锁相环74HC/HCT4046的数据手册,分析、设计数字锁相环倍频器,学习根据集成电路数据手册分析、设计电路的的一般方法。

二、实验器材双踪示波器、方波信号发生器、数字万用表、CD4046、74LS47。

三、实验预习、研究、思考题1 锁相环锁定与失锁的标志是什么?如何用示波器来判断?答:锁定的标志是输出信号和输入信号频率相同,仅有相位的不同。

用示波器判断,可以调节输入电压,若输出信号与输入信号相位差不变化,频率一致,即两信号相对稳定,则完成锁相。

2 锁相环的锁定范围主要由哪些因素决定?答:由CD4046技术手册可知,期锁定范围由R1、R2、C1三个主要参数决定。

具体值要看这三个参数的关系图。

其中,C1、R1决定中心频率,R2、C1决定最低频率,R1、R2决定最高频率和最低频率比值。

3 CD4046有两个相位比较器,有何区别?74HC4046有3个相位比较器,有何区别?答:对于CD4046,两个相位比较器分别为异或相位比较器(NOR )即PC1,其相位锁定范围为0——180°;相位——频率比较器(PFD ),即PC2,其相位锁定范围为-360°——360°。

其中PC1比较容易锁定,但是要求输入信号50%占空比,或者是波形较好小信号。

若条件达到尽可能用PC1,否则使用PC2已达到稳定的锁相。

一般多用PC2,比较容易满足条件。

对于74HC4046,除去CD4046已有的两个触发器外,还有第三个触发器 JK 触发相位比较器(JK ),即PC3,其相位锁定范围是0——360°。

选择方式与CD4046类似。

4 试推导有一个零点的二阶系统的单位阶跃响应的时域表达式和超调量的表达式。

答:对于有一个零点的二阶系统,其H(s)=bas s b as 2+++,其中a=2ζω,b=ω2,这是一个冲激响应。

单片数字锁相倍频电路的设计与实现

= Tin N

=

M N

ççèæ

12 f clk

÷÷øö

刘俊丰:硕士研究生

(3) 利用定时器 T1 实现倍频方波信号输出:置定

电 话 :010-62132436 ,62192616(T/F ) 《 嵌入式系统应用精选 200 例》

中国自控网:http://www.a utocontrol.cn

邮局订阅号:82-946 120 元 / 年 - 153 -

INT0 上升沿到来之际,启动定时器 T0 开始对内部时 钟(振荡频率的 1/12)进行计数,在下一个 INT0 上升 沿到来之后,关闭定时器 T0,读取计数值 M,并启动下 一次定时过程。输入信号周期为:

Tin

=

M ççèæ

12 f clk

÷÷øö

(2) 确定倍频输出信号周期,设倍频数为 N,则

Tout

(投稿日期:2004.12.20) (修稿日期:2004.12.28)

欢迎订阅 欢迎刊登广告

中国自控网:http://www.a utocontrol.com.cn

- 154 - 120 元 / 年 邮局订阅号:82-946

电 话 :010-62132436 ,62192616(T/F ) 《 P LC 技术应用 200 例》

上述过程循环执行,不断测量当前输入信号周 期,及时更新倍频定时器 T1 的计数初值,即可实现倍 频输出信号频率随输入信号频率的变化而相应变化, 但保持倍频数不变。为了保证倍频的正确实现,系统 振荡频率 fclk、输入信号频率 fin 和分频数 N 之间应满足 下式关系:

10 £ fclk ´ 1 £ 256 fin 2N

(西安理工大学)刘 俊 丰 同 向 前

基于数字锁相环的温控变频电路设计

基于数字锁相环的温控变频电路设计谢完成(娄底职业技术学院 湖南娄底 417000)摘 要:CC4046集成电路锁相环采用RC 型压控振荡器,外接RC 作为充放电元件,电路简单、成本低廉、实用价值大,可广泛应用于广播电视系统,各种通信系统,以及频率合成,自动控制及时钟同步等技术领域。

利用数字集成锁相环组成温控变频电路可以克服常见温控系统可靠性低、抗干扰能力差的缺点,为温度的精确测量及需要进行温度检测控制的设备提供了一种可行的电路设计方案。

关键词:数字锁相环;相位同步;温度控制;频率变换中图分类号:TN752 文献标识码:B 文章编号:10042373X (2008)022046202Design of T emperature Frequency Conversion Circuit B ased on Digital Phase Locked LoopXIE Wancheng(Loudi Vocational and Technical College ,Loudi ,417000,China )Abstract :The CC4046integrated circuit phase locked loop uses the RC Voltage Controlled Oscillator (VCO ),the exteriorconjunction RC component of charge and discharge ,the electric circuit is simple ,the cost is inexpensive ,the practical value is big ,and widely used in the broadcast television system ,several communications system ,frequency synthesis system ,automatic control and clock synchronization system.It overcomes these shortcoming such as low reliability and bad anti 2interference to make use of integrated circuit phase locked loop constitutes to temperature f requency conversion circuit.For the accurate dia 2graph of temperature and need to carry on a temperature examination a control of the equipments provided a kind of viable e 2lectric circuit design a project.K eywords :digital phase locked Loop ;phase modulating synchronization ;temperature control ;f requency conversion收稿日期:20072072121 引 言锁相的概念在20世纪30年代提出后,很快就被广泛地应用在电子和通讯领域中。

基于数字式锁相环频率合成器的设计与实现

基于数字式锁相环频率合成器的设计与实现————————————————————————————————作者:————————————————————————————————日期:四川师范大学本科毕业设计基于数字式锁相环频率合成器的设计与实现学生姓名院系名称专业名称班级学号指导教师完成时间2014年5月14日基于数字式锁相环频率合成器的设计与实现电子信息工程专业学生姓名指导老师摘要随着通信信息技术的快速发展,信号产生的方式多种多样,然而数字式锁相环频率合成器在信号产生技术中扮演了越来越重要的作用,数字式锁相环频率合成器在频率频率稳定度和频谱纯度上,频率输出个数上有着巨大的优势,是其他器件所不能代替的!因此在军用和民用雷达领域,各种导航器以及通信领域广泛运用!基于此,本人设计了一个由晶体振荡器和分频器,锁相环路(鉴相器,低通滤波器,压控振荡器)组成的数字式锁相环频率合成器,晶体振荡器的作用是产生一个固定的频率,然后通过分频器得到一个基准频率,锁相环路对基准频率进行频率合成,到最后,合成后的频率经过放大器,使不同的频率的幅度稳定在一定的范围内,这样的话不会是信号不会随着输出频率的变化而减少!数字式锁相环频率合成器是开环系统的,频率转换时间很短,分辨率也较高,结构相对简单,成本也不高,输出的频率在稳定度和精准度上也有很大的优势.但是,由于毕业在即时间紧张,本人经验有些不足,希望老师和同学们帮助与指导。

关键词:锁相环频率合成晶体振荡器分频器锁相环路The Design and Implementation of Digital Pll Frequency SynthesizerAbstract With the rapid development of communication technology,signal way is varied, but in signal digital phase locked loop frequency synthesizer technology plays an increasingly important role, digital phase locked loop frequency synthesizer on the frequency stability and frequency spectrum purity,frequency output factor has a huge advantage,is cannot replace by other device!So in the field of military and civilian radar,navigator,and widely used communication field。

基于延迟锁相环和锁频环结构的全数字同步倍频器

基于延迟锁相环和锁频环结构的全数字同步倍频器曹玉梅;梁珍珍【期刊名称】《电子器件》【年(卷),期】2018(041)001【摘要】针对现有基于PLLs/DLLs的全数字化同步倍频器结构存在的不足,提出了一种基于双环结构的全数字同步倍频器.它由延迟锁相环和锁频环共享一个共同的参考时钟信号(FREF)构成,不需要任何模拟组件,采用Verilog-HDL语言设计,在Altera DE2-70开发板上实现合成;实验结果表明,所提出的结构相比于现有的结构,能够获得更高频率的输出时钟信号,提供更好的频率分辨率、更好的抖动性能和高倍乘因子.%Aiming at the shortages of existing all-digital synchronous multiplier structure based on PLLs/DLLs,an all-digital synchronous multiplier based on a dual-loop architecture is proposed. It is composed of proposed delay-locked loops and frequency-locked loops that share a common reference clock signal(FREF)and requires no any analog components. The proposed architecture is designed using the Verilog-HDL language and synthesized on the Altera DE2-70 development board. The experimental results show that the proposed architecture,compared with the existing architectures,can generate output clock signal having a higher frequency,provide better frequency resolution and jitter performance as well as high multiplication factor.【总页数】6页(P60-65)【作者】曹玉梅;梁珍珍【作者单位】商丘学院电子信息工程学院,河南商丘476000;商丘学院电子信息工程学院,河南商丘476000【正文语种】中文【中图分类】TN911.8【相关文献】1.基于锁相环和单片机的柔性倍频器设计 [J], 徐静;李晓鹏;李矩;刘桂雄2.基于全数字锁相环的电力系统高精度同步时钟 [J], 李泽文;舒磊;邓丰;曾祥君;邓拓夫3.采用锁频环和锁相环联合捕获的载波跟踪 [J], 高亢;侯孝民;赵强;彭保童4.北斗导航载波锁相环和锁频环的混合应用 [J], 刘延海;张亮5.基于改进型延迟线的全数字延迟锁相环 [J], 张世琳; 邱舒晴; 王少昊因版权原因,仅展示原文概要,查看原文内容请购买。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

一、主要内容与要求1.掌握应用电子设计自动化(EDA)技术设计电子系统的方法;2.采用超高速集成电路硬件描述语言(Verilog)设计一种基于数字锁相环的倍频器;3.重点设计数字环路滤波器和数控振荡器;4.利用计算机仿真技术进行验证;5.阅读并翻译3000单词以上的英文资料。

二、主要技术要求n倍频;2 1.系统能够实现输出信号为输入信号的2.改变系统参数可以得到不同的倍频信号,且始终能够使输出信号与输入信号保持同步;3.用Verilog语言编写设计程序,利用计算机仿真予以验证。

三、研究方法1.在查阅大量技术资料的基础上,进行设计方案的比较;2.确定全数字锁相环系统的设计方案;3.采用自顶向下的设计方法,进行系统模块的划分,并确定用Verilog设计各功能模块的算法;4.编写系统设计程序,并进行仿真验证,经过反复修改使电路系统达到设计要求。

四、工作进度安排1.2012年12月学习掌握Verilog设计技术,收集和整理与毕业设计有关的资料;2.2013年1月在分析和整理资料的基础上写开题报告,确定设计方案和研究技术路线;3.2013年3月完成环路滤波器和数控振荡器的设计与仿真;4.2013年4月完成全数字倍频器的系统设计与仿真;5.2013年5月撰写毕业设计说明书和准备毕业答辩稿;6.2013年6月初毕业答辩。

指导教师南华大学本科生毕业设计(论文)开题报告设计(论文)题目基于数字锁相环的同步倍频器设计省部级课题设计(论文)题目来源起止时工程设计2012.12013.6设计(论文)题目类一、设计(论文)依据及研究意义锁相(phase-locked loop是一种反馈控制电路,作用是实现设备外部输入信号与内部的震荡信号同步其基本组成包括鉴相 phasedetector环路滤波器loopfilter)和压控振荡器 voltagecontroloscillato)倍频器frequencymultiplie)是使输出信号频率等于输入信号频率整倍的电路利用非线性电路产生高次谐波或者利用频率控制回路都可以构成倍器倍频器也可由一个压控振荡器和控制环路构成它的控制电路产生一控制压,使压控振荡器的振荡频率严格地锁定在输入频f的倍乘fnf因为非线性变换过程中产生的大量谐波使输出信号相位不稳定所以其构的倍频器,倍频噪声较大。

倍频次数越高,倍频噪声就越大,使倍频器的应用到限制在要求倍频噪声较小的设备中可采用根据锁相环原理构成的锁相环步倍频器模拟锁相环主要由相位参考提取电路压控振荡器相位比较器控制电等组成压控振荡器输出的是与需要频率很接近的等幅信号把它和由相位参提取电路从信号中提取的参考信号同时送入相位比较器用比较形成的误差通控制电路使压控振荡器的频率向减小误差绝对值的方向连续变化实现锁相而达到同步数字锁相环主要由相位参考提取电路、晶体振荡器、分频器、相位比较器脉冲补抹门等组成分频器输出的信号频率与所需频率十分接近把它和从信中提取的相位参考信号同时送入相位比较器比较结果示出本地频率高了时就过补抹门抹掉一个输入分频器的脉冲相当于本地振荡频率降低相反若示本地频率低了时就在分频器输入端的两个输入脉冲间插入一个脉冲相当于本振荡频率上升,从而达到同步。

.南华大学电气工程学院毕业设计摘要:随着数字通信系统的高速发展,数字锁相环的应用也越来越广。

由于非线性电阻构成的倍频器,倍频噪声较大,而为了满足倍频噪声小的的需求,本文通过应用EDA技术设计电子系统的方法,采用硬件描述语言Verilog,设计了一种基于数字锁相环的同步倍频器系统。

该系统经过Quartus II软件的仿真以及验证,实现了输出信号为输入信号的2^n倍频的功能,改变系统参数也可以得到不同倍频信号,而且始终能使输出信号与输入信号保持同步。

故该系统能够减少因倍频次数高而产生的倍频噪声,但有时会出现相位失锁等问题。

关键字:锁相环; 倍频器; Verilog ;Quartus IIi南华大学电气工程学院毕业设计Abstract: With the rapid development of modern digital communication system,digital phase lock loop is becoming more and more widely used. Because of the nonlinear resistance of frequency multiplier, frequency multiplication noise is larger.In order to meet the needs of times frequency noise, in this paper, by using EDA technology to design electronic system, the method of using Verilog hardware description language, designs a synchronous frequency multiplier based on digital phase locked loop system. The system through simulation and validation of the quartus ii software implements 2 ^ n times that of the output signal for the input signal frequency function, changes of system parameters can also get different times frequency signal, and have always been able to make the output signal is synchronized with the input signal. So the system can reduce because of The Timesthe frequency of several times as a result of the high frequency noise, but sometimes there will be a phase lock and so on.Key words: ; frequency multiplier ; Verilog ; Quartus II . Phase-Locked Loopii南华大学电气工程学院毕业设计目录1 绪论 .............................................................11.1 设计依据及其研究意义 (1)1.2 锁相环技术的发展 (2)1.2.1 锁相环技术发展的历史 (2)1.2.2 锁相环技术发展的现状及其前景 (2)2 关于EDA的介绍 (4)2.1 Verilog简介 (5)2.2 Verilog和VHDL语言的对比 (6)2.3 Quartus II简介 (7)2.4 本课题采用的设计方法 (8)3 锁相环的结构与原理 ...............................................93.1 模拟锁相环的基本结构及其工作原理 (9)3.2 全数字锁相环的基本结构及其工作原理 (11)4 基于数字锁相环的同步倍频器设计 (13)4.1 数字鉴相器的设计 (13)4.2 数字环路滤波器的设计 (15)4.3 数控振荡器的设计 (18)4.4 N分频参数控制的设计 (19)4.5 N分频器的设计 (21)4.6 倍频器的设计 (23)4.7 全数字锁相环倍频器的顶层模块设计 (25)5 基于数字锁相环的同步倍频器仿真分析 (27)6 总结 (30)iii南华大学电气工程学院毕业设计参考文献 ..........................................................31谢辞...............................................................32附录一 (33)附录二 (43)iv南华大学电气工程学院毕业设计1绪论1.1 设计依据及其研究意义本次研究的课题是基于数字锁相环的同步倍频器设计。

锁相环路是反馈电路的一种,锁相环的英文全称是Phase-Locked Loop,简称PLL。

因锁相环可以实现输出信号频率对输入信号频率的自动跟踪,故其通常用于闭环跟踪电路。

之所以叫锁相环,是因为其在工作的过程中,当输出信号的频率和输入信号的频率相等时,输出电压和输入电压能保持固定的相位差值,实现相位的锁定的功能。

锁相环不仅在雷达、测量、通信和自动化控制等领域应用极为广泛,而且随着电子技术向数字化方向发展,需要采用数字方式实现信号的锁相处理,对全数字锁相环的研究和应用得到了越来越多的关注。

倍频器(frequency multiplier)是实现输出信号频率等于输入信号频率整数倍的电路。

倍频器可由一个压控振荡器和控制环路组成,其控制电路产生一控制电压,使压控振荡器的振荡频率严格地锁定在输入频率fi的n倍值fo=nfi上。

倍频器用途十分广泛,如为了提高频率稳定度,发射机常采用倍频器以使主振器振荡在一个较低频率;而调频设备也常用倍频器来增大频率的偏移;倍频器也已然成为相位键控通信机中载波恢复电路的一个重要组成单元。

当然,倍频器也可利用非线性电路产生高次谐波或者利用频率控制回路构成。

由于非线性变换过程中产生的大量谐波可使输出信号得相位不稳定,所以这种倍频器,倍频噪声较大。

而倍频次数越高,倍频噪声就会越大,这就大大限制了倍频器的应用。

所以为了减小设备中的倍频噪声,我们可以采用基于锁相环原理构成的同步倍频器,这也正是本次课题研究意义之所在。

第1页,共43页南华大学电气工程学院毕业设计1.2 锁相环技术的发展1.2.1锁相环技术发展的历史锁相环技术起源于二十世纪三十年代,直至今日已经发展了八十余年。

锁相环技术首先是由DeBellescize于1932年提出的锁相环同步检波技术。

但首次公开对锁相环路的描述,却并未引起普遍的重视。

一直到1947年,锁相环第一次用于电视接收机水平和垂直扫描的同步,锁相环技术才开始得到应用。

由于较高的成本和技术上的复杂性,锁相环技术主要应用在航天方面,包括深空探测和轨道卫星的测速定轨等等;有时也用于性能要求较高的精密测量仪和通信设备上。

随着70年代半导体技术和集成电路技术的发展,逐渐出现了集成的环路部件、通用单片机集成锁相环路以及多种专用集成锁相环路。