西电fpga第一次上机报告解析

FPGA实验报告

FPGA实验报告Xilinx FPGA及应⽤实验报告(⼀)实验⼀全加器⼀、实验⽬的1、编写简单门电路的RTL级描述程序;2、创建简单电路的结构级VHDL描述程序;3、实现全加器功能,由半加器组成,以元件⽅式调⽤。

⼆、实验环境1、ISE软件⼀套;2、PC机⼀台。

三、实验步骤1、创建⼀个新的⼯程(1)选择“开始->所有程序->Xilinx ISE 9.1i”或直接在桌⾯双击Xilinx ISE 9.1i的图标,打开ISE 9.1i集成环境。

(2)在ISE中,选择菜单栏中的File->New Project 打开创建新⼯程界⾯,在Project Name 中填⼊⼯程名,在Project Location中填⼊⼯程所在⽂件夹。

2、编写半加器的RTL级描述和全加器的结构级描述半加器源程序为:library IEEE;use IEEE.STD_LOGIC_1164.ALL;entity half isPort ( a : in STD_LOGIC;b : in STD_LOGIC;s : out STD_LOGIC;co : out STD_LOGIC);end half;architecture Behavioral of half issignal c,d : STD_LOGIC;beginc <= a or b;d <= a nand b;s <= c and d;co <= not d;end Behavioral;波形仿真结果为:全加器源程序为:library IEEE;use IEEE.STD_LOGIC_1164.ALL;entity full isPort ( a : in STD_LOGIC;b : in STD_LOGIC;cin : in STD_LOGIC;s : out STD_LOGIC;co : out STD_LOGIC);end full;architecture Behavioral of full is component halfPORT (a, b: IN std_LOGIC;s,co: OUT std_LOGIC);end component;signal u0_co,u0_s,u1_co:std_logic;beginu0:half port map(a,b,u0_s,u0_co);u1:half port map(u0_s,cin,s,u1_co);co<=u0_co or u1_co;end Behavioral;波形仿真结果为:\ 实验⼆12进制计数器⼀、实验⽬的1、熟悉Xilinx的ISE软件的使⽤和设计流程;2、初步了解VHDL的编程⽅法;3、使⽤VHDL语⾔创建、仿真并验证12进制计数器。

西电算法导论上机实验报告

算法导论上机实验报告册班级: xxxxxx学号: xxxxxxx姓名: xxxx教师: xxxxxx目录实验一排序算法 0题目一: 01、题目描述:描述一个运行时间为θ(nlgn)的算法,给定n个整数的集合S和另一个整数x,该算法能确定S中是否存在两个其和刚好为x的元素。

02、所用算法:1、运用归并排序算法 03、算法分析: 04、结果截图: 05、总结: (1)题目二: (2)1、题目描述:实现优先级队列,即需要支持以下操作:INSERT(S,x):把元素x插入到集合S中;MAXMUM(S):返回S中具有最大key的元素;EXTRACT-MAX(S):去掉并返回S中的具有最大key的元素; (2)2、所用算法:堆排序,运用堆来实现优先队列。

(2)3、算法分析: (2)4、结果截图: (2)5、总结: (3)题目三: (3)1、题目描述:实现quick_sort算法,并且回答以下两个问题:(1)待排数组中的元素值都相同的情况下,运用quick_sort需要进行多少次比较(2)对于n个元素的数组,运用quick_sort举出需要进行比较次数的上限和下限是多少 (3)2、所用算法:快速排序算法 (3)3、算法分析:快速排序采用分治策略,时间复杂度为θ(nlgn),但是最坏情况下为θ(n2),并且快速排序算法属于原地排序,并不需要开辟空间。

快速排序复杂的步骤为其分解的步骤,分解的过程:数组A[p..r]被划分为两个子数组A[p..q-1]和A[q+1..r],使得A[p..q-1]中的每个元素都小于A[q],而A[q]也小于等于A[q+1..r]中的每个元素。

而在实现的过程总是选择将A[r]作为基准点进行划分A[p..r]数组。

(4)4、结果截图: (4)5、总结: (4)题目四: (5)1、题目描述:运用分治的策略将两个已经排好序的序列中,找出第k大的元素,且要求时间复杂度为θ(lgm+lgn),其中m和n分别为两个序列的长度。

fpga实训报告

fpga实训报告引言随着技术的不断发展,电子行业也在迅速进步。

作为电子产品领域的重要组成部分,FPGA(Field Programmable Gate Array)即现场可编程门阵列技术)在近年来受到越来越多的重视。

本文将分享我参与的一次FPGA实训项目的经验和体会。

一、FPGA的基本概念FPGA是一种集成电路芯片,它通过可编程逻辑门阵列构成的,能够实现电路的数字逻辑功能。

与传统的ASIC(Application-Specific Integrated Circuit)相比,FPGA具有可编程的优势,能够根据需要进行重新编程,具备更高的灵活性和可塑性。

二、实训项目背景本次实训项目是一个基于FPGA的数字信号处理系统设计。

我们小组的任务是设计一个音频信号处理系统,能够实现音频的输入、处理和输出等功能。

这个项目旨在让我们熟悉FPGA开发流程和工具,并锻炼我们的团队协作能力和解决问题的能力。

三、项目过程1.需求分析在开始项目之前,我们首先进行了需求分析。

我们确定了音频输入输出的格式要求,处理功能的要求,以及系统的性能指标。

这一步对于项目的成功实施非常关键,只有明确需求,才能确保后续的设计和开发效果。

2.系统设计在需求分析的基础上,我们开始进行系统设计。

我们首先进行模块拆分,将系统划分为音频输入模块、音频处理模块和音频输出模块。

然后,我们根据每个模块的功能设计相应的电路和逻辑。

3.软件仿真设计好电路和逻辑后,我们使用FPGA开发工具进行软件仿真。

通过仿真,我们可以验证设计的正确性和稳定性。

当发现问题时,我们及时进行修改和优化,直到达到预期的效果。

4.物理综合在软件仿真通过后,我们进行物理综合。

这一步骤将我们的设计映射到实际的硬件资源上,包括将逻辑电路映射到LUT(Lookup Table)、将时序电路映射到寄存器等。

物理综合过程中,我们需要考虑到硬件资源的利用率和系统的性能要求。

5.实际实现完成物理综合后,我们开始进行实际的系统实现。

fpga实验报告

fpga实验报告FPGA实验报告引言随着科技的发展和计算机应用的广泛应用,人们对于计算机硬件的需求也越来越高。

在这个背景下,FPGA(Field Programmable Gate Array)作为一种可编程逻辑器件,被广泛应用于数字电路设计和嵌入式系统开发。

本篇文章将就FPGA的基本原理、实验设计和实验结果进行探讨。

一、FPGA的基本原理FPGA是一种可编程逻辑器件,它由一系列可编程逻辑单元(PLU)和可编程互连资源(PIM)组成。

PLU可以根据用户的需求进行编程,实现不同的逻辑功能。

PIM则用于连接不同的PLU,构成用户所需的电路结构。

FPGA的可编程性使得它能够根据不同的应用需求进行灵活的配置和重构,具有很高的可扩展性和适应性。

二、FPGA实验设计在FPGA实验设计中,我们通常需要进行电路设计、编程和仿真等步骤。

1. 电路设计FPGA实验中的电路设计是实验的核心环节。

我们需要根据实验要求,设计出符合要求的逻辑电路。

在设计过程中,我们可以使用硬件描述语言(HDL)如Verilog或VHDL来描述电路结构和功能。

通过对电路进行分析和优化,我们可以得到满足实验要求的电路设计。

2. 编程在电路设计完成后,我们需要将电路设计转化为FPGA可识别的编程文件。

这一步骤通常使用专门的软件工具来完成,如Xilinx ISE或Quartus II。

通过这些软件工具,我们可以将电路设计转化为FPGA可执行的bit文件。

3. 仿真在将编程文件下载到FPGA之前,我们通常需要进行仿真验证。

通过仿真,我们可以验证电路设计的正确性和性能。

仿真可以帮助我们发现潜在的问题和错误,从而提前解决,确保实验的顺利进行。

三、FPGA实验结果在实验过程中,我们通过将编程文件下载到FPGA上,使其实现我们设计的逻辑电路。

通过实验,我们可以获得电路的输出结果,并对其进行验证和分析。

1. 输出验证通过与设计预期结果进行比对,我们可以验证电路的输出是否符合预期。

西电fpga第一次上机报告

FPGA设计基础实验报告班级:xxxxxxxx学号:xxxxxxxxxxx姓名:xx教师:xx1、创建一个工程File New ProjectFamily设置为Spart6Device设置为XC6SLX16Package设置为CSG234其他设置为默认2、设计输入选择Project->New Source,在左侧文件类型中选择Verilog Module,并输入Verilog文件名单击Next进入模块定义窗口,在其中填入模块端口定义。

这一步也可以略过,在源代码中再行添加具体代码略。

3、综合与实现在工程管理区的view中选择Implementation,然后在过程管理区双击Synthesize-XST,就可以开始综合过程展开Synthesize-XST,选择View RTL Schematic,可以查看综合出的RTL电路图添加用户约束文件:选择Project->New Source,在弹出的对话框中,左侧文件类型选中Implementation Constraints File,右侧填写文件名。

在工程管理区内选择Edit Constraints编辑约束文件,使用Nexys3开发板实现Gate2工程的用户约束文件代码如下所示。

综合完成后,下一个步骤就是实现(Implementation) 。

实现主要分为3个步骤:翻译(Translate) 、映射(Map) 与布局布线(place & Route)。

在ISE中,执行实现过程,会自动执行翻译、映射和布局布线过程:也可单独执行。

在过程管理区双击Implement Design选项,就可以自动完成实现的3个步骤。

4、器件配置器件配置是FPGA开发最关键的一步,只有将HDL代码下载到FPGA芯片中,才能进行调试并最终实现相应的功能。

首先我们必须生成能下载到硬件中的二进制比特文件。

双击过程管理区的Generate Programming File,ISE就会为设计生成相应的二进制比特文件。

西电微机原理与系统设计上机报告

微机原理与系统设计上机报告学号:*******姓名:**指导老师:**时间:2016年11月西安电子科技大学内容一 Debug程序的使用一、实验目的1. 学习使用DEBUG调试命令。

2. 学习用DEBUG调试简单程序。

3. 通过程序验证码制及其对标志位的影响。

4. 通过调试熟悉和掌握各寄存器的作用与特点。

二、实验内容用DEBUG调试简单程序。

三、实验仪器微机一台四、实验步骤1.由DOS进入DEBUG调试环境。

(1)DEBUG将调试程序装入内存注意:当机器控制权由DOS成功地转移给调试程序后,将显示“-”号,它是DEBUG的状态提示符,表示可以接受调试子命令了。

(2)-R 显示CPU中各寄存器当前初始内容,请记录下列各项:AX=0000 BX=0000 CX=0000 DX=0000 BP=0000 SI=0000 DI=0000 DS=13E0 ES=13E0 SS=13E0 SP=FFEE CS=13E0 IP=0100 FLAG寄存器中的8个标志位状态值是:OF DF IF SF ZF AF PF CFNV UP EI PL NZ NA PO NC DEBUG用符号给出标志寄存器中8个标志位的当前状态,其含义如下表所示。

标志位含义‘1’的对应符号‘0’的对应符号OF溢出OV有NV无DF方向DN递减UP递增IF中断EI允许DI禁止SF符号NG负PL正ZF全零ZR零NZ非零AF辅助进位AC有NA无PF奇偶性PE偶PO奇CF进位CY有NC无2.用DEBUG调试简单程序例1 -A CS:0106MOV AX,1234MOV BX,2345MOV CX,0ADD AX,BXMOV CX,AXINT 20运行程序(注:执行程序时IP应指向要执行的指令,需要修改该寄存器-RIP当前值输入需要值该处为0106,当然也可以在T或G命令中指出程序起始地址)-R 显示各寄存器当前内容及首条指令-T 3 跟踪执行三条赋值传送指令,观察寄存器及标志位-T 2跟踪执行相加及送和数指令,观察寄存器及标志位-G 执行软件中断指令INT 20,机器将显示“程序正常终止”的信息,并显示“-”,表明仍处在DEBUG的调试控制状态下,注意未用T命令,因为我们不想进入到20H中断处理程序中去,P命令也可实现相同操作实验现象记录:观察与记录按照上述要求命令执行后,哪些寄存器和标志位发生了变化。

FPGA实验报告

FPGA实验上机报告实验二1.Part1代码LIBRARY ieee;USE ieee.std_logic_1164.all;ENTITY part1 ISPORT(SW :IN STD_LOGIC_VECTOR(17 DOWNTO 0);LEDR :OUT STD_LOGIC_VECTOR(17 DOWNTO 0)); END part1;ARCHITECTURE Behavior OF part1 ISBEGINLEDR<=SW;END Behavior;运行结果:拨码开关控制LED闪亮2.Nice 代码LIBRARY ieee;USE ieee.std_logic_1164.all;ENTITY nice ISPORT(SW :IN STD_LOGIC_VECTOR(0 TO 17);HEX0 :OUT STD_LOGIC_VECTOR(0 TO 6);LEDR :OUT STD_LOGIC_VECTOR(0 TO 17));END nice;ARCHITECTURE Behavior OF nice ISSIGNAL temp :STD_LOGIC_VECTOR(0 TO 3);BEGINLEDR<=SW;temp(3)<=SW(0);temp(2)<=SW(1);temp(1)<=SW(2);temp(0)<=SW(3);PROCESS(temp)BEGINCASE temp ISWHEN "0000"=>HEX0<="1001111";WHEN "0001"=>HEX0<="0010010";WHEN "0010"=>HEX0<="0000110";WHEN "0011"=>HEX0<="1101100";WHEN "0100"=>HEX0<="1001100";WHEN "0101"=>HEX0<="0100100";WHEN "0110"=>HEX0<="0100000";WHEN "0111"=>HEX0<="0001111";WHEN "1000"=>HEX0<="0000000";WHEN "1001"=>HEX0<="0000100";WHEN OTHERS=>HEX0<="1001000";END CASE;END PROCESS;END Behavior;运行结果:拨码开关控制数码管显示数字3.数字时钟电路代码(1)watch.vhd:LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_UNSIGNED.ALL;-----This is a simple watch with sec/min/hour display in DE2 broad -----SW(0) is the reset input, when SW(0)=1,the program runs. ENTITY watch ISPORT(SW: IN STD_LOGIC_VECTOR(17 DOWNTO 0);clk_50:IN STD_LOGIC;HEX0:OUT STD_LOGIC_VECTOR(6 DOWNTO 0);HEX1:OUT STD_LOGIC_VECTOR(6 DOWNTO 0);HEX2:OUT STD_LOGIC_VECTOR(6 DOWNTO 0);HEX3:OUT STD_LOGIC_VECTOR(6 DOWNTO 0);HEX4:OUT STD_LOGIC_VECTOR(6 DOWNTO 0);HEX5:OUT STD_LOGIC_VECTOR(6 DOWNTO 0);HEX6:OUT STD_LOGIC_VECTOR(6 DOWNTO 0);HEX7:OUT STD_LOGIC_VECTOR(6 DOWNTO 0)); END watch;--------------------------------------------------ARCHITECTURE rtl OF watch ISCOMPONENT sec_clk IS -----create a clk signal 1Hz frequency PORT(clk_50 :IN STD_LOGIC;clk_div1 :OUT STD_LOGIC);END COMPONENT;COMPONENT count4 IS -----second counterPORT(res,stop,clk :IN STD_LOGIC;ca :OUT STD_LOGIC; --ca=1 when second count=59a :OUT STD_LOGIC_VECTOR(3 DOWNTO 0));END COMPONENT;COMPONENT count3 IS -----second counterPORT(res,clk :IN STD_LOGIC;ca :OUT STD_LOGIC; --ca=1 when second count=59a:OUT STD_LOGIC_VECTOR(3 DOWNTO 0));END COMPONENT;COMPONENT seccount IS -----second counterPORT(res,clk :IN STD_LOGIC;ca :OUT STD_LOGIC; --ca=1 when second count=59a,b :OUT STD_LOGIC_VECTOR(3 DOWNTO 0));END COMPONENT;COMPONENT mincount ISPORT(en,res,clk:IN STD_LOGIC;ca:OUT STD_LOGIC;a,b:OUT STD_LOGIC_VECTOR(3 DOWNTO 0));END COMPONENT;COMPONENT count24 ISPORT(en,res,clk:IN STD_LOGIC;a,b:OUT STD_LOGIC_VECTOR(3 DOWNTO 0));END COMPONENT;COMPONENT dis ISPORT(d:IN STD_LOGIC_VECTOR(3 DOWNTO 0);q:OUT STD_LOGIC_VECTOR(6 DOWNTO 0));END COMPONENT;SIGNAL stop: STD_LOGIC:='0';SIGNAL res: STD_LOGIC:='0';SIGNAL sec1: STD_LOGIC:='0';SIGNAL t1: STD_LOGIC:='0';SIGNAL m1: STD_LOGIC:='0';SIGNAL sec_c: STD_LOGIC:='0';SIGNAL min_c: STD_LOGIC:='0';SIGNAL m_a: STD_LOGIC_VECTOR(3 DOWNTO 0):="0000"; SIGNAL t_a: STD_LOGIC_VECTOR(3 DOWNTO 0):="0000"; SIGNAL sec_a: STD_LOGIC_VECTOR(3 DOWNTO 0):="0000"; SIGNAL sec_b: STD_LOGIC_VECTOR(3 DOWNTO 0):="0000"; SIGNAL min_a: STD_LOGIC_VECTOR(3 DOWNTO 0):="0000";SIGNAL min_b: STD_LOGIC_VECTOR(3 DOWNTO 0):="0000";SIGNAL hour_a: STD_LOGIC_VECTOR(3 DOWNTO 0):="0000";SIGNAL hour_b: STD_LOGIC_VECTOR(3 DOWNTO 0):="0000";BEGINres<=SW(0);stop<=SW(1);u1: sec_clk PORT MAP(clk_50, m1);u2: count4 PORT MAP(res, stop,m1,t1,m_a);u3: count3 PORT MAP(res, t1,sec1,t_a);u4: seccount PORT MAP(res, sec1,sec_c,sec_a, sec_b);u5: mincount PORT MAP(sec_c,res,sec1,min_c, min_a, min_b);u6: count24 PORT MAP(min_c, res,sec1,hour_a, hour_b);u7: dis PORT MAP(m_a,HEX0);u8: dis PORT MAP(t_a,HEX1);u9: dis PORT MAP(sec_a,HEX2);u10: dis PORT MAP(sec_b,HEX3);u11: dis PORT MAP(min_a,HEX4);u12: dis PORT MAP(min_b,HEX5);u13: dis PORT MAP(hour_a,HEX6);u14:dis PORT MAP(hour_b,HEX7);END rtl;(2)Sec_clk.vhd:LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_UNSIGNED.ALL;ENTITY sec_clk ISPORT(CLK_50: IN STD_LOGIC;clk_div1: OUT STD_LOGIC);END ENTITY sec_clk;ARCHITECTURE rtl OF sec_clk ISSIGNAL count: STD_LOGIC_VECTOR(21 DOWNTO 0);--50M=50000000=10111110101111000010000000-26BEGINPROCESS(CLK_50)BEGINIF(CLK_50'event AND CLK_50='1') THENIF(count(21)='1') THEN--10000000000000000000000000count<=(OTHERS=>'0');--33554432ELSEcount<=count+1;END IF;END IF;END PROCESS;clk_div1<= count(21);--67108864END ARCHITECTURE rtl;(3)seccount.vhd:LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_UNSIGNED.ALL;ENTITY seccount ISPORT(res,clk:IN STD_LOGIC;ca:OUT STD_LOGIC;a,b:OUT STD_LOGIC_VECTOR(3 DOWNTO 0)); END seccount;ARCHITECTURE rtl OF seccount ISSIGNAL aout,bout: STD_LOGIC_VECTOR(3 DOWNTO 0); SIGNAL cout:STD_LOGIC;BEGINPROCESS(clk,res)BEGINIF (res='0') THENaout<="0000";bout<="0000";-- cout<='0';ELSIF(clk'event and clk='1')THENIF(aout="1001")THENaout<="0000";IF (bout="0101") THENbout<="0000";-- cout<='1';ELSEbout<=bout+1;END IF;ELSEaout<=aout+1;bout<=bout;-- cout<='0';END IF;END IF;END PROCESS;PROCESS(clk,aout,bout)BEGINIF clk'event and clk='1' THENIF bout="0101" and aout="1001" THENcout<='1';ELSEcout<='0';END IF;END IF;END PROCESS;a<=aout;b<=bout;ca<=cout;END rtl;(4)midcount.vhd:LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_UNSIGNED.ALL;ENTITY mincount ISPORT(en,res,clk:IN STD_LOGIC;ca:OUT STD_LOGIC;a,b:OUT STD_LOGIC_VECTOR(3 DOWNTO 0)); END mincount;ARCHITECTURE rtl of mincount ISSIGNAL aout,bout: STD_LOGIC_VECTOR(3 DOWNTO 0); SIGNAL cout: STD_LOGIC;BEGINPROCESS(en,clk,res)BEGINIF (res='0') THENaout<="0000";bout<="0000";cout<='0';ELSIF(clk'event and clk='1')THENIF(en='1' )THENIF(bout>4)THENIF(aout>8)THENaout<="0001";bout<="0000";cout<='1';ELSE aout<=aout+1;END IF;ELSEIF(aout=9)THENaout<="0000";bout<=bout+1;ELSE aout<=aout+1; cout<='0';END IF;END IF;END IF;END IF;END PROCESS;a<=aout;b<=bout;ca<=cout;END rtl;(5)count24.vhd:LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_UNSIGNED.ALL;ENTITY count24 ISPORT(en,res,clk:IN STD_LOGIC;a,b:OUT STD_LOGIC_VECTOR(3 DOWNTO 0)); END;ARCHITECTURE rtl of count24 isSIGNAL aout,bout: STD_LOGIC_VECTOR(3 DOWNTO 0); BEGINPROCESS(en,clk,res)BEGINIF(res='0')THENaout<="0000";bout<="0000";ELSIF(clk'EVENT AND clk='1')THENIF en='1' THENIF(bout>1)THENIF(aout>2)THENaout<="0000";bout<="0000";ELSEaout<=aout+1;END IF;ELSEIF(aout=9)THENaout<="0000";bout<=bout+1;ELSEaout<=aout+1;END IF;END IF;END IF;END IF;END PROCESS;a<=aout;b<=bout;END rtl;(6)dis.vhd:LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;ENTITY dis ISPORT(d:IN STD_LOGIC_VECTOR(3 DOWNTO 0);q:OUT STD_LOGIC_VECTOR(6 DOWNTO 0)); END dis;ARCHITECTURE rtl OF dis ISBEGINPROCESS(d)BEGINCASE d ISWHEN"0000"=>q<="1000000";WHEN"0001"=>q<="1111001";WHEN"0010"=>q<="0100100";WHEN"0011"=>q<="0110000";WHEN"0100"=>q<="0011001";WHEN"0101"=>q<="0010010";WHEN"0110"=>q<="0000010";WHEN"0111"=>q<="1011000";WHEN"1000"=>q<="0000000";WHEN OTHERS=>q<="0010000";END CASE;END PROCESS;END rtl;(7)count3:LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_UNSIGNED.ALL;ENTITY count3 ISPORT(res,clk:IN STD_LOGIC;ca:OUT STD_LOGIC;a:OUT STD_LOGIC_VECTOR(3 DOWNTO 0)); END count3;ARCHITECTURE rtl OF count3 ISSIGNAL aout: STD_LOGIC_VECTOR(3 DOWNTO 0); SIGNAL cout:STD_LOGIC;BEGINPROCESS(clk,res)BEGINIF (res='0') THENaout<="0000";-- cout<='0';ELSIF(clk'event and clk='1')THENIF(aout="1001")THENaout<="0000";-- cout<='1';ELSEaout<=aout+1;-- cout<='0';END IF;END IF;END PROCESS;PROCESS(clk,aout)BEGINIF clk'event and clk='1' THENIF aout="1001" THENcout<='1';ELSEcout<='0';END IF;END IF;END PROCESS;a<=aout;ca<=cout;END rtl;(8)count4:LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_UNSIGNED.ALL;ENTITY count4 ISPORT(res,clk:IN STD_LOGIC;ca:OUT STD_LOGIC;a:OUT STD_LOGIC_VECTOR(3 DOWNTO 0)); END count4;ARCHITECTURE rtl OF count4 ISSIGNAL aout: STD_LOGIC_VECTOR(3 DOWNTO 0); SIGNAL cout:STD_LOGIC;BEGINPROCESS(clk,res)BEGINIF (res='0') THENaout<="0000";-- cout<='0';ELSIF(clk'event and clk='1')THEN IF(aout="1001")THENaout<="0000";-- cout<='1';ELSEaout<=aout+1;-- cout<='0';END IF;END IF;END PROCESS;PROCESS(clk,aout)BEGINIF clk'event and clk='1' THENIF aout="1001" THENcout<='1';ELSEcout<='0';END IF;END IF;END PROCESS;a<=aout;ca<=cout;END rtl;实验结果:可以实现计时,暂停功能。

操作系统上机实验报告(西电)

操作系统上机题目一、题目实验1:LINUX/UNIX Shell部分(一)系统基本命令1.登陆系统,输入whoami 和pwd ,确定自己的登录名和当前目录;登录名yuanye ,当前目录/home/yuanye2.显示自己的注册目录?命令在哪里?a.键入echo $HOME,确认自己的主目录;主目录为/home/yuanyeb.键入echo $PA TH,记下自己看到的目录表;/usr/local/sbin:/usr/local/bin:/usr/sbin:/usr/bin:/sbin:/bin:/usr/gamesc.键入which abcd,看看得到的错误信息;再键入which ls 和which vi,对比刚刚得到的结果的目录是否在a.、b.两题看到的目录表中;/bin/ls /usr/bin/vi3.ls 和cd 的使用:a.键入ls,ls -l ,ls -a ,ls -al 四条命令,观察输出,说明四种不同使用方式的区别。

1. examples.desktop 公共的模板视频图片文档音乐桌面; 总计322.-rw-r--r-- 1 yuanye yuanye 357 2011-03-22 22:15 examples.desktopdrwxr-xr-x 2 yuanye yuanye 4096 2011-03-22 23:25 公共的drwxr-xr-x 2 yuanye yuanye 4096 2011-03-22 23:25 模板drwxr-xr-x 2 yuanye yuanye 4096 2011-03-22 23:25 视频drwxr-xr-x 2 yuanye yuanye 4096 2011-03-22 23:25 图片drwxr-xr-x 2 yuanye yuanye 4096 2011-03-22 23:25 文档drwxr-xr-x 2 yuanye yuanye 4096 2011-03-22 23:25 音乐drwxr-xr-x 2 yuanye yuanye 4096 2011-03-22 23:25 桌面3. . .fontconfig .local .Xauthority.. .gconf .mozilla .xsession-errors.bash_logout .gconfd .nautilus 公共的.bashrc .gksu.lock .profile 模板.cache .gnome2 .pulse 视频.chewing .gnome2_private .pulse-cookie 图片.config .gnupg .recently-used.xbel 文档.dbus .gstreamer-0.10 .scim 音乐.dmrc .gtk-bookmarks .sudo_as_admin_successful 桌面.esd_auth .gvfs .update-manager-coreexamples.desktop .ICEauthority .update-notifier4. 总计156drwxr-xr-x 28 yuanye yuanye 4096 2011-03-24 16:55 .drwxr-xr-x 3 root root 4096 2011-03-22 22:15 ..-rw-r--r-- 1 yuanye yuanye 220 2011-03-22 22:15 .bash_logout-rw-r--r-- 1 yuanye yuanye 3115 2011-03-22 22:15 .bashrcdrwxr-xr-x 3 yuanye yuanye 4096 2011-03-22 23:30 .cachedrwx------ 2 yuanye yuanye 4096 2011-03-22 23:24 .chewingdrwxr-xr-x 4 yuanye yuanye 4096 2011-03-22 23:30 .configdrwx------ 3 yuanye yuanye 4096 2011-03-22 22:31 .dbus-rw------- 1 yuanye yuanye 49 2011-03-24 16:54 .dmrc-rw------- 1 yuanye yuanye 16 2011-03-22 22:31 .esd_auth-rw-r--r-- 1 yuanye yuanye 357 2011-03-22 22:15 examples.desktopdrwxr-xr-x 2 yuanye yuanye 4096 2011-03-22 23:15 .fontconfigdrwx------ 4 yuanye yuanye 4096 2011-03-24 16:54 .gconfdrwx------ 2 yuanye yuanye 4096 2011-03-24 16:56 .gconfd-rw-r----- 1 yuanye yuanye 0 2011-03-22 23:19 .gksu.lockdrwx------ 6 yuanye yuanye 4096 2011-03-22 23:20 .gnome2drwx------ 2 yuanye yuanye 4096 2011-03-22 22:32 .gnome2_privatedrwx------ 2 yuanye yuanye 4096 2011-03-22 22:31 .gnupgdrwxr-xr-x 2 yuanye yuanye 4096 2011-03-22 22:32 .gstreamer-0.10-rw-r--r-- 1 yuanye yuanye 156 2011-03-24 16:55 .gtk-bookmarksdr-x------ 2 yuanye yuanye 0 2011-03-24 16:54 .gvfs-rw------- 1 yuanye yuanye 479 2011-03-24 16:54 .ICEauthoritydrwx------ 3 yuanye yuanye 4096 2011-03-22 23:30 .localdrwx------ 4 yuanye yuanye 4096 2011-03-22 23:29 .mozilladrwxr-xr-x 3 yuanye yuanye 4096 2011-03-22 22:32 .nautilus-rw-r--r-- 1 yuanye yuanye 675 2011-03-22 22:15 .profiledrwx------ 2 yuanye yuanye 4096 2011-03-24 16:54 .pulse-rw------- 1 yuanye yuanye 256 2011-03-22 22:31 .pulse-cookie-rw------- 1 yuanye yuanye 861 2011-03-22 23:30 .recently-used.xbeldrwx------ 3 yuanye yuanye 4096 2011-03-22 23:24 .scim-rw-r--r-- 1 yuanye yuanye 0 2011-03-22 22:35 .sudo_as_admin_successful drwxr-xr-x 2 yuanye yuanye 4096 2011-03-22 22:33 .update-manager-core drwx------ 2 yuanye yuanye 4096 2011-03-22 22:32 .update-notifier-rw------- 1 yuanye yuanye 117 2011-03-24 16:54 .Xauthority-rw-r--r-- 1 yuanye yuanye 3385 2011-03-24 16:56 .xsession-errorsdrwxr-xr-x 2 yuanye yuanye 4096 2011-03-22 23:25 公共的drwxr-xr-x 2 yuanye yuanye 4096 2011-03-22 23:25 模板drwxr-xr-x 2 yuanye yuanye 4096 2011-03-22 23:25 视频drwxr-xr-x 2 yuanye yuanye 4096 2011-03-22 23:25 图片drwxr-xr-x 2 yuanye yuanye 4096 2011-03-22 23:25 文档drwxr-xr-x 2 yuanye yuanye 4096 2011-03-22 23:25 音乐drwxr-xr-x 2 yuanye yuanye 4096 2011-03-22 23:25 桌面b.利用cd 转到/bin,/sbin ,/etc ,/dev,再利用ls 列出各个目录的内容,如果"迷路",可以利用pwd 确定位置,或键入cd ,cd ~ 观察效果.cd ,cd ~的区别: 1. bash dnsdomainname mountpoint sleepbunzip2 dumpkeys mt sttybzcat echo mt-gnu subzcmp ed mv syncbzdiff egrep nano tailfbzegrep false nc tarbzexe fgconsole nc.traditional tempfilebzfgrep fgrep netcat touchbzgrep fuser netstat truebzip2 fusermount ntfs-3g ulockmgr_serverbzip2recover grep ntfs-3g.probe umountbzless gunzip open unamebzmore gzexe openvt uncompresscat gzip pidof unicode_startchgrp hostname ping vdirchmod ip ping6 whichchown kbd_mode ps zcatchvt kill pwd zcmpcp ld_static rbash zdiffcpio ln readlink zegrepdash loadkeys rm zfgrepdate login rmdir zforcedbus-cleanup-sockets ls rnano zgrepdbus-daemon lsmod run-parts zlessdbus-uuidgen mkdir sed zmoredd mknod setfont znewdf mktemp setupcondir more shdmesg mount sh.distrib2. acpi_available getty mii-tool resize_reiserfsalsa grub-install mkdosfs rmmodalsactl halt mke2fs routeapm_available hdparm mkfs rtacctapparmor_parser hwclock mkfs.bfs rtmonbadblocks ifconfig mkfs.cramfs runlevelblkid ifdown mkfs.ext2 sfdisk blockdev ifup mkfs.ext3 shadowconfig brltty init mkfs.ext4 shutdownbrltty-setup initctl mkfs.ext4dev slattachcfdisk insmod mkfs.minix sscrda installkernel mkfs.msdos startctrlaltdel ip mkfs.reiserfs start-stop-daemon debugfs ip6tables mkfs.vfat status debugreiserfs ip6tables-restore mkreiserfs stopdepmod ip6tables-save mkswap sulogin dhclient ipmaddr modinfo swapoff dhclient3 iptables modprobe swapon dhclient-script iptables-restore mount.fuse sysctldmsetup iptables-save mount.ntfs syslogddosfsck iptunnel mount.ntfs-3g tcdosfslabel isosize mount.vmhgfs telinitdumpe2fs iwconfig nameif tune2fse2fsck iwevent on_ac_power udevadme2image iwgetid pam_tally udevde2label iwlist parted umount.hale2undo iwpriv partprobe unix_chkpwd fdisk iwspy pccardctl unix_update findfs kbdrate pivot_root update-grubfsck killall5 plipconfig usplashfsck.cramfs klogd poweroff usplash_down fsck.ext2 ldconfig rarp usplash_write fsck.ext3 ldconfig.real raw vol_idfsck.ext4 logd readahead-list vstpfsck.ext4dev logsave readahead-watch wpa_action fsck.minix losetup reboot wpa_clifsck.msdos lrm-manager regdbdump wpa_supplicant fsck.nfs lsmod reiserfsckfsck.reiserfs lspcmcia reiserfstunefsck.vfat MAKEDEV resize2fs3. acpi login.defsadduser.conf logrotate.confadjtime logrotate.dalsa lsb-basealternatives lsb-base-logging.shanacrontab lsb-releaseapm ltrace.conf apparmor magicapparmor.d magic.mimeapport mailcapapt mailcap.orderat.deny manpath.configavahi mime.typesbash.bashrc mke2fs.confbash_completion modprobe.dbash_completion.d modules bindresvport.blacklist monoblkid.tab motdblkid.tab.old motd.tailbluetooth mtabbogofilter.cf mtools.confbonobo-activation nanorcbrlapi.key netscsid.confbrltty networkbrltty.conf NetworkManagerca-certificates networksca-certificates.conf nsswitch.confcalendar obex-data-server chatscripts openoffice checkbox.d optcompizconfig pam.conf ConsoleKit pam.dconsole-setup pangoconsole-tools papersizecron.d passwdcron.daily passwd-cron.hourly pcmciacron.monthly perlcrontab pmcron.weekly pnm2ppa.confcups PolicyKitdbus-1 popularity-contest.conf debconf.conf powerdebian_version pppdefault profiledefoma profile.ddeluser.conf protocolsdepmod.d pulse dhcp3 purple dictionaries-common pythondm python2.6 doc-base rc0.ddpkg rc1.de2fsck.conf rc2.d emacs rc3.d environment rc4.d esound rc5.d event.d rc6.d firefox-3.0 rc.localfonts rcS.d foomatic readahead fstab resolvconf fuse.conf resolv.conf gai.conf rmtgamin rpcgconf samba gdm sane.d gimp scim gnome screenrc gnome-app-install scsi_id.config gnome-system-tools securetty gnome-vfs-2.0 security gnome-vfs-mime-magic sensors.conf gre.d services groff sgmlgroup shadow group- shadow- grub.d shells gshadow skel gshadow- soundgtk-2.0 sshhal ssl hdparm.conf sudoers hesiod.conf sysctl.conf host.conf sysctl.d hostname syslog.conf hosts terminfo hosts.allow timezonehosts.deny tpvmlp.confhp ts.confifplugd ucf.confinit.d udevinitramfs-tools ufwinputrc updatedb.confiproute2 updatedb.conf.BeforeVMwareToolsInstallissue update-manager update-motd.dkbd update-notifierkernel usplash.confkernel-img.conf vimlaptop-mode vmware-toolsldap w3mld.so.cache wgetrcld.so.conf wodim.confld.so.conf.d wpa_supplicantlftp.conf X11libpaper.d xdglocale.alias xmllocaltime xulrunner-1.9logcheck zsh_command_not_foun4. adsp loop7 ram7 tty15 tty43 usbdev1.1_ep00agpgart lp0 ram8 tty16 tty44 usbdev1.1_ep81audio mapper ram9 tty17 tty45 usbdev2.1_ep00block mem random tty18 tty46 usbdev2.1_ep81bus midi rtc tty19 tty47 usbmon0cdrom1 mixer rtc0 tty2 tty48 usbmon1char net scd0 tty20 tty49 usbmon2console network_latency sda tty21 tty5 vcscore network_throughput sda1 tty22 tty50 vcs1cpu_dma_latency null sda2 tty23 tty51 vcs2disk oldmem sda5 tty24 tty52 vcs3dmmidi parport0 sequencer tty25 tty53 vcs4dsp pktcdvd sequencer2 tty26 tty54 vcs5ecryptfs port sg0 tty27 tty55 vcs6fd ppp sg1 tty28 tty56 vcs7fd0 psaux shm tty29 tty57 vcs8full ptmx snapshot tty3 tty58 vcsafuse pts snd tty30 tty59 vcsa1hpet ram0 sndstat tty31 tty6 vcsa2initctl ram1 sr0 tty32 tty60 vcsa3input ram10 stderr tty33 tty61 vcsa4kmem ram11 stdin tty34 tty62 vcsa5kmsg ram12 stdout tty35 tty63 vcsa6log ram13 tty tty36 tty7 vcsa7loop0 ram14 tty0 tty37 tty8 vcsa8loop1 ram15 tty1 tty38 tty9 vmciloop2 ram2 tty10 tty39 ttyS0 vsockloop3 ram3 tty11 tty4 ttyS1 xconsoleloop4 ram4 tty12 tty40 ttyS2 zeroloop5 ram5 tty13 tty41 ttyS3loop6 ram6 tty14 tty42 urandom区别:(二)基本操作1.用cp 将/usr/share 目录下的exercise 子目录连同目录下的文件拷贝到自己的主目录下,然后进入自己的exercise 目录:cp -r /usr/share ./.2.输入/输出重定向和cat,more 等显示命令的配合使用:a.输入cat 命令列出目录下longtext 文件中的内容;b.输入cat 命令列出目录下longtext 文件中的内容,是否发现一屏显示不完?c.使用more 命令列出longtext 的内容;d.输入cat hello.txt> hello2.txt,再输入cat hello.txt>>hello2.txt,再检查hello2.txt的内容有何变化;说明>与>>的区别。

西安电子科技大学自动控制技术与原理上机报告完整版

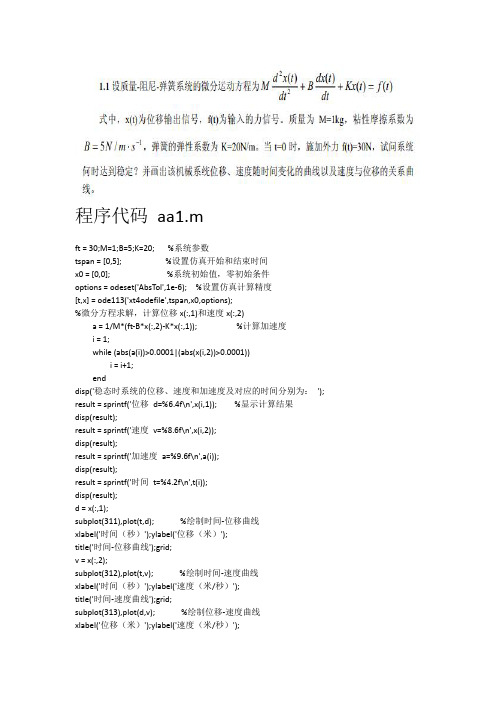

自动控制技术上机实验报告班级:0212#学号:0212##姓名:#####目录自动控制技术上机实验报告 (1)时域分析 (3)1.1源程序及结果 (3)1.2源程序及结果 (5)1.3源程序及结果 (6)1.4源程序及结果 (8)频域分析 (9)2.1源程序及结果 (9)2.2源程序及结果 (13)2.3源程序及结果 (14)2.4源程序及结果 (15)2.5源程序及结果 (16)现代控制理论 (18)3.1源程序及结果 (18)3.2源程序及结果 (21)3.3源程序及结果 (24)3.4源程序及结果 (25)3.5源程序及结果 (26)校正设计 (27)1.增量PID控制算法 (27)2.积分分离PID控制算法 (29)3.抗积分饱和PID控制算法 (32)4.带死区的PID控制算法 (36)时域分析1.1源程序及结果ft = 30;M=1;B=5;K=20;tspan = [0,5];x0= [0,0];options = odeset('AbsTol',[1e-6;1e-6]);[T,X]=ode45('xt4odefile',tspan,x0,options);figure(1)subplot(3,1,1),plot(T,X(:,1),'r'),title('位移随时间变化曲线'),grid on subplot(3,1,2),plot(T,X(:,2),'b'),title('速度随时间变化曲线'),grid on subplot(3,1,3),plot(X(:,2),X(:,1),'m'),title('位移随速度变化曲线'),grid ona = 1/M*(ft-B*X(:,2)-K*X(:,1));i = 1;while (abs(a(i))>0.0001|(abs(X(i,2))>0.0001))i = i+1;enddisp('系统到达稳态时的时间、速度和加速度及对应的位移分别为:'); result = sprintf('时间t=%4.2f\n',T(i));disp(result);result = sprintf('速度v=%9.6f\n',X(i,2));disp(result);result = sprintf('加速度 a=%9.6f\n',a(i)); disp(result);result = sprintf('位移 d=%6.4f\n',X(i,1)); disp(result);其中xt4odefile.m 文件为function xt = odefileC(t,x); ft = 30;M=1;B=5;K=20;xt = [x(2);1/M*(ft-B*x(2)-K*x(1))]; end输出:系统到达稳态时的时间、速度和加速度及对应的位移分别为: 时间 t=4.47速度 v=-0.000087加速度 a=-0.000060位移 d=1.500000.51 1.52 2.53 3.54 4.55012位移随时间变化曲线00.51 1.52 2.53 3.54 4.55-505速度随时间变化曲线-0.500.51 1.52 2.53 3.5012位移随速度变化曲线1.2源程序及结果num=[2,5,7];den=[1,6,10,6];[z,p,k]=tf2zp(num,den) [r,a,b]=residue(num,den)输出:z =-1.2500 + 1.3919i-1.2500 - 1.3919ip =-3.7693-1.1154 + 0.5897i-1.1154 - 0.5897ik =2r =2.2417-0.1208 - 1.0004i-0.1208 + 1.0004ia =b =[]结论:零点为-1.2500 + 1.3919i ,-1.2500 - 1.3919i ;极点为-3.7693 ,-1.1154 + 0.5897i,-1.1154 - 0.5897i ;增益为21.3源程序及结果num=[6.3223,18,12.811];den=[1,6,11.3223,18,12.811];t=0:0.005:20;[y,x,t]=step(num,den,t);plot(t,y);grid ontitle('单位阶跃响应曲线')xlabel('t')ylabel('c(t)')r10=1;while y(r10)<.1; r10=r10+1;end;r90=1;while y(r90)<.9; r90=r90+1;end;rise_time=(r90-r10)*0.005[ymax,tp]=max(y);peak_time=(tp-1)*.005max_overshoot=ymax-1s=4001;while y(s)>.98&y(s)<1.02;s=s-1;end;setting_time=(s-1)*.005输出:rise_time =0.5750peak_time =1.6700max_overshoot =0.6182setting_time =10.0300246810121416182000.20.40.60.811.21.41.61.8单位阶跃响应曲线tc (t )1.4源程序及结果num=[1 1];den=[1 5 6 0];sys1=tf(num,den)subplot(3,1,1)step(sys1)subplot(3,1,2)rlocus(num,den)title('系统的根轨迹曲线')r=rlocus(num,den,20.575)a=[1];b=[1 0.8989];sys2=tf(a,b)sys=series(sys1,sys2)%系统串联subplot(3,1,3)step(sys)输出:Transfer function:s + 1-----------------s^3 + 5 s^2 + 6 sr =-2.0505 + 4.3225i -2.0505 - 4.3225i -0.8989Transfer function:1----------s + 0.8989Transfer function:s + 1-------------------------------------s^4 + 5.899 s^3 + 10.49 s^2 + 5.393 s00.511.522.53x 104500010000Step ResponseTime (sec)A m p l i t u d e-3.5-3-2.5-2-1.5-1-0.500.5-10010系统的根轨迹曲线Real Axis I m a g i n a r y A x i s00.51 1.52 2.53x 104500010000Step ResponseTime (sec)A m p l i t u d e频域分析2.1源程序及结果w=logspace(-1,3,1000); %比例环节 num0=0.01; den0=1;g0=tf(num0,den0);bode(g0,w)title('比例环节')grid%二阶积分环节num1=1;den1=[1,0,0];g1=tf(num1,den1); figure(2)bode(g1,w)title('二阶积分环节') grid%二阶微分环节num2=[1,0.01,1]; den2=1;g2=tf(num2,den2); figure(3)bode(g2,w)title('二阶微分环节') grid%振荡环节num3=1;den3=[0.25,0.01,1]; g3=tf(num3,den3); figure(4)bode(g3,w)title('振荡环节')grid%总:num=0.01*[1,0.01,1]; den=[0.25,0.01,1,0,0]; g=tf(num,den); figure(5)bode(g,w)title('原总波特图') grid输出:-41-40.5-40-39.5-39M a g n i t u d e (d B )10-110101102103-1-0.500.51P h a s e (d e g )比例环节Frequency (rad/sec)-150-100-5050M a g n i t u d e (d B )10-110101102103-181-180.5-180-179.5-179P h a s e (d e g )二阶积分环节Frequency (rad/sec)-50050100150M a g n i t u d e (d B )10-1101011021034590135180P h a s e (d e g )二阶微分环节Frequency (rad/sec)-150-100-5050M a g n i t u d e (d B )10-110101102103-180-135-90-450P h a s e (d e g )振荡环节Frequency (rad/sec)-150-100-50M a g n i t u d e (d B )10-110101102103-180-135-90-450P h a s e (d e g )原总波特图Frequency (rad/sec)2.2源程序及结果num=[0,20,20,10];den=conv([1,1,0],[1,10]); nyquist(num,den)输出:-1-0.500.51 1.52-20-15-10-55101520Nyquist DiagramReal AxisI m a g i n a r y A x i s2.3源程序及结果num=[2000,2000];den=conv([1 0.5 0],[1 14 400]); nichols(num,den) v = [-270 -90 -40 40]; axis(v) ngrid输出:-270-225-180-135-90-40-30-20-10102030406 dB3 dB 1 dB 0.5 dB0.25 dB0 dBNichols ChartOpen-Loop P hase (deg)O p e n -L o o p G a i n (d B )2.4源程序及结果num = [0 2000 2000]; den = conv([1 0.5 0],[1 14 400]); h=tf(num,den); bode(h);num = [0 2000 2000]; den = conv([1 0.5 0],[1 14 400]); h=tf(num,den);[gm,pm,wg,wc]=margin(h)输出:gm =2.7493pm =73.3527wg =19.8244 wc =5.3477-150-100-50050100M a g n i t u d e (d B )10-210-110101102103-270-225-180-135-90P h a s e (d e g )Bode DiagramFrequency (rad/sec)2.5源程序及结果num=[0 0 0 1];den=conv([.5 1 0],[1 1]);sysp=tf(num,den)sys=feedback(sysp,1)w=logspace(-1,1);bode(sys,w)grid on;[mag,phase,w]=bode(sys,w);[Mp,k]=max(mag);resonant_peak=20*log10(Mp)resonant_fre=w(k)n=1;while 20*log10(mag(n))>-3;n=n+1;end; bandwidth=w(n)输出:Transfer function:1---------------------0.5 s^3 + 1.5 s^2 + sTransfer function:1-------------------------0.5 s^3 + 1.5 s^2 + s + 1resonant_peak =5.2388resonant_fre =0.7906bandwidth =1.2649-60-40-2020M a g n i t u d e (d B )10-110101-270-180-90P h a s e (d e g )Bode DiagramFrequency (rad/sec)现代控制理论3.1A3.1源程序及结果num = [1 2 3];den = [1 3 3 1];[A,B,C,D] = tf2ss(num,den)输出:A =-3 -3 -11 0 00 1 0B =1C =1 2 3D =3.2B源程序:Z=[-1 -3];P=[0 -2 -4 -6];K=4;[A,B,C,D]=zp2ss(Z,P,K)输出:A =-10.0000 -4.8990 0 04.8990 0 0 0-6.0000 -4.2866 -2.0000 00 0 1.0000 0B =11C =0 0 0 4D =3.1C源程序:A=[0 1;1 -2];B=[0;1];C=[1 3];D=1;[num,den]=ss2tf(A,B,C,D); tf(num,den)[z,p,k]=ss2zp(A,B,C,D);zpk(z,p,k)输出:Transfer function:s^2 + 5 s-------------s^2 + 2 s - 1Zero/pole/gain:s (s+5)--------------------(s+2.414) (s-0.4142)3.2源程序及结果A1=[0 1;-1 -2];B1=[0;1];C1=[1 3];D1=[1];A2=[0 1;-1 -3];B2=[0;1];C2=[1 4];D2=[0];[A,B,C,D]=series(A1,B1,C1,D1,A2,B2,C2,D2) [A,B,C,D]=parallel (A1,B1,C1,D1,A2,B2,C2,D2) [A,B,C,D]=feedback (A1,B1,C1,D1,A2,B2,C2,D2) [A,B,C,D]=feedback (A1,B1,C1,D1,A2,B2,C2,D2,+1)输出:串联连接A =0 1 0 0-1 -3 1 30 0 0 10 0 -1 -2B =11C =1 4 0 0D =并联连接A =0 1 0 0-1 -2 0 00 0 0 10 0 -1 -3B =11C =1 3 1 4D =1单位负反馈连接A =0 1 0 0-1 -2 -1 -40 0 0 11 3 -2 -7B =11C =1 3 -1 -4D =1单位正反馈连接A =0 1 0 0-1 -2 1 40 0 0 11 3 0 1B =11C =1 3 1 4D =13.3源程序及结果A=[0,-2;1,-3];t=.2;F=expm(A*t) %转移矩阵B=[2;0];C=[0,3];D=[0];x0=[1,1];t=[0,.2];u=0*t;[y,x]=lsim(A,B,C,D,u,t,x0)输出:F =0.9671 -0.29680.1484 0.5219y =3.00002.0110x =1.0000 1.00000.6703 0.6703结论:t=0.2时,系统响应为6703.0)0()0(21==x x ,y (0.2)=2.01103.4源程序及结果A=[-3,1;1,-3];B=[1,1;1,1];C=[1,1;1,-1];D=[0];Qc=ctrb(A,B)Qo=obsv(A,C)Rc=rank(Qc)Ro=rank(Qo)输出:Qc =1 1 -2 -21 1 -2 -2 Qo =1 11 -1-2 -2-4 4Rc =1Ro =2结论:能控性矩阵和能观性矩阵的秩分别为1,2,又系统阶次是2,故系统是不可控的,是可观测的。

FPGA实验分析报告()

FPGA实验报告()————————————————————————————————作者:————————————————————————————————日期:武汉工程大学电气信息学院《FPGA与硬件描述语言》实验报告[ 1 ]专业班级13电信01班实验时间2015 年 10 月 12 日学生学号1304201426 实验地点4B 315学生姓名曾维颖指导教师曹新莉实验项目闪烁的LED实验类别基础实验实验学时4学时实验目的及要求1.掌握QuartusII设计电路的基本流程,熟悉VHDL程序,分别设计分频电路,LED 闪烁延时计数程序。

2.将设计好的LED闪烁电路程序下载到DEII开发板上进行实物测试。

成绩评定表类别评分标准分值得分合计上机表现按时出勤、遵守纪律认真完成各项实验内容30分报告质量程序代码规范、功能正确填写内容完整、体现收获70分说明:评阅教师:日期: 2015年月日实验内容(说明:此部分应包含:实验内容、实验步骤、实验数据与分析过程等)一、实验内容1.用VHDL语言设计分频器,得到0.1Hz——1Hz 的时钟信号;2.设计闪烁延时程序,控制发光二极管的闪烁。

二、实验方法与步骤分频电路的产生1. 分频原理:(50MHz晶振信号怎样分频成你所需要的低频信号。

)50MHz=50×100×100×100Hz,这样就需要1个50Hz分频器,3个100Hz分频器2.50分频器:源程序如下(记作cnt50)library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;entity cnt50 isport( clk : in std_logic;en : in std_logic;clr : in std_logic;cout: out std_logic;q : buffer std_logic_vector (5 downto 0));end cnt50;architecture one of cnt50 isbeginprocess(clk,clr) beginif clr='1' then q<="000000";elsif clk'event and clk='1' thenif en='1' then if q="110001"then q<="000000";else q<=q+1;end if;end if;end if;if q="110001"then cout<='1'; else cout<='0';end if;end process;end one;3.100分频器:(记作cnt100)源程序:library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;entity cnt100 isport( clk : in std_logic;en : in std_logic;clr : in std_logic;cout: out std_logic;q : buffer std_logic_vector (6 downto 0));end cnt100;architecture one of cnt100 isbeginprocess(clk,clr) beginif clr='1' then q<="0000000";elsif clk'event and clk='1' thenif en='1' then if q="1100011"then q<="0000000";else q<=q+1;end if;end if;end if;if q="1100011"then cout<='1'; else cout<='0';end if;end process;end one;4. LED闪烁定时电路:源程序:library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;entity cnt5 isport( clk : in std_logic;en : in std_logic;clr : in std_logic;cout: out std_logic;q : buffer std_logic_vector (2 downto 0));end cnt5;architecture one of cnt5 isbeginprocess(clk,clr) beginif clr='1' then q<="000";elsif clk'event and clk='1' thenif en='1' then if q="100"then q<="000";else q<=q+1;end if;end if;end if;if q="100"then cout<='1'; else cout<='0';end if;end process;end one;5. 顶层文件,将所有底层原件集成为顶层设计文件:三、实验数据与结果分析t50波形图t100波形图实验总结(说明:总结实验认识、过程、效果、问题、收获、体会、意见和建议。

西电 自动控制 上机 实验 报告

程序代码aa1.mft = 30;M=1;B=5;K=20; %系统参数tspan = [0,5]; %设置仿真开始和结束时间x0 = [0,0]; %系统初始值,零初始条件options = odeset('AbsTol',1e-6); %设置仿真计算精度[t,x] = ode113('xt4odefile',tspan,x0,options);%微分方程求解,计算位移x(:,1)和速度x(:,2)a = 1/M*(ft-B*x(:,2)-K*x(:,1)); %计算加速度i = 1;while (abs(a(i))>0.0001|(abs(x(i,2))>0.0001))i = i+1;enddisp('稳态时系统的位移、速度和加速度及对应的时间分别为:'); result = sprintf('位移d=%6.4f\n',x(i,1)); %显示计算结果disp(result);result = sprintf('速度v=%8.6f\n',x(i,2));disp(result);result = sprintf('加速度a=%9.6f\n',a(i));disp(result);result = sprintf('时间t=%4.2f\n',t(i));disp(result);d = x(:,1);subplot(311),plot(t,d); %绘制时间-位移曲线xlabel('时间(秒)');ylabel('位移(米)');title('时间-位移曲线');grid;v = x(:,2);subplot(312),plot(t,v); %绘制时间-速度曲线xlabel('时间(秒)');ylabel('速度(米/秒)');title('时间-速度曲线');grid;subplot(313),plot(d,v); %绘制位移-速度曲线xlabel('位移(米)');ylabel('速度(米/秒)');title('位移-速度曲线');grid;其中xt4odefile函数为:functionxt = xt4odefile(t,x)ft = 30;M=1;B=5;K=20;xt = [x(2);1/M*(ft-B*x(2)-K*x(1))]; 运行结果:程序代码aa2.mclear all; close all; num=[2,5,7]; den=[1,6,10,6]; sys=tf(num,den); [z,p,k]=tf2zp(num,den) [r,p,k]=residue(num,den)运行结果z ,p ,k 分别代表零点,极点和增益。

FPGA实验报告实验1

西南科技大学实验报告课程名称:基于FPGA的现代数字系统设计实验名称:基于原理图的十进制计数器设计姓名:学号:班级:通信1301指导教师:刘桂华西南科技大学信息工程学院制实验题目:基于原理图的十进制计数器设计一、 实验原理1、实验设计的示意图如下图所示:2、七段数码管译码器的设计:七段数码管属于数码管的一种,是由7段二极管组成。

按发光二极管单元衔接方式分为共阳极数码管和共阳极数码管。

本实验使用共阳数码管。

它是指将一切发光二极管的阳极接到一同构成公共阳极(COM)的数码管。

共阳数码管在应用时应将公共极COM 接到电源VCC 上,当某一字段发光二极管的阴极为低电平相应字段就点亮,当某一字段的阴极为高电平相应字段就不亮。

显示译码器,一般是将一种编码译成十进制码或特定的编码,并通过显示器件将译码器的状态显示出来。

下图是七段译码管的显示真值表,对逻辑功能进行分析:时钟端异步清零端为了实现译码功能,采用“最小项译码器+逻辑门电路”的方法实现。

最小项译码器输出能产生输入变量的所有最小项,而任何一个组合逻辑函数都可以变换为最小项之和的标准形式,故采用译码器和门电路可实现任何单输出或多输出的组合逻辑函数。

当译码器输出低电平有效时,一般选用与非门;当译码器输出高电平有效时,一般选用或门。

本实验可以采用ISE软件自带的“Decoder”库中的4线-16线译码器D4_16E(带使能端,输出高电平有效)和“Logic”库中的16输入或门OR16。

由于D4-16E输出高电平有效,所以或门可以选择其中不能使数码管某段亮的输入,从而达到控制数码管每段的亮灭。

因此,将每段需要灭的译码器输出相或起来就可得到每段数码管的译码器。

2、十进制计数器的设计原理调用ISE软件自带的“Counter”库中的十进制计数器CD4CE。

CD4CE是一个同步十进制器,输入有异步清零控制端CLR、工作使能控制端CE和时钟输入端C,输出有BCD码计数值输出端Q3~Q0,进位输出端TC和输出状态标志位CEO。

fpga实训报告

fpga实训报告第一节:引言在本篇报告中,我将详细介绍我在FPGA实训项目中的学习和实践经验,以及我在该项目中所遇到的挑战和解决方案。

FPGA(现场可编程门阵列)是一种灵活的、可编程的集成电路技术,它具有可重构的硬件特性,具备广泛的应用前景和潜力。

通过本次实训,我将探索FPGA的原理、设计流程和实际应用,并在实践中提升我的技能和知识。

第二节:理论基础2.1 FPGA的概念和工作原理在这一部分,我将介绍FPGA的基本概念和工作原理。

首先,FPGA是一种可编程逻辑器件,可以根据特定的设计需求进行配置和重新配置。

其工作原理是通过配置内部的可编程逻辑单元(PL)和可编程交叉开关(PS)来实现特定的逻辑功能。

2.2 FPGA的设计流程在这一部分,我将详细介绍FPGA的设计流程。

设计流程包括需求分析、系统设计、逻辑设计、验证与仿真、综合与布局布线以及配置下载等环节。

每个环节都十分重要,合理的设计流程能够提高设计效率和设计质量。

第三节:实践过程3.1 项目需求分析在这一部分,我将详细说明我们实训项目的需求分析过程。

我们的项目是基于一个特定的应用场景,需要实现某种功能或解决某种问题。

通过仔细的需求分析,我们能够更好地理解项目目标,为后续的设计和开发奠定基础。

3.2 系统设计和逻辑设计在这一部分,我将阐述我们在系统设计和逻辑设计中的思考和决策过程。

系统设计是指将整个系统划分为模块并确定模块之间的关系和接口。

逻辑设计是指将系统级的功能需求转化为硬件级的逻辑电路实现。

3.3 验证与仿真在这一部分,我将探讨我们在验证与仿真阶段所采取的策略和方法。

验证与仿真是确保设计正确性和功能性的关键环节。

我们使用了仿真工具对设计进行验证,并通过测试案例来确保设计的正确性。

3.4 综合与布局布线在这一部分,我将描述我们在综合和布局布线阶段所采用的策略和工具。

综合将逻辑设计转换为门级设计,并进行时序优化。

布局布线则是将综合后的逻辑电路映射至FPGA芯片,进行优化和布线。

西电 计算机组成实验报告 1

实验一存储器实验一实验题目存储器实验二实验环境Quartus II三实验要求l、掌握FPGA中lpm_ROM的设置,作为只读存储器ROM的工作特性和配置方法。

2、用文本编辑器编辑 mif文件配置 ROM;3、在初始化存储器编辑窗口编辑mif文件配置ROM;4、验证FPGA中meg_lpm_ROM的功能。

四实验设计1、创建mif文件,并写入ROM信息也可以在文本文件添加ROM信息WIDTH=8;DEPTH=32;ADDRESS_RADIX=UNS;DATA_RADIX=UNS;CONTENT BEGIN0 : 4;1 : 3;2 : 2;3 : 4;4 : 3;5 : 2;6 : 1;7 : 5;8 : 0;9 : 3;10 : 6;[11..14] : 0;15 : 4;16 : 7;17 : 4;[18..26] : 0;[27..28] : 4;29 : 0;30 : 2;31 : 0;END;2、连接电路图五实验仿真与测试六实验结果分析仿真结果从上图可以看出,电路输出了ROM中保存的数据。

七实验小结通过本次试验,我掌握了FPGA中lpm_ROM的设置,以及其作为只读存储器ROM的工作特性和配置方法。

学会了用quartus创建并设置mif文件的方法,以及用文本文档修改mif文件方法。

经过这次实验,我学会了quartus的基本使用方法,以及仿真方法。

实验二运算器组成实验一实验题目运算器组成实验二实验环境Quartus II三实验要求1.掌握简单运算器的数据传输通路。

2.验证运算功能发生器的组合功能。

3.掌握算术逻辑运算加、减、与的工作原理。

4.熟悉简单运算的数据传送通路。

5.验证实验台运算的8位加、减、与、直通功能。

6.按给定数据,完成几种指定的算术和逻辑运算。

四实验设计结合上图74181结构设计电路图如下仿真使用数据如下六实验结果分析符合74181的功能,测试通过七实验小结通过本次实验,我学习了加法器74181的使用方法,简单运算器的数据传输通路。

西电微机原理上机报告上机报告

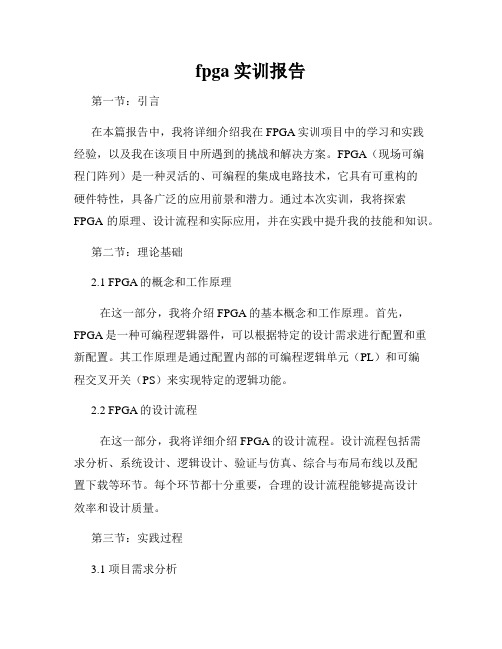

2、利用移位、传送和相加指令实现AX的内容扩大10倍。

(1)流程图如下,是简单的顺序结构。

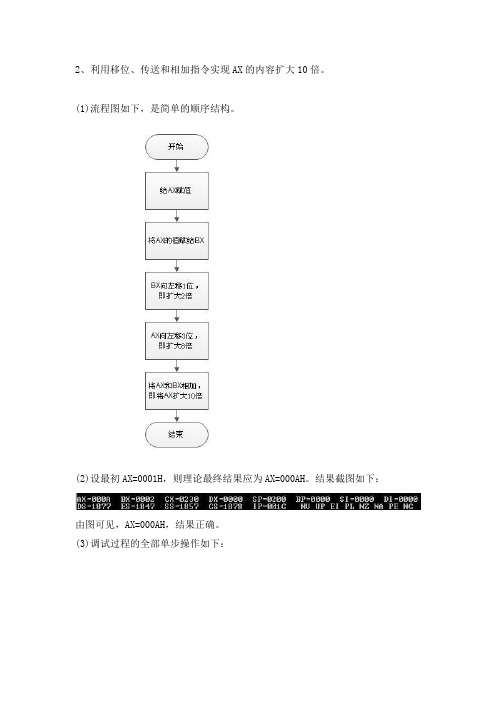

(2)设最初AX=0001H,则理论最终结果应为AX=000AH。

结果截图如下:由图可见,AX=000AH,结果正确。

(3)调试过程的全部单步操作如下:(4)程序代码:DATAS SEGMENT DATAS ENDSSTACKS SEGMENT DW100H DUP(?)TOP LABEL WORD STACKS ENDSCODES SEGMENTASSUME CS:CODES,DS:DATAS,SS:STACKSSTART:MOV AX,DATASMOV DS,AXMOV AX,0003HMOV BX,AXSHL AX,1SHL BX,1SHL BX,1SHL BX,1ADD AX,BXMOV AH,4CHINT21HCODES ENDSEND START3、在缓冲区VAR中连续存放着3个16位的无符号数,编写程序实现将其按递增关系排列;如果VAR中保存的为有符号数,再编写程序实现将其按递减关系排列。

(1)流程图如下。

第一个为无符号数的递增排列;第二个为有符号数的递减排列。

三个数字进行递增或者递减排列,最终结果仅有6种情况。

因此采用多重分支结构,对三个数字进行排列。

(2)将三个无符号数:2500、1000、4500进行递增排列,结果输出为:最终输出AX=03E8H=1000;BX=09C4H=2500;CX=1194H=4500。

结果正确。

将三个有符号数:-2500、-1000、-4500进行递减排列,结果输出为:最终输出AX=03E8H= -1000;BX=09C4H= -2500;CX=1194H= -4500。

结果正确。

(3)调试过程中的全部单步操作如下:(4)程序代码:<1>三个无符号数的递增排列:STACK SEGMENT STACKSTACK ENDSDATA SEGMENTVAR DW2500,1000,4500DATA ENDSCODE SEGMENTASSUME CS:CODE,DS:DATA,SS:STACK START:MOV AX,DATAMOV DS,AXMOV AX,VARCMP AX,VAR+2JBE S1JMP T1S1:CMP AX,VAR+4JAE S2MOV BX,VAR+2CMP BX,VAR+4JAE S3JMP S4T1:MOV AX,VAR+2CMP AX,VAR+4JAE T2MOV BX,VARJAE T3 JMP T4S2:MOV AX,VAR+4 MOV BX,VAR MOV CX,VAR+2 JMP FINS3:MOV AX,VAR MOV BX,VAR+4 MOV CX,VAR+2 JMP FINS4:MOV AX,VAR MOV BX,VAR+2 MOV CX,VAR+4 JMP FINT2:MOV AX,VAR+4 MOV BX,VAR+2 MOV CX,VAR JMP FINT3:MOV AX,VAR+2 MOV BX,VAR+4 MOV CX,VAR JMP FINT4:MOV AX,VAR+2MOV CX,VAR+4JMP FINFIN:MOV AH,4CHINT21HCODE ENDSEND START<2>三个有符号数的递减排序:STACK SEGMENT STACKSTACK ENDSDATA SEGMENTVAR DW-2500,-1000,-4500DATA ENDSCODE SEGMENTASSUME CS:CODE,DS:DATA,SS:STACK START:MOV AX,DATAMOV DS,AXMOV AX,VARCMP AX,VAR+2JGE S1JMP T1S1:CMP AX,VAR+4JLE S2MOV BX,VAR+2CMP BX,VAR+4JLE S3 JMP S4T1:MOV AX,VAR+2 CMP AX,VAR+4 JLE T2 MOV BX,VAR CMP BX,VAR+4 JLE T3 JMP T4S2:MOV AX,VAR+4 MOV BX,VAR MOV CX,VAR+2 JMP FINS3:MOV AX,VAR MOV BX,VAR+4 MOV CX,VAR+2 JMP FINS4:MOV AX,VAR MOV BX,VAR+2 MOV CX,VAR+4 JMP FINT2:MOV AX,VAR+4 MOV BX,VAR+2 MOV CX,VAR JMP FINT3:MOV AX,VAR+2MOV BX,VAR+4MOV CX,VARJMP FINT4:MOV AX,VAR+2MOV BX,VARMOV CX,VAR+4JMP FINFIN:MOV AH,4CHINT21HCODE ENDSEND START5、在变量VAR1和VAR2中分别保存有两个字节型的正整数,编写完整的汇编语言程序实现:(1)当两数中有一个奇数时,将奇数存入VAR1,偶数存入VAR2;(2)当两数均为奇数时,两个变量的内容不变;(3)当两数均为偶数时,两数缩小一半后存入原处。

西电数字信号处理上机实验报告

数字信号处理上机实验报告14020710021 张吉凯第一次上机实验一:设给定模拟信号()1000t a x t e -=,t 的单位是ms 。

(1) 利用MATLAB 绘制出其时域波形和频谱图(傅里叶变换),估计其等效带宽(忽略谱分量降低到峰值的3%以下的频谱)。

(2) 用两个不同的采样频率对给定的()a x t 进行采样。

○1()()15000s a f x t x n =以样本秒采样得到。

()()11j x n X e ω画出及其频谱。

○2()()11000s a f x t x n =以样本秒采样得到。

()()11j x n X e ω画出及其频谱。

比较两种采样率下的信号频谱,并解释。

(1)MATLAB 程序:N=10; Fs=5; T s=1/Fs;n=[-N:T s:N];xn=exp(-abs(n)); w=-4*pi:0.01:4*pi; X=xn*exp(-j*(n'*w)); subplot(211) plot(n,xn);title('x_a(t)时域波形');xlabel('t/ms');ylabel('x_a(t)'); axis([-10, 10, 0, 1]); subplot(212);plot(w/pi,abs(X)); title('x_a(t)频谱图');xlabel('\omega/\pi');ylabel('X_a(e^(j\omega))');ind = find(X >=0.03*max(X))*0.01; eband = (max(ind) -min(ind)); fprintf('等效带宽为%fKHZ\n',eband); 运行结果:等效带宽为12.110000KHZ(2)MATLAB程序:N=10;omega=-3*pi:0.01:3*pi;%Fs=5000Fs=5;T s=1/Fs;n=-N:T s:N;xn=exp(-abs(n));X=xn*exp(-j*(n'*omega));subplot(2,2,1);stem(n,xn);grid on;axis([-10, 10, 0, 1.25]); title('时域波形(f_s=5000)');xlabel('n');ylabel('x_1(n)');subplot(2,2,2);plot(omega/pi,abs(X));title('频谱图(f_s=5000)');xlabel('\omega/\pi');ylabel('X_1(f)');grid on;%Fs=1000Fs=1;T s=1/Fs;n=-N:T s:N;xn=exp(-abs(n));X=xn*exp(-j*(n'*omega));subplot(2,2,3);stem(n,xn);grid on;axis([-10, 10, 0, 1.25]); title('时域波形(f_s=1000)');xlabel('n');ylabel('x_2(n)');grid on;subplot(2,2,4);plot(omega/pi,abs(X));title('频谱图(f_s=1000)');xlabel('\omega/\pi');ylabel('X_2(f)');grid on;运行结果:实验二:给定一指数型衰减信号()()0cos 2at x t e f t π-=,采样率1s f T=,T 为采样周期。

FPGA实验报告

电气技术实践可编程逻辑器件FPGA应用开发实验报告2016年12月目录一、实验目的二、实验要求三、实验内容四、实验代码及实验结果(1)4位二进制加法计数器(2)半加器(3)LED静态显示(4)38译码器(5)点阵扫描显示(6)步进电机状态机五、实验感想六、学习并使用FPGA的心得与体会七、电气技术实践总结一、实验目的1、熟悉使用可编程逻辑器件(Altera公司FPGA Cyclone系列EP1C6Q)。

2、熟悉使用硬件描述语言VHDL。

3、掌握FPGA集成环境(Altera公司FPGA QuartusII 开发流程。

4、熟悉使用核心目标系统板与接口电路等工作原理及其功能模块绑定信息。

5、熟悉并掌握下载线方式和下载文件的选择。

二、实验要求1、学习并掌握文本、图形等输入和时序、功能仿真方法。

2、学习并熟悉门电路、组合电路、时序电路等单一模块功能。

3、学习并设计各种不同状态机逻辑功能。

4、学习并设计由单一模块→较多功能模块集成→系统集成方法。

5、学习并选择多种模式显示(发光二极管显示、米字型数码管显示、七段数码管→动态扫描或静态扫描显示、LED点阵显示各种字符和图形或静止或移动等方式、LCD液晶显示各种字符和图形或静止或移动等方式)。

6、根据自已的兴趣和愿望,可从以下给定的实验目录中选取或自已设定功能题目。

7、实验数目没有要求,关键是看质量,是否是自已编写、调试、实现。

三、实验内容1、按指导书集成开发环境章节操作实现文本编程实例1和图形编程实例2全过程。

2、任选门电路、组合电路、时序电路实验各完成一个其逻辑功能,其实现方案自已规定。

在进行FPGA目标器件输入和输出引脚绑定时,输入引脚绑定高/低电平、单脉冲、各种分频连续脉冲等多种信号,输出引脚可绑定发光二极管、七段数码管、LED点阵等显示模式。

3、在完成1位十进制计数器的基础上,可增加完成2或3等多位十进制计数器逻辑功能并用多位七段数码管来显示。

4、根据状态机工作特点,设计一个有一定功能效果的例程。

西安电子科技大学数字信号处理上机报告

xbn=[1]; xcn=ones(1,10); han=ones(1,10);

2

西安电子科技大学 电子工程学院 02091478 陈步华

hbn=[1,2.5,2.5,1]; yn=conv(xbn,hbn); %计算信号 xb(n)通过系统 hb(n)的响应 y(n) n1=0:length(yn)-1; n2=0:length(hbn)-1; subplot(2,1,1);stem(n1,yn,'.') %绘制 y(n)的时域特性曲线 xlabel('n');ylabel('y(n)') title('y(n)的时域特性曲线') subplot(2,1,2);stem(n2,hbn,'.') %绘制 hb(n)的时域特性曲线 xlabel('n');ylabel('hb(n)') title('hb(n)的时域特性曲线')

subplot(2,1,2);

plot(w/pi,angle(Hb)); xlabel('\omega/π');ylabel('相位') title('DTFT[hb(n)]的相位');

zn=conv(xcn,han); %观察系统 ha(n)对信号 xc(n)的响应特性

figure(4)

n3=[0:length(zn)-1];

2、实验步骤

8ቤተ መጻሕፍቲ ባይዱ

西安电子科技大学 电子工程学院 02091478 陈步华

(1) 复习 DFT 的定义、 性质和用 DFT 作谱分析的有关内容。 (2) 复习 FFT 算法原理与编程思想, 并对照 DIT-FFT 运算流图和程序框图, 读懂 本实验提供的 FFT 子程序。 (3) 编制信号产生子程序, 产生以下典型信号供谱分析用:

西南科技大学FPGA实验报告四2015

西南科技大学实验报告课程名称:FPGA实验名称:硬件电子琴电路设计姓名:学号: 2012 班级:电子12指导教师:西南科技大学信息工程学院制实验题目一、实验原理主系统由3个模块组成,例1是顶层设计文件,其内部有三个功能模块(如图1所示):Speakera.v(例4) 和ToneTaba.v (例3),NoteTabs.v (例2)。

模块ToneTaba是音阶发生器,当8位发声控制输入Index中某一位为高电平时,则对应某一音阶的数值将从端口Tone输出,作为获得该音阶的分频预置值;同时由Code输出对应该音阶简谱的显示数码,如‘5’,并由High输出指示音阶高8度显示。

模块Speakera中的主要电路是一个数控分频器,它由一个初值可预置的加法计数器构成,当模块Speakera由端口Tone获得一个2进制数后,将以此值为计数器的预置数,对端口Clk12MHZ输入的频率进行分频,之后由Spkout向扬声器输出发声。

增加一个NoteTabs模块用于产生节拍控制(Index数据存留时间)和音阶选择信号,即在NoteTabs模块放置一个乐曲曲谱真值表,由一个计数器的计数值来控制此真值表的输出,而由此计数器的计数时钟信号作为乐曲节拍控制信号,从而可以设计出一个纯硬件的乐曲自动演奏电路。

二、实验步骤分四步1、将待播放的《梁祝》音乐音符存入ROM:建立一个.txt的文本文件,将梁祝的音乐音乐音符数据写入,再将后缀名改为.coe文件。

建立一个IP core,名为MUSIC.将MUSIC.core添加到IP core中。

2、建立一个NoteTabs.V文件,从Music.v的ROM(只读存储器)读取数据,进行节拍控制,和音阶选择。

经过仿真无误后进行下一步。

3、建立div_50_12 module,将50MHZ的时钟频率转化成12.5MHZ近似为12MHZ。

4、建立div_50_4 module,对50MHZ的时钟频率分频成4HZ。

FPGA使用入门实验报告示例

FPGA使用入门实验报告示例FPGA使用入门实验报告示例一.实验目的(1)掌握ISE 13.2集成开发环境和Modelsim软件的使用方法;(2)熟悉S6 Card实验板的.使用方法。

(3)掌握使用Verilog HDL语言实现常用组合逻辑和时序逻辑的方法。

(4)了解Chipscope的功能与使用方法。

二.实验内容(1)熟悉S6 CARD实验板;(2)熟悉ISE集成开发环境;(3) 3比特加法器仿真与上板实验(4)m序列产生器仿真与在板Chipscope调试。

三.实验过程依照指导书进行四.实验代码分析(1)3bit加法器(见注释)module m_seq_gen(//端口I/O定义input clk,//定义clk为输入类型input reset,//定义resert为输入类型output seq//定义seq为输出类型);//内部信号说明reg [3:0] state;//定义变量state,为寄存器型,位宽为4//功能定义always @(posedge clk or negedge reset)//当clk上升沿来到或者reset下降沿来到,//触发敏感事件,执行以下程序beginif(!reset)//如果不是reset下降沿来到state <= 4'b1111;//state输出结果为4位的二进制数字1111 elsebeginstate[3:1] <= state[2:0];//state从第二位到第四位输出结果为其第一位//到第三位的数值state[0] <= ^(state & 4'b1001);//state第一位输出结果为state 原来的//值与二进制数1001相与的结果endendassign seq = state[0]; //连续赋值,将state第一位值赋给seqEndmodule(2)m序列测试文件代码分析(见注释)module test_m;// Inputs,将clk和reset定义为寄存器类型reg clk;reg reset;// Outputswire seq;//将seq定义为连线类型// Instantiate the Unit Under Test (UUT)m_seq_gen uut (.clk(clk),.reset(reset),.seq(seq));initial begin// Initialize Inputs,将初始值均设为0clk = 0;reset = 0;// Wait 100 ns for global reset to finish#100;reset = 0;#50 reset = 1;// Add stimulus hereendalways #10 clk = ~clk;//产生测试时钟,延时10s后使时钟取反endmodule五.实验仿真结果分析1.3比特加法器(见注释)(1)功能仿真波形由上图可知加法器功能正常,且当a、b之和大于7时产生进位(2)时序仿真波形板子上拨码开关的6、7、8和1、2、3分别作为加法器的输入,D1-D4 LED灯分别表示cout和sum,拨动拨码开关,观察LED的变化。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

FPGA设计基础实验报告

班级:xxxxxxxx

学号:xxxxxxxxxxx

姓名:xx

教师:xx

1、创建一个工程

File New Project

Family设置为Spart6

Device设置为XC6SLX16

Package设置为CSG234

其他设置为默认

2、设计输入

选择Project->New Source,在左侧文件类型中选择Verilog Module,并输入Verilog文件名

单击Next进入模块定义窗口,在其中填入模块端口定义。

这一步也可以略过,在源代码中再行添加

具体代码略。

3、综合与实现

在工程管理区的view中选择Implementation,然后在过程管理区双击Synthesize-XST,就可以开始综合过程

展开Synthesize-XST,选择View RTL Schematic,可以查看综合出的RTL电路图

添加用户约束文件:

选择Project->New Source,在弹出的对话框中,左侧文件类型选中Implementation Constraints File,右侧填写文件名。

在工程管理区内选择Edit Constraints编辑约束文件,使用Nexys3开发板实现Gate2工程的用户约束文件代码如下所示。

综合完成后,下一个步骤就是实现(Implementation) 。

实现主要分为3个步骤:翻译(Translate) 、映射(Map) 与布局布线(place & Route)。

在ISE中,执行实现过程,会自动执行翻译、映射和布局布线过程:也可单独执行。

在过程管理区双击Implement Design选项,就可以自动完成实现的3个步骤。

4、器件配置

器件配置是FPGA开发最关键的一步,只有将HDL代码下载到FPGA芯片中,才能进行调试并最终实现相应的功能。

首先我们必须生成能下载到硬件中的二进制比特文件。

双击过程管理区的Generate Programming File,ISE就会为设计生成相应的二进制比特文件。

然后利用USB-MiniUSB缆线,来为开发板提供电源和数据下载。

我们只需上网下载免费的Digilent Adept软件,即可快速实现Nexys3开发板上FPGA的配置。

用USB-MiniUSB缆线连接开发板和PC,打开开发板的电源开关。

然后启动Digilent Adept软件。

系统开始自动连接FPGA设备,成功检测到设备后,会显示出JTAG链上所用芯片。

在Browse中找到之前生成的设计的二进制比特文件,并点击旁边的Program按钮,软件就开始对FPGA进行配置。

配置成功后,下面的状态栏会显示Programming Successful。

至此,器件配置成功,我们就可以在器件上验证预期的设计有没有很好的得以实现。

步骤1略

2、设计输入

选择Project->New Source,在左侧文件类型中选择Verilog Module,并输入Verilog文件名。

单击Next进入模块定义窗口,在其中填入模块端口定义。

这一步也可以略过,在源代码中再行添加

具体代码略。

3、综合与实现

在工程管理区的view中选择Implementation,然后在过程管理区双击Synthesize-XST,就可以开始综合过程

展开Synthesize-XST,选择View RTL Schematic,可以查看综合出的RTL电路图

添加用户约束文件:

选择Project->New Source,在弹出的对话框中,左侧文件类型选中Implementation Constraints File,右侧填写文件名。

在工程管理区内选择Edit Constraints编辑约束文件,使用Nexys3开发板实现Gate2工程的用户约束文件代码如下所示。

综合完成后,下一个步骤就是实现(Implementation) 。

实现主要分为3个步骤:翻译(Translate) 、映射(Map) 与布局布线(place & Route)。

在ISE中,执行实现过程,会自动执行翻译、映射和布局布线过程:也可单独执行。

在过程管理区双击Implement Design选项,就可以自动完成实现的3个步骤。

4、器件配置

器件配置是FPGA开发最关键的一步,只有将HDL代码下载到FPGA芯片中,才能进行调试并最终实现相应的功能。

首先我们必须生成能下载到硬件中的二进制比特文件。

双击过程管理区的Generate Programming File,ISE就会为设计生成相应的二进制比特文件。

然后利用USB-MiniUSB缆线,来为开发板提供电源和数据下载。

我们只需上网下载免费的Digilent Adept软件,即可快速实现Nexys3开发板上FPGA的配置。

用USB-MiniUSB缆线连接开发板和PC,打开开发板的电源开关。

然后启动Digilent Adept软件。

系统开始自动连接FPGA设备,成功检测到设备后,会显示出JTAG链上所用芯片。

在Browse中找到之前生成的设计的二进制比特文件,并点击旁边的Program按钮,软件就开始对FPGA进行配置。

配置成功后,下面的状态栏会显示Programming Successful。

至此,器件配置成功,我们就可以在器件上验证预期的设计有没有很好的得以实现。