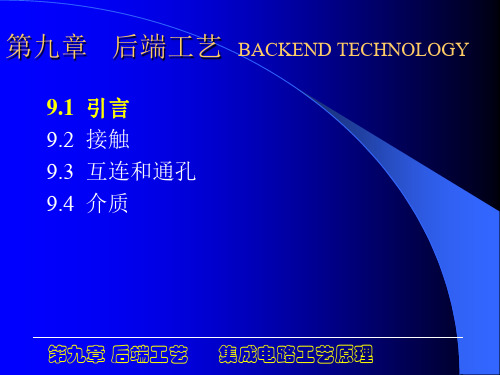

第九章 后端工艺

(二)VLSI后端设计实现

Schematic

版图设计例子5 ------I/O口电路

1、Input VSS

100um* 100um 左右

Nwell接 VDD

VDD

压焊点 (封装引点)

到内部 逻辑电 路

衬底接地

2、Output VSS

100um* 100um 左右

Nwell接 VDD

VDD

压焊点 (封装引点)

到内部 逻辑电 路

衬底接地

版图设计例子5 ------Latch电路

CLR E VDD

D

VSS Q EN

2、INV:剖面图和版图对照

Y V S S A V D D

NMOS

PMOS

3、INV另外一种版图形状

版图设计例子2 ------2输入与非门(或非门)单元设计

Y B V S S V D D

A

NMOS

PMOS

V S S NMOS

A B

V D D Y PMOS

Y B V S S V D D

A

NMOS

vss

Layout Vdd

Schematic

二、VLSI后端设计实现的几种常用方法 1、全定制设计实现

版图设计师从最底层的单元开始设计,所有的单元都是由版图设计师定制完成,包括 逻辑门、I/O口、连线等。电路实现性能较好,但设计效率较低。主要适合于模拟电路和 小规模电路的版图实现(10万门以下)。 2、门阵列实现技术 门阵列是用大量同种门构成的阵列,在排列紧密的单元行之间留有布线通道。一般我 们把布线之前的门阵列称为母片,用户可以根据电路完成最终连线。 3、基于标准单元库的设计 标准单元就是经过实践验证正确的电路单元的集合。包括电路符号库、功能参数库和 版图描述库三个部分。 I 、标准单元的特性 a、包括基本单元、宏单元、I/O单元。 b、 单元一般等高而不等宽。 c、Vdd和Vss的引出端一般在顶部或底部。

半导体后端工艺流程

半导体后端工艺流程【摘要】半导体后端工艺流程是半导体制造过程中的重要环节,涉及多个步骤和技术。

工艺准备阶段是整个流程的第一步,包括材料准备和设备校准等工作。

接着是掩膜图形制作,通过光刻技术将芯片上的电路图案转移到光刻胶上。

然后是晶圆清洁与表面处理,保证芯片表面无尘且具有良好的附着性。

电子束光刻是一种高精度的刻蚀技术,用于制作微小且复杂的芯片结构。

最后是蚀刻与沉积,通过化学腐蚀和沉积来改变芯片表面的性质。

半导体后端工艺流程需要精密的操作和先进的设备支持,是半导体制造中至关重要的环节。

【关键词】半导体后端工艺流程,工艺准备阶段,掩膜图形制作,晶圆清洁与表面处理,电子束光刻,蚀刻与沉积,半导体后端工艺流程总结1. 引言1.1 半导体后端工艺流程概述半导体后端工艺流程是指在半导体芯片制造的最后一道工序,主要包括工艺准备、掩膜图形制作、晶圆清洁与表面处理、电子束光刻和蚀刻与沉积等步骤。

这些步骤在半导体制造过程中起着至关重要的作用,直接影响着芯片的性能和质量。

在半导体后端工艺流程中,工艺准备阶段是整个流程的第一步,包括准备所需的材料、设备和工艺参数设置。

掩膜图形制作是将设计好的电路图案转移到晶圆上的关键步骤,需要通过光刻技术来实现。

晶圆清洁与表面处理是为了去除晶圆表面的杂质和氧化层,保证后续工艺的顺利进行。

电子束光刻是一种高精度的图案转移技术,可以将微米甚至亚微米级别的图案精确地转移到晶圆表面。

蚀刻与沉积是指利用化学蚀刻和蒸发沉积等方法,在晶圆表面形成所需的结构和层。

通过以上步骤的顺利进行,半导体后端工艺流程可以完成芯片的制造,从而生产出高性能、高质量的半导体产品。

半导体后端工艺流程是半导体制造中不可或缺的环节,对整个半导体产业的发展起着重要的推动作用。

2. 正文2.1 工艺准备阶段工艺准备阶段是半导体后端工艺流程中至关重要的一步。

在这个阶段,工程师们需要进行各种准备工作,以确保后续的工艺步骤能够顺利进行。

数字电路后端设计中的一些概念

天线效应:小尺寸的MO S 管的栅极与很长的金属连线接在一起,在刻蚀过程中 ,这根金属线有可能象一根天线一样收集带电粒子 ,升高电位,而且可以击穿 MO S 管的栅氧化层,造成器件的失效。

这种失效是不可恢复的。

不仅是金属连线 ,有时候多晶硅也可以充当天线。

Antenna Ratio(N 冷 G J 二铲包J A rea丫A rea(G K ) MO S 管的输入端开始算起,直至到达该回路最顶层金属线之下的所有金属互连线 (N i ,j ,i 为互连节点所属的金属层号,j 为金属层上的互连节点编号)的面积总和。

在这些金属互连线上将会累积电荷并导致输入端MO S 管栅氧化层出现可能被击穿的潜在危险。

而顶层金属线之下连至输出端晶体管栅极的金属线并不会被计算在内,这是因为在芯片的制造过程中其上多余的游离电荷可以通过低阻的输出端 MO S 管顺畅泻放。

同理,顶层金属线也不会对 A R 的值做出任何贡献,因其最后被刻蚀完成的同时,就标志着从输入 MO S 管到 输出MO S 管的通路正式形成,多余的电荷此时全部可以通过输出端得到泻放。

栅氧化层面积 A re a ga t e则是指各个输入端口所连接到的不同晶体管 (GK )的栅氧化层的面积总和。

以图1所 A 口聞门缸R 日込严铲Z Totallnpu tPorL-X 怕日* 工[inpuu+A 上 匕厲口 12 # inpct (2 )EM (电迁移):电迁移是指金属材料中存在大电流的情况下,金属离子在电流作用下出现宏观移动的现象,日常生活中的家用电线等金属导线由于没有良好 这里的导体面积 A r e a m e t a l 是指从图 1 M eta!3 l\ 实Pli A ri te nn a 的计门的散热能力,稍大的电流强度就会导致保险丝熔断而断路,移现象。

集成电路芯片中的金属连线则不同:它们有良好的散热环境,通常能够承受高达105A/cm2(约为普通家用电线承受极限的100倍)以上的电流强度和由此导致的大约100°C的高温。

第九章--钻削加工

第九章钻削加工钻床是加工内孔的机床,是用钻头在实体材料上加工孔,主要用于加工外形复杂,没有对称旋转轴线的工件,如杠杆、盖板、箱体、机架等零件上的单孔或孔系。

钻孔属粗加工。

·钻削加工的工艺特点(1)钻头在半封闭的状态下进行切削的,切削量大,排屑困难。

(2)摩擦严重,产生热量多,散热困难。

(3)转速高、切削温度高,致使钻头磨损严重。

(4)挤压严重,所需切削力大,容易产生孔壁的冷作硬化。

(5)钻头细而悬伸长,加工时容易产生弯曲和振动。

(6钻孔精度低,尺寸精度为IT13~IT10,表面粗糙度Ra为12.5~6.3μm。

·钻削加工的工艺范围钻削加工的工艺范围较广,在钻床上采用不同的刀具,可以完成钻中心孔、钻孔、扩孔、铰孔、攻螺纹、锪埋头孔和锪凸台端面等,如图所示。

在钻床上钻孔精度低,但也可通过钻孔----扩孔----铰孔加工出精度要求很高的孔(IT6~IT8,表面粗糙度为1.6~0.4μm),还可以利用夹具加工有位置要求的孔系。

在钻床上加工时,工件固定不动,刀具作旋转运动(主运动)的同时沿轴向移动(进给运动)。

第一节钻床钻床的主要类型有:台式钻床、立式钻床、摇臂钻床、铣钻床和中心孔钻床等。

钻床的主参数一般为最大钻孔直径。

一、立式钻床立式钻床是钻床中应用较广的一种,其特点是主轴轴线垂直布置,且位置固定,需调整工件位置,使被加工孔中心线对准刀具的旋转中心线。

由刀具旋转实现主运动,同时沿轴向移动作进给运动。

因此,立式钻床操作不便,生产率不高。

适用于单件小批生产中加工中小型零件。

·立式钻床的传动原理主运动:单速电动机经齿轮分级变速机构传动;主轴旋转方向的变换,靠电动机正反转实现进给运动:主轴随同主轴套筒在主轴箱中作直线移动。

进给量用主轴每转一转时,主轴的轴向移动量来表示二、台钻台式钻床简称台钻,其实质上是一种加工小孔的立式钻床,结构简单小巧,使用灵活方便,适于加工小型零件上的小孔。

钻孔直径一般小于15mm。

集成电路后端工艺

集成电路后端工艺

集成电路后端工艺,是指将设计好的电路图转化为实际硅芯片的制造过程。

该过程主要包括几个关键步骤:晶圆上进行光刻、蚀刻、沉积等工艺步骤,形成电路图案;再通过热处理、离子注入、镀银等技术,进行金属线的连结,最终完成封装封装,形成完整的集成电路芯片。

其中,最具挑战性的环节是制作不同层次之间的互连,即制作金属线路。

该工艺需要极高的精度,通常使用多层金属线来实现电路的连接。

另外,还需要进行严格的质量测试和检查,以确保芯片功能的可靠和稳定。

精细的集成电路后端工艺不仅对电子产品的性能和功能具有重要影响,还在智能制造和信息技术等领域具有重要应用前景。

芯片封装流程的前后端工艺环节

芯片封装流程的前后端工艺环节英文回答:Front-end Process.The front-end process of chip packaging involves the following steps:Wafer preparation: The silicon wafer is cleaned, patterned, and etched to create the integrated circuits (ICs).Die attach: The ICs are attached to a lead frame or substrate using a conductive adhesive.Wire bonding: Gold wires are used to connect the ICs to the lead frame or substrate.Molding: A plastic material is used to encapsulate the ICs and protect them from environmental factors.Back-end Process.The back-end process of chip packaging involves the following steps:Lead finishing: The leads are coated with a protective material such as solder or gold.Testing: The packaged chips are tested to ensure they meet electrical and functional specifications.Shipping: The packaged chips are shipped to the customer.中文回答:前端工艺。

后端工艺流程英文

后端工艺流程英文Backend Technology ProcessIntroduction:Backend technology refers to the implementation of server-side logic that manages data and facilitates communication between the front-end and database. It plays a crucial role in ensuring the smooth functioning of web applications, mobile apps, and other software systems. In this article, we will explore the backend technology process, including its phases and the technologies commonly used.1. Requirement Analysis:The first step in the backend technology process is to analyze the requirements of the project. This involves understanding the functionality and features that the application needs to provide. The backend developer works closely with the clients and the front-end team to gather the necessary information.2. Database Design:Once the requirements are clear, the next step is to design the database structure. This involves identifying the tables, fields, relationships, and constraints required to store and retrieve data efficiently. The backend developer often collaborates with the database administrator to ensure the optimal design.3. Server-side Programming:After the database design is finalized, the backend developer starts writing server-side code. This code is responsible for handling client requests, processing data, implementing business logic, andinteracting with the database. Popular programming languages for backend development include Java, Python, Ruby, and Node.js. 4. API Development:In many cases, the backend serves as an API (Application Programming Interface) that allows the front-end to communicate with the server. The backend developer designs and implements APIs that define the methods and endpoints through which the front-end can send requests and receive responses. API development requires careful consideration of security, scalability, and performance.5. Integration Testing:Once the server-side code and APIs are developed, it is necessary to test their integration with the front-end. Integration testing ensures that the communication between the client-side and server-side components works as expected. Various techniques, such as unit testing and mocking, are employed to simulate different scenarios and identify bugs or issues.6. Performance Optimization:In real-world scenarios, web applications often face heavy traffic and large data volumes. Therefore, it is crucial to optimize the backend performance to ensure fast and responsive user experience. Techniques like caching, load balancing, and using efficient algorithms are employed to achieve the desired level of performance.7. Security Implementation:Data security is a top priority in backend development. Thebackend developer needs to implement security measures, such as encryption, authentication, and authorization, to protect sensitive information and prevent unauthorized access. Regular vulnerability assessments and code reviews are performed to identify and fix security loopholes.8. Deployment and Maintenance:Once the backend technology is developed, it is deployed to production servers. Continuous integration and deployment(CI/CD) processes automate the deployment and ensure a smooth transition from development to production. Regular maintenance and monitoring are carried out to ensure system stability, scalability, and uptime.Conclusion:The backend technology process involves various phases, including requirement analysis, database design, server-side programming, API development, integration testing, performance optimization, security implementation, and deployment. It requires a combination of technical skills, architectural understanding, and attention to detail. By following a systematic approach, backend developers deliver robust and efficient solutions that power modern software systems.。

后端基本概念

为了方便大家尽快找到需要的话题,经icfb版主建议,编辑这个数字后端的FAQ。

如果您是初学者,建议先搜索相关的资料,读读其他人的帖子,一些基本概念在那里都已经讨论过了。

如果您已经有2年以上的实战经验,下面这些雕虫小技就不太值得您去浪费时间了。

先说说作为一个有经验的后端(暫不包括DFT工程师和layout工程师)工程师,需要掌握哪些知识4个级别:1)知道一些基本概念,2)简单地掌握这门技术,3)熟练4)精通半导体工艺--2RTL coding -- 2综合-- 2时序约束-- 3APR -- 3DFT -- 2DRC/LVS -- 3仿真-- 2形式验证-- 2以下是FAQ分类:2楼:时序约束,STA3楼:综合DC/RC4楼:APR (floorplan,place,CTS,route)5楼:验证(LEC,DRC,LVS等)6楼:DFT7楼:低功耗8楼:面试9楼:名词解释时序约束,STA(1) clockQ1.1 什么是同步时钟?时钟频率是整倍数,并且相互之间的相位是固定而且相差可预知的,才可以称得上是同步时钟。

其他的都算异步时钟。

比如,5M,10M是同步2M,3M一般算异步一个时钟,输出到另一个芯片中,转一圈后,以同样的频率返回到自己的芯片,因为无法确定时钟在另一个芯片里面的latency,所以输出的时钟与输入的时钟算异步一个时钟进到2个PLL,就算那2个PLL的输出频率相同,一般也算是异步时钟,除非你de-skewQ1.2 如何处理同步时钟?设计要求严格的公司,就算是同步时钟,数据在同步时钟间传送时,依然要用meta-stability FF,可以set_false_path如果放松要求,不用meta-stability FF,则同步时钟之间是real path,做CTS时,同步时钟要clock tree balance。

注意不同频率的同步时钟的最小时间间隔被用来检查setup如果上升下降沿混用的话,setup的时间间隔就只有半个时钟周期了Q1.3 如何处理异步时钟?很简单,set_false_path注意要from A to B,同时要from B to AQ1.4 如何定义时钟?create_clock 如果指定某个pin/port,就是实时钟,如果没有指定pin和port,就是虚拟时钟巧妙利用waveform选项可以做出不同波形的时钟被定义成时钟的net,在综合时,自动带有ideal network和dont_touch的属性。

键合的后道工艺

键合的后道工艺

键合的后道工艺包括以下几个方面:

1.切割:通过切割机将键合的芯片切成单个或多个尺寸相同的个体。

2.测试:对切割后的芯片进行测试,检验其是否符合质量标准。

3.成品检验:对键合后的完整产品进行严格的成品检验,确保产品质量符合相关标准。

4.封装:将芯片封装在合适的外壳中,以保护其不受到机械损伤、湿度和气候变化等影响。

5.标记和追踪:对每个产品进行标记,以便在产品出现问题时可以快速追踪其来源和质量问题。

6.装配:将芯片组装到其他电子设备中,如手机、电视等。

7.出货:将已经完成所有后道工艺的产品出货给客户。

第九章有机热载体炉的基本知识

• •

•

导热油的一般特性 (二)

• 粘度:是指导热油在规定条件下的稀稠程度及流动性. • 残碳:导热油在高温工作时会裂解或氧化产生胶质、 沥青质及聚合物,形成残碳。残碳值的大小可用以判 别导热油在高温使用中的结焦倾向性。一般要求控制 在残碳值0.03W%。当残碳值超过1.5%时,必须对导 热油进行处理。 • 酸值:是指导热油中的各种有机酸的总和。有机酸达 到一定值时,会对设备管道产生一定程度的腐蚀作用. 一般控制导热油的酸值在0.02mgKOH/g以下,如超 过0.5mgKOH/g时,这种导热油就不能使用了。

导热油的一般特性 (五)

• 毒性:毒性程度的高低是判断导热油使用安全性的一 个重要指标。大多数导热油是无毒的,少数品种的导 热油有一定毒性。有毒的导热油应防止泄露,防止人 和畜沾染中毒事故发生。 • 最高使用温度:表示导热油在这一温度及使用时,能 保持导热油的热稳定性。必须控制有机热载体即导热 油工作温度在其最高使用温度以下,不得超温使用。 • 膜温:导热油流过锅炉受热面时,会在受热面吸附一 层很薄的油膜。油膜温度往往高于主流体温度 10℃~40℃以上,油膜层温度控制不让超温是防止导 热油过热的关键。

导热油的一般特性 (四)

• 密度:导热油的密度大都小于1。 • 外观:其颜色应单一纯净,不应混浊或有悬浮物、沉 淀物,否则不能直接投入使用,应予处理。颜色多为 淡黄色或淡褐色。 • 凝固点:是指其液体转变为固体的温度点。凝固点越 低,导热油的运输、灌装就方便,低温启动就容易。 • 蒸汽压:是导热油的一个重要技术指标。导热油在密 封容器中高温使用时,会产生一些导热油蒸汽。导热 油的饱和蒸汽压力一般很低,大都不超过1MPa,且 多数在0.1MPa表压以下。

有机热载体炉的主要技术参数 (二)

后端流程(初学必看)

基本后端流程(漂流&雪拧)----- 2010/7/3---2010/7/8本教程将通过一个8*8的乘法器来进行一个从verilog代码到版图的整个流程(当然只是基本流程,因为真正一个大型的设计不是那么简单就完成的),此教程的目的就是为了让大家尽快了解数字IC设计的大概流程,为以后学习建立一个基础。

此教程只是本人探索实验的结果,并不代表内容都是正确的,只是为了说明大概的流程,里面一定还有很多未完善并且有错误的地方,我在今后的学习当中会对其逐一完善和修正。

此后端流程大致包括一下内容:1.逻辑综合(逻辑综合是干吗的就不用解释了把?)2.设计的形式验证(工具formality)形式验证就是功能验证,主要验证流程中的各个阶段的代码功能是否一致,包括综合前RTL 代码和综合后网表的验证,因为如今IC设计的规模越来越大,如果对门级网表进行动态仿真的话,会花费较长的时间(规模大的话甚至要数星期),这对于一个对时间要求严格(设计周期短)的asic设计来说是不可容忍的,而形式验证只用几小时即可完成一个大型的验证。

另外,因为版图后做了时钟树综合,时钟树的插入意味着进入布图工具的原来的网表已经被修改了,所以有必要验证与原来的网表是逻辑等价的。

3.静态时序分析(STA),某种程度上来说,STA是ASIC设计中最重要的步骤,使用primetime对整个设计布图前的静态时序分析,没有时序违规,则进入下一步,否则重新进行综合。

(PR后也需作signoff的时序分析)4.使用cadence公司的SOCencounter对综合后的网表进行自动布局布线(APR)5.自动布局以后得到具体的延时信息(sdf文件,由寄生RC和互联RC所组成)反标注到网表,再做静态时序分析,与综合类似,静态时序分析是一个迭代的过程,它与芯片布局布线的联系非常紧密,这个操作通常是需要执行许多次才能满足时序需求,如果没违规,则进入下一步。

6.APR后的门级功能仿真(如果需要)7.进行DRC和LVS,如果通过,则进入下一步。

半导体后端工艺:传统封装方法组装工艺的八个步骤

一、背景介绍半导体是现代电子行业的核心材料,其应用范围广泛,涉及到各种电子设备和系统。

半导体芯片的制作过程包括前端工艺(制作芯片)和后端工艺(封装芯片)。

后端工艺封装芯片是保护芯片、连接外部电路和提高功率传输效率的重要环节。

传统的封装方法组装工艺是后端工艺的关键部分,其包括多个步骤,需要严谨的操作和精密的设备。

二、后端工艺封装的意义半导体芯片在制造完成后需要进行封装,主要是为了保护芯片,连接外部电路和提高功率传输效率。

传统的封装方法组装工艺是后端工艺封装芯片的重要环节,对最终产品的性能和可靠性起到至关重要的作用。

三、传统封装方法组装工艺的八个步骤1. 原材料准备:准备封装芯片所需要的原材料,包括芯片、封装材料、连接线、塑料封装体等。

2. 芯片粘接:将芯片固定在封装底座或引线架上,使用导电胶水或金线等材料进行粘接。

3. 封装体注塑:将上述粘接好的芯片放入封装模具中,通过注塑工艺将封装材料注入模具,形成封装体。

4. 引线焊接:在封装体上焊接连接线,连接线的焊接需要高精度的自动化焊接设备。

5. 封装测试:对封装完成的芯片进行测试,检查连接线是否焊接良好,芯片功能是否正常。

6. 封装涂覆:对封装体进行表面处理,包括防潮、防尘、绝缘涂层等。

7. 功能测试:对封装完成的芯片进行功能测试,验证其性能和可靠性。

8. 包装:将封装完成的芯片进行包装,包括标识、说明书、静电防护包装等。

四、传统封装方法组装工艺的挑战和发展方向传统封装方法组装工艺存在着一些挑战,包括制程复杂、工艺精度要求高、生产效率低等问题。

随着半导体技术的发展,新型封装技术如3D封装、MEMS封装等逐渐成熟,为解决传统封装方法组装工艺的挑战提供了新的思路。

未来,随着智能手机、物联网、人工智能等应用领域的不断扩大,半导体芯片的封装工艺也将不断创新,以满足市场对芯片性能和功能的需求。

传统封装方法组装工艺在半导体后端工艺中扮演着重要的角色,其具体的步骤和发展方向对于半导体行业的发展具有重要意义。

后端工艺的N型欧姆接触

后端工艺的N型欧姆接触徐海铭;秦征峰;寇春梅;黄蕴【摘要】文章首先从原理上较为全面地阐述了欧姆接触形成的必要条件和广泛应用,其次主要针对工艺生产过程中产生的多种n+欧姆接触不良情况进行了汇总分析并提供了相应解决方案。

提出了等离子损伤对欧姆接触电阻有较大影响并对此进行实验对比验证。

伴随着现代工艺的不断发展进步,欧姆接触电阻将会在电路设计应用中越来越受到重视并发挥重大作用。

%This paper introduces the necessary conditions of the ohmic contact formation.Secondly,a variety of bad n+ ohmic contact is analyzed and provided appropriate solutions in process.At the same time plasma damage has a great influence in the ohmic contact that is proposed and verified.【期刊名称】《电子与封装》【年(卷),期】2012(012)003【总页数】4页(P33-35,40)【关键词】欧姆接触;PLASMA;台阶覆盖【作者】徐海铭;秦征峰;寇春梅;黄蕴【作者单位】中国电子科技集团公司第58研究所,江苏无锡214035;中国电子科技集团公司第58研究所,江苏无锡214035;中国电子科技集团公司第58研究所,江苏无锡214035;中国电子科技集团公司第58研究所,江苏无锡214035【正文语种】中文【中图分类】TN451 引言随着半导体技术不断发展,人们对欧姆接触的低阻性能要求也越来越高。

欧姆接触是金属与半导体界面的一种重要接触形式,它会对器件的效率、增益和开关速度等性能指标有直接影响,还可以用于一切器件和电路信号的输入、输出以及各元件间的相互连接。

09第九章 非确定型决策

1、利用决策树进行决策的过程:

• 从右向左逐步后退,从最后端开始算起。

• 首先,计算各个策略点 Hi 的期望损益值,其计算 公式为 E(Hi)=∑PjVij (i=1,2,…,n) • 然后,进行剪树枝,即根据不同节点(策略点) 的期望损益值大小进行选择,未被选取的方案树 枝上画上”||”, 表示剪掉。 • 最后,决策点只留下一条树枝,即为决策的最优 方案。

第九章>>第二节

第二节 风险型决策

第九章>>第二节

• 风险型决策,是指决策者对未来情况无法做出肯

定的判断,但是可以预测不同自然状态发生的概率 以及条件收益。 • 这样决策者采取的每一种策略的预测结果都是用不 同自然状态出现的概率表示的,因此不管决策者采 取哪一种行动方案,都要冒一定的风险,所以这种 决策属于风险型决策。

• 特征:选择每一种方案都具有风险,因为各方案

下的未来结果都是不确定的,每种可能结果只能 估计出来发生的概率。所以做出任何一种决策都 要冒一定的风险,故称为风险型决策。 • 通常要借助于各种结果出现的概率以及数学期望 概念的经济意义来决策。

• 主要内容:

一、期望值决策法 二、决策树法

第九章>>第二节

• 分为 • 单级决策 • 多级决策

这是一个两级 的决策树

利用决策树进行决策的步骤

• (1)画出决策树; • (2)计算各个节点的期望损益,将计算结 果填入决策树; • (3)比较各个方案,进行剪枝决策

2.决策过程:

后端设计

2013-6-17

43

• 部分截图

2013- Cell Placement 注意:这里我们选M1、M2

2013-6-17

45

• 本实验参考步骤 • 选择Place—Specify Placement Blockage for Strip and Route 选择M1、M2;

16

2013-6-17

3、Import Data

• 在linux终端执行:encounter命令,进入图 形界面:

2013-6-17

17

将相关文件和库导进去

• 选择Design—Design Import 在Verilog Netlist 中输入:hardreg.vg hardreg_pad.v; • Top Cell中选择:By User:MY_CHIP_PAD; • 在时间库中Max Timing Libraries: slow.lib tpz973gwc.lib Min timing Libraries: fast.lib tpz973gbc.lib; • 在物理库LEF Files中依次填 写:tsmc18_61m_cic.lef、tpz973g_51m_cic.lef、 tsmc18_61m_antenna_cic.lef、 antenna_6_cic.lef(注意库的顺序不能颠倒,否 则加载报错); • Timing Constraint File: MY_CHIP_PAD.sdc; 18 2013-6-17 IO Assignment File: pad_locs.io

2013-6-17 6

理解流程,明确概念

• 主要流程: RTL仿真综合自动布局布线参数提 取

• 穿插时序分析,形式验证等步骤

2013-6-17

第九章 后端工艺

集成电路工艺原理

• Backend processing is becoming more important.

• Larger fraction of total structure and processing. • Starting to dominate total speed of circuit.

cm2接触电阻rrcs第九章后端工艺集成电路工艺原理金属化层和硅衬底的接触既可以形成整流接触也可以形成欧姆接触主要取决于半导体的掺杂浓度及金半接触的势垒高度heavilydopedsimetalohmiccontactsimetalschottkycontact第九章后端工艺集成电路工艺原理低势垒欧姆接触一般金属和型半导体的接触势垒较低高复合欧姆接触alnsi势垒高度07ev需高掺杂欧姆接触alpsi势垒高度04ev晶体缺陷和杂质在半导体表面耗尽区起复合中心作用第九章后端工艺集成电路工艺原理铝和硅接触的问题spikingproblems硅不均匀溶解到al中并向al中扩散形成孔洞al填充到孔洞微米是不能采用纯铝工艺为了确保铝将si表明的自然氧化层还原和铝和硅良好的物理接触要在450度和氢气中进行退火

第九章Байду номын сангаас后端工艺

集成电路工艺原理

Intel 奔腾 III Merced (1999) 6层金属互连,0.18µ m工艺,集成晶体管数2500万个,连线总长 度达5km

第九章 后端工艺

集成电路工艺原理

电路特征尺寸不断缩小 芯片引线数急剧增加

芯片内部连线长度迅速上升

金属布线层数不断增加

第九章 后端工艺

9.1 9.2 9.3 9.4 引言 接触 互连和通孔 介质

BACKEND TECHNOLOGY

后端精华

1 PRQ1:IR DropIR压降是指出现在集成电路中电源和地网络上电压下降的一种现象。

随着半导体工艺的演进金属互连线的宽度越来越窄,导致它的电阻值上升,所以在整个芯片范围内将存在一定的IR压降。

IR压降的大小决定于从电源PAD到所计算的逻辑门单元之间的等效电阻的大小。

SoC设计中的每一个逻辑门单元的电流都会对设计中的其它逻辑门单元造成不同程度的IR压降。

如果连接到金属连线上的逻辑门单元同时有翻转动作,那么因此而导致的IR压降将会很大。

然而,设计中的某些部分的同时翻转又是非常重要的,例如时钟网络和它所驱动的寄存器,在一个同步设计中它们必须同时翻转。

因此,一定程度的IR压降是不可避免的。

IR压降可能是局部或全局性的。

当相邻位置一定数量的逻辑门单元同时有逻辑翻转动作时,就引起局部IR压降现象,而电源网格某一特定部分的电阻值特别高时,例如R14远远超出预计时,也会导致局部IR压降;当芯片某一区域内的逻辑动作导致其它区域的IR压降时,称之为全局现象。

IR压降问题的表现常常类似一些时序甚至可能是信号的完整性问题。

如果芯片的全局IR压降过高,则逻辑门就有功能故障,使芯片彻底失效,尽管逻辑仿真显示设计是正确的。

而局部IR压降比较敏感,它只在一些特定的条件下才可能发生,例如所有的总线数据同步进行翻转,因此芯片会间歇性的表现出一些功能故障。

而IR压降比较普遍的影响就是降低了芯片的速度。

试验表明,逻辑门单元上5%的IR压降将使正常的门速度降低15%。

危害:1.性能(performance)由管子的Tdelay=c/u可知,电压降低,门的开关速度越慢,性能越差。

2.功能(function)实际上在极端的情况下甚至功能也会受影响的。

在深亚微米下,如果Power/Groun d network做的也很差,然后碰上了很不好的case,IR drop会很大,如果用的是high Vt的process,则DC noisemargin就比较小了。

芯片封装流程的前后端工艺环节及定义

芯片封装流程的前后端工艺环节及定义温馨提示:该文档是小主精心编写而成的,如果您对该文档有需求,可以对它进行下载,希望它能够帮助您解决您的实际问题。

文档下载后可以对它进行修改,根据您的实际需要进行调整即可。

另外,本小店还为大家提供各种类型的实用资料,比如工作总结、文案摘抄、教育随笔、日记赏析、经典美文、话题作文等等。

如果您想了解更多不同的资料格式和写法,敬请关注后续更新。

Tips: This document is carefully written by the small master, if you have the requirements for the document, you can download it, I hope it can help you solve your practical problems. After downloading the document, it can be modified and adjustedaccording to your actual needs.In addition, the store also provides you with a variety of types of practical information, such as work summary, copy excerpts, education essays, diary appreciation, classic articles, topic composition and so on. If you want to know more about the different data formats and writing methods, please pay attentionto the following updates.芯片封装流程的前后端工艺环节及定义在半导体产业中扮演着至关重要的角色,它是将芯片封装成最终产品的关键步骤。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

第九章 后端工艺

9.1 9.2 9.3 9.4 引言 接触 互连和通孔 介质

BACKEND TECHNOLOGY

第九章 后端工艺

集成电路工艺原理

接触

早期结构是简单的AL/Si接触 Early structures were simple Al/Si contacts.

第九章 后端工艺

集成电路工艺原理

比接触电阻的单位 : 欧姆.cm2 接触电阻 R=Rc/S

第九章 后端工艺

集成电路工艺原理

金属化层和硅衬底的接触,既可以形成整流接触, 也可以形成欧姆接触,主要取决于半导体的掺杂 浓度及金-半接触的势垒高度

Ohmic Contact

metal

Heavily doped N+ Si

metal N- Si

Schottky Contact

第九章 后端工艺

集成电路工艺原理

形成欧姆接触的方式

低势垒欧姆接触

Al/p-Si势垒高度 0.4eV 一般金属和 P型半导体 的接触势垒较低

Al/N-Si势垒高度 0.7eV 需高掺杂欧姆接触

高掺杂欧姆接触

高复合欧姆接触

晶体缺陷和杂质在 半导体表面耗尽区起复合中心 作用

第九章 后端工艺

集成电路工艺原理

解决Al Spike的问题

方法2

利用扩散阻挡层( Diffusion Barrier ) – 常用扩散阻挡层:TiN, TiW, stable up to 500C 目前常用TiN淀积在 Ti上的双层结构,Ti和Si 形成TiSi2,接触好,而 TiN电阻率小,但接触 电阻较大。

低介电常数材料必须满足诸多条件,例如:

足够的机械强度以支撑多层连线的架构 高杨氏系数 高击穿电压(>4 MV/cm) 低漏电(<10-9 A/cm2 at 1 MV/cm) 高热稳定性(>450 oC ) 良好的粘合强度 低吸水性 低薄膜应力 Low-k integration 高平坦化能力 低热涨系数以及与化学机械抛光工艺的兼容性 等等

causing hillocks. Cooling back down can place Al under tension voids.

第九章 后端工艺

集成电路工艺原理

解决方法:加入少量的Cu稳定晶界和减少小丘的形成

Adding few % Cu stabilizes grain boundaries and minimizes hillock formation.

第九章 后端工艺

集成电路工艺原理

纯Al金属化系统的不足:

熔点较低和较软

问题之一:

需熔点较高的材料作为 栅 电极( 自对准工艺)和局部 互连线掺杂多晶硅

第九章 后端工艺

集成电路工艺原理

问题之二: 容易在Al中形成小丘和孔洞 由于Al中的应力和扩散造成

Heating places Al under compression

第九章 后端工艺

集成电路工艺原理

铝和硅接触的问题--- "spiking" problems

为了确保铝将Si表明的自然氧化层还原和铝和硅良好的物理 接触,要在450度和氢气中进行退火。然而在此温度,硅在铝中 的溶解度较大。 硅不均匀溶解到Al中,并向Al中扩散, 形成孔洞 ,Al填充到孔洞,引起短路,因此结深大于2-3微米,是 不能采用纯铝工艺

降低台阶高度,获得平坦形貌的工艺称平坦化工艺 第九章 后端工艺 集成电路工艺原理

平坦化是第一个问题--如何解决下节讨论

平坦化 程度定义

Demonstration of Degree of Planarization

第九章 后端工艺

集成电路工艺原理

电迁移是第二个问题

•Al的电迁移仍然是个问题,解决方法:在Al的上、下, 甚至中间加入分流金属层,如Ti,Ti-W,TiN和TiSi等。

第九章 后端工艺

集成电路工艺原理

Undoped SiO2 often used above and below PSG or BPSG to prevent corrosion of Al .

第九章 后端工艺

集成电路工艺原理

介质层(inter-metal dielectric)

SiO2-CVD(SiH4源)、PECVD SiO2(TEOS),SOG…

集成电路工艺原理

介质

Dielectrics

Dielectrics electrically and physically separate interconnects from each other and from active regions.

第九章 后端工艺

集成电路工艺原理

Two types: - First level dielectric - Intermetal dielectric (IMD)

集成电路工艺原理

有多种硅化物应用于集成电路工艺中

第九章 后端工艺

集成电路工艺原理

多层金属互连问题面临新挑战

Multilevel metal interconnects posed new challenges.

早期集成电路是二层金属结构(1970-1980) 当金属互连层增加,不平整的形貌将会使 光刻、淀积和填充等成为严重问题

第九章 后端工艺

集成电路工艺原理

• First level dielectric is usually SiO2 “doped” with P or B or both (2-8 wt. %) to enhance reflow properties. • PSG: phosphosilicate glass, reflows at 950-1100°C

集成电路工艺原理

• Backend processing is becoming more important.

• Larger fraction of total structure and processing. • Starting to dominate total speed of circuit.

第九章 后端工艺

集成电路工艺原理

问题之三:大电流密度(0.1-0.5MA/cm2)下,有 显著的电迁移现象

• 当直流电流流过金属薄膜时,导电电子与金属离子将发 生动量交换,使金属离子沿电子流的方向迁移,这种现象 称为金属电迁移 • 电迁移会使金属离子在阳极端堆积,形成小丘或晶须, 造成电极间短路,在阴极端由于金属空位的积聚而形成空 洞,导致电路开路

第九章 后端工艺

集成电路工艺原理

第九章 后端工艺

集成电路工艺原理

解决spiking问题的方法:

广泛采用的方法是在Al中掺入1-2% Si以满足溶解性,然而 当冷却时,会有硅的分凝并会增加c

方法1:TiSi2/TiN结构 较好的方法是采用阻挡层, Ti 或 TiSi2有好的接触和黏附性, TiN 可作为阻挡层

• BPSG: borophosphosilicate glass, reflows at 800°C.

SEM image of BPSG oxide layer after 800°C reflow step, showing smooth topography over step.

第九章 后端工艺

•分流层在多层布线中机械性能好且它的黏附性好,也是 好的阻挡层。

第九章 后端工艺

集成电路工艺原理

目前集成电路多层布线技术中采用了上述工艺

第九章 后端工艺

集成电路工艺原理

第九章 后端工艺

9.1 9.2 9.3 9.4 引言 接触 互连和通孔 介质

BACKEND TECHNOLOGY

第九章 后端工艺

第九章 后端工艺

9.1 9.2 9.3 9.4 引言 接触 互连和通孔 介质

BACKEND TECHNOLOGY

第九章 后端工艺

集成电路工艺原理

后端工艺技术 :

互连和介质

Backend technology: fabrication of interconnects and the dielectrics that electrically and physically separate them.

第九章 后端工艺

集成电路工艺原理

铝的电迁移

第九章 后端工艺

集成电路工艺原理

金属化层因电迁移引起的平均失效时间MTF

A MTF exp 2 CJ KT

式中 A 金属条横截面积 (cm2) J 电流密度 (A/cm2) 金属离子激活能 (ev) k 玻尔兹曼常数 T 绝对温度 C 与金属条形状、结构有关的常数

为什么早期纯铝作为接触和互连线?

•电阻率低 •和硅和氧化硅的黏附性好

•和重掺杂硅有良好的电接触

•在退火过程,对消除Si-SiO2界面陷阱有促进作用

第九章 后端工艺

集成电路工艺原理

第九章 后端工艺

集成电路工艺原理

特征电阻 Rc

衡量欧姆接触质量的参数是特征电阻Rc J 1 Rc V v0 定义:零偏压下的电流密度对电压偏微商 的倒数

图中硅化物TiSi2可用于;

1. 作为多晶硅栅上的连线 2. 作为和pn结的连线 3. 局部互连线

第九章 后端工艺

集成电路工艺原理

Spacer

第九章 后端工艺

集成电路工艺原理

自对准硅化物工艺

Salicide

Self-aligned silicide (“salicide”) process

第九章 后端工艺

第九章 后端工艺 集成电路工艺原理

Al是主要的互连材料

- low resistivity 低电阻率 对硅和氧化硅黏附性好