重庆大学数电唐治德版第6章触发器和定时器习题

数字电路习题及解答(触发器及时序逻辑电路)

1第8章 触发器和时序逻辑电路——基本习题解答8.4如果D 触发器外接一个异或门,则可把D 触发器转换成T 触发器,试画出其逻辑图。

解:Q n +1=D=T ⊕Q n 故D =T ⊕Q n 如题8.4图所示。

题8.4.图8.5试用T 触发器和门电路分别构成D 触发器和JK 触发器。

解:(1)T 触发器构成D 触发器Q n +1=D =T ⊕Q n ∴T =D ⊕Q n 如题8.5(a )图所示。

题8.5(a )图(2)T 触发器构成JK 触发器Q n +1=n n n n Q K Q J Q T Q T +=+=T ⊕Q n ∴T =n n n n n KQ Q J Q Q K Q J +=⊕+)(如题8.5(b )图所示。

题8.5(b )图8.6逻辑电路如题8.6图(a )所示,设初始状态Q 1=Q 2=0,试画出Q 1和Q 2端的输出波形。

时钟脉冲C 的波形如题8.6图(b )所示,如果时钟频率是4000Hz ,那么Q 1和Q 2波形的频率各为多少?题8.6图(a ) 题8.6图(b )解:JK 触发器构成了T ′触发器,逻辑电路为异步加法计数,Q 1和Q 2端的输出波形如题CP228.6图(c )所示。

Q 1输出波形为CP 脉冲的二分频,Q 2输出波形为CP 脉冲的四分频。

如果CP 脉冲频率为4000Hz ,则Q 1波形的频率是2000Hz ;Q 2波形的频率是1000Hz 。

题8.6图(c )8.8试列出题8.8图所示计数器的状态表,从而说明它是一个几进制计数器。

题8.8图解:F 0:J 0=21Q Q ,K 0=1F 1:J 1=Q 0,K 1=20=Q 0+Q 2 F 2:QJ 2=K 2=1假设初态均为0,分析结果如题8.8图(a )所示,Q 2Q 1Q 0经历了000-001-010-011-100-101-110七种状态,因此构成七进制异步加法计数器。

题8.8图(a )8.9试用主从型JK 触发器组成两位二进制减法计数器,即输出状态为“11”、“10”、“01”、Q Q Q3“00”。

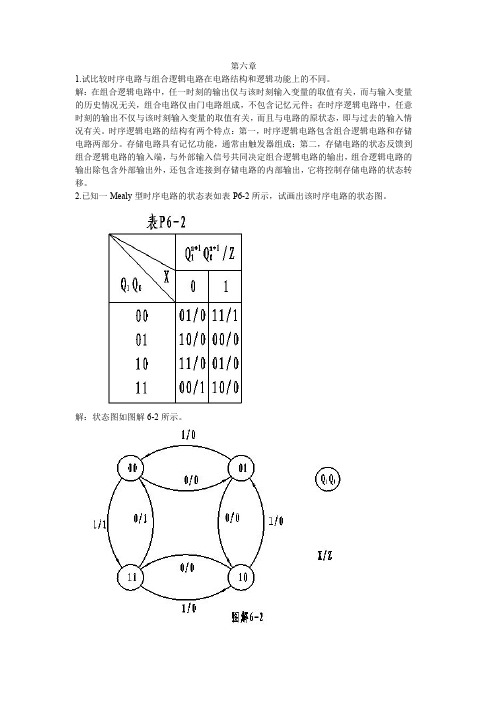

数字逻辑设计第6章 时序逻辑电路习题与解答

将方程代入 D 触发器的状态方程 Q*=D,得状态方程:

Q0*= Q0’,CLK 下降沿触发 Q1*=Q1’,Q0 上升沿触发 Q2*=Q2’, Q1 上升沿触发 根据状态方程可以画出 Q0、Q1、Q2 的波形图如下图所示,由图可见,该电路为 3 位异步二进制减法器。

6-14 用 74HCl61 构成的电路如图 6-77 所示,试分析其逻辑功能。

图 6-77 题 6-14 解:

由图可见,两个十六进制计数器 74HC161 形成级联方式,其中,161(1)的装

入值为 1100,进位输出 CO 接 161(2)的使能端 P 和 T,所以 161(1)为低 4 位,161(2) 为高 4 位,低 4 位计数达到 1111 时,进位输出 CO 有效,使下一时钟 CLK 上升沿 到达时,161(2)开始计数,而 161(2)计数达到 1111 时,其 CO 经反向形成装入 信号,高 4 位的装入值为 0011,所以在反复计数时,161(2)的计范围是从 0011 至 1111,而低 4 位的计数范围是从 1100 至 1111,整个 8 位从 00111100 到 11111111,其计数范围是从 60 到 255,共 196 个状态,所以该电路两片之间是 196 进制计数器。 6-15 试用 74HCl61 构成十一进制计数器。 题 6-15 解:

Q0*= Q0’ Q1*= Q0’Q1’+ Q0Q1 Q2*= Q0’Q1’Q2’+(Q0’Q1’)’Q2 根据状态方程可列出状态转换表如下:

C=1

C=0

Q2 Q1 Q0 000

Q2*Q1*Q0* 001

数字电子技术第6章习题及解答2

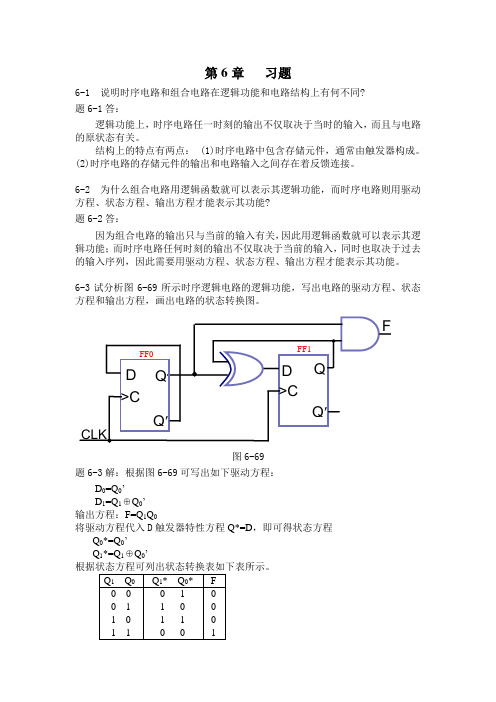

第6章习题解答1. 电路如图6-1所示,试分析其功能。

(1)写出驱动方程、次态方程和输出方程;(2)列出状态表,并画出状态图和时序波形。

图6-1 题1图z解 (1)根据图6-1写出驱动方程'1'21Q Q D =, 12Q D =将其代入D 触发器的特性方程,得每一触发器的状态方程'1'21*1Q Q D Q ==12*2Q D Q ==输出方程为 CP Q z ⋅=2(2)由状态方程可列出状态表如表6-1所示。

按表00,可作出时序波形图如图6-2(b )所示。

图6-2 题1状态图和波形图CP Q 2Q 1z(a )(b )2. 时序电路如图6-3所示。

(1)写出该电路的状态方程、输出方程;(2)列出状态表,画出状态图。

图6-3 题2图解 (1)驱动方程 x K J ==11 122xQ K J ==将其代入JK 触发器的特性方程,的状态方程21'21*21'1*1)'('Q xQ Q xQ Q Q x xQ Q +=+=输出方程 21Q xQ z =(2)假定一个现态,代入状态方程,得出对应的次态和输出状态,列表表示即得状态表,如表6-2所示。

由此算出状态图,如图6-4所示。

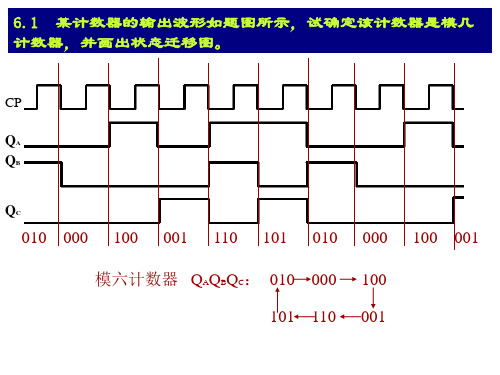

表6-2 题2状态表图6-4 题2的状态图3. 某计数器的输出波形如图6-5所示,试确定该计数器是模几计数器,并画出状态图。

图6-5 题3图CP Q A Q B QC解 由波形图画出状态图,Q C 为高位,Q A 为最低位。

010000001100011101Q C Q B Q A故该波形显示的计数器的计数模为六。

4. 分析如图6-6所示的同步时序电路。

图6-6 题4图解 (1)有题图得到各级触发器的驱动方程为⎪⎪⎩⎪⎪⎨⎧====34231242'3'11)'(Q D Q D Q D Q Q Q Q D(2)列出状态方程为⎪⎪⎩⎪⎪⎨⎧========34*423*312*242'3'11*1)'(Q D Q Q D Q Q D Q Q Q Q Q D Q由驱动方程和状态方程可以确定,该电路是移位寄存器型时序电路,其电路的状态转移决定于第一级的驱动信号。

重庆大学模电(唐治德版)课后习题答案习题7

e + vi _ Re rbe

c +

ib

b

RC

RL

vo _

(d)

解:画出图(d)电路的小信号等效电路:

Av

( Rc // RL )

rbe

rbe Ri Re // 1

Ro Rc

表达式(略)

7.18分别画出题7.18图所示电路的小信号等效电路,并注意标出各电压电流的正 方向;写出各图的电压增益Av及输入电阻Ri、输出电阻Ro的表达式。

Rb1 C1 Rc

+VCC

C2

ib

+ vi _ Rb3

b rbe e

c

ic

ib

+

RL

+ vi

Rb3 Rb2

Re1 Ce

vo

RC Re1

RL

7.20电路如题7.20图(a)所示,晶体管T1、T2的参数分别为β1、β2,rbe1、rbe2,Q点 合适。(1)画出小信号等效电路;(2)写出电压增益Av、输入电阻Ri和输出电 阻Ro的表达式。

+VCC

R3 R1 C1 Rs vs + + vi R2 R4 T1 R6 C2 C4 vo T2 R5 C3 +

解:

(2) C1,C2 为耦合电容,起通交流隔直流的作用。 Ce 为发射极旁路电容,将交流信号旁路。 (3)相同点:都起稳定静态工作点的作用; 不同点:Re2对交流无负反馈作用,而Re1却有。

Rb1 C1 Rs

Rc

+VCC

数字电子技术题目第六章

数字电子技术题目第六章第六章脉冲波形的变换与产生一.填空题1.用555构成的多谐振荡器如图所示,则其振荡频率为f=Hz,占空比q=2.用555构成的多谐振荡器如图所示,则其振荡频率为f=Hz,占空比q=。

3.用555构成的多谐振荡器如图4所示,其中R1=2kΩ,R2=2kΩ,C=10μF,则其振荡频率为f=Hz,占空比q=4.用555定时器构成的多谐振荡器如图2所示,其中R=80kΩ,C=100μF,则输入信号为(选择“高电平”还是“低电平”)时,灯泡L亮;灯泡亮的时间为秒。

二.简答题&计算题1.已知555定时器组成的单稳态触发器如图4所示,试画出电容器上电压波形vc和输出端vo的波形,并计算暂稳态的脉冲宽度。

其中R=10kΩ,C=10μF,要求写出分析计算过程。

uc2.已知如图4所示555定时器组成的施密特触发器中,VCC=9V,试画出输出端vo的波形,要求写出分析计算过程。

3.已知555定时器组成的单稳态触发器如图7所示,试画出电容器上电压波形vc和输出端vo 的波形,并计算脉冲宽度tw。

其中R=20kΩ,C=10μF,要求写出分析计算过程。

uc4.已知如图8所示555定时器组成的施密特触发器中,VCC=9V,试画出输出端vo的波形,要求写出分析计算过程。

(5分)答案一.填空题4.76,2/32.86,3/523.8,2/3低电平,8.8s二.简答题&计算题1.解:tW=1.1RC=1.1×10×103×10×10-6=0.11s2.解:∵∴∴………2分3.解:tW=1.1RC=1.1×20×103×10×10-6=0.22s4.解:∵∴∴。

数字电子技术第6章自测练习及习题解答

自测练习(6.1)1.4位寄存器需要()个触发器组成。

2.图6-1中,在CP()时刻,输入数据被存储在寄存器中,其存储时间为()。

3.在图6-4中,右移操作表示数据从()(FF0,FF3)移向(FF0,FF3)。

SHIFT LOAD为()电平时,寄存器执行并行数据输入操作;4.在图6-7中,当/5.74LS194的5种工作模式分别为()。

6.74LS194中,清零操作为()(同步,异步)方式,它与控制信号S1、S1()(有关,无关)。

7.74LS194中,需要()个脉冲可并行输入4位数据。

8.74LS194使用()(上边沿,下边沿)触发。

9.为了将一个字节数据串行移位到移位寄存器中,必须要()个时钟脉冲。

10.一组数据10110101串行移位(首先输入最右边的位)到一个8位并行输出移位寄存器中,其初始状态为11100100,在两个时钟脉冲之后,该寄存器中的数据为:(a)01011110 (b)10110101 (c)01111001 (d)001011011.42.上升沿,1个CP周期3.FF0,FF34.低5.异步清零,右移,左移,保持,并行置数6.异步,无关7.18.上边沿9.810.(c)01111001自测练习(6.2)1.为了构成64进制计数器,需要()个触发器。

2.2n进制计数器也称为()位二进制计数器。

3.1位二进制计数器的电路为()。

4.使用4个触发器进行级联而构成二进制计数器时,可以对从0到()的二进制数进行计数。

5.如题5图中,()为4进制加法计数器;()为4进制减法计数器。

Q0 Array Q1CP题5图(a )题5图(b )6.一个模7的计数器有( )个计数状态,它所需要的最小触发器个数为( )。

7.计数器的模是( )。

(a )触发器的个数(b )计数状态的最大可能个数(b )实际计数状态的个数 8.4位二进制计数器的最大模是( )。

(a )16 (b )32 (c )4 (d )89.模13计数器的开始计数状态为0000,则它的最后计数状态是( )。

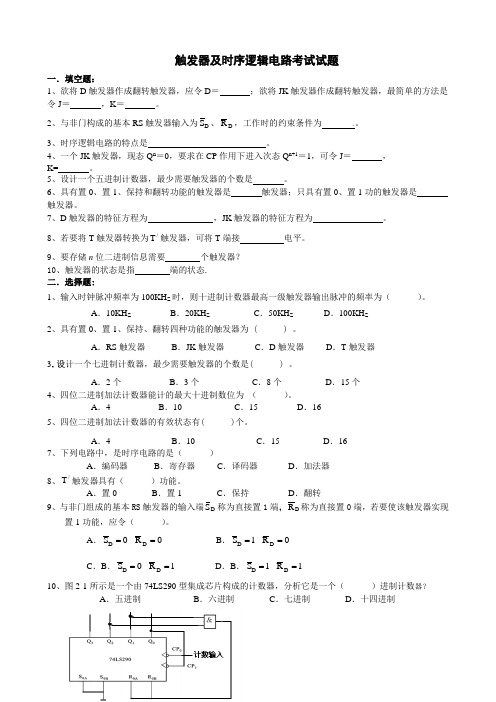

触发器及时序逻辑电路考试试题(电工电子技术大学专业试卷)

触发器及时序逻辑电路考试试题一.填空题:1、欲将D 触发器作成翻转触发器,应令D = ;欲将JK 触发器作成翻转触发器,最简单的方法是 令J = ,K = 。

2、与非门构成的基本RS 触发器输入为D S 、D R ,工作时的约束条件为 。

3、时序逻辑电路的特点是 。

4、一个JK 触发器,现态Q n =0,要求在CP 作用下进入次态Q n+1=1,可令J = , K= 。

5、设计一个五进制计数器,最少需要触发器的个数是 。

6、具有置0、置1、保持和翻转功能的触发器是 触发器;只具有置0、置1功的触发器是 触发器。

7、D 触发器的特征方程为 ,JK 触发器的特征方程为 。

8、若要将T 触发器转换为/T 触发器,可将T 端接 电平。

9、要存储n 位二进制信息需要 个触发器? 10、触发器的状态是指 端的状态. 二.选择题:1、输入时钟脉冲频率为100KH Z 时,则十进制计数器最高一级触发器输出脉冲的频率为( )。

A .10KH ZB .20KH ZC .50KH ZD .100KH Z2、具有置0、置1、保持、翻转四种功能的触发器为 ( ) 。

A .RS 触发器B .JK 触发器C .D 触发器 D .T 触发器3.设计一个七进制计数器,最少需要触发器的个数是( ) 。

A .2个B .3个C .8个D .15个 4、四位二进制加法计数器能计的最大十进制数位为 ( )。

A .4B .10C .15D .16 5、四位二进制加法计数器的有效状态有( )个。

A .4B .10C .15D .167、下列电路中,是时序电路的是( )A .编码器B .寄存器C .译码器D .加法器 8、/T 触发器具有( )功能。

A .置0B .置1C .保持D .翻转9、与非门组成的基本RS 触发器的输入端D S 称为直接置1端,D R 称为直接置0端,若要使该触发器实现置1功能,应令( )。

A .0S D = 0R D =B .1S D = 0R D =C .B .0SD = 1R D = D .B .1S D = 1R D =10、图2-1所示是一个由74LS290型集成芯片构成的计数器,分析它是一个( )进制计数器?A .五进制B .六进制C .七进制D .十四进制三、判断题:( )1、一个十进制计数器可以作为十分频器使用。

数字逻辑电路与系统设计第6章习题及解答.docx

第6章题解:6.1试用4个带异步清零和置数输入端的负边沿触发型JK 触发器和门电路设计一个异步余 3BCD 码计数器。

题6・1解:余3BCD 码计数器计数规则为:0011->0100->—1100-0011-*-,由于釆用 异步清零和置数,故计数器应在1101时产生清零和置数信号,所设计的电路如图题解6.1 所示。

题6.2试用中规模集成异步十进制计数器74290实现模48计数器。

题6.2解:图题解6. 16.3试用D触发器和门电路设计一个同步4位格雷码计数器。

题6.3解:根据格雷码计数规则,\Q1Q OQsQ>\00011110000000011000111111100111\QlQoQ.3Q>\00011110000001011111111110100000X^iQoQ3Q>\00011110000111010001110111100001\QlQoQ.3Q>\00011110001100010011111100100011 Qi Qo计数器的状态方程和驱动方程为:er1=D.=+型Q”+Q;莎er1=D2=+Q©+N Q;N QT = D L+ Q;Q;Q;; +Qj = D o = Q^Q;1+按方程画出电路图即可,图略。

6.5试用4位同步二进制计数器74163实现十二进制计数器。

74163功能表如表6.4所示。

题6・5解:可采取同步清零法实现。

电路如图题解6.5所示。

题6.6解:题6.4解:反馈值为1010c卜一进制计数器CLKCLR LD ENT ENP>c a[―<>40) a D DTC=\5图题解6. 5RCO74163当M=1时:六进制计数器八进制计数器6.7试用4位同步二进制计数器74163和门电路设计一个编码可控计数器,当输入控制变 量M=0时,电路为8421 BCD 码十进制计数器,M=1时电路为5421 BCD 码十进制计数器, 5421BCD 码计数器状态图如下图P6.7所示。

《数电》教材习题答案 第6章习题答案

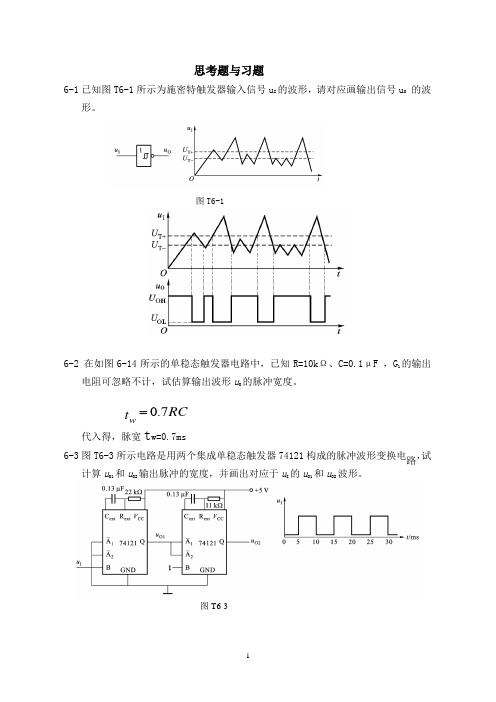

思考题与习题6-1已知图T6-1所示为施密特触发器输入信号u I 的波形,请对应画输出信号u O 的波形。

图T6-16-2 在如图6-14所示的单稳态触发器电路中,已知R=10k Ω、C=0.1μF ,G 1的输出 电阻可忽略不计,试估算输出波形u O 的脉冲宽度。

代入得,脉宽t w=0.7ms6-3图T6-3所示电路是用两个集成单稳态触发器74121构成的脉冲波形变换电路,试计算u O1和u O2输出脉冲的宽度,并画出对应于u I 的u O1和u O2波形。

图T6-3RCt w 7.06-4图T6-4所示电路为可控多谐振荡器,已知tW等于振荡器输出脉冲周期的5倍,请对应u k画u O1和u O2的波形。

图T6-46-5试构成一个如图6-23所示的RC环形振荡器电路,要求振荡器输出信号的频率为1kHZ ,请估算R和C的数值。

若要求振荡频率为1HZ,则R和C又该为多少?解:T≈2.2RC,f=1KHZ,则T=1ms,因此,当f=1KHZ时,RC=0.45ms;当f=1HZ 时,RC=0.45s。

6-6试用555定时器构成一个单稳态电路,要求输出脉冲幅度≥10V,输出脉冲宽度在1-10秒范围内连续可调。

解:根据题意,用555定时器设计得单稳态触发器取R1=22K,R2=18K,分压后输入端电压为6.75V(电源电压为15V),一般的,555定时器得输出高电平不低于其电源电压得90%,因此选15v.则UO输出脉宽t W=1.1RC设C=1000μF,则1≤1.1R×1000×10-6≤ 10 909≤R ≤9K6-7图T6-7是用两个555定时器接成的延迟报警器。

当开关S 断开后,经过一定的延 迟时间后扬声器开始发出声音。

如果在延迟时间内S 重新闭合,扬声器不会发出 声音。

在图中给定的参数下,试求延迟时间的具体数值和扬声器发出声音的频率。

图中的G 1是CMOS 反相器,电源电压为12V 。

重庆大学数字电路技术课件全集第6章_触发器和定时器

3. 触发特点和工作波形图

触发特点: 输入信号R和S直接改变触发器的状态,称为直接触发。 输入信号的任何一次改变,都可能引起触发器状态变化。

工作波形图(时序图)可直观反映触发器的触发特点。 在忽略门电路的传输延时的情况下,绘制触发器工作波 形的步骤是: 1)根据输入信号确定触发时刻tn(任何输入信号的变化 沿都是可能的触发时刻); 2)将时间区间[tn,tn+1)的输入信号值和前一时间区间 (tn-1,tn)触发器的现态代入触发器特性方程计算,或状态表, 得到时间区间(tn,tn+1)上的次态,画出波形图。

R 0

n S Q Qn1 功能说明 0 0 × 禁止 0 1 × 禁止 1 0 0 置0 1 1 0 置0 0 0 1 置1 0 1 1 置1 1 0 0 保持

次态Qn+1的卡诺图

0 0 0 1 1 1 1

1

1

1

保持

n 1 n Q S RQ 约束条件 R S 1

n 1

无↓ ↓ ↓ ↓ ↓

Qn × 0 × 1 0 0 0 1 1 0 1 1

0 0

S

Qn1 0

1 0 1 1 1 0

功能

保持

保持 保持 保持 置1 置1 置0

CP无↓

↓

Qn1 Qn

↓

↓ ↓

1

1 1

0

1 1

1

0 1

0

× ×

置0

禁止 禁止

2)电路特点和波形图

CP=1期间接收输入信号;CP下降沿到来时输出状态 发生改变。即:主从RS触发器的输入数据是CP=1期间的 R、S值,触发器的输出则相对于输入信号延迟到CP的下 降沿变化。

工作原理:

数电第六章答案全部

P6-19 解:由状态图作出状态转移表如表解 6-19 所示,由状态转移表可作出各触发器的次态卡 诺图和输出函数卡诺图如图解 6-19 所示。由图解 6-19 求得各触发器的状态方程和输出函 数,最后求得各触发器的激励函数:

n 1 Q2 Q1 Q0 Q 2 ,

Q1n 1 Q 2 Q0 Q1 Q2 Q1 Q0 Q 2 Q1 Q 0 Q 2 Q0 Q1 Q2 Q0 Q1 , Q0n 1 Q 2 Q 0 Q2 Q1 Q0 ,

3. 试用 JK 触发器和 D 触发器分别构成下列电路: (1) 四位二拍接收数据寄存器; (2) 四位单拍接收数据寄存器。 解: (1) 由 JK 触发器构成的四位二拍接收数据寄存器如图解 6-12(a)所示,由 D 触发器构成的四位二拍接收数据寄存器如图解 6-12(b)所示。

(2) 由 JK 触发器构成的四位单拍接收数据寄存器如图解 6-12(c) , (d)所示, 由 D 触发器构成的四位单拍接收数据寄存器如图解 6-12(e)所示。

J 2 Q1 Q0 , K2 1,

J 1 Q 2 Q0 , K 1 Q2 Q0 ,

J0 Q2 K 0 Q2 Q1

Z Q2 Q11 Q 0

20.设计一个时序逻辑电路,该时序电路的工作波形图由图 P6-20 给出。

图 P6-20 解:该时序电路可视为一个三输出的脉冲分配器,工作波形的周期为八拍,可以先用八进 制计数器产生 8 个状态作为组合电路的输入, 然后通过组合电路产生三路输出, 其电路结 构框图如图解 6-20 所示,组合电路的真值表如表解 6-20 所示。 (设计数器的输出为:

S1 为接收到一个 1 的状态;

S 2 为在收到 1 后接收到一个 0 的状态; S 3 为在顺序收到 10 后接收到一个 1 的状态;

重庆大学模电唐治德课后习题答案习题PPT学习教案

解:

iD

P沟道增强型 MOSFET,其开启电压VT=-4 V。 iD/mA

iD

3

2

vGS 0 VT

VP

N沟 道 耗 尽 型 MOS

vGS 0

1 -4 -2 0 vGS/V

N沟 道 增 强 型 MOS

iD VT

0 vGS

P沟 道 增 强 型 MOS

iD VP

0Leabharlann vGSiD VP0

vGS

IDSS

P沟 道 耗 尽 型 MOS

(1)画出电路的小信号等效电路。 (2)求电压增益Av。 (3)求放大器的输入电阻Ri及输出电阻Ro。

解:(1)小信号等效电路如图(b)所示。

Rg2 C1 +

vi Rg1 _

+VDD

Rd

C2

T+

Rs2

Rg3 Rs1

vo Cs _

(2)

Av

vO vi

gmvgs Rd vgs gmvgs Rs2

3.3

0.92

Ri Rg3 (Rg1 // Rg2) 2.075M

(a)放大电路

+ Rg3 vi

g

d

+

vgs

gmvgs

_s

RO

Rs

//

1 gm

1.02k

第6页/共7页

_ Rg1 Rg2

+ Rs v_o

(b)小信号等效电路

P沟 道 FET

第2页/共7页

iD IDSS

vGS 0

N沟 道 FET

8.13电路如题8.13图所示。设FET(T1)的参数为gm=0.8ms,rd=200kΩ;三极 管(T2)的参数β=40,rbe=1kΩ。 (1)画出放大电路的小信号等效电路。

数字电子技术 第六章习题答案

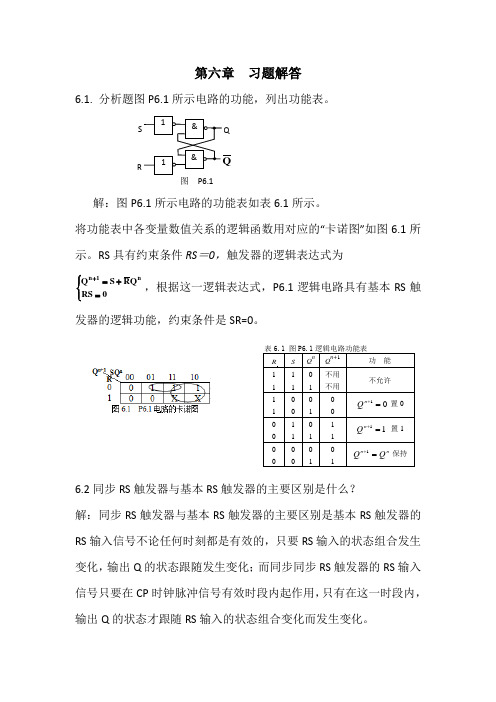

第六章 习题解答6.1. 分析题图P6.1所示电路的功能,列出功能表。

解:图P6.1所示电路的功能表如表6.1所示。

将功能表中各变量数值关系的逻辑函数用对应的“卡诺图”如图6.1所示。

RS 具有约束条件RS =0,触发器的逻辑表达式为⎪⎩⎪⎨⎧=+=+0RS Q R S Q n 1n ,根据这一逻辑表达式,P6.1逻辑电路具有基本RS 触发器的逻辑功能,约束条件是SR=0。

6.2同步RS 触发器与基本RS 触发器的主要区别是什么?解:同步RS 触发器与基本RS 触发器的主要区别是基本RS 触发器的RS 输入信号不论任何时刻都是有效的,只要RS 输入的状态组合发生变化,输出Q 的状态跟随发生变化;而同步同步RS 触发器的RS 输入信号只要在CP 时钟脉冲信号有效时段内起作用,只有在这一时段内,输出Q 的状态才跟随RS 输入的状态组合变化而发生变化。

1& & 1QR图 P6.1QR S Q nQ n+1功 能 1 1 1 1 0 1 不用 不用 不允许11 0 0 0 1 0 0 01=+n Q 置0 0 0 1 1 0 1 1 1 11=+n Q 置10 00 00 10 1n n Q Q =+1 保持6.3如图P6.3 (a)所示电路的初始状态为Q =1,R 、S 端和CP 端的信号如图P6.3(b )所示,画出该同步RS 触发器相应的Q 和Q 端的波形。

解:根据图P6.3 (a)所示电路结构,其功能为同步RS 触发器,电路的特性方程为:⎪⎩⎪⎨⎧=+=+0RS Q R S Q n 1n ,若R=S=1,在CP 时钟脉冲信号为“1”的时段内,触发器的两个输出端的状态均输出“1”,此种情况下,若CP 时钟脉冲信号从“1”状态,跳变为“0”的输入状态,则触发器的两个输出状态为不确定状态。

根据特性方程以及电路的初始状态,作出电路的输出端时序图如图6.3所示。

6.4 主从RS 触发器输入信号的波形如图P6.4(a )、(b )所示。

重庆大学数电唐治德版第6章触发器和定时器习题

VDD

100k

R1 5.1k

84 7 VDD Rd

Rw 3 C3

S

DIS

OUT

R2

6 TH

100k

5

C1

vC 2 TRIG

C-V

GND

C2

C4 33uF

0.01uF

1

0.01uF

图 P6.26

(3)改变R1、R2、和C1可改变555定时器的振荡频率

感谢下 载

2) T JK

T

T : Qn1 TQn TQn T Qn

JK : Qn1 JQ n KQn

令T Qn J Qn KQn 两边同时异或 Qn

则T Qn Qn (JQn KQn ) Qn

T (J Qn KQn ) Qn

J Qn KQn

图略

6.23 用 555 集成定时器组成的单稳态触发器如图 P6.23(a)所示。

图 P6.15

状态转换图-

&Y

解:

Qn1 J Qn KQn X (CP ) JK D触发器

6.19 用JK触发器和或非门构成D和T触发器。

解:

JK : Qn1 J Qn KQn

D : Qn1 D DQ n DQ n

JD KD D

1J

Q

1

C1

T

Qn1

:

TQn

TQn

1K

Q

J K D

100k

5

C1

vC 2 TRIG

C-V

GND

C2

C4 33uF

0.01uF

1

0.01uF

图 P6.26

(2)S断开后,复位端4依靠C4上的充电电压维持一段高电平时 间, 因此C4、RW值越大,铃响持续时间越长。

数字电路第6章习题参考答案

0

n

0

1 1 1

1

0 0 1

1

0 1 0

0

0 0 0

1

1 1 1

0

0 1 1

0

1 0 1

Q2

0 0 0

CP3 Q2 Q3

n 1

0

n

1

0

1

0

1

0

1

0 0 0

0

0 0 0

0

0 1 1

0

0 0 0

Q3

1

1

1 1

n

0

0 0 1

0

1 1 0

1

0 1 0

CP4 CP Q4

n 1

0

0 0 0

00

1000

Q1 n 0 1 0 1 0 1 0 1 0

11 10

0111

Q2n+1 0 1 1 0 0 1 1 0 0

01 11 10

0110

1 0 1 0 1 0 1 0 0

00 01

0101

11 10

10

Q2 n 0 0 1 1 0 0 1 1 0

01

Q4n+1 0 0 0 0 0 0 0 1 0

00 01 11 10

0 1 1 0

X

1 0 0

X

0 0 1

X

1 0 0

Q3n Q2n z Q1 n 00 01 11 10

0 1 1 0 0 0 X X 0 X

1

1

1

X

X

X

从6.9--6.19 共11道题,都是关于74LS90、 74LS160、 74LS194的习题。现将它们总结如下: 异步式2-5-10进制集成计数器74LS90功能表

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

VDD

100k

R1 5.1k

84 7 VDD Rd

Rw 3 C3

S

DIS

OUT

R2

6 TH

100k

5

C1

vC 2 TRIG

C-VLeabharlann GNDC2C4 33uF

0.01uF

1

0.01uF

图 P6.26

(1)S按下后,555定时器的复位端4由低电平变为高电平, 使555定时器成为多谐振荡器,而输出交流脉冲,喇叭鸣响。

(1)R=50kΩ,C=2.2μF,计算输出脉冲宽度

TW 1.1RC 1.1 50 103

Tw

。

2.2

10

6

S

0.121S

反相器 (2) vI 波形见图 P6.23(b), TI >Tw ,对应画出 vC 、 vO 的波形。

(3) v I 的波形见图 P6.23(c), TI < Tw ,对应画出 vC 、 vO 的波形。

VDD

100k

R1 5.1k

84 7 VDD Rd

Rw 3 C3

S

DIS

OUT

R2

6 TH

100k

5

C1

vC 2 TRIG

C-V

GND

C2

C4 33uF

0.01uF

1

0.01uF

图 P6.26

(3)改变R1、R2、和C1可改变555定时器的振荡频率

感谢下 载

Q

Qn1 J Qn KQn (CP )

6.13 已知维持阻塞D触发器输入端CP、A、B的波形如图P6.13所示, 画出输出端Q的波形(设触发器初态为0)。

Q CP

D

A

&

CP AB

B

图 P6.13

D

Q

6.15 电路如图P6.15所示,分析电路逻辑功能,画出状态转换图。

X

1J Q

1

C1 FF

1K Q CP

100k

5

C1

vC 2 TRIG

C-V

GND

C2

C4 33uF

0.01uF

1

0.01uF

图 P6.26

(2)S断开后,复位端4依靠C4上的充电电压维持一段高电平时 间, 因此C4、RW值越大,铃响持续时间越长。

6.26分析图P6.26所示的电子门铃电路,当按下按钮S时可使门铃鸣 响。 (1)说明门铃鸣响时555定时器的工作方式。 (2)改变电路中什么参数能改变铃响持续时间? (3)改变电路中什么参数能改变铃响的音调高低?

D

Q 1J

C1

1K

Q

6. 21 用T触发器构成D和JK触发器。

1) T D

T : Qn1 TQn TQn T Qn

D : Qn1 D DQ n DQ n

令T Qn D

两边同时异或 Qn

则T Qn Qn D Qn

T D Qn

D =1

T

6. 21 用T触发器构成D和JK触发器。

2) T JK

T

T : Qn1 TQn TQn T Qn

JK : Qn1 JQ n KQn

令T Qn J Qn KQn 两边同时异或 Qn

则T Qn Qn (JQn KQn ) Qn

T (J Qn KQn ) Qn

J Qn KQn

图略

6.23 用 555 集成定时器组成的单稳态触发器如图 P6.23(a)所示。

6.1 已知由与非门构成的基本RS触发器的输入波形如图P6.1所示。

画出基本RS触发器的 Q 和Q

端波形。

S R

解:

Q

S

Q

R

图P6.1

Q

Q

6.8 JK触发器的输入端波形如题图P6.8所示,试画出输出端的波形。

Sd

Sd

J

1J Q

CP Sd

CP

C1

K

1K Q

Rd

Rd

Rd

J

K

图 P6.8

解:设初态为1

Q

6.26分析图P6.26所示的电子门铃电路,当按下按钮S时可使门铃鸣 响。 (1)说明门铃鸣响时555定时器的工作方式。 (2)改变电路中什么参数能改变铃响持续时间? (3)改变电路中什么参数能改变铃响的音调高低?

VDD

100k

R1 5.1k

84 7 VDD Rd

Rw 3 C3

S

DIS

OUT

R2

6 TH

单稳态

VDD

vI

8

4

R

7 VDD Rd 3

TI

C

vI

DIS OUT 6 TH

5

TRIG C-V

2

GND

vO

0.01μF

0 vI

(b)

TI

t

1

0

t

(a)

图 P6.23

(c)

图略

6.26分析图P6.26所示的电子门铃电路,当按下按钮S时可使门铃鸣 响。 (1)说明门铃鸣响时555定时器的工作方式。 (2)改变电路中什么参数能改变铃响持续时间? (3)改变电路中什么参数能改变铃响的音调高低?

图 P6.15

状态转换图-

&Y

解:

Qn1 J Qn KQn X (CP ) JK D触发器

6.19 用JK触发器和或非门构成D和T触发器。

解:

JK : Qn1 J Qn KQn

D : Qn1 D DQ n DQ n

JD KD D

1J

Q

1

C1

T

Qn1

:

TQn

TQn

1K

Q

J K D