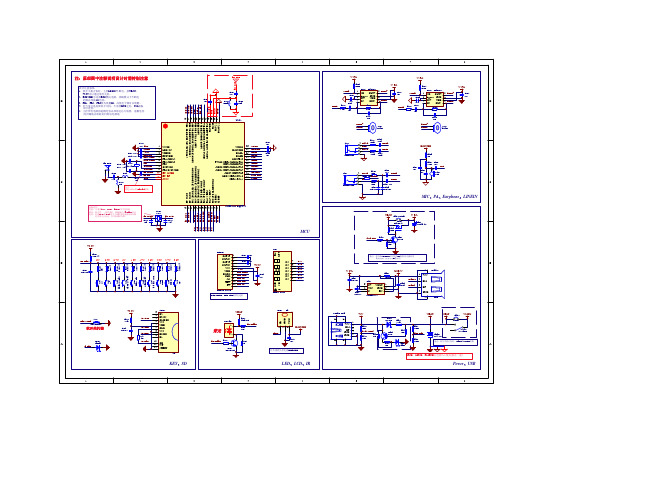

杰理AC6928A蓝牙、插卡单声道音箱方案原理图.PDF

AC6901A蓝牙方案标准原理图V1.0

VCOM DACVDD DACL DACR MIC AUXL AUXR LINEIN PHIN AD_KEY PWR_CTL MUTE

C105 105

J302

C106 105

2 4 3 1

LPF_R PHIN LPF_L

R301 100R

C303 10uF

DACR

DACVDD

DACL R302 100R C304 10uF R306 1K R307 2.2K R304 10K C308 224 C301 105 AUXR AUXL R305 10K C305 NC/202 C307 224 C306 NC/202 C302 102 C309 104 MIC

S401 V-

S402 V+

S410 NC

C/S C/S C/S C/S C/S C/S C/S

7 6 5 4 3 2 1

备注:若功放Shutdown 后功耗为uA级别, 此电路可省, 直接短接,但需考虑U盘耗电

C/S7 C/S6 C/S5 C/S4 C/S3 C/S2 C/S1

B V_PA

C601 NC/105

C110 15P Y101 C111 15P 32.768K C109 2.7P L102 NC L103 0R C113 106

1 2 3 4 5 6 7 8 9 10 11 12

VSSIO LDO_IN VDDIO RTCVDD PR1/ADC12 PR2/ADC13 PR3 OSC32KI PR0/OSC32KO BT_AVDD BT_RF AVSS

LCD_CS LCD_RES LCD_A0 LCD_DATA

BL_LIGHT LCD_CLK USBDM USBDP

BT_OSCI BT_OSCO

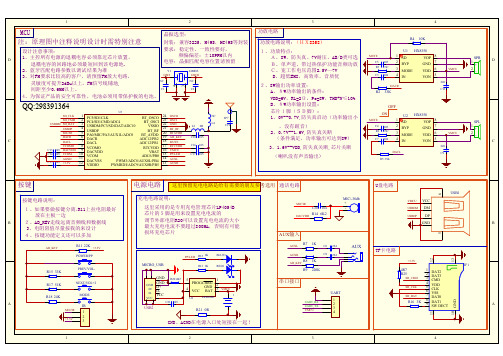

JL杰理AC6925C标准应用原理图.pdf

USB1

MICRO_USB R15 33K R17 51K R18 24K A

MIC/IR +3.3V

13

TF1

RED1

PREV/VOL-

NEXT/VOL+2

MODE

C21 105

R16 3K

GND

GND D+ DVCC

GND GND D+ DVCC

R20 4K7

5

1 PROG CHRG 2 GND 4 3 VCC BAT

C20

DACVDD

104

R14 6K2

B

AUX输入

AUXL

R11 22K

POWER/PP

R7

1K

+3.3V PP/LED R12 1K R13 1K BLUE1

C6 C8

224 224

AUX

TF卡电路

12

+3.3V

AUXR AD_KEY

6 R8 R9 1K 220K 4R7 R25

SD_CMD SD_CLK 1 UART_RX UART_TX VMCU

MIC/-38db + -

U盘电路

VMCU USBDM USBDP

充电电路说明: 这里采用的是专用充电管理芯片LP4054B 芯片的5脚是用来设置充电电流的 调节外部电阻R20可以设置充电电流的大小 最大充电电流不要超过800MA,否则有可能 损坏充电芯片

MIC/IR

VCC DM DP GND B 5

DACL R5 33K

R4 U1

MUTE C5 R3 C3 105 NC 104

10K

设计注意事项: 1、主控所有电源的退耦电容必须靠近芯片放置, 退耦电容的回路地必须最短回到该电源地. 2、蓝牙匹配电路参数以调试结果为准 Y1 OSCI 3、对FM要求比较高的客户,请预留FM放大电路, NC 灵敏度可提升2dBu以上。FM信号线铺地, C1 间距至少0.6MM以上。 4、为保证产品的安全可靠性,电池必须用带保护板的电池。

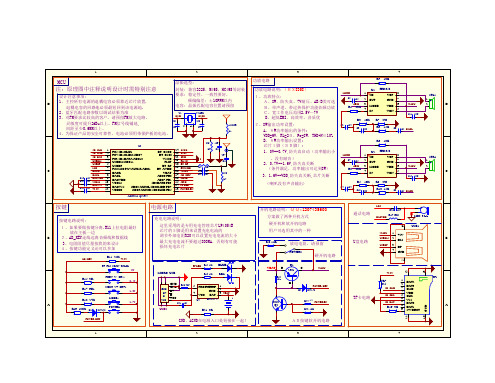

AC6908A方案说明V1.0

C13 105

C19 106

咪头用 -38db的就可以了

DACVDD

R4

6K8

电阻 R14(6K8)目前是 理想参数,不能随意改。

LEDB LEDR R131k R141k BLUE1 PRED1

C

U1 AC6908A

一、AC6908A方案设计要点说明:

充电

LDO_IN

目前AC6908A不支持内部充电管理

ADK_KEY BT_ANT

ADK_KEY R12 22K RTC_VDD

POWER/PP

耳机电路

C5 电容建议预留

DACL+R

R1 0R SPR 1 D + -

OSCO 2 4 3

C2

2P7

R3 9K1

NEXT/VOL+

NC C1

NC C3

LEDR 3 LEDB 4 MIC 5

18 ADK_KEY 17 RTC_VDD C10 105 16 BT_VDD C14 105 15 LDO_IN 14 VBAT 13 12 11 +3V3 SW L1 10UH R1120K

PREV/VOL-

VCCOMO R2 0R

C5 NC

2

R12(22K)上拉一定要接RTCVDD

DACL+R 6 VCCOMO 7

C8

NC

C15 105

BT_VDD

MIC

MIC C21 104

C22 104 NC C9 MIC1

C11 105 DACVDD 8 C12 105 VCOM

SGND C 9 10

解决在特殊情况死机不开机的问题 。

B

BT2 3V7

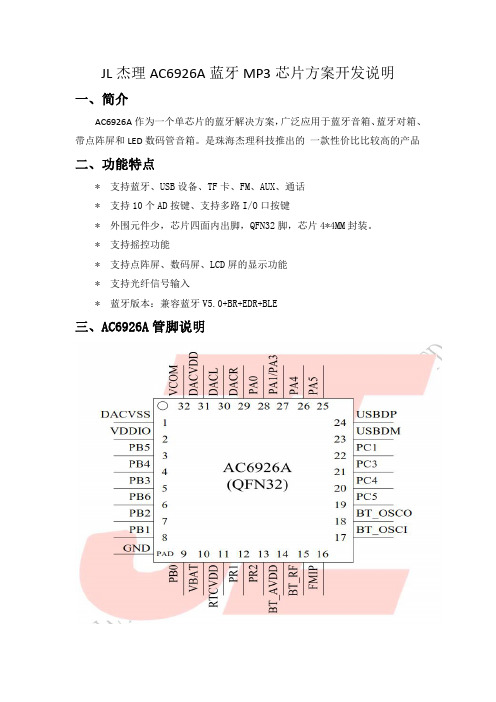

JL杰理AC6926A蓝牙MP3芯片IC方案的开发说明

JL杰理AC6926A蓝牙MP3芯片方案开发说明

一、简介

AC6926A作为一个单芯片的蓝牙解决方案,广泛应用于蓝牙音箱、蓝牙对箱、带点阵屏和LED数码管音箱。

是珠海杰理科技推出的一款性价比比较高的产品二、功能特点

*支持蓝牙、USB设备、TF卡、FM、AUX、通话

*支持10个AD按键、支持多路I/O口按键

*外围元件少,芯片四面内出脚,QFN32脚,芯片4*4MM封装。

*支持摇控功能

*支持点阵屏、数码屏、LCD屏的显示功能

*支持光纤信号输入

*蓝牙版本:兼容蓝牙V5.0+BR+EDR+BLE

三、AC6926A管脚说明

四、芯片资源说明

五、AC692N与之前蓝牙芯片的功能对比分析

六、AC692N功能选型表

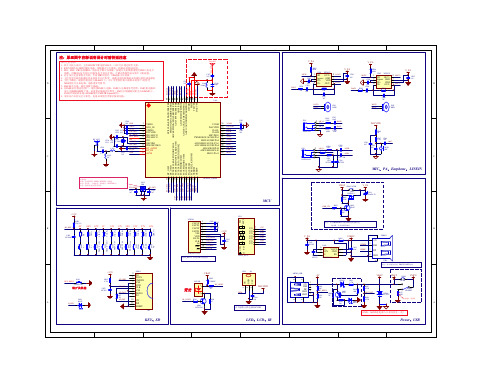

七、AC6926A标准原理图

原理图在网上可以下载到更清晰的资料,同时也可以向我们索取。

杰里的所有系列的芯片,都是一个晶圆,只是根据不同的需求,进行不同方式的封装,也就是说AC6920N系列里面SSOP24和LQFP48封装的晶圆是一样的

注意,AC692N系列的芯片是可以反复烧录的,有想法的朋友可以自己摸索的。

八、提醒说明

*芯片为可编程,由于程序是烧录在芯片内部的flash中,所以可以重复擦除*感兴趣的朋友,可以自己开发,因为AC692N系列不需要开发板,不需要烧录器

*如果要自己开发的话,最好要买一个现成的板子,引出基本的gpio和串口、USB口就可以了。

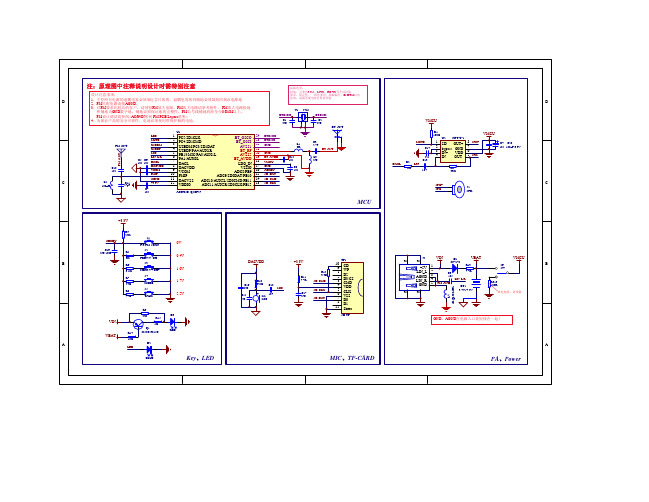

AC6905B单喇叭蓝牙方案标准原理图V1.0

L1 0R C12 105 C8 105

C3 2.7P BT_ANT L3 NC DACL

MUTE C14 225 C13 LPF 104

1 2 3 4

SPK-

R2 7.5K

R3 33K

SPK+ SPK-

C

J1 SPK

MCU

+3.3V

R4 22K ADKEY C19 NC/100P

D

Y1 BTOSCO C1 NC

24M BTOSCI C2 NC BT_ANT

VMCU

R1 100K U2 XPT4871

FM_ANT FM_ANT

C10 102

C

L2 100nH

C11 24pF

1 2 3 4 5 6 7 8 9 10 11 12

PC5/SD1CLK BT_OSCO PC4/SD1CMD BT_OSCI USBDM/PC3/SD1DAT AVSS1 USBDP/PA4/AUX1R BT_RF PB13/MIC/PA3/AUX1L AVSS2 PA1/AUX0L BT_AVDD DACL LDO_IN DACVDD VSSIO VCOM ADC8/PB9 FMIP ADC9/SD0DAT/PB10 DACVSS ADC10/AUX2L/SD0CMD/PB11 VDDIO ADC11/AUX2R/SD0CLK/PB12

S1 P/P/FM_SCAN

0V 0.4V DACVDD 1.0V 1.7V

C16 NC R10 6.8K R11 4.7R C18 104 MIC C17 NC

R5 3K

Hale Waihona Puke S2 PREV/V-/CHS3 NEXT/V+/CH+ S4 MODE S5 TALK

杰理6928B数据手册

AC6928B DatasheetZhuhai Jieli Technology Co.,LTDVersion:V1.0Date:2018.06.12Copyright © Zhuhai Jieli Technology Co.,LTD. All rights reserved.AC6928B FeaturesHigh performance 32-bit RISC CPURISC 32-bit CPUDC-160MHz operationSupport DSP instructions64Vectored interrupts4 Levels interrupt priorityFlexible I/O8 GPIO pinsAll GPIO pins can be programmable as input or output individuallyAll GPIO pins are internal pull-up/pull-down selectable individuallyCMOS/TTL level Schmitt triggered inputExternal wake up/interrupt on all GPIOsPeripheral FeatureOne full speed USB 2.0 OTG controllerOne audio interface supports IIS, left adjusted, right adjusted and DSP mode Four multi-function 16-bit timers, support capture and PWM modeThree 16-bit PWM generator for motor drivingOne 16-bit active parallel portOne full-duplex basic UARTTwo full-duplex advanced UARTOne SPI interface supports host and device modeOne SD Card Host controllerOne IIC interface supports host and device modeOne Quadrate decoderWatchdog1 Crystal Oscillator16-bit Mono DAC with headphone amplifier, SNR >= 95dB1 channel ADC , SNR >= 90dB1 channel MIC amplifier2 channels Stereo analog MUX5 channels 10-bit ADC2 channels 8 levels Low V oltage DetectorPower-on resetEmbedded PMU support low power modeBluetooth FeatureCMOS single-chip fully-integrated radio and basebandCompliant with Bluetooth V5.0+BR+EDR+BLE specificationBluetooth Piconet and Scatternet supportMeet class2 and class3 transmitting power requirementSupport GFSK and π/4 DQPSK all paket typesProvides +2dbm transmitting powerreceiver with -89dBm sensitivitySupport a2dp\avctp\avdtp\avrcp\hfp\spp\smp\att\gap\gatt\rfcomm\sdp\l2cap profile FM TunerSupport worldwide frequency band 76-108MHzFully integrated digital low-IF tuner & frequency synthesizerAutonomous search tuningDigital auto gain control (AGC)Digital adaptive noise cancellationProgrammable de-emphasis (50/75 uS)Receive signal strength indicator (RSSI)Radio search in multi-channel simultaneouslyDigital volume controlPower SupplyVBAT is 2.2V to 5.5VVDDIO is 2.2V to 3.6VRTCVDD is 2.2V to 3.6VPackagesTSSOP20Temperature℃℃Operating temperature: -20 to +70℃℃Storage temperature: -65 to +1501、Pin Definition1.1 Pin AssignmentFigure 1-1 AC6928B_TSSOP20 Package Diagram1.2 Pin DescriptionTable 1-1 AC6928B_TSSOP20 Pin DescriptionPINNO.NameI/OTypeHighDrive(mA)Function OtherFunction 1 PC5 I/O 24GPIOSD1CLKA:SD1 Clock(A);SPI1DOB:SPI1 Data Out(B);UART2RXD:Uart2 Data In(B);IIC_SDA_B:IIC SDA(B);2 PC4 I/O 24GPIOSD1CMDA:SD1 Command(A);SPI1CLKB:SPI1 Clock(B);UART2TXD:Uart2 Data Out(B);IIC_SCL_B:IIC SCL(B);3PC3 I/O24GPIOSD1DAT0A:SD1 Data0(A);SPI1DIB:SPI1 Data In(B);UART0RXC:Uart0 Data In(C);TMR3:Timer3 Clock Input;ADC10:ADC Input Channel 10;USBDM I/O4USB NegativeData(pull down)UART1RXD:Uart1 Data In(D);SPI2DOB:SPI2 Data Out(B);IIC_SDA_A:IIC SDA(A);ADC11:ADC Input Channel 11;4USBDP I/O4USB Positive Data(pull down)UART1TXD:Uart1 Data Out(D);SPI2CLKB:SPI2 Clock(B);IIC_SCL_A:IIC SCL(A);PA4 I/O24 GPIOPWM1:Timer1 PWM Output;AMUX1R:Simulator Channel1 Right;ADC1:ADC Input Channel 1;UART2RXA:Uart2 Data In(A);Touch11:Touch Input Channel 11;5PA0 I/O24GPIOMIC:MIC Input Channel;UART0RXB:Uart0 Data In(B);PA3 I/O24GPIOAMUX1L:Simulator Channel1 Left;ADC0:ADC Input Channel 0;UART2TXA:Uart2 DataOut(A);Touch10:Touch Input Channel10;6 DACL O / DAC Left Channel7 DACVDD P / DACPower8 VCOM P / DACReference9 VSSIO P / Ground 10VDDIOP/IO Power 3.3v11 PB5 I/O 24 GPIOUART0TXB :Uart0 Data Out(B); AMUX0R :Simulator Channel0 Right;SPI1DOA :SPI1 Data Out(A); SD0CLKB :SD0 Clock(B); ADC9:ADC Input Channel 9; Touch5:Touch Input Channel 5; 12 VBAT P / LDO Power 13RTCVDDP/RTC Power 3.3v14 PR1 I/O 10 RTCIO1(output 0V) RESET1:ADC12:ADC Input Channel 12; 15 PR2 I/O 10 RTCIO2 (pull up) RESET2:ADC12:ADC Input Channel 12; 16BT_A VDDP /BT Power 1.3v17 BT_RF P / 18 FMIP I / 19 BT_OSCI I / BT OSC In 20BT_OSCOO/BT OSC Out2、Electrical Characteristics2.1 PMU CharacteristicsTable 2-1Symbol Parameter Min Typ Max Unit Test ConditionsVBAT VoltageInput 2.2 3.7 5.5 VV3.3Voltage output_ 3.3 _ V LDO5V = 5V, 100mA loading V1.2_ 1.2 _ V LDO5V = 5V, 50mA loadingV1.3Voltage output 1.3 V LDO5V=5V, 100mA loadingV DACVDD DAC Voltage _ 3.1 _ V LDO5V = 5V, 10mA loadingI L3.3Loading current _ _ 150 mA LDO5V = 5V2.2 IO Input/Output Electrical Logical CharacteristicsTable 2-2IO input characteristicsSymbol Parameter Min Typ Max Unit Test ConditionsV ILLow-Level InputVoltage -0.3 _ 0.3* VDDIO V VDDIO = 3.3VV IH High-Level InputVoltage0.7*VDDIO_ VDDIO+0.3V VDDIO = 3.3V IO output characteristicsV OLLow-Level OutputVoltage _ _ 0.33 V VDDIO = 3.3VV OH High-Level OutputVoltage2.7 _ _ V VDDIO =3.3V2.3 Internal Resistor CharacteristicsTable 2-3PortGeneralOutputHighDriveInternalPull-UpResistorInternalPull-DownResistorCommentPA0 PA3~PA4PC3~PC58mA 24mA 10K 10K1、USBDM & USBDP default pulldown2、internal pull-up/pull-downresistance | accuracy ±20%3、PR1 default output 04、PR2 default pull upPR1PR2 8mA 10mA 10K 10KUSBDMUSBDP4mA _ 1.5K 15K2.4DAC CharacteristicsTable 2-4Parameter Min Typ Max Unit Test ConditionsFrequency Response20_20KHz1KHz/0dB 10Kohm loading With A-Weighted Filter THD+N _ -69 _ dB S/N _ 95 _ dB Crosstalk _ -80 _ dB Output Swing 1VrmsDynamic Range90 dB 1KHz/-60dB10Kohm loadingWith A-Weighted FilterDAC Output Power11_mW32ohm loading2.5 ADC CharacteristicsTable 2-5Parameter Min TypMaxUnitTest Conditions Dynamic Range85 dB 1KHz/-60dB10Kohm loadingWith A-Weighted FilterS/N _ 90 _ dB 1KHz/-60dB 10Kohm loading With A-Weighted Filter THD+N _ -72 _ dB Crosstalk _ -80 _ dB2.6 BT Characteristics2.6.1 TransmitterBasic Data Rate Table 2-6Parameter Min Typ Max Unit Test ConditionsRF Transmit Power 0 4 dBm 25, ℃ Power SupplyV oltage=5V2441MHzRF Power Control Range20 dB 20dB Bandwidth950KHzAdjacent Channel Transmit Power+2MHz-40 dBm-2MHz -38 dBm +3MHz -44 dBm -3MHz-35dBmEnhanced Data Rate Table 2-7Parameter Min Typ Max Unit Test ConditionsRelative Power 1.2 dB 25, ℃Power Supply V oltage=5V 2441MHz π/4 DQPSK Modulation AccuracyDEVM RMS6%DEVM 99% 10 % DEVM Peak 15 % Adjacent Channel Transmit Power+2MHz -40 dBm-2MHz -38 dBm +3MHz -44 dBm -3MHz -35 dBm2.6.2 ReceiverBasic Data Rate Table 2-8Parameter MinTypMaxUnitTest ConditionsSensitivity-89 dBm 25, ℃Power Supply V oltage=5V 2441MHz Co-channel Interference Rejection-13dBAdjacent Channel Interference Rejection+1MHz +5 dB-1MHz +2 dB+2MHz +37 dB -2MHz +36 dB +3MHz +40 dB -3MHz +35 dBEnhanced Data Rate Table 2-9Parameter MinTypMaxUnitTest ConditionsSensitivity-89 dBm 25, ℃Power Supply V oltage=5V 2441MHz Co-channel Interference Rejection-13dBAdjacent Channel Interference Rejection+1MHz +5 dB-1MHz +2 dB+2MHz +37 dB -2MHz +36 dB +3MHz +40 dB -3MHz +35 dB2.7FM Receiver CharacteristicsTable 2-10Parameter Min Typ Max Unit Test ConditionsInput Frequency 76 108 MHzUsable Sensitivity 3 4 8 dB μVEMF (S+N)/N=26dB Adjacent Channel Selectivity48dB± 200kHzIIP3 88db μV EMF Δ f1=200 kHz,Δ f2=400 kHzAudio Output Voltage 0 3 V Empty loadAudio Frequency Response20 20k Hz DAC testAudio (S+N)/N 52 dBStereo Separation40dBAudio Total Harmonic Distortion (THD)0.4 %3、Package Information3.1 TSSOP20Figure 3-1. AC6928B_TSSOP20 Package4、Revision HistoryDate Revision DescriptionRelease2018.06.12 V1.0 Initial。

蓝牙音箱方案耳机方案之杰理AC692N系列蓝牙、插卡MP3单芯片方案说明与选型

蓝牙音箱、耳机方案之杰理AC692N系列蓝牙、插卡MP3单芯片方案说明与选型一、简要说明随着时间的推移,杰理蓝牙技术也在不断成熟。

这不,杰理今年3月份又推出了AC692N 系列单芯片蓝牙ic。

也必将为今后两年蓝牙音箱和耳机产品的主选方案。

但对大多数的厂家来说,选用什么样的蓝牙芯片方案,也不是一件简单的事情。

以下是我列出了一些现有的主流方案,他们都有自己的市场定位,方案特点,希望对你有所帮助。

二、AC692N系列的优点:(1)、AC692N针对蓝牙音响市场:(2)、音质好,96dB。

(3)、收音效果提升2-3D,收音效果是AC692N最为明显的亮点。

(4)、功耗提升AC690N的40+MA,AC692N的20+MA。

(5)、抗静电提升AC690N600-700V,AC692N2000V。

(6)、DAC白噪声降一些,信噪比可到80多db以上。

三、AC692N选型表:四、杰里692N系列与之前版本的功能比较说明:三、AC692N系列功能引脚说明五、总结虽然市场很大,需求也很大,但是在实际的产品中,我们往往首先会问客的市场定位在哪里,因为只有你的产品市场定位准了,才能去选择的合适的方案。

不可能你产品定位在高端,并且销往欧美,还选用低端的方案。

也不可能你的产品定位低端销往东南亚,而选择高端的方案,所以这一点很重要,也是我们和户沟通中的第一要点。

同时也要考虑自己的产品是否功能有差异化,如果有,就能选择那种高端的方案,为什么呢?因为像CSR、创杰、TI这类的方案,可开的功能实在太少了.如果想灵活的定制很多功能,选则类型的方案是不合适的,可能别人答应可以做,但是实际做的时候往往会卡在一些地方,导致项目进展严重滞后。

所以,有需求的客户,请一定要定位好自己的产品,以及对自己产品的规划,再找到合适、并且有诚意的配合厂家,这样才能保证产品能顺利的走下去.。

杰理AC690N系列液晶点阵屏LCD12864蓝牙音箱开发说明总结

一、简介:目前市场上支持LCD12864液晶显示的方案不多,而性价比最高的还是AC6901A芯片,支持LCD12864显示中文、英文菜单,以及歌词显示二、硬件介绍:1、LCD12864和主芯片的连接电路:1、LCD12864的连接如下:LCD-CS---PB9LCD-RES---PB8LCD-AO---PB10LCD-CLK---PB11LCD-DAT---PB122、TF卡连接PB5、PB6、PB7三个脚3、AUX输入连接PA1、PA2.检测脚连接PA3[低电平有效]4、功放控制脚连接PA4[Q:2491352264]5、ADKEY按键连接PA96、串口打印连接的是PC2连接USB转TTL的RX2、LCD12864的pin脚接口(1)、注意排线使用下接触的,最右边为1脚,12脚可以为空样品链接:排线是12pin的。

正面从右往左数为1脚三、软件开发介绍说明:1、批处理中的文件说明:F_ASCII_S.PIX这个是ASCLL码的点阵库,C文字库,就是A、B、C、D,以及1/2/3/4这些数字的点阵库。

这个直接用,不用管F_GB2312.TAB这个是汉字字库,分GBK和2312,包含了韩文、日文。

这个是索引表这个直接用,不用管和深究F_GB2312_S.PIX这个是对应索引之后的点阵库,就是和“F_GB2312.TAB”相对应的menu.res这个是工具生成的,使用工具生成之后,同步替换[Q:2491352264]ui_sty.sty这个是工具生成的,如果有修改,直接同步替换就可以了1、lcd_disp.c这个文件是指上层的显示界面--这个要做成英文或者多国语音该怎么办??2、lcd_ui_menu.c这个是指的菜单的控制切换--具体原理是什么样的??3、menu.h这个文件是怎么对应点阵库的?基本不用,只看ui.h4、生成图片的那个软件到底怎么使用?见下面的教程5、我要做一个“系统界面”这个任务菜单,切换多国语音的改怎么写这个?见下面教程6、ui_pic(u16id,GUI_POINT*pos);这个坐标是啥意思,x、y的范围是多少?这个是以12864左上角为0点,其中x是0-127,y是0-63ui_pic(DVcRzImg2_1,0);这个的0代表什么意思---代表的是当前的坐标,不特地去指定坐标7、ui.h这个文件里面的图片所以得命名是不是有什么特殊的含义?是不是指的图片的大小或者尺寸见下面的截图详解–和PDV软件生成所对应的8、lcd_disp_text这个函数是如何确定显示的位置的---和ui.h里面文本索引表对应多国语言的主要切换说明,如上图四、上位机工具软件介绍说明:1、上位机软件的存放位置说明:(1)、一定要放在工程目录如上的路径中(2)、这样就生成了对应的坐标之类的东西。

AC6925A双声道蓝牙MP3音箱方案原理图详细说明

1 2 3 4

SD BYP MODE IN

8 7 6 5

C12 226 VMCU

SPR1 1 2 + C

L2

0R NC L4

C16 105 C17 105

R2

33K

R5

10K

R10 15K

按键

按键电路说明: 1、如果要做按键分离, R11上拉电阻最好 放在主板一边 2、AD_KEY走线远离音频线和数据线 3、电阻阻值尽量按我的来设计 4、按键功能定义还可以多加

1

2

3

4 R4 U1

MUTE C5 105 AB/D

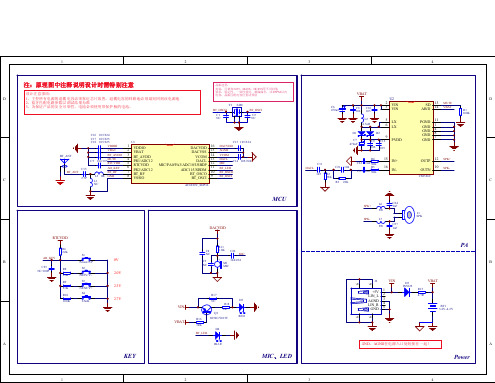

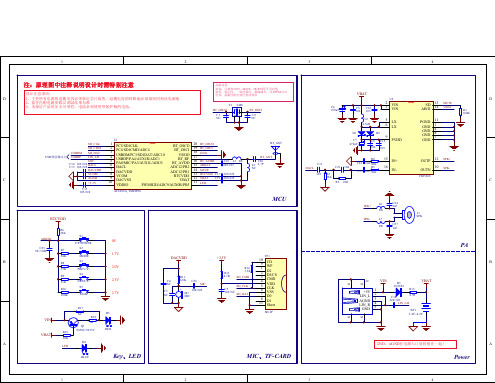

MCU 注:原理图中注释说明设计时需特别注意

D

晶振选型: 封装:兼容3225,M49S,HC49S等封装 要求:稳定性、一致性要好, 频偏偏差:±10PPM以内 电容:晶振匹配电容位置请预留

Y1 OSCI NC 24MHZ OSCO NC C2 180NH L1

R26 100R

MIC

通话电路

DACVDD

C20

104

R14 6K2

+ MIC/-38db USB1

VMCU

1 2 3 4

+5V DM DP GND 5 B

B

放电电阻,请预留

POWER2

U盘电路

USBDM USBDP

R11 22K

硬开机电路

VMCU

+3.3V PP/LED R12 1K R13 1K

C4 104 C10 NC

10K

HX8358 VOP GND VDD VON R7 R9 NC 15K

C6 105 DACL

设计注意事项: 1、主控所有电源的退耦电容必须靠近芯片放置, 退耦电容的回路地必须最短回到该电源地. 2、蓝牙匹配电路参数以调试结果为准 3、对FM要求比较高的客户,请预留FM放大电路, 灵敏度可提升2dBu以上。FM信号线铺地, 间距至少0.6MM以上。 4、为保证产品的安全可靠性,电池必须用带保护板的电池。

AC6901A蓝牙方案标准原理图

R504 NC

C504 105

R601 2K

D602 RED

A

红外接收头供电接DACVDD

GND 、AGND在电源入口处短接在一起!

KEY、SD

LED、LCD、IR

Power、USB

S409 TALK

SD

1 2 3 4 5 6 7 8 9 10 11

C501 C502

105 105

FM MP3

LCD501

备注:若功放 Shut d own后功耗为uA级别, 此电路可省 , 直接短 接,但需考虑U盘耗电

+3.3V

+3.3V LCD_DATA LCD_CLK LCD_A0 LCD_RES LCD_CS

J202 RSPK

C104 105 GND C102 105 C103 105 BT_ANT VMCU +3.3V RTCVDD DC_WKUP KEY_WKUP PR3 OSC32KI OSC32KO BT_AVDD BT_RF GND

BT_OSCI BT_OSCO PC5/SD1CLKA/SPI1DOB/CMO0 PC4/SD1CMDA/SPI1CLKB/COM1 PC3/SD1DATA/SPI1DIB/COM2 PC2/SPI2DIB/COM3 PC1/SPI2DOB/COM4 PA15/SEG15 PA14/SEG14 PC0/SPI2CLKB/COM5 USBDM USBDP

FM_ANT

FM_ANT

V_PA

R203 100K U201 MUTE C205 XPT4871

V_PA V_PA SD bypass IN+ INOUT+ GND VDD OUT8 7 6 5

LOUT+ C201 105 MUTE C206 LOUTR202 7.5K 225 C204 104 R204 100K U202 XPT4871

AC6929C纯蓝牙音箱标准原理图V1.0

OUTN 10

CS8326C

SPK-

R3 22K

C

NC

AC6929C_SOP16

RTCVDD

R6

22K

S1

B

AD_KEY

Power/P/P

0V

C25 NC/100P

R8

S2

33K

PREV/V-

2.0V

R9

S3

51K

NEXT/V+

2.3V

R10 100K

S4 TALK

2.7V

A

KEY

DACVDD

C4 NC

D1

C7 470uF

L2

5

4.7uH

6

D2

9

C9 C12

106 105

LX LX

PVDD

PGND GND GND GND GND

11 1 4 8 7

C11

R4 C22 104 30K

15 IN+

OUTP 12 SPK+

DACL 105

C21 104

R2 22K

R5 C23 104 30K

16 IN-

C3 NC

R11 6.8K

C26 MIC

+

104/224

M1

MIC

MCU

VIN VBAT

7

NC R18

1K

Q1

R16

8850C/9015C

10K D4

BT_LED

D5 RED

BLUE

MIC、LED

6

6

L6

C24

SPK+

1nF

FB

J1

SPK

JL杰理蓝牙音箱AC925F标准原理图标准软件_V1

晶振选型:

封装:兼容3225,M49S,HC49S等封装 要求:稳定性、一致性要好,

频偏偏差:±10PPM以内 电容:晶振匹配电容位置请预留

Y1 OSCI

24MHZ OSCO

BT_ANT

4 3

SDCLK SDCMD SDDAT MIC

C14 105 C6 105 C7 105

U1

B_LED

1 PC5/SD1CLKA

MCU D

C

1

2

设计注意事项: 1、主控所有电源的退耦电容必须靠近芯片放置,

退耦电容的回路地必须最短回到该电源地. 2、蓝牙匹配电路参数以调试结果为准 3、对FM要求比较高的客户,请预留FM放大电路,

灵敏度可提升2dBu以上。FM信号线铺地,

间距至少0. 6MM以上。qq:298391364

4、为保证产品的安全可靠性,电池必须用带保护板的电池。

OSCO OSCI GND

BT_RF BTAVDD AD_KEY MUTE RTCVDD VMCU AUXL AUXR

做耳机使用时接耳机喇叭共用负极

C15 C10 105

2P7

蓝牙天线接法适用倒F型天线 其它的天线要加增益网络

C8 105 C9 105

B_LED R8 1K

播放指示灯

BLED

3

4

音频电路

要音量记忆,开机时是上一次关机时的音量

R9 10K

U2 HX8018

MUTE

1 SD

8 VOP

SPK

C5

105 2

7

1

BYP

GND

+

R3

NC 3

MODE

6 VDD

VMCU

AC6921A蓝牙方案标准原理图V1.0

1 2 3 4 5 6 7 8 9 10 11 12

PB0/SD1DATB/ADC6 VSSIO VBAT RTCVDD PR1/ADC12 PR2/ADC12 PR3/OSC32KI PR0/OSC32KO BT_AVDD BT_RF FMIP VSSIO

DACR SEG1/PA1 SEG2/PA2 ADC0/SEG3/AUX1L/PA3 ADC1/SEG4/AUX1R/PA4 ADC2/SEG5/SD0DATA/PA5 ADC3/SEG6/SD0CMDA/PA6 SEG7/SD0CLKA/PA7 SEG8/PA8 SEG9/PA9 ADC5/SEG10/PA10 SEG11/PA11

R405 9.1K 1%

1.3V

R406 15K 1%

1.7V

R407 24K 1%

2.0V

R408 33K 1%

2.3V

R409 51K 1%

2.7V

R410 100K 1%

3.0V

R411 220K 1%

C402 NC/100P

S404 NEXT/V+/CH+

S403 PREV/V-/CH-

S406 NEXT/CH+

D2 D3/CS CMD/DI VSS VDD CLK VSS D0/DO D1 CD WP SHEET

SD

VMCU

GND VCC

R502 330R/NC BL_LIGHT R503 NC

+5V

D601 1N5819

VBAT

R611 2.7R R607 470K BAT_DET R608 470K BT601 3.4V~4.2V

Q603 8550

R612 10K

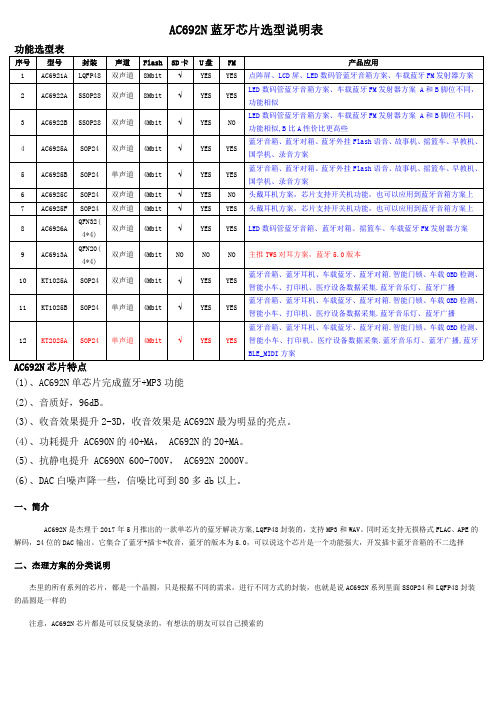

AC692N蓝牙芯片选型说明表

AC692N蓝牙芯片选型说明表功能选型表序号型号封装声道Flash SD卡U盘FM产品应用1AC6921A LQFP48双声道8Mbit√YES YES点阵屏、LCD屏、LED数码管蓝牙音箱方案、车载蓝牙FM发射器方案2AC6922A SSOP28双声道8Mbit√YES YES LED数码管蓝牙音箱方案、车载蓝牙FM发射器方案A和B脚位不同,功能相似3AC6922B SSOP28双声道4Mbit√YES NO LED数码管蓝牙音箱方案、车载蓝牙FM发射器方案A和B脚位不同,功能相似,B比A性价比更高些4AC6925A SOP24双声道4Mbit√YES YES 蓝牙音箱、蓝牙对箱、蓝牙外挂Flash语音、故事机、摇篮车、早教机、国学机、录音方案5AC6925B SOP24单声道4Mbit√YES YES 蓝牙音箱、蓝牙对箱、蓝牙外挂Flash语音、故事机、摇篮车、早教机、国学机、录音方案6AC6925C SOP24双声道4Mbit√YES NO头戴耳机方案,芯片支持开关机功能,也可以应用到蓝牙音箱方案上7AC6925F SOP24双声道4Mbit√YES YES头戴耳机方案,芯片支持开关机功能,也可以应用到蓝牙音箱方案上8AC6926A QFN32(4*4)双声道4Mbit√YES YES LED数码管蓝牙音箱、蓝牙对箱、摇篮车、车载蓝牙FM发射器方案9AC6913A QFN20(4*4)双声道4Mbit NO NO NO主推TWS对耳方案,蓝牙5.0版本10KT1025A SOP24双声道4Mbit√YES YES 蓝牙音箱、蓝牙耳机、车载蓝牙、蓝牙对箱.智能门锁、车载OBD检测、智能小车、打印机、医疗设备数据采集.蓝牙音乐灯、蓝牙广播11KT1025B SOP24单声道4Mbit√YES YES 蓝牙音箱、蓝牙耳机、车载蓝牙、蓝牙对箱.智能门锁、车载OBD检测、智能小车、打印机、医疗设备数据采集.蓝牙音乐灯、蓝牙广播12KT2025A SOP24单声道4Mbit√YES YES 蓝牙音箱、蓝牙耳机、车载蓝牙、蓝牙对箱.智能门锁、车载OBD检测、智能小车、打印机、医疗设备数据采集.蓝牙音乐灯、蓝牙广播,蓝牙BLE_MIDI方案AC692N芯片特点(1)、AC692N单芯片完成蓝牙+MP3功能(2)、音质好,96dB。

AC6928A蓝牙方案标准原理图V1.1

10K

RED

A

D4

LED

MCU

DACVDD

C4 NC

C3 NC

R11 6.8K

C26 MIC

+

104/224

M1

MIC

+3.3V

R13 4.7R

R14 3.3K

SD_CMD

SD_CLK C5

105/NC SD_DAT

TF1

10 9 1 2 3 4 5 6 7 8 11

CD WP D2 D3/CS CMD VDD CLK VSS D0 D1 Sheet

5 6

LX LX

D1

D2

C7

C9

9

C12

PVDD

PGND GND GND GND GND

11 1 4 8 7

C

USB预留测试点

SD_CLK

SD_CMD

USBDM SD_DAT

USBDP LIN_L/R

MIC

C14 C13

105/224 105/224

DACL

DACVDD

VCOM

AGND

+3.3V

1 2 3 4 5 6 7 8 9 10

SD-TF

6

6

L6

C24

SPK+

1nF

FB

J1

SPK

SPK-

L7

FB

C27

1nF

J2

VIN

D3

VBAT

6

IN5822

+5V LIN_L AGND LIN_R

GND

1 2 3 4 5

R15 4.7R C18 224/105 LIN_L/R

AC6925A立体声蓝牙方案标准原理图V1.0

DACL

DACVDD

VCOM

AGND

+3.3V

U1

1 2 3 4 5 6 7 8 9 10 11 12

PC5/SD1CLKA

BT_OSCO

PC4/SD1CMDA/ADC4

BT_OSCI

PC3/SD1DATA/ADC10

VSSIO

USBDM/ADC11

FMIP

USBDP

BT_RF

PA0/MIC/PA4/AUX1R/ADC1 BT_AVDD

A

Power

1

2

3

4

C18 470uF

6.8uH

SS54

D

9 13

U2

SW 22

PVDD PVDD

4、为保证产品的安全可 靠性,电池必须使用带保护 板的电池。

C1

C2

NC

NC

24 AVDD

R7

FM_ANT

C

SD_CLK

SD_CMD

SD_DAT

USBDM

USBDP

MIC

DACR

C23 C22

105/224 105/224

BYP BYP

MIX3901

FB 21

30K R8 30K

LOUTP LOUTN

11 10

LSPK+ LSPK-

ROUTP ROUTN

14 15

RSPK+ RSPK-

R11

COMP SS

1 2

4.7K

C

C24 105/224

AC6925A_QSOP24

MCU

C10

C11

105

105

C30

C31

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

B、单声道、带过热保护功能音频功放

R4 10K

2、蓝牙匹配电路参数以调试结果为准 3、为保证产品的安全可靠性,电池必须用带保护板的电池。

频偏偏差:±10PPM以内 电容:晶振匹配电容位置请预留

Y1 OSCI

24MHZ OSCO

C、宽工作电压范围2.5V—7V D、超低EMI,高效率,音质优

DACVDD

ADC12/PR1

VCOM

RTCVDD

DACVSS

VBAT

VDDIO

PWMH2H/ADC9/AUX0R/PB5

20 19 18 17 16 15 14 13 12 11

OSCO OSCI GND BT_RF BTAVDD AD_KEY C16 MUTE RTCVDD C17 VBAT PP/LED C4

2、8W输出功率设置: A、8W功率输出的条件:

MUTE C5 105

U1 1 SD 2 BYP

HX8358 VOP 8 GND 7

SPL1 1

+

NC

NC

4 3

C1

C2

VDD=6V,RL=2Ω,Po=8W,THD+N≤10% B、8W功率输出设置:

VBAT R1 33K

3 MODE 4 IN

VDD 6 VON 5

B

TF卡电路

13

12

+3.3V

TF1

4R7 R25

SD_CMD

SD_CLK

SD_DAT R16 3K

1 2 3 4 5 6 7 8 9

DAT2 DAT3 CMD VDD CLK VSS DAT0 DAT1 SW DECT

A

11

10 GND

1

2

3

4

GND GND GND D+ D+ DD- VCC VCC

R20 4K7

C21 105

USB2

5 4

PROGCHRG GND

VCC BAT

1 2 3

VBAT

U4

LP4054B

1

R21 0R

GND、AGND在电源入口处短接在一起!

通话电路

MIC C20 104

R14 6K2 DACVDD

+ -

MIC/-38db

A

R19 100K

POWER1

2.7V

电源电路

充电电路说明:

这里采用的是专用充电管理芯片LP4054B 芯片的5脚是用来设置充电电流的 调节外部电阻R20可以设置充电电流的大小 最大充电电流不要超过800MA,否则有可能 损坏充电芯片

MICRO_USB

PP/LED R12 1K R13 1K

BLUE1 RED1

L2 105

105

105

0R

2P7 C19

NC L4

,没有跛音) 2、0.7V--1.6V,防失真关断

C3 104

C9 NC

R9 15K C6 105 DACR+L

(条件满足,功率输出可达到8W)

C

3、1.6V--VDD,防失真关断,芯片关断

(喇叭没有声音输出)

QQ:1207435600

按键

按键电路说明:

1、如果要做按键分离,R11上拉电阻最好

放在主板一边

B

2、AD_KEY走线远离音频线和数据线

3、电阻阻值尽量按我的来设计

4、按键功能定义还可以多加

AD_KEY

R11 22K RTCVDD

PP/POWER 0V

R15 24K

MODE

1.7V

R17 33K

PREV/VOL-

2.0V

R18 51K

NEXY/VOL+ 2.3V

VCOM 8

SGND 9

+3.3V 10

PC5/SD1CLK

BT_OSCO

PC4/SD1CMD/ADC4

BT_OSCI

USBDM/PC3/SD1DAT/ADC10

VSSIO

USBDP/PA4/AUX1R/ADC1

BT_RF

PA0/MIC/PA3/AUX1L/ADC0 BT_AVDD

DACL

ADC12/PR2

1

2

3

4

MCU 注:原理图中注释说明设计时需特别注意

功放电路 功放电路说明:(HX8358)

设计注意事项:

晶振选型:

1、功放特点:

1、主控所有电源的退耦电容必须靠近芯片放置,

D

封装:兼容3225,M49S,HC49S等封装

A、8W、防失真、7V耐压、AB/D类可选

D

退耦电容的回路地必须最短回到该电源地.

VBAT

2-

芯片1脚(SD脚):

C11 226

U3

AC6928A_TSSOP20

1、0V--0.7V,防失真启动(功率输出小

R3 10K R7 NC

C

USBDM

C13 105 C14 105 C15 105

SD_CLK 1

SD_CMD 2

SD_DAT 3

USBDP 4

MIC

5

DACR+L 6

DACVDD 7