USRPN210使用说明

USRPN210使用说明

19

体系结构

Transmitter

User-defined Code

ETH

FPGA

DAC

PC

USRP-N210 (mother board)

RF Front end

Daughter board

Receiver

User-defined Code

ETH FPGA

ADC

RF Front end

PC

USRP-N210 (mother board)

Daughter board

20

体系结构-硬件

User-defined Code

ETH FPGA

ADC DAC

RF Front end

RX2400 2.3-2.9 GHz Transceiver 50mW output (17dBm) 0-70dB Gain Direct conversion architecture Transceiver switch

2

软件无线电技术和USRP

软件无线电

From FCC : “We view software radios as the result of an evolutionary process from purely hardware-based equipment to fully software-based equipment. In this regard, the process can be roughly described in three stages

See: /uhd_docs/manual/html/build.html

青岛明博pg210便携式气体探测器说明书

青岛明博环保科技有限公司PG210便携式气体探测器使用说明书1产品概述PG210便携式气体探测器(以下简称探测器),是一种可连续检测作业环境中可燃性气体浓度或者有毒有害气体浓度的本质安全型仪器。

它适用于防爆、有毒气体泄漏抢险、地下失。

探测器为自然扩散方式检测气体浓度,采用进口电化学传感器(可燃气为催化燃烧式),具有极好的灵敏度和出色的重复性;仪器采用嵌入式微控制技术,中文菜单操作简单,功能齐全,可靠性高,整机性能居国内领先水平。

探测器外壳采用高强度工程材料、复合弹性橡胶的双色材料精制而成,强度高、手感好,并且防水、防尘、防爆。

2主要功能及技术指标2.1主要功能仪器采用先进的16位超低功耗嵌入式微控制器STN型超大中文液晶显示开机全功能自检测,传感器、电池、电路和报警功能用户可自行设置高低报警点,屏幕显示报警类别中文标定菜单一键标定,方便用户标定电池电量实时显示,欠压提示,低压自动关机三重充电保护,充电时自动关机、充满时探测器自动切断电池电路、智能充电器停止输出电流具有实时时钟功能可更换的模块化传感器自动校准功能,减小测量误差两级三重报警(声、光、振动),不易忽略毒性气体另有STEL和TWA报警存储数据2000条密码管理功能,重要操作需密码验证,有效防止误操作10秒内不进行菜单操作自动退出2.2技术指标测量范围:见附表适用气体:可燃气体、毒性气体、氧气报 警 点:参见附表1显示误差:≤±3% F.S响应时间:T<30s显示方式:STN型大屏LCD显示实时数据及系统状态报警提示:广角发光二极管、85dB蜂鸣音随浓度增加频率加大、振动三重报警 故障指示:零点漂移提示、传感器故障提示工作环境:-30℃~+50℃;湿度<95%RH 无结露 工作电压:DC3.6V锂离子电池,1200mAh 充电时间: 4h~6h工作时间: 可燃气体≮ 8h 连续;毒性气体≮ 300h 连续 防护等级:IP66重 量: 约120g(包含电池)外观尺寸: 102mm×56mm×26mm3结构与功能3.1外观3.2显示信息1.电池电量2.蜂鸣器3.振动4.报警状态5.查询6.存储7.零点校准8.量程校准9.设置10.单位1 LED 指示灯透明窗 5 传感器感应孔2 液晶显示器 6 USB 充电孔3 按键 7 鳄鱼夹4 蜂鸣器发音孔3.3按键功能4 探测器的开、关机4.1 开机3s以上,探测器开机。

海曼USRP产品说明

1.5 FPGA

对 GNU Radio 用户来说,或许最重要的部分是理解 USRP FPGA 上所发生的 事情。如下图所示,所有的 ADCs 和 DACs 都连接到 FPGA。这块 FPGA 在 USRP 系 统中起着关键作用。基本上他们所做的是执行高带宽下的数学运算,并减少数 据传输速率至可以在 USB2.0 上传送。FPGA 连接到 USB2 接口芯片——Cypress FX2 。通过 USB2 总线,所有( FPGA 电路及 USB 微控制器)都是可编程的。

1 USRP母板

USRP 有 4 个高速模拟数字转换器( ADCs ),每符号 12 比特, 64M 符号 /秒。另有 4 个高速数字模拟转换器( DACs ),每符号 14 比特,128M 符号/ 秒。这 4 个输入和输出通道连接到 Altera 的 Cyclone EP1C12 FPGA 上。FPGA 进而连接到 USB2 接口芯片—— Cypress FX2,并接至计算机上。USRP 只通过 高速 USB2.0 接口连接到计算机,不能使用 USB1.1。 因此,原则上,如果使用实采样的话,有 4 个输入和 4 个输出通道。但是 如果使用复采样(IQ),可以有更大的灵活性(和带宽)。此时必须对它们进 行配对,这样就能获得 2 个复输入和 2 个复输出。

海曼无限 USRP 产品说明书

北京海曼无限信息技术有限公司 http://www.open‐ Copyright@2009‐2012 Highmesh Inc. All Right Reserved

目录

1 USRP母板 .............................................................................................................................. 3 1.1 模数转换器部分 ........................................................................................................ 4 1.2 数模转换器部分 ........................................................................................................ 4 1.3 辅助模拟I/O 端口 .................................................................................................... 5 1.4 辅助数字I/O 端口 .................................................................................................... 5 1.5 FPGA ............................................................................................................................ 5 2 子板 ....................................................................................................................................... 8 2.1 2.2 2.3 2.4 2.5 Basic TX/RX子板 ................................................................................................... 9 低频发射/接收子板 ............................................................................................... 9 TVRX子板 ................................................................................................................. 9 DBSRX子板 ............................................................................................................... 9 RFX子板 ................................................................................................................. 10

USRP-OFDM通信系统实验报告

实验一利用GNU-Radio和USRP搭建OFDM通信系统图1,基于GNU-Radio和USRP的OFDM通信系统示意图1 实验设备●设备清单●开发环境操作系统:Ubuntu 14.04 64bit软件平台:GNU-Radio v3.7.8 UHD release_003_009_0012 实验目的●理解OFDM信号的调制和解调原理;●熟悉使用GNU-Radio软件并对信号进行处理;●学会使用软件GNU-Radio和硬件USRP来完成点对点设备的通信。

3 实验内容本实验是在Linux桌面应用系统Ubuntu上进行的,使用到的包括一款免费的无线电和信号处理开发软件—GNU-Radio,和通用软件无线电外设硬件—USRP N210。

实验的任务是在GUN-Radio和USRP组成的软硬件平台,搭建了基于OFDM调制的无线通信环境,以便更好的了解OFDM通信原理和信号在无线信道中传播的特点。

实验主要包括三部分:发送端、信道和接收端。

其中发送端主要包括信源、符号映射、子载波分配、IFFT并加CP、USRP TX;无线信道所处的是室内环境,也被称为准静态信道环境(这也为接收端的均衡提供了思想);接收端主要包括USRP RX、同步、去CP FFT、信道估计和均衡、解符号映射、信宿。

4 实验步骤4.1 发送端在OFDM通信系统中,发送端需要完成以下几个功能:信源编码、数据打包、符号映射、子载波分配、IFFT变换、加CP、USRP发送射频信号等。

除USRP模块外其它几个模块中的信号处理都是在GNR-Radio中完成的,也即在主机中完成。

USRP模块拥有单独的DSP 和FPGA模块,因此可以独立对输入数据进行处理。

在USRP模块里面需要完成很多的功能,比如抽取、数字上变频、A/D转换、混频等功能都是在其中完成的。

发送端的主要目的是完成信号的调制、上变频、功放,最后通过专用天线将其发送到无线信道中去。

考虑到若上变频后的信号幅度过大,在经过功放后可能导致信号失真,因此需要在USRP模块前增加一个限幅器模块。

USRP系列产品简介与参考报价

USRP系列产品USRP(Universal Software Radio Peripheral,通用软件无线电外设)旨在使普通计算机能像高带宽的软件无线电设备一样工作。

从本质上讲,它充当了一个无线电通讯系统的数字基带和中频部分。

USRP由母板、连同各种子板以及相应的天线组成。

一个典型的USRP 产品系列包括两部分:一个带有高速信号处理的FPGA 母板,一个或者多个覆盖不同频率范围的可调换的子板。

它们共同实现把比特流数据从天线传到主机电脑(即接收),或者从主机电脑传送到天线(即发送)。

在各种子板中,USRP 系列涵盖从直流到 5.9GHz 的整个范围,这包括了从调幅广播到超过Wi‐Fi 的所有频率。

主要母板:1)USRP1 参考报价:$1027(嘉兆)、$707(Ettus),¥3400元♦缺省时钟64M,可以换成52M(用于OpenBTS)♦采样量化精度为8 bit情况下射频带宽(RF bandwidth)为16 MHz (AD9862)♦采样的量化精度为16 bit 情况下射频带宽(RF bandwidth)为8 MHz ♦USB 2.0 高速连接8M/秒传输速率♦MIMO 可构建性‐ USRP 母板上的两路收发使得单个USRP 可以构建MIMO♦FPGA:Altera Cyclone♦ADCs: 12‐位64 MS/s♦DACs: 14‐位128 MS/s2)USRP B100Xilinx Spartan 3A 1400 FPGA,其他一致3)USRP E100TI OMAP3(Spartan 3A‐DSP 1800 FPGA and a C64 DSP)4)USRP E110TI OMAP3(Spartan 3A‐DSP 3400 FPGA and a C64 DSP)5)USRP2(过渡产品)参考报价:13000元♦50 MHz 瞬时射频带宽♦千兆级以太网连接♦MIMO 电缆连接:基于每台USRP2 上只有单路收发链路,MIMO 的构建必须两台或两台以上USRP2 来构建♦板上FPGA 处理(Onboard FPGA processing)♦FPGA: Xilinx Spartan XC3S2000♦ADCs: 14‐位100 MS/s♦DACs: 16‐位400 MS/s6)USRP N200 $2200(嘉兆)、$1515(Ettus)模块化的设计允许USRP N200在从直流至6 GHz频率范围工作。

laugesoft N P100 服务器伯图 users 指南说明书

尊敬的浪潮英信服务器用户NP100服务器的技术特性与系统的设置有本手册介绍了浪潮英信NP100服务器助于您更详细地了解和便捷地使用浪潮英信以利于污染预防浪潮集团有限公司拥有本手册的版权任何单位和个人不得以任何形式复制本用户手册本手册中的内容如有变动恕不另行通知请向浪潮集团有限公司垂询"英信"是浪潮集团有限公司的注册商标Windows是微软公司的注册商标其他商标分别属于其相应的注册公司声 明 在您正式使用浪潮英信NP100服务器之前只有您阅读了以下声明并且同意以下条款后如果您对以下条款有任何疑问如您未向我们就以下条款提出疑问并开始使用浪潮英信NP100服务器1在任何时候您不要修改浪潮英信NP100服务器主板BIOS中的任何其他参数在您使用的浪潮英信NP100服务器出现任何硬件故障时或您希望对硬件进行任何升级时 服务器是十分精密的仪器3CPUCPU散热片CPU支架网卡都是特殊规格的4我们希望您首先和相应软件的提供商联系以方便我们沟通对于如数据库运行问题5请先仔细阅读我们的快速使用指南请联系我们的技术服务中心我们特别提醒您注意对您的数据进行必要的备份本手册中涉及之各软硬产品的标示8"我们"指代浪潮集团有限公司 本服务器主板配备可更换锂电池在更换过程中只允许使用与制造商提供的同类或等效类型的替换件 关 于 本 手 册本手册专为浪潮英信NP100服务器的最终用户而写浪潮英信NP100服务器用户手册为您提供一些必要的技术支持使其安全高效的运行第一章 如何连接安装第二章第三章第四章仅适用于RAID系统第五章第六章我们建议您在使用浪潮英信NP100服务器之前仔细阅读本手册由于我们的水平有限希望您能够包涵技术服务电话86-531-8514355网 址中国济南市山大路224号浪潮集团有限公司邮 编 sv_serv@langchao.com.cn 目 录第一章 开始使用浪潮英信服务器...........................1.1 开始使用浪潮英信NP100服务器.......................1.2 浪潮英信服务器随机资料.............................1.3 浪潮英信服务器外观.................................1.4 连接NP100服务器...................................1.5 NP100服务器技术特性................................第二章 系统设置.........................................2.1 系统CMOS跳线......................................2.2 POST...............................................2.3 系统BIOS...........................................第三章 系统硬件.........................................3.1 安装处理器.........................................3.2 安装内存...........................................3.3 安装硬盘...........................................3.4 安装板卡...........................................第四章 RAID系统.........................................4.1 进入RAID控制器BIOS设置...........................4.2 Auto Setup(自动设置查看磁盘分配创建阵列删除阵列重建阵列第五章 安装操作系统.....................................5.1 安装Windows NT4.0..................................5.2 安装Windowqs 2000 Server...........................5.3 安装RedHat linux 8.0...............................5.4 Novell Netware 6.0的安装...........................5.5 SCO UnixWare 7.1.3的安装...........................5.6 SCO OpenServer 5.0.7的安装.........................5.7 主板集成RAID配置下安装RedHar Linux 8.0............第六章 疑难解答.........................................6.1 常见故障解决.......................................6.2 技术支持信息.......................................第一章 开始使用浪潮英信服务器1.1开始使用浪潮英信NP100服务器1小包装箱中是显示器配件盒首先用裁纸刀把大包装箱的封条打开把主机从包装箱中抬出您购买的浪潮英信NP100服务器就展现在您的面前2 确信电源接地良好 方便从电源和电源插座上插拔电源线 环境干净无尘 通风良好并且远离热源 远离强电磁区域和由空调大电动机电视台发射塔1.2浪潮英信服务器随机资料1浪潮蓝海豚导航软件光盘1张1NP100 用户可以根据所安装的操作系统2您需要在安装前制作所需的驱动程序软盘在菜单中选择选择要制作的部件驱动程序点击制作驱动程序可以插入RAID卡或SCSI卡驱动随机光盘 浪潮英信服务器的随机软件建议您妥善保存对于这些随机软件1.3浪潮英信服务器外观1高度:428mm宽度:210 mm深度:470 mm前侧空间要求:250 mm (吸入气流温度<355232图1-1浪潮英信NP100服务器前面板示意图1复位按钮 3电源状态指示灯 5软驱 75.25"扩展槽 9NP1003电源接口 2鼠标接口 4USB接口1串口1 7千兆网卡接口 9百兆网卡接口 11并口 13将主机键盘 2连接好键盘网线45 3 4系统的连接完成最大支持4GB* 支持ECC Unbuffer内存* 支持DDR 400MHz/333MHz/266MHz 内存* 可以使用双通道或者单通道内存* 主板集成Promise PDC20378 RAID控制器* 支持IDE RAID* 支持SATA RAID (最多可支持两块SATA硬盘做RAID)* IED RAID和SATA RAID一块可以支持RAID 01.44MB* 标准IDE CD-ROM处理器内存RAID键盘和辅助设备扩展槽硬盘光驱NP100* ATI显卡第一章67第二章 系统设置前言BIOS设置又称CMOS设置可以利用专门的设置程序对系统参数和硬件参数进行调整内存容量COMS存储器要求电源功率很小备用电池为CMOS存储器提供电源随着硬件种类的增多和更新换代的加速由于BIOS对系统的运转和启动有重大影响设置了不当的参数后可能会引起硬件资源之间的冲突因此如果没有特殊的需要不要随意改变BIOS 只有合格的技术人员才可以对主板跳线进行设置 系统电源开关系统上有8mA的伺服电流必须拔下系统交流电源电缆 系统外接设备否则可能会对人员或设备造成意外伤害 静电释放和静电释放保护措施硬盘英信NP100永不停顿的浪潮英信服务器和系统的其它部件造成损害最好在防静电环境下进行操作人员必须佩带防静电手环 静电释放和板卡持拿持拿板卡必须小心当板卡暂时不用时芯片朝上放在接地工作平台上 机箱盖在系统上电前一定要安装机箱盖跳线可用于在系统的两个或多个选项之间选择可以改变跳线的功能请参考以下常用的跳线的解释说明造成不必要的错误向您介绍这款英信服务器的跳线设置情况可以清除系统CMOS值拔掉电源线2) 在JP3的pin2和pin3上加跳线除去跳线连接电源线在提示下按<DEL>进入BIOS设置Load Op-timized Defaults89图2-1 CMOS跳线设置2.2 POST系统在开始引导时上电自检检测服务器的主板闪存鼠标和其它已经安装的设备POST可以显示被访问的内存容量POST检测的结果存储在闪存里1POST开始运行检测完内存Press <DEL> to SETUP or <TAB> to POST如果您此时按下<DEL>键正常状态COMS清零英信NP100永不停顿的浪潮英信服务器2.3 系统BIOS2.3.1 如何进入BIOS设置当系统开始引导时 Press <DEL> to SETUP or <TAB> to POST按下<DEL>键进入系统BIOS设置BIOS的设置主要有><><键用于选择上一个菜单或值键用于选择下一个菜单或值 键用于选择左边的菜单键用于选择右边的菜单Enter键可用于激活它Enter键可用于显示选项列表可用于选定子字段用此键可撤销显示ESC键用于退出选项或在任意子菜单下时若在任意主菜单下增加菜单中设置的数字值或改变菜单设置值在Setup菜单按F1可启动帮助窗口F5键用来保存当前CMOS值1011注释这只是提供给用户的信息Press Enter按< Enter >键菜单选项栏进入BIOS之后其功能如下表所示仅对Setup菜单中各子菜单的选择项有效按下F10会显示如下Y"键后按键如输入Enter不会影响现有的字段值菜单选项Standard CMOS FeaturesAdvanced BIOS FeaturesAdvanced Chipset FeaturesIntegrated PeripheralsPower Management SetupPNP/PCI ConfigurationPC Health StatusFrequency/Voltage Control描述该菜单用于一些基本的系统设置日期等该菜单用于主板集成设备的一些特殊设置如果您的系统支持PnP/PCI设备的话显示该菜单该菜单用于频率/电压控制12英信NP100永不停顿的浪潮英信服务器Standard CMOS Features菜单菜单选项Load Fail-safe DefaultLoad Optimized DefaultSet Supervisor/User passwordSave & Exit SetupExit Without Saving描述该选项用于加载系统最稳定该选项用于加载系统最佳性能的BIOS默认值该菜单用于保存改动到CMOS并退出BIOS设置菜单描 述设置系统日期显示系统检测到的IDE设备选择软盘类型设置当系统启动时检测到错误时是否停止不可修改But Keyboard; AllBut Disk/Key13Advanced BIOS Features菜单描 述是否为IDE硬盘引导扇区保护提供报警设置只有CPU支持超线程时才显示该项设置成时设置成时不支持超线程参见后面的Boot Sequence一项Enabled如果芯片组和键盘控制器可以控制GateA20时当设置成时当设置成时在OS/2和Windows系统下将该项设置为时BIOS所执行的密码的类型设置用户进入Setup提示输入密码用户每次开机和进入Setup均提示输入密码在Win NT3.52选择1.1Win2000和Win XP下选择1.4Post时特 征Virus WarningCPU L1 & L2 CacheHyper-ThreadingTechnologyQuick Power On SelfTestBoot SequenceBoot Up NumLockGate A20 OptionSecurity OptionAPIC ModeMPS Version Control For OSHDD S.M.A.R.T Capabil-ity Small Logo(EPA)Show选 项Enabled; DisabledEnabled; DisabledEnabled; DisabledDisabled;EnabledEnabled; DisabledFast; NormalSetup14英信NP100永不停顿的浪潮英信服务器根据实际情况设置所检测到的硬盘的启动顺序各设备的引导顺序设置Enabled允许BIOS 的内存缓存使用F0000h-FFFFFh地址但是如果任何程序向该地址写数据选择时这样可以提升系统性能系统将会产生报错外部监视设备将会允许延迟该项所选择的一段时间当内存为Non-ECC类型时特 征System BIOSCacheableVideo BIOSCacheableDelay Prior to ThermalDRAM DataIntegrity Mode选 项Enabled; DisabledEnabled; Disabled4Min;8Min;16Min;32MinECC; Non-ECC15Integrated Peripherals菜单此主菜单下共有三项子菜单按<Enter>键进入子菜单Onboard Device 按<Enter>键进入子菜单 OnChip IDE Device子菜单描 述选择"Enabled"时IDE硬盘控制器采用块传输模式IDE硬盘采用标准传输模式选择"Enabled"时主板所支持的四个IDE设备的PIO(可编程输入/输出口)模式的设置Mode4成功提升了系统性能系统自动给每个设备分派一个最好的PIO模式该项设置为如果您要在不做RAID的IDE硬盘上装RedHat Linux时Disabled如果要在没有做RAID的SATA硬盘上装RedHat LinuxCombined ModeSATA 端口0/1模式设置英信NP100永不停顿的浪潮英信服务器Super IO Device子菜单描 述USB控制器和USB外部设备使能设置USB键盘使能设置Promise RAID使能设置支持RAID功能特 征USB ControllerUSB 2.0 ControllerUSB Keyboard SupportUSB Mouse SupportOnboard Promise RAID CtrlCSA LAN (GbE LAN)选 项Enabled; DisabledEnabled; DisabledEnabled; DisabledEnabled; DisabledEnabled; DisabledEnabled; Disabled描 述主板集成FDC控制器使能设置可以将该项设置成第二个串口IR Mode的设置IR 传输延迟使能设置LPT端口配置主板上I/O芯片IR传输模式设置Hi; HiHi; Lo1617Power Management Setup菜单描 述电源ACPI功能使能设置电源节能类型设置该项设置系统在暂停模式下是否关闭监视器所设置的中断将会使系统唤醒在其他设备还处于活动状态时该项设置当CPU温度达到预先设置的温度后请看下面Power ON Setup表中的各项子菜单特 征ACPI FunctionRun VGABIOS ifS3 ResumePower ManagementOptionVideo Off MethodVideo Off In SuspendSuspend TypeMODEM Use IRQHDD Power DownCPU THRM-Throt-tlingPower ON SetupReload GlobalTimer Events选 项Enabled; DisabledS1(POS)Use Define; MinSaving; Max SavingBlank Screen;Screen DPMS;V/H SYNC+Blank;Yes; NoStop Grant; PWRonSuspend3; 4; 5; 7; 9; 10;11; N/ADisabled;1 ̄15Min25%;50%18英信NP100永不停顿的浪潮英信服务器电源开关功能设置项电源开关作为一个普通的开关按钮当您按下电源开关时当按键时间超过4秒的时候该项设置当系统接受到PCI卡子上的PME发出的信号时该项设置当Modem拨号时系统是否被唤醒该项设置当USB键盘来信号时系统是否被唤醒电源开关键的一些功能设置该项才有效当POWER ON Function设置为Hot Key时选择您要设置的热键F1F1219Enabled0/1设备将会唤醒系统Enabled0/1设备将会唤醒系统EnabledFDD端口将会唤醒系统Enabled将会唤醒系统COM时子将会产生严重的冲突而使系统不能启动时时色寄存器20英信NP100永不停顿的浪潮英信服务器PC Health Status菜单Frequency/Voltage Control菜单Load Fail-Safe/Optimized Defaults菜单当您选择Load Fail-Safe Defaults菜单时描 述当CPU温度超过该项所设置温度的上限值时这些项显示了系统检测到的硬件设备系统温度以及各种风扇速度等当处理器温度达到该项设置的温度值时特 征CPU Warning Tem-peratureCurrent CPU/ SystemTemperature......Shutdown Tempera-ture选 项Disabled; 50/127;56/140;63/151;70/140;65/158;75建议使用默认设置当设置"Enabled"时该项是减少EMI影响使能设置建议使用默认设置DRAM频率设置Max22Auto; DefaultEnabled;DisabledEnabled166MHzAuto by SPD; DDR33;DDR400; Auto 按下"Y"键将会加载系统最稳定当您选择Load Optimized Defaults菜单时按下"Y"键将会加载系统最佳性能的BIOS出厂默认值将会出现下图所示的提示注意根据提示重新输入密码并按<Enter>键确认密码您也可以在提示您输入密码时仅按<Enter>键清除您设置的密码如果您将Advanced BIOS Features菜单中的"Security Option"项设置成"Sys-tem"时如果该项设置成"Setup"时输入超级用户密码可以进入Setup菜单并可改变菜单中各项的设置但是不能改变菜单中各项的值21英信NP100永不停顿的浪潮英信服务器Save & Exit Setup菜单当您选择该菜单时 Save to CMOS and EXIT (Y/N)? Y按下键后系统将保存对BIOS各项设置所作的改动并退出SETUP程序Quit without Saving菜单当你选择该项菜单时Quit without saving (Y/N)? Y按下键后系统将忽略对BIOS各项设置所作的改动并退出SETUP程序2223第三章 系统硬件本章将指导用户如何安装系统硬件 静电释放可能损坏服务器组件对静电释放进行防护是必要的一定要按照以下方法进行手腕上戴一个接地的防静电环用手持拿板卡时,注意只拿板卡的边沿3请放回各自的防静电袋持拿处理器时一定不要直接用手接触处理器的引脚1断开交流电电缆2支持MPGA478 ZIF封装的处理器 当安装处理器时把处理器的引脚和主板上的Socket 对准注意一定不要用力放注 意24英信NP100永不停顿的浪潮英信服务器置合适后如图3.1.2所示将散热片放在CPU上如图3.1.325图3.1.35 将其插在主板的CPU风扇电源插座上如图3.1.4所示否则将影响处理器的散热图3.1.4英信NP100永不停顿的浪潮英信服务器6将机箱安装好请使用经过我们测试认证的相应型号产品在安装内存条的时候否则会损坏内存或主板的内存插槽关闭系统电源2如图3.2.1所示Array把内存条垂直插入内存槽中轻轻按下内存条注意把两边的卡销卡上3.2.3所示2627图3.2.34将机箱盖及面板安装好如果您要扩展此类设备推荐使用经过我们测试认证过的相应型号的产品1断开交流电源线缆打开机箱 正确设置ATA-133/100/66 IDE硬盘的ID跳线用螺丝固定 连接硬盘数据线缆以及电源电缆3.3.128英信NP100永不停顿的浪潮英信服务器4将机箱盖及面板安装好1断开交流电源线缆打开机箱 SATA硬盘不需要跳线用螺丝固定 连接硬盘数据线缆以及电源电缆4将机箱盖及面板安装好在扩展安装PCI接口的扩展卡时1断开交流电电缆打开机箱 移走与要使用的插槽对应的后挡片 将板卡插入主板的扩展槽 用螺丝钉固定5将机箱盖及面板安装好图3.4.129英信NP100永不停顿的浪潮英信服务器第四章 RAID系统本章是专门针对主板集成的RAID系统而写的,如果您的系统是非主板集成RAID系统,可以不参阅本章开机启动检测2屏幕显示如下图[ 3 ]Delete Array[ 5 ][Key Available] Press 1...5 to Select Option [ESC] Exit304.2自动设置按键进入Auto Setup菜单FastBuild (tm) Utility 2.xx (c) 2002-2005 Promise Technology, Inc.[Auto Setup Options Menu ]Optimize array for 2Array Disk Capacity (size in MB)82217 [Keys Available][(] Up [(] Down [(, ?, Space] Change Option [ESC] Exit [Ctrl-Y] Save菜单中[Auto Setup Options Menu]为可设置部分阵列创建步骤如下 设置阵列类型选中项或空格键各参数表示意义如下 Security3132英信NP100永不停顿的浪潮英信服务器23如果是创建RAID1,保存设置后将提示N选择创建 然后按任意键重新启动机器在阵列创建后4.3查看磁盘分配按 键进入菜单Channel:ID CapacityModeDo you want the disk image to be duplicated toanother? (Yes/No)Y - Create and duplicateN - Create OnlyArray has been created.<Press any key to reboot >注 意4.4创建阵列 按键进入菜单菜单如下]Up [1下箭头键选择Array *进入下图所示菜单MBOFF[Drives Assignments]Channel : ID Drive Model Capacity(MB)1 :Mas xxxxxxxx 411102 :Mas xxxxxxxx 41110Any Key to Continue3334英信NP100永不停顿的浪潮英信服务器4.5删除阵列4删除已经存在的阵列1下箭头键选择要删除的阵列 按[Del]键3按[Ctrl - Y]键删除阵列按[ESC]键FastBuild (tm) Utility 2.xx (c) 2002-2005 Promise Technology, Inc.[Delete Array Menu]Array No RAID Mode Total Drv Capacity(MB) StatusArray 1 Stripe 1 82217 FunctionalArray 2 --------- --------- --------- ---------Array 3 --------- --------- --------- ---------Array 4 --------- --------- --------- ---------[Key Available][]Down [ESC]Exit [Del] DeleteAre you sure you want to delete this array?Press Ctrl - Y to Delete354.6重建阵列可以在该菜单中实现磁盘数据的重新存储工作重建阵列步骤如下 启动机器2 查看故障硬盘所处的通道和ID号 关闭机器新换的硬盘和故障硬盘容量相同5按<Ctrl-F>进入RAID主设置菜单 在主菜单中按键进入Rebuild Array菜单7按回车键继续在[Select Drive for Rebuild]列表中选择新更换的磁盘按回车键继续系统将开始重建阵列并显示进度按照提示重新启动机器]Up [英信NP100永不停顿的浪潮英信服务器第五章 安装操作系统本章为非RAID配置下操作系统的安装指南请从蓝海豚导航光盘中根据每个系统安装前的准备提示制作相应操作系统的驱动请根据SCSI卡或RAID卡手册里操作系统的安装部分安装系统 主板集成RAID功能支持的操作系统为Win-dows NT 4.0RedHat Lniux 8.0Windows NT 4.0的安装方法可以参照第五章前两节安装Windows NT 4.0和安装Windows 2000 Server部分的步骤RedHat Linux7.3的安装方法与其类似5.1 安装Windows NT 4.0本安装过程为Windows NT 4.0 (中文版)的基本安装步骤如果您的系统是非主板集成RAID系统具体如何设置有关选项如果系统配置了RAID卡或SCSI卡5.1.1 安装前的准备安装Windows NT 4.0操作系统前需要准备 Windows NT 4.0 安装光盘36键继续按<Enter>继续,开始加载驱动程序37英信NP100永不停顿的浪潮英信服务器继续安装 安装程序开始加载文件欢迎使用安装程序提示以下选项 在安装前如果想多了解Windows NT的安装过程请按Enter 修复在上次安装时损坏的4.0中文版Windows NT请按F3按<Enter>继续屏幕显示IDE CD-ROM (ATAPI 1.2) /PCI IDE ControllerWinNT Promise FastTrak 376/378 (tm) ControllerCD-ROM驱动器及特殊磁盘控制器请按S 如果您没有制造厂商提供的大容量存储设备的驱动软盘请按ENTER我们不再加载其他的驱动程序继续安装 显示按<Enter>键9或计算机已经安装了一个与Windows NT无法并存的操作系统请按C在启动硬盘上的任何数据将永久的丢失 退出安装程序38在此我们按C继续安装系统显示按<Page Down>键浏览协议按<F8>键接受协议内容系统加载信息文件安装程序检测出计算机内含有下列硬件和软件组件显示器键盘布局在此我们采用系统检测的信息Enter12使用上请按Enter 在未分区空间上创建一新的磁盘分区请按D可以先删除旧的分区或直接将NT装在旧的分区上并且分区最大不得超过4GB创建一个新的分区输入要创建分区的大小13新的按<En-ter>继续可选择的文件系统格式将显示出来 使用FAT文件系统格式化此磁盘分区下箭头键选择 15系统会显示一个黄色进度条39英信NP100永不停顿的浪潮英信服务器16如果要改变建议的位置然后键入想要安装Windows NT 的目录名按<Enter>键继续 系统提示 允许安装程序在硬盘上执行这种检测请按 ESC按<Enter>键开始检测硬盘检测完硬盘后系统会显示一个黄色进度条如果您的系统是RAID配置,在此系统需要加载RAID驱动程序根据提示将驱动软盘插入软驱中系统不会出现提示而自动加载驱动程序所有文件复制完成后按<Enter>键重新启动系统如果选择了 NTFS 文件系统格式转换完成后22依照提示重新插入 Windows NT ServerCD-ROM 光盘23用鼠标单击<确定>按钮以继续安装程序复制文件Windows NT安装程序点击<下一步>继续在提示准备安装后单击<下一步>继40续注册10位数字27单击<下一步>继续请先选择每服务器模式但只能进行一次反之不可更改输入计算机名称并且该名称在网络中是唯一的单击<下一步>继续选择服务器类型 主域控制器 独立的服务器按照您的需要选择30不多于14个字符单击<下一步>继续创建紧急修复磁盘是,创建一张紧急修复盘这是很重要的一个步骤32根据您的实际需要来选择组件33安装 Windows NT 网络单击<下一步>继续选择本计算机与网络的连接方式在此我们选择35安装Microsoft Internet Information Server41英信NP100永不停顿的浪潮英信服务器推荐选择安装36点击单击NIC1 Driver for WindowsNT 4.0点击<确定>继续屏幕显示选择OEM选项对话框IntelPRO/100 FamilyAdapterIntelPRO/1000 Family Adapter单击<确定>继续选中R选中R40NWLink IPX/SPX兼容传输然后单击<下一步>继续显示系统将安装下列服务的对话框 RPC 配置 工作站请单击<从列表中选择>单击要安装的网络服务单击<下一步>继续 Windows NT准备安装选定的和其他系统所需的网络组件,单击42<下一步>继续稍后提示Intel PROAdapter diskette 2将软盘插入软驱NIC1和NIC2软盘插入过程会反复几次43根据实际情况选择是否使用DHCP44您的网络配置有多个适配器要更改吗45分别为每个适配器指定IP地址46使用该页禁止网络绑定或重排计算机查找网络信息的顺序采用默认设置47Windows NT准备启动网络以完成网络安装48则提示必须提供主域控制器将要管理的域的名称根据实际情况输入域名提示49系统将显示安装对话框单击<确定>50下列目录不存在可以选择是或否本安装过程选择<是>51发行目录继续安装安装程序询问要创建吗43英信NP100永不停顿的浪潮英信服务器择53没有为该机器声明的Internet域名必须通过网络控制面板应用程序配置Internet域名54然后单击<确定>继续设置时间和日期/时区点击时区标签设置正确的时区为重庆然后单击<关闭>继续在以及对话框57在此过程中系统提示制作紧急修复磁盘按照提示将格式化好的软盘插入软驱推荐制作紧急修复磁盘58已经成功安装Windows NT4.0取出 WindowsNT CD-ROM 光盘及软盘59按<Ctrl+Alt+Del>登录60欢迎使用Windows NT单击<关闭>按钮将蓝海豚导航软件光盘插入光驱选择常用工具下拉菜单中的按照提示安装service pack 6补丁程序重新启动系统安装显卡驱动程序,系统重新启动后自动引导到安装界面依次在下拉菜单中选择NP100操作系统4445部件型号按照屏幕提示安装显卡驱动程序系统重新启动完成Windows NT server 4.0的基本安装过程可以作为安装参考请省略安装步骤3 到6 中的RAID驱动加载过程需要用户根据自己的实际情况而定操作系统的安装请参考RAID卡或SCSI卡手册中的相应内容 蓝海豚导航软件光盘非主板集成RAID系统不用制作该软盘)5.2.2安装步骤1将安装光盘插入光驱2在系统提示时系统将从光盘上启动Windows 2000安装程序 在提示。

usrp的基本结构和功能

USRP即Universal Software Radio Periphehal 的缩写,软件无线电外设。

其设计宗旨是使普通计算机能像高带宽的软件无线电外设一样工作。

从本质上讲,它充当一个无线通信系统的数字基带和中频部分。

USRP背后的设计理念是在主机CPU上完成所有波形相关方面的处理,比如调制和解调。

所有诸如数字上下变频、抽样和内插等高速通用操作都在USRP上的FPGA上完成。

USRP 由母版,覆盖不同带宽的子板以及相应的天线组成。

USRP有四路12位高速模数转换(ADCs)采样速率可达64MSsamples/sec,4路14位数模转换器(DACs),采样速率可达128 MSsamples/sec,转换器(DACs),采样速度可达128MSamples/sec。

这些4入4出通道同Altera 公司的Cyclone EP1 C12 FPGA相连。

FPGA相应地同Cypress公司的USB2接口芯片FX2相连,然后连接至计算机。

USRP同计算机通过高速的USB2接口相连,不能用于USB1.1接口。

因此,理论上,当采样信号时,系统具有4路输入4路输出。

但是,现实中csiji复合的(IQ)信号时,它只提供更多的灵活性(和带宽)。

因此把它们成对,便可形成两对复合输入两对复合输出。

基于USRP的成功经验,USRP2以更高速度和更高的精度(100MHz) 14位ADCs和400MHz 16位DACs ),允许使用更宽波段的信号,增加了信号的动态范围。

针对DSP应用优化了的大型现场可编程门阵列(FPGA)可以在高采样率下处理复杂波形。

千兆以太网络接口,使应用程序可以使用USRP2同时发送或接受50MHz的射频带宽。

在USRP2中,FPGA出现了诸如数字上变频器和下变频器等高速采样处理器。

较低采样率的操作可在主机电脑上,甚至可以在具有32位RISC微处理器和有很大用户设计自由空间的FPGA上。

USRP2的配置和固件被存储在一个SD闪存卡里,无需特别的硬件就可以轻松编程。

朗科 酷贝 P210 说明书

录音文件

Recorder

GPS地图文件 navione

预设文件夹不能在“文件”菜单中被剪切和删除。navione 与 FWUpgrade 文件 夹及存放在其下的文件只有在电脑上可见。 l 名为“Fm****-******.wav”/“Mic****-******.wav”的文件为 FM 录音和麦克风 录音文件的预设系统文件名,其中“* * * * - * * * * * * ”表示录音的“日期 _ 时间”。 l 本产品不能完全避免因使用不当或其它原因而造成文件或数据损坏或丢失,敬请您 对本产品中所有的文件或数据予以备份。 l 本用户手册中提及的 W indows 98 系指 W indows 98 第一版和第二版。

执行标准:Q/Netac 006

中国发明专利:ZL 99117225.6,ZL 00114081.7 美国发明专利:US 6829672

酷贝 TM P210

注意事项

1) 容量说明 l 本产品闪存中,存储 GPS 地图文件所占容量约 300MB,为节约闪存空间,建议

将 GPS 地图文件存放在 SD/MMC 卡中,需要使用 GPS 卫星导航功能时,将 SD/MMC 卡插入本产品的卡槽中即可。 2) 存放 l 请避免将本产品置于烈日直射下或灰尘较多处,以免造成损坏。 l 请避免将本产品从高处坠落或受到剧烈震动或冲击。 l 请避免液体或异物进入机内。 3) 清洁 l 请勿在本产品上使用挥发性汽油、稀释液及其他任何化学药品,否则会破坏产品 表面加工层。 l 请勿用未拧干的湿布擦拭本产品及其附件。 l 维修或清洁本产品前务必先断开与电脑的连接。 4) 电池 l 前三次对本产品电池进行充电时,建议充电时间大于 1 2 小时,以确保电池的最 佳使用状态。 l 请勿将本产品扔到火中,以免电池爆炸。 l 请勿自行拆卸电池。 5) 使用 l 请勿在低电时进行固件升级,以免破坏本产品文件系统。 l 为防止触电和损坏,请勿用湿手插拔或接触本产品。 l 请勿在本产品与电脑连接并读写数据时将其拔出,否则可能导致产品本身以及当 前正在读写的数据被损坏。 l 使用本产品时,请避免将本产品剧烈震动,以免造成本产品损坏。 l 在驾驶过程中看本产品的屏幕,可能会导致严重的交通事故。为了避免事故的发 生,请在停车后操作本产品。使用本产品的 GPS 卫星导航系统时,系统内地图可

VP-102使用手册

VP-102 IP电话机使用手册1.概要 (4)1.1. 简介 (4)1.2. 硬件特性 (4)1.3. 软件特性 (4)1.4. 协议 (5)1.5. 产品外观 (6)1.6. 前面板说明 (7)1.7. 后面板说明 (8)2.安装 (9)2.1. 连接 (9)2.2. 启动电话 (9)3.使用说明 (10)3.1. 键盘 (10)3.1.1. 数字键盘 (10)3.1.2. 功能键盘 (11)3.2. LCD (11)3.3. 音量调整 (11)3.3.1. 调整免提音量 (11)3.3.2. 调整响铃音量 (12)3.4. LCD对比度 (12)3.5. 拔打电话 (12)3.5.1. 普通模式 (12)3.5.2. 免提模式 (12)3.5.3. 普通模式和免提模式互转 (12)3.6. 接听电话 (12)3.7. 接听等待电话 (13)3.8. 呼叫保持 (13)3.9. 电话会议(三方通话) (13)3.10. 呼叫转移 (14)3.10.1. 无应答转移 (14)3.10.2. 应答转移 (14)4.电话菜单 (15)4.1. 菜单操作 (15)4.2. 菜单内容 (15)4.2.1. 呼叫记录 (15)4.2.2. 电话簿 (16)4.3. 系统工具 (17)4.3.1. 电话状态 (17)4.3.2. 系统版本 (17)4.3.3. 振铃类型 (17)4.3.4. 自动配置 (18)4.3.5. 快速拔号 (18)4.3.6. 恢复出厂 (18)5.配置 (18)5.1. 开始配置 (18)5.1.1. 获得信息 (18)5.1.2. 登录到配置页面 (19)5.2. 电话状态 (19)5.3. 配置 (20)5.3.1. 网络配置 (21)5.3.2. 呼叫设置 (24)5.3.3. 话机设置 (28)5.3.4. 保存改动 (29)5.3.5. 放弃改动 (29)5.3.6. 电话本 (29)5.4. 工具 (29)5.4.1. 在线升级 (29)5.4.2. 修改密码 (30)5.4.3. 备份/恢复配置 (31)5.4.4. 恢复出厂配置 (31)5.4.5. 重启设备 (31)5.4.6. 注销 (31)1.概要1.1. 简介VP-102是得伯乐公司自行研发的廉价商务IP电话,她是一款同时兼容H.323 V4和SIP V2,拥有单行英文字母、单行数字LCD显示器,带标准PC耳机接口,真正全双工免提通话的IP电话机。

USR10-10v2 用户手册

USR10-10v2用户手册深圳市新格林耐特通信技术有限公司版权声明版权所有2001-2013,深圳市新格林耐特通信技术有限公司,保留所有权利。

使用本产品,表明您已经阅读并接受了 EULA 中的相关条款。

如有变更,恕不另行通知。

遵守所生效的版权法是用户的责任。

在未经深圳市新格林耐特通信技术有限公司明确书面许可的情况下,不得对本文档的任何部分进行复制、将其保存或引进检索系统;不得以任何形式或任何方式(电子、机械、影印、录制或其他可能的方式)进行商品传播或用于任何商业、赢利目的。

深圳市新格林耐特通信技术有限公司拥有本文档所涉及主题的专利、专利申请、商标、商标申请、版权及其他知识产权。

在未经深圳市新格林耐特通信技术有限公司明确书面许可的情况下,使用本文档资料并不表示您有使用有关专利、商标、版权或其他知识产权的特许。

此处所涉及的其它公司、组织或个人的产品、商标、专利,除非特别声明,归各自所有人所有。

感谢您使用深圳市新格林耐特通信技术有限公司的多WAN口全千兆企业级路由器(以下文本中简称本产品)。

本产品可以接入不同的ISP线路,满足您不同的需求。

支持多WAN 口流量负载均衡以及线路冗余备份,将宽带连接达到最高效。

本产品为您提供了高效的网络安全。

由于拥有强大的防火墙保护,可监控来自Internet 的包,过滤对局域网内服务器的非法请求,过滤黑客对局域网IP地址和端口的扫描,以防止外来的恶意攻击。

还能通过IP地址和MAC地址的绑定功能,防止IP地址被盗,使您的网络更加安全稳定。

WEB界面实时监控和管理局域网内的流量和用户,通过智能流控及IP流控完美分配局域网多用户对外网资源的使用。

除此之外,本产品还具有舒适的界面,结合简易的设置接口,让用户能很快的完成设置,让用户使用起来更方便快捷。

第一章产品概述。

简述路由器主要特点和产品规格。

第二章硬件安装。

指导您进行硬件安装。

第三章详细配置指南。

帮助您配置路由器的参数和高级特性。

现代数字信号处理在前沿学科中的应用实验-认知无线电

武汉理工大学现代数字信号处理在前沿学科中的应用实验认知无线电学院:学号:姓名:班级:实验一认知无线电的开发环境与基础实验入门一、实验目的1、掌握Linux系统下的基本操作。

2、了解认知无线电实验平台。

3、掌握GNU Radio软件平台的搭建过程。

4、了解USRP N210设备的检测。

二、系统、硬件配备一台配有千兆网卡的PC机,ubuntu11.10系统,GNU Radio3.5.0安装包(也可以选择其他带有UHD的GNU Radio版本)。

三、实验流程GNU Radio的安装主要包括三个部分的安装,准备库的安装、UHD的安装、GNU Radio的安装,下面将从这三个部分开始介绍。

1、网络连接在ubuntu下进行网络IP设置,打开命令终端,常用的命令:使用ls命令查看当前路径下文件,使用cd命令进入文件夹。

2、准备库的安装:在/redmine/projects/gnuradio/wiki/UbuntuInstall中,有其安装方法,对应找到我们的ubuntu11.10所需要的准备库内容,利用apt-get来安装。

安装完毕之后可以根据build-guide程序中所提到的库进行验证。

3、UHD的安装可以到官网上看见很多uhd的版本,我们采用的版本是003.004.000,可以直接从设备所带的光盘中获得(/tmp/uhd/host):执行:cd /tmp/uhd/hostmkdir buildcd buildcmake ../makemake testsudo make install4、GNU Radio的安装本文以GNU Radio为例,从官网上可以下到gnuradio3.5.0的安装包,我们可以通过安装包中的version.sh文件来查看其版本,选择gnuradio3.5.0来安装。

执行:cd /gnuradiomkdir buildcd buildcmake ../makemake testmake install5、设置环境变量按照README中指示设置环境变量,但是,其中python路径要根据我们的python版本设置,改正之后如下:export PYTHONPATH=/usr/local/lib/python2.7/disk-packagesexportLD_LIBRARY_PATH=$LD_LIBRARY_PATH:$HOME/local/libsudoldconfig三,实验结果执行gnuradio-companion指令,系统输出如下界面,安装成功实验二psk 数字调制实现一、 实验目的1、 熟悉Ubuntu 操作系统的使用。

基于无线电干涉的室内定位跟踪方法

基于无线电干涉的室内定位跟踪方法徐兵;齐望东;赵跃新;陈隆亮;黄明周;威力【摘要】无线电干涉定位系统(Radio Interferometric Positioning System,RIPS)是一种新型高精度测相定位系统,但RIPS在室内环境受多径效应影响无法进行有效定位.首先揭示了由多径引起的RIPS相位观测误差具有空间多样性特征,服从“类高斯”统计分布,然后提出基于无线电干涉的室内定位跟踪方法RIT(Radio Interferometric Tracking).不同于传统RIPS,RIT利多径相位误差的统计分布特性对运动速度进行估计,以此来完成室内目标的有效定位和跟踪.基于USRP N210软件无线电平台构建了原型系统,并在室内环境进行实际系统实验.实验结果表明,随着距离的增长RIT定位误差均值和中值大致稳定在80 cm和70 cm,相比RIPS分别下降了87.8%和60.7%,验证了RIT方法的有效性.【期刊名称】《微型机与应用》【年(卷),期】2017(036)024【总页数】4页(P58-61)【关键词】无线电干涉定位系统;室内定位;多径效应;空间多样性;无线电干涉室内定位跟踪【作者】徐兵;齐望东;赵跃新;陈隆亮;黄明周;威力【作者单位】中国人民解放军陆军工程大学指挥信息系统学院,江苏南京210007;中国人民解放军陆军工程大学指挥信息系统学院,江苏南京210007;中国人民解放军陆军工程大学指挥信息系统学院,江苏南京210007;中国人民解放军陆军工程大学指挥信息系统学院,江苏南京210007;中国人民解放军陆军工程大学指挥信息系统学院,江苏南京210007;中国人民解放军陆军工程大学指挥信息系统学院,江苏南京210007【正文语种】中文【中图分类】TN961位置信息在现代社会中发挥着重要的作用[1-3]。

无线电干涉定位系统(Radio Interferometric Positioning System,RIPS)是为了解决无线传感器网络中的节点高精度定位问题提出的一种新型定位方法[4-5]。

NI-USRP-2小时上手教程

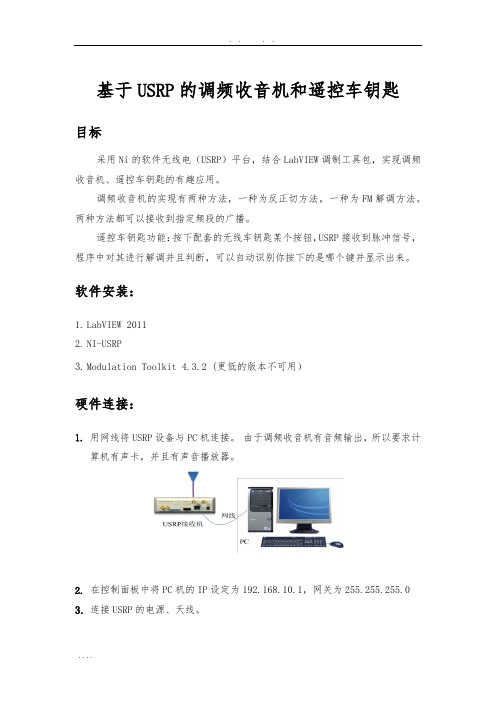

基于USRP的调频收音机和遥控车钥匙目标采用Ni的软件无线电(USRP)平台,结合LabVIEW调制工具包,实现调频收音机、遥控车钥匙的有趣应用。

调频收音机的实现有两种方法,一种为反正切方法,一种为FM解调方法。

两种方法都可以接收到指定频段的广播。

遥控车钥匙功能:按下配套的无线车钥匙某个按钮,USRP接收到脉冲信号,程序中对其进行解调并且判断,可以自动识别你按下的是哪个键并显示出来。

软件安装:bVIEW 20112.NI-USRP3.M odulation Toolkit4.3.2 (更低的版本不可用)硬件连接:1.用网线将USRP设备与PC机连接。

由于调频收音机有音频输出,所以要求计算机有声卡,并且有声音播放器。

2.在控制面板中将PC机的IP设定为192.168.10.1,网关为255.255.255.03.连接USRP的电源、天线。

4.在windows的开始菜单中All Programs\\National Instruments\\NI-USRP目录下面找到NI-USRP Configuration Utility,在Change IP Address 选项卡中应该能够看到设备(包括Device ID, IP Address, Type/revision)。

如果看不到设备,请点击Find Devices来寻找设备。

如果需要,可以选定一个设备并且在右边New IP Address栏中输入新IP地址,点击Change IP Address来修改USRP设备的IP地址。

操作流程一、基于反正切(Arctangent)方法的调频收音机1.该Demo只能使用USRP 2920(或者USRP N210)。

2.找到Demos中的FM Radio - Arctangent Method文件夹,打开NI USRP FM Demo- ArcTan Method_LV2011.VI,会看到如下图所示的“基于软件无线电的调频收音机”前面板。

Ccon102使用手册v1.1

7

2.3.4 舵机

7

2.3.5 计数

8

2.4 电机界面

8

2.5 设置界面

9

2.5.1 EEPROM(电可擦可编程只读存储器)

9

第3章 VJC4.1的安装与第一次使用

11

3.1 VJC4.1安装过程

11

3.2 选择控制器

12

3.3 菜单栏与工具栏

12

3.3.1 流程图界面下的部分菜单

12

3.3.2 JC界面下的部分菜单

33

5.2 其他传感器

35

5.2.1 控制器按键

35

5.2.2 旋转计数器

35

5.3 执行器

36

5.3.1 DO控制的执行器

36

5.3.2 直流电机和闭环电机

36

5.3.3 数字舵机

37

第6章 编程实例

39

6.1 显示模拟口的返回值

39

6.2 旋转计数器控制电机运动

40

6.3 光控手控灯开关

41

6.4 灰度传感器巡线原理

Ccon102 控制器 使用手册 v1.1

目录

第0章 前言

1

第1章 控制器简介

3

1.1 控制器硬件参数

3

1.2 电源与开关机

4

第2章 控制器界面介绍与操作方式

5

2.1 主界面

5

2.2 程序界面

5

2.3 端口界面

6

2.3.1 AI(模拟输入)

6

2.3.2 DO(数字输出)

7

2.3.3 DI(数字输入)

端口的DI功能是数字量传感器输入测试功能,只需读取数 值,没有下一步操作。

LP102-2AI微功耗GPRSRTU产品说明

LP102-2AI微功耗GPRS RTU产品说明1.简述_______________________________________________ 错误!未定义书签。

2.产品技术参数_______________________________________ 错误!未定义书签。

1)RTU指示灯说明 ___________________________________________ 错误!未定义书签。

2)产品技术参数列表_________________________________________ 错误!未定义书签。

3.微功耗或低功耗工作模式的实现_______________________ 错误!未定义书签。

1)低功耗工作模式的类型说明_________________________________ 错误!未定义书签。

2)低功耗工作模式的实现:___________________________________ 错误!未定义书签。

3)低功耗工作模式的时间设置_________________________________ 错误!未定义书签。

4.GPRS通信的实现___________________________________ 错误!未定义书签。

1)RTU连接配置软件和读取参数_______________________________ 错误!未定义书签。

2)设置RTU GPRS通信参数____________________________________ 错误!未定义书签。

3)设置RTU的通信选项 ______________________________________ 错误!未定义书签。

5.模拟量输入的连接和设置_____________________________ 错误!未定义书签。

1)模拟量输入的连接方式:___________________________________ 错误!未定义书签。

客所思外置声卡安装连接使用方法及简单故障排除

客所思外置声卡安装连接使用方法及简单故障排除产品使用方法声卡机身接口使用说明:声卡机身旋钮操作说明:监听音量:调节本地耳机、耳塞的监听输出音量。

调节监听音量不影响网络对方听到的信号(即录音音量)。

录音音量:调节电脑录音后、网络聊天唱歌对方听的音量。

音乐音量:调节电脑播放音乐、电影等素材的音量。

调节音乐音量不可调节外部音乐输入信号的音量。

效果音量:调节话筒湿声音量,由于不能调节干声音量,因此,必须通过调节效果音量的大小,来获取恰当的干湿比例,使得输出的人声清晰且具备自然的混响效果。

★注:调节以上 4 个音量时,6 个指示灯和功能绿灯将准确显示所调音量大小。

效果种类:(KX-2究极版)效果种类共有6种,通过按下效果种类按键来完成切换,顺序为 1~7 循环。

当指示灯显示 7 的时候,为无混响效果状态。

(KX-2传奇版)效果种类共有5种,通过按下效果种类按键来完成切换,顺序为 1~6 循环。

当指示灯显示 6 的时候,为无混响效果状态。

效果强度:通过按下效果时间按键来完成切换,顺序为 1~8 循环。

话筒音量、话筒高音、话筒中音、话筒低音为人声模拟调节,用于准确调整话筒均衡效果。

一般建议话筒音量 12-15 点钟位置,低音在 9-12 点钟位置,中音在 12点钟位置,高音在 11-13 点钟位置,具体需根据不同的嗓音条件和麦克风特点进行微调,直至声音清晰自然。

声卡机身显示灯说明:PC/静音:在接收到电脑控制界面的控制信息时闪烁;在音乐静音、话筒静音、录音静音三者之一被点击生效时长亮。

混音:混音状态开启时红灯亮,关闭时则红灯灭。

功能:用于显示 PEAK 状态(话筒音量达到峰值)、闪避状态、以及其他的辅助功能1-6双色指示灯,用于显示数字:工作模式:KX-2究极版KX-2传奇版KX-2传奇版控制面板功能说明(KX-2究极版不支持):客所思声卡电脑端设置方法:XP系统:1、屏蔽其它声卡:我的电脑→鼠标右键→管理→设备管理器→声音、视频和游戏控制器→鼠标右键停用除USB Audio Device 之外的所有英文开头声卡:(停用电脑自带声卡后系统会提示需要重启)2、鼠标右键点击电脑屏幕右下角的小喇叭,选择“调整音频属性”(从“控制面板”选项也可进入,选择“声音和音频设备”)。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

• Digital down-converters with programmable decimation rates

• Digital up-converters with programmable interpolation rates

RF Front end

Daughter board

Receiver

User-defined Code

ETH FPGA

ADC

RF Front end

PC

USRP-N210 (mother board)

Daughter board

15

N210平台结构

N210基本情况简介

• Two 100 MS/s 14-bit analog to digital converters

21

体系结构-硬件

User-defined Code

ETH FPGA

ADC DAC

RF Front end

Spartan-3A DSP FPGA XC3D3400A UHD FPGA Firmware in flash, loaded in power-cycle Digital down converters (DDC) implemented with cascaded

电子战的最主要的特点是频段宽(几乎复盖整个无线 频段),待处理的信号种类多,而且是处有被动接收 的条件下工作。

而目前的电子战系统往往都是已知的,或者在事先假 设的几种信号样式下工作,一旦目标信号的特征或信 号的通信方式发生变化,该系统就无能为力了,必须 研制开发新的电子战系统来适应变化,这样必然贻误 战机。

ADC DAC

RF Front end

Spartan-3A DSP FPGA XC3D3400A UHD FPGA Firmware in flash, loaded in power-cycle Digital down converters (DDC) implemented with cascaded

2

软件无线电技术和USRP

软件无线电

From FCC : “We view software radios as the result of an evolutionary process from purely hardware-based equipment to fully software-based equipment. In this regard, the process can be roughly described in three stages

wide variety of RF daughter boards

18

N210基本情况简介

• Auxiliary analog and digital I/O support complex radio controls such as RSSI and AGC

• Fully coherent multi-channel systems (MIMO capable)

17

N210基本情况简介

• Gigabit Ethernet Interface • Capable of processing signals

up to 100 MHz wide • Capable of streaming signals

up to 50 MHz wide • Modular architecture supports a

7

应用--无线电监测

对于传统的无线电监测任务可以有更灵活的解决方案 提供对新的智能认知无线电监测的能力。

8

应用--科学研究

认知无线电 新的调制解调方法 新的通信协议

9

应用--业余无线电台

可配置/可编程 多频段/多模式 可联网 同时收发语音、数据

和视频

10

应用--电子战

• 1 MB of on-board high-speed SRAM • TCXO Frequency Reference

19

体系结构

Transmitter

User-defined Code

ETH

FPGA

DAC

PC

USRP-N210 (mother board)

RF Front end

Daughter board

Definition From SDR Forum:

SW defines all waveform properties, cryptography and applications, is re-programmable, and may be upgraded in the field with new capabilities

4

理想的软件无线电体系结构

天线

基带(软件部分)

ADC DAC

GPU

5

软件无线电的优点-功能方面

可配置(Re-configurability) 增强可能的潜在应用 能最优化网络资源 便于演进到新的标准

多功能设备(Multifunctional devices) 可工作在多种模式(Multi-mode) 可工作在多个频段(Multi-band)

1. Hardware driven radios: Transmit frequencies, modulation type and other radio frequency (RF) parameters are determined by hardware and cannot be changed without hardware changes.

USRP-N210平台结构和使用介绍

北京海曼无限信息技术有限公司

Beijing Highmesh Info. Tech. Corp. Ltd. 2012年5月5日

介绍内容

软件无线电技术和USRP N210 平台结构 UHD和GNU Radio 编程和开发指南 应用案例(OpenBTS)

Receiver

User-defined Code

ETH FPGA

ADC

RF Front end

PC

USRP-N210 (mother board)

Daughter board

20

体系结构-硬件

User-defined Code

ETH FPGA

ADC DAC

RF Front end

RX2400 2.3-2.9 GHz Transceiver 50mW output (17dBm) 0-70dB Gain Direct conversion architecture Transceiver switch

Operators

Add Const Add Subtract Multiply constant Multiplier Divider Log function Or RMS …

31

List of GNU Radio Blocks

Type Conversions Complex to Arg Synchronizers Complex to Real Level Controls

25

LED指示

A:transmitting C: receiving

E: reference lock

B: mimo cable link D: firmware loaded F: CPLD loaded

26

UHD和GNU Radio

安装 UHD

Source Code C++ compiler CMake Boost Python Cheetah Doxygen (Optional) Docutils (Optional)

目标

电视 塔

12

软件定义无线电体系结构

天线 射频

中频

基带(软件部分)

ADC 带通滤波器 DAC

频率振荡器

FPGA DSP CPU GPU

13

体系结构-总体

Hardware Software

14

体系结构

Transmitter

User-defined Code

ETH

FPGA

DAC

PC

USRP-N210 (mother board)

GLFSR source Wav File source Message source Pad source Virtual source

30

List of GNU Radio Blocks

Signal Sinks

Null sinks Vector sinks File sinks Audio sink TCP/UDP sink Wav File sink Message sink Pad sink Virtual Sink

See: /uhd_docs/manual/html/build.html

/redmine/ettus/projects/uhd/wiki

28

GNU Radio

29

List of GNU Radio Blocks

更短的市场投放时间(Shorter time-to-market) 更快的提供更有针对性得差异化产品 向后的兼容性

6

软件无线电的优点-性能方面

低硬件成本 硬件设备可以复用 使用更多标准的硬件模块

“灵活”的无线软件架构 应用复用

应用可被移植到不通的硬件平台 应用可根据需要灵活调整 改善开发生产效率 标准的APIs, 开放的体系结构 第三方应用的即插即用