STM32F103ZET6引脚

STM32F103RCT6引脚功能及使用

STM32F103RCT6引脚功能及使用脚号引脚名称主功能默认复用重定义备注1VBAT VBAT----说明1 2PC13-TAMPER-RTC PC13TAMPER-RTC--说明3 3PC14-OSC32_IN PC14OSC32_IN--说明3 4PC15-OSC32_OUT PC15OSC32_OUT--说明3 5OSC_IN OSC_IN--CAN_RX晶振6OSC_OUT OSC_OUT--CAN_TX晶振7NRST NRST----复位8PC0PC0ADC123_IN10--ADC 9PC1PC1ADC123_IN11--ADC 10PC2PC2ADC123_IN12--ADC 11PC3PC3ADC123_IN13--ADC 12VSSA VSSA----模拟地13VDDA VDDA----模拟电14PA0-WKUP PA0WKUP--说明4 USART2_CTS说明5 ADC123_IN0TIM2_CH1_ETR说明6 TIM5_CH1TIM8_ETR15PA1PA1USART2_RTS--ADC123_IN1TIM2_CH2TIM5_CH216PA2PA2USART2_TX--ADC123_IN2TIM2_CH3TIM5_CH317PA3PA3USART2_RX--ADC123_IN3TIM2_CH4TIM5_CH418VSS_4VSS_4----数字地19VDD_4VDD_4----数字电20PA4PA4USART2_CK--ADC12_IN4SPI1_NSSDAC_OUT121PA5PA5ADC12_IN5--SPI1_SCKDAC_OUT222PA6PA6ADC12_IN6TIM1_BKIN TIM3_CH1TIM8_BKINSPI1_MISO23PA7PA7ADC12_IN7TIM1_CH1N TIM3_CH2TIM8_CH1NSPI1_MOSI24PC4PC4ADC12_IN14--25PC5PC5ADC12_IN15--26PB0PB0ADC12_IN8TIM1_CH2N TIM3_CH3TIM8_CH2N27PB1PB1ADC12_IN9TIM1_CH3N TIM3_CH4TIM8_CH3N28PB2PB2----BOOT129PB10PB10USART3_TXTIM2_CH3 I2C2_SCL30PB11PB11USART3_RXTIM2_CH4 I2C2_SDA31VSS_1VSS_1----数字地32VDD_1VDD_1----数字电33PB12PB12USART3_CK--TIM1_BKINSPI2_NSS说明7 I2C2_SMBAI2S2_WS34PB13PB13USART3_CTS--TIM1_CH1NSPI2_SCKI2S2_CK35PB14PB14USART3_RTS--TIM1_CH2NSPI2_MISO36PB15PB15TIM1_CH3N--SPI2_MOSII2S2_SD37PC6PC6TIM8_CH1TIM3_CH1I2S2_MCKSDIO_D6说明838PC7PC7TIM8_CH2NTIM3_CH2 I2S3_MCKSDIO_D739PC8PC8TIM8_CH3NTIM3_CH3 SDIO_D040PC9PC9TIM8_CH4TIM3_CH4 SDIO_D141PA8PA8USART1_CK--TIM1_CH1MCO42PA9PA9USART1_TX--TIM1_CH243PA10PA10USART1_RX--TIM1_CH344PA11PA11USART1_CTS--TIM1_CH4USBDMCAN_RX45PA12PA12USART1_RTS--TIM1_ETRUSBDPCAN_TX46PA13JTMS--PA13 SWDIO47VSS_2VSS_2----数字地48VDD_2VDD_2----数字电49PA14JTCK--PA14SWCLK50PA15JTDI SPI3_NSS PA15I2S3_WSTIM2_CH1_ETRSPI1_NSS51PC10PC10UART4_TX USART3_TXSDIO_D252PC11PC11UART4_RX USART3_RXSDIO_D353PC12PC12UART5_TX USART3_CKSDIO_CK54PD2PD2UART5_RX--TIM3_ETRSDIO_CMD55PB3JTDO SPI3_SCKPB3TIM2_CH2 I2S3_CKSPI1_SCKTRACESWO56PB4NJTRST SPI3_MISOPB4 TIM3_CH1 SPI1_MISO57PB5PB5SPI3_MOSI TIM3_CH2 I2C1_SMBASPI1_MOSI I2S3_SD58PB6PB6TIM4_CH1USART1_TXI2C1_SCL59PB7PB7TIM4_CH2USART1_RXI2C1_SDA60BOOT0BOOT0----61PB8PB8TIM4_CH3I2C1_SCL SDIO_D4CAN_RX62PB9PB9TIM4_CH4I2C1_SDA SDIO_D5CAN_TX63VSS_3VSS_3----数字地64VDD_3VDD_3--数字电说明:1)VBAT:VBAT给RTC和备份区域供电,目的是在VDD断电时保证相关区域的数据内容有效,一般连接到外部电池。

STM32F103ZET6的基本定时器

STM32F103ZET6的基本定时器1、定时器的分类 STM32F103ZET6总共有8个定时器,它们是:TIM1~TIM8。

STM32的定时器分为基本定时器、通⽤定时器和⾼等定时器。

TIM6、TIM7是基本定时器。

基本定时器是只能向上计数的16位定时器,基本定时器只能有定时的功能,没有外部IO⼝,所以没有捕获和⽐较通道。

TIM2、TIM3、TIM4、TIM5是通⽤定时器。

通⽤定时器是可以向上计数,也可以向下计数的16位定时器。

通⽤定时器可以定时、输出⽐较、输⼊捕捉,每个通⽤定时器具有4个外部IO⼝。

TIM1、TIM8是⾼等定时器。

⾼等定时器是是可以向上计数,也可以向下计数的16位定时器。

⾼等定时器可以定时、输出⽐较、输⼊捕捉、还可以输出三相电机互补信号,每个⾼等定时器有8个外部IO⼝。

定时器分类图如下:2、基本定时器 基本定时器没有外部IO⼝,所以它只有定时的功能。

基本定时器只能向上计数,也就是说基本定时器只能递增计数。

基本定时器功能框图如下: 从功能图的1中可以看到,基本定时器的时钟TIMxCLK来⾃内部时钟,该内部时钟为经过APB1预分频器分频后提供的。

基本定时器跟APB1总线时钟的关系如下:如果APB1预分频系数为1,则基本定时器的时钟等于APB1总线时钟。

如果APB1预分频系数不为1,则基本定时器的时钟等于APB1总线时钟经过分频后的2倍。

⽐如APB1总线经过2分频后的时钟为36MHZ,那么基本定时器的时钟就是72MHZ3(36*2)。

功能图中的2是⼀个预分频器,来⾃内部的时钟经过预分器分频后的时钟,⽤来驱动基本定时器的计数器计数。

基本定时器的预分频器是⼀个16位的预分频器,预分频器可以对定时器时钟进⾏1~65536之间的任何⼀个数进⾏分频。

计算⽅式如下: 定时器⼯作时钟 = 来⾃APB1的时钟/(预分频系数+1) 功能图中的3是⼀个16位的计数器,该计数器能能向上计数,最⼤计数值位65535。

STM32学习笔记-STM32F103ZET6

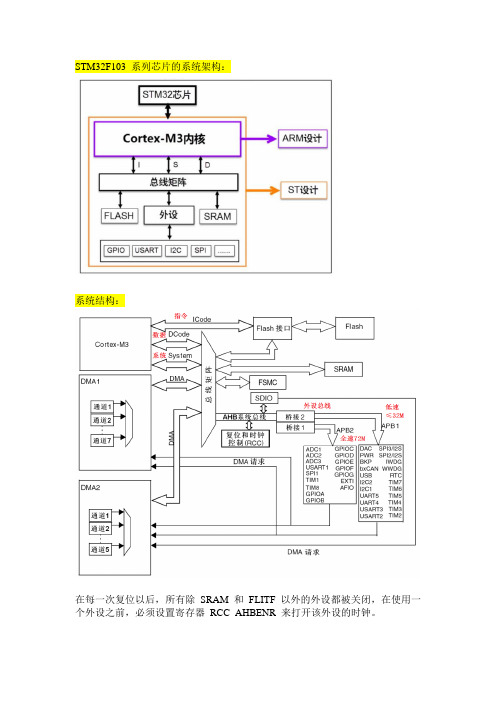

STM32F103 系列芯片的系统架构:系统结构:在每一次复位以后,所有除SRAM 和FLITF 以外的外设都被关闭,在使用一个外设之前,必须设置寄存器RCC_AHBENR 来打开该外设的时钟。

GPIO 输入输出,外部中断,定时器,串口。

理解了这四个外设,基本就入门了一款MCU。

时钟控制RCC:-4~16M 的外部高速晶振-内部8MHz 的高速RC 振荡器-内部40KHz低速RC 振荡器,看门狗时钟-内部锁相环(PLL,倍频),一般系统时钟都是外部或者内部高速时钟经过PLL 倍频后得到- 外部低速32.768K 的晶振,主要做RTC 时钟源ARM存储器映像:数据字节以小端格式存放在存储器中。

一个字里的最低地址字节被认为是该字的最低有效字节,而最高地址字节是最高有效字节。

存储器映像与寄存器映射:ARM 存储器映像4GB0X0000 00000X1FFF FFFF0X2000 00000X3FFF FFFF0X4000 00000X5FFF FFFF寄存器名称相对外设基地址的偏移值编号位表读写权限寄存器位功能说明使用C语言封装寄存器:1、总线和外设基地址封装利用地址偏移(1)定义外设基地址(Block2 首地址)(2)定义APB2总线基地址(相对外设基地址偏移固定)(3)定义GPIOX外设基地址(相对APB2总线基地址偏移固定)(4)定义GPIOX寄存器地址(相对GPIOX外设基地址偏移固定)(5)使用 C 语言指针操作寄存器进行读/写//定义外设基地址#define PERIPH_BASE ((unsigned int)0x40000000) 1)//定义APB2 总线基地址#define APB2PERIPH_BASE (PERIPH_BASE + 0x00010000) 2)//定义GPIOC 外设基地址#define GPIOC_BASE (AHB1PERIPH_BASE + 0x0800) 3)//定义寄存器基地址这里以GPIOC 为例#define GPIOC_CRL *(unsigned int*)(GPIOC_BASE+0x00) 4)#define GPIOC_CRH *(unsigned int*)(GPIOC_BASE+0x04)#define GPIOC_IDR *(unsigned int*)(GPIOC_BASE+0x08)#define GPIOC_ODR *(unsigned int*)(GPIOC_BASE+0x0C)#define GPIOC_BSRR *(unsigned int*)(GPIOC_BASE+0x10)#define GPIOC_BRR *(unsigned int*)(GPIOC_BASE+0x14)#define GPIOC_LCKR *(unsigned int*)(GPIOC_BASE+0x18)//控制GPIOC 第0 管脚输出一个低电平5)GPIOC_BSRR = (0x01<<(16+0));//控制GPIOC 第0 管脚输出一个高电平GPIOC_BSRR = (0x01<<0);2、寄存器封装利用结构体、外设基地址和寄存器地址偏移typedef unsigned int uint32_t; /*无符号32 位变量*/typedef unsigned short int uint16_t; /*无符号16 位变量*//* GPIO 寄存器列表*/typedef struct{uint32_t CRL; /*GPIO 端口配置低寄存器地址偏移: 0x00 */uint32_t CRH; /*GPIO 端口配置高寄存器地址偏移: 0x04 */uint32_t IDR; /*GPIO 数据输入寄存器地址偏移: 0x08 */uint32_t ODR; /*GPIO 数据输出寄存器地址偏移: 0x0C */uint32_t BSRR; /*GPIO 位设置/清除寄存器地址偏移: 0x10 */uint32_t BRR; /*GPIO 端口位清除寄存器地址偏移: 0x14 */uint16_t LCKR; /*GPIO 端口配置锁定寄存器地址偏移: 0x18 */}GPIO_TypeDef;只要给结构体设置好首地址,就能把结构体内成员的地址确定下来,然后就能以结构体的形式访问寄存器。

stm32f103zet6定时器详解及应用

stm32f103zet6定时器详解及应用

1、stm32f103zet6芯片及引脚图

2、stm32f103xx器件功能与配置

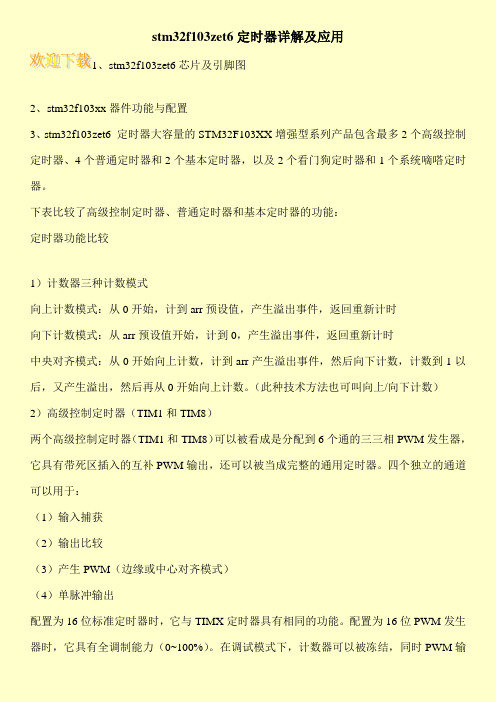

3、stm32f103zet6 定时器大容量的STM32F103XX增强型系列产品包含最多2个高级控制定时器、4个普通定时器和2个基本定时器,以及2个看门狗定时器和1个系统嘀嗒定时器。

下表比较了高级控制定时器、普通定时器和基本定时器的功能:

定时器功能比较

1)计数器三种计数模式

向上计数模式:从0开始,计到arr预设值,产生溢出事件,返回重新计时

向下计数模式:从arr预设值开始,计到0,产生溢出事件,返回重新计时

中央对齐模式:从0开始向上计数,计到arr产生溢出事件,然后向下计数,计数到1以后,又产生溢出,然后再从0开始向上计数。

(此种技术方法也可叫向上/向下计数)

2)高级控制定时器(TIM1和TIM8)

两个高级控制定时器(TIM1和TIM8)可以被看成是分配到6个通的三三相PWM发生器,它具有带死区插入的互补PWM输出,还可以被当成完整的通用定时器。

四个独立的通道可以用于:

(1)输入捕获

(2)输出比较

(3)产生PWM(边缘或中心对齐模式)

(4)单脉冲输出

配置为16位标准定时器时,它与TIMX定时器具有相同的功能。

配置为16位PWM发生器时,它具有全调制能力(0~100%)。

在调试模式下,计数器可以被冻结,同时PWM输。

红牛开发板stm32f103zet6用户手册

红牛开发板用户手册 CopyRight@20091.概述红牛STM32开发板是以意法半导体 (ST)公司推出的基于ARM Cortex-M3系列最高配置芯片STM32F103ZE为核心组成。

板上资源:●CPU:STM32F103ZET6;(LQFP144脚,片上集成512K flash、64KRAM、12Bit ADC、DAC、PWM、CAN、USB、SDIO、FSMC等资源)●板上外扩512K SRAM, 2M NOR FLASH (板上支持最大1024kSRAM,16M的NOR FLASH)满足大容量数据采集、处理及分析要求●板上外扩128M或256M NAND FLASH(标配128M)满足彩屏上丰富的图片存储、数据表格存储,文件管理等应用● 搭配2.8寸TFT真彩触摸屏模块或3.2寸TFT真彩触摸屏模块(由用户选择),FSMC控制,彩屏模块上配置RSM1843(ADS7843、TSC2046脚对脚兼容)触摸控制器芯片,支持一个SD卡(SPI方式)可用于存储图片,支持一个AT45DBxxx 的DATA FLASH(可用于存储汉字库)● 一路CAN通信接口,驱动器芯片SN65VHD230● 两路RS232接口● 一路RS485通信接口● 一个SD卡座SDIO控制方式● 一个I2C存储器接口,标配24LC02(EEPROM)● 一个SPI存储器接口,标配AT45DB161D(DATA FLASH)● 一路ADC调节电位器输入● 三路ADC输入接线端子引出● 两路PWM输出接线端子引出● 两路DAC输出接线端子引出● 一个蜂鸣器、五个用户LED灯、一个电源指示灯,一个USB通信指示灯,● 四个用户按键,一个系统复位按键● 电源选择跳线,支持外接5V 电源供电,USB 供电或JLINK 供电 ● 板子规格尺寸:13CM X 10CM● 所有I/O 口通过2.54MM 标准间距引出,方便二次开发板上的全部硬件特性能快速帮助你评估STM32F103ZE 所有外设(USB 、motor control,、CAN,、SPI 、MicroSD card 、smartcard 、USART 、NOR Flash 、NAND flash 、 SRAM )和开发你自己的应用项目。

STM32F103ZET6时钟

STM32F103ZET6时钟1、STM32F103ZET6时钟说明 STM32F103ZET6的时钟树图如下所⽰: STM32F103ZET6有很多个时钟源,分别有: HSE:⾼速外部时钟信号。

HSI:⾼速内部部时钟信号。

LSI:低速内部时钟信号。

LSE:低速外部时钟信号。

HSI和LSI是芯⽚内置的时钟源,它们的频率⼤⼩是固定的,HSI是8MHZ,LSI是⼤约40KHZ。

时钟树中的序号1是⾼速外部时钟信号HSE: HSE是由有源晶振或⽆源晶振通过OSC_OUT和OSC_IN脚提供的,从图⽚中可以看到,HSE频率从4MHZ到16MHZ不等。

当使⽤有源晶振时,时钟从OSC_IN引脚进⼊,OSC_OUT引脚悬空;当使⽤⽆源晶振时,时钟从OSC_IN和OSC_OUT进⼊,并且要配谐振电容。

HSE最常使⽤的就是8MHZ的⽆源晶振。

时钟树中的序号D是外部低速时钟LSE: LSE是由有源晶振或⽆源晶振通过OSC32_OUT和OSC32_IN脚提供的。

LSE⼀般使⽤的是32.768KHZ的⽆源晶振。

时钟树中的序号2是选择PLL(倍频后的时钟)的时钟源: 从图中可以看出,PLL时钟的来源可以是HSE或HSI/2,通过PLLSRC(CFGR寄存器的bit16)来选择使⽤哪⼀个时钟源。

HSI是8MHZ的内部⾼速时钟信号,HSI会根据温度和环境的情况频率会有漂移,⼀般不作为PLL的时钟来源。

⼀般使⽤HSE作为PLL的时钟源。

时钟树中的序号3是设置PLL的倍频因⼦: 可以对PLL的时钟来源进⾏倍频,然后得到PLLCLK时钟源。

倍频因⼦可以通过时钟配置寄存器CFGR的bit21~bit18:PLLMUL[3:0]来配置,分别可配置成2、3、4、5、6、7、8、9、10、11、12、13、14、15、16倍频。

举个例⼦来说,如果选择HSE作为PLL的时钟源,⽽且HSE=8MHZ,且将PLL的倍频因⼦设置为9倍频,那么PLLCLK=9*8MHZ = 72MZH。

STM32F103ZET6串口通信

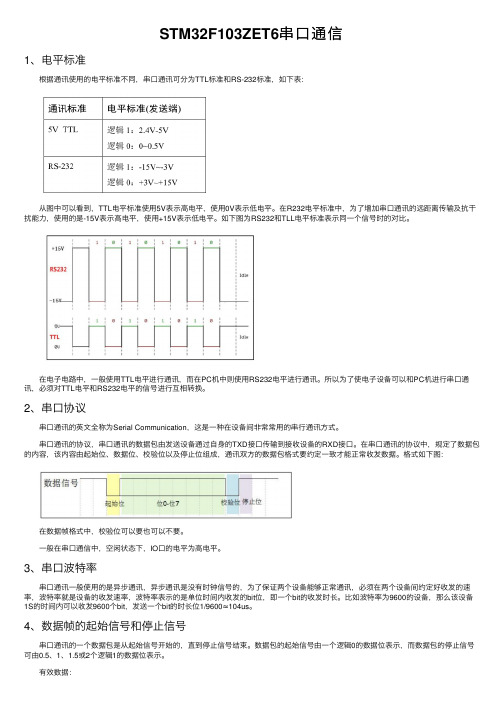

STM32F103ZET6串⼝通信1、电平标准 根据通讯使⽤的电平标准不同,串⼝通讯可分为TTL标准和RS-232标准,如下表: 从图中可以看到,TTL电平标准使⽤5V表⽰⾼电平,使⽤0V表⽰低电平。

在R232电平标准中,为了增加串⼝通讯的远距离传输及抗⼲扰能⼒,使⽤的是-15V表⽰⾼电平,使⽤+15V表⽰低电平。

如下图为RS232和TLL电平标准表⽰同⼀个信号时的对⽐。

在电⼦电路中,⼀般使⽤TTL电平进⾏通讯,⽽在PC机中则使⽤RS232电平进⾏通讯。

所以为了使电⼦设备可以和PC机进⾏串⼝通讯,必须对TTL电平和RS232电平的信号进⾏互相转换。

2、串⼝协议 串⼝通讯的英⽂全称为Serial Communication,这是⼀种在设备间⾮常常⽤的串⾏通讯⽅式。

串⼝通讯的协议,串⼝通讯的数据包由发送设备通过⾃⾝的TXD接⼝传输到接收设备的RXD接⼝。

在串⼝通讯的协议中,规定了数据包的内容,该内容由起始位、数据位、校验位以及停⽌位组成,通讯双⽅的数据包格式要约定⼀致才能正常收发数据。

格式如下图: 在数据帧格式中,校验位可以要也可以不要。

⼀般在串⼝通信中,空闲状态下,IO⼝的电平为⾼电平。

3、串⼝波特率 串⼝通讯⼀般使⽤的是异步通讯,异步通讯是没有时钟信号的,为了保证两个设备能够正常通讯,必须在两个设备间约定好收发的速率,波特率就是设备的收发速率,波特率表⽰的是单位时间内收发的bit位,即⼀个bit的收发时长。

⽐如波特率为9600的设备,那么该设备1S的时间内可以收发9600个bit,发送⼀个bit的时长位1/9600≈104us。

4、数据帧的起始信号和停⽌信号 串⼝通讯的⼀个数据包是从起始信号开始的,直到停⽌信号结束。

数据包的起始信号由⼀个逻辑0的数据位表⽰,⽽数据包的停⽌信号可由0.5、1、1.5或2个逻辑1的数据位表⽰。

有效数据: 在数据包的起始位之后紧接着的就是要传输的主体数据内容,也称为有效数据,有效数据的长度常被约定位5、6、7或8位。

STM32F103引脚功能定义资料

2.1 器件一览表二:器件功能和配置(STM32F103xx增强型)图一.STM32F103xx增强型模块框图工作温度=-40至+105°C (结温达125°C) AF: I/O口上的其他功能3管脚定义图二.STM32F103xx增强型VFQFPN36管脚图四.STM32F103xx增强型LQFP64管脚表三. 管脚定义表三.管脚定义(续)注:1. I :输入, O:输出, S:电源, HiZ:高阻2. FT:兼容5V3. 其中部分功能仅在部分型号芯片中支持,具体信息请参考表2。

4. PC13,PC14和PC15引脚通过电源开关进行供电,因此这三个引脚作为输出引脚时有以下限制:9作为输出脚时只能工作在2MHz模式下9最大驱动负载为30pF9同一时间,三个引脚中只有一个引脚能作为输出引脚。

5. 仅在内嵌大等于64K Flash的型号中支持此类功能。

6. VFQFPN36封装的2号,3号引脚和LQFP48,LQFP64封装的5号,6号引脚在芯片复位后默认配置为OSC_IN和OSC_OUT功能脚。

软件可以重新设置这两个引脚为PD0和PD1功能脚。

但对于LQFP100封装,由于PD0和PD1为固有的功能脚,因此没有必要再由软件进行设置。

更多详细信息请参考STM32F10xxx参考手册的复用功能I/O章节和调试设置章节。

PD0和PD1作为输出引脚只能工作在50MHz模式下。

7. 此类复用功能能够由软件配置到其他引脚上,详细信息请参考STM32F10xxx参考手册的复用功能I/O章节和调试设置章节。

4存储器映像图七存储器图5电气特性请参考英文版数据手册6封装参数请参考英文版数据手册7订货代码表四. 订货代码型号闪存存储器K字节SRAM存储器K字节封装STM32F103C6T6 32 10STM32F103C8T6 64 20STM32F103CBT6 128 20LQFP48STM32F103R6T6 32 10STM32F103R8T6 64 20STM32F103RBT6 128 20LQFP64STM32F103V8T6 64 20STM32F103VBT6 128 20LQFP100STM32F103V8H6 64 20STM32F103VBH6 128 20LFBGA100STM32F103T6U6 32 6STM32F103T8U6 64 10VFQFPN367.1 后续的产品系列后续的STM32F103xx增强型系列产品将会有更广泛的型号选择,芯片将会有更大的封装尺寸并内嵌多达512KB的Flash和48KB的SRAM。

STM32F103ZET6(中文)

本文档英文原文下载地址: /stonline/products/literature/ds/14611.pdf

参照2009年3月 STM32F103xCDE数据手册 英文第5版 (本译文仅供参考,如有翻译错误,请以英文原稿为准)

1/87

深圳市迪通科技有限公司 TEL:0755-83312947 83313941 83317488FAX:0755-83311568

功能

■ 内核:ARM 32位的Cortex™-M3 CPU − 最高72MHz工作频率,在存储器的0等待周 期访问时可达1.25DMips/MHz(Dhrystone 2.1) − 单周期乘法和硬件除法

■ 存储器

− 从256K至512K字节的闪存程序存储器 − 高达64K字节的SRAM − 带4个片选的静态存储器控制器。支持CF卡、

深圳市迪通科技有限公司 TEL:0755-83312947 83313941 83317488FAX:0755-83311568

数据手册

STM32F103xC STM32F103xD STM32F103xE

增强型,32位基于ARM核心的带512K字节闪存的微控制器 USB、CAN、11个定时器、3个ADC 、13个通信接口

■ CRC计算单元,96位的芯片唯一代码

■ ECOPACK®封装

表1 器件列表

参考 STM32F103xC STM32F103xD STM32F103xE

基本型号

STM32F103RC 、 STM32F103VC 、 STM32F103ZC STM32F103RD 、 STM32F103VD 、 STM32F103ZD STM32F103RE 、 STM32F103ZE 、 STM32F103VE