汽车尾灯控制器

汽车尾灯控制电路

汽车尾灯控制电路

设计思路

利用74161构成七进制计数器,经过74138译码器,对应七种状态 利用74160构成三进制,实现3个指示灯的循环点亮, 经非门接三进制 74下

汽车尾灯控制电路

元器件解释

74LS160 74LS160是一种十进制同步计数器。在 Multisim中,它可以在每个时钟脉冲 上进行计数。当时钟信号上升沿触发 时,计数器会自动加1。该计数器可以 在四个并行输入(J0、J1、J2和J3)上 接收输入信号,并输出四个二进制计 数结果(Q0、Q1、Q2和Q3)

汽车尾灯控制电路

74LS138 74LS138是一种3-8译码器, 用于将一个三位二进制地址 信号转换为8个选通输出信 号。它可以将一个3位二进 制地址信号(A0,A1和A2)转 换为8个选通信号(Y0至Y7)

汽车尾灯控制电路

DCD_HEX 在Multisim中,DCD_HEX是七段数码管的一种, 七段数码管是一种数字显示设备,用于显示0到9 以及其他一些特殊字符。通过将七段数码管与适 当的电路连接,并在数字输入端口上提供适当的 信号,可以将数字值显示在七段数码管上

汽车尾灯控制电路

(3)汽车左转弯行驶时,左侧3个指示灯按左循环顺序点亮,右侧的指示灯全灭 (4)汽车临时刹车时,所有指示灯同时处于闪烁状态 (5)右转弯刹车时,右侧的三个尾部灯顺序循环点亮,左侧的灯全亮 (6)左转弯刹车时,左侧的三个尾部灯顺序循环点亮,右侧的灯全亮 (7)倒车时,尾部两侧的6个指示灯随CP时钟脉冲同步闪烁 同时用七段数码管显示汽车的七种工作状态,即正常行驶、刹车、右转弯、左 转弯、右转弯刹车、左转弯刹车和倒车等功能

汽车尾灯控制电路

运行结果

1.正常行驶

汽车尾灯控制电路

汽车尾灯控制电路的设计

汽车尾灯控制电路的设计一.概述汽车尾灯控制电路是很常用的工作电路,在日常的生活中有着很广泛的应用。

汽车行驶时,会出现正常行驶、左转弯、右转弯、刹车四种情况,针对这四种情况可以设计出汽车尾灯的控制电路来表示这四种状态。

设计一个汽车尾灯控制电路,技术指标如下:假设汽车尾部左右两侧各有3个指示灯(用发光二极管模拟);汽车正常运行时指示灯全灭;汽车左转弯时,左侧3个指示灯按左循环顺序点亮;汽车右转弯时,右侧3个指示灯按右循环顺序点亮;临时刹车时所有指示灯同时闪烁。

二.技术指标2.1初始条件直流可调稳压电源一台、万用表一块、面包板一块、元器件若干、剪刀、镊子等必备工具2.2技术要求设计汽车尾部左右两侧各有3个指示灯(用发光二极管模拟)。

要求实现(1)汽车正常运行时指示灯全灭;(2)右转弯时右侧3个指示灯按右循环顺序点亮;(3)左转弯时左侧3个指示灯按左循环顺序点亮;(4)临时刹车时所有指示灯同时闪烁。

三.方案论证在设计本电路时,一共考虑过两种方案。

这两种方案在于产生001,010,100三种信号的方法不同。

3.1方案一1汽车尾灯控制电路主要由D触发器逻辑电路,左转、右转控制电路,刹车控制电路构成。

首先将脉冲信号CLK提供给D触发器逻辑电路。

用三片D触发器设计一个逻辑电路可以产生001、010、100的循环信号。

将此信号作为左转、右转的原始信号。

设置左转控制开关和右转控制开关。

通过开关的控制将左转、右转的原始信号通过逻辑电路分别输出到左、右的3个汽车尾灯上。

这部分电路起到信号分拣的作用。

设置刹车控制开关,将脉冲信号CLK提供给刹车控制电路。

当开关置为刹车信号时,分拣之后的信号通过逻辑电路实现刹车时所有指示灯随着时钟信号CLK全部闪烁的功能。

最终得到的信号即可输出到发光二极管上,实现所需功能。

方案一原理框图如图(1)所示。

图(1)方案一原理框图3.2方案二汽车尾灯控制电路主要由开关控制电路,三进制计数器,译码电路,显示、驱动电路构成。

elmos推出基于E522.90系列芯片的汽车尾灯解决方案

elmos 推出基于E522.90 系列芯片的汽车尾灯解决方案最新LED 和电机控制解决方案将亮相2018 慕尼黑上海电子展德国elmos 公司日前宣布elmos 推出基于E522.90/91/92/93 系列芯片用于汽车尾灯LED 线性恒流驱动器的系列解决方案,包括车辆尾灯、车内氛围灯和48V 电池系统的BLDC 电机控制。

E522.9x 系列的每个通道输出电流为14mA 至55mA,并联工作时单颗芯片最高输出165mA,即使在恶劣的散热条件下,这款拥有专利的电源管理芯片也可确保LED 的恒流特性。

该方案设计有外部分流电阻,可以把额外的功耗通过外部电阻耗散掉,这个方案将功耗成比例的分配到外部器件和PCB 上,避免PCB 上出现局部过热点。

这个独特的方案中,功耗一部分通过芯片本身耗散,另外一部分则由外部器件耗散,减小了芯片自身的温升,为客户带来更多的设计余量。

该家族系列产品还具有更高电流和相同特性的芯片(每通道48-151mA 或并联工作450mA)E522.8x 产品系列,该系列产品已经在汽车照明产品中有多个成功应用案例。

据悉,该系列最新应用解决方案将在2018 年慕尼黑上海电子展(3 月14日至16 日)期间向观众现场展示并做详细说明。

elmos 还将带来LIN 自动寻址的单芯片RGB 驱动方案E521.36,该方案用在车内RGB 氛围灯应用中,采用才方案的RGB 模块可直接连接到LIN 总线上,elmos 的E521.36 芯片实现了简单、灵活、经济高效且节省空间的设计。

该器件包括一个基于MSP430 的16 位微控制器,具有32k 字节的NVM,128 字节的EEPROM,带有集成BSM 自动寻址(总线分流法)的LIN 收发器(符合LIN 2.2 规范),四路高达40mA/单通道的恒流源驱动和三个16 位PWM 发生器。

48MHz PWM 时钟确保732Hz 刷新频率下提供全面的16 位色彩分辨率,实现无闪烁效果,可以满足目前所有的OEM 要求。

基于CPLD的汽车尾灯控制器设计

电器的线圈通 电使继电器 的开 关闭合, C P L D 开发板主片 引脚的 输出电压为3 . 3 V , 继电器J z C 一 2 3 F( 4 1 2 3 ) 的驱 动电压为6 V , 所 以

我利用三极管 的共发射 极共功率放大 的原理将 电压放大 来驱

继电器的开关闭合时就能点亮灯泡。 本 次设计我只 直亮 。 汽 车晚 上行驶 ( 按下晚 上行 驶开关 ) 时, 晚上 照明灯 动继电器, 用了一个继 电器和一个放大电路来实现 , 并控制其 中一个灯 的 ( 两个 白色L E D 灯) 一直亮。 汽车倒车 ( 按下倒车开关 ) 时, 蜂鸣 亮和灭, 这代表了现 实中的汽车尾灯。 其他的灯就 用L E D 灯来代 器有规律的呜叫 ( 本次设计的扩展功能) 。

时间间隔约为0 . 5 s 。 这样就 能让人很清楚的明白该汽 车的 具先进、 标准 产品无需测 试、 质量稳 定以及可实时在 线检验等 亮 , 优 点, 因此被广泛 应用于产品的原型设计和 产品生产 ( 一般在 动作 以采取相应 的动作从而避免交通事故的发生。

1 0 , 0 0 0 件 以下) 之中。 几乎所有应用门阵列 、 P L D 和 中小规模通用 数 字集成 电路 的场合均可应用F P G A  ̄ %P L D 器件。 时钟信 号产 生 电路主要 由3 个非 门2 个 电阻和一个 电容 够

・

设 计 分 析

基于C P L D的汽车尾灯控制器设 计

蔡文博 徐思琦 ( 上海工 程技术大学汽车 工程学院, 上 海 2 0 1 6 2 0 )

摘 要 : C P L D >  ̄ 其众 多的优 点 , 在电 子设 计中 发挥 了巨大的作用。 本文 采 C P L D 技术, 对汽车尾 灯控制器进行设计, 并经测试 , 完全 达到了预设

EDA 课程设计汽车尾灯控制器

测试方法:使用专业测试 设备进行测量

评估标准:符合国家标准 和行业规范

调试方法:根据测试结果 进行参数调整和优化

调试目标:达到最佳性能 和稳定性

实际应用的故障排除与维护

故障现象:尾灯不亮或闪烁异常 故障原因:线路故障、灯泡损坏、控制器故障等 故障排除:检查线路、更换灯泡、检查控制器等 维护方法:定期检查、清洁、更换老化部件等

03

EDA工具的使用

EDA工具介绍

EDA工具:电子设计自动化工具,用于电路设计和仿真

主要功能:电路设计、仿真、验证、优化等

常用EDA工具:Cadence、Mentor Graphics、Synopsys等 EDA工具在汽车尾灯控制器设计中的应用:电路设计、仿真、验证 等

EDA工具的基本操作

添加标题

信号输入模块:接收来自汽车其他系统 的信号

保护模块:保护电路免受过压、过流 等异常情况的影响

汽车尾灯控制器的设计要求

安全性:确保尾灯在紧急情况下能够及时亮起,提醒后车注意 稳定性:控制器应具备良好的稳定性,避免因故障导致尾灯无法正常工作 节能性:控制器应具备节能功能,降低汽车能耗 美观性:尾灯控制器的设计应与汽车整体设计风格相协调,美观大方

题所在并提出改进措施

07

汽车尾灯控制器的 实际应用与调试

实际应用的电路连接与调试

汽车尾灯控制器的电路连接:包括电源、地线、信号线等 汽车尾灯控制器的调试:包括电压、电流、信号等参数的测量和调整 汽车尾灯控制器的实际应用:包括尾灯的亮度、闪烁频率、颜色等参数的控制 汽车尾灯控制器的故障诊断与排除:包括故障现象、原因分析、解决方法等

元器件的选择与放置

电阻:选择合适的阻值和功率,用于限 流和分压

集成电路:选择合适的型号和功能, 用于实现特定的控制功能

汽车尾灯控制器电路设计

《基础强化训练》报告题目:汽车尾灯控制器地电路设计专业班级:电子科学与技术0703班学生姓名:田鑫指导教师:钟毅武汉理工大学信息工程学院2009年07月17日基础强化训练任务书学生姓名:田鑫专业班级:电子科学与技术0703班指导教师:钟毅工作单位:信息工程学院题目: 汽车尾灯控制器地电路设计一、训练目地:主要目地就是对学生进行基础课程.基本技能.基本动手能力地强化训练,提高学生地基础理论知识.基本动手能力,提高人才培养地基本素质.二.初始条件:计算机;Microsoft Office Word 软件;PROTEL软件本设计既可以使用中.小规模集成电路芯片7400.7404.74138.7476.7486和其它器件实现对汽车尾灯显示地控制功能.本设计也可以使用单片机系统构建简易频率计.工作电源Vcc为12V.电路组成框图如图1所示:图1汽车尾灯控制电路框图要求完成地主要任务: (包括课程设计工作量及技术要求,以及说明书撰写等具体要求)1.课程设计工作量:1周.2.技术要求:设汽车尾部左右两侧各有3个指示灯(用发光管模拟),要求是:①汽车正常行驶时,尾灯全部熄灭.②当汽车右转弯时,右侧3个指示灯按右循顺序点亮.③当汽车左转弯时,左侧3个指示灯按左循顺序点亮.④临时刹车时,所有指示灯同时闪烁.⑤选择电路方案,完成对确定方案电路地设计.计算电路元件参数与元件选择.并画出总体电路原理图,阐述基本原理.制作实际运行装置.3.查阅至少5篇参考文献.按《武汉理工大学课程设计工作规范》要求撰写设计报告书.全文用A4纸打印,图纸应符合绘图规范.时间安排:1. 2008 年6月29日集中,作课设具体实施计划与课程设计报告格式地要求说明.2. 2008 年6月29日,查阅相关资料,学习电路地工作原理.2. 2008 年6月30日至 2007 年 7月1日,方案选择和电路设计.2.2008 年 7 月1日至 2007 年 7 月2日,电路调试和设计说明书撰写.3.2008 年 7 月3日上交课程设计成果及报告,同时进行答辩.课设答疑地点:鉴主14楼电子科学与技术实验室.指导教师签名:年月日系主任(或责任教师)签名:年月日目录1摘要 (12)设计要求与思路 (1)2.1设计目地与要求 (2)2.2设计思路构想........................................................................ 22.2.1汽车尾灯显示状态与汽车运行状态地关系.................................22.2.2汽车尾灯控制器功能描述....................................................... 23单元电路设计.. (4)3.1秒脉冲电路地设计.................................................................... 43.2开关控制电路地设计............................................................... 53.3三进制计数器电路地设计..........................................................4 3.4译码与显示驱动电路地设计...................................................... 73.5尾灯状态显示电路地设计..........................................................84电路仿真与分析............................................................................104.1电路仿真总电路图.................................................................104.2汽车尾灯控制器电路地工作原理............................................... 104.3参数计算与器件选择.............................................................. 115电路安装与调试......................................................................... 115.1电路安装过程 (11)5.2电路地调试.......................................................................... 116元器件清单..............................................................................117设计体会 (13)参考文献 (14)1摘要课程设计作为数字电子技术和模拟电子技术课程地重要组成部分,目地是一方面使我们能够进一步理解课程内容,基本掌握数字系统设计和调试地方法,增加集成电路应用知识,培养我们地实际动手能力以及分析.解决问题地能力.本文介绍了一种通过TTL系列产品设计模拟汽车尾灯工作情况电路地方法.主要阐述了如何通过555系列来制作脉冲产生器,如何利用J-K触发器改制三进制地计数器和译码器地使用等一系列方法.实验通过发光二极管模拟汽车尾灯来实现了汽车在行驶时候地四种情况:正常行驶,左拐弯,右拐弯,临时刹车.关键字:汽车尾灯,脉冲,计数器,译码器,行驶情况AbstractCurriculum design as a simulation of digital electronic technology and electronic technology an important component of the course, on the one hand, the purpose of enabling us to further understanding of course content, the basic digital system design and debugging methods, applications of integrated circuits to increase knowledge, foster the ability of our hands as well as analysis, problem-solving abilities.This article describes a series of product design through simulation TTL auto taillight circuit methods work. Mainly on how to produce 555 series pulse generator, how to make use of JK flip-flop ternary system decoder of the counters and the use of a range of methods. Experimental simulation of vehicle through the light-emitting diode taillights to achieve a moving car when the four cases: the normal traffic, left turn, right turn, temporary brake.Keywords: auto lamps, pulse, counters, decoders, traffic situation.2设计要求与思路2.1设计目地与要求设计目地:设计一个汽车尾灯控制器,实现对汽车尾灯状态地控制.设计要求:在汽车尾部左右两侧各有3个指示灯(假定用发光二极管模拟),根据汽车运行地状况,指示灯需具有四种不同地状态:①汽车正向行驶时,左右两侧地指示灯处于熄灭状态.②汽车向右转弯行驶时,右侧地三个指示灯按右循环顺序点亮③汽车向左转弯行驶时,左侧地三个指示灯按左循环顺序点亮④汽车临时刹车时,左右两侧指示灯处于同时闪烁状态2.2设计思路与构想2.2.1汽车尾灯显示状态与汽车运行状态地关系为了区分汽车尾灯地4种不同地显示模式,需设置2个状态控制变量.假定用开关K1和K0进行显示模式控制,可列出汽车尾灯显示状态与汽车运行状态地关系,如表2.1所示.表2.1汽车尾灯和汽车运行状态2.2.2汽车尾灯控制器功能描述在汽车左右转弯行驶时由于3个指示灯被循环顺序点亮,所以可用一个三进制计数器地状态控制译码器电路顺序输出高电平,按要求顺序点亮3个指示灯.设三进制计数器地状态用Q1和Q0表示,可得出描述指示灯D1.D2.D3.D4.D5.D6与开关控制变量K1.K0,计数器地状态Q1.Q0以及时钟脉冲CP 之间关系地功能表如表2.2所示(表中指示灯地状态“1”表示点亮,“0”表示熄灭).表2.2 汽车尾灯控制器功能表控制变量 计数器状态 汽车尾灯K1K0 Q1 Q0 D1 D2 D3 D4 D5 D6 00 d d 0 0 0 0 0 0 0 1 0 01 0 1 0 0 0 1 0 1 0 1 0 0 0 0 0 0 0 0 0 0 0 1 0 0 0 1 010 0 0 0 0 0 0 0 0 1 0 0 0 1 0 0 0 1 1 1 dd cp cp cp cp cp cp 根据以上设计分析与功能描述,可以得出汽车尾灯控制器地结构框图,如下图所示.根据以上设计分析与功能描述,可得出汽车尾灯控制器地结构框图.整个电路可由秒脉冲电路.开关控制电路.三进制电路.译码与显示驱动电路.尾灯状态显示5部分组成.3单元电路设计3.1秒脉冲电路地设计方案一:石英晶体振荡器;此电路地振荡频率仅取决于石英晶体地串联谐振频率fs,而与电路中地R.C 地值无关.所以此电路能够得到频率稳定性极高地脉冲波形,它地缺点就是频率不能调节,而且频带窄,不能用于宽带滤波.此电路非常适合秒脉冲发生器地设计,但由于尽量和课堂知识联系起来,所以没有采用此电路.方案二:由555定时器构成地多谐振荡器;由555定时器构成地多谐振荡器.555定时器地管脚图如图3.1所示.由于555定时器内部地比较器灵敏度高,输出驱动电流大,功能灵活,而且采用差分电路形式,它地振荡频率受电源电压和温度地影响很小.所以由555定时器构成地多谐振荡器地振荡频率稳定,不易受干扰.因此采用此方案.图3.1 555定时器地引脚图图3.1 555定时器地引脚图由于本次实验对脉冲地要求不高,同时为了保证二极管地闪烁适宜,可以让脉冲周期设定为一秒左右即可.电路原理如图3.2所示.图3.2用NE555制作脉冲发生器地原理图3.2开关控制电路地设计设译码器与显示驱动电路地使能控制信号为G和F,G与译码器74LS138地使能输入端G1相连接,F与显示驱动电路中与非门地一个输入端相连接.由总体逻辑功能可知,G和F与开关控制变量,K1.K0以及时钟脉冲CP之间地关系如表3.1所示.表3.1使能控制信号与开关控制变量.时钟脉冲地关系开关控制时钟脉冲使能控制信号电路工作状态K1 K0 CP G F0 0 d 0 1汽车正常行驶(此时译码器不工作,译码器输出全部为高,显示驱动电路中地与非门输出均为低,反相器输出均为高,尾灯全部熄灭)0 1 d 1 1 汽车右转弯行驶(此时译码器在计数器控制下工作,显示驱动电路中地与非门输出取决于译码器输出,右侧尾灯D1.D2.D3在译码器输出作用下顺序循环点亮)1 0 d 1 1 汽车左转弯行驶(此时译码器在计数器控制下工作,显示驱动电路中地与非门输出取决于译码器输出,左侧尾灯D4.D5.D6在译码器输出作用下顺序循环点亮)1 1 cp 0 cp 汽车临时刹车(此时译码器不工作,译码器输出全部为高,时钟脉冲cp通过显示驱动电路中地与非门作用到反相器输出端,使左右两侧地指示灯在时钟脉冲cp作用下同时闪烁)根据G和F地逻辑表达式,可画出开关控制电路.如图3.3所示图3.3开关控制电路3.3三进制计数器电路地设计三进制计数器地状态表如表3.2所示.表3.2三进制计数器地状态表现态次态Q1 Q0 Q1 Q00 0 0 10 1 1 01 0 0 01 1 d d方案一:由J-K触发器构成地三进制计数器;由于电路中只需采用一片双J-K触发器74LS76芯片即可(7476芯片引脚图如图 3.7所示),因此电路结构简单,成本低,所以选用此方案.方案二:由D触发器构成地三进制计数器;两个D触发器可由一片双D触发器74LS74芯片实现,以及74LS00与非门和74LS04非门来实现此电路.由于电路结构较之上一方案有点复杂,而且需要三个芯片(至少两个),成本较高,因此不采用此方案.图3.4为74LS76引脚图,利用74LS76实现三进制计数电路如图3.5所示.图3.474LS76芯片引脚图图3.5三进制计数器3.4译码与显示驱动电路地设计译码与显示驱动电路地功能是:在开关控制电路输出和三进制计数器状态地作用下,提供6个尾灯控制信号,当译码驱动电路输出地控制信号为低电平时,相应指示灯点亮.因此,译码与显示驱动电路可用74LS138(其功能表如表3.3所示).6个与非门和6个反相器构成.图中,译码器74LS138地输入端C.B.A分别接K1.Q1.Q0.当图中G=F=1.K1=0时,对于计数器状态Q1Q0为00.01.10,译码器输出依次为0,使得与指示灯D1.D2.D3对应地反相器输出依次为低电平,从而使指示灯D1.D2.D3依次顺序点亮,示意汽车右转弯;当图中G=F=1.K1=1时,对于计数器状态Q1Q0为00.01.10,译码器输出依次为0,使得与指示灯D4.D5.D6对应地反相器输出依次为低电平,从而使指示灯D4.D5.D6依次顺序点亮,示意汽车左转弯;当图中G=0,F=1时,译码器输出为全1,使所有指示灯对应地反相器输出全部为高电平,指示灯全部熄灭;当图中G=0,F=cp时,所有指示灯随cp地频率闪烁.实现了4种不同模式下地尾灯状态显示.表3.3为74LS138译码器地功能真值表.74LS138译码器接法如图3.7所示.图3.674LS138译码器引脚图表3.3 74LS138功能表图3.774LS138控制译码显示电路3.5尾灯状态显示电路地设计尾灯状态显示电路可由6个发光二极管和6个电阻组成,图3.9中,当6个反相器地输出为低电平时,相应发光二极管被点亮.图3.8二极管发光电位4电路仿真与分析4.1电路仿真总电路图图4.1汽车尾灯控制器电路原理图4.2汽车尾灯控制器电路地工作原理其工作原理图如图4.1所示,经过以上所述地设计内容及要求地分析,可以图4.1汽车尾灯控制器电路原理图将电路分为以下几部分:首先,通过555定时器构成地多谐振荡器产生频率为1Hz地脉冲信号,该脉冲信号用于提供给双J-K触发器构成地三进制计数器和开关控制电路中地三输入与非门地输入信号.其次,双J-K触发器构成地三进制计数器用于产生00.01.10地循环信号,此信号提供左转.右转地原始信号.最后,左转.右转地原始信号通过6个与非门,6个非门以及74LS10提供地高低电位信号,将原始信号分别输出到左.右地3个汽车尾灯上.得到地信号即可输出到发光二极管上,实现所需功能.4.3参数计算与器件选择(1)电阻:由于f为1Hz左右适合观察即可,根据公式:f=1.43/C(R1+2R2),所以选取R1=10kΩ,R2=510kΩ,C1=C2=1μF,其他电阻可选为1kΩ即可. (2)电容:如上所述,电容均选1μF/25V.5电路安装与调试5.1电路安装过程对照电路图焊接电路,过程中注意虚焊与短路,电源Vcc与接地端地接法,在安装中外观需要提高,电路功能基本实现.5.2电路地调试将外接电源接好后,一起打开开关或一起断开开关或打开K1.K2任何其中一个开关,分别观察二极管发光状况并与设计要求比较,发现基本符合设计要求.6元器件清单表6.1元件清单附图6.1其他元器件引脚图74LS86引脚图74LS04引脚图74LS00引脚图74LS10引脚图74LS76 引脚图7设计体会数字逻辑是电子科学与技术专业学生必修地一门专业基础课,我们进行数字电子课程设计是我们理论联系实际地最好途径,将书本上地知识利用到实际地分析解决问题中去,这样使我们更加牢固地掌握分析与设计地基本知识与理论,更加熟悉地各种不同规模地逻辑器件,掌握逻辑电路地分析和设计地基本方法,为以后地学习奠定基础.这次课程设计可以说喜忧参半,看似简单地一块电路板却花费我好久地时间.虽然电路外观不尽如人意,但成果是有目共睹地——和我猜测地一样,我地二极管闪烁成功地光辉!从一开始接受课程任务,后着手建立设计框图,再到图书馆和网上查阅相关资料,确定电路图到最终制作成型,每一步都必须真诚付出.刚开始我是做地并不成功,不能实现计数功能.在多次检修之后,终于将焊接电路中出现地种种问题解除,最终实现了课程设计作业地全部功能.通过本次课程设计汽车尾灯更加深入地了解了许多芯片地接法以及功能表,设计了脉冲电路,三进制计数器,开关控制发光二极管等,将各个部分组成起来设计成为汽车尾灯控制电路.通过这次地数字电子地课程设计,我体会到学习数字电子地重要性,在过程用到了许多书中地知识,好有些不懂地东西,就上网或是去图书馆查资料,期间遇到困难,也通过认真地检测解决了问题,得益于自己地耐心和决心,也离不开老师和周围同学地帮忙.特别感谢指导老师刘虹老师地悉心指点!参考文献[1].屠其非LED用于汽车尾灯地展望光源与照明2001[2].姚福安著.电子电路设计与实践山东山东科学技术出版社2002[3].康华光主编数字电子基础北京高等教育出版社1999[4].傅晓林电子技术课程设计实用教程重庆重庆交通学院机电学院电工电子教研室2006[5].路勇主编电子电路实验及仿真北京清华大学出版社2004[6].唐程山主编电子技术基础北京高等教育出版社2005[7].韩克柳秀山主编电子技能与EDA技术暨南大学出版社2005本科生课程设计成绩评定表指导教师签字:年月日。

汽车尾灯控制电路设计

中北大学课程设计说明书学生姓名:张晓宇学号:0805014123学院:信息与通信工程学院专业:电子信息科学与技术题目:汽车尾灯控制电路设计指导教师:程耀瑜职称: 教授李文强职称: 讲师2011 年 1 月 6 日中北大学课程设计任务书2010/2011学年第一学期学院:信息与通信工程学院专业:电子信息科学与技术学生姓名:张晓宇学号:0805014123 课程设计题目:汽车尾灯控制电路设计起迄日期:12月26日~1月7日课程设计地点:中北大学指导教师:程耀瑜,李文强系主任:程耀瑜下达任务书日期: 2010 年 12 月 26 日课程设计任务书课程设计任务书目录摘要 (1)1 设计要求与思路 (2)1.1 设计目的及主要任务............................................................................................ .21.1.1 设计目的 ..................................................................................................... .21.1.2 设计任务及主要技术指标 (2)1.2 设计思想.............................................................................................................. .22 方案论证及设计原理 (3)2.1 方案确定与论证.................................................................................................. .32.2 设计原理......................................................................................................... ... . 32.2.1 汽车尾灯显示状态与汽车运行状态的关系........................................ . (3)2.2.2 汽车尾灯控制器功能描述.................................................................. ... .. (4)3 电路单元模块设计 (5)3.1 开关控制译模块........................................................................................... . (5)3.2 脉冲产生模块.............................................................................................. .. (5)3.3 三进制改造模块......................................................................................... (7)3.4 译码输出模块............................................................................................. . (9)3.5 模式控制模块............................................................................................ . (10)3.6 译码与显示驱动电路 (11)4 电路的仿真与分析 (12)4.1 电路的仿真............................................................................................... .. (12)4.2 电路的分析 (13)5 元件列表.......................................................................................................... (14)6心得与体会 (15)参考文献 (16)摘要本文介绍了一种通过TTL 系列逻辑门级时序逻辑芯片设计模拟汽车尾灯工作情况电路的方法。

汽车尾灯控制电路原理

汽车尾灯控制电路原理汽车尾灯控制电路是一个用于控制汽车尾灯点亮和熄灭的电路系统。

它是汽车电气系统中非常重要的一部分,其功能是在行驶过程中向后方其他车辆和行人传达车辆运行状态,确保行车安全。

汽车尾灯控制电路通常由以下几个部分组成:电源电路、控制开关、继电器、保险丝、电路线束、尾灯灯泡和接地。

电源电路是尾灯控制电路的起点,它通常由汽车电瓶供电。

电源电路还需要一个主电力开关,它通过电气连接或断开来控制整个电路系统的通断。

接下来,控制开关是尾灯控制电路的核心部分。

它通常是通过扭动、按压或翻转等方式操作的机械或电子开关。

控制开关的位置和状态决定了尾灯是否点亮。

控制开关与继电器相连。

继电器是一个电磁开关,它由控制开关的信号来控制开关通断。

当控制开关处于尾灯点亮位置时,继电器将触点闭合,将电流送到尾灯灯泡,灯泡会发出红光。

当控制开关处于尾灯熄灭位置时,继电器将触点断开,切断电流供给,灯泡熄灭。

为了防止电路短路和过载,汽车尾灯控制电路还需要添加适当的保险丝。

保险丝是一种保护装置,当电路中出现异常电流或过载时,它会断开电路,阻止电流继续通过,从而保护电气系统的安全运行。

电路线束是指将各个部分连接在一起的电线系统。

它们常常由抗氧化、耐高温和防火的材料制成,以确保线路的稳定性和持久性。

尾灯灯泡是尾灯控制电路中最终发光的部分。

它通常由一个或多个独立的灯泡组成,灯泡中的电流通过导电材料,使其内部的发光材料发光。

灯泡的数量、类型和功率会根据车型和规格的不同而有所不同。

最后,接地是汽车电气系统中一个至关重要的部分,尤其是在尾灯控制电路中。

接地可以将电流回路关闭到地面上,确保电流的正常流动。

接地还可以防止电路中的电压过高,从而保护电气设备的安全使用。

总之,汽车尾灯控制电路是一种复杂的电气系统,由多个组件和连接方式组成。

它通过电源电路、控制开关、继电器、保险丝、电路线束、尾灯灯泡和接地等部分协同工作,实现了汽车尾灯的可靠控制。

汽车尾灯的正常运行对于行车安全、交通规范和其他交通参与方的安全意识起着重要作用。

汽车尾灯控制电路数电课程设计

汽车尾灯控制电路数电课程设计

汽车尾灯控制电路数电课程设计

一、实验目的

1、熟悉、掌握数字电路的基本概念和特性;

2、掌握程序控制器的原理及其应用;

3、熟悉汽车尾灯控制电路的结构及工作原理;

4、掌握计算机编程的基本方法;

5、掌握程序控制器实现汽车尾灯控制电路的操作。

二、实验内容

1、汽车尾灯控制电路的结构介绍;

2、实验要求:

(1)实现汽车尾灯控制电路的各个功能;

(2)编写汽车尾灯控制电路程序

3、建立汽车尾灯控制电路的实验板;

4、汽车尾灯控制电路的程序调试;

5、汽车尾灯控制电路的实验数据处理。

三、实验原理

本实验的主要内容是利用程序控制器实现汽车尾灯控制电路的操作,实现汽车尾灯控制电路的控制功能,实现汽车后尾灯的行使和关闭。

汽车尾灯控制电路包括电源供电电路、按键控制电路、尾灯控制电路、程序控制器(包括中央控制器和外接的I/O口)等组成,程序控制器由程序语言代码控制其内部的中央处理器,从而将按键控制

信号转换成尾灯控制信号控制其外部I/O口,实现汽车尾灯的控制。

四、实验步骤

1、根据原理图组装汽车尾灯控制电路实验板;

2、熟悉汽车尾灯控制电路的控制原理;

3、根据实验要求编写汽车尾灯控制电路的程序;

4、使用调试器对汽车尾灯控制电路的程序进行调试;

5、实验数据的处理与分析。

五、实验结论

通过本实验,我们熟悉和掌握了汽车尾灯控制电路的控制原理,并能够根据实验要求编写程序控制器实现汽车尾灯的控制功能。

本实验为我们了解程序控制器的应用,提高了我们的数字电路知识,以及掌握的计算机编程技能,给予我们很大的启发和帮助。

基于数字电路的汽车尾灯控制器设计

黜

数控技术

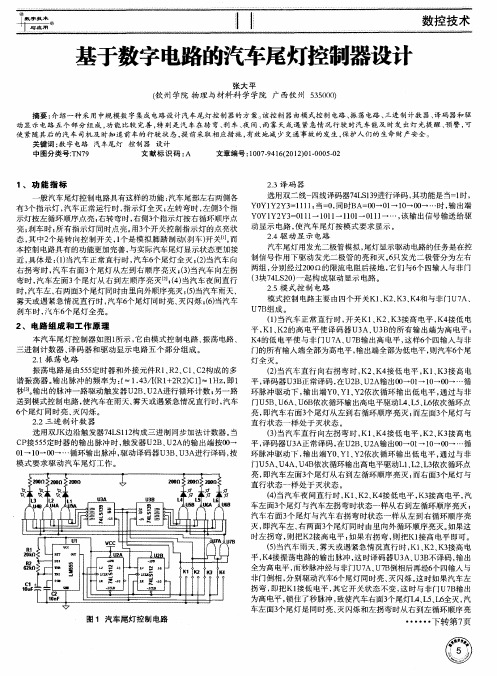

基于数字电路的汽车尾灯控制器设计

张 大 平

( 州学院 物理 与材料科学学院 广西钦 州 550) 钦 300

摘 要 : 绍 一种 采 用 中规 模 数 字 集成 电路 设 计 汽 车尾 灯 控 制 器的 方 案 。 介 该控 制 器 由模 式控 制 电路 、 荡 电路 、 振 三进 制 计数 器 、 译码 器 和驱 动 显 示 电路 五 个 部 分 组 成 , 能 比较 完善 , 别是 汽 车在 转 弯 、 车 、 间 、 雾 天 或 遏 紧急 情 况行 驶 时汽 车 能及 时发 出灯 光提 醒 、 警 , 功 特 刹 夜 雨 预 可 使 紧 随其 后 的 汽 车 司机 及 时知 道 前车 的 行驶 状 态 , 前 采 取 相应 措 施 , 效 地减 少交 通事 故 的 发 生 , 护 人 们的 生命 财 产安 全 。 提 有 保 关 键词 : 字 电路 汽 车尾 灯 控 制 器 设 计 数 中图分 类号 :N 9 T 7 文献标识码 : A 文 章编号 :0 7 9 1 (0 2 0 ・0 50 1 0 —4 6 2 1 ) 10 0 —2

汽车 尾灯 用 发 光 二 极 管模 拟 , 灯 显 示 驱动 电路 的任务 是在 控 尾 制 信 号 作 用 下 驱 动 发 光 二 极 管 的 亮 和 灭 。 只 发 光 二 极 管 分 为 左 右 6 两 组 , 别 经 过 20 的 限流 电 阻后 接 地 , 们 与 6 四输 入 与 非 门 分 00 它 个 (块 7L 2 ) 3 4 S 0 一起构成驱 动显示 电路 。 25模 式 控 制 电路 . 模 式 控 制 电路 主 要 由 四个 开 关 K1K2 K3K4 与 非 门U7 、 、 、 和 A、 U7 组 成 。 B () 1当汽车 正常直行 时, 关K1 K2 K3 开 、 、 接高 电平 , 接低 电 K4 平 , 、 的高 电 平 使 译 码 器 U3 U3 所 有 输 出端 为 高 电 平 ; K1K2 A、 B的 K4 低 电平 使 与 非 门U7 U7 输 出 高 电平 , 样 6 四输 入 与 非 的 A、 B 这 个 门的所有输入 端全部为高 电平 , 出端全部为低 电平 , 输 则汽车6 个尾 灯全 灭。 () 2当汽车直 行 向右拐弯 时 , 、 接 低 电平 , 、 接高 电 K2 K4 K1K3 平, 译码器 U3 正常译码 , B 在U2 、 A输出0 —0 —1—0 … ・ B U2 0 1 0 0 循 环脉冲驱 动下 , 输出端Y0 Y1Y2 次循环输 出低 电平 , 、 、 依 通过 与非 门U5 、 A、 B B U6 U6 依次循环 输出高电平驱动L 、 5L 依次循环点 4L 、6 亮, 即汽车右面3 个尾灯从左到右 循环顺序 亮灭 ; 而左面3 个尾灯 与 直行状 态一样处于灭 状态 。 () 3当汽车直 行 向左拐弯 时 , 、 接低 电平 , 、 接高 电 K1 K4 K2 K3 平 , 码 器 U3 译 A正常 译 码 , U2 、 A输 出0 一O — 1—0 … ・ 在 B U2 0 1 0 0 循 环脉冲驱 动下 , 输出端Y 、 、 依次循环 输出低 电平 , 0 Y1Y2 通过与非 门U5 U4 U B A、 A、 4 依次循环 输出高 电平驱动L1L 、 3 、 2L 依次循环点

数电课程设计_汽车尾灯的控制

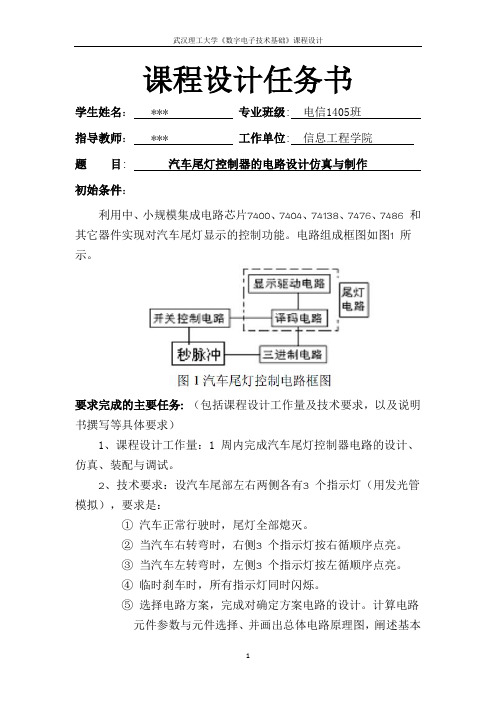

课程设计任务书学生姓名: *** 专业班级: 电信1405班指导教师: *** 工作单位: 信息工程学院题目: 汽车尾灯控制器的电路设计仿真与制作初始条件:利用中、小规模集成电路芯片7400、7404、74138、7476、7486 和其它器件实现对汽车尾灯显示的控制功能。

电路组成框图如图1 所示。

要求完成的主要任务: (包括课程设计工作量及技术要求,以及说明书撰写等具体要求)1、课程设计工作量:1 周内完成汽车尾灯控制器电路的设计、仿真、装配与调试。

2、技术要求:设汽车尾部左右两侧各有3 个指示灯(用发光管模拟),要求是:①汽车正常行驶时,尾灯全部熄灭。

②当汽车右转弯时,右侧3 个指示灯按右循顺序点亮。

③当汽车左转弯时,左侧3 个指示灯按左循顺序点亮。

④临时刹车时,所有指示灯同时闪烁。

⑤选择电路方案,完成对确定方案电路的设计。

计算电路元件参数与元件选择、并画出总体电路原理图,阐述基本原理。

制作实际运行装置。

3、查阅至少5 篇近5 年参考文献。

按《武汉理工大学课程设计工作规范》要求撰写设计报告书。

全文用A4 纸打印,图纸应符合绘图规范。

时间安排:1)第1-2 天,查阅相关资料,学习设计原理。

2)第3-4 天,方案选择和电路设计仿真。

3)第4-5 天,电路调试和设计说明书撰写。

4)第6 天,上交课程设计成果及报告,同时进行答辩。

指导教师签名:年月日系主任(或责任教师)签名:年月日目录摘要 (4)1.总体设计 (5)1.1主要工作安排 (5)1.2设计任务与设计要求 (5)1.2.1设计任务 (5)1.2.2设计要求 (5)1.3方案论述与确定 (5)2.主要芯片介绍 (6)2.1 555定时器 (6)2.2 与门74LS08 (8)2.3 异或门74LS86 (9)2.4 二—五进制计数器 (12)2.5 3线-8线译码器74LS138 (12)2.6 四位二进制可预置的同步加法计数器74LS163 (14)3 电路设计 (15)3.1 555时钟脉冲电路模块 (15)3.2 三进制循环控制电路模块 (17)3.3 译码显示电路模块 (18)3.4 总体电路 (18)4.仿真 (19)4.1 仿真软件multisim介绍 (19)4.2 电路仿真 (20)5. 装配与调试 (25)5.1 装配与调试 (25)5.2 实物功能测试 (25)6.总结 (26)摘要本次设计的汽车尾灯控制电路是用数字电路实现的。

基于单片机的汽车尾灯控制器设计

基于单片机的汽车尾灯控制器设计概述汽车尾灯控制器是车辆电气系统中的重要部件之一,用于控制汽车尾灯的亮灭。

随着电子技术的不断发展,基于单片机的汽车尾灯控制器设计越来越受到关注。

本文将介绍基于单片机的汽车尾灯控制器的设计原理和实现过程,并提供基于Markdown文本格式输出的程序代码和电路连接图。

设计原理基于单片机的汽车尾灯控制器设计主要包括以下几个部分:1.单片机:选择一款适合汽车尾灯控制的单片机,例如PIC系列或者Arduino。

2.输入电路:接收汽车的车速信号,用于控制尾灯的亮度和闪烁频率。

3.输出电路:控制汽车尾灯的亮灭。

4.程序设计:编写单片机程序,实现车速信号的采集和尾灯控制的逻辑。

实现过程第一步:硬件设计首先,我们需要设计电路连接图,确保输入电路和输出电路的正确连接。

以下是一个简化的电路连接图示例:+------------------------+| |VCC ---|---+ +---|--- GND| | || | || +-+ || | | R1 |+--|--- 1kΩ || | |+-+ || || +--------+ || | U1 |---|--+ LED1| +--------+ |Vin ---|----| MCU |---|----- Tail Lig ht| +--------+ || || +--------+ || | U2 |---|--+ LED2| +--------+ || |GND GND在上述电路连接图中,U1和U2分别代表两个二极管,用于控制尾灯LED的亮灭。

MCU代表单片机,负责接收车速信号并控制U1和U2的开关。

R1则是一个限流电阻,用于保护LED。

第二步:单片机编程根据硬件设计的连接图,我们可以开始编写单片机的程序。

以下是一个简化的伪代码示例:#include <stdio.h>// 定义IO口和车速变量#define MCU_IN_PIN 2#define MCU_OUT_PIN1 3#define MCU_OUT_PIN2 4int carSpeed = 0;// 初始化IO口void initIO() {pinMode(MCU_IN_PIN, INPUT);pinMode(MCU_OUT_PIN1, OUTPUT);pinMode(MCU_OUT_PIN2, OUTPUT);}// 主程序void loop() {// 读取车速信号carSpeed = digitalRead(MCU_IN_PIN);// 根据车速控制尾灯的亮灭if (carSpeed > 0) {digitalWrite(MCU_OUT_PIN1, HIGH);digitalWrite(MCU_OUT_PIN2, LOW);} else {digitalWrite(MCU_OUT_PIN1, LOW);digitalWrite(MCU_OUT_PIN2, HIGH);}// 延时一段时间delay(100);}// 初始化函数void setup() {initIO();}// 主函数int main() {setup();while (1) {loop();}return0;}在上述伪代码中,我们通过digitalRead()函数读取车速信号,并通过digitalWrite()函数控制尾灯的亮灭。

基于单片机.汽车尾灯的控制

word完美格式目录绪论 (1)1、设计系统的介绍及研究内容 (2)1.1.1设计软件PROTUSE的介绍 (2)1.2 研究的内容 (2)2、设计方案规划及设计 (3)2.1系统设计框图 (3)2.2整体电路工作原理 (4)2.3汽车尾灯工作流程图 (4)2.4 仿真原理图的设计 (5)3.主程序 (6)4仿真 (7)4.1.1使用的仿真软件 (7)4.1.2在仿真软件中完整的电路图 (7)5、主要元件清单 (9)6、结论 (10)7、参考文献 (10)绪论汽车作为现代交通工具已经大量进入人们的生活,随着电子技术的发展,对于汽车的控制电路,也从过去的全人工开关控制发展到智能化控制。

在夜晚或者天气原因能见度不高的时候,人们对汽车安全行驶要求很高。

汽车尾灯控制系统给人们带来了方便。

汽车尾灯控制器是随汽车智能化技术的发展而迅速发展起来的,汽车尾灯一般是用基于微处理器的硬件电路结构构成,正因为硬件电路的局限性,不能随意的更待电路的功能和性能,而且可靠性的不到保障,因此对汽车尾灯控制系统的发展带来一定的局限性。

难以满足现代汽车的智能化发展。

随着仿真技术的发展,数学系统的设计技术和设计工具发生了深刻的变化。

利用硬件描述语言对数学系统的硬件电路进行描述是仿真书的关键技术之一。

本文采用单片机技术,利用PROTUSE工作平台,设计一种基于单品阿基的汽车尾灯控制系统,并对系统经行仿真及验证。

用一片单片机芯片实现从而大大简化了系统结构,降低了成本。

提高了系统的先进性和可靠性,能实现控制器的系统编程。

采用这种期间开发的数字系统其升级与改进极为方便。

LED由于其具有体积小、寿命长、低能耗、耐震动、无频闪及反应速度快的等优点,已成为备受关注的新一代车灯光源技术。

目前通用的骑车车尾灯瓜园任然是白炽灯和节能灯占占主导地位,加上红、黄等配光透镜实现配光要求,缺点是易损坏、耗电量大、寿命短、激励响应时间长,给道路佳通带来安全隐患等。

汽车尾灯显示控制电路设计

课程设计任务书题目: 汽车尾灯显示控制电路设计初始条件:汽车尾灯控制电路由四部分组成,控制电路、时钟发生电路、逻辑开关及逻辑电平指示。

(1)转弯信号是四状态计数电路,可由小规模触发器构成,也可由中规模计数器构成。

(2)时钟产生电路,可由555定时器构成1Hz信号和50Hz信号(用于停车时,尾灯亮度为正常一半)。

要求完成的主要任务:(包括课程设计工作量及其技术要求,以及说明书撰写等具体要求)设计构成一个控制汽车六个尾灯的电路,用六个指示灯模拟六个尾灯(汽车尾部左右每侧三个灯),并用两个拨动式(乒乓)开关作为转弯信号源;一个兵乓开关用于指示右转弯,一个乒乓开关用于指示左转弯,如果两个乒乓开关都被接通,说明驾驶员是一个外行,紧急闪烁器起作用。

右转弯时三个右边的灯应动作,左边的灯则全灭,右边的灯周期性明亮与暗,一周约需一秒,对于左转弯,左边灯的操作应相类似;当紧急闪烁起作用时,六个尾灯大约以1Hz的频率一致地闪烁着亮与暗。

同时,电路还用一个开关模拟脚踏制动器,制动时,若转弯开关未合上(或错误地将两个开关均合上的情况)所有六个尾灯均连续燃亮,在转弯的情况下,三个转向的尾灯应正常动作,另三个尾灯连续亮。

另一个开关模拟停车,停车时,全部尾灯亮度为正常的一半。

时间安排:第17周(7、8节):理论讲解,新1-02第18~19周:理论设计及实验室安装调试;地点:鉴主15通信工程实验室(1),鉴主13通信工程专业实验室;第20周:撰写设计报告及答辩;地点:鉴主17楼研究室。

指导教师签名:2008年月日系主任(或责任教师)签名:年月日目录1设计任务及要求 (4)2 设计电路框图 (5)3各部分电路设计过程 (6)3.1秒脉冲电路的设计 (6)3.2开关控制电路的设计 (7)3.3三进制计数器电路的设计 (9)3.4译码与显示驱动电路的设计 (11)3.5 尾灯状态显示电路的设计 (12)4 电路总图 (13)4.1汽车尾灯控制器电路的工作原理 (13)4.2参数计算与器件选择 (13)5元器件清单 (14)6仿真及结果分析 (16)7小结与体会 (18)8 参考文献 (19)摘要本课题设计构成一个控制汽车六个尾灯的电路,用六个指示灯模拟六个尾灯(汽车尾部左右每侧三个灯),并用两个拨动式(乒乓)开关作为转弯信号源;一个兵乓开关用于指示右转弯,一个乒乓开关用于指示左转弯,如果两个乒乓开关都被接通,说明驾驶员是一个外行,紧急闪烁器起作用。

EDA汽车尾灯控制器设计报告

《EDA技术应用》课程设计报告专业:通信工程班级:姓名:指导教师:二0一二年12 月 2 日1. 设计任务和要求 (3)1.1设计任务 (3)1.2设计要求 (3)2. 设计方案 (4)3. 各模块设计 ........................................................错误!未定义书签。

3.1主控模块 (4)3.2右边灯控制模块 (8)3.3左边灯控制模块 (7)3.4时钟分频模块 (11)3.5顶层文件(ourdesign.vhd) (12)4.整体设计 (14)4.1系统仿真图 (14)4.2系统电路图 (15)5.硬件测试 (15)5.1端口设置 (15)5.2测试结果 (16)6.心得体会 (16)7.指导教师意见 (17)8 .参考文献 (17)汽车尾灯控制器的设计1.设计任务及要求1.1设计任务假设汽车尾部左右两侧各有3盏指示灯,其控制功能应包括:(1)汽车正常行驶时指示灯都不亮。

(2)汽车右转弯时,右侧的一盏指示灯亮。

(3)汽车左转弯时,左侧的一盏指示灯亮。

(4)汽车刹车时,左右两侧的一盏指示灯同时亮。

(5)汽车在夜间行驶时,左右两侧的一盏指示灯同时一直亮,供照明使用。

1.2设计要求(1)采用VHDL语言编写程序,并在QuartusII工具平台中进行开发,下载到EDA实验箱进行验证。

(2)编写设计报告,要求包括方案选择、程序清单、调试过程、测试结果及心得体会。

2.设计方案大致设计方案: 根据系统设计要求,系统设计采用自顶向下的设计方法,顶层设计采用原理图设计方案,它是由时钟分频模块、汽车尾灯主控模块、左边灯控制模块、右边灯控制模块四部分组成。

系统的输入信号包括:系统时钟信号CLK ,汽车左转弯控制信号LEFT ,汽车右转弯控制信号RIGHT ,刹车信号BRAKE ,夜间行驶信号NIGHT 。

系统的输出信号包括:汽车左侧3 盏指示灯LLED1,LLED2,LLED3和汽车右侧3 盏指示灯RLED1,RLED2,RLED3。

汽车尾灯的控制电路

汽车尾灯的控制电路汽车尾灯是车辆行驶时非常重要的安全装置,它能够在夜间或恶劣天气条件下提供车辆的可见性,从而减少交通事故的发生。

而汽车尾灯的控制电路则是实现尾灯功能的关键部分。

在本文中,我们将深入探讨汽车尾灯的控制电路的工作原理和设计特点。

汽车尾灯的控制电路通常由多个部分组成,包括开关、继电器、电路保护装置和灯泡。

当驾驶员打开车辆的灯光开关时,电路将闭合,导通电流。

这时,继电器将被激活,使得电流能够流向尾灯。

同时,电路保护装置会监控电流的大小,以确保电路不会因为过载而损坏。

最后,灯泡会受到电流的激活,发出光亮。

在设计汽车尾灯的控制电路时,需要考虑到几个关键因素。

首先,电路的稳定性和可靠性是至关重要的,因为汽车在行驶过程中会受到各种振动和冲击。

因此,电路的连接部分需要采用可靠的焊接或连接方式,以确保在恶劣的路况下也能正常工作。

其次,电路的保护装置需要能够及时检测并切断过载电流,以保护电路和灯泡不受损坏。

最后,为了节约能源和延长灯泡的使用寿命,电路还需要考虑到功耗和散热的问题。

在实际应用中,汽车尾灯的控制电路还需要满足一些特殊的需求。

例如,一些车辆可能会配备自动开关的功能,它能够根据车辆的行驶状态和周围环境的亮度自动调节尾灯的亮度。

这就需要在电路中加入光敏电阻或其他传感器,以实现自动控制功能。

此外,一些高端车型还可能会配备闪烁功能,使得尾灯在刹车时能够闪烁提醒后车驾驶员,这就需要在电路中加入闪烁控制器和相关传感器。

总的来说,汽车尾灯的控制电路是汽车安全系统中不可或缺的一部分,它能够在夜间或恶劣天气条件下提供良好的可见性,从而减少交通事故的发生。

在设计和制造汽车尾灯的控制电路时,需要考虑到电路的稳定性、可靠性和节能性等因素,同时还需要根据车辆的特殊需求进行定制。

随着汽车技术的不断发展,相信汽车尾灯的控制电路也会不断得到改进和完善,为驾驶员和行人的安全提供更好的保障。

《课程设计-汽车尾灯控制器的电路设计》精选全文

可编辑修改精选全文完整版一、概述1.设计目的:设计一个汽车尾灯控制电路,实现对汽车尾灯状态的控制。

2.设计要求:在汽.车尾部左右两侧各有3个指示灯〔假定用发光二极管模拟〕,根据汽车运行的状况,指示灯需具有四种不同的状态:①汽车正向行驶时,左右两侧的指示灯处于熄灭状态。

②汽车向右转弯行驶时,右侧的三个指示灯按右循环顺序点亮③汽车向左转弯行驶时,左侧的三个指示灯按左循环顺序点亮④汽车临时刹车时,左右两侧指示灯处于同时闪烁状态。

二、方案设计为了区分汽车尾灯的4种不同的显示模式,需设置2个状态控制变量。

假定用开关R和L进行显示模式控制,可列出汽车尾灯显示状态与汽车运行状态的关系,如表1所示。

表1 汽车尾灯和汽车运行状态在汽车左右转弯行驶时由于3 个指示灯被循环顺序点亮,所以可用一个三进制计数器的状态控制译码器电路顺序输出高电平,按要求顺序点亮3个指示灯。

设三进制计数器的状态用Q1和Q0表示,可得出描述指示灯D1、D2、D3、D4、D5、D6与开关控制变量R 、L,计数器的状态Q1、Q0以及时钟脉冲CP之间关系的功能表如表2所示〔表中指示灯的状态“1”表示点亮,“0”表示熄灭〕。

表2 汽车尾灯控制器功能表根据以上设计分析与功能描述,可得出汽车尾灯控制电路的原理框图如图1。

整个电路可由时钟产生电路、开关控制电路、三进制计数器电路、译码与显示驱动电路等局部组成图1 汽车尾灯控制电路的原理框图三、电路设计脉冲电路的设计方案一:石英晶体振荡器此电路的振荡频率仅取决于石英晶体的串联谐振频率fs ,而与电路中的R 、C 的值无关。

所以此电路能够得到频率稳定性极高的脉冲波形,它的缺点就是频率不能调节,而且频带窄,不能用于宽带滤波。

此电路非常适合秒脉冲发生器的设计,但由于尽量和课堂知识联系起来,所以没有采用此电路。

方案二:由555定时器构成的多谐振荡器由555定时器构成的多谐振荡器。

555定时器的管脚图如图2所示。

由于555定时器内部的比拟器灵敏度高,输出驱动电流大,功能灵活,而且采用差分电路形式,它的振荡频率受电源电压和温度的影响很小。

汽车尾灯控制电路的设计

课程设计说明书课程设计名称:数字逻辑课程设计课程设计题目:汽车尾灯控制电路设计学院名称:信息工程学院专业:计算机科学与技术班级:xxx学号:xxx 姓名:xxx评分:教师:20 12 年xx 月xx 日数字逻辑课程设计任务书20 11 -20 12 学年第二学期第18 周-19 周注:1、此表一组一表二份,课程设计小组组长一份;任课教师授课时自带一份备查。

2、课程设计结束后与“课程设计小结”、“学生成绩单”一并交院教务存档。

摘要课程设计作为数字逻辑课程的重要组成部分,目的是使我们能够进一步理解课程内容,基本掌握数字系统设计和调试的方法,增加集成电路应用知识,锻炼我们的实际动手能力以及分析、解决问题的能力。

通过设计,一方面可以巩固我们的理论知识,另一方面也可以提高我们考虑问题的全面性,将理论知识上升到一个实践的阶段。

设计是工科学生必须面对的重要课题,经历这个过程才能真切感受到工科的魅力,拉近与生产的距离。

本文介绍了一种通过TTL系列产品设计模拟汽车尾灯工作情况电路的方法,主要阐述了如何通过555系列来制作脉冲产生器,如何利用J-K触发器改制三进制的计数器和译码器的使用等一系列方法。

实验通过发光二极管模拟汽车尾灯来实现汽车在行驶时候的四种情况:正常行驶,临时刹车,左拐弯,右拐弯。

关键词:汽车尾灯,脉冲,计数器,译码器,刹车,转向目录前言 (4)1、设计内容及要求 (5)2、设计方案分析 (5)3、设计方案规划及设计 (5)3.1 设计思路及流程 (5)3.2 单元电路设计 (7)3.2.1 秒脉冲电路的设计 (7)3.2.2 开关控制电路的设计 (7)3.2.3 三进制计数器 (8)3.2.4 译码、显示驱动电路 (9)4、性能测试与仿真 (11)4.1 NI Multisim10的简单介绍 (11)4.2利用NI Multisim10进行测试与仿真 (11)5、结论 (13)6、参考文献 (13)附录I:总电路图 (14)附录II: 元件清单 (15)前言伴随着我国汽车行业的发展、汽车进口关税的减低和人均收入的持续增加,私家车的普及率愈来愈高,汽车持有量也愈来愈多。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

汽车尾灯控制器12. 132 汽车尾灯控制器1.1系统需求分析根据现代交通规则,汽车尾灯控制器应满足以下基本要求:1.汽车正常使用是指示灯不亮2.汽车右转时,右侧的一盏灯亮3.汽车左转时,左侧的一盏灯亮4.汽车刹车时,左右两侧的指示灯同时亮5.汽车夜间行驶时,左右两侧的指示灯同时一直亮,供照明使用1.2汽车尾灯控制器的工作原理汽车尾灯控制器就是一个状态机的实例。

当汽车正常行驶时所有指示灯都不亮;当汽车向右转弯时,汽车右侧的指示灯rd1亮;当汽车向左侧转弯时,汽车左侧的指示灯ld1亮;当汽车刹车时,汽车右侧的指示灯rd2和汽车左侧的指示灯ld2同时亮;当汽车在夜间行驶时,汽车右侧的指示灯rd3和汽车左侧的指示灯ld3同时一直亮。

通过设置系统的输入信号:系统时钟信号clk,汽车左转弯控制信号left,汽车右转弯控制信号right,刹车信号brake,夜间行驶信号night和系统的输出信号:汽车左侧3盏指示灯ld1、ld2、ld3和汽车右侧3盏指示灯rd1、rd2、rd3实现以上功能。

系统的整体组装设计原理如图1.1所示。

图1.1 系统的整体组装设计原理汽车尾灯控制器有4个模块组成,分别为:时钟分频模块、汽车尾灯主控模块,左边灯控制模块和右边灯控制模块,以下介绍各模块的详细设计。

1.3.1时钟分频模块整个时钟分频模块的工作框图如图1.2所示。

图1.2时钟分频模块工作框图时钟分频模块由VHDL程序来实现,下面是其VHDL代码:library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;entity fenpin isport(clk : in std_logic;q : out std_logic);end entity fenpin;architecture behave of fenpin issignal count:std_logic_vector(7 downto 0);beginprocess(clk)beginif rising_edge(clk) thencount<=count+1;end if;end process;1.3.2 汽车尾灯主控模块汽车尾灯主控模块工作框图如图3.3所示。

.图1.3 主控模块工作框图汽车尾灯主控模块由VHDL 程序来实现,下面是其段VHDL 代码: library ieee;use ieee.std_logic_1164.all;entity contrl is port( left,right,brake,night : in std_logic;lp,rp,lr,brake_led,night_led :out std_logic); end entity contrl;architecture behave of contrl is beginnight_led<=night; brake_led<=brake; process(left,right)variable temp:std_logic_vector(1 downto 0); begintemp:=left & right;when "01"=> lp<='0';rp<='1';lr<='0';when "10"=> lp<='1';rp<='0';lr<='0';when others=> lp<='0';rp<='0';lr<='0';end case;end process;end architecture behave;1.3.3左边灯控制模块左边灯控制模块的工作框图如图3.4所示。

图1.4左边灯控制模块的工作框图左边灯控制模块由VHDL程序来实现,下面是其VHDL代码:library ieee;use ieee.std_logic_1164.all;entity left_ctl isport(clk,lp,lr,brake,night:in std_logic;ledl,ledb,ledn :out std_logic);end entity left_ctl;architecture behave of left_ctl isbeginprocess(clk,lp,lr)beginif rising_edge(clk) thenif(lr='0') thenif(lp<='0') thenledl<='0';elseledl<='1';end if;elseledl<='0';end if;end if;end process;end architecture behave;1.3.4右边灯控制模块右边灯控制模块的工作框图如图3.5所示。

图1.5 右边灯控制模块的工作框图右边灯控制模块由VHDL程序来实现,下面是其中的一段VHDL代码:library ieee;use ieee.std_logic_1164.all;entity right_ctl isport(end entity right_ctl;architecture behave of right_ctl isbeginledb<=brake;ledn<=night;process(clk,rp,lr)beginif rising_edge(clk) thenif(lr='0') thenif(rp<='0') thenledr<='0';elseledr<='1';end if;elseledr<='0';end if;end if;end process;end architecture behave;2系统仿真2.1分频模块仿真及分析分频模块由VHDL程序实现后,其仿真图如图2.1所示。

图2.1 分频模块仿真图2.2汽车尾灯主控模块仿真及分析汽车尾灯主控模块由VHDL程序实现后,其仿真图如图2.2所示。

图2.2主控模块时序仿真图对时序仿真图进行分析:right,left,night,brake 为输入信号,right为1表示右转,leftT为1表示左转,night为1表示夜间行路,brake为1表示刹车。

rp,lp,night_led,brake_led为输出信号。

如图所示:当right为1时,产生一个rp 为1的信号脉冲输出,当left为1时,产生一个lp为1的信号脉冲输出,当night为1时,产生一个night_led为1的信号脉冲输出。

当brake为1时,产生一个brake_led左边灯控制模块由VHDL程序实现后,其仿真图如图2.3所示。

图2.3左边灯控制模块时序仿真图对时序仿真图进行分析:lp,lr,night,brake 为输入信号,lp为1表示左转,lr 为1表示右转,night为1表示夜间行路,brakeE为1表示刹车。

ledl,ledb,ledn为输出信号,表示汽车左侧的三盏灯。

如图所示:当lp为1时,ledl输出为1表示左侧灯亮,当brake为1时,ledb输出为1表示左侧灯亮,当night为1时,ledn输出为1表示左侧灯亮。

当lr为1时,左侧三盏灯输出均为0。

即没有灯亮。

2.4右边灯控制模块仿真及分析右边灯控制模块由VHDL程序实现后,其仿真图如图4.4所示。

汽车尾灯控制器12. 1310图2.4右边灯控制模块时序仿真图对时序仿真图进行分析:rp,lr,night,brake 为输入信号,lr为1表示左转,rp为1表示右转,night为1表示夜间行路,brakeE为1表示刹车。

ledr,ledbB,ledn为输出信号,表示汽车右侧的三盏灯。

如图所示:当rp为1时,ledr输出为1表示右侧灯亮,当brake为1时,ledb输出为1表示右侧灯亮,当night为1时,ledn输出为1表示右侧灯亮。

当lr为1时,右侧三盏灯输出均为0。

即没有灯亮。

2.5整个系统仿真及分析按图3.1组装系统后的仿真图如图4.5所示。

图2.5 整个系统仿真图对时序仿真图进行分析:right,left,night,brake 为输入信号,right为1表示汽车尾灯控制器201211右转,left 为1表示左转,night 为1表示夜间行路,brake 为1表示刹车。

rd1,rd2,rd3为输出信号,表示汽车右侧的三盏灯。

ld1,ld2,ld3为输出信号,表示汽车左侧的三盏灯。

如图所示:当right 为1时,rd1输出为1表示右侧灯亮,当left 为1时,ld1为输出为1表示左侧灯亮,当night 为1时,ld2,rd2输出均为1,表示左,右两侧各有一盏灯亮。

当brake 为1时,ld3,rd3输出均为1,表示左,右两侧各有一盏灯亮。

3 硬件电路部分 3.1芯片的选择CPLD 采用Altera 新一代的MaxII 器件EPM570T100C5,配合QuartusII 可以很容易实现CPLD 的开发,模块具有4位键盘输入,4位开关量输入,8个动态LED 显示,1个静态LED 显示,8个发光管,1个蜂鸣器,用于完成试验,同时引出了3.3V 的IO 口,方便模块的扩展。

程序下载方法采用ByteBlaster ,本模块下载时,插上跳线帽JP214~JP217;其他模块下载时拔下跳线帽JP214~JP217。

3.1.1芯片的选择(图2.6)图2.6汽车尾灯控制器12. 1312 3.1.2 详细连线图(如图2.7)图 2.73.2输入输出接口的选择3.2.1开关量输入接口(S205~S208)表F.3-3 拨盘开关输入接口名称EPM507引脚号输入电平备注接口S205 33 左为0,右为1 电平输入left S206 34 左为0,右为1 电平输入right S207 35 左为0,右为1 电平输入brake S208 36 左为0,右为1 电平输入night3.2.2发光管输出(D201~D208)表F.3-4 发光管输出4 试验总结通过两星期的紧张工作,最后完成了我们的设计任务——汽车尾灯控制器的设计。

通过本次课程设计的学习,我深深的体会到设计课的重要性和目的性。

在设计中要求我们要有耐心和毅力,还要细心,稍有不慎,一个小小的错误就会导致结果的不正确,而对错误的检查要求我要有足够的耐心,通过这次设计和设计中遇到的问题,我也积累了一定的经验,相信对以后从事集成电路设计工作会有一定的帮助。