DF01M中文资料

电源入口模块DF11及其他相关产品说明说明书

IEC Appliance Inlet C14 or C18 with recessed Circuit Breaker TA45See below:Approvals and CompliancesC1470° CC1870° CDescription- Panel mount :Screw-on version from front or rear side, snap-in version from frontside- 2 Functions :Appliance Inlet protection class I or II , circuit breaker type TA45 2-pole- Quick connect terminals 6.3 x 0.8 mmCharacteristics- All single elements are already wired- Circuit Breaker non-illuminated or illuminated- Suitable for use in equipment according to IEC/UL 60950Other versions on request- Unwired versions- Other rocker marking- Variant with notch for V-Lock mating CordsetsReferencesAlternative: version with line filter DF12Substitute for type 6145Weblinkspdf datasheet, html-datasheet, General Product Information, Distributor-Stock-Check, Accessories, Detailed request for product, Microsite Newly available variants corresponding to V-Lock mating cordset. The connector is equipped with a notch intended for use with the latching cordset. The cord latching system prevents against accidental removal of the cordset.T echnical DataRatings IEC10 A / 250 VAC; 50 H zRatings UL/CSA15 A / 250 VAC; 60 H zDielectric Strength> 2.5 kVAC between L-N> 3 kVAC between L/N-PE(1 min/50 H z)Allowable Operation Tempe-rature-10 °C to 55 °CIP-Protection from front side IP 40 acc. to IEC 60529Insulation cover Suitable for appliances with protectionclass I or II acc. to IEC 61140Terminal Quick connect terminals 6.3 x 0.8 mmPanel Thickness S Screw: max 8 mmMounting screw torque max 0.5 NmSnap-in: 1/1.5/2/2.5/3 mmMaterial: Housing Thermoplastic, black, UL 94V-0appliance inlet/-outlet C14 / C18 acc. to IEC 60320-1,UL 60320-1, CSA C22.2 no. 60320-1(for cold conditions) pin-temperature 70°C, 10 A, Protection Class I or IICircuit Breakers Acc. IEC/EN 60934, UL 1077, CSA22.2 no. 2352-pole rocker switch, illuminated or non-illuminated. Optional with undervoltage-or remote trip releaseShort circuit capacity Icn:at In < 3A/240VAC : 10 x Inat In ≥ 3A/240VAC : 300AApprovals and CompliancesDetailed information on product approvals, code requirements, usage instructions and detailed test conditions can be looked up in Details about ApprovalsApprovalsThe approval mark is used by the testing authorities to certify compliance with the safety requirements placed on electronic products.Approval Reference T ype: DF11Approval Logo Certificates Certification Body DescriptionVDE Approvals VDE Certificate Number: 40011305UL Approvals UL UL File Number: E964541Product standardsProduct standards that are referencedOrganization Design StandardDescriptionDesigned according to IEC 60320-1Appliance couplers for household and similar general purposesDesigned according to UL 60320-1Standard for Attachment Plugs and ReceptaclesDesigned according to CSA C22.2 no. 60320-1General Use Receptacles, Attachment Plugs, and Similar Wiring Devices Application standardsApplication standards where the product can be usedOrganization Design StandardDescriptionDesigned for applications acc.IEC/UL 60950IEC 60950-1 includes the basic requirements for the safety of informationtechnology equipment.CompliancesThe product complies with following Guide LinesIdentification Details Initiator DescriptionCE declaration of conformity SCHURTER AG The CE marking declares that the product complies with the applicablerequirements laid down in the harmonisation of Community legislation onits affixing in accordance with EU Regulation 765/2008.RoHS SCHURTER AG EU Directive RoHS 2011/65/EUChina RoHS SCHURTER AG The law SJ / T 11363-2006 (China RoHS) has been in force since 1 March2007. It is similar to the EU directive RoHS.REACH SCHURTER AG On 1 June 2007, Regulation (EC) No 1907/2006 on the Registration,Evaluation, Authorization and Restriction of Chemicals 1 (abbreviated as"REACH") entered into force.MicrositeV-Lock SCHURTER AG V-Lock system are based on a matching plug-dose combination. Theconnector is equipped with a notch intended for use with the latchingcordset. The cord latching system prevents against accidental removal ofthe cordset.Dimensions [mm]Screw-on mounting23Snap-in version* --- Version TA45 with undervoltage releaseDiagrams1)2)NL PE 1) Line 2) Load45Technical data (continued) Circuit breaker Tripping characteristics I n < 3 ATripping characteristics I n >_ 3… <_ 15 AOptional Variants 0 standard 9 V-Lock Colour 0 blackMounting0 Screw mounting1 Snap-in mounting s = 1.0 mm2 Snap-in mounting s = 1.5 mm3 Snap-in mounting s = 2.0 mm4 Snap-in mounting s = 2.5 mm 5 Snap-in mounting s = 3.0 mm Terminal PE0 without terminal (PCII)1 Quick-connect terminal 6.3x0.8 mmTerminal N1 Quick-connect terminals 6.3x0.8mm, without connection to TA453 connection to TA45 non insulated Terminal L1 Quick-connect terminals 6.3x0.8mm, without connection to TA453 connection to TA45 non insulated60[ min ]10513020Multiple of rated current[ x I n ]T r i p p i n g t i m e60[ min ]10513020[ x I n ]Multiple of rated currentT r i p p i n g t i m eConfiguratorcode (example)Packaging unit 20 Pcs AccessoriesDescriptionAssorted CoversRear CoverMating Outlets/ConnectorsCategory / DescriptionAppliance Outlet Overview completeIEC Appliance Outlet F, Screw-on Mounting, Front Side, Solder Terminal4787IEC Appliance Outlet F, Snap-in Mounting, Front Side, Solder or Quick-connect Terminal4788IEC Appliance Outlet F or H, Screw-on Mounting, Front Side, Solder, PCB or Quick-connect Terminal5091Appliance Outlet further types to DF11Connector Overview complete4782 Mounting: Power Cord, 3 x 1 mm² / 3 x 18 AWG, Cable, Connector: IEC C1347824785 Mounting: Power Cord, 3 x 1 mm² / 3 x 18 AWG, Cable, Connector: IEC C1347854300-06 Mounting: Power Cord, 3 x 1 mm² / 3 x 18 AWG, Cable, Connector: IEC C134300-06IEC Connector C15 for hot conditions 120°C, Rewireable, Straight4781IEC Connector C15 for hot conditions 120°C, Rewireable, Angled4784Connector further types to DF11...Mating Outlets/Connectors shutteredPower Cord Overview completeVAC13KS, Overview, diverse Connector IEC C13, cord end:VAC13KSPower Cord further types to DF11The specifications, descriptions and illustrations indicated in this document are based on currentinformation. All content is subject to modifications and amendments. Information furnished is believed11.9.2186。

DF04M;DF06M;DF02M;DF01M;DF08M;中文规格书,Datasheet资料

Absolute Maximum Ratings * T A = 25°C unless otherwise noted* These ratings are limiting values above which the serviceability of any semiconductor device may be impaired.Thermal Characteristics* Device mounted on PCB with 0.5 × 0.5” (13 × 13mm).Electrical Characteristics T A = 25°C unless otherwise notedSymbolParameterValueUnits005M 01M02M04M06M08M10MV RRM Maximum Repetitive Reverse Voltage 501002004006008001000V V RMS Maximum RMS Bridge Input Voltage 3570140280420560700V V R DC Reverse Voltage (Rated V R )501002004006008001000V I F(AV)Average Rectified Forward Current,@ T A = 40°C 1.5A I FSM Non-repetitive Peak Forward Surge Current8.3 ms Single Half-Sine-Wave 50A T STG Storage Temperature Range -55 to +150°C T JOperating Junction Temperature-55 to +150°CSymbolParameter ValueUnitsP D Power Dissipation3.1W R θJAThermal Resistance, Junction to Ambient, * per leg40°C/WSymbolParameterValueUnitsV F Forward Voltage, per element @ 1.0A 1.1V I RReverse Current, per element @ rated V RT A = 25°C T A = 125°C 5.0500μA μA I 2t Rating for Fusing t < 8.35ms10A 2s C TTotal Capacitance, per leg V R = 4.0V, f = 1.0MHz25pFDIPThe following includes registered and unregistered trademarks and service marks, owned by Fairchild Semiconductor and/or its global subsidiaries, and is notAccuPower¥Auto-SPM¥Build it Now¥CorePLUS¥CorePOWER¥CROSSVOLT¥CTL¥Current Transfer Logic¥DEUXPEED®Dual Cool™ EcoSPARK®EfficientMax¥ESBC¥®Fairchild®Fairchild Semiconductor®FACT Quiet Series¥FACT®FAST®FastvCore¥FETBench¥FlashWriter®*FPS¥F-PFS¥FRFET®Global Power Resource SMGreen FPS¥Green FPS¥ e-Series¥G max¥GTO¥IntelliMAX¥ISOPLANAR¥MegaBuck¥MICROCOUPLER¥MicroFET¥MicroPak¥MicroPak2¥MillerDrive¥MotionMax¥Motion-SPM¥OptoHiT™OPTOLOGIC®OPTOPLANAR®®PDP SPM™Power-SPM¥PowerTrench®PowerXS™Programmable Active Droop¥QFET®QS¥Quiet Series¥RapidConfigure¥¥Saving our world, 1mW/W/kW at a time™SignalWise¥SmartMax¥SMART START¥SPM®STEALTH¥SuperFET¥SuperSOT¥-3SuperSOT¥-6SuperSOT¥-8SupreMOS®SyncFET¥Sync-Lock™®*The Power Franchise®TinyBoost¥TinyBuck¥TinyCalc¥TinyLogic®TINYOPTO¥TinyPower¥TinyPWM¥TinyWire¥TriFault Detect¥TRUECURRENT¥*P SerDes¥UHC®Ultra FRFET¥UniFET¥VCX¥VisualMax¥XS™* Trademarks of System General Corporation, used under license by Fairchild Semiconductor.DISCLAIMERFAIRCHILD SEMICONDUCTOR RESERVES THE RIGHT TO MAKE CHANGES WITHOUT FURTHER NOTICE TO ANY PRODUCTS HEREIN TO IMPROVE RELIABILITY, FUNCTION, OR DESIGN. FAIRCHILD DOES NOT ASSUME ANY LIABILITY ARISING OUT OF THE APPLICATION OR USE OF ANY PRODUCT OR CIRCUIT DESCRIBED HEREIN; NEITHER DOES IT CONVEY ANY LICENSE UNDER ITS PATENT RIGHTS, NOR THE RIGHTS OF OTHERS. THESE SPECIFICATIONS DO NOT EXPAND THE TERMS OF FAIRCHILD’S WORLDWIDE TERMS AND CONDITIONS, SPECIFICALLY THE WARRANTY THEREIN, WHICH COVERS THESE PRODUCTS.LIFE SUPPORT POLICYFAIRCHILD’S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF FAIRCHILD SEMICONDUCTOR CORPORATION.As used herein:1. Life support devices or systems are devices or systems which, (a) areintended for surgical implant into the body or (b) support or sustain life, and (c) whose failure to perform when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury of the user. 2. A critical component in any component of a life support, device, orsystem whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.ANTI-COUNTERFEITING POLICYFairchild Semiconductor Corporation's Anti-Counterfeiting Policy. Fairchild's Anti-Counterfeiting Policy is also stated on our external website, , under Sales Support.Counterfeiting of semiconductor parts is a growing problem in the industry. All manufacturers of semiconductor products are experiencing counterfeiting of their parts. Customers who inadvertently purchase counterfeit parts experience many problems such as loss of brand reputation, substandard performance, failed applications, and increased cost of production and manufacturing delays. Fairchild is taking strong measures to protect ourselves and our customers from the proliferation of counterfeit parts. Fairchild strongly encourages customers to purchase Fairchild parts either directly from Fairchild or from Authorized Fairchild Distributors who are listed by country on our web page cited above. Products customers buy either from Fairchild directly or from Authorized Fairchild Distributors are genuine parts, have full traceability, meet Fairchild's quality standards for handling and storage and provide access to Fairchild's full range of up-to-date technical and product information. Fairchild and our Authorized Distributors will stand behind all warranties and will appropriately address any warranty issues that may arise. Fairchild will not provide any warranty coverage or other assistance for parts bought from Unauthorized Sources. Fairchild is committed to combat this global problem and encourage our customers to do their part in stopping this practice by buying direct or from authorized distributors.PRODUCT STATUS DEFINITIONSDefinition of TermsDatasheet Identification Product Status Definition分销商库存信息:FAIRCHILDDF04M DF06M DF02M DF01M DF08M DF10M DF005M。

常用施工中英文对照表

SML CONC RED JCK BW

内部资料,仅供参考,

1

中英文对照表

序号 43 44 45 46 47 48 49 50 51 52 53 54 55 56 57 58 59 60 61 62 63 64 65 66 67 68 69 70 71 72 73 74 75 76 77 78 79 80 81 82 83 84 英文名称 M QUICK CPL BW F QUICK CPL RUBH WN FLG RF WN FLG RJ WN FLG FF SO FLG RF SW FLG RF SCR FLG SCR PN320 SCR STUB END LE PN320 BL FLG RG RF RED BL FLG RJ JCK STUB END+LJ FLG LE PN320 LWN FLG-JCK P DRN VLF LWN FLG-PIPE DRN VLF LWN FLG-P PRES CON RF LWN FLG-P PRES CON RJ LWN FLG-JCKP PRESC CON RF LWN FLG-JCKP PRESC RJ LWN FLG-JCKP PRESC RF PLATE DISC BL FLG RF DRIP RING (1/2″NPT HOLES)RF DRIP RING (3/4″NPT HOLES)RF DRIP RING (3/4″NPT HOLES)RJ SPECTACLE FLG RF SINGLE DERIV RINGLE+INT GSK/MALE THR PN320 HOR TEMPSTR RF HOR TEMPSTR RED FLG RF BW GATE VALVE BW GLOBE VALVE BW CHECK VALVE FLG FLG FLG FLG FLG FLG FLG FLG GATE VALVE CHECK VALVE PLUG BALL Y STR SIGHT GLASS JACK PLUG VALVE 3WAY PLUG VALVE VALVE VALVE FLG GLOBE VALVE 中文名称 对焊快装接头(公扣) 快装接头(母扣) 对焊法兰(RF) 对焊法兰(RJ) 对焊法兰(FF) 平焊法兰(RF) 承插焊法兰(RF) 高压螺纹法兰 盲法兰(RF) 堆焊盲法兰(PN320lens) 盲法兰(RJ) 异径盲法兰(RF) 异径盲法兰(RJ) 夹套管用管端突缘(PN320) 夹套管排液阀用长颈对焊法兰 排液阀用长颈对焊法兰 管道压力表连接用长颈对焊法兰(RF) 管道压力表连接用长颈对焊法兰(RJ) 标准号 STD-F35A TY ABW STD-F35A TY B ASMEB16.5 ASMEB16.5 ASMEB16.5 ASMEB16.5 ASMEB16.5 STD-F315 ASMEB16.5 STD-F316 ASMEB16.5 STD-F182A STD-F182A STD-F321 STD-F183A STD-F184A STD-F187A STD-F187A

抗菌药物DDD值 按中文名称排序

ATC code English_name药品名称DDD值(WHO-ATC)DDD值(C)给药途径备注J01CA09Azlocillin阿洛西林12.0g PJ01GB06Amikacin阿米卡星 1.0g PJ01CA04Amoxicillin阿莫西林 1.0g OJ01CA04Amoxicillin阿莫西林 1.0g P Amoxicillin and Flucloxacillin阿莫西林氟氯西林 1.5g O(1:1) Amoxicillin and Flucloxacillin阿莫西林氟氯西林 5.0g P(1:1) J01CR02Amoxiciliin and Clavulanate Pot阿莫西林克拉维酸钾 1.0g O*J01CR02Amoxiciliin and Clavulanate Pot阿莫西林克拉维酸钾 3.0g P*J01CR02Amoxiciliin and Sulbactam阿莫西林钠舒巴坦 1.0g O*J01CR02Amoxicillin and Sulbactam阿莫西林钠舒巴坦 3.0g P* Amoxicillin and Dicloxacillin阿莫西林双氯西林 2.0g O(2:1) Apalcillin阿帕西林 2.0g PJ01CA19Aspoxicillin阿扑西林 4.0g PJ01FA10Azithromycin阿奇霉素0.3g OJ01FA10Azithromycin阿奇霉素0.5g P Astromicin阿司米星 1.5g PJ01CA01Ampicillin氨苄西林 2.0g OJ01CA01Ampicillin氨苄西林 2.0g PATC code English_name药品名称DDD值(WHO-ATC)DDD值(C)给药途径备注Ampicillin and Probenecid氨苄西林丙磺舒 4.5g PAmpicillin and Cloxacillin氨苄西林氯唑西林 3.0g P(1:1) J01CR01Ampicillin and Sulbactam氨苄西林舒巴坦 1.5g OJ01CR01Ampicillin and Sulbactam氨苄西林舒巴坦 2.0g PJ01DF01Aztreonam氨曲南 4.0g PJ01XD03Ornidazole奥硝唑 1.0g PP01AB03Ornidazole奥硝唑 1.5g OA07AA06Paromomycin巴龙霉素 3.0g OJ01CF04Oxacillin苯唑西林 2.0g OJ01CF04Oxacillin苯唑西林 2.0g PJ01DH05Biapenem比阿培南 1.2g PJ01MB04Pipemidic acid吡哌酸0.8g OJ01CE08Benzathine benzylpenicillin苄星青霉素 3.6g PJ01XX04Spectinomycin大观霉素 3.0g PJ01GB09Dibekacin地贝卡星0.14g PJ01FA13Dirthromycin地红霉素0.5g OJ01AA02Doxycycline多西环素0.1g OJ01AA02Doxycycline多西环素0.1g PATC code English_name药品名称DDD值(WHO-ATC)DDD值(C)给药途径备注J01XB02Polymyxin B多粘菌素B0.15g PJ01DH03Ertpenem厄他培南 1.0g P Faropenem法罗培南0.5g OJ01XC01Fusidic acid夫西地酸 1.5g OJ01XC01Fusidic acid夫西地酸 1.5g P furbenicillin呋布西林 6.0g PJ02AC03Voriconazole伏立康唑0.4g OJ02AC03Voriconazole伏立康唑0.4g PJ02AX01Flucytosine氟胞嘧啶10.0g OJ02AX01Flucytosine氟胞嘧啶10.0g PJ02AC01Fluconazole氟康唑0.2g OJ02AC01Fluconazole氟康唑0.2g PJ01CF05Flucloxacillin氟氯西林 2.0g OJ01CF05Flucloxacillin氟氯西林 2.0g PJ01MA08fleroxocin氟罗沙星0.4g OJ01MA08fleroxocin氟罗沙星0.4g PJ01DC14Flomoxef氟氧头孢 2.0g PJ01EE01Sulfamethoxazole and Trimethopr复方磺胺甲噁唑(复方新诺明) 1.92g O(4片)ATC code English_name药品名称DDD值(WHO-ATC)DDD值(C)给药途径备注J01EE01Sulfamethoxazole and Trimethopr复方磺胺甲噁唑(复方新诺明)0.84g P(2支)J01MA11Grepafloxacin格帕沙星0.4g O Guamecycline胍甲环素 1.2g OJ01BG10Ribostamycin核糖霉素 1.0g PJ01FA01Erythromycin红霉素 1.0g OJ01FA01Erythromycin红霉素 1.0g PJ01FA01Erythromycin ethylsuccinate琥乙红霉素 2.0g OJ01MA02Ciprofloxacin环丙沙星 1.0g OJ01MA02Ciprofloxacin环丙沙星0.5g P Erythromycin Cyclocarbonate环酯红霉素 1.25g OJ01EB03Sulfadimidine磺胺二甲嘧啶 4.0g PJ01EC01Sulfamethoxazole磺胺甲噁唑 2.0g OJ01EC02Sulfadiazine磺胺嘧啶0.6g OJ01EC02Sulfadiazine磺胺嘧啶 4.0g PJ01CA16Sulbenicillin磺苄西林15.0g PD01BA01Griseofulvin灰黄霉素0.5g OJ01MA15Gemifloxacin吉米沙星0.32g O Leucomycin吉他霉素 1.2g OATC code English_name药品名称DDD值(WHO-ATC)DDD值(C)给药途径备注Leucomycin吉他霉素0.8g P J01MA16Gatifloxacin加替沙星0.4g O J01MA16Gatifloxacin加替沙星0.4g P J01BA02Thiamphenicol甲砜霉素 1.5g O J01BA02Thiamphenicol甲砜霉素 1.5g P G01AF01Metronidazole甲硝唑0.5g V J01XD01Metronidazole甲硝唑 1.5g P P01AB01Metronidazole甲硝唑 2.0g O J01EA01Trimethoprim甲氧苄氨嘧啶0.4g P J01EA01Trimethoprim甲氧苄氨嘧啶(TMP)0.4g O J01FA07Josamycin交沙霉素 2.0g O J02AX05Caspofungin卡泊芬净50mg P J01GB04Kanamycin卡那霉素 1.0g P J01FA09Clarithromycin克拉霉素0.5g O J01FA09Clarithromycin克拉霉素 1.0g P J01FF01Clindamycin克林霉素 1.2g O J01FF01Clindamycin克林霉素 1.8g P G01AF02Clotrimazole克霉唑0.1g VATC code English_name药品名称DDD值(WHO-ATC)DDD值(C)给药途径备注G01AA04Candicidin克念菌素6mg VJ01DD06Latamoxef拉氧头孢 4.0g PJ04AB03Rifamycin利福霉素0.6g PJ01XX08Linezolid利奈唑胺 1.2g OJ01XX08Linezolid利奈唑胺 1.2g PJ01GA01Streptomycin链霉素 1.0g PJ02AA01Amphotericin B两性霉素B35mg PJ02AA01Amphotericin B两性霉素B脂质体35mg PJ01FF02Lincomycin林可霉素 1.8g OJ01FF02Lincomycin林可霉素 1.8g PJ01XX01Fosfomycin磷霉素8.0g P Fosfomycin and Trimethoprim磷霉素钙甲氧苄啶0.45g O(5:1) J01MA10Rufloxacin芦氟沙星0.2g OJ01BA01Chloramphenicol氯霉素 3.0g OJ01BA01Chloramphenicol氯霉素 3.0g PJ01CF02cloxacillin氯唑西林 2.0g OJ01CF02cloxacillin氯唑西林 2.0g P lenampicillin仑氨西林 1.75g OATC code English_name药品名称DDD值(WHO-ATC)DDD值(C)给药途径备注J01FA06Roxithromycin罗红霉素0.3g OJ01FA12Rokitamycin罗他霉素0.8g OJ01MA07Lomefloxacin洛美沙星0.4g OJ01MA07Lomefloxacin洛美沙星0.4g P Mekeumycin麦白霉素 1.0g OJ01FA03Midecamycin麦迪霉素 1.0g OJ01DH02Meropenem美罗培南 2.0g PJ01CA10Mezlocillin美洛西林 6.0g P Mezlocillin and Sulbactam美洛西林舒巴坦 6.0g P* J01AA05Metacycline美他环素0.6g OJ01CA11Mecillinan美西林钠 1.2g PG01AF04Miconazole咪康唑0.1g VJ02AB01Miconazole咪康唑 1.0g PJ01AA08Minocycline米诺环素0.2g OJ01AA08Minocycline米诺环素0.2g PJ01MA14Moxifloxacin莫昔沙星0.4g OJ01MA14Moxifloxacin莫昔沙星0.4g P Nafcillin奈夫西林 3.5g OATC code English_name药品名称DDD值(WHO-ATC)DDD值(C)给药途径备注Nafcillin奈夫西林 4.0g PJ01GB07Netilmicin奈替米星0.35g OJ01GB07Netilmicin奈替米星0.35g PJ01MA06Norfloxacin诺氟沙星0.4g PJ01MA06Norfloxacin诺氟沙星(氟哌酸)0.8g OJ01DH55Panipenem and Betamipron帕尼培南 2.0g P* J01MA18Pazufloxacin帕珠沙星 1.0g PJ01CA12Piperacilin哌拉西林14.0g PJ01CR05Piperacillin and sulbactam哌拉西林钠舒巴坦14.0g P* J01CR05Piperacilin and Tazobactam哌拉西林钠他唑巴坦14.0g P* J01MA03Pefloxacin培氟沙星0.8g OJ01MA03Pefloxacin培氟沙星0.8g PJ01CA08Pivmecillinam匹美西林0.6g OJ01CE09Procaine benzylpenicillin普鲁卡因青霉素0.6g PJ01CE01Benzylpenicillin青霉素 3.6g PJ01CE02Phenoxymethylpenicillin青霉素Ⅴ 2.0g OJ01GB03Gentamicin庆大霉素0.3g OJ01GB03Gentamicin庆大霉素0.24g PATC code English_name药品名称DDD值(WHO-ATC)DDD值(C)给药途径备注J01MA13Trovafloxacin曲伐沙星0.2g OJ01MA13Trovafloxacin曲伐沙星0.2g P Norvancomycin去甲万古霉素 1.6g PP01AB07Secnidazole塞克硝唑 2.0g OG01AF08Ttioconazole噻康唑0.3g VJ01CG01Sulbactan舒巴坦钠 1.0g PJ01CR04sultamicillin舒他西林 1.5g O* J01CF01dicloxacillin双氯西林 2.0g OJ01CF01dicloxacillin双氯西林 2.0g PJ01MA09Sparfloxacin司帕沙星0.2g OJ01AA07Tatracycline四环素 1.0g OJ01AA07Tatracycline四环素 1.0g PJ01CA03Carbenicillin羧苄西林12.0g PJ01FA15Telithromycin泰利霉素0.8g OD01BA02Terbinafine特比奈芬0.25g OJ01AA12Tigecycline替加环素0.1g PJ01CA13Ticarcillin替卡西林15.0g PJ01CR03Ticarcillin and Clavulanate Pot替卡西林克拉维酸钾15.0g P*ATC code English_name药品名称DDD值(WHO-ATC)DDD值(C)给药途径备注J01XA02Teicoplanin替考拉宁0.4g PJ01XD02Tinidazole替硝唑 1.5g PP01AB02Tinidazole替硝唑 2.0g OG01AF11Ketoconazole酮康唑0.4g VJ02AB02Ketoconazole酮康唑0.2g OJ01DB01Cefalexin头孢氨苄 2.0g O Cefalexin and Trimethoprim头孢氨苄甲氧苄啶0.9g O(5:1) J01DE01Cefepime头孢吡肟 2.0g PJ01DC10Cefprozil头孢丙烯 1.0g OJ01DD13Cefpodoxime头孢泊肟0.4g OJ01DD14Ceftibuten头孢布烯(布坦)0.4g OJ01DD15Cefdinir头孢地尼0.6g OJ01DD09Cefodizime头孢地秦 2.0g PJ01DC02Cafuroxime头孢呋辛 3.0g PJ01DC02Cafuroxime头孢呋辛酯0.5g OJ01DD03Cefsilodin头孢磺啶(头孢磺吡苄)4.0g PJ01DD05Cefmenoxime头孢甲肟 2.0g P Cefcidin头孢克定 4.0g PATC code English_name药品名称DDD值(WHO-ATC)DDD值(C)给药途径备注J01DC04Cefaclor头孢克洛 1.0g OJ01DD08Cefixime头孢克肟0.4g OJ01DB09Cefradine头孢拉定 2.0g OJ01DB09Cefradine头孢拉定 2.0g PJ01DC13Cefbuperazone头孢拉宗 2.0g PJ01DC11Ceforanide头孢雷特 4.0g P Cefathiamidine头孢硫脒 3.0g PJ01DC09Cefmetazole头孢美唑 4.0g PJ01DC03Cefamandole头孢孟多(头孢羟唑) 6.0g P Cefpimizolec头孢咪唑未查到J01DC12Cefminox头孢米诺 4.0g PJ01DC06Cefonicide头孢尼西 1.0g PJ01DD12Cefoperazone头孢哌酮 4.0g PJ01DD62Cefoperazone,combinations头孢哌酮钠舒巴坦 4.0g P*J01DD62Cefoperazone,combinations头孢哌酮他唑巴坦 4.0g PJ01DD11Cefpiramide头孢匹胺 2.0g PJ01DB08Cefapirin头孢匹林 4.0g PJ01DE02Cefpirome头孢匹罗 4.0g P第11页共14页ATC code English_name药品名称DDD值(WHO-ATC)DDD值(C)给药途径备注J01DB05Cefadroxil头孢羟氨苄 2.0g O Cefadroxil and Trimethoprim头孢羟氨苄甲氧苄啶0.9g O(5:1) J01DD04Ceftriaxone头孢曲松 2.0g PJ01DD54Ceftriaxone,combinations头孢曲松钠舒巴坦 2.0g P*J01DB02Cefaloridine头孢噻啶 3.0g PJ01DB03Cefalotin头孢噻吩 4.0g P Cefoselis头孢噻利 2.0g PJ01DD01Cefotaxime头孢噻肟 4.0g P Cefotaxime and Sulbactam头孢噻肟舒巴坦 4.0g P*J01DB11Cefroxadine头孢沙定0.75g OJ01DD02Ceftazidime头孢他啶 4.0g P Ceftazidime and Sulbactam头孢他啶舒巴坦 4.0g P*J01DD10Cefetamet头孢他美酯 1.0g O Cefteram头孢特仑酯0.375g OJ01DC07Cefotiam头孢替安 4.0g PJ01DB12Ceftezole头孢替唑 6.0g PJ01DC01Cefoxitin头孢西丁 6.0g PJ01DB10Cefacetrile头孢乙氰 4.0g P第12页共14页ATC code English_name药品名称DDD值(WHO-ATC)DDD值(C)给药途径备注J01DB04Cefazolin头孢唑林 3.0g P Cefazolin and Sulbactam头孢唑啉舒巴坦 3.0g P* Cefuzonam头孢唑喃 1.5g PJ01DD07Ceftizoxime头孢唑肟 4.0g PJ01AA06Oxytetracycline土霉素 1.0g OJ01AA06Oxytetracycline土霉素 1.0g PJ01GB01Tobramycin妥布霉素0.24g P Tosufloxacin妥舒沙星0.375g OJ01XA01Vancomycin万古霉素(稳可信) 2.0g PJ01GB08Sisomicin西索米星0.24g PS01AA22Micronomicin小诺米星0.18g PJ01GB05Neomycin新霉素 1.0g OJ01DH51Imipenem and Cilastatin亚胺培南/西司他丁 2.0g P* J01MA01Ofloxacin氧氟沙星0.4g OJ01MA01Ofloxacin氧氟沙星0.4g PJ02AC02Itraconazole伊曲康唑0.2g OJ02AC02Itraconazole伊曲康唑0.2g PJ01MA04Enoxacin依诺沙星0.8g O第13页共14页ATC code English_name药品名称DDD值(WHO-ATC)DDD值(C)给药途径备注J01MA04Enoxacin依诺沙星0.4g PEtimicin依替米星0.25g PErythromycin Estolate依托红霉素 1.375g OJ01FA02Spiramycin乙酰螺旋霉素 3.0g OAcetylspiramycin乙酰麦迪霉素0.9g O(5:1)J01GB11Isepamicin异帕米星0.4g PG01AF05Econazole益康唑0.1g VJ01ED20Combinations Sulfadiazine增效联磺 1.92g O(4片)J01XB01Colistin粘菌素(多粘菌素E) 3.0MU PA07AA02Nystatin制霉菌素 1.5MU OG01AA01Nystatin制霉菌素0.1MU VJ01FA05Oleandomycin竹桃霉素 1.0g PJ01MA12Levofloxacin左氧氟沙星0.5g OJ01MA12Levofloxacin左氧氟沙星0.5g P说明:1.给药途径中:O(oral).口服给药;P(parenteral).肠道外给药(注射给药);V(vaginal).阴道给药。

DF06中文资料

DF005 – DF101.0A GLASS PASSIVATED BRIDGE RECTIFIERSingle Phase, half wave, 60Hz, resistive or inductive load.For capacitive load, derate current by 20%.Characteristic Symbol DF005DF01DF02DF04DF06DF08DF10UnitPeak Repetitive Reverse Voltage Working Peak Reverse Voltage DC Blocking Voltage V RRMV RWMV R501002004006008001000VRMS Reverse Voltage V R(RMS)3570140280420560700V Average Rectified Output Current @T A = 40°C I O 1.0A Non-Repetitive Peak Forward Surge Current 8.3msSingle half sine-wave superimposed on rated load(JEDEC Method)I FSM30A Forward Voltage per element @I F = 1.0A V FM 1.1VPeak Reverse Current @T A = 25°C At Rated DC Blocking Voltage @T A = 125°C I RM10500µATypical Junction Capacitance per element (Note 1)C j25pF Typical Thermal Resistance (Note 2)R JA40K/W Operating and Storage Temperature Range T j, T STG-55 to +150°CNote: 1. Measured at 1.0 MHz and applied reverse voltage of 4.0V D.C.2. Thermal resistance junction to ambient mounted on PC board with 13mm2 copper pad.WTE0.010.11.0100.40.60.81.01.21.4I ,I N S T A N T A N E O U S F O R W A R D C U R R E N T (A )F V ,INSTANTANEOUS FORWARD VOLTAGE (V)Fig.2T yp Forward Characteristics (per element)F 0102030405060110100I ,P E A K F O R W A R D S U R G E C U R R E N T (A )F S M NUMBER OF CYCLES AT 60 HzFig. 3 Max Non-Repetitive Peak Forward Surge Current110100110100C ,C A P A C I T A N C E (p F )J V ,REVERSE VOLTAGE (V)Fig.4Typ Junction Capacitance (per element)R 0.010.11.01010020406080100120140I ,I N S T A N T A N E O U S R E V E R S E C U R R E N T (µA )R PERCENT OF RATED PEAK REVERSE VOLTAGE (%)Fig.5Typ Reverse Characteristics (per element)1.00.5406080100120140I ,A V E R A G E F O R W A R D C U R R E N T (A )(A V )T ,AMBIENT TEMPERATURE (°C)Fig.1Output Current Derating Curve AORDERING INFORMATIONProduct No.Package TypeShipping QuantityDF005DIL Bridge 50 Units/Tube DF01DIL Bridge 50 Units/Tube DF02DIL Bridge 50 Units/Tube DF04DIL Bridge 50 Units/Tube DF06DIL Bridge 50 Units/Tube DF08DIL Bridge 50 Units/Tube DF10DIL Bridge50 Units/TubeShipping quantity given is for minimum packing quantity only. For minimum order quantity, please consult the Sales Department.Won-Top Electronics Co., Ltd (WTE) has checked all information carefully and believes it to be correct and accurate. However, WTE cannot assume any responsibility for inaccuracies. Furthermore, this information does not give the purchaser of semiconductor devices any license under patent rights to manufacturer. WTE reserves the right to change any or all information herein without further notice.WARNING : DO NOT USE IN LIFE SUPPORT EQUIPMENT. WTE power semiconductor products are not authorized for use as critical components in life support devices or systems without the express written approval.We power your everyday.Won-Top Electronics Co., Ltd.No. 44 Yu Kang North 3rd Road, Chine Chen Dist., Kaohsiung, Taiwan Phone: 886-7-822-5408 or 886-7-822-5410Fax: 886-7-822-5417Email: sales@Internet: 。

AT26DF161中文资料

Features Array•Single 2.7V - 3.6V Supply•Serial Peripheral Interface (SPI) Compatible–Supports SPI Modes 0 and 3•66 MHz Maximum Clock Frequency•Flexible, Uniform Erase Architecture–4-Kbyte Blocks–32-Kbyte Blocks–64-Kbyte Blocks–Full Chip Erase•Individual Sector Protection for Program/Erase Protection–Sixteen 128-Kbyte Physical Sectors•Hardware Controlled Locking of Protected Sectors•Flexible Programming–Byte/Page Program (1 to 256 Bytes)•JEDEC Standard Manufacturer and Device ID Read Methodology•Low Power Dissipation–7 mA Active Read Current (Typical)–4 µA Deep Power-Down Current (Typical)•Endurance: 100,000 Program/Erase Cycles•Data Retention: 20 Years•Complies with Full Industrial Temperature Range•Industry Standard Green (Pb/Halide-free/RoHS Compliant) Package Options –8-lead SOIC (200-mil wide)–8-contact MLF (5 mm x 6 mm)1.DescriptionThe AT26DF161 is a serial interface Flash memory device designed for use in a wide variety of high-volume consumer based applications in which program code is shad-owed from Flash memory into embedded or external RAM for execution. The flexible erase architecture of the AT26DF161, with its erase granularity as small as 4-Kbytes, makes it ideal for data storage as well, eliminating the need for additional data storage EEPROM devices.The physical sectoring and the erase block sizes of the AT26DF161 have been opti-mized to meet the needs of today's code and data storage applications. By optimizing the size of the physical sectors and erase blocks, the memory space can be used much more efficiently. Because certain code modules and data storage segments must reside by themselves in their own protected sectors, the wasted and unused memory space that occurs with large sectored and large block erase Flash memory devices can be greatly reduced. This increased memory space efficiency allows addi-tional code routines and data storage segments to be added while still maintaining thesame overall device density.23599A–DFLASH–11/05AT26DF161 [Preliminary]The AT26DF161 also offers a sophisticated method for protecting individual sectors against erroneous or malicious program and erase operations. By providing the ability to individually pro-tect and unprotect sectors, a system can unprotect a specific sector to modify its contents while keeping the remaining sectors of the memory array securely protected. This is useful in applica-tions where program code is patched or updated on a subroutine or module basis, or in applications where data storage segments need to be modified without running the risk of errant modifications to the program code segments.Specifically designed for use in 3-volt systems, the AT26DF161 supports read, program, and erase operations with a supply voltage range of 2.7V to 3.6V. No separate voltage is required for programming and erasing.2.Pin Descriptions and PinoutsTable 2-1.Pin DescriptionsSymbolName and FunctionAsserted StateTypeCS CHIP SELECT : Asserting the CS pin selects the device. When the CS pin is deasserted, thedevice will be deselected and normally be placed in standby mode (not Deep Power-Down mode), and the SO pin will be in a high-impedance state. When the device is deselected, data will not be accepted on the SI pin.A high-to-low transition on the CS pin is required to start an operation, and a low-to-high transition is required to end an operation. When ending an internally self-timed operation such as a program or erase cycle, the device will not enter the standby mode until the completion of the operation.Low InputSCK SERIAL CLOCK : This pin is used to provide a clock to the device and is used to control the flow of data to and from the device. Command, address, and input data present on the SI pin is always latched on the rising edge of SCK, while output data on the SO pin is always clocked out on the falling edge of SCK.InputSI SERIAL INPUT : The SI pin is used to shift data into the device. The SI pin is used for all data input including command and address sequences. Data on the SI pin is always latched on the rising edge of SCK.InputSO SERIAL OUTPUT : The SO pin is used to shift data out from the device. Data on the SO pin is always clocked out on the falling edge of SCK.OutputWP WRITE PROTECT : The WP pin controls the hardware locking feature of the device. Please refer to “Protection Commands and Features” on page 11 for more details on protection features and the WP pin.The WP pin is internally pulled-high and may be left floating if hardware controlled protection will not be used. However, it is recommended that the WP pin also be externally connected to V CC whenever possible.Low InputV CC DEVICE POWER SUPPLY : The V CC pin is used to supply the source voltage to the device.Operations at invalid V CC voltages may produce spurious results and should not be attempted.Power GNDGROUND : The ground reference for the power supply. GND should be connected to the system ground.Power33599A–DFLASH–11/05AT26DF161 [Preliminary]3.Block Diagram4.Memory ArrayTo provide the greatest flexibility, the memory array of the AT26DF161 can be erased in four lev-els of granularity including a full chip erase. In addition, the array has been divided into physical sectors of uniform size, of which each sector can be individually protected from program and erase operations. The size of the physical sectors is optimized for both code and data storage applications, allowing both code and data segments to reside in their own isolated regions. Fig-ure 4-1 on page 4 illustrates the breakdown of each erase level as well as the breakdown of each physical sector.Figure 2-1.8-SOIC Top ViewFigure 2-2.8-MLF Top View43599A–DFLASH–11/05AT26DF161 [Preliminary]Figure 4-1.Memory Architecture Diagram53599A–DFLASH–11/05AT26DF161 [Preliminary]5.Device OperationThe AT26DF161 is controlled by a set of instructions that are sent from a host controller, com-monly referred to as the SPI Master. The SPI Master communicates with the AT26DF161 via the SPI bus which is comprised of four signal lines: Chip Select (CS), Serial Clock (SCK), Serial Input (SI), and Serial Output (SO).The SPI protocol defines a total of four modes of operation (mode 0, 1, 2, or 3) with each mode differing in respect to the SCK polarity and phase and how the polarity and phase control the flow of data on the SPI bus. The AT26DF161 supports the two most common modes, SPI Modes 0 and 3. The only difference between SPI Modes 0 and 3 is the polarity of the SCK signal when in the inactive state (when the SPI Master is in standby mode and not transferring any data). With SPI Modes 0 and 3, data is always latched in on the rising edge of SCK and always output on the falling edge of SCK.Figure 5-1.SPI Mode 0 and 3mands and Addressingpin has been asserted, the SPI Master must then clock out a valid 8-bit opcode on the SPI bus.Following the opcode, instruction dependent information such as address and data bytes would then be clocked out by the SPI Master. All opcode, address, and data bytes are transferred with Opcodes not supported by the AT26DF161 will be ignored by the device and no operation will be started. The device will continue to ignore any data presented on the SI pin until the start of the next operation (CS pin being deasserted and then reasserted). In addition, if the CS pin is deas-serted before complete opcode and address information is sent to the device, then no operation will be performed and the device will simply return to the idle state and wait for the next operation.Addressing of the device requires a total of three bytes of information to be sent, representing address bits A23-A0. Since the upper address limit of the AT26DF161 memory array is 1FFFFFh, address bits A23-A21 are always ignored by the device.63599A–DFLASH–11/05AT26DF161 [Preliminary]Table 6-1.Command ListingCommandOpcodeAddress BytesDummy BytesData BytesRead CommandsRead Array0Bh 0000 1011311+Read Array (Low Frequency)03h0000 001131+Program and Erase CommandsBlock Erase (4-KBytes)20h 0010 0000300Block Erase (32-KBytes)52h 0101 0010300Block Erase (64-KBytes)D8h 1101 1000300Chip Erase60h 0110 0000000C7h 1100 0111000Byte/Page Program (1 to 256 Bytes)02h0000 001031+Protection CommandsWrite Enable 06h 0000 0110000Write Disable 04h 0000 0100000Protect Sector 36h 0011 0110300Unprotect Sector39h 0011 1001300Read Sector Protection Registers 3Ch0011 110031+Status Register CommandsRead Status Register 05h 0000 0101001+Write Status Register 01h0000 00011Miscellaneous CommandsRead Manufacturer and Device ID 9Fh 1001 111100 1 to 4Deep Power-DownB9h 1011 1001000Resume from Deep Power-DownABh1010 101173599A–DFLASH–11/05AT26DF161 [Preliminary]7.Read Commands7.1Read ArrayThe Read Array command can be used to sequentially read a continuous stream of data from the device by simply providing the SCK signal once the initial starting address has been speci-fied. The device incorporates an internal address counter that automatically increments on every clock cycle.Two opcodes, 0Bh and 03h, can be used for the Read Array command. The use of each opcode depends on the maximum SCK frequency that will be used to read data from the device. The 0Bh opcode can be used at any SCK frequency up to the maximum specified by f SCK . The 03h opcode can be used for lower frequency read operations up to the maximum specified by f RDLF .To perform the Read Array operation, the CS pin must first be asserted and the appropriate opcode (0Bh or 03h) must be clocked into the device. After the opcode has been clocked in, the three address bytes must be clocked in to specify the starting address location of the first byte to read within the memory array. If the 0Bh opcode is used, then one don’t care byte must also be clocked in after the three address bytes.After the three address bytes (and the one don’t care byte if using opcode 0Bh) have been clocked in, additional clock cycles will result in serial data being output on the SO pin. The data is always output with the MSB of a byte first. When the last byte (1FFFFFh) of the memory array has been read, the device will continue reading back at the beginning of the array (000000h). No delays will be incurred when wrapping around from the end of the array to the beginning of the array.ance state. The CS pin can be deasserted at any time and does not require that a full byte of data be read.Figure 7-1.Read Array – 0Bh OpcodeFigure 7-2.Read Array – 03h Opcode83599A–DFLASH–11/05AT26DF161 [Preliminary]8.Program and Erase Commands8.1Byte/Page ProgramThe Byte/Page Program command allows anywhere from a single byte of data to 256 bytes of data to be programmed into previously erased memory locations. An erased memory location is one that has all eight bits set to the logical “1” state (a byte value of FFh). Before a Byte/Page Program command can be started, the Write Enable command must have been previously issued to the device (see Write Enable command description) to set the Write Enable Latch (WEL) bit of the Status Register to a logical “1” state.To perform a Byte/Page Program command, an opcode of 02h must be clocked into the device followed by the three address bytes denoting the first byte location of the memory array to begin programming at. After the address bytes have been clocked in, data can then be clocked into the device and will be stored in an internal buffer.If the starting memory address denoted by A23-A0 does not fall on an even 256-byte page boundary (A7-A0 are not all 0), then special circumstances regarding which memory locations will be programmed will apply. In this situation, any data that is sent to the device that goes beyond the end of the page will wrap around back to the beginning of the same page. For exam-ple, if the starting address denoted by A23-A0 is 0000FEh, and three bytes of data are sent to the device, then the first two bytes of data will be programmed at addresses 0000FEh and 0000FFh while the last byte of data will be programmed at address 000000h. The remaining bytes in the page (addresses 000001h through 0000FDh) will be unaffected and will not change.In addition, if more than 256 bytes of data are sent to the device, then only the last 256 bytes sent will be latched into the internal buffer.When the CS pin is deasserted, the device will take the data stored in the internal buffer and pro-gram it into the appropriate memory array locations based on the starting address specified by A23-A0 and the number of complete data bytes sent to the device. If less than 256 bytes of data were sent to the device, then the remaining bytes within the page will not be altered. The pro-gramming of the data bytes is internally self-timed and should take place in a time of t PP .The three address bytes and at least one complete byte of data must be clocked into the device before the CS pin is deasserted; otherwise, the device will abort the operation and no data will be programmed into the memory array. In addition, if the address specified by A23-A0 points to a memory location within a sector that is in the protected state (see “Protect Sector” on page 12), then the Byte/Page Program command will not be executed, and the device will return to the idle state once the CS pin has been deasserted. The WEL bit in the Status Register will be reset back to the logical “0” state if the program cycle aborts due to an incomplete address being sent,an incomplete byte of data being sent, or because the memory location to be programmed is protected.While the device is programming, the Status Register can be read and will indicate that the device is busy. For faster throughput, it is recommended that the Status Register be polled rather than waiting the t PP time to determine if the data bytes have finished programming. At some point before the program cycle completes, the WEL bit in the Status Register will be reset back to the logical “0” state.93599A–DFLASH–11/05AT26DF161 [Preliminary]Figure 8-1.Byte ProgramFigure 8-2.Page Program8.2Block EraseA block of 4K-, 32K-, or 64K-bytes can be erased (all bits set to the logical “1” state) in a single operation by using one of three different opcodes for the Block Erase command. An opcode of 20h is used for a 4K-byte erase, an opcode of 52h is used for a 32K-byte erase, and an opcode of D8h is used for a 64K-byte erase. Before a Block Erase command can be started, the Write Enable command must have been previously issued to the device to set the WEL bit of the Sta-tus Register to a logical “1” state.52h, or D8h) must be clocked into the device. After the opcode has been clocked in, the three address bytes specifying an address within the 4K-, 32K-, or 64K-byte block to be erased must be clocked in. Any additional data clocked into the device will be ignored. When the CS pin is deasserted, the device will erase the appropriate block. The erasing of the block is internally self-timed and should take place in a time of t BLKE .Since the Block Erase command erases a region of bytes, the lower order address bits do not need to be decoded by the device. Therefore, for a 4K-byte erase, address bits A11-A0 will be ignored by the device and their values can be either a logical “1” or “0”. For a 32K-byte erase,address bits A14-A0 will be ignored, and for a 64K-byte erase, address bits A15-A0 will be ignored by the device. Despite the lower order address bits not being decoded by the device, the complete three address bytes must still be clocked into the device before the CS pin is deas-serted; otherwise, the device will abort the operation and no erase operation will be performed.103599A–DFLASH–11/05AT26DF161 [Preliminary]If the address specified by A23-A0 points to a memory location within a sector that is in the pro-tected state, then the Block Erase command will not be executed, and the device will return to The WEL bit in the Status Register will be reset back to the logical “0” state if the erase cycle aborts due to an incomplete address being sent or because a memory location within the region to be erased is protected.While the device is executing a successful erase cycle, the Status Register can be read and will indicate that the device is busy. For faster throughput, it is recommended that the Status Regis-ter be polled rather than waiting the t BLKE time to determine if the device has finished erasing. At some point before the erase cycle completes, the WEL bit in the Status Register will be reset back to the logical “0” state.Figure 8-3.Block Erase8.3Chip EraseThe entire memory array can be erased in a single operation by using the Chip Erase command.Before a Chip Erase command can be started, the Write Enable command must have been pre-viously issued to the device to set the WEL bit of the Status Register to a logical “1” state.Two opcodes, 60h and C7h, can be used for the Chip Erase command. There is no difference in device functionality when utilizing the two opcodes, so they can be used interchangeably. To perform a Chip Erase, one of the two opcodes (60h or C7h) must be clocked into the device.Since the entire memory array is to be erased, no address bytes need to be clocked into the device, and any data clocked in after the opcode will be ignored. When the CS pin is deasserted,the device will erase the entire memory array. The erasing of the device is internally self-timed and should take place in a time of t CHPE .wise, no erase will be performed. In addition, if any sector of the memory array is in the protected state, then the Chip Erase command will not be executed, and the device will return to the idle state once the CS pin has been deasserted. The WEL bit in the Status Register will be reset back to the logical “0” state if a sector is in the protected state.While the device is executing a successful erase cycle, the Status Register can be read and will indicate that the device is busy. For faster throughput, it is recommended that the Status Regis-ter be polled rather than waiting the t CHPE time to determine if the device has finished erasing. At some point before the erase cycle completes, the WEL bit in the Status Register will be reset back to the logical “0” state.AT26DF161 [Preliminary] Figure 8-4.Chip Erase9.Protection Commands and Features9.1Write EnableThe Write Enable command is used to set the Write Enable Latch (WEL) bit in the Status Regis-ter to a logical “1” state. The WEL bit must be set before a program, erase, Protect Sector,Unprotect Sector, or Write Status Register command can be executed. This makes the issuanceof these commands a two step process, thereby reducing the chances of a command beingaccidentally or erroneously executed. If the WEL bit in the Status Register is not set prior to theissuance of one of these commands, then the command will not be executed.must be clocked into the device. No address bytes need to be clocked into the device, and anythe Status Register will be set to a logical “1”. The complete opcode must be clocked into thestate of the WEL bit will not change.Figure 9-1.Write Enable9.2Write DisableThe Write Disable command is used to reset the Write Enable Latch (WEL) bit in the Status Reg-ister to the logical “0” state. With the WEL bit reset, all program, erase, Protect Sector, UnprotectSector, and Write Status Register commands will not be executed. The Write Disable commandis also used to exit the Sequential Program Mode. Other conditions can also cause the WEL bitto be reset; for more details, refer to the WEL bit section of the Status Register description onpage 18.must be clocked into the device. No address bytes need to be clocked into the device, and anythe Status Register will be reset to a logical “0”. The complete opcode must be clocked into thestate of the WEL bit will not change.Figure 9-2.Write Disable9.3Protect SectorEvery physical sector of the device has a corresponding single-bit Sector Protection Registerthat is used to control the software protection of a sector. Upon device power-up or after adevice reset, each Sector Protection Register will default to the logical “1” state indicating that allsectors are protected and cannot be programmed or erased.Issuing the Protect Sector command to a particular sector address will set the correspondingSector Protection Register to the logical “1” state. The following table outlines the two states ofthe Sector Protection Registers.Table 9-1.Sector Protection Register ValuesValue Sector Protection Status0Sector is unprotected and can be programmed and erased.1Sector is protected and cannot be programmed or erased. This is the default state.Before the Protect Sector command can be issued, the Write Enable command must have beenpreviously issued to set the WEL bit in the Status Register to a logical “1”. To issue the ProtectSector command, the CS pin must first be asserted and the opcode of 36h must be clocked intothe device followed by three address bytes designating any address within the sector to belocked. Any additional data clocked into the device will be ignored. When the CS pin is deas-serted, the Sector Protection Register corresponding to the physical sector addressed by A23-A0 will be set to the logical “1” state, and the sector itself will then be protected from programAT26DF161 [Preliminary] and erase operations. In addition, the WEL bit in the Status Register will be reset back to the log-ical “0” state.serted; otherwise, the device will abort the operation, the state of the Sector Protection Registerwill be unchanged, and the WEL bit in the Status Register will be reset to a logical “0”.As a safeguard against accidental or erroneous protecting or unprotecting of sectors, the SectorProtection Registers can themselves be locked from updates by using the SPRL (Sector Protec-tion Registers Locked) bit of the Status Register (please refer to “Status Register Commands”on page 16 for more details). If the Sector Protection Registers are locked, then any attempts toissue the Protect Sector command will be ignored, and the device will reset the WEL bit in thedeasserted.Figure 9-3.Protect Sector9.4Unprotect SectorIssuing the Unprotect Sector command to a particular sector address will reset the correspond-ing Sector Protection Register to the logical “0” state (see Table 9-1 on page 12 for SectorProtection Register values). Every physical sector of the device has a corresponding single-bitSector Protection Register that is used to control the software protection of a sector.Before the Unprotect Sector command can be issued, the Write Enable command must havebeen previously issued to set the WEL bit in the Status Register to a logical “1”. To issue theUnprotect Sector command, the CS pin must first be asserted and the opcode of 39h must beclocked into the device. After the opcode has been clocked in, the three address bytes designat-ing any address within the sector to be unlocked must be clocked in. Any additional data clockedtor Protection Register corresponding to the sector addressed by A23-A0 will be reset to thelogical “0” state, and the sector itself will be unprotected. In addition, the WEL bit in the StatusRegister will be reset back to the logical “0” state.serted; otherwise, the device will abort the operation, the state of the Sector Protection Registerwill be unchanged, and the WEL bit in the Status Register will be reset to a logical “0”.As a safeguard against accidental or erroneous locking or unlocking of sectors, the Sector Pro-tection Registers can themselves be locked from updates by using the SPRL (Sector ProtectionRegisters Locked) bit of the Status Register (please refer to “Status Register Commands” onpage 16 for more details). If the Sector Protection Registers are locked, then any attempts toissue the Unprotect Sector command will be ignored, and the device will reset the WEL bit in theStatus Register back to a logical “0” and return to the idle state once the CS pin has beendeasserted.Figure 9-4.Unprotect Sector9.5Read Sector Protection RegistersThe Sector Protection Registers can be read to determine the current software protection statusof each sector. Reading the Sector Protection Registers, however, will not determine the statusTo read the Sector Protection Register for a particular sector, the CS pin must first be assertedand the opcode of 3Ch must be clocked in. Once the opcode has been clocked in, three addressbytes designating any address within the sector must be clocked in. After the last address bytehas been clocked in, the device will begin outputting data on the SO pin during every subse-quent clock cycle. The data being output will be a repeating byte of either FFh or 00h to denotethe value of the appropriate Sector Protection RegisterTable 9-2.Read Sector Protection Register – Output DataOutput Data Sector Protection Register Value00h Sector Protection Register value is 0 (sector is unprotected).FFh Sector Protection Register value is 1 (sector is protected).ance state. The CS pin can be deasserted at any time and does not require that a full byte ofdata be read.In addition to reading the individual Sector Protection Registers, the Software Protection Status(SWP) bit in the Status Register can be read to determine if all, some, or none of the sectors aresoftware protected (please refer to “Status Register Commands” on page 16 for more details).AT26DF161 [Preliminary]Figure 9-5.Read Sector Protection Register9.6tus of the memory array. Instead, the WP pin, in conjunction with the SPRL (Sector Protection Registers Locked) bit in the Status Register, is used to control the hardware locking mechanism of the device. For hardware locking to be active, two conditions must be met-the WP pin must be asserted and the SPRL bit must be in the logical “1” state.When hardware locking is active, the Sector Protection Registers are locked and the SPRL bit itself is also locked. Therefore, sectors that are protected will be locked in the protected state,and sectors that are unprotected will be locked in the unprotected state. These states cannot be changed as long as hardware locking is active, so the Protect Sector, Unprotect Sector, and Write Status Register commands will be ignored. In order to modify the protection status of a reset back to the logical “0” state.the only way to reset the bit back to the logical “0” state is to power-cycle or reset the device.This allows a system to power-up with all sectors software protected but not hardware locked.Therefore, sectors can be unprotected and protected as needed and then hardware locked at a later time by simply setting the SPRL bit in the Status Register.When the WP pin is deasserted, or if the WP pin is permanently connected to V CC , the SPRL bit in the Status Register can still be set to a logical “1” to lock the Sector Protection Registers. This provides a software locking ability to prevent erroneous Protect Sector or Unprotect Sector com-mands from being processed.The tables below detail the various protection and locking states of the device.Note:1.“n” represents a sector numberTable 9-3.Software ProtectionWP Sector Protection Registern (1)Sector n (1)X(Don't Care)0Unprotected 1Protected。

FDMM煤磨收尘说明

目录一、产品简介 2二、工作原理 2三、性能特点 2四、袋收尘的控制 4五、型号说明 5六、选型参数及选型原则 5七、技术性能表 6八、供货范围10九、售后服务10十、运行与维护注意事项10 十一、设备外形及基础图11FDMM系列煤粉袋式收尘器1、FDMM型系列煤粉袋式收尘器是合肥丰德科技有限公司在消化吸收国内外同类产品最新技术的基础上研制开发的新一代防爆型高效环保袋式收尘器。

该设备采用高压大流量脉冲阀和逐条滤袋脉冲清灰技术,除尘效率高达99.99%,其技术性能具有国内领先水平,该产品被广泛应用于各行各业的煤粉制备系统。

本公司以先进的结构设计和优良的制造工艺,确保产品质量上乘、换袋方便、设备能长期高效运行,收尘率高达99.99%以上。

2、FDMM型煤粉袋式收尘器采用负压操作、外滤形式、高压大流量脉冲加文氏管诱导式脉喷清灰,同时具有惯性除尘和袋式除尘两种功能。

2.1除尘含尘气体进入预收尘室,粗颗粒粉尘在撞击导流板和重力作用下落入灰斗,实现惯性除尘;而含有较细粉尘的气体则流入装有滤袋的过滤室,经滤袋过滤后的洁净气体经过净气室、排风道、由风机排出,滤袋外的积尘经脉喷清灰落入灰斗。

2.2清灰本设备采用高压大流量脉冲加文氏管诱导式反吹风清灰,通过对逐条滤袋内部吹入大流量脉动气流,既可将滤袋外附着粉尘抖落,又可由里向外吹透滤袋,清灰效率高,产品性能稳定。

3、3.1煤粉特性介绍煤粉在输送、粉磨与收尘过程中的主要危害是易燃易爆,高浓度煤粉在输送、收尘过程中燃烧和爆炸的危险性更大,而引起煤粉燃烧的主要原因常见于煤粉的自燃及外来火源。

煤粉的自燃主要决于以下几个因素:环境温度、煤粉浓度、煤粉细度、煤粉气体中的含氧量以及静电起火。

水泥厂煤粉制备系统烟气具有以下一些特征:3.1.1入口浓度高。

以往采用二级收尘时煤粉收尘系统入口浓度一般控制在60g/Nm3以下,而采用一级收尘时,其收尘浓度可高达1000g/Nm3以上,处于煤粉的可燃与爆炸范围(国内外资料表明,煤粉浓度的可燃与爆炸范围为40~2000g/Nm3)。

PSOBB全道具代码中文版

000D02,妮之爪

000D03,PHOENIX CLAW灼炎鳳牙

000E00,双头剑

000E01,男用双切

000E02,双烙印

000F00,勇者之拳

000F01,愤怒之拳

000F02,上帝之手

000F03,索尼克拳套

001000,大蛇腭

001001,腭刀1975

000A01,手杖

000A02,权杖

000A03,球杖

000A04,拉科尼姆金属杖

000A05,金刚石杖

000A06,业障石杖

000A07,LOLIPOP棒棒糖

000B00,[长杖]

000B01,[魔杖]

000B02,[魔息杖]

000B03,[魔击杖]

000B04,战斗杖

000B05,勇者之锤

00A200,棕狂熊之爪

00A201,黄狂熊之爪

00A202,紫狂熊之爪

00A300,宝石枪

00A400,玫瑰之恋

00A500,S武 双手剑

00A600,S武 发射器

00A700,S武 卡片

00A800,S武 拳套

00A900,S武 斧头

00AA00,狂信者

00AB00,银剑之剑

001402,L&K38 COMBATコンバット

001500,火焰喷射器

001501,BURNING VISIT强化火焰喷射器バーニングビ

001600,秋子婶婶的平底锅

001700,混沌魔法师之杖

001800,西诺兽之剑

001900,合体怪之剑

001A00,剑魔之剑

温湿度模块 AM2001 AMT2001 产品手册说明书

温湿度模块AM2001/AMT2001 产品手册更多详情请登陆:一、产品概述AM2001/AMT2001是湿敏电容型温湿度传感器,其中AM2001是单湿型,AMT2001是温湿度一体型传感器;传感器信号采用模拟电压输出方式;本模块具有精度高,可靠性高,一致性好,且已带温度补偿,确保长期稳定性好,使用方便及价格低廉等特点,尤其适合对质量、成本要求比较苛刻的企业使用图1实物图图2外形尺寸(单位:mm)二、应用范围暖通空调、加湿器、除湿机、通迅、大气环境监测、工业过程控制、农业、测量仪表等应用领域。

三、产品亮点低功耗,小体积、带温度补偿、单片机校准线性输出、使用方便、成本低、完全互换、超长的信号传输距离、精确校准。

四、产品选型区别仅仅是增加了温度,其他功能一样,此后不再重复说明。

五、接口定义5.1 引脚分配表1:引脚分配图3:引脚分配图5.2 电源引脚(VDD GND)该模块的供电电压范围为4.5V - 5.5V,建议供电电压为5.0V。

5.3 电压输出信号线(Hout)湿度信号从该信号线以电压的形式输出,电压输出范围为0-3V,具体湿度与电压关系请参照电压与湿度特性表(表6)。

5.4 温度输出信号线(Tout)温度输出有两种选择:第一种:模拟信号输出.所接传感器为LM35,测温范围为0-80℃,+10.0mv/℃线性刻度系数,0℃时输出0.0V;连接方式为图4中的第3种接线方式;第二种:温度传感器为10K NTC B.3435热敏电阻而非模拟信号输出,用户需另加读取电路。

特殊注意:客户在购买本产品时,须注明温度传感器的类型,如接NTC10K热敏电阻须说明连接方式;如无说明,则默认为LM35模拟型温度传感器,按图4中的第3种连接方式,输出0-0.8V的电压信号。

客户如特殊要求请注明或在线咨询。

5.5温度传感器接线方式示意图图4:温度接线方式示意图六、传感器性能6.1 相对湿度表2:相对湿度性能表[1] 此精度为出厂时检验时,传感器在25℃和5V,条件下测试的精度指标,其不包括迟滞和非线性,且只适合非冷凝环境。

DF005M_08中文资料

DF005M thru DF10MVishay General SemiconductorDocument Number: 88571For technical questions within your region, please contact one of the following:Miniature Glass Passivated Single-Phase Bridge RectifiersFEATURES•UL recognition, file number E54214 •Ideal for printed circuit boards•Applicable for automative insertion•High surge current capability•Solder dip 260 °C, 40 s•Component in accordance to RoH S 2002/95/EC and WEEE 2002/96/EC TYPICAL APPLICATIONSGeneral purpose use in ac-to-dc bridge full wave rectification for SMPS, lighting ballaster, adapter,battery charger, home appliances, office equipment,and telecommunication applications.MECHANICAL DATA Case: DFMEpoxy meets UL 94V-0 flammability ratingTerminals: Matte tin plated leads, solderable per J-STD-002 and JESD22-B102E3 suffix for consumer grade, meets JESD 201 class 1A whisker testPolarity:As marked on bodyPRIMARY CHARACTERISTICSI F(AV) 1 A V RRM 50 V to 1000 VI FSM 50 A I R 5 µA V F 1.1 V T J max.150 °C~~MAXIMUM RATINGS (T A = 25°C unless otherwise noted)PARAME TER SYMBOL DF005M DF01M DF02M DF04M DF06M DF08M DF10M UNIDevice marking codeDF005 DF01 DF02 DF04 DF06 DF08 DF10Maximum repetitive peak reverse voltage V RRM 50 100 200 400 600 800 1000 V Maximum RMS voltage V RMS 35 70 140 280 420 560 700 VMaximum DC blocking voltageV DC50 100 200 400 600 800 1000 VMaximum average forward output rectified current at T A = 40 °CI F(AV) 1.0 APeak forward surge current singlesine-wave superimposed on rated load I FSM 50 A Rating for fusing (t < 8.3 ms) I 2t 10 A 2s Operating junction and storage temperature rangeT J , T STG- 55 to + 150°C元器件交易网DF005M thru DF10MVishay General Semiconductor For technical questions within your region, please contact one of the following:Document Number: 88571Note:(1) Thermal resistance from junction to ambient and from junction to lead mounted on P.C.B. with 0.5 x 0.5" (13 x 13 mm) copper padsRATINGS AND CHARACTERISTICS CURVES (T A = 25°C unless otherwise noted)ELECTRICAL CHARACTERISTICS (T A = 25°C unless otherwise noted)PARAME TER TES TCONDI TIONS SYMBOL DF005M DF01M DF02M DF04M DF06M DF08M DF10M UNI TMaximuminstantaneous forward voltage drop per diode 1.0 AVF 1.1V Maximumreverse current at rated DC blocking voltage per diode T A = 25 °C T A = 125 °CI R5.0 500µATypical junctioncapacitance per diode4.0 V , 1 MHzC J 25 pFTHERMAL CHARACTERISTICS (T A = 25°C unless otherwise noted)PARAME TERSYMBOL DF005M DF01M DF02M DF04M DF06M DF08M DF10M UNI TTypical thermal resistance (1)R θJA R θJL40 15°C/W ORDERING INFORMATION (Example)PREFERRED P/N UNIT WEIGHT (g)PREFERRED PACKAGE CODEBASE QUANTITYDELIVERY MODEDF06M-E3/450.4164550TubeFigure 1. Derating Curve Output Rectified CurrentFigure 2. Maximum Non-Repetitive Peak Forward SurgeCurrent Per Diode元器件交易网DF005M thru DF10MVishay General SemiconductorDocument Number: 88571For technical questions within your region, please contact one of the following:PACKAGE OUTLINE DIMENSIONS in inches (millimeters)Figure 3. Typical Forward Characteristics Per Diode Figure 4. Typical Reverse Leakage Characteristics Per DiodeFigure 5. Typical Junction Capacitance Per DiodeFigure6. Typical Transient Thermal Impedance元器件交易网Disclaimer Legal Disclaimer NoticeVishayAll product specifications and data are subject to change without notice.Vishay Intertechnology, Inc., its affiliates, agents, and employees, and all persons acting on its or their behalf (collectively, “Vishay”), disclaim any and all liability for any errors, inaccuracies or incompleteness contained herein or in any other disclosure relating to any product.Vishay disclaims any and all liability arising out of the use or application of any product described herein or of any information provided herein to the maximum extent permitted by law. The product specifications do not expand or otherwise modify Vishay’s terms and conditions of purchase, including but not limited to the warranty expressed therein, which apply to these products.No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted by this document or by any conduct of Vishay.The products shown herein are not designed for use in medical, life-saving, or life-sustaining applications unless otherwise expressly indicated. Customers using or selling Vishay products not expressly indicated for use in such applications do so entirely at their own risk and agree to fully indemnify Vishay for any damages arising or resulting from such use or sale. Please contact authorized Vishay personnel to obtain written terms and conditions regarding products designed for such applications.Product names and markings noted herein may be trademarks of their respective owners.元器件交易网Document Number: 。

DF无线数据收发模块

用途DF无线数据收发模块无线数据传输广泛地运用在车辆监控、遥控、遥测、小型无线网络、无线抄表、门禁系统、小区传呼、工业数据采集系统、无线标签、身份识别、非接触RF智能卡、小型无线数据终端、安全防火系统、无线遥控系统、生物信号采集、水文气象监控、机器人控制、无线232数据通信、无线485/422数据通信、数字音频、数字图像传输等领域中。

这是DF发射模块,体积:19x19x8毫米,右边是等效的电路原理图主要技术指标:1。

通讯方式:调幅AM2。

工作频率:315MHZ (可以提供433MHZ,购货时请特别注明)3。

频率稳定度:±75KHZ4。

发射功率:≤500MW5。

静态电流:≤0.1UA6。

发射电流:3~50MA7。

工作电压:DC 3~12V315MHZ发射模块 8元一个433MHZ发射模块 8元一个DF数据发射模块的工作频率为315M,采用声表谐振器SAW稳频,频率稳定度极高,当环境温度在-25~+85度之间变化时,频飘仅为3ppm/度。

特别适合多发一收无线遥控及数据传输系统。

声表谐振器的频率稳定度仅次于晶体,而一般的LC振荡器频率稳定度及一致性较差,即使采用高品质微调电容,温差变化及振动也很难保证已调好的频点不会发生偏移。

DF发射模块未设编码集成电路,而增加了一只数据调制三极管Q1,这种结构使得它可以方便地和其它固定编码电路、滚动码电路及单片机接口,而不必考虑编码电路的工作电压和输出幅度信号值的大小。

比如用PT2262等编码集成电路配接时,直接将它们的数据输出端第17脚接至DF数据模块的输入端即可。

DF数据模块具有较宽的工作电压范围3~12V,当电压变化时发射频率基本不变,和发射模块配套的接收模块无需任何调整就能稳定地接收。

当发射电压为3V时,空旷地传输距离约20~50米,发射功率较小,当电压5V时约100~200米,当电压9V时约300~500米,当发射电压为12V时,为最佳工作电压,具有较好的发射效果,发射电流约60毫安,空旷地传输距离700~800米,发射功率约500毫瓦。

测井符号

测井解释常用参数的中英文名称参数名称/符号英文名称中文名称Por / Ф Porosity 孔隙度Port / Фt total porosity 总孔隙度Pore / Фe effective porosity 有效孔隙度Perm / K Permeability 渗透率Sw Water saturation 含水饱和度Swxo flushed zone water saturation 冲洗带含水饱和度Swirr / SIRR irredusiable water saturation 束缚水饱和度So Oil saturation 含油饱和度Sor residual oil saturation 残余油饱和度Vsh / Sh Shale Volume 泥质含量Rw Formation water resistivity 地层水电阻率Rm mud resistivity 泥浆电阻率Rmf Mud filtrate resistivity 泥浆滤液电阻率M cementation exponent 胶结指数N saturation exponent 饱和度指数F formation factor 地层因数BHT borehole bottom temperature 井底温度地层因素\岩性系数和胶结系数岩性系数:岩样实测渗透率与理论渗透率之比.m 为地层胶结指数, 又称地层因素, 是反映地层胶结情况、孔隙大小尤其是孔隙连通情况的一个指标。

m 这个参数的地质意义与孔喉张开度有关, 还反映了地层导电截面大小的变化.地层因素(地层因数):纯水层电阻率与地层水电阻率之比.纯岩石电阻率?与地层的孔隙度和孔隙结构有关,一般用于阿尔奇公式,可用于计算纯岩石电阻率,进行地层评价,它一般和孔隙度呈负线性关系.岩性系数和胶结系数都是阿尔奇公式中的系数,是表示孔隙结构的量,是各种因素的综合反映,两者之间为一个变大时,另一个就变小.胶结系数随岩石变细和胶结程度增加而变大,他们的数值一般通过岩心确定.测井技术基本术语什么是测井:测井是记录钻入地幔的一口井中岩石或流体混合物不同的物理、化学、电子或其他性质的过程。

FAN7888MX;FAN7888M;中文规格书,Datasheet资料

FAN7888 — 3 Half-Bridge Gate-Drive IC3 Half-Bridge Gate-Drive ICFeaturesFloating Channel for Bootstrap Operation to +200V Typically 350mA/650mA Sourcing/Sinking Current Driving Capability for All Channels 3 Half-Bridge Gate DriverExtended Allowable Negative V S Swing to -9.8V for Signal Propagation at V BS =15VMatched Propagation Delay Time Maximum 50ns 3.3V and 5V Input Logic CompatibleBuilt-in Shoot-Through Prevention Circuit for All Channels with Typically 270ns Dead TimeBuilt-in Common Mode dv/dt Noise Canceling CircuitBuilt-in UVLO Functions for All ChannelsApplications3-Phase Motor Inverter DriverDescriptionThe FAN7888 is a monolithic three half-bridge gate-drive IC designed for high-voltage, high-speed driving MOS-FETs and IGBTs operating up to +200V.Fairchild’s high-voltage process and common-mode noise canceling technique provide stable operation of high-side drivers under high-dv/dt noise circumstances.An advanced level-shift circuit allows high-side gate driver operation up to V S = -9.8V (typical) for V BS =15V. The UVLO circuits prevent malfunction when V DD and V BS are lower than the specified threshold voltage. Output drivers typically source/sink 350mA/650mA,respectively, which is suitable for three-phase half-bridge applications in motor drive systems.Ordering InformationAll packages are lead free per JEDEC: J-STD-020B standard.20-SOICPart NumberPackageOperating Temperature RangePacking MethodFAN7888M 20-SOIC-40°C to +125°CTube FAN7888MXTape & ReelFAN7888 — 3 Half-Bridge Gate-Drive ICFigure 1. 3-Phase BLDC Motor Drive ApplicationInternal Block DiagramUVWUU ULVU VLWU WLQ4Q6Q2Q1Q3Q5Q1Q3Q5Q4Q6Q23-Phase InverterGND LO3LIN1V DD V S1HO1V B1HIN1V S2HO2V B2V S3HO3V B3HIN2HIN3LIN2LIN3LO2LO120191817161514131212345678910V S1V S3V S2V S2V S3V S1FAN78883-PhaseBLDC Motor Controller I UI VI W11FAN7888 Rev.00UVLOR R SQDELAYDRIVERDRIVERV Phase DriverU Phase DriverLO2V S2HO2V B2HO3V B3UHINULINV DDVHIN V DD VDD_UVLOHIN1HIN2HIN3LIN1LIN2LIN3VLINSCHMITT TRIGGER INPUTSHOOT-THOUGH PREVENTIONCONTROL LOGICUVLOVDDV DDLO1GNDV S1HO1V B1NOISE CANCELLERPULSE GENERATORFAN7888 — 3 Half-Bridge Gate-Drive ICFigure 3. Pin Configuration (Top View)Pin DefinitionsPin #NameDescription1HIN1Logic input 1 for high-side gate 1 driver 2LIN1Logic input 1 for low-side gate 1 driver 3HIN2Logic input 2 for high-side gate 2 driver 4LIN2Logic input 2 for low-side gate 2 driver 5HIN3Logic input 3 for high-side gate 3 driver 6LIN3Logic input 3 for low-side gate 3 driver 7LO3Low-side gate driver 3 output8V S3High-side driver 3 floating supply offset voltage 9HO3High-side driver 3 gate driver output 10V B3High-side driver 3 floating supply voltage 11GND Ground12V DD Logic and all low-side gate drivers power supply voltage 13LO2Low-side gate driver 2 output14V S2High-side driver 2 floating supply offset voltage 15HO2High-side driver 2 gate driver output 16V B2High-side driver 2 floating supply voltage 17LO1Low-side gate driver 1 outputGNDLO3FAN7888V DD V S1HIN2HIN3LIN2LIN3LO2LO11817161514131211345678910V S2HO2V B2V S3HO3V B3FAN7888 Rev.00FAN7888 — 3 Half-Bridge Gate-Drive ICAbsolute Maximum RatingsStresses exceeding the absolute maximum ratings may damage the device. The device may not function or be opera-ble above the recommended operating conditions and stressing the parts to these levels is not recommended. In addi-tion, extended exposure to stresses above the recommended operating conditions may affect device reliability. The absolute maximum ratings are stress ratings only. T A =25°C, unless otherwise specified.Notes:1. Mounted on 76.2 x 114.3 x 1.6mm PCB (FR-4 glass epoxy material).2. Refer to the following standards:JESD51-2: Integral circuits thermal test method environmental conditions - natural convection JESD51-3: Low effective thermal conductivity test board for leaded surface-mount packages.3. Do not exceed P D under any circumstances.Recommended Operating ConditionsThe Recommended Operating Conditions table defines the conditions for actual device operation. Recommended operating conditions are specified to ensure optimal performance to the datasheet specifications. Fairchild does not recommend exceeding them or designing to Absolute Maximum Ratings.SymbolParameterMin.Max.UnitV B High-side Floating Supply Voltage of V B1,2,3-0.3225.0V V S High-side Floating Supply Offset Voltage of V S1,2,3V B1,2,3-25V B1,2,3+0.3V V HO1,2,3High-side Floating Output Voltage V S1,2,3-0.3V B1,2,3+0.3V V DD Low-side and Logic-fixed Supply Voltage -0.325.0V V LO1,2,3Low-side Output Voltage-0.3V DD +0.3V V IN Logic Input Voltage (HIN1,2,3 and LIN1,2,3)-0.3V DD +0.3V dV S /dt Allowable Offset Voltage Slew Rate 50V/ns P D Power Dissipation (1)(2)(3)1.8W θJA Thermal Resistance, Junction-to-ambient 80 °C/W T J Junction Temperature +150°C T SStorage Temperature-55+150°CSymbolParameterMin.Max.UnitV B1,2,3High-side Floating Supply Voltage V S1,2,3+10V S1,2,3+20V V S1,2,3High-side Floating Supply Offset Voltage 6-V DD 200V V DD Supply Voltage1020V V HO1,2,3High-side Output Voltage V S1,2,3 V B1,2,3V V LO1,2,3Low-side Output VoltageGND V DD V V IN Logic Input Voltage (HIN1,2,3 and LIN1,2,3)GND V DD V T AAmbient Temperature-40+125°CNote:4. This parameter is guaranteed by design.BOOTSTRAPPED POWER SUPPLY SECTION I QBS1,2,3Quiescent V BS Supply Current for each ChannelV HIN1,2,3=0V or 5V 50120µA I PBS1,2,3Operating V BS Supply Current for each Channelf HIN1,2,3=20kHz, rms Value 400800µA V BSUV+V BS Supply Under-Voltage Positive-going ThresholdV DD =15V, V BS =Sweep7.28.29.0V V BSUV-V BS Supply Under-Voltage Negative-goingThresholdV DD =15V, V BS =Sweep6.87.88.5V V BSHYS V BS Supply Under-Voltage Lockout HysteresisV DD =15V, V BS =Sweep 0.4V I LK Offset Supply Leakage Current V B1,2,3=V S1.2.3=200V10µA GATE DRIVER OUTPUT SECTIONV OH High-level Output Voltage, V BIAS -V O I O =20mA 1.0V V OL Low-level Output Voltage, V OI O =20mA0.6V I O+Output HIGH Short-circuit Pulsed Current (4)V O =0V, V IN =5V with PW<10µs 250350mA I O-Output LOW Short-circuit Pulsed Current (4)V O =15V, V IN =0V with PW<10µs 500650mAV SAllowable Negative V S Pin Voltage for IN Signal Propagation to H O -9.8-7.0VLOGIC INPUT SECTION (HIN, LIN)V IH Logic "1" Input Voltage 2.5V V IL Logic "0" Input Voltage 1.0V I IN+Logic "1" Input Bias Current V IN =5V 2550µA I IN-Logic "0" Input Bias Current (4)V IN =0V2.0µA R IN Input Pull-down Resistance100200300K ΩFigure 4. Turn-on Propagation Delay vs. Temp.Figure 5. Turn-off Propagation Delay vs. Temp.Figure 6. Turn-on Rise Time vs. Temp.Figure 7. Turn-off Fall Time vs. Temp.-40-20020406080100120020406080100120t R [n s ]Temperature [°C]-40-20020406080100120020406080100t F [n s ]Temperature [°C]1020304050M T 1 [n s ]1020304050M T 2 [n s ]Figure 10. Dead Time vs. Temp.Figure 11. Dead-Time Matching vs. Temp.Figure 12. Quiescent V DD Supply Currentvs. Temp.Figure 13. Quiescent V BS Supply Currentvs. Temp.-40-20020406080100120050100150200250300350I Q D D [μA ]Temperature [°C]-40-20020406080100120020*********120I Q B S [μA ]Temperature [°C]2004006008001000I P D D [μA ]2004006008001000I P B S [μA ]Figure 16. V DD UVLO+ vs. Temp.Figure 17. V DD UVLO- vs. Temp.Figure 18. V BS UVLO+ vs. Temp.Figure 19. V BS UVLO- vs. Temp.-40-200204060801001207.07.58.08.59.0V B S U V + [V ]Temperature [°C]-40-200204060801001207.07.58.08.59.0V B S U V - [V ]Temperature [°C]0.20.40.60.81.0V O H [V ]0.150.300.450.60V O L [V ]Figure 22. Logic High Input Voltage vs. Temp.Figure 23. Logic Low Input Voltage vs. Temp.Figure 24. Logic Input High Bias Current vs. Temp.Figure 25. Allowable Negative V S Voltage vs. Temp.-40-2002040608010012001020304050I I N + [μA ]Temperature [°C]-40-20020406080100120-12-11-10-9-8-7V S [V ]Temperature [°C]100200300400500R I N [k Ω]分销商库存信息:FAIRCHILDFAN7888MX FAN7888M。

ABB 系统 pro M 编程 新的零序流Protection 电流保护设备说明书

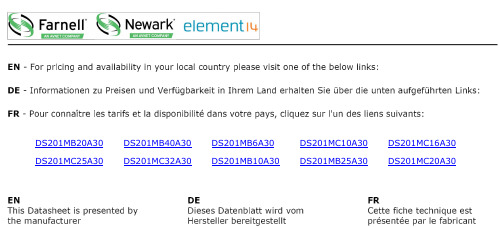

DS201MB20A30DS201MB40A30DS201MB6A30DS201MC10A30DS201MC16A30 DS201MC25A30DS201MC32A30DS201MB10A30DS201MB25A30DS201MC20A30Like all electromechanical residual current devices, these new products ensure protection against earth fault currents,Clear indications to identify and react to any event The signalling of the internal contact position allows anA project that supports the safety and quality of the entire A special adhesive label on the lateral side of the new DS201/DS202C residual current circuit-breakers with overcurrent technology appliedof the entire the new DS201/h overcurrent logy applied8 chapter title | ABB brochure type 8Technical data1P+N DS201 RCBO1P+N DS201 RCBO Standard IEC/EN 61009Nr. of poles 1P+N Rated voltage Un230V Working voltage range for test button 110...253 V Rated frequency50/60HzRated residual breaking capacity I D m4,5 kA (DS201 L), 6 kA (DS201 and DS201 M)Rated breaking capacity according to IEC/EN 60947-2 @230 V AC - ultimate Icu 6 kA (DS201 L), 10 kA (DS201 and DS201 M)Rated breaking capacity according to IEC/EN 60947-2 @230 V AC - service Ics 4,5 kA (DS201 L), 6 kA (DS201), 7,5 kA (DS201 M)Rated impulse withstand voltage (1,2/50) Uimp 4kV Dielectric test voltage at ind. freq. for 1 min.2,5kVSurge current resistance (wave 8/20)250A (3000A APR versions)Top Terminals failsafe bi-directional cylinder-lift terminal Bottom Terminalsfailsafe bi-directional cylinder-lift terminal Terminals size top/bottom for cable 25/25 mm 2Terminals size top/bottom for busbar 10/10 mm 2Tightening torque top/bottom 2,8 NmFlag indications Differential trip indicator (blue)Contact position indicator (green/red)Electrical life 10000Mechanical life 20000Protection degree IP4X (housing)IP2X (terminals)Ambient temperature -25...+55 °C Storage temperature -40...+70 °CMountingon DIN rail 60715 (35 mm)Dimensions (HxDxW)85x69x35 mmDS201 - B characteristicDS201 - 6 kADS201 - 6 kAIcn [kA]66Type AC A In [A] 6...40 6 (40)I D n [A]0,03-0,1-0,30,01(1)-0,03-0,1-0,3DS201 - C characteristicIcn [kA]666Type AC A APR In [A] 6 (40)2 (40)6...40I D n [A]0,03-0,1-0,3-10,01(1)-0,03-0,1(2)-0,30,03-0,1-0,3DS201 L - C characteristicDS201 L - 4,5 kADS201 - 6 kAIcn [kA]4,54,54,5Type AC A APR In [A] 6...32 6 (32)6...32I D n [A]0,03-0,30,01(4)-0,03-0,30,03DS201 M - B characteristicDS201 M - 10 kADS201 M - 10 kAIcn [kA]1010Type AC A In [A] 6...40 6 (40)I D n [A]0,03-0,1-0,30,01(3)-0,03-0,1-0,3DS201 M - C characteristicIcn [kA]101010Type AC A APR In [A] 6...40 4 (40)6 (40)I D n [A]0,03-0,1-0,30,01(3)-0,03-0,1(2)-0,3(2)0,03-0,1-0,3DS201 - K characteristicIcn [kA]6Type A In [A] 1...40I D n [A]0,01(1)-0,03-0,3(1) Available only in 10-13-16A rated current.(2)Available with rated current from 6A.(3) Available only in 10-16A rated current. (4)Available only in 6-10-16A rated current.Technical data2P DS202C RCBO2P DS202C RCBOStandard IEC/EN 61009Nr. of poles 2PRated voltage Un230VWorking voltage range for test button110...253 VRated frequency50/60HzRated residual breaking capacity I D m 6 kARated breaking capacity according to IEC/EN 60947-2 @230 V AC - ultimate Icu10 kA (DS202C and DS202C M)Rated breaking capacity according to IEC/EN 60947-2 @230 V AC - service Ics 6 kA (DS202C), 7,5 kA (DS202C M) Rated impulse withstand voltage (1,2/50) Uimp4kVDielectric test voltage at ind. freq. for 1 min.2,5kVSurge current resistance (wave 8/20)250A (3000A APR versions)Top Terminals failsafe bi-directional cylinder-lift terminal Bottom Terminals failsafe bi-directional cylinder-lift terminal Terminals size top/bottom for cable25/25 mm2Terminals size top/bottom for busbar10/10 mm2Tightening torque top/bottom2,8 NmFlag indications Differential trip indicator (blue)Contact position indicator (green/red) Electrical life10000Mechanical life20000Protection degree IP4X (housing)IP2X (terminals)Ambient temperature-25...+55 °CStorage temperature-40...+70 °CMounting on DIN rail 60715 (35 mm) Dimensions (HxDxW)85x69x35 mmDS202C M - B characteristic DS202C M - C characteristic DS202C M - 10 kA DS202C M - 10 kAIcn [kA]1010 Type A APRIn [A] 6...32 6 (32)I D n [A]0,01(1)-0,03-0,30,03-0,3Icn [kA]1010 Type A APR In [A] 6...32 6 (32)I D n [A]0,01(5)-0,03-0,30,03DS202C - B characteristic DS202C - C characteristic DS202C - 6 kA DS202C - 6 kAIcn [kA]6 Type AIn [A] 6 (32)I D n [A]0,03-0,3Icn [kA]6 Type AIn [A] 6 (32)I D n [A]0,03-0,3(1) Available only in 10-13-16A rated current.(5) Available only in 10-16A rated current.ABB brochure type | chapter title 9 9ABB brochure type | chapter title 27 27DS201 and DS202C Overall dimensions Dimensions in mmDS201 - DS202CDS2C-CMS2C-S/H6R - S2C-H6R Auxiliary components 4543735867853517,585 8,8 6,84445 69S 2C-H..L S 2C-S/H 6 RS 2C-H 6 R 35,5 15,4 15,5 30,525,455121 89 45 80,5 50,3F2C-A - S2C-UA - S2C-OVP 6,8 S 2C-A S 2C-A 45 85 8517,4 44 69 74 S2C-EST 17,516459,866,6Contact us 2CSC4224B23-8/2009 - 1.500 P z . - C A L .ABB SACEA division of ABB S.p.A.Line Protection Devices Viale dell’Industria, 1820010 Vittuone (MI) - Italy Tel.: +39 02 9034 1 Fax: +39 02 9034 7609 The data and illustrations are not binding. We reserve the right to modify the contents of this document on the basis of technical development of the products, without prior notice.Copyright 2009 ABB. All rights reserved.DS201MC40A30DS201MB16A30DS201MB32A30DS201MC6A30DS201MB20A30DS201MB40A30DS201MB6A30DS201MC10A30DS201MC16A30 DS201MC25A30DS201MC32A30DS201MB10A30DS201MB25A30DS201MC20A30。

01m自动变速箱

QADC或QADD

一、液力变矩器的结构与作用

作用: 1、增大由发动机产生 的扭矩 2、起到离合器的作用 传递(不传递)发动 机扭矩至变速器 3、缓冲发动机和传动 系的扭振 4、起到飞轮作用,使 发动机转动平稳 5、驱动油泵 6、通过锁止离合器, 实现刚性传动

液力变矩器的结构与工作原理

液力变矩器

K3

九、拆装2、4档制动器B2

1、螺栓(7颗、8NM拧紧后再转90°) 2、带B2活塞的变速器油泵 3、圆形密封圈 4、密封垫 5、弹簧盖(共6个) 6、弹簧(3个) 7、波形弹簧垫圈 8、外片B2(3.0mm厚) 9、内片(4片) 10、外片(2.0mm厚) 11、外片(3.0mm厚) 12、隔离管(68.30mm高) 13、壳体

01M FDC(bora 1.8T) QCDD QLB 内片 5 5 6 6 5 2.714 1.441 1.000 0.742 2.884 45 44 15 68 外片 5 5 5 6 6

自动变速器 代 滑阀箱 摩擦片数量 离合器K1 离合器K2 离合器K3 制动器B1 制动器B2 1档传动比 2档传动比 3档传动比 4档传动比 R档传动比 中间传动主动齿轮 中间传动从动齿轮 主传动主动齿轮 主传动从动齿轮 内片 4 3 5 4 4 2.714 1.441 1.000 0.743 2.884 61 63 16 78 码 FDH(Bora 1.6) QADD QLB 外片 4 3 4 4 5 变矩器代码

• B1 制动行星齿轮支架

• B2 制动大太阳轮

动力系统

1档

• I=2.71

•离合器K1驱动小太阳轮

•单向离合器制动行星齿轮支架

•电磁阀动作情况

电嗞阀 通1/断0 N88 0 N89 0 N90 1

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

DF005M - DF10M

1.0A GLASS PASSIVATED BRIDGE RECTIFIERS

Features

• Glass Passivated Die Construction

• Low Forward Voltage Drop, High Current Capability

• Surge Overload Rating to 50A Peak

• Designed for Printed Circuit Board Applications

• UL Listed Under Recognized Component Index, File Number E94661

• Lead Free Finish, RoHS Compliant (Date Code 0532+) (Note 3)

Mechanical Data

• Case: DF-M

• Case Material: Molded Plastic. UL Flammability Classification Rating 94V-0

• Moisture Sensitivity: Level 1 per J-STD-020C

• Terminals: Finish - Tin. Solder Plated Leads,

Solderable per MIL-STD-202, Method 208

• Polarity: As Marked on Case

• Marking Information: Type Number, See Page 3

• Weight: 0.38 grams (approximate)

DF-M

Dim Min Max

A 7.40 7.90

B 6.20 6.50

C 0.22 0.30

D 1.27 2.03

E 7.60 8.90

G 3.81 4.69

H 8.13 8.51

J 2.40 3.40

K 5.00 5.20

L 0.46 0.58

All Dimensions in mm

Maximum Ratings and Electrical Characteristics@T A = 25°C unless otherwise specified

Single phase, half wave, 60Hz, resistive or inductive load.

For capacitive load, derate current by 20%.

Characteristic Symbol

DF

005M

DF

01M

DF

02M

DF

04M

DF

06M

DF

08M

DF

10M

Unit Peak Repetitive Reverse Voltage

Working Peak Reverse Voltage

DC Blocking Voltage

V RMM

V RWM

V R

50 100 200 400 600 800 1000 V RMS Reverse Voltage V RMS35 70 140 280 420 580 700 V Average Rectified Output Current @ T A = 40°C I O 1.0 A

Non-Repetitive Peak Forward Surge Current, 8.3 ms

Single Half Sine-Wave Superimposed on Rated Load

I FSM50 A Forward Voltage (per element) @ I F = 1.0 A V FM 1.1 V Peak Reverse Current @ T A = 25°C

at Rated DC Blocking Voltage (per element) @ T A = 125°C

I RM

10

500

µA I2t Rating for Fusing (t<8.3ms) I2t 10.4 A2s Typical Total Capacitance per element (Note 1)C T25 pF Typical Thermal Resistance, Junction to Ambient (Note 2) RθJA40 °C/W Operating and Storage Temperature Range T j, T STG-65 to +150 °C

Notes: 1. Measured at 1.0MHz and applied reverse voltage of 4.0V DC.

2. Thermal Resistance, junction to ambient, measured on PC board with 5.0mm2 (0.03mm thick) land areas.

3. RοHS revision 13.2.2003. Glass and high temperature solder exemptions applied, see EU Directive Annex Notes 5 and 7.

I , A V E R A G E F O R W A R D C U R R E N T (A )

(A V )T , AMBIENT TEMPERATURE (°C)Fig. 1 Output Current Derating Curve

A

I ,I N S T A N T A N E O U S F O R W A R D C U R R E N T (A )

F V , INSTANTANEOUS FORWARD VOLTAGE (V)

Fig. 2 Typical Forward Characteristics (per element)F I , P E A K F O R W A R D S U R G E C U R R E N T

(A )F S M NUMBER OF CYCLES AT 60 Hz

Fig. 3 Max Non-Repetitive Peak Forward Surge Current

C , T O T A L C A P A C I T A N C E (p F )

T V , REVERSE VOLTAGE (V)

Fig. 4 Typical Total Capacitance (per element)R

1.0

10

100

PERCENT OF RATED PEAK REVERSE VOLTAGE (%)Fig. 5 Typ Reverse Characteristics (per element)

Ordering Information (Note 4)

Device* Packaging Shipping

DFxM DF-M Tube

* x = Device type, e.g. DF005M or DF10M, etc.

Notes: 4. For packaging details, visit our website at /datasheets/ap02007.pdf.

Marking Information

= Manufacturers’ code marking

XXXXX = Product type marking code, ex: DF10M

YWW = Date code marking

XXXXX

Y = Last digit of year ex: 2 for 2002

WW = Week code 01 to 52

IMPORTANT NOTICE

Diodes Incorporated and its subsidiaries reserve the right to make modifications, enhancements, improvements, corrections or other changes without further notice to any product herein. Diodes Incorporated does not assume any liability arising out of the application or use of any product described herein; neither does it convey any license under its patent rights, nor the rights of others. The user of products in such applications shall assume all risks of such use and will agree to hold Diodes Incorporated and all the companies whose products are represented on our website, harmless against all damages.

LIFE SUPPORT

Diodes Incorporated products are not authorized for use as critical components in life support devices or systems without the expressed written approval of the President of Diodes Incorporated.。