多进制数字相位调制系统课程设计

多进制数字调制系统PPT课件(通信原理)

13

8PSK信号点

14

在L=8 的5种信号星座图可以看 出,(4) 是最佳的一种方案

在同样的性能下,即在保证信 号状态点之间的最小距离为2 的情况下,(4)方案所用的平 均信号功率最小.

15

1

6.4.1 MASK

L电平的调制信号

可看成由时间上不重叠的L个不同振幅值 的OOK信号的叠加,因而,其功率谱密度便是这L 个信号的功率谱密度之和,尽管叠加后的谱结构 很复杂,但就带宽而言,L电平调制信号的带宽与 二电平的相同.

2

A(t)

×

x(t)

A(t)

BPF

× LPF 抽样判决

… 门限电平

每个四进制码元又被称为双比特码元

ab

(A方式) (B方式)

00 10 11 01

0° 90° 180° 270°

225° 315° 45° 135°

8

10

01

11

11

00

参考相位

参考相位

00

10

01

QPSK信号的矢量图

9

a

×

输入

串/并变换

-π/2

b

×

输出

+

调制

×

LPF

抽样判决

a

-π/2

并/串

×

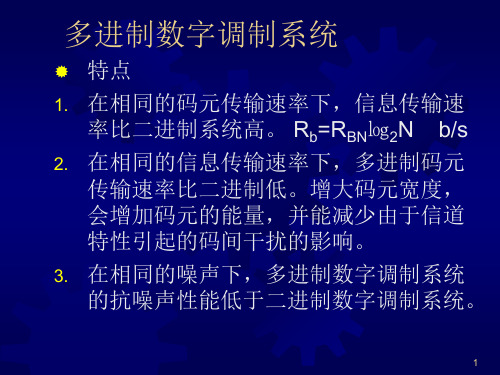

多进制数字调制系统

特点 1. 在相同的码元传输速率下,信息传输速

率比二进制系统高。 Rb=RBN㏒2N b/s 2. 在相同的信息传输速率下,多进制码元

传输速率比二进制低。增大码元宽度, 会增加码元的能量,并能减少由于信道 特性引起的码间干扰的影响。 3. 在相同的噪声下,多进制数字调制系统 的抗噪声性能低于二进制数字调制系统。

毕业论文-多进制数字信号调制系统

本科毕业设计(论文)题目多进制数字信号调制系统设计学生姓名XX 学号0907050208教学院系电气信息学院专业年级通信工程2009级指导教师汪敏职称讲师单位西南石油大学辅导教师职称单位完成日期2013 年 6 月9 日Southwest Petroleum UniversityGraduation ThesisSystem Design of M-ary Digital Signal ModulationGrade: 2009Name:Liu ShaSpeciality: Telecommunications EngineeringInstructor: Wang MinSchool of Electrical Engineering and Information摘要由于数字通信系统的实际信道大多数具有带通特性,所以必须用数字基带信号对载波进行数字调制。

也因此,数字调制方法成为了当今的热点研究对象,其中最常用的一种是键控法。

在带通二进制键控系统中,每个码元只能传输1比特的信息,其频带利用率不高,而频率资源又是极其宝贵的,为了能提高频带利用率,最有效的办法是使一个码元能够传输多个比特的信息,这就是本文主要研究的多进制数字调制系统,包括多进制数字振幅调制(MASK)、多进制数字频率调制(MFSK)和多进制数字相位调制(MPSK)。

多进制键控系统可以看作是二进制键控系统的推广,可以大大提高频带利用率,而且因其抗干扰性能强、误码性能好,能更好的满足未来通信的高要求,所以研究多进制数字调制系统是很有必要的。

本文通过对多进制数字调制系统的研究,采用基于EP2C35F672C8芯片,运用VHDL硬件描述语言,完成了多功能调制器的模块化设计。

首先实现多进制数字振幅调制(MASK)、多进制数字频率调制(MFSK)和多进制数字相位调制(MPSK) 的设计,将时钟信号通过m序列发生器后产生随机的二进制序列,再通过串/并转换器转换成并行的多进制基带信号;其次分别实现数字调制模块2-M电平变换器、分频器以及四相载波发生器的设计;最后在顶层文件中调用并结合四选一多路选择器,从而完成多功能调制器的设计。

FSK信号调制与解调技术【范本模板】

1 引言1。

1 研究的背景与意义现代社会中人们对于通信设备的使用要求越来越高,随着无线通信技术的不断发展,人们所要处理的各种信息量呈爆炸式地增长.传统的通信信号处理是基于冯·诺依曼计算机的串行处理方式,利用传统的冯·诺依曼式计算机来进行海量信息处理的话,以现有的技术,是不可能在短时间内完成的.而具于并行结构的信息处理方式为提高信息的处理速度提供了一个新的解决思路。

随着人们对于通信的要求不断提高,应用领域的不断拓展,通信带宽显得越来越紧张.人们想了很多方法,来使有限的带宽能尽可能的携带更多的信息。

但这样做会出现一个问题,即:信号调制阶数的增加可以提升传送时所携带的信息量,但在解调时其误码率也相应显著地提高。

信息量不断增加的结果可能是,解调器很难去解调出本身所传递的信息。

如果在提高信息携带量的同时,能够找到一种合适的解调方式,将解调的误码率控制在允许的范围内,同时又不需要恢复原始载波信号,从而降低解调系统的复杂程度,那将是很好的。

通信技术在不断地发展,在现今的无线、有线信道中,有很多信号在同时进行着传递,相互之间都会有干扰,而强干扰信号也可能来自于其它媒介。

在军事领域,抗干扰技术的研究就更为必要。

我们需要通信设备在强干扰地环境下进行正常的通信工作。

目前常用的通信调制方法有很多种,如FSK、QPSK、QAM等。

在实际的通信工程中,不同的调制制式由于自身的特点而应用于不同场合,而通信中不同的调制、解调制式就构成了不同的系统。

如果按照常规的方法,每产生一种信号就需要一个硬件电路,甚至一个模块,那么要使一部发射机产生几种、几十种不同制式的通信信号,其电路就会异常复杂,体积重量都会很大。

而在接收机部分,情况也同样是如此,即对某种特定的调制信号,必须有一个特定的对应模块电路来对该信号进行解调工作。

如果发射端所发射的信号调制方式发生改变,这一解调模块就无能为力了。

实际上,随着通信技术的进步和发展,现代社会对于通信技术的要求越来越高,比如要求通信系统具有最低的成本、最高的效率,以及跨平台工作的特性,如PDA、电脑、手机使用时所要求的通用性、互连性等。

多进制数字调制技术

概述

特点

在相同的码元传输速率下,多进制调制系统信息传输速率 比二进制系统高。

Rb RBN log 2 N

b

s

在相同的信息传输速率下,多进制码元传输速率比二进制 低。增大码元宽度,会增加码元能量,并能减少由于信道 特性引起的码间干扰的影响。 在相同的噪声下,多进制数字调制系统的抗噪声性能低于 二进制数字调制系统。

k

RS W 1

概述

常见的多进制调制:多振幅调制(MASK)、多频率调制、多相位调 制以及它们的组合等。 多进制调制提高了信息速率,同时节约了频带。但是误码率会增加。

概述

在相同时间内二进制编码只传输6位二进制数,但多进制 编码共传输了12位二进制

(a)用二进制数进行传输二进制数“101101”的波形图 ( b )是用四进制数传输四进制数 “011011100010 (用二进制表示四 进制数)的波形图

项目1-2 数字调制技术

鄢立

多进制调制技术

录

目

Contents

02

01

概述 多进制数字调制技术

Part

01

概述

鄢 立

概述

为了有效利用频带,提高信息传输速率而采用多进制调制。 多进制调制通常以降低功率利用率为代价来提高其频带利用 率。 (1)频带利用率——单位频带内所能传输的最大比特率。频 带利用率大于2bit/Hz的调制为高效调制。 (2)功率利用率——误码率达到要求时所需的最小信号与噪 声的功率比值。

多进制频移键控(MFSK)

利用串并变换电路和逻辑电路将输入的二进制码转换成多 进制码。当某组二进制码到来时,逻辑电路的输出仅打开 相应的一个门电路,将和该门电路相应的载波发送出去; 其他频率对应的门电路此时是关闭的。当一组组二进制码 元输入时,通过相加器输出的就是一个多进制频率键控的 波形。

基于多进制数字的相位解调技术的分析

V l 2 No o_ . 3 2 Ma.0 1 r2 1

井冈山大学学报 ( 然科学版) 自 Jun l f ig a gh nUnv ri Na rl c n e o ra o n g n s a iesy( t a S i c) J t u e

解调和延迟解调两种分别进行 了较详细地分析 。 关键词 :数字调制 ;码元 ;比特 ;信噪 比 中图分类号 :T 1 N9 4 文献标识码 :A I : .9 9 .s . 7 - 0 5 0 1 20 8 3 1 3 6 /i n1 4 8 8 . 1. .1 OI 0 js 6 2 0

Ab t a t Th — r h s e d l t n a d d tc i n we e a a y e h sp p r T e sg a x r s i n f s r c : e M a y p a e d mo u a i n e e t r n l z d i t i a e . h i n le p e so s o o o n M -r h s d l t n we e i t d c d b s d o em ut b n i i l h s d l t n s se d 1 I h a y p a e mo u a i r nr u e a e n t l — a d d g t a e mo u a i y tm mo e. n t e o o h i a p o mu t b n i i l h s d lt n t e f u h s b o u e p a es i e i g a d t e f u h s ea i e p a e l — a d d g t a e mo u a i , h o rp a e a s l t h s h f k y n n r p a e r l t h s i a p o t h o v s i e i g we e r s e t e y a a y e n d t i h f k y n r e p ci l n l s d i ea l i al ,t e f u h s b o u e p a e s it k y n s t v .F n l y h r p a e a s l t h s h f e i g wa o

大学通信原理讲课教案设计

课程名称:通信原理授课对象:通信工程、电子信息等相关专业本科生授课时间:2课时教学目标:1. 使学生掌握通信系统的基本概念、组成和分类。

2. 理解信号与频谱的基本知识,包括傅里叶级数、傅里叶变换等。

3. 了解模拟通信系统和数字通信系统的基本原理,包括调制、解调、编码、解码等。

4. 掌握通信系统中的信道特性、噪声特性及抗噪声技术。

教学内容:一、绪论1. 通信系统的基本概念、组成和分类。

2. 通信系统的发展历程和未来趋势。

二、信号与频谱1. 信号的分类:确定性信号和随机信号。

2. 信号的时域和频域表示。

3. 傅里叶级数和傅里叶变换。

4. 能量谱密度和功率谱密度。

三、模拟通信系统1. 调制和解调的基本原理。

2. 幅度调制(AM)、频率调制(FM)和相位调制(PM)。

3. 频分复用(FDM)。

四、数字通信系统1. 数字信号的基本特性。

2. 数字调制技术:二进制数字调制、多进制数字调制。

3. 数字信号传输中的抗噪声技术。

教学方法和手段:1. 讲授法:讲解基本概念、原理和关键技术。

2. 案例分析法:通过实际案例讲解通信系统中的关键技术。

3. 图表法:利用图表展示信号、频谱、调制解调等基本概念。

4. 实验法:通过实验演示通信系统中的关键技术。

教学过程:一、导入1. 介绍通信原理课程的重要性。

2. 阐述本节课的教学目标和内容。

二、讲授新课1. 绪论:讲解通信系统的基本概念、组成和分类。

2. 信号与频谱:讲解信号的分类、时域和频域表示、傅里叶级数和傅里叶变换等。

3. 模拟通信系统:讲解调制、解调、幅度调制、频率调制、相位调制和频分复用等。

4. 数字通信系统:讲解数字信号的基本特性、数字调制技术和抗噪声技术。

三、案例分析1. 以实际案例讲解通信系统中的关键技术。

2. 引导学生分析案例,提高学生的实际应用能力。

四、课堂小结1. 总结本节课的重点内容。

2. 强调通信原理在实际工程中的应用。

五、作业布置1. 完成课后习题,巩固所学知识。

26多进制数字调制(二)_2

–OQPSK信号功率谱密度与QPSK相同,其表达式为

PQPSK

(

f

)

POQPSK

(

f

)

2

A2Tb

sin[2(

2( f

f

fC )Tb fC )Tb

]

–因OQPSK相干解调与QPSK相干解调相同。由于I(t)、 Q(t)互相独立,因此OQPSK相干解调的误码率性能 也与QPSK相同

最小频移键控 MSK

• 单独使用振幅或相位携带信息时不能最充分地利用信 号平面:MASK信号矢量端点在一条轴上分布; MPSK矢量端点在一园上分布。随M增加,这些端点 间的最小距离减小。

• 为充分利用信号平面,将这些矢量端点重新合理分布, 可在不减小最小距离情况下增加信号矢量端点的数目

振幅相位联合调制系统

• 星座图——星座调制

LPF

+ cos t O

LPF

sin t O

信道

串/并 变换

低通 cos t

O

低通

sin t O

判决L-1 门限

定时 脉冲

判决L-1 门限

Rb/2

串/并 输出

变换 Rb

Rb/2

(b)MQAM的调制解调

正交振幅调制 QAM

• MQAM的调制与解调(正交调幅法)

QPSK 调制解调

关键词: 相移键控 四相移键控 QPSK调制 相干解调

I

×××大学本科毕业设计

QPSK Demodulation Experimental Design

Abstract:Indigitalcommunication,weoftenmodulatanddemodulat digital

signalbyFSKandPSKtotransmitdigitalinformation。 Nowadays,PSKoftenuse QPSK and NPSK. Any digital modulation scheme uses a finite number of distinct signals to represent digital data. PSK uses a finite number of phases, each assigned a unique pattern of binary digits. Usually, each phase encodes an equal number of bits. Each pattern of bits forms the symbol that is represented by the particular phase. The demodulator, which is designed specifically for the symbol-set used by the modulator, determines the phase of the received signal and maps it back to the symbol it represents, thus recovering the original data. This requires the receiver to be able to compare the phase of the received signal toareferencesignal— suchasystemistermedcoherent(andreferredtoas CPSK). This text is detailed on the concept,implement and principle of QPSK. It also detailed introduces the designedand realize of QPSK.

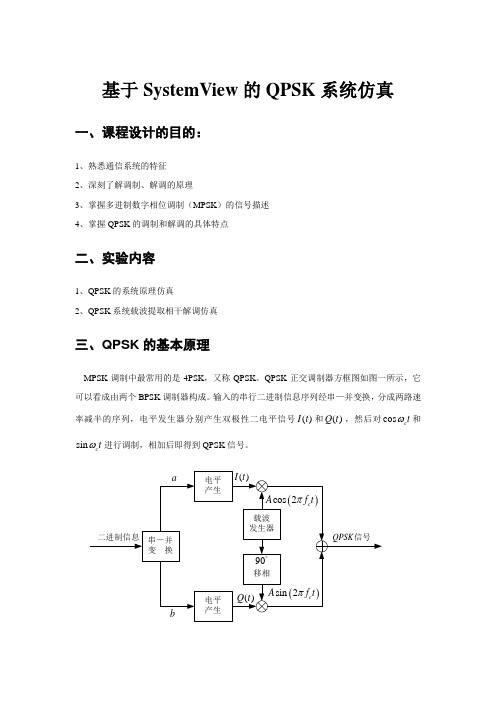

基于SystemView的QPSK系统仿真

基于SystemView 的QPSK 系统仿真一、课程设计的目的:1、熟悉通信系统的特征2、深刻了解调制、解调的原理3、掌握多进制数字相位调制(MPSK )的信号描述4、掌握QPSK 的调制和解调的具体特点二、实验内容1、QPSK 的系统原理仿真2、QPSK 系统载波提取相干解调仿真三、QPSK 的基本原理MPSK 调制中最常用的是4PSK ,又称QPSK 。

QPSK 正交调制器方框图如图一所示,它可以看成由两个BPSK 调制器构成。

输入的串行二进制信息序列经串—并变换,分成两路速率减半的序列,电平发生器分别产生双极性二电平信号()I t 和()Q t ,然后对cos c t ω和sin c t ω进行调制,相加后即得到QPSK 信号。

图一 QPSK 的调制过程QPSK 信号可以用两个正交的载波信号实现相干解调。

它的相干解调器如图二所示。

正交路和同相路分别设置两个相关器(或匹配滤波器),得到()I t 和()Q t ,经电平判决和并—串变换即可恢复原始信息。

图二 QPSK 的相干解调过程假设输入的QPSK 信号为:判决准则为:()cos 2n aI t ϕ=()sin 2n aQ t ϕ=()cos()c n r t a t ωϕ=+在MPSK的相干解调中,恢复载波时存在相位模糊度问题,在QPSK中常用的基带数字处理载波跟踪环,它把载波恢复和相干解调结合起来,下面讨论它们的工作原理。

经整理后得:四、课程设计的内容要求1、QPSK调制与相干解调原理仿真以v26标准的QPSK信号为为表转,在SystemView平台上仿真QPSK调制与解调的通信系统的仿真方法。

v26信号的一些参数如下:该信号为差分编码正变调制的QPSK信号,其调制信号的码速率为2.4kb/s,经串并变换后,I、Q通道的码速率分别为1.2kb/s;调制载波为1.8kHz的正弦波,为实现软解调,其数据采样频率为9.6kb/s。

要求取得的数据结果是:比较输入数据和输出数据的波形图,观看I通路输出码元序列的眼图2、QPSK信号载波提取相干解调其相关参数与上一样,但在仿真中利用载波提取环,也就是说利用用于QPSK信号解调的载波跟踪环,可以从QPSK信号中提取载波从而完成相干解调。

调制与解调信号课程设计

调制与解调信号课程设计一、课程目标知识目标:1. 学生能够理解调制与解调信号的基本概念,掌握不同类型的调制方法及其原理;2. 学生能够描述调制与解调信号在通信系统中的作用和重要性;3. 学生能够运用数学表达式和图形来表示调制与解调过程。

技能目标:1. 学生能够运用所学知识,设计简单的调制与解调电路,并进行仿真实验;2. 学生能够分析调制与解调信号的特点,解释其在实际通信系统中的应用;3. 学生能够运用相关工具和软件进行调制与解调信号的观察、分析和调试。

情感态度价值观目标:1. 学生能够认识到调制与解调技术在现代通信领域的重要地位,增强对通信科学的兴趣和好奇心;2. 学生通过合作学习和实践操作,培养团队协作意识,提高问题解决能力和创新思维;3. 学生能够关注通信技术对社会发展的积极影响,树立正确的科学价值观。

课程性质:本课程属于电子信息类学科,以理论教学和实践操作相结合的方式进行。

学生特点:学生具备一定的电子基础和数学知识,对通信原理有一定的了解,但实践经验不足。

教学要求:注重理论与实践相结合,提高学生的动手能力和实际问题解决能力,培养学生对通信技术的兴趣和热情。

通过具体的学习成果分解,使学生在课程结束后能够达到上述目标。

二、教学内容本章节教学内容主要包括以下几部分:1. 调制与解调信号基本概念:- 调制信号的分类(模拟调制、数字调制)- 解调信号的分类(同步解调、异步解调)2. 常见调制方法及其原理:- 幅度调制(AM)、频率调制(FM)、相位调制(PM)- 二进制数字调制(ASK、FSK、PSK、QAM)3. 调制与解调信号在通信系统中的应用:- 调制解调器工作原理- 调制技术在无线电广播、电视、卫星通信等领域的应用4. 调制与解调电路设计及仿真:- 搭建调制与解调电路- 使用Multisim、MATLAB等软件进行仿真实验5. 教学内容的安排与进度:- 第一周:调制与解调信号基本概念,调制信号分类- 第二周:常见调制方法及其原理,教材第二章- 第三周:调制与解调信号在通信系统中的应用,教材第三章- 第四周:调制与解调电路设计及仿真,教材第四章教学内容根据课程目标进行科学性和系统性地组织,注重理论与实践相结合,使学生能够逐步掌握调制与解调信号相关知识,提高实际操作能力。

有关MDPSK和MPSK的讲解

第五次实验讲座实验四:数字载波调制系统 07.4§ 1、限带BPSK 系统 一、 命题1、范例:运行限带BPSK 系统程序,观察各时频域图形和信噪误码性能。

2、分析:在高斯信道下,这六对时频域图的原理和系统误码性能。

二、BPSK 要点 二进制绝对相移键控。

信号表达式:()(){112,cos +-=⎥⎦⎤⎢⎣⎡-=∑n c n b T n psk a t nT t g a A t s ω功率谱密度:频谱搬移、带宽增加一倍。

信噪误码率:()SNRQ N E Q N E erfc P b b e *222100=⎪⎪⎭⎫⎝⎛=⎪⎪⎭⎫⎝⎛=三、限带BPSK 系统的技术指标和仿真的内容码元速率2.4Kb/s, 基带带宽1.2KHz, 载波频率2.4KHz, 信道带宽1.2KHz, 等效信道干扰A WGN 。

仿真该系统:(1)各点的时、频域图形,(2)系统的信噪误码性能。

四、源系统设计用升余弦滚降滤波器对基带信号限带,实现1.2kHz 带宽传输2.4Kb/s 码率的原始信号 ,基带滤波器参数:()()5.02.1==αZd b d b KHf f H f H 、:、 。

用升余弦滚降滤波器使频带信号作残留边带传输,实现1.2kHz 带宽传 输2.4Kb/s 码率的已调信号,残留边带滤波器参数: ()()75.04.2==αZR T R T KHf f H f H 、:、 。

信源为{+1、-1},最佳判决时刻t=t m , 判决门限α=0 。

五、目标系统设计将源系统离散化,适合计算机运行,目标系统图如下: 信源→ fft → * → ifft → * → fft → * → AWGN Rayl. →比计 H b (k) cos (nw c ) H T (k) H信宿 ← 判决 ← 抽样 ← ifft ← * ← fft ← * ← ifft H d (k) cos ( nw c)为显示信号的图形,每比特抽4个样本,而在判决时择其中一个样本。

MSK调制解调实习报告

通信系统课程设计MSK调制与解调姓名:班级:学号:指导老师:时间:通信系统课程设计MSK调制与解调1.实习目的:研究MSK连续相位技术,在其调制指数h=1/2下,用systemview仿真软件对其进行仿真观察其调制过程。

熟悉课本知识,掌握通信原理数字带通传输系统的原理和过程。

本次实习选择运用msk多进制数字调制来实现整体过程。

2.实习仪器:计算机;systemview。

3.实习内容:1)MSK调制过程MSK调制的基本原理MSK最小频移键控是2FSK的改进型,它解决了2FSK的一些不足之处,具有着包络恒定,相位连续,带宽最小、并且严格正交的优点。

此处“恒定包络”的含义并非指产生的信号幅度包络恒定,而是指移相键控信号通过限带信道或非线性系统后,幅度包络几乎不产生AM/PM转换效应,这取决于移相键控信号在码元转换时刻的相位变化是否剧烈、相位路径是否连续平缓,因为相位特性直接影响信号的功率谱旁瓣是否快速收敛,信号能量是否集中等特性。

事实上,现代数字通信要求以最小的信号功率付出和频带资源最高效率地利用进行数据传输,数字调制技术改进过程中的许多工作几乎就是围绕如何改进调制信号的相位路径特性进行的。

MSK信号是一种正交连续相位移频键控(CP-FSK)信号,在码元转换时刻无相位突变,且相位变化量仅为90°。

MSK的一般表达式为:MSK信号属于恒定包络调制信号,此处“恒定包络”的含义并非指产生的信号幅度包络恒定,而是指移相键控信号通过限带信道或非线性系统后,幅度包络几乎不产生AM/PM转换效应,这取决于移相键控信号在码元转换时刻的相位变化是否剧烈、相位路径是否连续平缓,因为相位特性直接影响信号的功率谱旁瓣是否快速收敛,信号能量是否集中等特性。

事实上,现代数字通信要求以最小的信号功率付出和频带资源最高效率地利用进行数据传输,数字调制技术改进过程中的许多工作几乎就是围绕如何改进调制信号的相位路径特性进行的。

第17讲 多进制数字调制原理

相加 电路

s(t)

b

相乘 电路

图7-37 第一种QPSK信号产生方法

通信原理

第6章 数字带通传输系统

码元串并变换: 0

0 1

1 2 3 4 (a) 输入基带码元

2 4 (b) 并行支路a码元

5

t t t

3 5 (c) 并行支路b码元 图7-38 码元串/并变换

通信原理

第6章 数字带通传输系统

矢量图:

f1 00

f2 01

f3 10

f4 11

(b) 4FSK信号的取值

通信原理

第6章 数字带通传输系统

• MFSK信号的带宽: B = fM - f1 + f 式中, f1 - 最低载频 fM - 最高载频 f - 单个码元的带宽

通信原理

第6章 数字带通传输系统

• MFSK非相干解调器的原理方框图:

通信原理

第6章 数字带通传输系统

– 正交相移键控(QPSK) • 4PSK常称为正交相移键控(QPSK) • 格雷(Gray)码 – 4PSK信号每个码元含有2 比特的信息,现用ab代表 这两个比特。 – 两个比特有4种组合,即00、01、10和11。它们和 相位k之间的关系通常都按格雷码的规律安排,如 下表所示。 QPSK信号的编码: a 0 0 1 1 b 0 1 1 0

01 10 11 11

10

01 00 00

10 t

0

(c) 基带多电平双极性不归零信号

11 01 00 00 11

01

10

10

10

0

t

(d) 抑制载波MASK信号

通信原理

第6章 数字带通传输系统

6.5.2 多进制频移键控(MFSK)

MQAM(M进制正交幅度调制)

• 等效方差

2

1 n0 BT 2

• 等概率时的误码率:

Pe Q(d / 2 )

pe1

f0(x) f1(x)

pe0

DG d

x Q(a)

多进制数字振幅调制MASK

• 抗噪声性能

–设发送端L电平的基 带码元的振幅位于 ªA、ª3A、…ª(L1)A,相邻电平振幅 的距离为2A。 –相邻信号点的距离为:

M 1 n0

3A 2A A O t 2 3 0 1

P

n

1

TB

多进制数字振幅调制MASK

• 带宽

–其功率谱密度为C)+G(f-fC)]

与2ASK一样,带宽 为基带信号的二倍 ,但可传送log2M信 息量。如要求传送 信息量相同,则可 加大TS,减小带宽

• 调制解调

多进制数字调制系统概述

• 在每个符号间隔0 ≤t≤TS内可发送的状态有M种 S1(t)~ SM(t) ,称M进制。实际应用中取M=2n(n>1的 正整数),可有MASK、MFSK、MPSK,及其组合起 来的MAPK、MQAM(M进制正交幅度调制) • M进制中每个符号携带的信息量IS=log2M,可提高信 息传输速率(注意多进制系统的码元速率与比特速率 的关系)。如四进制系统,信息传输速率是二进制系 统的二倍,等效于提高频带利用率。其代价是增加信 号功率和实现上的复杂性 • 相同信息速率下,多进制传输速率比二进制低,即TS 加大,码元能量增加,能减小由于信道特性引起的码 间干扰的影响。 目前多进制数字调制系统应用更为广泛

多进制数字振幅调制MASK

• 时域表达式

S MASK (t ) [ bn g(t nTS )]cosC t

通信原理课件——数字调制系统

② 2DPSK信号的解调

——

极性比较—码变换法即是2PSK解调加差分译码,其方框图如(a) 原理:2DPSK解调器将输入的2DPSK信号还原成相对码{bn},再由差分译码器把 相对码转换成绝对码,输出{an},从而恢复发送的信息。在次过程中,若相干

载波产生1800模糊,会发生“反向工作”现象。但是经过码反变换器后,输出的 绝对码不会发生任何倒置现象。

根据题中已知条件,码元传输速率为1000B,“1”码元的载 波频率为3000Hz,“0”码元的载波频率为2000Hz。因此, 在2FSK信号的时间波形中,每个“1”码元时间内共有3个 周期的载波,每个“0”码元时间内共有两个周期的载波。

数字基带信号s(t)和2FSK信号的时间波形如图:

(2)2FSK信号是一种非线性调制信号,其功率谱结构可以近似看成是两 个2ASK信号频谱的叠加。

n

n

n1

(2) 2PSK和2DPSK信号的调制

模拟调相法:原理框图如图所示,码变换器(即差分编码器)是用来完成绝

对码波形到相对码波形变换的,去掉码变换器,则可进行2PSK信号的调制。

(3) 2PSK和2DPSK信号的解调 ① 2PSK信号的解调

——

2PSK信号的解调只能采用相干解调的方法,其方框图及波形如图所示。

2. 二进制频移键控(2FSK)

数字频率调制又称频移键控,记作FSK(Frequency Shift Keying), 二进制频移键控记作2FSK。

(1) 2FSK信号的调制方法:

前面已提到,2FSK信号可以采用模拟调频法和数字键控法来产生。

模拟调频法:用数字基带矩形脉冲控制一个振荡器的某些参数(例如电

3. 二进制相移键控及二进制差分相位键控

通信课设--16PSK

目录1课程设计目的 (1)2 课程设计要求 (1)3 相关知识 (1)4 课程设计分析 (4)5仿真 (6)6 结果分析 (10)7参考文献 (15)16PSK系统仿真1.课程设计目的(1)根据题目,查阅有关资料,掌握16进制相移键控的基本原理。

(2)学习MATLAB软件,掌握MATLAB中元器件使用及参数的设置。

(32.课程设计要求(1)掌握相移键控的相关知识、概念清晰。

(2)掌握MATLAB使用方法,利用软件绘制图像。

(3)程序设计合理、能够正确运行。

3.相关知识3.1数字通信系统简介通信系统是为了有效可靠的传输信息,信息由信源发出,以语言、图像数据为媒体,通过电(光)信号将信息传输,由信宿接收。

通信系统又可分为数字通信与模拟通信。

实现数字通信,必须使发送端发出的模拟信号变为数字信号,这个过程称为“模数变换”。

模拟信号数字化最基本的方法有三个过程,第一步是“抽样”,就是对连续的模拟信号进行离散化处理,通常是以相等的时间间隔来抽取模拟信号的样值。

第二步是“量化”,将模拟信号样值变换到最接近的数字值。

因抽样后的样值在时间上虽是离散的,但在幅度上仍是连续的,量化过程就是把幅度上连续的抽样也变为离散的。

第三步是“编码”,就是把量化后的样值信号用一组二进制数字代码来表示,最终完成模拟信号的数字化。

数字信号送入数字网进行传输。

接收端则是一个还原过程,把收到的数字信号变为模拟信号,即“数据摸变换”,从而再现声音或图像。

数字通信系统模型如图3.1所示。

图3.1 数字通信系统模型3.2MATLAB简介3.2.1基本功能MATLAB是很实用的数学软件它在数学类科技应用软件中在数值运算方面首屈一指。

MATLAB可以进行运算、绘制函数和数据、实现算法、创建用户界面、连接接其他编程语言的程序等,主要应用于工程计算、控制设计、信号处理与通讯、金融建模设计与分析等领域。

MATLAB的基本数据单位是矩阵,它的指令表达式与数学、工程中常用的形式十分相似,故用MATLAB来解算问题要比用C,FORTRAN等语言完成相同的事情简捷得多,并且mathwork也吸收了像Maple等软件的优点,使MATLAB成为一个强大的数学软件。

数字相位调制

四相相移键控调制 (QPSK)

图2-21

QPSK信号相位矢量图

四相相移键控调制 (QPSK)

图2-22 QPSK正交调制器

四相相移键控调制 (QPSK)

由图2-22可见,它把二进制双极性不归零数据序列首先经串/ 并变换分成奇偶两路,即将二进制数据每两比特分为一组, 共有四种组合:-1-1,-1+1,+1-1和+1+1,每路的码元宽度 Tb扩展为2 Tb , 如表2-6所示。其中一路数据送入Q信道,对载波- sin ω t 进 c 行二相调制;而另一路数据送入I信道,对载波 进行 cos ωc t 二相调制;两个二相信号相加得到四相PSK信号。 这样,QPSK信号的相位就有四种可能的取值;且由于两个 信道上的数据沿对齐,所以在码元转化时刻上QPSK信号的 相位,可能产生±90º突变(当两个信道上只有一路数据改 变极性时),也可能产生± 180º突变(当两个信道上数据 同时改变极性时),而且每隔2Tb跳变一次。 其星座图及相位转移图示于图2-23(a)中。

I π

0

Q

3π / 2 π /2

7π / 4 5π / 4 3π / 4 π /4

QPSK

±

π

2

±π

四相相移键控调制 (QPSK)

图2-23 QPSK和OQPSK的星座图和相位转移图

四相相移键控调制 (QPSK)

I、Q路误码率分别为

PeI

,

PeQ

1 都是BPSK信号的误码率: erfc r 2

其中

四相相移键控调制 (QPSK)

为了减小传输信号频带,提高信道频带利用率,可以将二进 制数据变换为多进制(即M进制)数据来传输。用M进制数 据控制载波的相位,就是M相相移键控。当M=4时,就是四 相相移键控(QPSK)调制。 在QPSK系统中,载波相位共有四个可能的取值,其相位矢 量图如图2-21所示。 以参考相位为基准,本图(a)中的已调波相位取的π/4奇 数倍,即取(2n+1) π/4 ,因此称为π/4系统QPSK;本图 (b)中的已调波相位取π/4的整数倍,即取n π/2 ,因此 称它为π/2系统QPSK。 由图可见,无论哪种系统,QPSK信号都可看成是载波相互 正交的两个二相PSK信号之和。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

多进制数字相位调制系统课程设计

石家庄经济学院

通信实习报告

院系:信息工程学院学号:

姓名:

日期:2013.1.15

一、实习目的

1、通过本次专业课程设计巩固并扩展通信课程的基本概念、基本理论、分

析方法和仿真实现方法。

2、结合所学的MATLAB和EDA等软件仿真技术,完成通信专业相关课程内容的

建模和设计仿真。

到达通信专业相关理论课程有效的巩固和整合,实现将理论知识和软件设计紧密结合。

3、通过本次专业课程设计达到培养学生的创新能力、通信系统建模和仿真设计

能力以及软件调试和分析能力的目的。

二、实习要求

1、应用通信类软件完成通信系统相关内容的设计和建模,并仿真出正确结果,

对仿真波形加以重点分析和说明。

2、按要求格式书写报告,原理充分、设计方法及仿真结果分析正确、条理清晰、

重点突出。

三、实习内容

(1)实习题目

多进制数字相位调制系统设计

(2)设计原理

一、多进制数字相位调制(MPSK)

多进制数字相位调制也称多元调相或多相制。

它利用具有多个相位状态的正弦波来代表多组二进制信息码元,即用载波的一个相位对应于一组二进制信息码元。

如果载波有2k个相位,它可以代表 k位二进制码元的不同码组。

多进制相移键控也分为多进制绝对相移键控和多进制相对(差分)相移键控。

在MPSK信号中,载波相位可取M个可能值,

因此,MPSK信号可表示为

假定载波频率是基带数字信号速率的整数倍,则上式可改写为

上式表明,MPSK信号可等效为两个正交载波进行多电平双边带调幅所得已调波之和。

因此其带宽与MASK信号带宽相同,带宽的产生也可按类似于产生双边带正交调制信号的方式实现。

下面以四相相位调制为例进行讨论。

四相调相信号是一种四状态符号,即符号有00、01、10、11四种状态。

所以,对于输入的二进制序列,首先必须分组,每两位码元一组。

然后根据组合情况,用载波的四种相位表征它们。

这种由两个码元构成一种状态的符号码元称为双比特码元。

同理,k位二进制码构成一种状态符号的码元则称为k比特码元。

二、4PSK信号

四相PSK(4PSK)信号实际是两路正交双边带信号。

串行输入的二进制码,两位分成一组。

若前一位用A表示,后一位用B表示,经串/并变换后变成宽度加倍的并行码(A、B码元在时间上是对齐的)。

再分别进行极性变换,把单极性码变成双极性码,然后与载波相乘,形成正交的双边带信号,加法器输出形成4PSK信号。

显然,此系统产生的是π/4系统PSK信号。

如果产生π/2系统的PSK信号,只需把载波移相π/4后再加到乘法器上即可。

(系统信号的产生原理框图 )

因为 4 PSK信号是两个正交的2 PSK信号的合成,所以可仿照 2 PSK信号的相平解调方法,用两个正交的相干载波分别检测A和B两个分量,然后还原成串行二进制数字信号,即可完成4 PSK信号的解调。

此法是一种正交相平解调法,又称极性比较法,原理图在下页

(系统PSK信号解调原理框图)

为了分析方便,可不考虑噪声的影响。

这样,加到接收机上的信号在符号持续时间内可表示

两路乘法器的输出分别为

LPF输出分别是

根据π/4移相系统PSK信号的相位配置规定,抽样判决器的判决准则表在下页。

当判决器按极性判决时,若正抽样值判为1,负抽样值判为0,则可将调相信号解调为相应的数字信号。

解调出的A和B再经并/串变换,就可还原出原调制信号。

若解调π/2移相系统的PSK信号,需改变移相网络及判决准则。

(π/4 系统判决器判决准则)

三、MPSK 调制电路VHDL 程序及仿真

(MPSK 调制方框图)

注:电路符号图中没有包含模拟电路部分,输出信号为数字信号。

基带信号通过串/并转换器xx 得到2位并行信号yy ;四选一开关

根据yy 的数据,选择载波对应的相位进行输出,即得调制信号y 。

FPGA

clk

star

基带分频

0901827

串/

四选一

调制

--文件名:MPSK

--功能:基于VHDL硬件描述语言,对基带信号进行MPSK调制

--说明:调制信号说明如下表所示。

(3)设计方法

library ieee;

use ieee.std_logic_arith.all;

use ieee.std_logic_1164.all;

use ieee.std_logic_unsigned.all;

entity MPSK is

port(clk :in std_logic; --系统时钟

start :in std_logic; --开始调制信号 x :in std_logic; --基带信号

y :out std_logic); --调制信号

end MPSK;

architecture behav of MPSK is

signal q:integer range 0 to 7; --计数器

signal xx:std_logic_vector(1 downto 0);--中间寄存器

signal yy:std_logic_vector(1 downto 0);--2位并行码寄存器

signal f:std_logic_vector(3 downto 0); --载波f

begin

process(clk)--通过对clk分频,得到4种相位;并完成基带信号的串并转换begin

if clk'event and clk='1' then

if start='0' then q<=0;

elsif q=0 then q<=1;f(3)<='1'; f(1)<='0'; xx(1)<=x;yy<=xx;

elsif q=2 then q<=3;f(2)<='0'; f(0)<='1';

elsif q=4 then q<=5;f(3)<='0'; f(1)<='1'; xx(0)<=x;

elsif q=6 then q<=7;f(2)<='1'; f(0)<='0';

else q<=q+1;

end if;

end if;

end process;

y<=f(0) when yy="11" else

f(1) when yy="10" else

f(2) when yy="01" else

f(3); --根据yy寄存器数据,输出对应的载波

end behav;

(4)仿真结果及分析

(MPSK调制VHDL程序仿真全图)

(MPSK调制VHDL程序仿真局部放大图1)(5)结论

多进制数字调制技术与FPGA的结合使得通信系统的性能得到了迅速的提高。

本文基于FPGA实现了MPSK调制解调电路部分。

在实际应用中,完全可以把调制部分和解调部分电路都集成到一片FPGA芯片内,这样即提高了FPGA内部结构的利用率,又可以降低系统的成本。

四、参考文献

【1】徐以涛,沈良,王金龙.FPGA技术在软件无线电中的应用【J】.电信科学,200l(11):36-39.

【2】樊昌信,张甫翊,徐炳祥,等.通信原理【M】.第五版.北京:国防工业出版社,2001.

【3】阳晰.高速数字调制解调【D】.成都:电子科技大学,2005.

【4】损增友.基于FPGA的MPSK调制器的设计【J】.数字技术与应用,2009(7):19-20.

【5】詹仙宁,田耘.VHDL开发精解与实例剖析【M】.北京:电子工业出版社,2009.

五、实习体会

本次课程设计过程中,遇到的一个难点就是程序的调试,本来编写的程序是没错的,但是一旦

输入调试软件中就会报告各种错误,有些错误很难找出来,有时候明明设计的一个程序是正确的,但是就是报错,有时候大家一起合作可以找出错误,但是有时候就只能寻求帮助。

从调试中我学到了我们平时自己写程序的时候一定要规范,字体、格式等等,都要严格的按照要求来做。

通过这次课程设计,我也意识到了我对这门课掌握还有一定的不足,还有许多的知识我不了解;有的是一知半解;有的即使原理懂了,但在应用方面却是丝毫不知。

所以在今后的学习中,我会更加努力,不仅要学好理论知识,还要把它应用到实践中去,使两者很好的结合起来,互补互助。

六、实习效果评价

指导教师评语:

实习成绩:优良中及格不及格

指导教师签名:

年月日。