五种高精度ADC中杂散问题分析及应对方法

ADC发泡剂产品中含杂质原因分析及改进措施

第3期2021年3月中国氣碱China Chlor-AlkaliNo.3Mar.,202111 ADC发泡剂产品中含杂质原因分析及改进措施曹绍良(江西世龙实业股份有限公司,江西乐平333311)摘要:介绍了 ADC发泡剂产品中杂质产生的原因,采取切实有效的措施进行改进,优化ADC发泡 剂生产操作控制,进一步稳定提高产品质量。

关键词:ADC发泡剂;杂质;过滤;产品质量中图分类号:TQ225.26+8 文献标识码:B文章编号:1009-1785(2021 )03-0011-03Cause analysis and improvement measures of impurities in ADCfoaming agent productsCA0Shao-liang(Jiangxi Selon Industrial Co.,Ltd.,Leping333311,China)Abstract:This paper introduces the causes of impurities in ADC foaming agent products,and makes technical improvement,optimizes the production operation control,and improves the product quality.Key words:ADC foaming agent;impurity;filter;product qualityADC发泡剂是江西世龙实业股份有限公司的 主导产品,2017年,该公司成立ADC发泡剂产品质 量攻关小组,对ADC发泡剂产品中的杂质及生产过 程、生产工序进行全面分析,提出了具体改进措施,通过分析改进,层层落实到位,ADC发泡剂产品质 量得到稳定提升。

1杂疏种类分析杂质在ADC发泡剂产品中体现为黑点、黄点、白点等。

经过认真总结分析,生产过程中可能混人的 杂质归类为以下几种情况。

adc芯片,之间有串扰

adc芯片,之间有串扰ADC芯片是模拟信号转换为数字信号的关键组件,广泛应用于各种电子设备中。

然而,在ADC芯片的应用中,我们常常会遇到一个问题,那就是串扰。

本文将探讨ADC芯片之间的串扰现象及其影响,并提出一些解决方案。

我们来了解一下什么是ADC芯片之间的串扰。

串扰是指在多个ADC 芯片共享同一个电源或地线时,由于电源或地线的干扰,信号在ADC芯片之间相互干扰的现象。

这种干扰可能会导致信号失真、噪声增加以及采样精度下降等问题,影响系统的性能和稳定性。

那么,为什么会出现ADC芯片之间的串扰呢?主要有以下几个原因:电源线和地线的电磁辐射是串扰的主要来源之一。

当多个ADC芯片共享同一个电源或地线时,其中一个芯片的电流变化会通过电源或地线传播到其他芯片中,导致信号相互干扰。

ADC芯片本身的设计和布局也会影响串扰的程度。

例如,芯片之间的距离过近、布线不合理或者地线回路不良等都会增加串扰的可能性。

ADC芯片的工作频率和信号幅度也会对串扰产生影响。

当芯片的工作频率较高或者信号幅度较大时,串扰的问题更容易出现。

那么,串扰会对系统性能产生什么样的影响呢?首先,串扰会导致ADC芯片的输出信号失真。

由于信号相互干扰,原本应该是平滑连续的信号可能会出现波动或者断裂的情况,从而导致输出数据的准确性下降。

串扰还会引入额外的噪声。

由于信号相互干扰,本来应该是纯净的信号可能会受到其他信号的干扰,从而增加了系统的噪声水平,降低了信噪比。

串扰还会降低系统的采样精度。

由于信号相互干扰,原本应该是准确的采样值可能会发生偏移或者误差,从而影响系统对信号的准确度和精度。

面对ADC芯片之间的串扰问题,我们可以采取一些解决方案来减少其影响。

首先,合理设计和布局ADC芯片的电源和地线是非常重要的。

我们可以采取分离电源和地线、增加电源和地线的接地点、减小电源和地线的长度等方法来降低串扰的可能性。

选择合适的ADC芯片也可以减少串扰的问题。

一些高性能的ADC芯片在设计时考虑了串扰的问题,采用了一些抗串扰的技术,如分离电源和地线、采用差分信号输入等,可以有效地减少串扰的影响。

adc模块实验遇到的问题及收获

adc模块实验遇到的问题及收获篇一:ADC(自动分光光度计)模块是电子测量中常用的一种传感器,可以测量物体反射的光线的亮度和颜色等信息。

在实验中,ADC模块可能会遇到一些问题,下面是一些常见的问题和解决方法:1. 采样不足:当光线强度较低或者物体表面反射的光线较少时,ADC模块可能会采样不足,导致测量结果不准确。

解决方法是增加采样频率或者增加采样位数。

2. 测量误差:由于 ADC 模块本身的限制,如精度、分辨率等,可能会导致测量误差。

解决方法是选择合适的 ADC 模块、优化电路设计、提高信号传输距离等。

3. 接口不匹配:不同品牌、型号的 ADC 模块可能有不同的接口,如 USB、RS-232 等。

实验中需要确保接口匹配,否则可能会导致数据传输错误。

4. 电源电压不稳定:ADC 模块需要一定的电源电压,如果电源电压不稳定,可能会导致 ADC 模块无法正常工作。

解决方法是使用稳定的电源、设置稳压器等。

在实验中,通过解决这些问题,可以获得更好的实验结果。

此外,还可以学习到 ADC 模块的基本原理、应用场景、设计方法等方面的知识。

拓展:除了 ADC 模块本身的问题之外,实验中还可能会涉及到其他问题,如电路干扰、信号传输距离、信号噪声等。

这些问题都需要在实验中仔细排查和解决,以提高实验效果和准确度。

实验不仅仅是为了获得准确的测量结果,还需要学习实验设计、实验操作、数据处理等方面的知识和技能。

通过实验,可以加深对理论知识的理解和应用,提高实践能力和创新能力。

篇二:ADC(数字到模拟转换器)模块是电子电路中常用的一种模块,用于将数字信号转换为模拟信号。

在进行ADC模块实验时,可能会遇到一些问题,但通过解决这些问题,可以获得一些收获。

在实验过程中,可能会遇到以下问题:1. 输入信号过大或过小:ADC模块的输入信号范围通常有一定的限制,如果输入信号过大或过小,可能会导致模块无法正常工作。

因此,在实验前需要确保输入信号符合ADC模块的输入范围。

adc原理及应用出现的问题

ADC原理及应用出现的问题1. ADC原理简介ADC(Analog-to-Digital Converter)即模拟到数字转换器,是一种能将连续的模拟信号转换为相应的离散数字码的电子设备。

ADC广泛应用于各种领域,包括通信、电子测量、自动控制等。

2. ADC的分类根据不同的转换方式,ADC可以分为几种不同的类型:•逐次逼近型ADC:逐次逼近型ADC通过不断逼近来获取输入模拟信号的数字量,并输出对应的数字码。

•并行型ADC:并行型ADC同时将输入的模拟信号转换为多个并行输出的数字码。

•逐次逼近型ADC:逐次逼近型ADC通过逼近法逐步获取输入模拟信号的数字量,逐渐逼近最终结果。

3. ADC应用中可能出现的问题在ADC的应用过程中,常常会遇到一些问题,以下列举一些常见的问题及解决方法:3.1 量化误差量化误差是指模拟信号与对应数字码之间的差异。

量化误差由于ADC的分辨率有限和量化阶数引起。

当分辨率较低时,量化误差会更大。

解决方法包括提高分辨率、使用更高精度的ADC等。

3.2 噪声干扰特别是在低信噪比场景下,ADC输入信号中会受到噪声干扰。

噪声会引入ADC 中,导致输出数字码的不准确性。

解决方法包括降低噪声对信号的干扰、增加信号的信噪比等。

3.3 采样速率不足采样速率不足会导致输入模拟信号无法完整地被采样,进而导致输出结果的失真。

解决方法包括增加采样频率、使用更高速的ADC等。

3.4 温度漂移ADC的性能会受到温度变化的影响,可能导致输出结果的偏差。

解决方法包括使用温度补偿技术、选择温度稳定性较好的器件等。

3.5 输入阻抗问题ADC的输入阻抗可能对输入信号产生不良影响,例如降低信号电平、改变信号频率响应等。

解决方法包括选择合适的输入电路、减小电路中的冗余电流等。

4. 小结ADC作为模拟信号转数字码的重要组成部分,在各个领域都有着广泛的应用。

然而,在实际应用过程中,我们经常会遇到一些问题,如量化误差、噪声干扰、采样速率不足等。

五种高精度ADC中杂散问题分析及应对方法

五种⾼精度ADC中杂散问题分析及应对⽅法五种⾼精度ADC中杂散问题分析及应对⽅法虽然⽬前的⾼分辨率SAR ADC和Σ-ΔADC可提供⾼分辨率和低噪声,但系统设计师们可能难以实现数据⼿册上的额定SNR性能。

⽽要达到最佳SFDR,也就是在系统信号链中实现⽆杂散的⼲净噪底,可能就更加困难了。

杂散信号可能源于ADC周围的不合理电路,也有可能是因恶劣⼯作环境下出现的外部⼲扰⽽导致。

针对⾼分辨率、精密ADC应⽤中的杂散问题,本⽂将介绍⼏种判断其根本原因的⽅法,并提出相应的解决⽅案。

这些技术和⽅法将有助于提⾼终端系统的EMC能⼒和可靠性。

本⽂将针对五种不同的应⽤情况阐述⽤于降低杂散的特定设计解决⽅案:1、由控制器板上的DC-DC电源辐射⽽导致的杂散问题。

2、由AC-DC适配器噪声通过外部基准源⽽导致的杂散问题。

3、由模拟输⼊电缆⽽导致的杂散问题。

4、由模拟输⼊电缆上的耦合⼲扰⽽导致的杂散问题。

5、由室内照明设备导致的杂散问题。

6、杂散与SFDR众所周知,⽆杂散动态范围(SFDR)表⽰可从⼤⼲扰信号分辨出的最⼩功率信号。

对于⽬前的⾼分辨率、精密ADC,SFDR ⼀般主要由基波频率与⽬标基波频率的第⼆或第三谐波之间的动态范围构成。

然⽽,由于系统其他⽅⾯的因素,可能会导致杂散产⽣并限制系统的性能。

这些杂散可分为输⼊频率相关杂散和固定频率杂散。

输⼊频率相关杂散与谐波或⾮线性特性有关。

本⽂将重点分析由电源、外部基准源、数字连接、外部⼲扰等造成的固定频率杂散。

根据应⽤情况,可降低或完全避免这些类型的杂散,以助于实现最佳的信号链性能。

由ADC周围DC-DC电源⽽导致的杂散问题由于DC-DC开关稳压器会产⽣较⾼的纹波噪声,通常建议将LDO作为在精密测量系统中为精密ADC⽣成低噪声电源轨的解决⽅案。

固定频率或脉宽调制开关稳压器会产⽣开关纹波,该纹波⼀般位于⼏万⾄⼏兆赫兹固定频率处。

固定频率噪声可能会通过ADC的。

高分辨率Δ-ΣADC中有关噪声的十大问题

高分辨率Δ-ΣADC中有关噪声的十大问题任何高分辨率信号链设计的基本挑战之一是确保系统本底噪声足够低,以便模数转换器(ADC)能够分辨您感兴趣的信号。

例如,如果您选择ADS1261(一个24位低噪声Δ-ΣADC),您可在2.5 SPS下解析输入低至6 nVRMS,增益为128 V / V的信号。

但是,从系统的角度来看,您需要担心的不仅仅是ADC 噪声——毕竟所有组件(包括放大器、电压基准、时钟和电源)都会产生一些噪声——这些器件对系统噪声的累积影响是什么?更重要的是,您的系统能够解决您感兴趣的信号吗?为助您更好地理解系统噪声并将这些知识应用到您的设计中,我最近撰写了一篇名为“解决信号”的技术文章系列。

该系列探讨了典型信号链中的常见噪声源,并通过降低噪声和保持高精度测量的方法辅助理解。

以下是该系列中10个最关键的问题和答案,可帮助您开始使用精密ADC进行设计。

1.您将在ADC中发现何种类型的噪声?总ADC噪声有两个主要组成部分:量化噪声和热噪声。

量化噪声来自将无限数量的模拟电压映射到有限数量的数字代码的过程(图1左侧)。

因此,任何单个数字输出都可对应于数个模拟输入电压,这些电压可能相差一半的最低有效位(LSB)。

由于电导体内电荷的物理移动(图1右侧),热噪声是所有电子元件中固有的现象。

不幸的是,ADC终端用户不能干涉器件的热噪声,因为它是ADC设计的一个功能。

图1:量化噪声(左)和热噪声(右)热噪声和量化噪声是否同样影响低分辨率和高分辨率ADC?阅读第1部分“Δ-ΣADC中的噪声简介了解相关信息”。

2.如何测量和指定ADC噪声?ADC制造商使用两种方法来测量ADC噪声。

第一种方法将ADC的输入短接在一起,以测量由于热噪声导致的输出代码的微小变化。

第二种方法涉及输入具有特定幅度和频率的正弦波(例如1kHz下为1 VPP)并报告ADC如何量化正弦波。

图2展示了这些类型的噪声测量。

图2:正弦波输入测试设置(左)和输入短路测试设置(右)每类ADC使用哪种测量方法?请阅读第2部分中有关噪声测量方法和规范的更多信息。

单片机adc采样问题及解决方法

一、概述随着现代科技的飞速发展,单片机作为一种常见的嵌入式系统,广泛应用于各个领域。

在很多单片机应用中,采样外部模拟信号是一个非常重要的环节,而单片机内置的ADC(模数转换器)模块则是常用的采样工具。

然而,在实际应用中,单片机ADC采样过程中可能会遇到一些问题,如采样精度不高、采样速率不稳定等。

本文将介绍单片机ADC采样问题的具体原因以及解决方法。

二、单片机ADC采样问题分析1. 采样精度低单片机内置的ADC模块通常有一定的分辨率,如8位、10位、12位等。

但是在实际应用中,由于外部环境噪声、电源波动等因素影响,可能会导致ADC的采样精度降低。

采样精度低的情况会影响系统的测量准确性,特别是对于需要高精度测量的应用来说,这是一个非常严重的问题。

2. 采样速率不稳定在一些实时采样的应用中,采样速率的稳定性非常重要。

然而,在单片机ADC采样过程中,由于中断响应不及时、数据传输处理效率低等原因可能导致采样速率不稳定,从而影响系统的实时性能。

3. ADC输入阻抗不匹配ADC模块的输入端通常需要外部连接源,而外部源的输出电阻往往与ADC的输入阻抗不匹配。

如果ADC的输入阻抗比外部源的输出阻抗低很多,会导致信号采样时发生失真,从而影响采样精度。

三、单片机ADC采样问题解决方法针对上述单片机ADC采样问题,我们可以采取以下措施进行解决:1. 提高ADC模块的供电电压为了提高ADC的采样精度,可以尝试提高ADC模块的供电电压,这样可以减小电源噪声对采样精度的影响。

当然,在提高供电电压的同时也要考虑模块的额定工作电压范围,避免损坏模块。

2. 添加滤波电路在ADC输入端添加合适的滤波电路可以滤除外部环境的噪声,提高采样信号的稳定性和准确性。

常用的滤波电路有低通滤波器、带通滤波器等,具体选择应根据实际的采样信号频率和噪声特性进行。

3. 增加采样频率控制通过在软件层面上增加采样频率控制的功能,可以提高采样速率的稳定性。

通过定时器或者中断控制实现定时采样,避免因为系统负载变化而导致采样频率不稳定的问题。

STM32F0多路ADC采样中的BUG和解决方案

STM32F0多路ADC采样中的BUG和解决方案在STM32F0系列中,多路ADC采样时可能会出现一些问题,下面是一些常见的BUG以及对应的解决方案:1.ADC转换结果误差较大:-原因:ADC的转换精度受到参考电压和时钟精度的影响,以及输入信号的干扰等。

-解决方案:-确保参考电压稳定,可以使用稳压器等电压源。

-降低输入信号的干扰,可以使用滤波电路。

-选择合适的采样率和分辨率,根据实际需求调整。

-使用校准功能对ADC进行校准,可以提高转换精度。

2.ADC采样速度不稳定:-原因:在多通道ADC采样时,切换通道可能会引入额外的时间延迟,导致采样速度不稳定。

-解决方案:-配置ADC转换模式为扫描模式,使得ADC可以按照一定的顺序进行多通道采样。

-调整通道切换速度,可以通过增加延时或者降低采样速率来解决。

3.ADC采样结果不准确或者不稳定:-原因:在多路ADC采样时,可能存在模拟输入信号的串扰或者共模干扰,导致采样结果不准确或者不稳定。

-解决方案:-选择合适的参考电压和可靠的电源地,以减少参考电压的波动或者输入信号的干扰。

-适当延长采样时间,可以通过增加采样周期来提高稳定性。

-使用信号调制技术,如差分信号采样、抗共模干扰技术等。

4.ADC采样中断丢失:-原因:在多通道ADC采样时,如果不及时处理中断,可能会导致中断丢失。

-解决方案:-配置合适的优先级分组和中断优先级,以确保ADC中断能够得到及时处理。

-在中断处理函数中尽量减少处理时间,避免长时间占用CPU。

5.ADC采样时CPU占用率过高:-原因:在ADC连续转换模式中,如果没有合适的采样间隔,可能会导致CPU占用率过高。

-解决方案:-合理配置ADC的采样频率和采样间隔,根据实际需求进行调整。

-使用DMA传输数据,减少CPU的负载,提高系统的稳定性和响应速度。

以上是一些常见的STM32F0多路ADC采样中可能出现的BUG以及对应的解决方案,根据实际情况进行调试和优化,可以提高ADC的准确性和稳定性。

如何解决无损检测技术中的杂散信号问题

如何解决无损检测技术中的杂散信号问题无损检测技术是一种非破坏性的测试方法,广泛应用于工业制造、航空航天、铁路交通等领域。

然而,在实际应用中,杂散信号问题是无损检测技术中常见的挑战之一。

这些杂散信号会干扰到测试结果的准确性和可靠性。

因此,解决无损检测技术中的杂散信号问题对保证产品质量和安全至关重要。

本文将探讨解决无损检测技术中杂散信号问题的方法和策略。

一、增强信号处理能力首先,提高信号处理能力是解决无损检测技术中杂散信号问题的关键。

可以采用以下几种方法来增强信号处理能力:1. 优化信号采集系统:通过提高采样率、增强前置放大器的增益等手段,可以增强信号的强度和质量。

同时,选择合适的采集传感器和设备以及使用高品质的供电电源也有助于提高信号采集系统的性能。

2. 降低噪声水平:采用滤波器、去噪算法等方法,可以有效地降低噪声对于信号的干扰。

常见的噪声源包括电源噪声、信号线干扰等,通过减少这些噪声源可以提高信号的纯净度。

3. 使用高精度的数学模型:建立准确、可靠的数学模型,可以对信号进行更精确的分析和处理。

这种模型可以基于物理原理、统计学或其他适用的理论建立。

二、信号滤波和去噪信号滤波和去噪是解决杂散信号问题的重要手段之一。

以下是几种常见的信号滤波和去噪方法:1. 数字滤波器:数字滤波器通过对信号进行数字处理,滤除非目标信号的干扰成分。

常见的数字滤波器包括低通滤波器、带通滤波器、陷波滤波器等。

2. 小波变换:小波变换是一种对信号进行时频分析的方法,可以将信号分解为不同频率的小波系数。

通过设置合适的阈值和滤波器,可以去除杂散信号的干扰。

3. 统计方法:利用统计学的方法,可以对信号中的随机噪声进行建模和处理。

例如,使用平均滤波、中值滤波等方法可以降低噪声对信号的影响。

三、提高检测系统的抗干扰能力除了增强信号处理能力和使用信号滤波和去噪方法外,提高检测系统的抗干扰能力也是解决杂散信号问题的重要措施。

1. 选择合适的检测设备和传感器:不同的检测设备和传感器具有不同的抗干扰能力,选择合适的设备和传感器对于减少杂散信号的干扰至关重要。

Giga ADC 介绍及杂散分析(下)

Giga ADC 介绍及杂散分析(下)3、Giga ADC 杂散的分析ADC 应用中,输出的杂散信号决定了ADC 的动态范围。

在传统的流水线ADC 中,起决定作用的主要是谐波杂散,即输入信号的二次、三次或更高次谐波混叠进入第一个Nyquist 区。

除此以外,GigaADC的interleave 架构带来了其它杂散。

如前文说提到的,为了达到更高的采样速率,每路ADC 实际包括两个子ADC,这两个子ADC 工作在interleave 模式下。

在这种情况下,两路子ADC 之间的失配将会产生新的杂散信号。

总体来说,Giga ADC 的杂散主要分为三类杂散信号:1)interleave 杂散;2)固定频点杂散;3)和输入信号相关的杂散。

3.1 Interleave 相关的杂散Interleave 模式,如Figure7 所示,就是相同的输入信号,输入到两个(或N 个)采样率相同,但采样时钟相位相反(或相差2π/N)的ADC 中,从而达到采样率增倍的目的。

但由于两路ADC 不可能完全一致,存在一些失配,从而导致了一些输出杂散的生成。

这些失配包括偏置误差、增益误差以及采样时钟的相位误差。

这里假定:N:一路ADC 中包含的子ADC 个数Fin:输入有用信号Fnoise:输出的杂散信号Fs:ADC 采样时钟3.1.1 输入偏置误差假定ADC 其它参数都是理想的,只考虑输入偏置误差。

通过数学分析可以得到,输入偏置误差带来的杂散主要分布在从Figure13 可以看出,输入偏置误差带来的杂散和输入信号的幅度和频率没有关系,从频域上看,均匀的分布在第一Nyquist 区。

由输入偏置带来的杂散固定的分布在公式一给出的各个频点。

3.1.2 输入增益误差假定输入电路除增益误差以外,其它参数都是理想的,可以看出当输入信号幅度增大时,增益误差也随之变大。

输出的误差信号类似于输入信号的一个调。

ADC采样误差分析

ADC采样误差分析摘要本文将介绍ADC(模数转换器)采样过程中产生的误差,并分析其对数据准确性的影响。

首先,我们将回顾ADC的工作原理和采样流程。

接着,将介绍ADC采样误差的分类及其原因。

最后,将讨论一些解决ADC采样误差的方法。

1. ADC工作原理和采样流程回顾ADC是一种将模拟信号转换为数字信号的器件。

它通常由样本保持电路(Sample and Hold Circuit)、模拟到数字转换器(Analog-to-Digital Converter)和数字数据处理电路等组成。

ADC采样过程包括采样、保持和转换三个步骤。

在采样阶段,ADC对模拟信号进行离散化,即按一定时间间隔对输入信号进行采样。

采样过程中需要考虑信号的带宽、信噪比等因素。

在保持阶段,样本保持电路将采样到的信号保持在一个稳定的电压上,以便转换器能够准确地对信号进行转换。

保持阶段对信号保持时间的控制十分重要,过长或过短的保持时间都会引起误差。

在转换阶段,模拟信号被转换为数字信号。

转换器的精度和速度对转换结果的准确性有着重要影响。

ADC通常使用逐次逼近(Successive Approximation)或逐次逼近寻找法(SAR-ADC)进行模拟到数字的转换。

2. ADC采样误差的分类及原因ADC采样过程中会产生各种误差,主要包括量化误差、采样保持误差、线性度误差和噪声误差等。

2.1 量化误差量化误差是由于数字化过程中对模拟信号进行离散化所引起的误差。

在ADC 中,模拟信号被划分为多个离散的电平,每个电平对应一个数字代码。

量化误差即为模拟信号与其对应的数字代码之间的差值。

量化误差的主要原因是ADC的分辨率有限,即能够表示的电平数目是有限的。

2.2 采样保持误差采样保持误差是由于样本保持电路在信号保持阶段引入的误差。

样本保持电路在保持信号的过程中,可能会存在保持电容的不均匀性、采样切换的延迟等问题,导致采样信号与原始信号之间产生差异。

2.3 线性度误差线性度误差是指ADC在转换过程中由于非线性特性引起的误差。

ADC有哪些实际应用-如何利用噪声扰动提高ADC无杂散动态范围-

ADC有哪些实际应用?如何利用噪声扰动提高ADC无杂散动态范围?ADC是模数转换器的简称,在本文中不是游戏中的ADC哦。

为了增进大家对ADC的认识,本文将基于两个方面介绍ADC:1.ADC的实际应用、2.如何利用噪声扰动提高ADC无杂散动态范围。

如果你对ADC具有兴趣,不妨和我一起继续往下阅读哦。

一、ADC实际应用1.音乐录制模数转换器是2000年代音乐再现技术和基于数字音频工作站的声音记录所不可或缺的。

人们通常使用模拟记录在计算机上制作音乐,因此需要模数转换器来创建脉冲码调制(PCM)数据流,该数据流会进入光盘和数字音乐文件。

当前用于音乐的模数转换器可以以高达192 kHz的速率采样。

在这些问题上存在大量文献,但是商业考虑通常起着重要作用。

许多录音棚采用24位/ 96 kHz(或更高)脉冲编码调制(PCM)或直接流数字录音(DSD)格式,然后对信号进行下采样或抽取,以进行光盘数字音频制作(44.1 kHz),对于常用的广播和电视广播应用,由于人类的奈奎斯特频率和听觉范围,将其降低到48 kHz 。

2.数字信号处理要求ADC处理,存储或传输几乎任何数字形式的模拟信号。

例如,电视调谐卡使用快速视频模数转换器。

慢速片上8、10、12或16位模数转换器在微控制器中很常见。

数字存储示波器需要非常快速的模数转换器,这对于软件定义的无线电及其新应用也至关重要。

3.科学仪器数字成像系统通常使用模数转换器将像素数字化。

一些雷达系统通常使用模数转换器将信号强度转换为数字值,以进行后续信号处理。

许多其他原位和遥感系统通常使用类似技术。

所得数字化数值中的二进制位数反映了分辨率,xxx的离散量化级数(信号处理)。

模拟信号和数字信号之间的对应关系取决于量化误差。

量化过程必须以足够的速度进行,这可能会限制数字信号的分辨率。

科学仪器中的许多传感器都会产生模拟信号。

温度、压力、pH、光强度等。

所有这些信号都可以放大并馈送到模数转换器,以产生与输入信号成比例的数字。

ADC噪声分析与消除

ADC的输入噪声:好噪声,坏噪声和丑噪声。

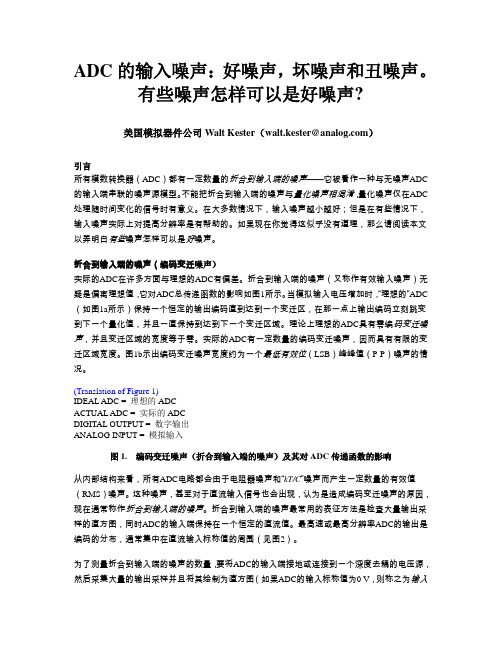

有些噪声怎样可以是好噪声?美国模拟器件公司Walt Kester(walt.kester@)引言所有模数转换器(ADC)都有一定数量的折合到输入端的噪声——它被看作一种与无噪声ADC 的输入端串联的噪声源模型。

不能把折合到输入端的噪声与量化噪声相混淆,量化噪声仅在ADC 处理随时间变化的信号时有意义。

在大多数情况下,输入噪声越小越好;但是在有些情况下,输入噪声实际上对提高分辨率是有帮助的。

如果现在你觉得这似乎没有道理,那么请阅读本文以弄明白有些噪声怎样可以是好噪声。

折合到输入端的噪声(编码变迁噪声)实际的ADC在许多方面与理想的ADC有偏差。

折合到输入端的噪声(又称作有效输入噪声)无疑是偏离理想值,它对ADC总传递函数的影响如图1所示。

当模拟输入电压增加时,“理想的”ADC(如图1a所示)保持一个恒定的输出编码直到达到一个变迁区,在那一点上输出编码立刻跳变到下一个量化值,并且一直保持到达到下一个变迁区域。

理论上理想的ADC具有零编码变迁噪声,并且变迁区域的宽度等于零。

实际的ADC有一定数量的编码变迁噪声,因而具有有限的变迁区域宽度。

图1b示出编码变迁噪声宽度约为一个最低有效位(LSB)峰峰值(P-P)噪声的情况。

(Translation of Figure 1)IDEAL ADC = 理想的ADCACTUAL ADC = 实际的ADCDIGITAL OUTPUT = 数字输出ANALOG INPUT = 模拟输入图1. 编码变迁噪声(折合到输入端的噪声)及其对ADC传递函数的影响从内部结构来看,所有ADC电路都会由于电阻器噪声和“kT/C”噪声而产生一定数量的有效值(RMS)噪声。

这种噪声,甚至对于直流输入信号也会出现,认为是造成编码变迁噪声的原因,现在通常称作折合到输入端的噪声。

折合到输入端的噪声最常用的表征方法是检查大量输出采样的直方图,同时ADC的输入端保持在一个恒定的直流值。

adc模块实验遇到的问题及收获

adc模块实验遇到的问题及收获篇一:ADC(自动检测数字电路)模块是一种将模拟信号转换为数字信号的电路,在数字电路和嵌入式系统中广泛应用。

在进行ADC模块的实验时,可能会遇到一些问题,下面是一些常见的问题以及相应的解决方法:1. 数据采集不完整:在采集模拟信号时,由于信号的幅度、频率等特性可能发生变化,导致数据采集不完整或者出现误差。

为了避免这个问题,可以使用滤波器或者采样定理等方法对信号进行预处理,以提高数据采集的准确性和完整性。

2. 数据位宽限制:ADC模块通常只能读取一定范围内的数字信号,超出范围的数据将无法读取。

为了解决这个问题,可以使用数字信号转换器或者硬件计数器等设备,将数据位宽扩展至需要的范围内。

3. 精度限制:ADC模块的精度受到内部电路和元器件的影响,可能无法满足高精度测量的需求。

为了解决这个问题,可以使用更高精度的ADC模块或者使用数字信号处理技术来提高测量精度。

4. 电源电压限制:ADC模块需要一定的电源电压来工作,如果电源电压不足,可能会导致ADC模块无法正常工作。

为了解决这个问题,可以使用稳定的电源供应系统或者采用电源转换器等设备,以保证ADC模块的正常工作。

在进行ADC模块的实验时,需要充分了解实验目的、实验条件和实验方法等因素,以确保实验的顺利进行和实验结果的准确性。

通过实验,可以深入了解ADC 模块的工作原理和实际应用,提高对数字电路和嵌入式系统的理解。

篇二:adc模块实验遇到的问题及收获ADC(数字信号采样与量化)模块是计算机系统中非常重要的组成部分,用于将模拟信号转换为数字信号,以便计算机能够处理和分析。

在ADC模块的实验中,可能会遇到一些问题,但通过解决这些问题,可以获得一些收获。

1. 精度问题在ADC模块的实验中,精度是非常重要的。

在输入信号噪声较大、采样频率较低或输入信号的幅度很小的时候,可能会出现精度问题。

为了解决这个问题,需要使用合适的采样频率、滤波器和放大器,以提高输入信号的精度。

ADC常见问题解答

#1楼主:工业应用Sigma-Delta ADC常见问题解答贴子发表于:2008/12/25 13:14:35问题:峰峰值噪声与有效噪声的区别,峰峰值分辨率与有效分辨率的区别?无失码分辨率又是指的什么?答案:无失码分辨率是对ADC线性性能的评价指标。

峰峰值分辨率和有效值分辨率是评价ADC噪声性能的重要指标。

它们之间的关系是峰峰值分辨率=有效分辨率-2.7 bits这个关系的理论基础是,噪声通常是随机的,并且它的分布是正态分布。

那么Vnoise (peak-to-peak) = Vnoise (rms) x 6.6;99.9%的出现概率如果转换为分辨率,就是2.7位的差别。

(log26.6=2.7)如果对应于ADC的转换结果,峰峰值分辨率是没有跳码的位数,也就是保持稳定的位数。

我们以AD7799为例,在数据手册中都会有两个表格,如下所示:第一个表格是在不同的增益和数据输出速率的条件下有效噪声的值。

第二个表格是在不同的增益和数据输出速率的条件下的有效分辨率和峰峰值分辨率。

例如,在16.7Hz数据输出速率,64倍增益条件下,有效噪声是0.065uV,对应的有效分辨率为20位,峰峰值分辨率为17.5位。

要了解具体的原理和推导,请参见ADI网站上的应用笔记AN-615“Peak to Peak Resolution vs. Effective Resolution”问题:为什么转换结果的后几位总在跳,是不是正常?答案:判断是不是正常要先了解造成这种情况的原因。

如果排除掉输入信号的原因,ADC转换结果的不稳定是由于噪声引起的。

在ADC的数据手册中对ADC在不同配置的情况下的噪声有详细的数据表格。

所以对于用户ADC的转换结果的分析,要进行与数据手册相同测试条件的测试,然后与表格中数据进行比较。

数据手册中的噪声性能表格中的数据结果的测试条件是:使用高精度低噪声的参考电压源,短路ADC的差分输入端并接到正确的共模电平上,然后设置ADC的增益、滤波器系数,C HOP模式,BUFFER状态等等,然后采集足够多的转换结果,一般至少要几百个样本,做噪声分析。

Giga ADC 介绍及杂散分析

Giga ADC 介绍及杂散分析Giga ADC 是 TI 推出的采样率大于 1GHz 的数据转换产品系列,主要应用于微波通信、卫星通信以及仪器仪表。

本文介绍了 Giga ADC 的主要架构以及 ADC 输出杂散的成因分析,以及优化性能的主要措施。

1、Giga ADC 架构及 TI 的 Giga ADC1.1 Giga ADC 架构演进Giga ADC 目前已经广泛的应用于数据采集、仪器仪表、雷达和卫星通信系统;随着采样速率和精度的进一步提高,越来越多的无线通信厂商开始考虑使用 Giga ADC 实现真正的软件无线电。

软件无线电不仅可以简化接收通道设计,同时可以方便不同平台的移植和升级,从而降低开发成本和周期。

Figure 1 列出了在使用各种采样架构下,采样精度和采样速率之间关系。

随着技术和工艺的发展,各种架构可以支持的采速率在不断的提升,但就目前的水平来看,要实现 1Gpbs 以上的采样率,必须采用 Flash 或者折叠(Folding)架构。

这主要是因为在其它架构中,都采用了反馈环路;这些反馈环路的传输延时限制了 ADC 速率的进一步提升。

例如在 pipeline 中,每一级都有一个 DAC,用于把本级的数据输出转换成模拟信号,反馈给本级的模拟输入,取差以后放大输出给下一级。

类似的限制也存在于Subranging 或者 multi-step 架构中,都需要一个反馈环路辅助判决。

另一方面,虽然目前业界最快的 ADC 架构是 Flash 架构,但一个 N bit 的 flash ADC 需要2N-1 个比较器,当 N>= 8 时,比较器的数量将会非常庞大;而且随着转换精度的增加,后端的译码逻辑也会变得异常复杂;这些都会对芯片的体积和功耗造成很大的影响。

所以在 TI 的 Giga ADC 中,采用了折中的折叠(folding)架构。

事实上,折叠是和flash 类似的架构,不同的是,在折叠架构中,输入信号分别通过了粗分 ADC 和折叠电路+细分 ADC;折叠电路的理想传输特性为三角状循环的折叠信号。

ADC噪声分析与消除

ADC的输入噪声:好噪声,坏噪声和丑噪声。

有些噪声怎样可以是好噪声?美国模拟器件公司Walt Kester(walt.kester@)引言所有模数转换器(ADC)都有一定数量的折合到输入端的噪声——它被看作一种与无噪声ADC 的输入端串联的噪声源模型。

不能把折合到输入端的噪声与量化噪声相混淆,量化噪声仅在ADC 处理随时间变化的信号时有意义。

在大多数情况下,输入噪声越小越好;但是在有些情况下,输入噪声实际上对提高分辨率是有帮助的。

如果现在你觉得这似乎没有道理,那么请阅读本文以弄明白有些噪声怎样可以是好噪声。

折合到输入端的噪声(编码变迁噪声)实际的ADC在许多方面与理想的ADC有偏差。

折合到输入端的噪声(又称作有效输入噪声)无疑是偏离理想值,它对ADC总传递函数的影响如图1所示。

当模拟输入电压增加时,“理想的”ADC(如图1a所示)保持一个恒定的输出编码直到达到一个变迁区,在那一点上输出编码立刻跳变到下一个量化值,并且一直保持到达到下一个变迁区域。

理论上理想的ADC具有零编码变迁噪声,并且变迁区域的宽度等于零。

实际的ADC有一定数量的编码变迁噪声,因而具有有限的变迁区域宽度。

图1b示出编码变迁噪声宽度约为一个最低有效位(LSB)峰峰值(P-P)噪声的情况。

(Translation of Figure 1)IDEAL ADC = 理想的ADCACTUAL ADC = 实际的ADCDIGITAL OUTPUT = 数字输出ANALOG INPUT = 模拟输入图1. 编码变迁噪声(折合到输入端的噪声)及其对ADC传递函数的影响从内部结构来看,所有ADC电路都会由于电阻器噪声和“kT/C”噪声而产生一定数量的有效值(RMS)噪声。

这种噪声,甚至对于直流输入信号也会出现,认为是造成编码变迁噪声的原因,现在通常称作折合到输入端的噪声。

折合到输入端的噪声最常用的表征方法是检查大量输出采样的直方图,同时ADC的输入端保持在一个恒定的直流值。

破解神秘杂散之谜: 别责怪DDC!

破解神秘杂散之谜:别责怪DDC!

最近在评估贵公司一款集成数字下变频器(DDC)功能的高速ADC 的输出频谱时,一些人发现了一些奇怪的现象。

针对这一现象,什么样的回答才能解释为什么存在一种神秘的杂散呢?

DDC 包括一个抽取滤波器,它可以消除传统的输入抗混叠滤波要求,同时又以数字方式滤出目标基带信号,要处理的净有效数据量会更少。

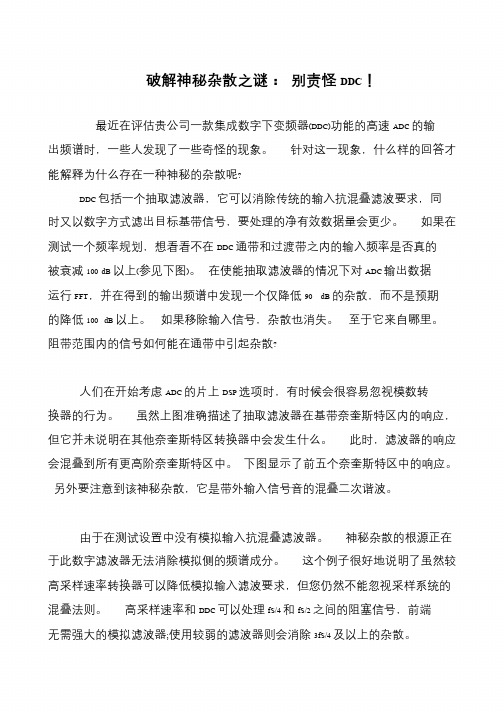

如果在测试一个频率规划,想看看不在DDC 通带和过渡带之内的输入频率是否真的被衰减100 dB 以上(参见下图)。

在使能抽取滤波器的情况下对ADC 输出数据运行FFT,并在得到的输出频谱中发现一个仅降低90 dB 的杂散,而不是预期的降低100 dB 以上。

如果移除输入信号,杂散也消失。

至于它来自哪里。

阻带范围内的信号如何能在通带中引起杂散?

人们在开始考虑ADC 的片上DSP 选项时,有时候会很容易忽视模数转换器的行为。

虽然上图准确描述了抽取滤波器在基带奈奎斯特区内的响应,但它并未说明在其他奈奎斯特区转换器中会发生什么。

此时,滤波器的响应会混叠到所有更高阶奈奎斯特区中。

下图显示了前五个奈奎斯特区中的响应。

另外要注意到该神秘杂散,它是带外输入信号音的混叠二次谐波。

由于在测试设置中没有模拟输入抗混叠滤波器。

神秘杂散的根源正在于此数字滤波器无法消除模拟侧的频谱成分。

这个例子很好地说明了虽然较高采样速率转换器可以降低模拟输入滤波要求,但您仍然不能忽视采样系统的混叠法则。

高采样速率和DDC 可以处理fS/4 和fS/2 之间的阻塞信号,前端无需强大的模拟滤波器;使用较弱的滤波器则会消除3fS/4 及以上的杂散。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

五种高精度ADC中杂散问题分析及应对方法

虽然目前的高分辨率SAR ADC和Σ-ΔADC可提供高分辨率和低噪声,但系统设计师们可能难以实现数据手册上的额定SNR性能。

而要达到最佳SFDR,也就是在系统信号链中实现无杂散的干净噪底,可能就更加困难了。

杂散信号可能源于ADC周围的不合理电路,也有可能是因恶劣工作环境下出现的外部干扰而导致。

针对高分辨率、精密ADC应用中的杂散问题,本文将介绍几种判断其根本原因的方法,并提出相应的解决方案。

这些技术和方法将有助于提高终端系统的EMC能力和可靠性。

本文将针对五种不同的应用情况阐述用于降低杂散的特定设计解决方案:

1、由控制器板上的DC-DC电源辐射而导致的杂散问题。

2、由AC-DC适配器噪声通过外部基准源而导致的杂散问题。

3、由模拟输入电缆而导致的杂散问题。

4、由模拟输入电缆上的耦合干扰而导致的杂散问题。

5、由室内照明设备导致的杂散问题。

6、杂散与SFDR

众所周知,无杂散动态范围(SFDR)表示可从大干扰信号分辨出的最小功率信号。

对于目前的高分辨率、精密ADC,SFDR一般主要由基波频率与目标基波频率的第二或第三谐波之间的动态范围构成。

然而,由于系统其他方面的因素,可能会导致杂散产生并限制系统的性能。

这些杂散可分为输入频率相关杂散和固定频率杂散。

输入频率相关杂散与谐波或非线性特性有关。

本文将重点分析由电源、外部基准源、数字连接、外部干扰等造成的固定频率杂散。

根据应用情况,可降低或完全避免这些类型的杂散,以助于实现最佳的信号链性能。

由ADC周围DC-DC电源而导致的杂散问题

由于DC-DC开关稳压器会产生较高的纹波噪声,通常建议将LDO作为在精密测量系统中为精密ADC生成低噪声电源轨的解决方案。

固定频率或脉宽调制开关稳压器会产生开关纹波,该纹波一般位于几万至几兆赫兹固定频率处。

固定频率噪声可能会通过ADC的。