基于FPGA的VHDL语言m序列生成详解+源码

VHDL源代码

VHDL源代码:library ieee; --显示器彩条发生器use VGA isport(clk,mode :in std_logic; --扫描时钟/显示模式选择时钟d,hs,vs,r,g,b:out std_logic); --行,场同步/红,绿,蓝end VGA;architecture a of VGA issignal hs1,vs1,fclk,cclk,divide_clk,dly: std_logic;signal mmode :std_logic_vector(1 downto 0); --方式选择signal cnt :std_logic_vector(2 downto 0);signal fs :std_logic_vector(3 downto 0);signal cc :std_logic_vector(4 downto 0); --行同步/横彩条生成 signal ll :std_logic_vector(8 downto 0); --长同步/竖彩条生成 signal grbh :std_logic_vector(3 downto 1); --X 横彩条signal grby :std_logic_vector(3 downto 1); --Y 竖彩条signal grbx :std_logic_vector(3 downto 1); --文字signal grbt :std_logic_vector(3 downto 1); --图案signal grbp :std_logic_vector(3 downto 1);signal grb :std_logic_vector(3 downto 1);signal x :integer range 0 to 800;signal x1: integer range 0 to 800;signal y1: integer range 0 to 600;signal x2: integer range 0 to 800;signal x3: integer range 0 to 800;signal x4: integer range 0 to 800;signal x5: integer range 0 to 800;signal x7: integer range 0 to 800;signal x8: integer range 0 to 800;signal x9: integer range 0 to 800;signal x10: integer range 0 to 800;signal x11: integer range 0 to 800;signal y2: integer range 0 to 600;signal y3: integer range 0 to 600;signal y4: integer range 0 to 600;signal y5: integer range 0 to 600;signal y6: integer range 0 to 600;signal c: integer range 0 to 30;begingrb(3)<=(grbp(3) xor mode) and hs1 and vs1;grb(2)<=(grbp(2) xor mode) and hs1 and vs1;grb(1)<=(grbp(1) xor mode) and hs1 and vs1;process(mode)beginif mode'event and mode='1' thenif mmode="11" thenmmode<="00";elsemmode<=mmode+1;end if;end if;end process; --四种模式process (mmode)beginif mmode="00" then grbp<=grbx;elsif mmode="01" then grbp<=grbh; --选择横彩条 elsif mmode="10" then grbp<=grby; --选择竖彩条elsif mmode="11" then grbp<=grbh xor grby; --选择棋盘格 else grbp<="000";end if;end process;process(clk) --3/4分频 beginif clk'event and clk='1' thencnt<=cnt+3;dly<=cnt(2);end if;--if cnt<3 then-- divide_clk<='0';--elsif cnt<5 then-- divide_clk<='1';--else-- cnt<="000";--end if;end process;divide_clk<=(cnt(2) xor dly) and clk;process(divide_clk) --13分频beginif divide_clk'event and divide_clk='1' thenif fs=12 thenfs<="0000";elsefs<=fs+1;end if;end if;end process;process(fclk)beginif fclk'event and fclk='1' thenif cc=29 thencc<="00000";elsecc<=cc+1;end if;end if;end process;d<=fclk;process(cclk)beginif cclk'event and cclk='1' thenif ll=481 thenll<="000000000";elsell<=ll+1;end if;end if;end process;process(cc,ll)beginif cc>23 then --行同步hs1<='0';elsehs1<='1';end if;if ll>479 then --长同步 vs1<='0';elsevs1<='1';end if;end process;process(clk)beginif clk'event and clk='1' thenif hs1='0' thenx<=0;elsex<=x+1;end if;end if;end process;process(x,ll,cc,hs1,vs1)variable s1: integer range 0 to 3;beginif cc<3 then grbh<="111"; --竖彩条 elsif cc<6 then grbh<="110";elsif cc<9 then grbh<="101";elsif cc<12 then grbh<="100";elsif cc<15 then grbh<="011";elsif cc<18 then grbh<="010";elsif cc<21 then grbh<="001";else grbh<="000";end if;if ll<60 then grby<="111"; --横彩条 elsif ll<120 then grby<="110";elsif ll<180 then grby<="101";elsif ll<240 then grby<="100";elsif ll<300 then grby<="011";elsif ll<360 then grby<="010";elsif ll<420 then grby<="001";else grby<="000";end if;if x=4 thengrbx<="100";elsif x=180 thengrbx<="001";elsegrbx<="000";end if;if ll>20 and ll<24 thenif x<110 thengrbx<="100";end if;end if;if ll>30 and ll<33 thenif x<80 thengrbx<="100";end if;end if;if ll>445 and ll<449 thenif x>90 thengrbx<="001";end if;end if;if ll>437 and ll<440 thenif x>100 thengrbx<="001";end if;end if;--"湖"if ll>89 and ll<94 thenif x=100 or x=103 or x=106 or x=107 or x=108 then grbx<="110";end if;end if;if ll>93 and ll<98 thenif x=102 or x=103 or x=104 or x=106 or x=108 then grbx<="110";end if;end if;if ll>97 and ll<102 thenif x=100 or x=103 or x=106 or x=107 or x=108 then grbx<="110";end if;end if;if ll>101 and ll<106 thenif x=102 or x=103 or x=104 or x=106 or x=108 thengrbx<="110";end if;end if;if ll>105 and ll<110 thenif x=100 or x=102 or x=104 or x=106 or x=107 or x=108 then grbx<="110";end if;end if;if ll>109 and ll<114 thenif x=100 or x=102 or x=103 or x=104 or x=106 or x=108 then grbx<="110";end if;end if;if ll>113 and ll<118 thenif x=106 thengrbx<="110";end if;end if;--"南"if ll>121 and ll<126 thenif x=104 thengrbx<="110";end if;end if;if ll>125 and ll<130 thenif x>99 and x<109 thengrbx<="110";end if;if ll>129 and ll<134 thenif x=104 thengrbx<="110";end if;end if;if ll>133 and ll<138 thenif x>99 and x<109 thengrbx<="110";end if;end if;if ll>137 and ll<142 thenif x=100 or x=108 thengrbx<="110";end if;end if;if ll>141 and ll<146 thenif x=100 or x=103 or x=105 or x=108 thengrbx<="110";end if;end if;if ll>145 and ll<150 thenif x=100 or x=102 or x=103 or x=104 or x=105 or x=106 or x=108 then grbx<="110";end if;end if;if ll>149 and ll<154 thenif x=100 or x=104 or x=108 thengrbx<="110";end if;if ll>153 and ll<158 thenif x=100 or x=102 or x=103 or x=104 or x=105 or x=106 or x=108 thengrbx<="110";end if;end if;if ll>157 and ll<162 thenif x=100 or x=104 or x=108 thengrbx<="110";end if;end if;--"大"if ll>165 and ll<170 thenif x=103 or x=104 thengrbx<="110";end if;end if;if ll>169 and ll<174 thenif x=103 or x=104 thengrbx<="110";end if;end if;if ll>173 and ll<178 thenif x=100 or x=101 or x=102 or x=103 or x=104 or x=105 or x=106 or x=107 or x=108 thengrbx<="110";end if;end if;if ll>177 and ll<182 thenif x=103 or x=104 thengrbx<="110";end if;end if;if ll>181 and ll<186 thenif x=103 or x=104 thengrbx<="110";end if;end if;if ll>185 and ll<190 thenif x=103 or x=105 thengrbx<="110";end if;end if;if ll>189 and ll<194 thenif x=102 or x=103 or x=106 thengrbx<="110";end if;end if;if ll>193 and ll<198 thenif x=101 or x=102 or x=107 thengrbx<="110";end if;end if;if ll>197 and ll<202 thenif x=100 or x=101 or x=107 or x=108 then grbx<="110";end if;end if;--"学"if ll>205 and ll<210 thenif x=102 or x=104 or x=106 thengrbx<="110";end if;end if;if ll>209 and ll<214 thenif x=100 or x=101 or x=102 or x=103 or x=104 or x=105 or x=106 or x=107 or x=108 thengrbx<="110";end if;end if;if ll>213 and ll<218 thenif x=100 or x=108 thengrbx<="110";end if;end if;if ll>217 and ll<222 thenif x=102 or x=103 or x=104 or x=105 or x=106 thengrbx<="110";end if;end if;if ll>221 and ll<226 thenif x=105 thengrbx<="110";end if;end if;if ll>225 and ll<230 thenif x=104 thengrbx<="110";end if;end if;if ll>229 and ll<234 thenif x=100 or x=101 or x=102 or x=103 or x=104 or x=105 or x=106 or x=107 or x=108 thengrbx<="110";end if;end if;if ll>233 and ll<238 thenif x=104 thengrbx<="110";end if;end if;if ll>237 and ll<242 thenif x=104 thengrbx<="110";end if;end if;if ll>241 and ll<245 thenif x=103 or x=104 thengrbx<="110";end if;end if;if vs1'event and vs1='1' thenif c=20 thenc<=0;case s1 iswhen 0 =>if x1=120 thens1:=1;elsex1<=x1+1 ; end if;when 1 =>if y1=350 thens1:=2;elsey1<=y1+1; end if;when 2 =>if x1=35 thens1:=3;elsex1<=x1-1; end if;when 3 =>if y1=280 thens1:=0;elsey1<=y1-1; end if;end case;elsec<=c+1;end if;end if;--"HU NAN DA XUE"x2<=x1+1;x3<=x1+2;x4<=x1+3;x5<=x1+5;x7<=x1+7;x8<=x1+8;x9<=x1+9;x10<=x1+10;x11<=x1+11;--y1<=250;y2<=y1+4;y3<=y1+8;y4<=y1+12;y5<=y1+16;y6<=y1+20;if ll>=y1 and ll<y2 thenif x=x1 or x=x5 or x=x7 or x=x8 or x=x11 thengrbx<="101";end if;end if;if ll>=y2 and ll<y3 thenif x=x1 or x=x5 or x=x7 or x=x8 or x=x9 or x=x11 then grbx<="101";end if;end if;if ll>=y3 and ll<y4 thenif x=x1 or x=x2 or x=x3 or x=x4 or x=x5 or x=x7 or x=x9 or x=x11 then grbx<="101";end if;end if;if ll>=y4 and ll<y5 thenif x=x1 or x=x5 or x=x7 or x=x10 or x=x11 thengrbx<="101";end if;end if;if ll>=y5 and ll<y6 thenif x=x1 or x=x5 or x=x7 or x=x10 or x=x11 thengrbx<="101";end if;end if;if ll>100 and 11<150 then --图案设计if ll>121 and ll<126 thenif x>43 and x<57 thengrbx<="100";end if;elsif x=50 thengrbx<="100";end if;end if;if ll>150 and 11<200 thenif ll>171 and ll<176 thenif x>60 and x<74 thengrbx<="010";end if;elsif x=67 thengrbx<="010";end if;end if;if ll>200 and 11<250 then if ll>221 and ll<226 then if x>74 and x<88 then grbx<="001";end if;elsif x=81 thengrbx<="001";end if;end if;end process;fclk<=fs(2);cclk<=cc(4);hs<= not hs1;vs<= not vs1;g<=grb(3);r<=grb(2);b<=grb(1);end a;。

基于VHDL的m序列

(1) 随机性 m 序列一个周期N = 2n- 1 内“1”和“0”的码元 数大致相等, “0”出现 2n- 1- 1 次, “1”出现 2n- 1次 (“1”比“0”只多一个) 。m 序列中连续的为“1”或

收稿日期: 2003 数称为游程长度。一个周期 P = 2n- 1 内, 共有 2n- 1个游程, 其中长度为 1 (单“1”, 或 单 “0 ”, ) 的 游 程 占 总 游 程 的 1 2, 长 度 为 2 ( “11”或 “00”) 的游程占总游程的 1 4, 长度为 3 ( “111”或“000”) 的游程占总游程的 1 8, 长度为 k 的 游程占总游程的 1 2k, 只有一个包含 (n 一 l) 个 “0”的游程, 也只有一个包含 n 个 “1”的游程。

示断开, C i= 1 表示连接。因此这个N 阶移位寄存器的

反馈函数为:

n

∑ F (X 1, X 2, …, X n) =

C iX i

i= 1

特征多项式是:

n

∑ f (x ) =

C iX i = C 0 + C 1X 1 + C 2X 2 + … + C nX n

i= 0

特征多项式中的 X i ( i= 0, 1, 2111n) 与移位寄

m Sequence Ba sed on VHDL

FAN Q iuhua, J I Hongyan

(D ep artm en t of Com p u ter Engineering, Q ingdao In stitu te of A rch itech tu re Engineering, Q ingdao, 266033, Ch ina)

《现代电子技术》2003 年第 7 期总第 150 期

基于FPGA的m序列发生器的设计

的周期最长的一种基本序 列。本文首先分析m序列 的基本原 理 、结构 、性质 ,然 后实现了1 位m序列 的仿真 以 5 及硬件 实现 ,最终用示波器 观察 波形。实验表 明 ,使 用该方法实现 的m 序列发生器 , 结构简单, 快, 用范 速度 适

围广。

关键词 :m序列 ;伪随机码 ;F GA P

号 , 还可用作噪声源及在保密通 信中起加密作用等 。伪噪声

发生器在 测距 、通信 等领域的应用 日益受 到人 们重视 。有

灵活性 , 且由于 F G 并 P A便于实现大规模的数字系统 , 中 其

中 图 分 类 号 : N9 5 . T 2 +9 文献标识码 : A

D e i f di t lt a m it r ba e sgn o gia r ns t e s d on FPG A

G oL i h nZ i a g a e,C e hq n ,W uLh i P  ̄i g i iu , uNa a n ( n tue f i a Ca tr g&P o e igT c n lg , a ie i f hn , a u n0 0 5 , hn ) Istt g l p i i oSn u n r c sn eh oo yNo hUnv r t o ia i a ,3 0 C ia s sy C T y 1

2 " 年 8月 o 第 8期

电 子

测

试

ELECTR0N I C T ES T

Aug. 2011 N o. 口

基于F G P A的m序列 发生器 的设 计★

高磊 ,陈志强 ,吴黎 慧 ,蒲南江 ( 中北大 学信息探测 与处理技术研究所 ,山西 太原 0 0 5 ) 3 0 1 摘要 :随机码越来越受 到人 们的重视 ,被广泛应用于导弹 、卫 星、飞船轨道 测量和 跟踪 、雷达 、导航 、移动通 信 、保密通 信和通 信系统性能的测量 以及 数字信息处理系统 中。1序 列是 伪随机码 中,带线性反馈移位寄存器 T I

基于FPGA的M序列的设计与实现

0 引言

扩频 通信 系统 与传统 通信 系统 的区别 在 于其

利 用伪 随机序 列来 实现 扩频 与解 扩步 骤 。而伪 随 机 序列 作为扩 频通 信系 统 的关 键 ,将 直接 影 响到

系统 的性 能 。

实 现 同步 与 捕获 等 都 与 扩频 码 的设 计 密 切相 关 。

自相关 函数 .即 :

6 电 子元 器 件 主 用 20. 4 079

. dan e c c c

维普资讯

第9 卷

期 2 7第月 0年 9 0 9

莲钎渗

V1 N. o o . 9 9

S . 2 07 ep 0

f l

当r 0 =

香农在 证 明编码 定理 的时候 ,也 提 出 了使 用具 有 白噪声 统计特性 的信号 来编码 。

通 常采 用 的 二 电平 ( ,1 0 )伪 随 机 序列 的结 构 已预先 确定 ,但 它们 都具 有类 似 白噪声 的相 关 特性 ,只是 幅度概 率分 布不 再服 从高 斯分 布 。伪

22 基 于 V D 语 言 的 F G . H L P A实 现

FG P A器 件 具 有 集 成 度 高 、编 程 灵 活 、阵 列 引脚 数 多 、功 耗 低 、设 计 编程 速 度 快 等 特 点 [ 4 1 。 Q ats1 . A tr 司第 五 代 可 编 程 逻 辑 器 u r 0是 l a公 u I5 e 件 的集 成开 发 环 境 。该 软件 可 提供 从 设 计 输入 、 设计 编译 、功能 仿 真 、设 计处 理 、时 序仿 真 到器

尺 小 于C,二 是 编 码 的 码 长 周 期 足 够 长 。 同 时 ,

以确保 抗 侦破 、抗 干扰 的要求 。

基于VHDL可编程m序列发生器的设计及应用

m 序列 广泛应 用 于数字基 带信 号进行 加扰 , 改 善 数字 序列 的位 定 时质 量 与 帧 同步 和 自适 应 时 域 均 衡性 能 , 同时 也是 构 造 平衡 G L O D码 的基 础 . 目 前 , 序 列产 生 电路 的实 现方 法主要 有 3种 : i n 1 )门电路实 现 . 方法设 计简 单 , 随移位 寄 该 但 存 器级 数 的增长 , 电路 装 调 困难 , 占用 的 印制 板 且

计输 入 、 速处 理和器 件编 程 引. 快

线 性反 馈移 位寄存 器 的特征 多项 式 :

摘要 : 介绍 了在 实 际教 学 中应 用 V L设计 出一 种能产 生 1 序 列数 字信 号 的发 生 器. HD T I 该序 列发 生 器具 有序 列长 度 和反 馈 连 接 设 置 , 能产 生 多种 i 列 波形 的 特 点. 软 件 上 采 用 Ata公 司 的 n序 在 lr e

种 序列 . 在今 天 的数 字 信 号 的传 输 中 , 发送 机往

往要 加扰码 器 , 对应 的接 收 端要 加 解 扰器 , n 相 而 l

序列 属 于伪 噪声 序列 和 伪 随 机序 列 , 容 易产 生 、 它

规律 性强 、 很 好 的 自相 关 性 和 较 好 的互 相 关 特 有

一

2 S 程实现 . )D P编 该方 法专 业性 过强 , 适合 不

实际教 学 中应 用. 3 H L与 C L )V D P D实现 . 由于 C L P D的高 集成

度, 而且 V L语 言 编程 较 为 方便 , 可 以大 大减 HD 故

少 电路 的装调 的 困难.

V D H L已成 为 电子工 程 领 域 事实 上 的 通 用硬

基于FPGA的m序列信号发生器设计

基于FPGA的m序列信号发生器设计摘要:m序列是一种伪随机序列(PN码),广泛用于数据白噪化、去白噪化、数据传输加密、解密等通信、控制领域。

基于FPGA与Verilog硬件描述语言设计井实现了一种数据率按步进可调、低数据误码率、反馈多项式为的m序列信号发生器。

系统时钟为20MHz,m序列信号发生器输出的数据率为20~100 kbps,通过2个按键实现20 kbps步进可调与系统复位,输出误码率小于1%。

m序列是最长线性反馈移位寄存器序列的简称,它是由带线性反馈的移位寄存器产生的周期最长的一种伪随机序列。

是由移位寄存器、反馈抽头及模2加法器组成。

m序列一旦反馈多项式及移位寄存器初值给定,则就是可以预先确定并且可以重复实现的序列,该特点使得m序列在数据白噪化、去白噪化、数据传输加密、解密等通信、控制领域使用广泛。

因此,深入学习研究m序列具有重要的实际意义。

1 m序列信号发生器的组成基于FPGA的m序列信号发生器硬件结构极其简单,仅需两个独立按键(一个是复位按键与另一个控制数据率切换按键)、一个48 MHz 的用于提供系统时钟有源晶振、系统电源、一块配置芯片、几个简单的电阻与电容即可实现。

按键去抖动、按键复位、按键切换数据率、时钟分频等功能均在FPGA内部编程实现。

2 m序列信号发生器的关键设计本文中m序列信号发生器的反馈多项式为。

其反馈及移位寄存器的关系图如图2所示。

从本设计中的反馈及移位寄存器的关系图可以看出,一个时钟周期,移位寄存器右移一位,最高位输入为x0、x2、x3、x4及x8的异或(模2相加)。

m序列的输出是移位寄存器的最低位。

图2所示的关系是m序列呈现为随机性、周期性的根本原因。

为了满足信号发生器输出数据率20 kbps的步进通过按键可调,则生成按步进20 kbps可调的时钟是实现该功能的关键。

当按键发生,时钟的输出频率加20 kbps。

在实际电路中,按键会有很大抖动,对系统会造成很大的不稳定性,因此,必须想办法减小这样的不利影响。

基于FPGA的简易m序列信号发生器

基于FPGA的简易m序列信号发生器【摘要】本系统基于FPGA为控制核心,采用EXCD-XC3S500E开发板及模拟电路,完成了简易数字m序列信号发生器的设计,实现对数字m序列信号的生成与发送。

【关键词】FPGA;m序列信号;曼彻斯特编码1.方案论证与比较数字信号为m序列,m序列发生器是一种反馈移位型结构的电路,它由n 位移位寄存器加异或反馈网络组成,反馈多项式为本原多项式。

实现移位寄存器的长与反馈式的编程选择,即可实现对m序列的控制。

m序列码发生器是一种反馈移位型结构的电路,它由n位移位寄存器加异或反馈网络组成,其序列长度M=2n-1 。

序列信号发生器一般有两种结构形式:一种是反馈移位型,另一种是计数型。

方案一:反馈移位型序列信号发生器反馈移位型序列码发生器的结构框图如图1所示,它由移位寄存器和组合反馈网络组成,从移存器的某一输出端可以得到周期性的序列码。

方案二:计数型序列码发生器计数型序列码发生器结构框图如图2所示。

它由计数器和组合输出网络两部分组成,序列码从组合输出网络输出。

综合比较,本次设计时由于已知数字信号和伪随机信号各自的f(x)表达式,故采用方案一,采用VHDL硬件描述语言,在XILINX的开发板上编程实现产生所要求的数字信号。

2.系统设计数字信号V为f(x)=1+x +x +x +x 的m序列,采用线性移位寄存器发生器产生数字信号和对应的时钟信号,要求数据率10~100kbps,步进值10kbps,其误差绝对值不大于1%,输出信号为TTL电平。

m序列数字信号是基于FPGA的存储器结构,采用线性移位寄存器发生器产生m序列的本原多项式,并且可以对任意级数的m序列发生器采用VHDL语言进行编写。

其产生原理是m序列信号发生器是在n级线性移位寄存器的基础上可以产生多个m序列,而每一个m序列有对应着一个确定的反馈函数,m序列线性移位寄存器在逻辑上仅可用加法器实现。

其反馈函数:本原多项式f1(x)=1+x +x +x +xm序列的移位寄存器逻辑反馈:f1(x)=x(8)⊕x(4)⊕x(3)⊕x(2)反馈移位寄存器的逻辑功能图如图3所示。

两种利用FPGA产生m序列的算法分析

两种利用FPGA产生m序列的算法分析作者:陈天成王艳红来源:《现代电子技术》2014年第05期摘要:为了产生性能良好且节省硬件资源的m序列,分别提出了基于现场可编程门阵列(FPGA)的逻辑法和核调用法两种算法,并详细介绍了两种算法的实现步骤。

通过在Xilinx 公司的NEXYS3开发板上进行设计和编程,对两种算法的可行性进行了检测;并结合ISE编程软件的仿真功能和Matlab对算法的自相关性、硬件占用率和实现难度等性能进行了分析。

最终,了解到核调用法在m序列产生中的优越性。

关键词: m序列; FPGA; IP核; ISE中图分类号: TN919⁃34 文献标识码: A 文章编号: 1004⁃373X(2014)05⁃0058⁃030 引言伪随机序列作为一种信号形式,具有良好的相关特性和伪随机性,可应用于扩频通信和信号加密等领域。

根据应用场合的不同,可以将伪随机序列设计成具有不同特性的序列,其中,m序列便是应用最广泛的一种伪随机序列[1⁃2]。

m序列是最长线性反馈移位寄存器序列的简称,由[N]级移位寄存器和模二加法器产生。

对于一个[N]级移位寄存器来说,最多可以有[2N]个状态。

由于全“0”状态不会转入其他状态,所以线性移位寄存器的序列的最长周期为 [2N-1。

]当[N]级线性移位寄存器产生的序列[{ai}]的周期为[T=2N-1]时,称[{ai}]为[N]级m序列[3]。

本文采用Xilinx公司的spartan⁃6开发板来产生m序列。

FPGA因其高速的计算速度和简便的编译步骤被越来越广泛的应用于数字信号处理领域。

Spartan⁃6自带100 MHz内部晶振,最高可以提供高达300 MHz的运算速度。

1 m序列的实现算法1.1 逻辑法程序的移位寄存器功能模拟部分,根据特征方程,将序列Seq_r的第0、2、3和4位对应数值进行模二运算并将结果作为新的数据输入寄存器的高位。

此处应避免初始状态为全零[4]。

基于FPGA的VHDL语言m序列生成详解+源码

说明可控m序列产生器我分成四个小模块来做,M,M1,M2,M3分别对应为:m序列产生器、控制器、码长选择器、码速率选择器。

一、M: m序列产生器这是该设计的核心部分,原理就是设计一个通用m序列产生子单元,然后由外部选择器来写入码型,码长等参数,加以循环可连接成任意长度的m序列产生器,其子单元结构如下:如上图,若N=15,就有15个这样的子单元首尾相接。

注意:开头和结尾的两个子单元会有所不同,因为首单元需要输入初值,尾单元要进行直通反馈,在程序里请多留意。

图中,主要部件是一个D触发器,Q(N+1)为上一级输出;Q(N)既是本级输出;CP为选择后的时钟脉冲;B(N)为本级参数选择控制;A(N)受控于B(N),决定本级输出Q(N)是否反馈(B(N)为1时反馈);C(N)为本级反馈;C(N-1)为下一级反馈。

具体原理参看m序列组成结构。

此外,本程序还加入了EN(发送控制)、RN(首单元置数)、SEL1(码长选择,即N的选择,N=2-15)、SEL2(码型选择,即正逆码选择)四个控制端,可满足设计要求。

OP为码输出端。

二、M1:控制器控制器主要是将外部的序列发送控制信号STA转换为EN和RN 两个控制信号。

其中,EN与STA的波形基本一致,只是它与CP进行了同步处理;RN在EN为‘1’的头一个脉冲周期里置高电平,以达到为序列发生器的首端置数的目的。

如果不清楚的话可以看一下它的模拟波形。

(注意:STA要采用自锁定开关,高电平有效)三、M2:码长选择序列的码长选择既是N值的选择,码长=2**N-1。

核心就是一个计数器,可从2计到15。

按一次PUSH就可以自动加一(注意:按键建议采用自弹跳按键,如过需要软件清除按键震颤的话,我再做发给你),没有0,1两个状态。

如果需要的话还可以扩展7段数码管的接口,以显示N值。

四、M3:码速率选择器码的传输速率是靠CP来控制的,CP的频率就等于码元速率。

这段程序包含一个倍频器,一个5分频的分频器,可把5MHZ的脉冲源CLK扩展成1MHZ和10MHZ。

基于VHDL的m序列伪随机信号发生器设计 精品

成都电子机械高等专科学校毕业设计论文作者姚世刚学号2009111733系部电子与电气工程系专业电子测量技术与仪器题目基于VHDL的m序列伪随机信号发生器的设计指导教师赵茂林评阅教师完成时间:2012年4 月30日毕业设计(论文)中文摘要题目:基于VHDL的m序列发生器的设计摘要:VHDL/CPLD即复杂可编程逻辑器件作为一种大规模集成电路,可根据用户的需要自行构造逻辑功能,可实现较大规模的电路设计,因此被广泛应用于产品的原型设计和产品生产之中。

几乎所有应用中小规模通用数字集成电路的场合均可应用CPLD器件。

本文介绍了基于CPLD的m序列发生器的设计方法。

关键词:CPLD;MAX+PLUS II;伪随机码;m序列发生器毕业设计(论文)外文摘要Title : M—sequence Generator Based CPLDAbstract: VHDL/CPLD Complex Programmable Logic Device that is, as a large scale integrated circuits can be constructed according to the needs of users on their own logic, enabling large-scale circuit design, it is widely used in product design and prototype production into. Almost all applications of small and medium general-purpose digital integrated circuits may be applied CPLD devices occasions. This article describes the m-sequence generator based on CPLD design method.Key words: CPLD;MAX+PLUS II;Pseudorandom Code;m sequence code Generator目录前言 (6)1课题介绍 (7)1.1为什么研究此课题 (7)1.2伪随机序列的应用与意义 (7)1.3伪随机序列的研究现状 (8)1.4研究内容 (8)2设计中使用芯片及VHDL语言介绍 (9)2.1 CPLD芯片介绍 (9)2.1.1概述 (9)2.1.2 MAX7000特点 (9)2.1.3 EPM7128LC84-7 (11)3 伪随机序列介绍 (12)3.1 伪随机序列理论的发展史 (13)3.2 伪随机序列的构造方法 (13)4 序列信号发生器原理 (14)4.1序列信号发生器的设计 (15)4.1.1反馈移位型序列信号发生器 (15)4.1.2计数型序列码发生器 (18)5 移位寄存器 (20)5.1移位寄存器 (20)5.1.1 寄存器 (20)5.1.2移位寄存器 (21)5.2 线性反馈移位寄存器结构 (22)5.2.1 D触发器 (22)5.2.1.1 D触发器工作原理 (22)5.2.1.2 D触发器真值表 (23)5.2.1.3 特征方程 (23)5.2.1.4 状态转移图 (23)5.2.1.5时序图 (24)5.2.1.6 脉冲特性 (24)5.2.2异或门 (25)5.2.2.1 基本原理 (25)5.2.2.2 异或门逻辑符号 (25)5.2.2.3 逻辑表达式 (25)5.2.2.4 真值表 (25)5.3 线性反馈移位寄存器 (26)5.3.1 什么是反馈移位寄存器 (26)5.3.2 线性反馈移位寄存器 (26)5.3.3 性质 (26)6 伪随机信号 (27)6.1 伪随机信号 (27)6.2 m序列码发生器 (30)7 m序列性质 (33)7.1 均衡性 (33)7.2游程特性 (33)7.3 移位相加性 (33)7.4 相关特性 (33)7.5 伪随机特性 (34)8 序列信号发生器的设计和仿真实现 (35)8.1 m序列生成单元的电路设计 (35)8.1.1 系统组成 (35)8.1.2 程序方框图 (36)8.2 m序列发生器 (36)8.3 VHDL语言实现 (37)8.4 仿真数据及结论 (39)结论 (42)致谢 (43)参考文献 (43)前言CPLD(Complex Programmable Logic Device)复杂可编程逻辑器件,是从PAL和GAL器件发展出来的器件,相对而言规模大,结构复杂,属于大规模集成电路范围。

基于FPGA的m序列发生器

基于FPGA的m序列发生器摘要m序列广泛应用于密码学、通信、雷达、导航等多个领域,本文提出了一种基于FPGA的伪随机序列产生方法,应用移位寄存器理论从序列的本原多项式出发,获得产生该序列的移位寄存器反馈逻辑式,结合FPGA芯片结构特点,在序列算法实现中采用元件例化语句。

算法运用VHDL语言编程,以A1tera的QuartusⅡ软件为开发平台,给出了序列的仿真波形。

序列的统计特性分析表明:该方法产生的序列符合m序列的伪随机特性,验证了算法的正确性。

关键词:m序列;移位寄存器理论;VHDL语言1 m序列m序列是伪随机序列的一种 ,结构简单 ,实现方便。

在现代工程实践中 , m 序列在通讯、导航、雷达、通信系统性能的测量等领域中有着广泛的应用。

例如 , 在连续波雷达中可用作测距信号 , 在遥控系统中可用作遥控信号 , 在多址通信中可用作地址信号 , 在数字通信中可用作群同步信号 ,还可用作噪声源及在保密通信中起加密作用等。

伪噪声发生器在测距、通信等领域的应用日益受到人们重视。

目前,m序列产生实现方法主要有3种:(1)门电路实现该方法设计简单,但随移位寄存器级数的增长,电路装调困难,且占用的印制板面积较大。

(2)DSP编程实现该方法专业性过强,不适合一般用户。

(3)VHDL与CPLD实现由于CPLD的高集成度,而且VHDL语言编程较为方便,故可以大大减少电路的装调的困难。

文章提出VHDL语言实现,,l序列电路是周期、初相位可编程变化的,其应用较为灵活,通过微处理器对其进行适当的初始化,即可产生用户所需周期、初相位的m序列输出。

用软件方式构成的特点是采用灵活的数据查询方式可以获得任意级数 n 的本原多项式系数 ,从而实现 m 序列的产生 , 但速度受到单片机工作速度的限制。

而 FPGA 具有硬件电路实现的优点 , 又具有设计上的灵活性 , 并且由于FPGA 便于实现大规模的数字系统。

1.1 理论基础m 序列是最长线性反馈移位寄存器序列的简称,它是由带线性反馈的移位寄存器产生的周期最长的一种序列。

两种利用FPGA产生m序列的算法分析

两种利用FPGA产生m序列的算法分析陈天成;王艳红【摘要】为了产生性能良好且节省硬件资源的m序列,分别提出了基于现场可编程门阵列(FPGA)的逻辑法和核调用法两种算法,并详细介绍了两种算法的实现步骤。

通过在Xilinx公司的NEXYS3开发板上进行设计和编程,对两种算法的可行性进行了检测;并结合ISE编程软件的仿真功能和Matlab对算法的自相关性、硬件占用率和实现难度等性能进行了分析。

最终,了解到核调用法在m序列产生中的优越性。

%In order to produce m sequence with high performance and resource-saving,two algorithms based on FPGA,which respectively named as Logic Description and IP Core Transfer,are provided,and the implementation steps of the two algorithms are introduced. NEXYS3 developing platform from Xilinx Company is used to program and design. The feasibility of the two algo-rithm os tested. Combine with the emulation facility of ISE program,the autocorrelation,hardware occupancy rate and implemen-tation difficulty of the Matlab are analyzed. Finally the advantages of IP Core Transfer in m sequence are comprehended.【期刊名称】《现代电子技术》【年(卷),期】2014(000)005【总页数】3页(P58-60)【关键词】m序列;FPGA;IP核;ISE【作者】陈天成;王艳红【作者单位】烟台大学光电信息科学技术学院,山东烟台 264000;烟台大学光电信息科学技术学院,山东烟台 264000【正文语种】中文【中图分类】TN919-34伪随机序列作为一种信号形式,具有良好的相关特性和伪随机性,可应用于扩频通信和信号加密等领域。

基于FPGA可配置m序列发生器的设计与实现

现代电子技术Modern Electronics Technique2018年4月15日第41卷第8期Apr.2018Vol.41No.8DOI :10.16652/j.issn.1004⁃373x.2018.08.001m 序列作为伪随机序列[1]的一种,具有优良的伪随机序列性质,在雷达[2]、导航[3]、常规通信[4⁃5]、保密通信[6]、地球物理勘察[7]和电子对抗[8]等领域中都有着广泛的应用。

有关产生m 序列发生器的方案很多。

其中,基于专用集成电路的m 序列发生器,其发生速率可以很快,但由于硬件电路不便修改的特性,只能产生单一的m 序列;基于软件的m 序列发生器[9]采用灵活的数据查询方式可以获得任意的m 序列,因而得到了大量的关注和研究,但其产生速率不及硬件实现方式且实现过程较为复杂,故而在许多高速设计场合往往使用更为简单的FPGA 实现方式。

FPGA 即现场可编程门阵列,使用FPGA 来实现设计,既具有硬件电路实现的优点,又具有设计上的灵活性。

本文提出了一种基于FPGA 的m 序列发生器,具有初始状态可配置的特点,可以通过配置线性反馈移位寄存器的初始值来改变产生的m 序列,并给出了一个在保密通信系统中的应用实例,对工程应用有一定的现实意义。

1m 序列发生器的设计原理传统的m 序列发生器有Fabonacci 和Galois 两种类型[10],其中前者是在n 级线性移位寄存器的基础上,加上反馈回路构成的,结构简单,易于实现,具体结构如图1所示。

图1中的c i 是反馈系数,由本原多项式系数确定,当c i =1时,反馈回路连接,当c i =0时,反馈回路断开。

a i 用于表示各级触发器的状态,a i 只能等于0或1,表示触发器的储值是0还是1。

发生器工作时,产基于FPGA 可配置m 序列发生器的设计与实现晏浩文1,2,陈伟1,吴琼1,黄庆超1,刘建国1,祝宁华1(1.中国科学院半导体研究所,北京100083;2.中国科学院大学,北京100049)摘要:针对某些设计场合对可变m 序列的需求,提出并验证了一种基于FPGA 的m 序列发生器方案。

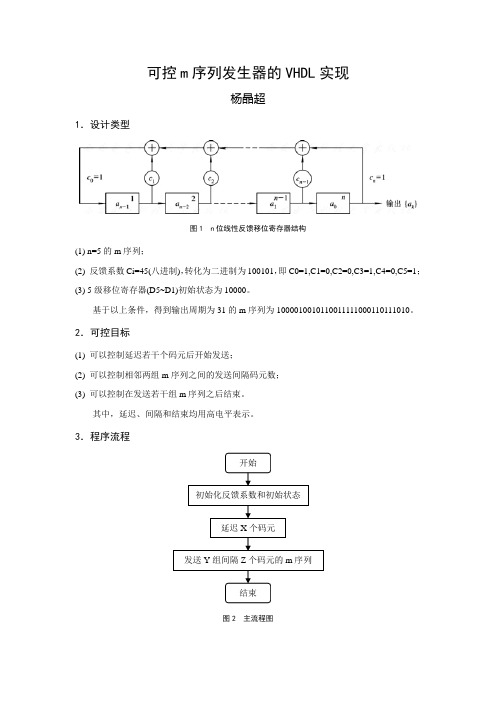

可控m序列发生器的VHDL实现

可控m序列发生器的VHDL实现杨晶超1.设计类型图1 n位线性反馈移位寄存器结构(1) n=5的m序列;(2) 反馈系数Ci=45(八进制),转化为二进制为100101,即C0=1,C1=0,C2=0,C3=1,C4=0,C5=1;(3) 5级移位寄存器(D5~D1)初始状态为10000。

基于以上条件,得到输出周期为31的m序列为1000010010110011111000110111010。

2.可控目标(1) 可以控制延迟若干个码元后开始发送;(2) 可以控制相邻两组m序列之间的发送间隔码元数;(3) 可以控制在发送若干组m序列之后结束。

其中,延迟、间隔和结束均用高电平表示。

3.程序流程图2 主流程图图3 延迟X个码元发送图4 间隔Z个码元发送图5 发送Y组m序列4.实现结果图6 延迟0个码元,间隔5个码元,发送2个周期图7 延迟1个码元,间隔10个码元,发送3个周期图8 延迟2个码元,间隔15个码元,发送4个周期附程序代码:library IEEE;use IEEE.STD_LOGIC_1164.ALL;use IEEE.STD_LOGIC_ARITH.ALL;use IEEE.STD_LOGIC_UNSIGNED.ALL;entity m_sequence isgeneric (length : positive: =4;tap1 : positive: =4;tap2 : positive: =2);port (clk, reset : in bit;prbs : out bit);end m_sequence;architecture Behavioral of m_sequence issignal prreg : bit_vector (length downto 0);signal enable : std_logic:='0';signal enable2 : integer: =0;signal cnt : integer: =0;beginprocess (clk)variable count: integer: =0;beginif (clk'event and clk='1') thenif (count < 2 or cnt = 4) then --延迟2个码元,发送4个周期count: = count + 1;enable <='0';else enable <='1';end if;end if;end process;process (clk, reset, prreg, enable)beginif reset='0' thenprreg<=(length=>'1',others=>'0'); --初始状态elsif (clk'event and clk='1') and enable='1' thenprreg<=prreg ((length-1) downto 0) & (prreg (tap1) xor prreg (tap2));if prreg="01000" thenenable2<=15; --间隔15个码元cnt<=cnt+1;else enable2<=0;end if;if enable2 /= 0 thenenable2 <= enable2 - 1;prreg<= (length=>'1', others=>'0');end if;end if;end process;process (enable, prreg (length))beginif enable='1' thenprbs<=prreg (length);else prbs<='1';end if;end process;end Behavioral;。

基于FPGA的m序列发生器要点

基于FPGA的m序列发生器摘要m序列广泛应用于密码学、通信、雷达、导航等多个领域,本文提出了一种基于FPGA的伪随机序列产生方法,应用移位寄存器理论从序列的本原多项式出发,获得产生该序列的移位寄存器反馈逻辑式,结合FPGA芯片结构特点,在序列算法实现中采用元件例化语句。

算法运用VHDL语言编程,以A1tera的QuartusⅡ软件为开发平台,给出了序列的仿真波形。

序列的统计特性分析表明:该方法产生的序列符合m序列的伪随机特性,验证了算法的正确性。

关键词:m序列;移位寄存器理论;VHDL语言1 m序列m序列是伪随机序列的一种 ,结构简单 ,实现方便。

在现代工程实践中 , m 序列在通讯、导航、雷达、通信系统性能的测量等领域中有着广泛的应用。

例如 , 在连续波雷达中可用作测距信号 , 在遥控系统中可用作遥控信号 , 在多址通信中可用作地址信号 , 在数字通信中可用作群同步信号 ,还可用作噪声源及在保密通信中起加密作用等。

伪噪声发生器在测距、通信等领域的应用日益受到人们重视。

目前,m序列产生实现方法主要有3种:(1)门电路实现该方法设计简单,但随移位寄存器级数的增长,电路装调困难,且占用的印制板面积较大。

(2)DSP编程实现该方法专业性过强,不适合一般用户。

(3)VHDL与CPLD实现由于CPLD的高集成度,而且VHDL语言编程较为方便,故可以大大减少电路的装调的困难。

文章提出VHDL语言实现,,l序列电路是周期、初相位可编程变化的,其应用较为灵活,通过微处理器对其进行适当的初始化,即可产生用户所需周期、初相位的m序列输出。

用软件方式构成的特点是采用灵活的数据查询方式可以获得任意级数 n 的本原多项式系数 ,从而实现 m 序列的产生 , 但速度受到单片机工作速度的限制。

而 FPGA 具有硬件电路实现的优点 , 又具有设计上的灵活性 , 并且由于FPGA 便于实现大规模的数字系统。

1.1 理论基础m 序列是最长线性反馈移位寄存器序列的简称,它是由带线性反馈的移位寄存器产生的周期最长的一种序列。

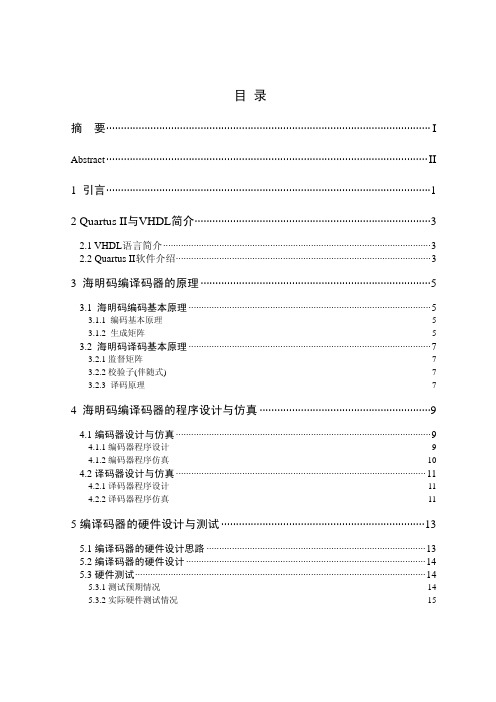

基于FPGA和VHDL的汉明码编解码器设计

3.1 海明码编码基本原理 ·······························································································5

目录

摘 要·············································································································· I

Abstract ·············································································································II

如果一个分组码的数据位长度为k校验位长度为r总的编码长度为kr则总的可以编码的合法码字的个数为2k总的码字个数为2n可以看出检验位的长度越长合法码字所占的比例就越小如果这些码字能够尽可能地在所有的码字中均匀分布的话合法码字之间的最小海明码距就越大编码的抗干扰能力也就越强因此设计编码方法的最重要的任务就是尽量使合法码字尽可能地均匀分差错控制编码在通信电子系统中得到广泛应用其中一类重要的差错控制编码是线性分组码线性分组码中信息位和监督位通过代数方程相联系

5.3.1 测试预期情况 ······················································································································14 5.3.2 实际硬件测试情况 ··············································································································15

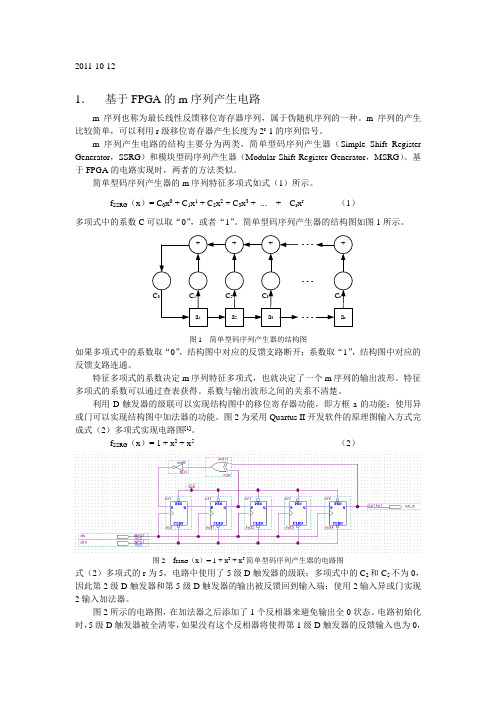

m序列产生

2011-10-121. 基于FPGA 的m 序列产生电路m 序列也称为最长线性反馈移位寄存器序列,属于伪随机序列的一种。

m 序列的产生比较简单,可以利用r 级移位寄存器产生长度为2r -1的序列信号。

m 序列产生电路的结构主要分为两类,简单型码序列产生器(Simple Shift Register Generator ,SSRG )和模块型码序列产生器(Modular Shift Register Generator ,MSRG )。

基于FPGA 的电路实现时,两者的方法类似。

简单型码序列产生器的m 序列特征多项式如式(1)所示。

f SSRG (x )= C 0x 0 + C 1x 1 + C 2x 2 + C 3x 3 + … + C r x r (1) 多项式中的系数C 可以取“0”,或者“1”。

简单型码序列产生器的结构图如图1所示。

图1 简单型码序列产生器的结构图如果多项式中的系数取“0”,结构图中对应的反馈支路断开;系数取“1”,结构图中对应的反馈支路连通。

特征多项式的系数决定m 序列特征多项式,也就决定了一个m 序列的输出波形。

特征多项式的系数可以通过查表获得。

系数与输出波形之间的关系不清楚。

利用D 触发器的级联可以实现结构图中的移位寄存器功能,即方框a 的功能;使用异或门可以实现结构图中加法器的功能。

图2为采用Quartus II 开发软件的原理图输入方式完成式(2)多项式实现电路图[1]。

f SSRG (x )= 1 + x 2 + x 5 (2)图2 f SSRG (x )= 1 + x 2+ x 5简单型码序列产生器的电路图式(2)多项式的r 为5,电路中使用了5级D 触发器的级联;多项式中的C 2和C 5不为0,因此第2级D 触发器和第5级D 触发器的输出被反馈回到输入端;使用2输入异或门实现2输入加法器。

图2所示的电路图,在加法器之后添加了1个反相器来避免输出全0状态。

基于VHDL语言并选用FPGA设计了一个卷积码编码器

基于VHDL语言并选用FPGA设计了一个卷积码编

码器

数字信号在有噪声的信道中传输时,由于受到干扰的影响,会发生误码。

在设计数字通信系统时,首先应合理设计基带信号,选择调制、解调方式,

并采用均衡措施等,使误码率达到指标要求。

若仍然不能满足要求时,则必

须采用差错控制编码等信道编码技术,使误码率进一步降低。

卷积码是深度

空间通信系统和无线通信系统中常用的一种差错控制编码。

在编码过程,卷

积码充分利用了各码字之间的相关性。

卷积码广泛应用于卫星通信,

GSM,CDMA数字移动通信等通信系统,对其进行研究具有很大的现实意义。

FPGA是可编程逻辑器件,采用FPGA等新型可编程器件进行数字系统设计,不仅使设计的电子产品达到微型化、高集成化和高可靠性,而且开发周

期短、成本低、风险小。

本设计采用VHDL语言并选用FPGA设计了一个(2,1,9)卷积码编码器。

1 卷积码编码器原理卷积码是1955年由Elias等人提出的一种十分常见且有效的前向纠错码(FEC)。

卷积码(n,k,N)主要用来纠随机错误,它的码

元与前后码元有一定的约束关系。

卷积码(n,k,N)将是个信息比特编为n个比特,N为约束长度。

即卷积码的当前码元不仅与当前输入的k个信息码元

有关,而且还与前面(N-1)个时刻输入的信息码元有关,卷积码的纠错能力不。

基于m序列同步的FPGA实现

基于m序列同步的FPGA实现随则辉;常文革【摘要】In the communication system,synchronization is one of the key technologies to realize the correct signal demodu-lation. To achieve synchronization,a synchronization method based on m-sequence is proposed in this paper. At first,the demod-ulation sequence is got by the differential coherent demodulation operation of the receivedsignal;then,all bits of the result of the demodulation sequence and the local m-sequence′s with-or operation are summed;finally,the comparison of the sum value and the threshold is carried out to judge whether the synchronization is achieved. The sum of the with-or operation′s result avoids the complex relevant operation,which performs fast and save the hardware resources. The implementation of the entire process is based on the Spartan6 series′ FPGA of the Xilinx Company. The simulation results show that the method can accurate-ly realize the synchronization and has high stability.%在通信系统中,同步问题是实现信号正确解调的关键技术之一。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

说明可控m序列产生器我分成四个小模块来做,M,M1,M2,M3分别对应为:m序列产生器、控制器、码长选择器、码速率选择器。

一、M: m序列产生器这是该设计的核心部分,原理就是设计一个通用m序列产生子单元,然后由外部选择器来写入码型,码长等参数,加以循环可连接成任意长度的m序列产生器,其子单元结构如下:如上图,若N=15,就有15个这样的子单元首尾相接。

注意:开头和结尾的两个子单元会有所不同,因为首单元需要输入初值,尾单元要进行直通反馈,在程序里请多留意。

图中,主要部件是一个D触发器,Q(N+1)为上一级输出;Q(N)既是本级输出;CP为选择后的时钟脉冲;B(N)为本级参数选择控制;A(N)受控于B(N),决定本级输出Q(N)是否反馈(B(N)为1时反馈);C(N)为本级反馈;C(N-1)为下一级反馈。

具体原理参看m序列组成结构。

此外,本程序还加入了EN(发送控制)、RN(首单元置数)、SEL1(码长选择,即N的选择,N=2-15)、SEL2(码型选择,即正逆码选择)四个控制端,可满足设计要求。

OP为码输出端。

二、M1:控制器控制器主要是将外部的序列发送控制信号STA转换为EN和RN 两个控制信号。

其中,EN与STA的波形基本一致,只是它与CP进行了同步处理;RN在EN为‘1’的头一个脉冲周期里置高电平,以达到为序列发生器的首端置数的目的。

如果不清楚的话可以看一下它的模拟波形。

(注意:STA要采用自锁定开关,高电平有效)三、M2:码长选择序列的码长选择既是N值的选择,码长=2**N-1。

核心就是一个计数器,可从2计到15。

按一次PUSH就可以自动加一(注意:按键建议采用自弹跳按键,如过需要软件清除按键震颤的话,我再做发给你),没有0,1两个状态。

如果需要的话还可以扩展7段数码管的接口,以显示N值。

四、M3:码速率选择器码的传输速率是靠CP来控制的,CP的频率就等于码元速率。

这段程序包含一个倍频器,一个5分频的分频器,可把5MHZ的脉冲源CLK扩展成1MHZ和10MHZ。

FSEL1、FSLE2、FSEL3分别在选择1、5、10MHZ时为高电平,其余两个为低,建议采用3选1单刀单掷开关。

M1-------------------------------------------------- LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_ARITH.ALL;USE IEEE.STD_LOGIC_UNSIGNED.ALL;ENTITY CTRL ISPORT(CP,STA : IN STD_LOGIC;EN,RN : OUT STD_LOGIC);END CTRL;ARCHITECTURE a OF CTRL ISSIGNAL Q1,Q2 :STD_LOGIC; BEGINPROCESS(CP)BEGINIF CP’event AND CP=’1’ THENQ2<=Q1;Q1<=STA;END IF;END PROCESS;EN<=Q1;RN<=Q1 AND NOT Q2;END a;M2------------------------------------------------- LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_ARITH.ALL;USE IEEE.STD_LOGIC_UNSIGNED.ALL;ENTITY COUNTER ISPORT(PUSH,EN,RST : IN STD_LOGIC;SEL1 : OUT STD_LOGIC_VECTOR(3 DOWNTO 0) );END COUNTER;ARCHITECTURE a OF COUNTER ISSIGNAL B,C : STD_LOGIC;SIGNAL QN : STD_LOGIC_VECTOR(3 DOWNTO 0); BEGINPROCESS(PUSH,C)BEGINIF EN=’0’ THENIF C=’1’ THENQN<=”0010”;ELSEIF PUSH’EVENT AND PUSH=’1’ THENQN<=QN+1;END IF;ELSEQN<=QN;END IF;END PROCESS;B<=’1’ WHEN QN=”0000” ELSE‘0’;C<=B OR RST;SEL1<=QN;END a;M3-----------------------------------LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_ARITH.ALL;USE IEEE.STD_LOGIC_UNSIGNED.ALL;ENTITY FP ISPORT(CLK,FSEL1,FSEL2,FSEL3 : IN STD_LOGIC;CP : OUT STD_LOGIC);END FP;ARCHITECTURE a OF FP ISSIGNAL Q1,Q2,Q3,RST : STD_LOGIC;SIGNAL M1,M5,M10 : STD_LOGIC;SIGNAL QN : STD_LOGIC_VECTOR(2 DOWNTO 0); BEGINBP1 : BLOCKBEGINPROCESS(CLK,Q1)BEGINIF Q1=’1’ THENQ1<=’0’ELSEIF CLK’EVENT AND CLK=’1’ THENQ1<=’1’;END IF;END PROCESS;END BLOCK BP1;BP2 : BLOCKBEGINPROCESS(CLK,Q2)BEGINIF Q2=’1’ THENQ2<=’0’ELSEIF CLK’EVENT AND CLK=’0’ THENQ2<=’1’;END IF;END PROCESS;END BLOCK BP2;FP : BLOCKBEGINPROCESS(CLK,RST)BEGINIF RST=’1’ THENQN<=”000”;ELSEIF CLK’EVENT AND CLK=’1’ THENQN<=QN+1;END IF;END PROCESS;END BLOCK FP;Q3<=Q1 OR Q2;RST<=’1’ WHEN QN=”101” ELSE‘0’;M1<=QN(2) AND FSEL1;M2<=CLK AND FSEL2;M3<=Q3 AND FSEL3;CP<=M1 OR M2 OR M3;END a;M----------------------------------------LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_ARITH.ALL;USE IEEE.STD_LOGIC_UNSIGNED.ALL;ENTITY PN1 ISPORT(CP,SEL2,EN,RN : IN STD_LOGIC;SEL1 : IN STD_LOGIC_VECTOR(3 DOWNTO 0);OP : OUT STD_LOGIC);END PN1;ARCHITECTURE a OF PN1 ISSIGNAL Q, A,B,C : STD_LOGIC_VECTOR(14 DOWNTO 0);SIGNAL SEL : STD_LOGIC_VECTOR(4 DOWNTO 0);BEGINSEL<=SEL1&SEL2;PROCESS (CP,SEL)BEGINIF CP'event AND CP='1' THENIF EN='0' THENQ<="0000";OP<=Q(0);ELSEQ(14)<=C(14) OR RN;B<="0000";CASE SEL ISWHEN"11111"=>C(0)<=Q(0);B(1)<='1';FOR I IN 1 TO 14 LOOPQ(I-1)<=Q(I);A(I)<=Q(I) AND B(I);C(I)<=C(I-1) XOR A(I);END LOOP;OP<=Q(0);WHEN"11110"=>C(0)<=Q(0);B(14)<='1';FOR I IN 1 TO 14 LOOPQ(I-1)<=Q(I);A(I)<=Q(I) AND B(I);C(I)<=C(I-1) XOR A(I);END LOOP;OP<=Q(0);WHEN"11101"=>C(1)<=Q(1);B(2)<='1';B(7)<='1';B(11)<='1';FOR I IN 2 TO 14 LOOPQ(I-1)<=Q(I);A(I)<=Q(I) AND B(I);C(I)<=C(I-1) XOR A(I);END LOOP;OP<=Q(1); WHEN"11100"=>C(1)<=Q(1);B(5)<='1';B(9) <='1';B(14) <='1';FOR I IN 2 TO 14 LOOPQ(I-1)<=Q(I);A(I)<=Q(I) AND B(I);C(I)<=C(I-1) XOR A(I);END LOOP;OP<=Q(1); WHEN"11011"=>C(2) <=Q(2);B(3) <='1';B(5) <='1';B(6) <='1';FOR I IN 3 TO 14 LOOPQ(I-1)<=Q(I);A(I)<=Q(I) AND B(I);C(I)<=C(I-1) XOR A(I);END LOOP;OP<=Q(2); WHEN"11010"=>C(2) <=Q(2);B(11) <='1';B(12) <='1';B(14) <='1';FOR I IN 3 TO 14 LOOPQ(I-1)<=Q(I);A(I)<=Q(I) AND B(I);C(I)<=C(I-1) XOR A(I);END LOOP;OP<=Q(2); WHEN"11001"=>C(3) <=Q(3);B(4) <='1';B(7) <='1';B(9) <='1';FOR I IN 4 TO 14 LOOPQ(I-1)<=Q(I);A(I)<=Q(I) AND B(I);C(I)<=C(I-1) XOR A(I);END LOOP;OP<=Q(3); WHEN"11000"=>C(3) <=Q(3);B(9) <='1';B(11) <='1';B(14) <='1';FOR I IN 4 TO 14 LOOPQ(I-1)<=Q(I);A(I)<=Q(I) AND B(I);C(I)<=C(I-1) XOR A(I);END LOOP;OP<=Q(3); WHEN"10111"=>C(4) <=Q(4);B(6) <='1';FOR I IN 5 TO 14 LOOPQ(I-1)<=Q(I);A(I)<=Q(I) AND B(I);C(I)<=C(I-1) XOR A(I);END LOOP;OP<=Q(4); WHEN"10110"=>C(4) <=Q(4);B(13) <='1';FOR I IN 5 TO 14 LOOPQ(I-1)<=Q(I);A(I)<=Q(I) AND B(I);C(I)<=C(I-1) XOR A(I);END LOOP;OP<=Q(4); WHEN"10101"=>C(5) <=Q(5);B(8) <='1';FOR I IN 6 TO 14 LOOPQ(I-1)<=Q(I);A(I)<=Q(I) AND B(I);C(I)<=C(I-1) XOR A(I);END LOOP;OP<=Q(5); WHEN"10100"=>C(5) <=Q(5);B(12) <='1';FOR I IN 6 TO 14 LOOPQ(I-1)<=Q(I);A(I)<=Q(I) AND B(I);C(I)<=C(I-1) XOR A(I);END LOOP;OP<=Q(5); WHEN"10011"=>C(6) <=Q(6);B(10) <='1';FOR I IN 7 TO 14 LOOPQ(I-1)<=Q(I);A(I)<=Q(I) AND B(I);C(I)<=C(I-1) XOR A(I);END LOOP;OP<=Q(6); WHEN"10010"=>C(6) <=Q(6);B(11) <='1';FOR I IN 7 TO 14 LOOPQ(I-1)<=Q(I);A(I)<=Q(I) AND B(I);C(I)<=C(I-1) XOR A(I);END LOOP;OP<=Q(6); WHEN"10001"=>C(7) <=Q(7);B(9) <='1';B(10) <='1';B(11) <='1';FOR I IN 8 TO 14 LOOPQ(I-1)<=Q(I);A(I)<=Q(I) AND B(I);C(I)<=C(I-1) XOR A(I);END LOOP;OP<=Q(7); WHEN"10000"=>C(7) <=Q(7);B(11) <='1';B(12) <='1';B(13) <='1';FOR I IN 8 TO 14 LOOPQ(I-1)<=Q(I);A(I)<=Q(I) AND B(I);C(I)<=C(I-1) XOR A(I);END LOOP;OP<=Q(7); WHEN"01111"=>C(8) <=Q(8);B(11) <='1';FOR I IN 9 TO 14 LOOPQ(I-1)<=Q(I);A(I)<=Q(I) AND B(I);C(I)<=C(I-1) XOR A(I);END LOOP;OP<=Q(8); WHEN"01110"=>C(8) <=Q(8);B(12) <='1';FOR I IN 9 TO 14 LOOPQ(I-1)<=Q(I);A(I)<=Q(I) AND B(I);C(I)<=C(I-1) XOR A(I);END LOOP;OP<=Q(8); WHEN"01101"=>C(9) <=Q(9);B(10) <='1';FOR I IN 10 TO 14 LOOPQ(I-1)<=Q(I);A(I)<=Q(I) AND B(I);C(I)<=C(I-1) XOR A(I);END LOOP;OP<=Q(9); WHEN"01100"=>C(9) <=Q(9);B(14) <='1';FOR I IN 10 TO 14 LOOPQ(I-1)<=Q(I);A(I)<=Q(I) AND B(I);C(I)<=C(I-1) XOR A(I);END LOOP;OP<=Q(9); WHEN"01011"=>C(10) <=Q(10);B(12) <='1';FOR I IN 11 TO 14 LOOPQ(I-1)<=Q(I);A(I)<=Q(I) AND B(I);C(I)<=C(I-1) XOR A(I);END LOOP;OP<=Q(10); WHEN"01010"=>C(10) <=Q(10);B(13) <='1';FOR I IN 11 TO 14 LOOPQ(I-1)<=Q(I);A(I)<=Q(I) AND B(I);C(I)<=C(I-1) XOR A(I);END LOOP;OP<=Q(10); WHEN"01001"=>C(11) <=Q(11);B(12) <='1';FOR I IN 12 TO 14 LOOPQ(I-1)<=Q(I);A(I)<=Q(I) AND B(I);C(I)<=C(I-1) XOR A(I);END LOOP;OP<=Q(11); WHEN"01000"=>C(11) <=Q(11);B(14) <='1';FOR I IN 12 TO 14 LOOPQ(I-1)<=Q(I);A(I)<=Q(I) AND B(I);C(I)<=C(I-1) XOR A(I);END LOOP;OP<=Q(11);WHEN"00111"=>C(12) <=Q(12);B(13) <='1';FOR I IN 13 TO 14 LOOPQ(I-1)<=Q(I);A(I)<=Q(I) AND B(I);C(I)<=C(I-1) XOR A(I);END LOOP;OP<=Q(12);WHEN"00110"=>C(12) <=Q(12);B(14) <='1';FOR I IN 13 TO 14 LOOPQ(I-1)<=Q(I);A(I)<=Q(I) AND B(I);C(I)<=C(I-1) XOR A(I);END LOOP;OP<=Q(12);WHEN OTHERS=>C(13) <=Q(13);B(14) <='1';Q(13)<=Q(14);A(14)<=Q(14) AND B(14);C(14)<=C(13) XOR A(14);OP<=Q(13);END CASE;END If;END IF;END PROCESS;END a;。