中文数据手册

MCP41010数据手册中文版

抽头控制 电阻 寄存器 阵列 1*

PDIP/SOIC/TSSOP

CS SCK SI VSS PB1 PW1 PA1 1 2 14 13 VDD SO SHDN RS PB0 PW0 PA0

MCP42XXX

3 4 5 6 7

12 11 10 9 8

* 只有在双 MCP42XXX 器件上才有电位器 P1。

DS11195C_CN 第 2 页

2006 Microchip Technology Inc.

MCP41XXX/42XXX

直流特性:50 kΩ 器件

电气特性:除非另外声明,否则 VDD = +2.7V 至 5.5V 且 TA = -40°C 至 +85°C (规定 TSSOP 器件只能在 +25°C 和 +85°C 条件下工作) 。 典型规范值:VDD = 5V、 VSS = 0V、 VB = 0V 且 TA = +25°C。 参数 变阻器模式 标称电阻 变阻器差分非线性度 变阻器积分非线性度 变阻器温度系数 抽头电阻 抽头电流 标称电阻匹配 电位器分压器 分辨率 单调性 差分非线性度 积分非线性度 分压器温度系数 满量程误差 零刻度误差 电阻端子 电压范围 电容 (CA 或 CB) 电容 动态特性 (测试所有动态特性时 VDD = 5V) 带宽 -3dB 稳定时间 电阻噪声电压 串扰 施密特触发器高电平输入电压 施密特触发器低电平输入电压 施密特触发器输入迟滞 低输出电压 高输出电压 输入泄漏电流 引脚电容 (所有输入 / 输出) 电源要求 工作电压范围 输入电流,有源 输入电流,静态 电源灵敏度 注 1: 2: 3: 4: 5: 6: VDD IDDA IDDS PSS PSS 2.7 - - - - - 340 0.01 0.0015 0.0015 5.5 500 1 0.0035 0.0035 V µA µA %/% %/% VDD = 5.5V, CS = VSS, fSCK = 10 MHz, SO = 开路,编码 FFh (注 6) CS, SHDN, RS = VDD = 5.5V, SO = 开路 (注 6) VDD = 4.5V - 5.5V, VA = 4.5V,编码 80h VDD = 2.7V - 3.3V, VA = 2.7V,编码 80h BW tS eNWB CT VIH VIL VHYS VOL VOH ILI CIN, COUT - - - - 0.7VDD - - - VDD - 0.5 -1 - 280 8 20 -95 - - .05VDD - - - 10 - - - - - .3VDD - 0.40 - +1 - V V µA pF IOL = 2.1 mA, VDD = 5V IOH = -400 µA, VDD = 5V CS = VDD, VIN = VSS 或 VDD,包括 VA SHDN=0 VDD = 5.0V, TA = +25°C, fc = 1 MHz MHz µS nV/√Hz dB V V VB = 0V,在编码为 80h,输出负载 = 30 µF 时测 得 VA = VDD, VB = 0V,误差范围为 ±1%,从编码 00h 过渡到 80h,输出负载 = 30 pF VA = 开路,编码 80h, f = 1 kHz VA = VDD, VB = 0V (注 5) CW VA,B,W 0 - - - 11 5.6 VDD - - pF pF 注4 f = 1 MHz,编码 = 80h,请参见图 2-30 f =1 MHz,编码 = 80h,请参见图 2-30 N N DNL INL ∆VW/∆T VWFSE VWFSE VWZSE VWZSE 8 8 -1 -1 - -1 -1 0 0 - - ±1/4 ±1/4 1 -0.25 -0.35 +0.25 +0.35 - - +1 +1 - 0 0 +1 +1 位 位 LSB LSB LSB LSB LSB LSB 注3 注3 编码 FFh, VDD = 5V,请参见图 2-25 编码 FFh, VDD = 3V,请参见图 2-25 编码 00h, VDD = 5V,请参见图 2-25 编码 00h, VDD = 3V,请参见图 2-25 R R-DNL R-INL ∆RAB/∆T RW RW IW ∆R/R 35 -1 -1 - - - -1 - 50 ±1/4 ±1/4 800 125 175 - 0.2 65 +1 +1 - 175 250 +1 1 kΩ LSB LSB ppm/°C Ω Ω mA % 仅 MCP42050, P0 到 P1 ; TA = +25°C VDD = 5.5V, IW = 1 mA,编码 00h VDD = 2.7V, IW = 1 mA,编码 00h TA = +25°C (注 1) 注2 注2 符号 最小值 典型值 最大值 单位 条件

ADI中文版数据手册说明书

ADI 中文版数据手册是英文版数据手册的译文,敬请谅解翻译中可能存在的语言组织或翻译错误,ADI 不对翻译中存在的差异或由此产生的错误负责。

如需确认任何词语的准确性,请参考ADI 提供的最新英文版数据手册。

消除影响JESD204B 链路传输的因素作者:Ian Beavers ,ADI 公司应用工程师JESD204B 串行数据链路接口针对支持更高速转换器不断增长的带宽需求而开发。

作为第三代标准,它提供更高的通道速率最大值(每通道高达12.5 Gbps),支持确定延迟和谐波帧时钟。

此外,得益于转换器性能的提升——这些转换器兼容开放市场FPGA 解决方案,并且可扩展——现已能轻松传输大量待处理的数据。

FPGA 供应商已讨论了许多年有关千兆串行/解串(SERDES)接口的话题,虽然过去大部分模数转换器(ADC)和数模转换器(DAC)并未配备这类高速串行接口。

FPGA 和转换器不与任何通用标准接口,无法利用SERDES 的高带宽。

JESD204B 兼容型转换器能够解决这个问题,而人们针对这种新功能提出了一些问题。

什么是8b/10b 编码,为什么JESD204B 接口需使用这种编码?无法确保差分通道上的直流平衡信号不受随机非编码串行数据干扰,因为很有可能会传输大量相反的1或0数据。

通过串行链路传输的随机数据还可能长时间无活动状态,并在相对较长的时间内为全1或全0。

发生这种情况时,未编码串行数据流的直流平衡被隔离,产生两种极端情况中的一种。

此时,若链路上再次传输有效数据,则很有可能发生位错误,因为线路重新开始偏置。

另外,一个长期的问题是电子迁移,因为相对差分对的另一侧,会保持一侧的差分直流电压。

为了克服这些问题,通常在差分串行数据流中(包括JESD204B)采用8b/10b 编码方案。

8b/10b 编码采用10个数据位,通过查找表方式从源端发送器发送8位初始信息。

这种方式具有25%的固有开销(10b/8b = 1.25),效率较低。

CC2530数据手册(中文)

RF 接收

测量按照 TI 公司 CC2530EM 设计参考进行,若无其他规定,则 TA=25℃,VDD=3V, fc=2440MHz。 黑体字仅适用于整个工作范围,TA= -40℃到 125℃,VDD=2V 到 3.6V,fc=2394MHz 到 2507MHz。

参 数 测试条件 根据 IEEE 802.15.4,PER=1%。IEEE 802.15.4 需求的灵敏度为-85dBm。 根据 IEEE 802.15.4,PER=1%。IEEE 802.15.4 需求的饱和度为-20dBm。 要求信号强度-82dBm, 相邻的已调制信道 相邻信道抑制 信道间隔 5MHz 间隔 5MHz, 根据 IEEE 802.15.4, PER=1%。 IEEE 802.15.4 需求的相邻信道抑制为 0dB。 要求信号强度-82dBm, 相邻的已调制信道 相邻信道抑制 信道间隔-5MHz 间隔-5MHz,根据 IEEE 802.15.4, PER=1%。IEEE 802.15.4 需求的相邻信道 抑制为 0dB。 要求信号强度-82dBm, 相邻的已调制信道 交替信道抑制 信道间隔 10MHz 间隔 10MHz,根据 IEEE 802.15.4, PER=1%。IEEE 802.15.4 需求的相邻信道 抑制为 30dB。 要求信号强度-82dBm, 相邻的已调制信道 交替信道抑制 信道间隔-10MHz 信道抑制 ≥20MHz ≤-20MHz 间隔-10MHz,根据 IEEE 802.15.4, PER=1%。IEEE 802.15.4 需求的相邻信道 抑制为 30dB。 要求信号强度-82dBm,不需要的信号在 802.15.4 调制的信道中,逐步通过 2405~ 2480MHz 的整个信道。PER=1%。 6 华亨科技有限公司深圳分公司 http://www. 57 57 dB 57 dB 57 dB 49 dB 49 dB 最小值 典型值 -97 最大值 -92 -88 单位 dBm

Datasheet MLX90614 中文 数据手册 rev008

3901090614 Rev 008

第 2 / 52 页

数据手册 2013/2/28

MLX90614 系列

单区视场和双区视场 TO-39 封装 红外温度传感器

3 目录

1 功能图 ........................................................................................................................................................................................................ 1 2 概述 ............................................................................................................................................................................................................ 1 3 目录 ............................................................................................................................................................................................................ 3 4 术语缩写 ...........................................................

UART(中文版的数据手册)

UART(中⽂版的数据⼿册)第⼗⼀章异步串⼝通信概述S3C2410的UART提供3个独⽴的异步串⾏通信端⼝,每个端⼝可以基于中断或者DMA进⾏操作。

换句话说,UART控制器可以在CPU和UART之间产⽣⼀个中断或者DMA请求来传输数据。

UART在系统时钟下运⾏可⽀持⾼达230.4K 的波特率,如果使⽤外部设备提供的UEXTCLK,UART的速度还可以更⾼。

每个UART通道各含有两个16位的接收和发送FIFO。

S3C2410的UART包括可编程的波特率,红外接收/发送,⼀个或两个停⽌位插⼊,5-8位数据宽度和奇偶校验。

每个UART包括⼀个波特率发⽣器、⼀个发送器、⼀个接收器和⼀个控制单元,如图11-1所⽰。

波特率发⽣器的输⼊可以是PCLK或者UEXTCLK。

发送器和接收器包含16位的FIFO和移位寄存器,数据被送⼊FIFO,然后被复制到发送移位寄存器准备发送,然后数据按位从发送数据引脚TxDn输出。

同时,接收数据从接收数据引脚RxDn按位移⼊接收移位寄存器,并复制到FIFO。

特性—RxD0, TxD0, RxD1, TxD1, RxD2, 和TxD2基于中断或者DMA操作—UART Ch 0, 1, 和 2 具有 IrDA 1.0 & 16 字节 FIFO—UART Ch 0 和 1 具有 nRTS0, nCTS0, nRTS1, 和 nCTS1—⽀持发⽣/接收握⼿图11-1 UART⽅框图串⼝操作下述部分描述了UART的⼀些操作,包括数据发送、数据接收、中断产⽣、波特率发⽣、loop-back模式、红外模式和⾃动流控制。

数据发送发送数据的帧结构是可编程的,它由1个起始位、5-8个数据位、1个可选的奇偶位和1-2个停⽌位组成,这些可以在线控制寄存器ULCONn中设定。

接收器可以产⽣⼀个断点条件——使串⾏输出保持1帧发送时间的逻辑0状态。

当前发送字被完全发送出去后,这个断点信号随后发送。

断点信号发送之后,继续发送数据到Tx FIFO(如果没有FIFO则发送到Tx保持寄存器)。

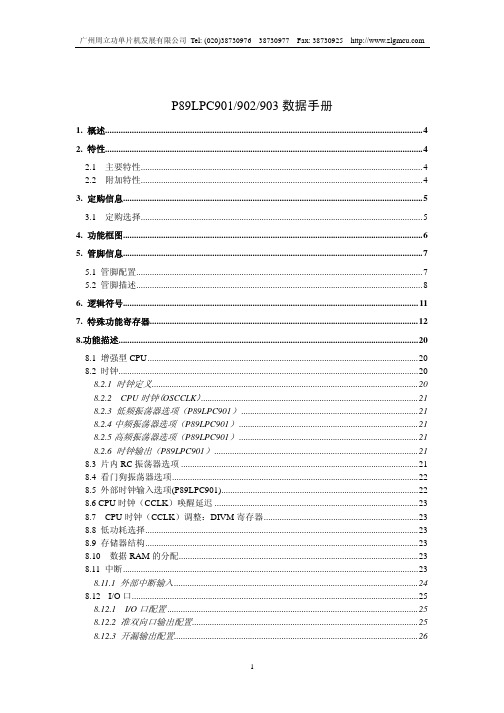

P89LPC901_902_903中文数据完整手册

3. 定购信息......................................................................................................................................5 3.1 定购选择..............................................................................................................................5

4. 功能框图......................................................................................................................................6 5. 管脚信息......................................................................................................................................7 5.1 管脚配置................................................................................................................................7 5.2 管脚描述................................................................................................................................8 6. 逻辑符号.................................................................................................................................... 11 7. 特殊功能寄存器........................................................................................................................12 8.功能描述......................................................................................................................................20 8.1 增强型 CPU.........................................................................................................................20 8.2 时钟......................................................................................................................................20 8.2.1 时钟定义 .......................................................................................................................20 8.2.2 CPU 时钟(OSCCLK) .................................................................................................21 8.2.3 低频振荡器选项(P89LPC901) ...............................................................................21 8.2.4 中频振荡器选项(P89LPC901) ................................................................................21 8.2.5 高频振荡器选项(P89LPC901) ................................................................................21 8.2.6 时钟输出(P89LPC901) ...........................................................................................21 8.3 片内 RC 振荡器选项 ..........................................................................................................21 8.4 看门狗振荡器选项 ..............................................................................................................22 8.5 外部时钟输入选项(P89LPC901)........................................................................................22 8.6 CPU 时钟(CCLK)唤醒延迟 ...........................................................................................23 8.7 CPU 时钟(CCLK)调整:DIVM 寄存器 .....................................................................23 8.8 低功耗选择 ..........................................................................................................................23 8.9 存储器结构 ..........................................................................................................................23 8.10 数据 RAM 的分配...........................................................................................................23 8.11 中断 ....................................................................................................................................23 8.11.1 外部中断输入 .............................................................................................................24 8.12 I/O 口 ................................................................................................................................25 8.12.1 I/O 口配置 ................................................................................................................25 8.12.2 准双向口输出配置 .....................................................................................................25 8.12.3 开漏输出配置 .............................................................................................................26

ADI中文版数据手册说明书

Rev. 0 Document FeedbackInformation furnished by Analog Devices is believed to be accurate and reliable. However , no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties that may result from its use. Speci cations subject to change without notice. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices. T rademarks and registered trademarks are the property of their respective owners.One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.Tel: 781.329.4700 ©2013 Analog Devices, Inc. All rights reserved. Technical Support ADI 中文版数据手册是英文版数据手册的译文,敬请谅解翻译中可能存在的语言组织或翻译错误,ADI 不对翻译中存在的差异或由此产生的错误负责。

如需确认任何词语的准确性,请参考ADI 提供的最新英文版数据手册。

典型应用电路CHANNEL 2BUCK REGULATOR (1.2A/2.5A/4A)CHANNEL 3BUCK REGULATOR(1.2A)OSCILLATOR INT VREG 100mAQ1Q2L1L2VREGSYNC/MODERT FB1BST1SW1DL1PGND DL2SW2BST2FB2L3BST3SW3FB3PGND3L4BST4SW4FB4PGND4VREGPVIN1COMP1EN1PVIN2COMP2EN2PVIN3PWRGD SS34COMP3EN3PVIN4COMP4EN4C2C1C4C3C5C6C7C8C9C10C11C12C134.5V TO 15VVOUT1VOUT2VOUT3VOUT4R ILIM1R ILIM2VREGEXPOSED PADSS12C0VDDCHANNEL 5200mA LDO REGULATORFB5PVIN5EN5VOUT5C14C15VOUT51.7V TO 5.5VADP5052CHANNEL 1BUCK REGULATOR (1.2A/2.5A/4A)CHANNEL 4BUCK REGULATOR(1.2A)10900-001图1.带四通道降压调节器和200 mA LDO 调节器的5通道集成式电源解决方案产品特性宽输入电压范围:4.5 V 至15 V输出精度:±1.5%(整个温度范围内)可调开关频率范围:250 kHz 至1.4 MHz 可调/固定输出选项,可通过工厂熔丝调节电源调节通道1和通道2:带低端FET 驱动器的可编程1.2 A/2.5 A/4 A 同步降压调节器通道3和通道4:1.2 A 同步降压调节器通道5:200 mA 低压差(LDO)调节器针对小负载要求,5.1 V LDO 电源始终处于激活状态8 A 单通道输出(通道1和通道2并联工作)精密使能,0.8 V 精确阈值有源输出放电开关FPWM 或自动PWM/PSM 模式选择频率同步输入或输出针对OVP/OCP 故障提供可选的闩锁保护所选通道的电源良好指示UVLO 、OCP 和TSD 保护48引脚7 mm × 7 mm LFCSP 封装结温范围:−40°C 至+125°C应用小型蜂窝基站FPGA 和处理器应用安防和监控医疗应用概述ADP5052在一个48引脚LFCSP 封装中集成了四个高性能降压调节器和一个200 mA 低压差(LDO)调节器,可满足严苛的性能和电路板空间要求。

DS18B20数据手册-中文版

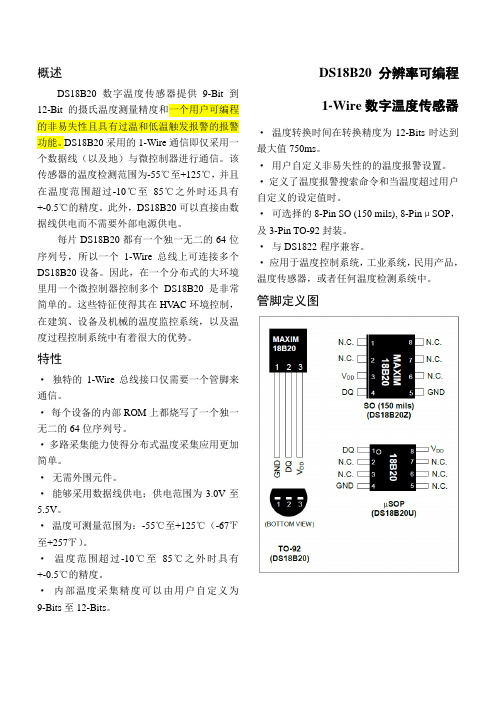

概述DS18B20数字温度传感器提供9-Bit 到12-Bit的摄氏温度测量精度和一个用户可编程的非易失性且具有过温和低温触发报警的报警功能。

DS18B20采用的1-Wire通信即仅采用一个数据线(以及地)与微控制器进行通信。

该传感器的温度检测范围为-55℃至+125℃,并且在温度范围超过-10℃至85℃之外时还具有+-0.5℃的精度。

此外,DS18B20可以直接由数据线供电而不需要外部电源供电。

每片DS18B20都有一个独一无二的64位序列号,所以一个1-Wire总线上可连接多个DS18B20设备。

因此,在一个分布式的大环境里用一个微控制器控制多个DS18B20是非常简单的。

这些特征使得其在HV AC环境控制,在建筑、设备及机械的温度监控系统,以及温度过程控制系统中有着很大的优势。

特性·独特的1-Wire总线接口仅需要一个管脚来通信。

·每个设备的内部ROM上都烧写了一个独一无二的64位序列号。

·多路采集能力使得分布式温度采集应用更加简单。

·无需外围元件。

·能够采用数据线供电;供电范围为3.0V至5.5V。

·温度可测量范围为:-55℃至+125℃(-67℉至+257℉)。

·温度范围超过-10℃至85℃之外时具有+-0.5℃的精度。

·内部温度采集精度可以由用户自定义为9-Bits至12-Bits。

DS18B20 分辨率可编程1-Wire数字温度传感器·温度转换时间在转换精度为12-Bits时达到最大值750ms。

·用户自定义非易失性的的温度报警设置。

·定义了温度报警搜索命令和当温度超过用户自定义的设定值时。

·可选择的8-Pin SO (150 mils), 8-PinμSOP,及3-Pin TO-92封装。

·与DS1822程序兼容。

·应用于温度控制系统,工业系统,民用产品,温度传感器,或者任何温度检测系统中。

ENC28J60_cn中文手册

2

20

3

19

4 ENC28J60 18

5

17

6

16

7

15

8 9 1011121314

VDDOSC

OSC2 OSC1 VSSOSC VSSPLL VDDPLL VDDRX

2006 Microchip Technology Inc.

高级信息

DS39662A_CN 第 1 页

ENC28J60

目录

1.0 概述 ... 2.0 外部连接 ... 3.0 存储器构成 ... 4.0 串行外设接口 (SPI) ... 5.0 以太网概述 ... 6.0 初始化 ... 7.0 发送和接收数据包 ... 8.0 接收过滤器 ... 9.0 双工模式配置和协商 ... 10.0 流量控制 ... 11.0 复位 ... 12.0 中断 ... 13.0 直接存储器访问控制器 ... 14.0 掉电 ... 15.0 内置自测试控制器 ... 16.0 电气特性 ... 17.0 封装信息 ... 索引 ... 客户支持 ... 系统信息和升级热线 ... 读者反馈表 ... 产品标识体系 ...

... 3 .. 5 .. 11 . 25 .. 31 . 33 . 39 .. 47 ... 53 ... 55 . 59 . 65 .. 75 . 77 . 79 ... 83 ... 89 .. 95 . 97 . 97 ... 98 .. 99

致客户

我们旨在提供᳔佳文档供客户正确使用 Microchip 产品。为此,我们将不断改进出版物的内容和质量,使之更好地满足您的要求。 出版 物的质量将随新文档及更新版本的推出而得到提升。 如果您对本出版物有任何问题和建议,请通过电子邮件联系我公司 TRC 经理,电子邮件地址为 CTRC@,或将本 数据手册 后附的 《读者反馈表》传真到 86-21-5407 5066。我们期待您的反馈。

CC2530数据手册(中文)

应用

2.4-GHz IEEE 802.15.4 系统 RF4CE 远程控制系统(64-KB 或者更高的 Flash) ZigBee 系统(256-KB Flash) 家庭/建筑自动化 照明系统 工业控制和监测 低功耗无线传感器网络 消费类电子 医疗保健 请注意关于是否可用、标准保修,德州仪器半导体产品的关键应用和免责条款在本 数据手册的末尾。 RemotTI、SmartRF、Z-Stack 是德州仪器的商标。 IAR Embedded Workbench 是 IAR 系统公司的商标。 ZigBee 是 ZigBee 联盟的注册商标。 所有其它商标均为其所有者所有。 � � � � � � � � �

0 数据手册 CC253 CC2530

和 16MHz RC 振荡器启动 活动→TX 或 RX 最初运行于 16MHz RC 振荡器, 32MHz 晶体振荡器关闭 32MHz 晶体振荡器初始开启。 RX/TX 和 TX/RX 转换 无线模块部分 RF 频率范围 无线比特率 无线片码率 信道间可编程设置步长 1MHz 或者 5MHz,以适应 IEEE 80EE 802.15.4 定义的相同 2394 250 2 2507 MHz kbps MChip/s 0.5 192 192 ms us us

推荐运行条件

最小值 运行环境温度范围,TA 运行供电电压 -40 2 最大值 125 3.6 单位 ℃ V

电气特性

测量按照 TI 公司 CC2530EM 设计参考进行,若无其他规定,则 TA=25℃,VDD=3V。 黑体字仅适用于整个工作范围,TA= -40℃到 125℃,VDD=2V 到 3.6V,fc=2394MHz 到 2507MHz。

90 90 60 70 0.6

uA uA uA uA uA

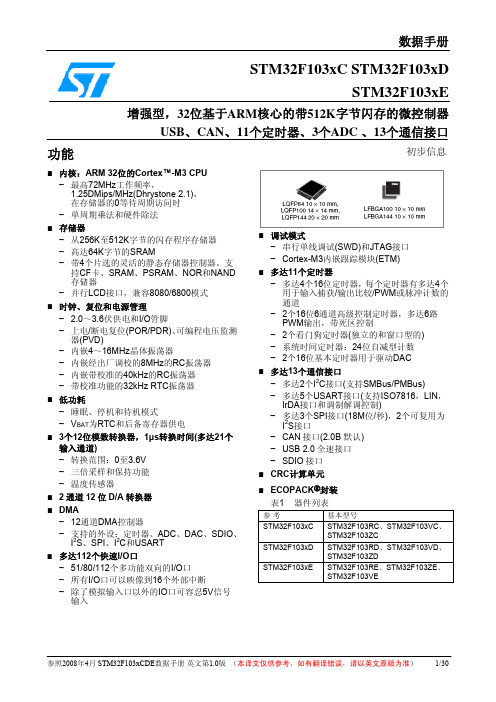

STM32F103_数据手册(中文)

参照2008年4月 STM32F103xCDE数据手册 英文第1.0版 (本译文仅供参考,如有翻译错误,请以英文原稿为准)

4/30

STM32F103xC, STM32F103xD, STM32F103xE数据手册

● 代码可以在除PC卡外的片外存储器运行; ● 目标频率为SYSCLK/2,即当系统时钟为72MHz时,外部访问的速度可达36MHz;

数据手册

STM32F103xC STM32F103xD

功能

STM32F103xE

增强型,32位基于ARM核心的带512K字节闪存的微控制器 USB、CAN、11个定时器、3个ADC 、13个RM 32位的Cortex™-M3 CPU − 最高72MHz工作频率, 1.25DMips/MHz(Dhrystone 2.1), 在存储器的0等待周期访问时 − 单周期乘法和硬件除法

STM32F103xC, STM32F103xD, STM32F103xE数据手册

1 介绍

本文给出了STM32F103xC、STM32F103xD和STM32F103xE增强型的订购信息和器件的机械特性。

有关闪存存储器的编程、擦除和保护等信息,请参考《STM32F10xxx闪存编程参考手册》。 有关Cortex-M3的信息,请参考《Cortex-M3技术参考手册》

嵌套的向量式中断控制器(NVIC) STM32F103xC、STM32F103xD和STM32F103xE增强型内置嵌套的向量式中断控制器,能够处

理多达60个可屏蔽中断通道(不包括16个Cortex™-M3的中断线)和16个优先级。 ● 紧耦合的NVIC能够达到低延迟的中断响应处理 ● 中断向量入口地址直接进入内核 ● 紧耦合的NVIC接口 ● 允许中断的早期处理 ● 处理晚到的较高优先级中断 ● 支持中断尾部链接功能 ● 自动保存处理器状态 ● 中断返回时自动恢复,无需额外指令开销 该模块以最小的中断延迟提供灵活的中断管理功能。

stm32f407数据手册中文

本参考手册涵盖了基于ARM® Cortex®-M3内核的单片机STM32F101xx, STM32F102xx, STM32F103xx, STM32F105xx and STM32F107xx产品线,它为用户使用以上单片机提供了完整的存储器和外设信息。

(STM32F101xx, STM32F102xx, STM32F103xx, STM32F105xx and STM32F107xx advanced ARM-based 32-bit MCUs)

计算机图形学,输入的是对虚拟场景的描述,通常为多边形数组,而每个多边形由三个顶点组成,每个顶点包括三维坐标、贴图坐标、RGB 颜色等。

输出的是图像,即二维像素数组。

计算机视觉,输入的是图像或图像序列,通常来自相机、摄像头或视频文件。

输出的是对于图像序列对应的真实世界的理解,比如检测人脸、识别车牌。

图像处理,输入的是图像,输出的也是图像。

Photoshop中对一副图像应用滤镜就是典型的一种图像处理。

常见操作有模糊、灰度化、增强对比度等。

尽管三者所涉及的都是运用计算机来处理对象,但是长期以来却是属于不同技术领域,近些年来,随着多媒体技术、计算机动画以及三维数据场显示技术等的迅速发展,计算机图形学、图像处理和计算机视觉结合日益紧密,并且相互渗透。

例如,三维游戏为了增加表现力会叠加全屏的后期特效,原理就是数字图像处理,只是将计算量放在了显卡端;计算机视觉对需要识别的照片进行预处理也是运用了数字图像处理技术;最明显的是增强现实(AR),用数字图像处理技术进行预处理,用计算机视觉技术进行跟踪物体的识别与姿态获取,用图形学技术进行虚拟三维物体的叠加和显示。

stm32f103中文手册[14]

![stm32f103中文手册[14]](https://img.taocdn.com/s3/m/8c1a2e2b6d175f0e7cd184254b35eefdc8d31580.png)

stm32f103中文手册一、概述stm32f103c8/cb:64KB或者128KB闪存,20KBSRAM,48引脚或者64引脚LQFP封装。

stm32f103r8/rb:64KB或者128KB闪存,20KBSRAM,64引脚LQFP封装。

stm32f103v8/vb:64KB或者128KB闪存,20KBSRAM,100引脚LQFP封装。

stm32f103rc/rd/re:256KB或者384KB或者512KB闪存,48KB或者64KB SRAM,64引脚或者100引脚LQFP封装。

stm32f103vc/vd/ve:256KB或者384KB或者512KB闪存,48KB或者64KB SRAM,100引脚或者144引脚LQFP封装。

stm32f103zc/zd/ze:256KB或者384KB或者512KB闪存,48KB或者64KB SRAM,144引脚LQFP封装。

stm32f103的主要特性如下:72MHz的主频,1.25 DMIPS/MHz的性能。

从32KB到512KB的闪存容量,从20KB到64KB的SRAM容量。

从37到112个GPIO引脚,支持多种工作模式和中断功能。

从3到7个定时器,支持多种工作模式和中断功能。

从2到3个12位ADC,支持多种触发模式和DMA传输功能。

从2到3个SPI接口,支持全双工和单向通信模式。

从2到3个I2C接口,支持标准模式和快速模式。

从3到5个USART接口,支持同步和异步通信模式。

一个USB 2.0全速设备接口,支持12Mbps的数据传输速率。

一个CAN 2.0B接口,支持标准帧和扩展帧格式。

一个SDIO接口,支持SD卡和MMC卡的读写操作。

一个RTC实时时钟模块,支持日历功能和闹钟功能。

一个CRC循环冗余校验模块,支持多种多项式计算方式。

多种低功耗模式,包括睡眠模式、住手模式和待机模式。

多种时钟源选择,包括内部RC振荡器、外部晶振、PLL锁相环等。

多种复位源选择,包括电源复位、软件复位、看门狗复位等。

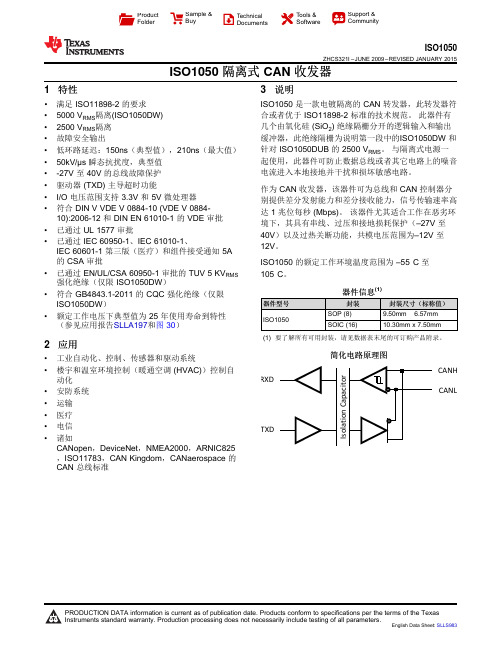

ISO1050中文资料_数据手册_参数

器件型号 ISO1050

器件信息(1)

封装

封装尺寸(标称值)

SOP (8)

9.50mm × 6.57mm

SOIC (16)

10.30mm x 7.50mm

(1) 要了解所有可用封装,请见数据表末尾的可订购产品附录。

简化电路原理图

CANH RXD

CANL

TXD

1பைடு நூலகம்

PRODUCTION DATA information is current as of publication date. Products conform to specifications per the terms of the Texas Instruments standard warranty. Production processing does not necessarily include testing of all parameters.

English Data Sheet: SLLS983

ISO1050

ZHCS321I – JUNE 2009 – REVISED JANUARY 2015

目录

1 特性.......................................................................... 1 2 应用.......................................................................... 1 3 说明.......................................................................... 1 4 修订历史记录 ........................................................... 2 5 Pin Configuration and Functions ......................... 5 6 Specifications......................................................... 6

Nrf2401 datasheet 数据手册 中文资料

3 在接收模式下 当接收到与本机地址一致是 通过 DR1 输出中断指示 高有效 单片机通过 DATA CLK1 接收数据

3 通道 2 接口 通道 2 接口 CLK2 DOUT2 DR2 为三线数据接口 在 PTR4000 模块中保留未使用

五 PTR4000 的配置 PTR4000 上电以后首先必须通过单片机对其进行配置 单片机首先将按照模式控制真值表 表 4

1 在配置模式下 单片机通过通道 1 的 DATA CLK1 线配置 PTR4000 的工作参数 2 在发射模式下 单片机通过通道 1 的 DATA CLK1 发送数据

COPYRIGHT ©2003 ALL RIGHTS RESERVED 迅通科技 TEL: 0451 86349363 E-mail: sales@ 2

六 PTR4000 的软件编程 1 配置编程

1 上电以后 MCU 首先配置 PTR4000 模块 先将 CS CE 设为配置模式 见表 4 1 MCU 通 过 CLK1 DATA 将配置数据移入 PTR4000 模块 CLK1 由 MCU 提供 MSB 首先移入

2 全部配置 120 bit 配置数据均移入后 由 MCU 将 CS CE 设为工作模式 此时 PTR4000 将刷 新内部配置并使得新配置立即生效 在掉电和待机模式工作后 配置内容仍然有效 配置数据 只有当电源撤除后才会丢失

1 编程配置接口

该接口由 CE CS PWR 组成 控制 PTR4000 的四种工作模式 配置模式 发射/接收模式 待机模

式 Power down 掉电模式 配置数据由 DATA CLK1 输入 各种模式的控制模式见下表 4 1

模式

PWR

CE

CS

工作模式 发射/接收

SI4010中文手册

SI4010-C2数据手册-中文特点⏹ 可配置不使用外部晶振➢ 晶振源可配置 ⏹ 高速8051UC 内核 ➢管道指令架构 ➢ 70%的指令执行需要1个或2个时钟周期 ➢ 高达24 MIPs(使用24M 时钟时) ➢ 4k RAM/8k NVM(一次性非易失性存储器) ➢128 bit EEPROM ➢256字节的内部数据RAM ➢ 12 kB API 函数(嵌入在ROM 中) ⏹ 大量的数字外设 ➢ 128位AES 加速器 ➢5/9个具有唤醒功能GPIO ➢LED 驱动器 ➢数据串行器 ➢高速频率计数器 ➢在线调试接口:C2 ➢唯一的4字节序列号 ➢ 超低功耗睡眠定时器 ⏹ 一枚纽扣电池➢ 供给电压:1.8到3.6V ➢ 待机电流 < 10nA ⏹ 高性能射频发射机 ➢ 频率范围:27-960 MHz ➢ +10 dBm 输出功率(可调的) ➢ 天线自动调整 ➢ 符号速率高达100kbps ➢ FSK/OOK 调制方式 ➢ Manchester, NRZ, 4/5编码 ⏹ 模拟外设 ➢带POR 电路的LDO 调节器 ➢ 电池电压监测 ⏹ 温度范围-40至+85℃ ⏹ 可选汽车质量标准AEC-Q100(等待最后的资格测试) ⏹ 10-pin MSOP / 14-pinSOIC说明Si4010是一个全集成无晶体CMOS SoC射频发射机,内置CIP-518051单片机。

该设备可以在-40至85°C的温度范围内运行,而无需外部晶体参考源,从而减少板面积和BOM成本。

该设备包括用于编程用户应用程序的8kb非易失性存储器块以及可以被用户应用程序调用API函数的12k内嵌ROM(存放API函数代码)。

Si4010包括Silicon Laboratories的2线C2调试和编程接口,允许客户在开发阶段将其代码下载到芯片RAM中,以便在对NVM编程之前进行测试和调试。

NVM为一次性烧录,程序开发完毕之后使用NVM烧录最后的应用程序。

OV7670 中文版数据手册1.01

OV7670/OV7171CM OS VGA(O m niPixel®)CAMERAC 简介功能●●●●●●●●●●●●●●●1 OV7670/OV7171管脚图(俯视OV7670/OV7171 CMOS VGA 图像传感器数据手册数据手册. OmniPixel,VarioPixel,OmniVision图标已注册为功能简介图2 描述的是OV7670/OV7171图像传感器的功能模块,包括:●感光阵列(共有656x488个像素,其中在YUV的模式中,有效像素为640x480个)●模拟信号处理●A/D转换●测试图案发生器●数字信号处理器●图像缩放●时序发生器●数字视频端口●SCCB接口●LED和闪光灯输出控制图 2 功能框Note1: DSP*(镜头校正、去噪声、黑白点补偿、自动白平衡等) 7670CSP_DS_002测试图案发生器测试图案发生器有如下功能:●八色彩色条图案●渐变至黑白彩色条图案●输出脚移位“1”数字处理器(DSP)这个模块控制由原始信号插值到RGB 信号的过程,并控制一些图像质量:●边缘锐化(二维高通滤波器)●颜色空间转换(原始信号到RGB 或者YUV/YCbYCr)●RGB 色彩矩阵以消除串扰●色相和饱和度的控制●黑/白点补偿●降噪●镜头补偿●可编程的伽玛●十位到八位数据转换缩放功能这个模块按照预先设置的要求输出数据格式,能将YUV/RGB 信号从VGA 缩小到CIF 以下的任何尺寸。

数字视频接口寄存器COM2[1:0]调节IOL/IOH 的驱动电流,以适应用户的负载。

SCCB 接口SCCB 接口控制图像传感器芯片的运行,详细使用方法参照OmniVision Te ch nolo g ies Seril Camera Control B u s(SCCB) Spe c ifi c ation LED 和闪光灯的输出控制OV7670/OV7171有闪光灯模式,控制外接闪光灯或闪光LED 的工作。

DS18B20数据手册-中文版

DS18B20数据手册-中文版关键信息项1、协议名称:DS18B20 数据手册中文版2、适用产品:DS18B20 传感器3、数据格式:详细说明数据的传输和存储格式4、测量范围:明确传感器能够测量的温度范围5、精度:给出测量温度的精度数值6、响应时间:描述传感器对温度变化的响应速度7、供电要求:说明所需的供电电压和电流等参数8、接口类型:注明与其他设备连接的接口类型和规范11 概述本协议旨在提供关于DS18B20 传感器的详细技术规格和使用说明,以确保用户能够正确、有效地使用该传感器进行温度测量和数据处理。

111 DS18B20 简介DS18B20 是一款数字式温度传感器,具有体积小、精度高、接口简单等优点,广泛应用于各种温度测量场景。

112 特点1、独特的单总线接口,仅需一根数据线即可与微控制器进行通信。

2、测量范围广,可满足大多数应用场景的需求。

3、在-10℃至+85℃范围内,精度可达 ±05℃。

12 技术规格121 测量范围-55℃至+125℃122 精度在-10℃至+85℃范围内,精度为 ±05℃;在其他温度范围内,精度会有所降低。

123 分辨率用户可通过编程设置分辨率,可选 9 位至 12 位。

124 响应时间典型的温度转换时间为 750ms(12 位分辨率)。

13 供电要求131 供电电压工作电压范围为 30V 至 55V。

132 电流消耗在待机模式下,电流消耗极低;在温度转换期间,电流消耗会有所增加。

14 接口类型141 单总线接口采用独特的单总线协议进行通信,数据线需要上拉电阻。

142 时序要求严格遵循单总线的时序要求,以确保数据的正确传输。

15 数据格式151 温度数据以 16 位补码形式存储温度值。

152 校验位包含校验位以确保数据的准确性。

16 操作指令161 初始化指令用于启动传感器与控制器之间的通信。

162 温度转换指令触发传感器进行温度测量和转换。

163 读取数据指令读取传感器转换后的温度数据。

中文 数据手册

中文数据手册

数据手册是一种详细描述产品或系统技术规格和性能参数的技术文档。

对于中文数据手册,它主要针对中国市场的特定用户需求进行编写,提供产品或系统的中文信息,以便更好地满足中文用户的需求。

数据手册的内容可能包括产品的概述、技术规格、使用指南、性能参数、产品优势等,以帮助用户更好地了解和使用产品或系统。

对于中文数据手册,其内容可能需要考虑语言习惯、文化差异和用户需求等因素,以确保信息的准确性和可读性。

同时,中文数据手册的编写也需要遵循一定的规范和标准,以确保信息的准确性和一致性。

如果您需要中文数据手册,建议您查找相关的官方网站、技术论坛或联系相关厂商获取。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

AD9854特征·300M内部时钟频率·可进行频移键控(FSK),二元相移键控(BPSK),相移键控(PSK),脉冲调频(CHIRP),振幅调制(AM)操作·正交的双通道12位D/A转换器·超高速比较器,3皮秒有效抖动偏差·外部动态特性:80 dB无杂散动态范围(SFDR)@ 100 MHz (±1 MHz) A·4倍到20倍可编程基准时钟乘法器·两个48位可编程频率寄存器·两个14位可编程相位补偿寄存器·12位振幅调制和可编程的通断整形键控功能·单引脚FSK和BPSK数据输入接口·PSK功能可由I/O接口实现·具有线性和非线性的脉冲调频(FM CHIRP)功能,带有引脚可控暂停功能·具有过渡FSK功能·在时钟发生器模式下,有小于25 ps RMS抖动偏差·可自动进行双向频率扫描·能够对信号进行sin(x)/x校正·简易的控制接口:可配置为10MHZ串行接口,2线或3线SPI兼容接口或100MHZ 8位并行可编程接口·3.3V单电源供电·具有多路低功耗功能·单输入或差分输入时钟·小型80脚LQFP 封装应用·便携式频率特性分析仪·可编程时钟发生器·应用于雷达和扫频系统的脉冲调频信号源·测试和测量设备·商业和业余的射频(RF)发射机概述AD9854数字合成器是高集成度的器件,它采用先进的DDS技术,片内整合了两路高速、高性能正交D/A转换器通过数字化编程可以输出I、Q两路合成信号。

在高稳定度时钟的驱动下,AD9854将产生一高稳定的频率、相位、幅度可编程的正弦和余弦信号,作为本振用于通信,雷达等方面。

AD9854的DDS核具有48位的频率分辨率(在300M系统时钟下,频率分辨率可达1uHZ)。

输出17位相位截断保证了良好的无杂散动态范围指标。

AD9854允许输出的信号频率高达150MHZ,而数字调制输出频率可达100MHZ。

通过内部高速比较器正弦波转换为方波输出,可用作方便的时钟发生器。

器件有两个14位相位寄存器和一个用作BPSK操作的引脚。

对于高阶的PSK调制,可通过I/O接口改变相位控制字实现。

具有改进DDS结构的12位I和Q通道D/A转换器可以提供较大的带宽并有较好的窄带无杂散动态范围(SFDR)。

如果不使用Q通道的正交功能,它还可以通过配置,由用户编程控制D/A转换。

当配置高速比较器时,12位D/A输出的方波可以用来做时钟发生器。

它还有两个12位数字正交可编程幅度调制器,和通断整形键控功能,并有一个非常好的可控方波输出。

同时脉冲调制功能在宽带扫频中也有重要应用。

AD9854的300M系统时钟可以通过4X和20X可编程控制电路由较低的外部基准时钟得到。

直接的300M时钟也可以通过单端或差分输入。

AD9854还有单脚输入的常规FSK和改进的斜率FSK输出。

AD9854采用先进的0.35微米COMS工艺在3.3V单电源供电的情况下提供强大的功能。

AD9854采用节省空间的80脚LQFP表面装配封装和改进散热的80脚LQFP封装。

AD9854的引脚与AD9852的单频信号发生器模式相兼容。

AD9854的特定操作允许温度是工业级范围:-40到85摄氏度。

引脚配置和功能描述图1 管脚配置RD/CSFSK/BPSK/HOLD SHAPED KEYING AVDDAGNDVOUTVINPIOUT2IOUT2 DACBPDAC RPLL FILTERREFCLK REFCLKS/P SELECT MASTER RESET操作说明AD9854正交数字信号发生器是一款有着广泛应用的非常灵活的器件。

器件包括一个48位的相位累加器,可编程基准时钟乘法器,反辛格滤波器,数字乘法器,两个12位/300HZ 数模转换器,一个高速模拟比较器和内部逻辑电路。

这款高度集成的器件可以用作本机震荡发生器,灵活的时钟发生器和FSK/BPSK调制器。

Analog Devics股份有限公司的技术指南提供了关于器件功能模块的操作说明。

指南包括利用DDS器件产生信号的技术描述并提供了适合多种数字化实体的基本应用。

文件,《关于数字信号发生器的技术指南》在AD公司DDS网页DDS技术库中提供。

操作模式AD9854有5种可编程操作模式。

为了选择某一模式,必须对控制寄存器(并行操作地址:1FH)中的3个相关位进行编程设置。

具体描述在下表:表2. 模式选择表在每种模式下都有许多功能不被允许。

单信号模式(模式000)这是用户复位之后的一种默认模式。

也可以通过用户编程使能这种模式。

相位累加器用以产生信号的频率,它有48位有效值,取自频率调整寄存器1,它的默认值为0。

保留寄存器的默认值更能决定输出信号的质量。

用户复位后,默认设置配置器件,输出0HZ,0相位的信号。

在上电复位时,在I和Q 通道输出的是一半满幅电流的直流信号。

这是默认模式的0幅度输出。

选择幅度开关键控模式则需要更多细节的输出幅度控制。

若输出用户定义的信号需要对28个寄存器全部或部分进行编程。

表35显示了从默认0HZ到用户定义输出频率的变化。

和所有AD DDS器件一样,频率控制字有如下定义:FTW = (Desired Output Frequency × 2N)/SYSCLK式中:N相位累加器的资源(本器件48位)。

Frequency 以HZ表示。

FTW (频率调整字)是一个定义数字。

一旦定义数字选定,它必须转换为内部的权重为1或0的48位串行二进制码。

建立的DAC输出信号频率范围从直流到1/2系统时钟。

改变频率时相位是连续的,这意味着新的频率的相位取样值参考之前输出频率的相位取样值。

AD9854的I和Q通道输出的信号总是保持90度的相位差。

调整每个通道的输出相位两个14位相位寄存器并不是独立的。

换而言之,两DAC输出通过相位补偿互相影响。

单信号模式允许用户控制以下信号参数:·48位输出频率精度·12位输出幅度精度-固定的,用户定义的幅度-可变的,可编程幅度控制-自动的,可编程,单引脚控制,幅度成型键控·14位输出相位精度这些参数可以在100MHZ并行速度下通过8位并行端口或10MHZ串行端口通过编程改变和调整。

联合这些属性在单信号模式下可以实现FM,AM,PM,FSK,PSK和ASK操作。

无斜率FSK(模式001)当这种模式被选中,输出的DDS频率是一个选择频率控制寄存器1和2的函数,它的输出取决于29脚逻辑电平的高低。

29脚为逻辑低电平时选择F1(频率控制字1,并行地址为04H到09H),29脚为逻辑高电平时选择F2(频率控制字2,并行地址为0AH到0FH)。

改变频率相位连续,并且和FSK数据引脚内部一致。

但是,FSK数据信号和DAC输出存在线性时延。

无斜率FSK ,是传统FSK,它传输的是数字信号,它在数字通信中有着重要作用。

但是它会影响RF发射机的使用带宽,因此用斜率FSK来改善使用带宽。

斜率FSK(模式010)这种FSK模式下,频率从F1到F2不是直接变化,而是通过扫频和斜率形成。

线性扫频和斜率形成可以很容易的自动完成,不过这都是许多设置中的一项。

其它频率传输的设置,用户可以配置增量控制寄存器,来编程控制扫频间隔和扫频速度。

频率斜率变化不管是线性还是非线性都会输出许多介于F1和F2之间的频率,而不仅是这两个基本输出。

图37和38描述了一线性斜率FSK信号的频率输出与时间的关系。

需要注意,在斜率FSK模式下,频率步进字是要求编程设置的,它被用作双作用的补足值。

须要注意的另一个问题是,最低频率一定要放在频率控制寄存器1中。

斜率FSK通过同缓慢的、用户定义变化率的实时频率来改善传统FSK对带宽的限制。

输出信号在F1和F2频率点保持时间与其它实时点相同或稍大。

与传统FSK不同,斜率FSK 要求:F1和F2分别存储低频率和高频率,而不能任意。

用户必须通过编程来设定DDSd的中间频率变化的步进量of C48位)和每一步所持续的时间△T (20位)。

另外,如果要想让频率输出从0开始变化必须先给CLR ACC1位送一个正脉冲。

对于分段的非线性频率传输,必须对影响输出的寄存器进行编程设置。

并行寄存器1AHex~1CHex构成一个20位的斜率时钟寄存器。

它是一个减计数器,当计数值为0时输出一个脉冲信号。

在29脚的输入电平没有变化时计数器一直有效。

这个计数器在系统时钟下运行,最大频率是300MHZ。

每两个脉冲之间的时间周期用下式表示:(N+1)*(System Clock Period)此处N是用户编程设置的20位斜率变化率。

N的允许范围是1到(2^20-1)。

斜率变化时钟决定频率F1和F2 之间的实时频率持续时间。

当频率达到目标频率时计数器自动停止,而F1和F2两频率点的持续时间由29脚输入的电平决定,电平的高低决定到达的频率点的状态。

图39 FSK功能模块图并行寄存器10Hex~15Hex构成一个48位的双作用的斜率步进寄存器。

当接收到斜率变化时钟时,这个48位控制字被累加。

此控制字被用来加或减到控制正弦或余弦输出的相位步进的频率控制字寄存器F1或F2。

在这种模式下,29脚的电平状态决定输出的频率是增量或减量斜率。

其频率变化率是20位斜率变化寄存器的功能,一旦目标频率到达,计数器将停止计数即频率累加过程停止。

一般来说,频率步进字与频率控制字相比是一个比较小的值,举个例子,如果F1和F2分别是1KHZ和13MHZ,那么步进频率字只有25HZ。

图41显示了,电平过早的变化使频率的斜率变化翻转,并且以相同的变化率返回原状态。

控制寄存器(1FHex)中含有一个“三角形”位。

在010模式下设置此位为高电平将会再频率F1和F2之间进行三角形自动扫频,而不会受29脚电平变化的影响,如图40。

一旦这个位设置为1,29脚的状态将不会起作用。

这一功能需要设置频率变化率和频率步进字来保证F1和F2之间的连续线性扫频具有相同的持续时间。

使用此功能,可以对直流到最大输出频率之间的自动扫频。

在斜率FSK模式下29脚的电平和“三角形”位的上升沿决定扫频是从F1或F2开始(如图42)。

如果29脚电平是高电平而不是低电平,扫频则从F2开始而不是F1。

在F1和F2之间的斜率变化时,通过改变20位频率变化控制字和频率步进控制字,可增加斜率FSK模式的灵活性。

结合多个线性斜率变化和各分段的不同斜率设置,可实现非线性的频率变化。

在不同的设置下,DDS的输出频率在Fl和F2之间以不同的方式变化,实现多种方式扫频。