存储器和总线实验..26页PPT

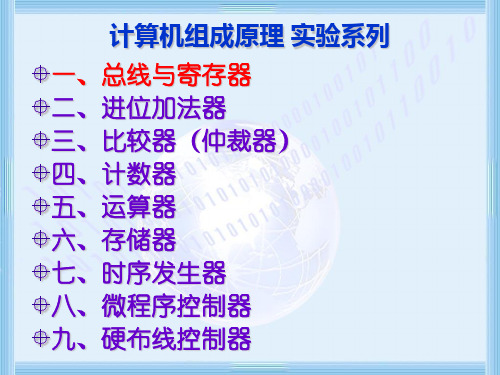

计算机组成原理实验2.1总线与寄存器

1) 令#R0_BUS= #DR_BUS= #SFT_BUS=1,#SW_BUS=0;启动仿 真,通过拨码开关送入总线BUS任意八位二进制数,赋值 74LS194的输入端D0D1D2D3。按照后页的逻辑功能表置位 74LS194的MR、S1、S0 、SL、SR端,观察并记录CLK端上升 沿和下降沿跳变时刻输出端Q0Q1Q2Q3的状态。

2) 令#SW_BUS=0,三态门74LS244导通,记录BUS总线上的数 据,与总线BIN相比较:

BUS_7 BUS_6 BUS_5 BUS_4 BUS_3 BUS_2 BUS_1 BUS_0 BUS总线

单位D触发器:74LS74 四位D触发器:74LS175

D触发器逻辑功能 表

【2】D触发器实验(一Fra bibliotek总线与寄存器 实验 电路图

三态门74LS244

拨码开关与总线缓冲器(注意观察74LS244左右电平)

【1】总线实验

实验步骤:

1) #SW_BUS = #R0_BUS= #DR_BUS= #SFT_BUS=1;启动仿真, 手动拨码开关在总线DIN上置位数据0x55。比较拨码开关 所在的总线DIN与总线BUS上的数据。

实验步骤:

1) 令#R0_BUS= #DR_BUS= #SFT_BUS=1, #SW_BUS=0,启动 仿真,手动拨码开关输入数据到BUS总线,改变74LS74的 D端(即BUS总线的BUS_0)状态,按照后页逻辑功能表置 位74LS74的#Sd端、#Rd端,观察并记录CLK端上升沿 、 下降沿跳变时刻的Q端和#Q端状态。

的0xAA数据存入DR。观察寄存器74LS273的输出端。 6) 再令#R0_BUS=1;观察寄存器74LS374的输出端,请比较器

计算机组成原理实验报告 存储器和总线实验

西华大学数学与计算机学院实验报告课程名称:计算机组成原理年级:2011级实验成绩:指导教师:祝昌宇姓名:蒋俊实验名称:存储器和总线实验学号:312011*********实验日期:2013-12-15一、目的熟悉存储器和总线的硬件电路二、实验原理(1)存储器和总线的构成1、总线由一片74LS245、一片74LS244组成,把整个系统分为内部总线和外部总线。

二片74LS374锁存当前的数据、地址总线上的数据以供LED显示。

(如图1)图1 总线布局图2、存储器采用静态RAM(1片6264)3、存储器的控制电路由一片74LS32和74LS08组成。

(如图2)图2 存储器控制电路布局图(2)存储器和总线的原理1.总线的原理:由于本系统内使用8根地址线、8根数据线,所以使用一片74LS245作为数据总线,另一片74LS244作为地址总线(如图3)。

总线把整个系统分为内部数据、地址总线和外部数据、地址总线,由于数据总线需要进行内外部数据的交换,所以由BUS信号来控制数据的流向,当BUS=1时数据由内到外,当BUS=0时数据由外到内。

图3 总线单元2.由于本系统内使用8根地址线、8根数据线,所以6264的A8~A12接地,其实际容量为256个字节(如图4)。

6264的数据、地址总线已经接在总线单元的外部总线上。

存储器有3个控制信号:地址总线设置存储器地址,RM=0时,把存储器中的数据读出到总线上;当WM =0,并且EMCK有一个上升沿时,把外部总线上的数据写入存储器中。

为了更方便地编辑内存中的数据,在实验机处于停机状态时,可由监控来编辑其中的数据。

图4 内存单元原理图三、使用环境计算机组成原理实验箱四、实验步骤(一)存储器的写操作1.把内部地址总线AJ1(8芯的盒型插座)与CPT-B板上二进制开关单元中的J3插座相连(对应二进制开关H0~H7),把内部数据总线DJ8与CPT-B板上的J2插座相连(对应二进制开关H8~H15)。

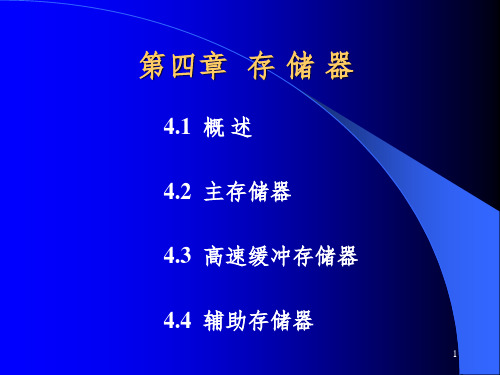

计算机组成原理4第四章存储器PPT课件精选全文

4.2

11

4.2

请问: 主机存储容量为4GB,按字节寻址,其地址线 位数应为多少位?数据线位数多少位? 按字寻址(16位为一个字),则地址线和数据线 各是多少根呢?

12

数据在主存中的存放

设存储字长为64位(8个字节),即一个存 取周期最多能够从主存读或写64位数据。

读写的数据有4种不同长度:

字节 半字 单字 双字

34

3. 动态 RAM 和静态 RAM 的比较

主存

DRAM

SRAM

存储原理

电容

触发器

集成度

高

低

芯片引脚

少

多

功耗

小

大

价格

低

高

速度

慢

快

刷新

有

无

4.2

缓存

35

内容回顾: 半导体存储芯片的基本结构 4.2

…… ……

地

译

存

读

数

址

码

储

写

据

线

驱

矩

电

线

动

阵

路

片选线

读/写控制线

地址线(单向) 数据线(双向) 芯片容量

D0

…… D 7

22

(2) 重合法(1K*1位重合法存储器芯片)

0 A4

0,00

…

0,31

0 A3

X 地

X0

32×32

… …

0址

矩阵

A2

译

0码

31,0

…

31,31

A1

器 X 31

0 A0

Y0 Y 地址译码器 Y31 A 9 0A 8 0A 7 0A 6 0A 5 0

存储器和总线实验..26页PPT

1

0

、

倚南窗以寄傲,审

容

膝

之

易

安

。

▪

26、要使整个人生都过得舒适、愉快,这是不可能的,因为人类必须具备一种能应付逆境的态度。——卢梭

▪

27、只有把抱怨环境的心情,化为上进的力量,才是成功的保证。——罗曼·罗兰

▪

28、知之者不如好之者,好之者不如乐之者。——孔子

存储器和总线实验..

6

、

露

凝

无

游

氛

,

天

高

风

景

澈

。

7、翩翩新 来燕,双双入我庐 ,先巢故尚在,相 将还旧居。

8

、

吁

嗟

身

后

名

,

于

我

若

浮

烟

。

9、 陶渊 明( 约 365年 —427年 ),字 元亮, (又 一说名 潜,字 渊明 )号五 柳先生 ,私 谥“靖 节”, 东晋 末期南 朝宋初 期诗 人、文 学家、 辞赋 家、散

▪

29、勇猛、大胆和坚定的决心能够抵得上武器的精良。——达·芬奇

▪

30、意志是一个强壮的盲人,倚靠在明眼的跛子肩上。——叔本华

谢谢!

26

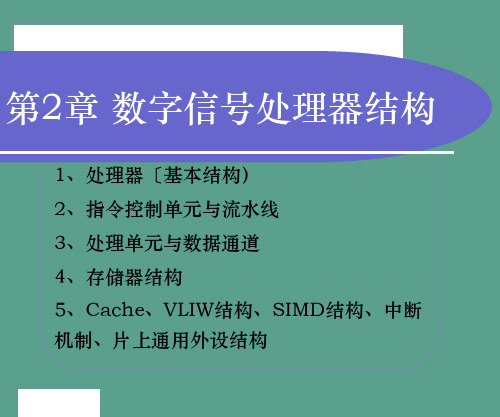

结构4总线和存储器结构ppt课件

2m-1 m-1

MAB

(a) 低位 m 路交叉存取

7、提高存储器带宽技术:高位交叉访问

存储器地址

LSB

MSB

字地址 模块地址

字地址缓冲

模块地址译码器

···

···

··· ···

数 据 总 线 /开 关 网 络

MDB

n-1)

模块 0

1 0

MAB

MDB

···

存储器数据缓冲

2n-1

模块 1

n+1 n

冯诺曼结构 只有一个存储器空间,它通过一套总线〔包

括数据总线和地址总线〕与处理器内核相连 接,程序和数据存放在同一存储空间。 总线带宽低 哈佛结构 指令存储空间和程序存储空间分离,采用两 套独立的总线,一套连接程序存储器和处理 器内核,另一套连接数据存储器和处理器内 核 改进哈佛结构把存储空间分成3个独立空间 现代DSPs为了方便用户,片外存储器使用冯 诺曼结构,但片内存储器充分地利用哈佛结 构

交叉访问例子ldbldhldwlddw指令bitti198存储器的层次结构指令和通用寄存器外部存储器高速缓存cache主存储器cpu内部图2ccc处理器存储器层次结构bitti209存储系统原理存储器在处理器系统仸意组织是丌能成为一个有效的存储系统两个或两个以上速度容量和价格各丌相同的存储器用硬件或和软件连接起来的对应用程序员透明统一的一个数据和或指令存放系统它的速度接近速度最快的存储器的速度它的容量等于或接近容量最大的存储器的容量它的单位容量价格接近容量最大的存储器的单位容量价格bitti219存储系统原理存储系统存储器m1当作系统从外部看

延迟线位置)

2、冯诺曼结构和哈佛结构

处理器内核 地址总线 数据总线

(计算机组成原理)实验二存储器和总线实验

2020/7/8

返回

25

四、实验步骤

❖ 按图接线;控制信号开关置于无效状态。 ❖ 数据3FH写入寄存器R0; ❖ R0数据送总线,置入74299移位器; ❖ 74299执行带进位循环左移一位,并写入输出设备 ❖ R0数据送总线,置入74299移位器; ❖ 74299执行循环右移一位,并写入输出设备 ❖ 74299再执行循环右移2次,写入R0 ❖ 读出R0的数据,送输出部件显示; ❖ 观察总线指示灯,记录实验结果,验证正确与否

拨INPUT的数据开 关(8位二进制地 址)

将地址送上总线 I/O-R=0,Ai=0,打 开地址寄存器 B-AR=

拨输入单元控制信 号I/O-R=1

读存储器:

关闭存储器写信号 M-W=1,拨输入单元 控制信号I/O-R=1

将数据送上总线 I/O-R=0,置写存储 器信号M-W=0将数 据写入相应单元

MEM UNIT

17 16 15 14 13 11 10 9

D7 — D0

❖ 实验仪只使用了8根地址线、8根数据线

❖ 其余地址线及CS# --接地

❖ 存储器的地址由AR通过地址总线提供。

❖ WE#--由M-W#信号控制

OE# 20❖20/7/8 --由M-R#信号控制

7

读存储器的操作时序图

A7--0 M-R D7--0

2020/7/8

10

D0 D1

D2 D3 D4 D5 D6 D7

I/O-W

Ai

D1

Q1

D2

Q2

74LS374

D3

Q3

D4

Q4

驱

D5

Q5

D6

实验一 存储器和总线实验指导书

实验一 存储器和总线实验1.1 实验目的1.熟悉计算机组成原理教学实验系统Dais-CMH+的组成及其使用方法;2.掌握静态随机存储器RAM的工作原理及其使用方法;3.了解存储器和总线组成的硬件电路,了解与存储器有关的总线信号功能及使用方法;1.2 实验内容内部存储器(RAM 6116)读写实验在实验系统的手动工作方式下完成下列操作:(1) 内部总线数据写入存储器:向存储器01H、2EH两个地址单元中分别写入数据1AH、1BH,记录相关数据,填表2-1-4。

(2) 读存储器中数据至总线:依次读出01H、2EH两个地址单元中的内容,查看其各单元中的内容是否与自己写入的内容一致,记录相关数据,填表2-1-5。

1.3实验要求内部存储器(RAM 6116)读写实验要求(1)根据实验原理图2-1-2,在实验设备平台上将存储器单元、地址总线单元、缓冲输入单元、时序启停单元的各控制信号用短线连接好;将各数据总线及地址总线也连好。

(2)按照实验内容完成实验项目。

(3)以表格形式记录实验中的写入/读出数据和对应的控制信号状态等信息。

1.4 实验器材1.Dais-CMH+ 计算机组成原理教学实验系统1台;2.8芯扁平排线2条,双头导线若干;3.逻辑笔,万用表等。

1.5 实验原理一、内部存储器(RAM 6116)读写实验本存储器实验的电路原理如图2-1-2所示,主要由RAM(6116)、地址寄存器AR(74LS273)、数据显示、地址显示、数据输入开关及其相关的控制信号(二进制开关单元)等组成。

其中,数据输入开关可用来设置地址或数据。

控制信号为逻1辑“1”时有效(开关拨向上方),否则无效。

静态随机存储器(RAM)由一片6116芯片构成,如图2-1-1所示。

6116的容量是2KB,有A10~A0共11条地址线。

在本实验系统中,只用到A7~A0这8条地址线,高3位地址线A10~A8接地,因此,其实际容量为256B。

D7~D0是6116的数据线。

计算机组成原理实验存储器PPT学习教案

第21页/共27页

实验一 存储器实验

第22页/共27页

实验一 存储器实验

实验注意事项 1. 实验初始状态:

“运行控制”开关置为“运行”状态,“运行方式” 开关置为“单步”状态。W1和W2旋钮应旋至中间 位置。 2.T3脉冲的产生: 每按动一次“启动运行”开关,T3输出一个正单 脉冲。 3. 所有控制信号的跳线接至左边手动方式。 4. 总清开关(LCLR)应为“1”,不能为“0”,为 “0”时,地址总线上的数据永第远23页为/共2070页H。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

21、没有人陪你走一辈子,所以你要 适应孤 独,没 有人会 帮你一 辈子, 所以你 要奋斗 一生。 22、当眼泪流尽的时候,留下的应该 是坚强 。 23、要改变命运,首先改变自己。

24、勇气很有理由被当作人类德性之 首,因 为这种 德性保 证了所 有其余 的德性 。--温 斯顿. 丘吉尔 。 25、梯子的梯阶从来不是用来搁脚的 ,它只 是让人 们的脚 放上一 段时间 ,以便 让别一加并使享受加强。 ——德 谟克利 特 67、今天应做的事没有做,明天再早也 是耽误 了。——裴斯 泰洛齐 68、决定一个人的一生,以及整个命运 的,只 是一瞬 之间。 ——歌 德 69、懒人无法享受休息之乐。——拉布 克 70、浪费时间是一桩大罪过。——卢梭