绘制层次电路原理图

Altium Designer 16电路设计 第六章 绘制层次电路原理图

图6-14

6.3层次电路原理图的绘制方法

再将光标移到图纸符号内部的指定位置,按下键盘上【TAB】按键,弹出图纸入口 属性对话框,如图6-15所示

① ② ③

图6-15

6.3层次电路原理图的绘制方法

(2)设置图纸入口属性。 图纸入口属性对话框的主要属性如下: 【名称】 图纸入口的名称,必须与子电路图中端口的名称一致,下拉列表 中包含已自动识别出的名字;值得注意的是,图纸入口名称不能含有“.” 等非法符号,否则会出错,如要表示P1.0端口,命名为P10即可,如要表示 P1.0~P1.7端口,则命名为P1[0..7]即可。 【线束类型】 如果应该的子图中有多个线束,则需要手工添加或选择线束 类型,添加或选择线束类型后,后面的【I/O类型】就不需要重新定义。 【I/O类型】 端口信号输入/输出类型,即端口中信号的流向,共有四个选 项,其含义如下: 【Unspecified】不确定 【Output】输出 【Input】输入 【Bidrectional】双向 【锁定】 固定图纸入口符号的位置。

图6-18

6.3层次电路原理图的绘制方法

6.绘制子原理图 完成顶层原理图即母图的绘制后,由各图纸符号产生相对于的子原理图, 具体操作步骤如下: (1)产生子原理图文件。 单击【设计】→【产生图纸】,此时光标变成一个十字型,移动光标到 图纸符号上,单击左键,自动生成一个与图纸符号名称一致的子原理图 文件,里面有与图纸符号入口相对应的输入/输出端口。以产生显示模块 子原理图文件为例,如图6-19所示:

Altium Designer 16电路设计 第六章 绘制层次电路原理图

6.3层次电路原理图的绘制方法

(3)放置显示模块图纸入口,如图6-16所示。

图6-16 显示模块放置了3个图纸入口,说明有三个通过需要跟其他图纸符号连接,一个是+5V 电源端口,一个GND地线端口,PA[2..5]是代表PA2、PA3、PA4、PA5的总线端口。 放置图纸入口前,先规划好子电路图与子电路图之间电气连接的端口类型、名称、数 量,采用何种方式连接,在AD16中,连接方式可分为三种:导线连接、总线连接、信 号线束连接,三者之间的区别将在绘制子原理图详细讲解。

母原理图 一级子图 二级子图

图6-1

图6-2

6.1 层次电路原理图简介

二、层次电路图产生的原因: 对于结构复杂的、元器件较多的、规模庞大的电路系统,很难在一张电路 原理图上完整的绘制出来;企业或者公司在电子产品的开发与研究上,为了缩 短周期,往往是一个团队同时在工作,需要把完整复杂的电路系统分割成不同 的电路模块,分派给不同的设计组完成。因此,层次电路原理图的设计方式应 运而生。 母原理图由图表符连接而成,而一个图表符对应一个子电路图,如图6-3所 示:

① ②

③

图6-12

6.3层次电路原理图的绘制方法

(3)完成图纸符号绘制。

填写完图纸符号属 性,单击【确认】 按钮完成设置,拖 动光标带出图纸符 号轮廓,当图纸符 号尺寸大小合适时, 再次单击鼠标左键, 完成图纸符号的绘 制。 用同样的方法依次 绘制出其他模块的 图纸符号,绘制完 的效果图如图6-13 所示。

第六章 绘制层次电路原理图

Altium Designer16电路设计

教学内容

1

2 3 层次电路原理图简介 层次电路原理图的设计方法 层次电路原理图的绘制方法

4 5 6

绘制层次电路原理图讲解

《电路CAD 》课程实验报告实验名称绘制层次电路原理图实验序号实验二姓名张伟杰系专业电科班级一班学号201342203 实验日期5月5日指导教师曹艳艳组名第一组成绩一、实验目的和要求1 掌握层次原理图的绘制方法。

2 理解层次原理图模块化的设计方法。

二、实验设备计算机、Altium Designer 10三、实验过程(步骤、程序等)1 新建工程项目文件1)单击菜单File/New/PCB Project,新建工程项目文件。

2)单击菜单File/Save Project保存工程文件,并命名为“洗衣机控制电路.PrjPCB”。

2 绘制上层原理图1)“在洗衣机控制电路.PrjPCB”工程文件中,单击菜单File/New/Schematic,新建原理图文件。

2)单击菜单File/Save As..,将新建的原理图文件保存为“洗衣机控制电路.SchDoc”3) 单击菜单Place/Sheet Symbol或单击“Wring”工具栏中的按钮,如图1所示,依次放置复位晶振模块,CPU模块,显示模块,控制模块四个模块电路,并修改其属性,放置后如图2所示图1 模块电路属性图2 放置四个模块电路4)单击菜单P1ace/Add sheet Entry或单击“Wring”工具栏的按钮,放置模块电路端口,并修改其属性,完成后效果如图3所示图3 放置模块电路端口5)连线。

根据各方块电路电气连接关系,用导线将端口连接起来,如图4所示图4 连线3 创建并绘制下层原理图1)在上层原理图中,单击菜单Design/Create Sheet From Symbol,此时鼠标变为十字形。

2)将十字光标移到“复位晶振模块”电路上,单击鼠标左键,系统自动创建下层原理图“复位晶振模块.SchDoc”及相对应的I/O端口。

如图5所示。

图5 自动生成的I/0端口4)绘制“复位晶振模块”电路原理图。

其用到的元件如下表1所示。

绘制完成后的效果如图6所示。

层次电路原理图绘制

建立子图

1.放置子图图框 命令【Place】/【Sheet Symbol】或单击布线工 具栏中的 按钮

2.定义子图名称并设置属性

一种方法是双击图中 已放置的子图图框, 弹出其属性设置对话 框

需要修改的两项是: 标识符和文件名称

另一种方法是在子图图框上双击标识符或文件名称

3.添加子图入口

命令【Place】/【Add Sheet Entry】或单击布线工 具栏中的 按钮

(2)单击菜单“文件→保存”命令,将Sheet1.SchDoc更名为“线束 检测电路(顶层).

二、顶层原理图的绘制

1.图纸参数设置 单击菜单:“设计--文档选项”命令,“参数”选项卡设置如 下: Drawn By-- 作者姓名 Title--- 原理图标题栏 即 “线束检测电路(顶层)” Sheet Number--当前原理图编号数(1) Sheet Total--项目中图纸总数(5)

2020/4/28

三、 创建子图及层次关系

1.将图纸符号转换为对应的子电路原理图

(1)在“线束检测电路(顶层).SchDoc”原理图编辑界面中,单击菜 单“设计→产生图纸命令”。 (2)鼠标下带有一个浮动的十字光标,在“感应输入电路”图纸符号区 域内,单击鼠标即可生成一张带有电路端口的同名空白图纸。 (3)用相同的方法,继续在“线束检测电路(顶层).SchDoc”原理 图编辑界面中生成其他子电路原理图,如图所示

一、 层次电路图的设计准备

1.正确划分电路工程模块

2.创建“层次电路.PrjPcb”工程

2020/4/28

3.创建顶层原理图文件“线束检测电路(顶 层()1).S单c击h“DoPcro”jec,ts”对话框中“工程”按钮,在弹出的菜单中选

AltiumDesigner13标准教程第四章层次化原理图的设计

层次化原理图的设计内容指南 在前面,学习了一般电路原理图的基本设计方法,将整个系统的电路绘制在一张原理图纸上。

这种方法适用于规模较小、逻辑结构比较简单的系统电路设计。

而对于大规模的电路系统来说,由于所包含的对象数量繁多,结构关系复杂,很难在一张原理图纸上完整地绘出,即使勉强绘制出来,其错综复杂的结构也非常不利于电路的阅读分析与检测。

因此,对于大规模的复杂系统,应该采用另外一种设计方法,即电路的层次化设计。

将整体系统按照功能分解成若干个电路模块,每个电路模块能够完成一定的独立功能,具有相对的独立性,可以由不同的设计者分别绘制在不同的原理图纸上。

这样,电路结构清晰,同时也便于多人共同参与设计,可加快工作进程。

知识重点层次原理图的概念层次原理图的设计方法 层次原理图之间的切换4.1 层次原理图的设计方法层次电路原理图的设计理念是将实际的总体电路进行模块划分,划分的原则是每一个电路模块都应该有明确的功能特征和相对独立的结构,而且还要有简单、统一的接口,便于模块彼此之间的连接。

基于上述的设计理念,层次电路原理图设计的具体实现方法有两种:一种是自上而下的层次原理图设计,另一种是自下而上的层次原理图设计。

自上而下的设计思想是在绘制电路原理图之前,要求设计者对这个设计有一个整体的把握。

把整个电路设计分成多个模块,确定每个模块的设计内容,然后对每一模块进行详细地设计。

在C 语言中,这种设计方法被称为自顶向下,逐步细化。

该设计方法要求设计者在绘制原理图之前就对系统有比较深入地了解,对于电路的模块划分比较清楚。

自下而上的设计思想则是设计者先绘制原理图子图,根据原理图子图生成方块电路图,进而生成上层原理图,最后生成整个设计。

这种方法比较适用于对整个设计不是非常熟悉的用户,这也是初学者一种不错的选择方法。

4.1.1 自上而下的层次原理图设计自上而下的层次电路原理图设计就是先绘制出顶层原理图,然后将顶层原理图中的各个方块图对应的子原理图分别绘制出来。

电路原理第3章层次电路图的设计

第三章层次电路图的设计在设计原理图的过程中,设计人员经常会遇到电路元件很多,而打印机幅面有限的问题。

而采用层次电路设计方法后,这一问题就迎刃而解了。

所谓层次电路设计,就是把一个完整的电路系统按功能分为若干个子系统,即子功能电路模块,需要的话,把子功能电路模块再分成若干个子系统,即子功能电路模块,然后用方块电路的输入/输出端口将各子功能电路连接起来,于是就可以在较小的幅面的多张图纸上分别编辑、打印各模块电路的原理图。

在早期,层次原理图设计主要是为了解决复杂的大型电路系统的原理图设计问题。

但现在,设计人员为了增强原理图的可读性和利用设计人员之间的分工合作,即使所设计的电路系统并不十分复杂,也把整个电路系统按功能模块分别绘制出相应的模块电路原理图。

在Protel DXP设计系统中,层次原理图是由母原理图和子原理图构成的。

母原理图的功能是用来给出子原理图之间的层次连接关系,它是有方块电路符号、方块电路I/O端口符号代表着子原理图之间的端口连接关系;导线的作用是用来将代表子原理图的方快电路符号组成一个完整的电路系统原理图。

子原理图就是一个由各种电路元件符号组成的实实在在的原理图,它通常对应着设计电路系统中的一个子功能电路模块。

可以看出,通过这种组织式的母原理图和子原理图可以用来描述任何形式、任何大型复杂的电路系统。

3.1 绘制层次原理母图绘制Protel DXP层次电路原理图的母图步骤如下:(1)新建工程和原理图母图新建一个PCB工程,并在该工程下新建一个原理图文件作为层次原理图的母图,可以命名为Z80 Processor.SchDoc。

(2)放置方块电路图以绘制Serial Interface.SchDoc对应的方块电路图为例。

执行菜单命令Place→Symbol,或单击Wiring工具条中的按钮,即可启动放置方块电路图命令。

执行方块电路图命令后,出现一个方块电路图的虚影随鼠标移动,如图3-1所示。

图3-1 放置方块电路图此时,按[Tab]键,即可进入方块电路图属性设置,如图3-2所示。

7第5章 层次化电路的设计

一、层次原理图结构

层次式电路主要包括两大部分:主电路图和子电路图。 层次式电路主要包括两大部分:主电路图和子电路图。 其中主电路图与子电路图的关系是父电路与子电路的关 系,在子电路图中仍可包含下一级子电路。 在子电路图中仍可包含下一级子电路。 1.主电路图 . 主电路图文件的 扩展名是.prj。 扩展名是 。 主电路图相当于整机电路 图中的方框图, 图中的方框图,一个方块图 相当于一个模块。 相当于一个模块。图中的每 一个模块都对应着一个具体 的子电路图。 的子电路图。

Sheet Entry属性设置对话框中有关选项 属性设置对话框中有关选项 含义: 含义: Name:方块电路端口名称。如WR。 :方块电路端口名称。 。 Type:端口的电气类型。 I / O Type:端口的电气类型。单击图 5.8中Input旁的下拉按钮,出现端口电 旁的下拉按钮, 中 旁的下拉按钮 气类型列表。 气类型列表。 Unspecified:不指定端口的电气类 : 型。 Output:输出端口。 :输出端口。 Input:输入端口。 :输入端口。 Bidirectional:双向端口。 :双向端口。

打开一个设计数据库文件。 打开一个设计数据库文件。 执行菜单命令File|New,系统弹出New Document对话框。 对话框。 ① 执行菜单命令 ,系统弹出New Document对话框 选择Document Fold(文件夹)图标,单击Ok按钮。 Ok按钮 ② 选择Document Fold(文件夹)图标,单击Ok按钮。 将该文件夹的名字改为Z80。 ③ 将该文件夹的名字改为Z80。

第五章 层次电路图设计

层次电路图设计方法 层次化电路图设计 层次电路图之间的切换

5.1 电路的层次化设计方法

层次电路图设计方法实际上是一种模块化设 计方法。 计方法。用户可以将待设计的系统划分为多个子 系统,每个子系统下面又可以化分为若干个功能 系统, 模块, 模块,每个功能模块还可以再细化为若干个基本 模块。设计好每个基本模块, 模块。设计好每个基本模块,定义好每个基本模 块之间连接关系,就可完成整个系统的设计过程。 块之间连接关系,就可完成整个系统的设计过程。

5层次电路原理图设计

完成主原理图的绘制后,就可以由 各方块电路产生各自相应的子原理 图。下面以产生显示模块子原理图 display.SchDoc为例,介绍由方块 电路产生子原理图的方法。

由方块电路产生子原理图菜单

是否反转端口的输入/输出方向

弹出如图所示的 是否反转端口的 输入/输出方向 对话框,点击 【NO】按钮不 反转端口的输入 /输出方向。

编码 编码.SCHDOC

LOCK D1 D2 D3

LOCK D1 D2 D3

锁存 锁存.SCHDOC

LOCK D1 D2 D3

显示 显示.SCHDOC

A[1..3]

A[1..3] XL

A[1..3] XL

响铃 响铃.SCHDOC

XL

数码抢答器方块电路图 分析

整体原理图主要由编码、锁存、显示、响铃四 个模块组成,其编码部分主要将抢答开关K1~ K8编码为D3~D1,以及形成锁存脉冲LOCK。 而锁存电路主要将D3~D1锁存下来后送往显 示和响铃模块,因此编码和锁存模块之间主要 有四个连接端口,编码信号D3~D1以及锁存 信号LOCK。而锁存和显示模块之间由于采用 总线连接,所以只有一个复合连接端口A[1..3], 锁存和响铃模块之间通过响铃触发信号XL连接, 所以数码抢答器各模块的划分以及各方块电路 之间的连接关系如上图所示。

3. 操作步骤和提示

(1)新建工程文件,并保存为“抢 答器层次电路.PRJPCB”

(2)新建原理图文件,并保存为 “抢答器主原理图.SchDoc”。

(3)绘制方块电路并连线。

产生并绘制编码模块电路图“编码.SCHDOC

1

2

3 U3

4

8

5

6 11

74LS30

12

实验三 protel DXP中绘制层次电路原理图

实验三绘制层次电路原理图一、实验目的1.熟练掌握ProtelDXP的操作。

2.掌握层次电路原理图的绘制方法,能够绘制较复杂的层次电路。

3.进一步熟悉ERC校验和网络表的生成。

二、实验内容1.新建电路原理图,图纸大小设置为A4,参照图5所示,完成层次电路原理图主图的绘制。

图中,VSIN选用仿真库(Simulation Sources.IntLib)中的VSIN元件;各子图符号I/O端口中,子图Modulator中的端口Vcarrier和Vsingal为输入,Vmod为输出,子图Amplifier中的端口Vmod为输入,OUT为输出。

将电路原理图以文件名“AMPMOD.prj’’存盘。

图5 主图“AMPMOD.prj”执行菜单Design—Document Options—Parameters填写图样信息,在Sheet Number栏中设置图纸编号(NO)为1;在Sheet Total栏中设置图纸总数(Total)为3。

2.执行菜单命令Design—Create Sheet From Symbol,将光标移到子图符号Modulator 上,单击鼠标左键,在产生的新电路原理图上按照图6绘制第一张子图,设置图样编号为2,并保存该电路。

3·采用同样的方法,分别参照图7绘制第二张子图,设置图样编号为3。

图6 子图modulator.sch 图7 子图amplifier.sch4.对整个层次电路原理图进行ERC校验(执行菜单:Project—Compile PCB Project1.PrjPCB),若有错误,加以修改。

5.生成此层次电路的网络表,检查网络表各项内容,是否与原理图相符合。

三、思考题1.简述设计层次电路原理图的步骤。

2.设计层次电路原理图时应注意哪些问题?3.画出下图的洗衣机控制电路的层次电路图顶层图CPU电路晶震、复位电路控制电路1K显示电路。

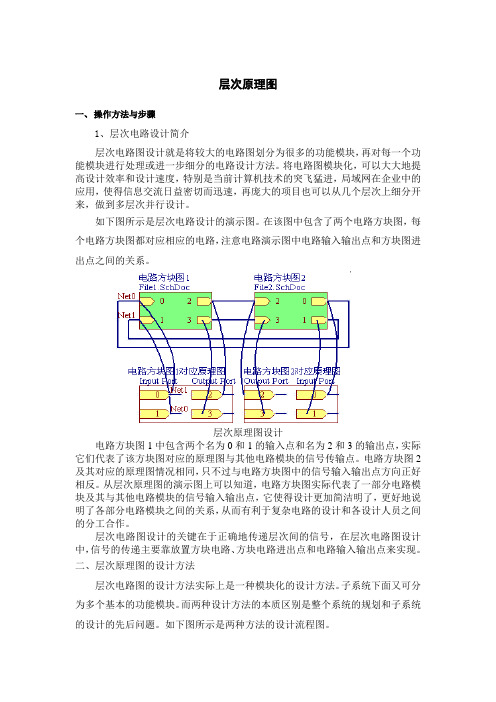

层次原理图

层次原理图一、操作方法与步骤1、层次电路设计简介层次电路图设计就是将较大的电路图划分为很多的功能模块,再对每一个功能模块进行处理或进一步细分的电路设计方法。

将电路图模块化,可以大大地提高设计效率和设计速度,特别是当前计算机技术的突飞猛进,局域网在企业中的应用,使得信息交流日益密切而迅速,再庞大的项目也可以从几个层次上细分开来,做到多层次并行设计。

如下图所示是层次电路设计的演示图。

在该图中包含了两个电路方块图,每个电路方块图都对应相应的电路,注意电路演示图中电路输入输出点和方块图进出点之间的关系。

层次原理图设计电路方块图1中包含两个名为0和1的输入点和名为2和3的输出点,实际它们代表了该方块图对应的原理图与其他电路模块的信号传输点。

电路方块图2及其对应的原理图情况相同,只不过与电路方块图中的信号输入输出点方向正好相反。

从层次原理图的演示图上可以知道,电路方块图实际代表了一部分电路模块及其与其他电路模块的信号输入输出点,它使得设计更加简洁明了,更好地说明了各部分电路模块之间的关系,从而有利于复杂电路的设计和各设计人员之间的分工合作。

层次电路图设计的关键在于正确地传递层次间的信号,在层次电路图设计中,信号的传递主要靠放置方块电路、方块电路进出点和电路输入输出点来实现。

二、层次原理图的设计方法层次电路图的设计方法实际上是一种模块化的设计方法。

子系统下面又可分为多个基本的功能模块。

而两种设计方法的本质区别是整个系统的规划和子系统的设计的先后问题。

如下图所示是两种方法的设计流程图。

自上而下设计流程图自下而上设计流程图三、 放置方块电路(重点)1、方块电路(Sheet Symbol )是层次式电路设计不可缺少的组件。

简单地说,方块电路就是设计者通过组合其他元器件自己定义的一个复杂器件,这个复杂器件在图纸上用简单的方块图来表示,至于这个复杂器件由哪些其他元件组成,内部的接线又如何,可以由另外一张电路图来详细描述。

绘制复杂的多层次电路原理图

步骤3:将图纸下方端口移到对应处;

步骤4:保存图纸,完成第一位全加器电路图

FullAdd1.sch 。

任务六

绘制复杂的多层次电路原理图

3、绘制第二位全加器FullAdd2.sch(即第二层图) 由于结构与第一位全加器相同,采用复制、粘贴方 法进行绘制。 步骤1:回到方块电路图(根图)产生第二位全加器 电路图的空白图纸; 步骤2:在FullAdd1.sch中复制选定电路; 步骤3:在空白的FullAdd2.sch中粘贴电路; 步骤4:修改相应内容; 步骤5:将图纸FullAdd2.sch下方端口移到相应位置;

以“Z80 Processor.prj”为例,图中的六个方块图对应下 层的六个原理图。下层的六个原理图见后。

任务六

绘制复杂的多层次电路原理图

PROTEL99SE 电 子 线 路 设 计

任务六

绘制复杂的多层次电路原理图

PROTEL99SE 电 子 线 路 设 计

任务六

绘制复杂的多层次电路原理图

PROTEL99SE 电 子 线 路 设 计

PROTEL99SE 电 子 线 路 设 计

2、P97 实训题1、2

任务六

绘制复杂的多层次电路原理图

PROTEL99SE 电 子 线 路 设 计

任务六

绘制复杂的多层次电路原理图

PROTEL99SE 电 子 线 路 设 计

任务六

绘制复杂的多层次电路原理图

PROTEL99SE 电 子 线 路 设 计

任务六

绘制复杂的多层次电路原理图

电 子 线 路 设 计

PROTEL99SE 电 子 线 路 设 计

步骤6:保存。

任务六

EDA层次原理图的设计方法

My51 GNDUnsFra bibliotekecified

51T1 Output

51R1 Input

VCC

Unspecified

GND

Unspecified

Outpu t

⑤执行菜单命令Design/Create Sheet from Symbol.系统会自动创建一个底 层原理图,并且自动命名为51_232_232.SchDoc. (6)绘制原理图;

(1)检查规则的设置 执行菜单命令Project/Project Options,在Error Reporting中进行设置

(2) 检查结果报告 左键单击System,选择Messages 查看 例:以项目555 Astable Multivibrator.PrjPcb为例进行电气检查。

被检查的原理图文档

②将电路原理图所产生的网络表文件与印刷电路板得到的网络表进行比较, 以检查原理图与印刷电路板之间是否一致。 网络表中的内容主要为原理图中各元件的数据(标号、元件类型和包装 信息)以及元件之间网络连接的数据。 网络表在结构上分为两大部分:第一部分为元件描述;第二部分为网 络连接描述

(1)创建网络表 网络表可以由单个原理图文档生成,也可以由项目生成。 由单个原理图文档生成 执行菜单命令Design/Netlist for Document/Protel 由项目生成 执行菜单命令Design/Netlist for Project/Protel (2)网络表的格式 ①元件描述部分

注意:此实例仅仅只是为帮助理解层次原理图的建立,并未考虑电气特性

3. 切换不同层次电路原理图文件 (1)从顶层图切换到子原理图 在顶层图中执行菜单命令Tools/Up/Down Hierachy

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

《电路CAD 》课程实验报告

按钮,如图

图2 放置四个模块电路

)单击菜单P1ace/Add sheet Entry或单击“Wring”工具栏的按钮,放置模块电路端口,并修改其属性,完成后效果如图3所示

图3 放置模块电路端口

图4 连线

创建并绘制下层原理图

在上层原理图中,单击菜单Design/Create Sheet From Symbol,此时鼠标变为十字形。

将十字光标移到“复位晶振模块”电路上,单击鼠标左键,系统自动创建下层原理图“复.SchDoc”及相对应的I/O端口。

如图5所示。

自动生成的I/0

晶振模块”电路原理图。

所示。

绘制完成后的效果如图

晶振模块”电路元件列表

所在元件库

图7 DS80C310-MCL元件搜索图8 CPU电路模块

表3 显示模块电路元件列表

元件标号元件名所在元件库元件值元件封装

Miscellaneous Devices.IntLib LEDDIP-10

R3 RES2 Miscellaneous Devices.IntLib 1k AXIAL0.4 R4 RES2 Miscellaneous Devices.IntLib 1k AXIAL0.4 R5 RES2 Miscellaneous Devices.IntLib 1k AXIAL0.4 R6 RES2 Miscellaneous Devices.IntLib 1k AXIAL0.4 R7 RES2 Miscellaneous Devices.IntLib 1k AXIAL0.4 R8 RES2 Miscellaneous Devices.IntLib 1k AXIAL0.4 R9 RES2 Miscellaneous Devices.IntLib 1k AXIAL0.4 R10 RES2 Miscellaneous Devices.IntLib 1k AXIAL0.4 VCC 电源工具栏

图10 控制电路模块。