七段数码管显示十进制数字 (10)

2022金华市《电子技术基础》模拟卷3

2022金华市《电子技术根底》模拟卷22022金华市中职会考《电子技术根底》模拟卷武义职校班级______姓名______学号______?填空题〔每空1分,共30分〕1.晶体二极管具有___ _______,硅二极管的死区电压约为______V。

2.在选择整流二极管时我们主要考虑参数是:最大整流电流和_____________。

3.按内部结构的不同,三极管可分为型和型。

三极管的三个电极名称分别是、集电极和发射极。

4.三极管电流放大的实质____ ____的微小变化控制较大的__ ____电流变化。

5.放大器无信号输入时的直流工作状态叫_________,要使放大器不失真地将电信号放大,须建立适宜的______ ______。

6.多级放大器有三种耦合方式,即阻容耦合,__ __耦合和_ _耦合。

7.放大器的_____________的全部或局部通过某种方式回送到输入端,这局部信号叫反应信号。

根据反应的极性来分,可分为_______反应和反应。

8.按照逻辑功能和电路组成的不同,数字电路可以分成_________电路和_______电路两大类。

9.根本的逻辑门电路有________、________、________三种。

10.A·0=_______ A+ā=________ A+AB= 11.8421BCD码为0101它代表的十进制数__________。

12.组合逻辑电路的特点是任何时刻的输出状态,直接由当时的所决定,也就是说,组合逻辑电路不具有功能。

?三极管作为开关使用时,它是工作在、两种状态下。

14.D触发器具有置0、置1、保持和功能。

15.一个七段数码管显示器,输入为高电平时数码管发光,那么当abcdefg=1101101时,显示的十进制数为。

二、是非题〔每题1分,共10分〕? 单级共射放大器接上负载后,电压放大倍数将增大。

-----------------------( ) ? 稳压管、整流管都工作在正向导通状态。

共阳极七段数码管真值表

共阳极七段数码管真值表共阳极七段数码管是一种常见的电子显示器件,它由七个段码组成,可以显示0-9的数字以及一些其他字符。

下面是共阳极七段数码管的真值表,包含七个段码a、b、c、d、e、f、g。

1. 段码a:* 数字0:0x3F(二进制:00111111)* 数字1:0x06(二进制:00000110)* 数字2:0x5B(二进制:01011011)* 数字3:0x4F(二进制:01001111)* 数字4:0x66(二进制:01100110)* 数字5:0x6D(二进制:01101101)* 数字6:0x7D(二进制:01111101)* 数字7:0x07(二进制:00000111)* 灭零:0x7C(二进制:01111100)2. 段码b:* 数字0:0x39(二进制:00111001)* 数字1:0x5F(二进制:01011111)* 数字2:0x49(二进制:01001001)* 数字3:0x65(二进制:01100101)* 数字4:0x77(二进制:01110111)* 数字5:0x79(二进制:01111111)* 数字6:0x3D(二进制:00111101)* 数字7:没有对应的编码。

可以通过特定的编程实现显示。

3. 段码c:* 数字0:没有对应的编码。

可以通过特定的编程实现显示。

* 数字8以下与段码b相同。

4. 段码d、e、f、g与b相同。

请注意,这里提供的编码是基于常见的共阳极七段数码管编码,不同型号或品牌的数码管可能会有不同的编码。

此外,对于大于9的数字或特殊字符,可能需要通过特定的编程来实现显示。

七段数码管设计电路

EDA基础及应用实验项目报告项目题目:七段数码管显示电路设计姓名:胡小琴院系:电子信息工程学院专业:电子信息工程(对口高职)学号: 201315294127指导教师:徐正坤综合成绩:完成时间: 2015年5月22日一、项目实验内容摘要1、设计一个共阴7段数码管控制接口,要求:在时钟信号的控制下,使8位数码管动态刷新显示0—9。

2、设计一个基本功能十进制计数器,实现十进制计数器输出的动态显示。

二、项目实验源代码程序1LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_UNSIGNED.ALL;ENTITY countbasic ISPORT(CLK:IN STD_LOGIC;DOUT:OUT STD_LOGIC_VECTOR(3 DOWNTO 0);COUT:OUT STD_LOGIC);END countbasic ;ARCHITECTURE behav OF countbasic ISBEGINPROCESS(CLK)V ARIABLE Q:STD_LOGIC_VECTOR(3 DOWNTO 0);BEGINIF CLK'EVENT AND CLK='1' THENIF Q<9 THEN Q:=Q+1;ELSE Q:=(OTHERS=>'0');END IF;END IF;IF Q="1001" THEN COUT<='1';ELSE COUT<='0';END IF;DOUT<=Q;END PROCESS;END behav;程序2 ENTITY countbasic_vhd_tst ISEND countbasic_vhd_tst;ARCHITECTURE countbasic_arch OF countbasic_vhd_tst IS -- constants-- signalsSIGNAL CLK : STD_LOGIC;SIGNAL COUT : STD_LOGIC;SIGNAL DOUT : STD_LOGIC_VECTOR(3 DOWNTO 0); constant clk_cycle : time := 100 ns;COMPONENT countbasicPORT (CLK : IN STD_LOGIC;COUT : OUT STD_LOGIC;DOUT : OUT STD_LOGIC_VECTOR(3 DOWNTO 0));END COMPONENT;BEGINi1 : countbasicPORT MAP (-- list connections between master ports and signalsCLK => CLK,COUT => COUT,DOUT => DOUT);processbeginclk <= '1';wait for clk_cycle;clk <= '0';wait for clk_cycle;end process;END countbasic_arch;程序3LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_ARITH.ALL;USE IEEE.STD_LOGIC_UNSIGNED.ALL;ENTITY Seg7_Dsp isPORT(CP : IN STD_LOGIC; -- CLOCKSEGOUT : OUT STD_LOGIC_VECTOR(7 DOWNTO 0); -- SEG7 Display O/PSELOUT : OUT STD_LOGIC_VECTOR(7 DOWNTO 0); -- Select SEG7 O/PNUMOUT : OUT STD_LOGIC_VECTOR(3 DOWNTO 0); -- Number Display Signal OUTNUM : IN STD_LOGIC_VECTOR( 3 DOWNTO 0); -- Number Display Signal INM : OUT STD_LOGIC_VECTOR(3 DOWNTO 0));END Seg7_Dsp;ARCHITECTURE a OF Seg7_Dsp ISSIGNAL SEG : STD_LOGIC_VECTOR( 7 DOWNTO 0); -- SEG7 Display Signal SIGNAL SEL : STD_LOGIC_VECTOR( 7 DOWNTO 0); -- Select SEG7 Signal BEGINConnection : BlockBeginM <= "0010";SELOUT <= SEL; -- Seg7 Disp Selection SEGOUT(7 DOWNTO 0) <= SEG; -- Seven Segment Display NUMOUT <= NUM;End Block Connection;Free_Counter : Block -- 计数器-- 产生扫描信号Signal Q : STD_LOGIC_VECTOR(24 DOWNTO 0);Signal S : STD_LOGIC_VECTOR(2 DOWNTO 0);BeginPROCESS (CP) -- 计数器计数BeginIF CP'Event AND CP='1' thenQ <= Q+1;END IF;END PROCESS;S <= Q(15 DOWNTO 13); --about 300 Hz--扫描信号SEL <= "11111110" WHEN S=0 ELSE"11111101" WHEN S=1 ELSE"11111011" WHEN S=2 ELSE"11110111" WHEN S=3 ELSE"11101111" WHEN S=4 ELSE"11011111" WHEN S=5 ELSE"10111111" WHEN S=6 ELSE"01111111" WHEN S=7 ELSE"11111111";End Block Free_Counter;SEVEN_SEGMENT : Block -- Binary Code -> Segment 7 CodeBegin--SEG <= "00111111"WHEN NUM = 0 ELSE"00000110"WHEN NUM = 1 ELSE"01011011"WHEN NUM = 2 ELSE"01001111"WHEN NUM = 3 ELSE"01100110"WHEN NUM = 4 ELSE"01101101"WHEN NUM = 5 ELSE"01111101"WHEN NUM = 6 ELSE"00000111"WHEN NUM = 7 ELSE"01111111"WHEN NUM = 8 ELSE"01101111"WHEN NUM = 9 ELSE"01110111"WHEN NUM = 10 ELSE"01111100"WHEN NUM = 11 ELSE"00111001"WHEN NUM = 12 ELSE"01011110"WHEN NUM = 13 ELSE"01111001"WHEN NUM = 14 ELSE"01110001"WHEN NUM = 15 ELSE"00000000";End Block SEVEN_SEGMENT;END a;三、项目实验工具软件项目试验工具:EL-SOPC400试验箱、主芯片:EP4CE22F17C8、计算机与QUARTUS Ⅱ软件四、实验步骤1、建立项目文件以及VHDL文件同前几个实验一样2、将前两个程序按照一点的步骤设置然后进行仿真3、将三个实验添加到项目中来并设置为顶层文件4、建立顶层图,选择“File→New→Block Diorgram Schematic File”按OK 就可以建立一个顶层图,我们在把他进行保存,名字为默认的文件名,并将“Add file to current project”选项选中,让他加入到工程中去。

一个8421码十进制计数器(异步置数)及七段数码管显示系统

一个8421码十进制计数器(异步置数)及七段数码管显示系统一个8421码十进制计数器(异步置数)及七段数码管显示系统LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_UNSIGNED.ALL;ENTITY counter10 ISPORT( clk: IN STD_LOGIC;load: IN STD_LOGIC;din: IN STD_LOGIC_VECTOR(3 DOWNTO 0);qout: OUT STD_LOGIC_VECTOR(3 DOWNTO 0);c: OUT STD_LOGIC);END counter10;ARCHITECTURE art2 OF counter10 ISSIGNAL temp: STD_LOGIC_VECTOR(3 DOWNTO 0);BEGINPROCESS(clk,load,din)BEGINIF(load='0') THENtemp<=din;ELSIF(clk'EVENT AND clk='1') THENIF(temp="1001") THENtemp<="0000";ELSEtemp<=temp+1;END IF;END IF;END PROCESS;qout<=temp;c<='1' WHEN temp="1001" ELSE'0';END art2;LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;ENTITY bcd ISPORT(A:IN STD_LOGIC_VECTOR(3 DOWNTO 0); Y:OUT STD_LOGIC_VECTOR(6 DOWNTO 0) );END bcd;ARCHITECTURE art1 OF bcd ISBEGINY<="1111110" WHEN A="0000" ELSE "0110000" WHEN A="0001" ELSE "1101101" WHEN A="0010" ELSE "1111001" WHEN A="0011" ELSE "0110011" WHEN A="0100" ELSE "1011011" WHEN A="0101" ELSE "0011111" WHEN A="0110" ELSE "1110000" WHEN A="0111" ELSE "1111111" WHEN A="1000" ELSE "1110011" WHEN A="1001" ELSE "0000000";END art1;LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_UNSIGNED.ALL;ENTITY counter10_bcd ISPORT(clkin,clrin: IN STD_LOGIC;yout: OUT STD_LOGIC_VECTOR(6 DOWNTO 0);d: IN STD_LOGIC_VECTOR(3 DOWNTO 0));END counter10_bcd;ARCHITECTURE art3 OF counter10_bcd IS COMPONENT counter10PORT( clk: IN STD_LOGIC;load: IN STD_LOGIC;din: IN STD_LOGIC_VECTOR(3 DOWNTO 0);qout: OUT STD_LOGIC_VECTOR(3 DOWNTO 0);c: OUT STD_LOGIC);END COMPONENT;COMPONENT bcdPORT(A:IN STD_LOGIC_VECTOR(3 DOWNTO 0);Y:OUT STD_LOGIC_VECTOR(6 DOWNTO 0));END COMPONENT;SIGNAL q: STD_LOGIC_VECTOR(3 DOWNTO 0);SIGNAL c1: STD_LOGIC;BEGINu1:counter10 PORTMAP(clk=>clkin,load=>clrin,din=>d,qout=>q,c=>c1);u2:bcd PORT MAP(A=>q,Y=>yout);END art3;。

数字电子技术课程设计题目

数电课设说明1.单人单题,每个题目在同一班不能超过5人选择!为了避免重复过多,请填写两个心仪的题目。

2.如果这些题目都进不了尊驾法眼,请自行设计题目名称、题目要求并提交给老师,审核通过后也可以正式进场施工。

3.建议先用Multisim或Proteus仿真测试再制作。

1.智力竞赛抢答装置的设计(1)基本功能①4名选手编号为:1,2,3,4。

各有一个抢答按钮,按钮的编号与选手的编号对应;②给主持人设置一个控制按钮,用来控制系统清零(抢答显示数码管灭灯)和抢答的开始;③抢答器具有数据锁存和显示的功能。

抢答开始后,若有选手按动抢答按钮,该选手编号立即锁存,并在抢答显示器上显示该编号,同时给出音响提示,封锁输入编码电路,禁止其他选手抢答。

抢答选手的编号一直保持到主持人将系统清零为止;④抢答器具有定时(9秒)抢答的功能。

当主持人按下开始按钮后,定时器开始倒计时,定时显示器显示倒计时间,若无人抢答,倒计时结束时,扬声器响,音响持续0.5秒。

参赛选手在设定时间(9秒)内抢答有效,抢答成功,扬声器响,音响持续0.5秒,同时定时器停止倒计时,抢答显示器上显示选手的编号,定时显示器上显示剩余抢答时间,并保持到主持人将系统清零为止;⑤如果抢答定时已到,却没有选手抢答时,本次抢答无效。

系统扬声器报警(音响持续0.5秒),并封锁输入编码电路,禁止选手超时后抢答,时间显示器显示0。

(2)设计成果要求①利用集成芯片、分立元件制作线路板,实现有关电路功能;②设计报告一份。

(3)主要器件74LS175、74LS20、74LS00、CC40192、CC4511、CC40106、555、数码管、蜂鸣器2.多功能数字钟的设计(1)基本功能①用七段LED数码管以十进制显示“时”、“分”、“秒”;②计时计数器用24进制计时电路;③可手动校时,能分别进行时、分的校正;④整点报时。

(2)设计成果要求①利用集成芯片、分立元件制作线路板,实现有关电路功能;②设计报告一份。

七段数码管动态显示控制

实验二七段数码管动态显示控制一、实验目的利用AT89S52和使用两位数码管显示器,循环显示两位数00-99。

其中P2.0和P2.1端口分别控制数码管的个位和十位的供电,当相应的端口变成低电平时,驱动相应的三极管会导通,+5V通过驱动三极管给数码管相应的位供电,这时只要P3口送出数字的显示代码,数码管就能正常显示数字。

二、实验要求1、使用两位数码管显示器,循环显示两位数00-99;2、具有电源开关和指示灯,有复位键;3、数码管动态显示,即扫描方式,每一位每间隔一段时间扫描一次。

字符的亮度及清晰度与每位点亮的停留时间和每位显示的时间内轮换导通次数有关。

三、实验电路四、实验器材AT89S52;动态扫描显示;共阳极数码管;电阻五、实验原理说明图1 AT89S52引脚图图2 共阳极七段数码管引脚图1AT89S52引脚图,说明如下:按照功能,AT89S52的引脚可分为主电源、外接晶体振荡或振荡器、多功能I/O 口、控制和复位等。

1.多功能I/O口AT89S52共有四个8位的并行I/O口:P0、P1、P2、P3端口,对应的引脚分别是P0.0 ~ P0.7,P1.0 ~ P1.7,P2.0 ~ P2.7,P3.0 ~ P3.7,共32根I/O线。

每根线可以单独用作输入或输出。

①P0端口,该口是一个8位漏极开路的双向I/O口。

在作为输出口时,每根引脚可以带动8个TTL输入负载。

当把“1”写入P0时,则它的引脚可用作高阻抗输入。

当对外部程序或数据存储器进行存取时,P0可用作多路复用的低字节地址/数据总线,在该模式,P0口拥有内部上拉电阻。

在对Flash存储器进行编程时,P0用于接收代码字节;在校验时,则输出代码字节;此时需要外加上拉电阻。

②P1端口,该口是带有内部上拉电阻的8位双向I/O端口,P1口的输出缓冲器可驱动(吸收或输出电流方式)4个TTL输入。

对端口写“1”时,通过内部的上拉电阻把端口拉到高电位,此时可用作输入口。

七段数码管显示十进制数字 (2)

Led灯显示实验

1.实验目的:

通过相关的逻辑电路在proteus上实现单片的led灯的显示;

2.实验内容:

选取相关工具,在仿真环境下配置电路图如图一。

当按上面那个开关时,led灯显示0。

按下面那一排开关的时候从右至左依次是1,2,3,4,5,6,7,8,9。

当然不按的时候灯是灭的。

如图一所示,当不按的时候,1,2,3,4,5,6,7,8,9开关可以看成接高电平,与一相连的那个非与门的另一端接地,所以是0。

通过9个非与门后B1端输入0,所以灭零。

0开关也没按所以也是0.当按0时,B1端有高电平,配合九个输入显示0.当按1开关时,一号非与门两个输入端为0,自然输出1给B1,所以这个时候U1工作。

根据九个输入显示相应的1.余下的2至9开关原理一样。

3.实验过程:

图一

各数字显示如下:

1

2

3,4,5,6,7,8,9由于原理一样所以图略。

4.实验总结:

本次实验没有采用教员上课所讲授的那种方法,这是我在选工具的过程中意外发现的一个非与门工具,然后联想到了led灯显示,所以想做得不一样,就用了此种方法。

这次实验的难

点还是0的显示。

实验2:8255七段数码管静动态显示

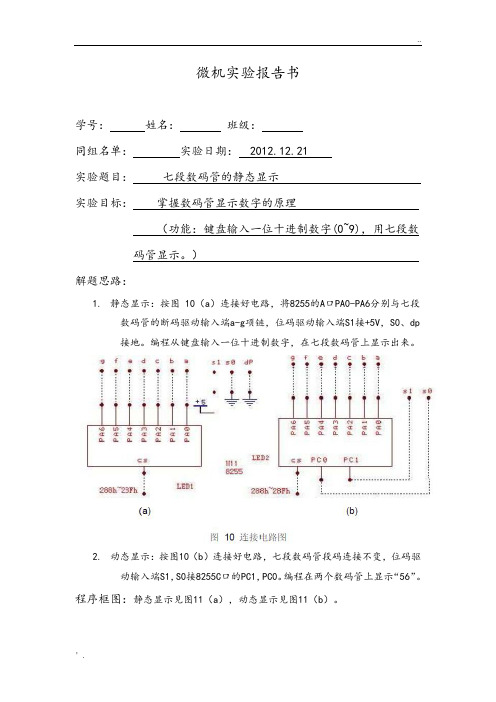

微机实验报告书学号:姓名:班级:同组名单:实验日期: 2012.12.21实验题目:七段数码管的静态显示实验目标:掌握数码管显示数字的原理(功能:键盘输入一位十进制数字(0~9),用七段数码管显示。

)解题思路:1.静态显示:按图 10(a)连接好电路,将8255的A口PA0-PA6分别与七段数码管的断码驱动输入端a-g项链,位码驱动输入端S1接+5V,S0、dp接地。

编程从键盘输入一位十进制数字,在七段数码管上显示出来。

2.动态显示:按图10(b)连接好电路,七段数码管段码连接不变,位码驱动输入端S1,S0接8255C口的PC1,PC0。

编程在两个数码管上显示“56”。

程序框图:静态显示见图11(a),动态显示见图11(b)。

关键问题分析(静态显示):1、按键判断和程序结束判断按键来说,由于程序中必须输入数字,所以没有必要对是否按键进行判断,只需要判断按键是否在0-9之间即可。

用以下程序即可:cmp al,'0'jl exit ; jl,条件转移指令,即在小于时转移cmp al,'9'jg exit ;jg, 条件转移指令,即在大于时转移程序中还要用到“cmp”即比较指令,用来比较输入数与0、9的大小关系。

程序结束:如若输入的数字小于0或者大于9,必须直接跳出程序,即结束指令必须单独占用一个程序段,这样,程序顺序执行完毕也可以顺利返回DOS。

2、七段码显示。

实验指导书中给出了七段码的字型代码。

这样一来,七段码的显示只需要用换码指令“XLAT”便可以轻松实现。

前提是必须将七段码字型编成数码表以字符串的形式写进程序中。

3、数字键ASCII码与数值间的转换。

因为0的ASCII码为30H,所以数字键ASCII码与数值间的转换时只需减去30H即可,可用下列语句实现:sub al,30h程序清单:静态显示:data segmentioport equ 0c800h-0280hio8255a equ ioport+288hio8255b equ ioport+28bhled db 3fh,06h,5bh,4fh,66h,6dh,7dh,07h,7fh,6fhmesg1 db 0dh,0ah,'Input a num (0--9h):',0dh,0ah,'$'data endscode segmentassume cs:code,ds:datastart: mov ax,datamov ds,axmov dx,io8255b ;使8255的A口为输出方式mov al,80h ;10000000B,控制字PA以方式0输出out dx,alzby: mov dx,offset mesg1 ;显示提示信息mov ah,09hint 21hmov ah,01 ;从键盘接收字符int 21hcmp al,'0' ;是否小于0jl exit ;如若小于0,则跳转到exit退出程序cmp al,'9' ;是否大于9jg exit ; 如若大于9,则跳转到exit退出程序sub al,30h ;将所得字符的ASCII码减30H,数字键ascii码同数值转换mov bx,offset led ;bx为数码表的起始地址xlat ;求出相应的段码mov dx,io8255a ;从8255的A口输出out dx,aljmp zby ;转zbyexit: mov ah,4ch ;返回DOSint 21hcode endsend start动态显示:data segmentioport equ 0c800h-0280hio8255a equ ioport+28ahio8255b equ ioport+28bhio8255c equ ioport+288hled db 3fh,06h,5bh,4fh,66h,6dh,7dh,07h,7fh,6fh ;段码buffer1 db 5,6 ;存放要显示的个位和十位bz dw ? ;位码data endscode segmentassume cs:code,ds:datastart: mov ax,datamov ds,axmov dx,io8255b ;将8255设为A口输出mov al,80h ;10000000B,控制字PA以方式0输出out dx,almov di,offset buffer1 ;设di为显示缓冲区loop2: mov bh,02zby: mov byte ptr bz,bhpush didec diadd di, bzmov bl,[di] ;bl为要显示的数pop dimov al,0mov dx,io8255aout dx,almov bh,0mov si,offset led ;置led数码表偏移地址为SIadd si,bx ;求出对应的led数码mov al,byte ptr [si]mov dx,io8255c ;自8255A的口输出out dx,almov al,byte ptr bz ;使相应的数码管亮mov dx,io8255aout dx,almov cx,3000delay: loop delay ;延时mov bh,byte ptr bzshr bh,1jnz zbymov dx,0ffhmov ah,06int 21hje loop2 ;有键按下则退出mov dx,io8255amov al,0 ;关掉数码管显示out dx,almov ah,4ch ;返回int 21hcode endsend start运行结果:静态显示:在键盘上输入一个0-9的任意数字,会显示在数码管上。

译码器的应用(七段码)

译码器的应⽤(七段码)效果展⽰:这是74HC138芯⽚,有三个输⼊脚,8个输出脚,共有8种⾼低电平输⼊组合,每⼀种组合对应⼀种7⾼1低电平组合态,假设⾼电平数码管亮,低电平数码管灭,那么通过控制⾼低电平的输⼊就可以随意控制七段数码管的亮灭情况,通过多个芯⽚的组合封装就可以拼接成0~9这10个数字,这就是译码器的七段码应⽤原理。

⼀个简单的数字底层是通过复杂的⼆进制组合实现的。

三种基本译码器在译码器基础中,解释了完全译码器(n-2n)的基本⼯作原理,即:当使能端有效时:Y i = m i或者/Y i = !m i (注:这⾥的!表⽰⾮号)除了完全译码器之外,还有4-10线译码器,七段显⽰译码器,相对也⽐较简单,这⾥简单进⾏介绍:- 4-10译码器由真值表可以看出,当A3A2A1A0的取值为[0000~1001]时,输出有效,其它情况均为⽆效,其对应的逻辑器件图如下图所⽰:七段显⽰译码器七段显⽰译码器⼀般⽤于液晶或LED显⽰屏,显⽰0~9数字(⼗进制)或0~F数字(⼗六进制)。

所谓七段,表⽰的是0~9或0~F这些数字可⽤七根数码管显⽰,对应的图为:对应的真值表如下图所⽰:译码器的应⽤译码器主要⽤于地址译码、指令译码以及逻辑表达式表⽰。

下⾯重点解释如何内存寻址以及如何表达逻辑表达式。

内存寻址在⼀⽂中,说明了可执⾏程序的执⾏流程,其中的程序计数器(Program Counter,简称PC)中保存了CPU将要执⾏的指令,那如何在内存中定位到那条指令所在的内存地址呢?(重点理解:这是硬件实现,我们要⽤组合电路寻址)。

下图描述了早期8086的内存寻址⽅式。

(计算机中⽤三类总线:数据总线、地址总线、控制总线进⾏数据传输,数据总线⽤于传输数据,地址总线⽤于传输地址,控制总线⽤于传输控制信号。

三类总线⽤于在IO、内存、CPU以及外设之间进⾏数据传输;每⼀块内存中有rd、wr、adder、cs和data⼏个输⼊输出,其中的rd表⽰读内存,wr表⽰写内存,adder下⽂中解释,cs(chip select)表⽰⽚选,data⽤于内存和总线之间数据的传输)在8086机器中,内存只有4KB(受限于当时的⽣产⼯艺,4KB内存由4块1KB的内存块组成),⽤12位⼆进制串表⽰地址。

七段数码管显示实验

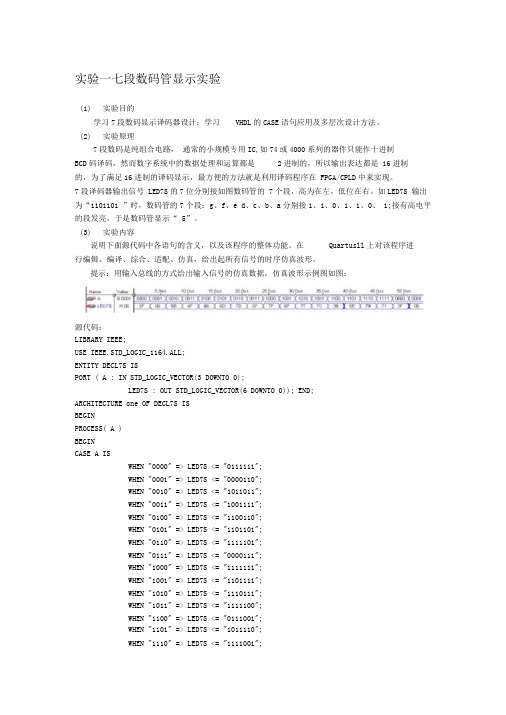

实验一七段数码管显示实验(1)实验目的学习7段数码显示译码器设计;学习VHDL的CASE语句应用及多层次设计方法。

(2)实验原理7段数码是纯组合电路,通常的小规模专用IC,如74或4000系列的器件只能作十进制BCD码译码,然而数字系统中的数据处理和运算都是2进制的,所以输出表达都是 16进制的,为了满足16进制的译码显示,最方便的方法就是利用译码程序在 FPGA/CPLD中来实现。

7段译码器输出信号 LED7S的7位分别接如图数码管的 7个段,高为在左,低位在右。

如LED7S 输出为“1101101 ”时,数码管的7个段:g、f、e d、c、b、a分别接1、1、0、1、1、0、 1;接有高电平的段发亮,于是数码管显示“ 5”。

(3)实验内容说明下面源代码中各语句的含义,以及该程序的整体功能。

在Quartusll上对该程序进行编辑、编译、综合、适配、仿真,给出起所有信号的时序仿真波形。

提示:用输入总线的方式给出输入信号的仿真数据,仿真波形示例图如图:源代码:LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;ENTITY DECL7S ISPORT ( A : IN STD_LOGIC_VECTOR(3 DOWNTO 0);LED7S : OUT STD_LOGIC_VECTOR(6 DOWNTO 0)); END;ARCHITECTURE one OF DECL7S ISBEGINPROCESS( A )BEGINCASE A ISWHEN "0000" => LED7S <= "0111111";WHEN "0001" => LED7S <= "0000110";WHEN "0010" => LED7S <= "1011011";WHEN "0011" => LED7S <= "1001111";WHEN "0100" => LED7S <= "1100110";WHEN "0101" => LED7S <= "1101101";WHEN "0110" => LED7S <= "1111101";WHEN "0111" => LED7S <= "0000111";WHEN "1000" => LED7S <= "1111111";WHEN "1001" => LED7S <= "1101111";WHEN "1010" => LED7S <= "1110111";WHEN "1011" => LED7S <= "1111100";WHEN "1100" => LED7S <= "0111001";WHEN "1101" => LED7S <= "1011110";WHEN "1110" => LED7S <= "1111001";WHEN "1111" => LED7S <= "1110001";END CASE;END PROCESS;END;编译得到模块DECL7S:程序运行后可以看到 7段数码管以每秒一次的跳变速度往上自加,到“F”后归“0”。

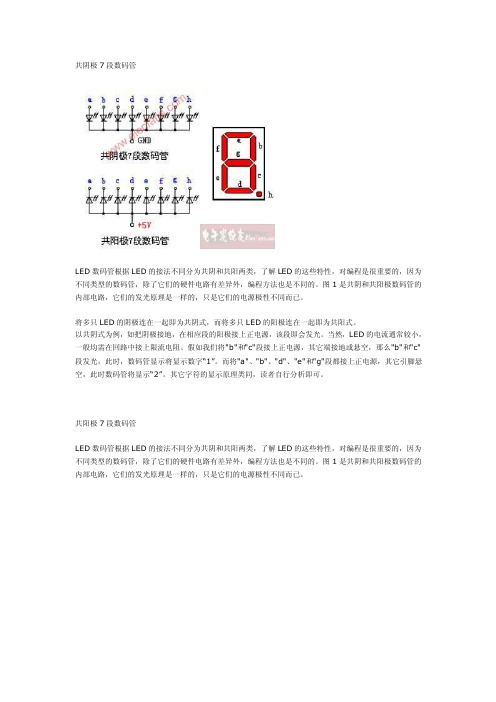

共阴极7段数码管

共阴极7段数码管LED数码管根据LED的接法不同分为共阴和共阳两类,了解LED的这些特性,对编程是很重要的,因为不同类型的数码管,除了它们的硬件电路有差异外,编程方法也是不同的。

图1是共阴和共阳极数码管的内部电路,它们的发光原理是一样的,只是它们的电源极性不同而已。

将多只LED的阴极连在一起即为共阴式,而将多只LED的阳极连在一起即为共阳式。

以共阴式为例,如把阴极接地,在相应段的阳极接上正电源,该段即会发光。

当然,LED的电流通常较小,一般均需在回路中接上限流电阻。

假如我们将"b"和"c"段接上正电源,其它端接地或悬空,那么"b"和"c"段发光,此时,数码管显示将显示数字“1”。

而将"a"、"b"、"d"、"e"和"g"段都接上正电源,其它引脚悬空,此时数码管将显示“2”。

其它字符的显示原理类同,读者自行分析即可。

共阳极7段数码管LED数码管根据LED的接法不同分为共阴和共阳两类,了解LED的这些特性,对编程是很重要的,因为不同类型的数码管,除了它们的硬件电路有差异外,编程方法也是不同的。

图1是共阴和共阳极数码管的内部电路,它们的发光原理是一样的,只是它们的电源极性不同而已。

将多只LED的阴极连在一起即为共阴式,而将多只LED的阳极连在一起即为共阳式。

以共阴式为例,如把阴极接地,在相应段的阳极接上正电源,该段即会发光。

当然,LED的电流通常较小,一般均需在回路中接上限流电阻。

假如我们将"b"和"c"段接上正电源,其它端接地或悬空,那么"b"和"c"段发光,此时,数码管显示将显示数字“1”。

而将"a"、"b"、"d"、"e"和"g"段都接上正电源,其它引脚悬空,此时数码管将显示“2”。

fpga七段数码管 -回复

fpga七段数码管-回复FPGA七段数码管(FPGA Seven-Segment Display)是一种常见的数字显示设备,常用于数码时钟、计数器等嵌入式系统中。

它由七个LED组成,可以显示0到9的十进制数字,以及A到F的十六进制字符。

本文将一步一步回答有关FPGA七段数码管的问题,并介绍如何在FPGA 开发板上使用七段数码管进行数字显示。

第一步:了解FPGA首先,我们需要了解什么是FPGA。

FPGA(Field-Programmable Gate Array)是一种可编程逻辑器件,可以通过配置实现不同的逻辑功能。

它包含了大量的可编程逻辑门和存储单元,可以在硬件层面上实现各种功能。

第二步:认识七段数码管七段数码管由七个LED组成,分别命名为a、b、c、d、e、f和g,以及一个小数点标志dp。

每个LED可以被独立地点亮或熄灭,从而显示不同的数字和字符。

七段数码管的排列方式可以根据不同的设计进行调整,通常是共阴极(Common Cathode)或共阳极(Common Anode)。

第三步:连接FPGA开发板和七段数码管将FPGA开发板和七段数码管连接在一起,通常需要通过引脚或引脚头进行连接。

在连接之前,需要确认七段数码管的连接方式(共阴极或共阳极)以及引脚对应关系。

第四步:编写VHDL程序使用VHDL语言编写FPGA的逻辑代码,实现对七段数码管的控制。

VHDL 是一种硬件描述语言,可以用于描述数字电路的行为和结构。

通过编写VHDL程序,我们可以实现对七段数码管不同位的点亮和熄灭。

第五步:实现数字显示通过FPGA的逻辑代码,可以根据需要点亮或熄灭七段数码管的LED。

为了实现数字显示,我们需要将要显示的数字或字符编码为对应的LED点亮模式。

根据这个编码,我们可以在不同的时间间隔内点亮七段数码管的不同位,从而显示出数字或字符。

第六步:调试和测试完成VHDL程序编写后,需要进行调试和测试。

通过在FPGA开发板上加载并运行程序,可以验证七段数码管的正常工作。

七段数码管

七段数码管

蒲俊林学号:10071201012姓名:同组:杨永增学号:10071201020

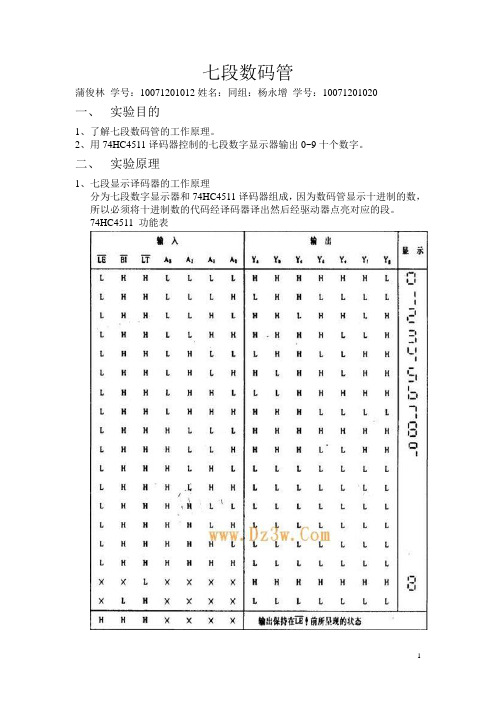

一、实验目的

1、了解七段数码管的工作原理。

2、用74HC4511译码器控制的七段数字显示器输出0~9十个数字。

二、实验原理

1、七段显示译码器的工作原理

分为七段数字显示器和74HC4511译码器组成,因为数码管显示十进制的数,所以必须将十进制数的代码经译码器译出然后经驱动器点亮对应的段。

74HC4511 功能表

七段数字显示器发光组合图:

分段布置图

段组合图

三、 实验步骤

将74HC4511芯片、七段数字显示器插入实验箱并连接导线如下图:

其中 3D 、2D 、1D 、0D 分别接开关K4 、K3、K2、K1。

LE 、BL 、LT 分别接开关K7、K6、K5。

1、显示灯测试—只接通LT --K5并且开关打到低电平,则七段数字显示器全亮。

同理接通BL -- K6、LT --K5且K6低电平、K7高电平则七段数字显示器全灭。

2、接通全部电路,其中K7打到低电平、K6打到高电平、K5打到高电平,通过控制开关K1,K2,K3, K4低电平表示0,高电平表示1。

用二进制控制七段数字显示器显示的数字。

例如:K4低电平K3低电平K2低电平K1高电

平则表示0001,七段数字显示器显示1。

3、控制开关K1,K2,K3, K4输出0~9十个数字。

输出0

输出2。

2020年江苏省单招试卷(14电子电工专业,2015年新课标)

2020年江苏省普通高校对口单招文化统考试题及答案14电子电工专业2020年对口单招电子电工专业技能考试时间表文化统考时间为5月23日上午9:00-11:30语文,下午14:30-17:00专业综合理论(艺术科目组考生不考),5月24日上午9:00-11:00数学,下午14:30-16:30英语。

专业综合理论300分,考试时长为150分钟;语文150分,考试时长为150分钟;数学150分,考试时长为120分钟;英语100分,考试时长为120分钟。

专业技能考试满分为300分。

2020年江苏省普通高校单独招生专业技能考试试题14电子电工专业电工考试部分一、电工专业技能考试参考电气原理图二、电工技能考试准备要求序号名称规格型号数量备注1 断路器DZ47/16A或自定 12 熔断器 23 交流接触器220V10A或380V10A自定 34 热继电器JR16或自定 25 时间继电器JS14或自定 1 晶体管式,配底座6 按钮开关LA10-3或自定 1 不少于3只按钮7 行程开关LX19-B或自定 2同一个考场中交流接触器、中间继电器、时间继电器的线圈额定电压要一致。

时间继电器通电延时触点(转换触点)不少于两组。

同一考场的不同工位的器材应统一型号、标准。

如与推荐要求不一致,请各考点考前1周内将器材分布图报联考委,以便统一发布。

器材设备备份应不少于10%。

二、考场其他准备要求:1.配线板的上角应贴有工位号。

2.考场内干净整洁,通风和采光良好,无噪声等干扰。

3.考场内应配备多组装有漏电保护器的三相四线制交流电源,并备有足够的电源引线(插头)。

4.每块配线板要事先安装好各种元器件(断路器1只,熔断器2只,交流接触器3只,热继电器2只,时间继电器1只,按钮3只,行程开关2只,接线端子排30片以上),建议的器件分布可参考下图。

如有不同,请各考点考前1周将器材分布图报联考委。

5.重要元器件安装后要进行通电测试,防止因元件故障(如吸力不够)影响考试。

七段数码管显示十进制数字

一、实验内容实现某开关闭合时对应显示相应的十进制数字二、设计方案1、实验中需要十个按钮来表示输入的数字,一个十进制数码显示器。

2、要将按钮与数码显示器连接起来,则需要一个74147编码器和一个7449译码器。

因7449译码器为高电频有效,所以数码显示器应该选用共阴极数码显示器。

由于74147编码器是低点频有效,而7449译码器是高电频有效,所以需要在编码器和译码器之间每个连线上加上一个反相器。

又因为74147编码器为低电频有效,所以每个开关闭合时应该为低点频,所以开关左端应接地。

3、当所有输入都为高电频时,74147编码器默认输出0的8421BCD编码,此时数码显示器上显示“0”,这样的话不能与按下开关“0”区别开来。

所以应想办法使得所有按钮都不按下时,数码显示器不显示数字。

注意到7449译码器上有一个输入BI。

当BI为高电频时,译码器才正常输出,当BI为低电频时,无论其他输入是什么,都不输出。

因此可以利用这一点。

如果当所有按钮都不按下时,译码器的BI输入为低电频,那么数码显示器就不显示数字。

因此在所有按钮与译码器的BI端之间加上一个与非门,则可以实现当所有按钮都不按下时,译码器无输出,当按钮“0”按下时,数码显示器显示“0”,当其他按钮按下时,数码显示器显示相应的数字。

4、由于没有10输入的与非门,所以使用一个3输入的与门和一个8输入的与非门代替10输入的与非门。

5、在电源和开关之间、电源和数码显示器之间需要串联若干个上拉电阻,保护元器件。

三、实验过程根据实验方案的设计,用proteus设计电路,如图所示:实验结果分别按下各个按钮,数码显示器上则显示相应的十进制数字。

当所有按钮都不按下时,显示器不显示。

七段数码管数字显示

永城职业学院项目设计七段数码管数字显示班 级:082班专 业:矿山机电姓名:倪开放指导老师:马红雷日期:2010年6月8日目录摘要 (2)关键词: (2)1、PLC概况 (3)1.1 PLC的特点 (3)1.2 PLC应用领域 (3)1.3 PLC的发展 (4)2、控制要求 (4)3、硬件控制设计 (4)3.1 PLC的选型 (4)3.2 I/O设备的选择 (5)4软件控制设计 (6)4.1I/O接线图及I/O分配图 (6)4.2波形图 (7)4.3逻辑表达式 (9)4.4梯形图 (9)4.5程序显示工作原理 (11)4.6流程图 (11)4.7助记符 (13)4.8程序的调试 (14)5、心得体会 (16)参考文献 (17)评分标准 (18)摘要七段数码管广泛应用于医院、学校及一些商业机构。

7段LED数码管,则在一定形状的绝缘材料上,利用单只LED组合排列成“8”字型的数码管,分别引出它们的电极,点亮相应的点划来显示出0-9的数字。

本次设计就是利用这个特点显示自己的学号,选用的是松下FP0系列进行控制的。

本次设机采用的是共阴极七段数码管数码管。

关键词:PLC 控制设计工作原理1、PLC概况1.1 PLC的特点PLC即可编程控制器(Programmable logic Controller,是指以计算机技术为基础的新型工业控制装置。

“PLC是一种专门为在工业环境下应用而设计的数字运算操作的电子装置。

它采用可以编制程序的存储器,用来在其内部存储执行逻辑运算、顺序运算、计时、计数和算术运算等操作的指令,并能通过数字式或模拟式的输入和输出,控制各种类型的机械或生产过程。

具体特点如下:(1)可靠性高,抗干扰能力强(2)配套齐全,功能完善,适用性强(3)易学易用,深受工程技术人员欢迎(4)系统的设计、建造工作量小,维护方便,容易改造(5)体积小,重量轻,能耗低1.2 PLC应用领域目前,PLC在国内外已广泛应用于钢铁、石油、化工、电力、建材、机械制造、汽车、轻纺、交通运输、环保及文化娱乐等各个行业,使用情况大致可归纳为如下几类: a:开关量的逻辑控制b:模拟量控制c:运动控制d:过程控制e:数据处理f:通信与联网1.3 PLC的发展PLC技术的发展,其中有两个趋势方向,一方面,PLC已经不再是自成体系的封闭系统,而是迅速向开放式系统发展,各大品牌PLC除了形成自己各具特色的PLC系统,完成设备控制任务之外,还可以与上位计算机管理系统,实现信息交流,成为整个信息管理系统的一部分。

实验一七段数码管显示译码器

实验⼀七段数码管显⽰译码器实验⼀七段数码显⽰译码器⼀.实验⽬的:1.设计七段显⽰译码器,并在实验板上验证;2.学习Verilog HDL⽂本⽂件进⾏逻辑设计输⼊;3.学习设计仿真⼯具的使⽤⽅法;⼆.实验内容1.实现BCD/七段显⽰译码器的“ Verilog ”语⾔设计。

说明:7段显⽰译码器的输⼊为:IN0…IN3共5根, 7段译码器的逻辑表同学⾃⾏设计,要求实现功能为:输⼊“ 0…15 ”(⼆进制),输出“ 0…9…F ”(显⽰数码),输出结果应在数码管(共阴)上显⽰出来。

2.使⽤⼯具为译码器建⽴⼀个元件符号3.设计仿真⽂件,进⾏验证。

4.编程下载并在实验箱上进⾏验证。

三.实验原理:7段数码是纯组合电路,通常的⼩规模专⽤IC,如74或4000系列的器件只能作⼗进制BCD码译码,然⽽数字系统中的数据处理和运算都是⼆进制的,所以输出表达都是⼗六进制的,为了满⾜⼗六进制数的译码显⽰,最⽅便的⽅法就是利⽤译码程序在FPGA/CPLD 中来实现。

例如6-18作为7段译码器,输出信号LED7S的7位分别接图6-17数码管的7个段,⾼位在左,低位在右。

例如当LED7S输出为“1101101”时,数码管的7个段g,f,e,d,c,b,a分别接1,1,0,1,1,0,1;接有⾼电平的段发亮,于是数码管显⽰“5”。

这⾥没有考虑表⽰⼩数点的发光管,如果要考虑,需要增加段h,然后将LED7S改为8位输出。

四.实验步骤1.编辑和输⼊设计⽂件新建⽂件夹——输⼊源程序——⽂件存盘2.创建⼯程打开并建⽴新⼯程管理窗⼝——将设计⽂件加⼊⼯程中——选择⽬标芯⽚——⼯具设置——结束设置3.全程编译前约束项⽬设置选择FPGA⽬标芯⽚——选择配置器件的⼯作⽅式——选择配置器件和编程⽅式——选择⽬标器件引脚端⼝状态——选择Verilog语⾔版本4.仿真测试五.实验参考程序module LED(A,LED7S);input [3:0]A;output [6:0]LED7S;reg [6:0]LED7S;always @ (A)begin:case(A)4'b0000: LED7S<=7'b0111111;4'b0001: LED7S<=7'b0000110;4'b0010: LED7S<=7'b1011011;4'b0011: LED7S<=7'b1001111; 4'b0100: LED7S<=7'b1100110; 4'b0101: LED7S<=7'b1101101; 4'b0110: LED7S<=7'b1111101; 4'b0111: LED7S<=7'b0000111; 4'b1000: LED7S<=7'b1111111; 4'b1001: LED7S<=7'b1101111; 4'b1010: LED7S<=7'b1110111; 4'b1011: LED7S<=7'b1111100; 4'b1100: LED7S<=7'b0111001; 4'b1101: LED7S<=7'b1011110; 4'b1110: LED7S<=7'b1111001; 4'b1111: LED7S<=7'b1110001; default: LED7S<=7'b0111111; endcaseendendmodule六.编译仿真结果1.时序仿真:2.延时分析及结果:3.⽣成RTL原理图:4.该实验的配置模式:5.适配板布局图及实验仪IO脚与芯⽚的管脚对应关系和其详细放⼤图⽚:6.⼗六进制逻辑分析:7.计数器和译码器连接电路的顶层⽂件原理图:七.体会思考:通过本次实验对EDA和QUARTER2有了初步的了解,第⼀次上机感觉挺难的,这次对Verilog也有了深⼊了解。

vhdl七段数码管显示0到9计数器显示电路设计 -回复

vhdl七段数码管显示0到9计数器显示电路设计-回复如何设计一个能够显示0到9的计数器的七段数码管显示电路。

文章长度:1500-2000字一、引言(100字左右)计数器是数字电路中非常常见的一个组件,而七段数码管则是用于显示数字的一种常用装置。

本文将详细介绍如何设计一个能够实现0到9的计数器,并利用七段数码管进行显示的电路。

二、理论基础(200字左右)在开始设计电路之前,我们需要掌握一些基本的理论知识。

七段数码管是由七个LED组成的,每个LED被称为一个段,分别用a、b、c、d、e、f、g表示。

通过控制七个段的亮灭可以显示不同的数字。

例如,要显示数字0,将a、b、c、d、e、f亮起,而要显示数字1,则只需将b、c 亮起。

三、设计电路(600字左右)1. 确定计数范围根据题目要求,我们需要设计一个能够显示0到9的计数器。

因此,计数范围为0到9,共有10个数字需要显示。

2. 确定计数位数根据题目要求,我们需要设计的是一个十进制计数器,因此需要三个计数位。

每个计数位都是一个0到9的计数器。

3. 设计逻辑电路我们可以使用JK触发器作为计数器的基本构建模块。

JK触发器有两个输入和两个输出,分别称为J、K和Q、~Q。

其中,J和K分别用于控制触发器状态的跳变,而Q和~Q是触发器的两个状态。

我们可以使用三个JK触发器构建一个三位的二进制计数器。

具体电路如下:第一个JK触发器的CLK输入连接计数器电路的时钟信号,J、K和第二个JK触发器的CLK端连接在一起,第二个JK触发器的Q输出连接第三个触发器的J输入,第一个触发器的Q输出连接了第三个触发器的K输入。

这样的设计将会实现三个触发器之间的互动。

4. 连接七段数码管根据七段数码管的布局,我们需要将七段的对应输入连接到计数器的输出。

根据计数器的输出值,我们可以设定哪些段需要亮起或熄灭。

连接七段数码管的具体方法可以参考其数据手册或规格说明。

四、测试与调试(400字左右)完成电路的设计之后,我们需要进行测试和调试,以确保电路能够正常显示0到9的数字。

七段数码管显示十进制数字 (7)

第二次实验报告实验题目:设有十个开关,编号为0,1,2…9,设计电路实现某开关闭合时对应显示相应的十进制数字,写出设计说明并且用proteus仿真。

实验方案:1、可以利用下述装置当按键闭合时,电路接通,电阻两端电压降为5V,故输出Y 为0;当按键打开时,电路断开,电阻两端电压降为0V,故输出Y 为1。

因此我们可以利用0-9这十个按键来控制输入0或者1。

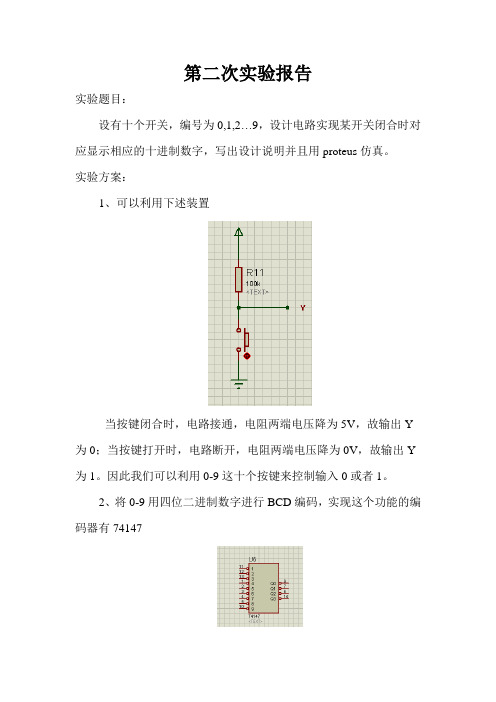

2、将0-9用四位二进制数字进行BCD编码,实现这个功能的编码器有74147其功能表如下图所示9I 8I 7I 6I 5I 4I 3I 2I 1I3Y 2Y 1Y 0Y0 * * * * * * * * 1 0 * * * * * * * 1 1 0 * * * * * * 1 1 1 0 * * * * * 1 1 1 1 0 * * * * 1 1 1 1 1 0 * * * 1 1 1 1 1 1 0 * * 1 1 1 1 1 1 1 0 * 1 1 1 1 1 1 1 1 0 1 1 1 1 1 1 1 1 10 1 1 0 0 1 1 1 1 0 0 0 1 0 0 1 1 0 1 0 1 0 1 1 1 1 0 0 1 1 0 1 1 1 1 0 1 1 1 1按照这个表格,当我们按下某个数字所代表的按键时,该位输入对应就为0,其他位均为1,因此74147会给相对应的数字进行二进制编码。

当同时有两个按键被按下的时候,因为编码器有优先性,故只会对最大的数字进行编码,不会产生混乱。

但是这个编码器有一个小问题就是对0没有编码,这样当按下0键的时候,无法说明输出的是0.。

3、对相应的数字进行编码之后,我们就可以用译码器,七段显示译码器7449将对应的数字用发光二极管显示出来。

其输入就应该是74147的输出。

但是因为7449是高电位有效,而74147是低电位有效,所以在译码器输入之前,应该先用非门处理一下。

Protues 中没有十端口的与非门,可以用一个八端口的与非门和一个三端口的与门来代替。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

实验报告

一、实验题目

有10个开关,编号为0,1,2,3,4,5,6,7,8,9。

设计电路实现某开关闭合时对应显示相应的十进制数字.

二、实验方案设计

该实验分四个主要部分。

一是按键部分,二是将十进制数字编成对应的BCD代码,三是将BCD编码译为七段显示码,四是LED数码管显示。

对应第二、三部分,可以分别选取74LS147和74LS49作为主要器件。

三、四部分的连接:74LS49是集电极开路输出的8421BCD码七段显示译码器。

该译码器的输出为高电平有效,因此适用于连接共阴极数码管。

二、三部分的连接。

由于74LS147输出为低电平有效,而74LS49输入为高电平有效,故在连接这两个器件时应加入反向器,器件型号为74LS04。

连接一、二部分时,因为74LS147只有9个输入端,故先不连接按键“0”,因此直接将按键1~9与74LS147连接即可。

三、实验过程

先连接三、四部分。

具体电路如下所示:

连接二、三部分,电路如图所示:

连接一、二部分,电路如图所示:整体电路如图所示:

于是,一个实现编号为0~9的某开关闭合时对应显示相应的十进制数字的电路完成。

四、实验结果

下图为按键4按下的结果:

下图为按键7均按下的结果:。