加州理工学院-计算系统导论 (38)

高性能计算导论课件-高性能计算导论-PPT文档资料

• 作业2:

– 任意选择一个演讲题目,谈谈你对该研究领域的理解 – 长度不限、鼓励原创观点

• 作业提交

– 9月10日,最后一节课上提交打印版

In+Lab@SYSU

3

智能规划

中山大学计算机软件所教授,博士生导师 吉林大学珠海学院计算机科学与技术系主任 中国计算机学会理事 中国计算机教育专业委员会秘书长 姜云飞 教授 中国计算机学会人工智能专业委员会自动推 理学组组长

高性能计算导论

超级计算系 数据科学与计算机学院 中山大学 2019年夏季学期

In+Lab@SYSU

1

课程时间表

In+Lab@SYSU

2

课程作业

• 作业1:

– – – – 写一个高性能计算的综述 定义、起源、分支、应用、最新研究方向等 请做好引用及提供参考文献 A4纸张、单栏、小4号宋体、4页以上

In+Lab@SYSU

4

机器学习辅助的进化计算方法

• • • • • • 詹志辉

副教授

2019年广东省自然科学杰出青年基金获得者 2019年中国高被引学者(计算机科学)入选者 2019年珠江科技新星人才计划项目入选者 2019年中国计算机学会(CCF)优秀博士论文奖 2019年广东省优秀博士学位论文奖 已发表学术论文40多篇,其中IEEE Transactions 等 SCI期刊论文13篇,ESI前1%高被引论文3篇,其中一 篇入选ESI 前0.1% Hot Paper.

李全忠

讲师

In+Lab@SYSU

7

数据密集型视觉计算

• 视觉计算、智能学习、大规模数据处理 • 教育部新世纪优秀人才支持计划入选者,广东省自然科 学杰出青年基金获得者,主持中山大学智能媒体计算实 验室 • 迄今共发表或录用论文70余篇(Proceeding of the IEEE论文1篇,IEEE TPAMI论文4 篇,IEEE TIP论文4 篇,IEEE TCSVT论文4篇,国际会议论文ICCV、CVPR 、NIPS、ACM Multimedia 20余篇) • 香港理工大学,访问教授 • 美国加州大学洛杉矶分校(UCLA),博士后研究员

计算机导论(黄国兴)

计算机导论

6

计算机的发展

第一代计算机(1946年~1957年) 第二代计算机(1958年~1964年) 第三代计算机(1965年~1971年) 第四代计算机(1972年~今) 第五代计算机

计算机导论

计算机导论

4

计算机的特点

运算速度快 运算精度高 具有记忆能力 具有逻辑判断能力 存储程序

计算机导论

5

计算机的用途

科学计算 数据处理 实时控制 人工智能 娱乐与游戏 计算机辅助工程和辅助教育

问题的符号表示及其处理过程的机械化严格化的固有特性决定了数学是计算机科学与技术学科的重要基础之一数学及其形式化描述严密的表达和计算是计算机科学与技术学科所用的重要工具建立物理符号系统并对其实施变换是计算机科学与技术学科进行问题描述和求解的重要手段

第1章

内容提要

绪论

本章在介绍计算机的定义、分类、特点、用途和发展 等基本概念的基础上,介绍了计算机科学与技术学科的教 育和对计算机科学与技术学科毕业生的基本要求。本章还 分析了信息化社会的基本特征、Internet对信息化社会的 影响以及信息化社会对计算机人才及其知识结构的基本要 求,概要地介绍了计算机科学与技术学科的内涵、知识体 系和研究范畴。通过本章的学习,应理解计算机的基本概 念、信息化社会的特征以及信息化社会对计算机人才的需 求,并初步了解计算机科学技术的研究范畴和作为一名计 算机科学技术专业毕业的学生应具有的知识和能力,明确 今后学习的目标和内容,树立作为一个未来计算机科学技 术工作者的自豪感和责任感。

15

计算机科学与技术学科的教育

计算机科学与技术学科的发展速度是非常快的 , 计

《计算科学导论》课件

06

网站测试与部署

对网站进行测试,确保各项功能正常,然后将 网站部署到服务器上。

人工智能应用实战项目

总结词

通过开发一个基于人工智能的应用程序,学生可以掌握 人工智能的基本原理和技术,提高实际应用能力。

选择合适的人工智能技术

根据项目的需求,选择合适的人工智能技术,如机器学 习、深度学习等。

数据收集与标注

20世纪90年代

大数据和云计算技术的出现,为 计算科学带来了新的挑战和机遇

。

20世纪80年代

互联网的兴起,推动了计算机网 络的快速发展。

20世纪70年代

个人计算机的出现,使得计算机 技术更加普及。

计算科学的应用领域

数据科学

涉及数据挖掘、数 据分析、数据可视 化等领域。

软件工程

包括软件开发、软 件测试、软件维护 等领域。

生物信息学与计算生物学

随着基因组学和蛋白质组学等研究的 深入,计算科学将在生命科学领域发 挥越来越重要的作用。

个人如何学习与发展计算科学

基础学科知识

掌握数学、物理、计算机等基础学科知 识,为深入学习计算科学打下坚实基础

。

参加竞赛与项目实践

参加算法竞赛、数据科学竞赛等活动 ,参与开源项目和实际应用开发,提

云计算与虚拟化技术包括云平台架构、虚拟机技术、容器化技术等,这 些技术能够实现资源的动态管理和调度,提高资源利用率,降低运维成

本,同时也为应用程序的开发和部署提供了便利。

云计算与虚拟化技术的发展对于推动企业数字化转型、促进软件产业升 级等方面具有重要意义,同时也为人工智能、大数据等领域的快速发展 提供了基础支撑。

物联网与智能家居

物联网与智能家居是计算科学领域中的 另一前沿技术,它通过互联网连接家居 用品,实现智能化控制和管理,提高生

美国加州大学圣塔芭芭拉分校之计算科学与工程

一所成立于1909年位于美国西部小城圣塔芭芭拉的大型公立综合性全国大学,亦是加州大学系统10个成员之一。

主校区位于加州戈丽塔市,占地面积约1022公顷,离洛杉矶约100英里,其前身是一所师范院校,后于1944年加入加州大学系统,成为第三历史最古老大学成员。

加州大学圣塔芭芭拉分校属美国公立常春藤之一,是一所综合性大学,提供本、硕、博三种学位类型。

计算科学与工程

加州大学圣塔芭芭拉分校计算科学与工程(Computational Science & Engineering,缩写CSE)是一个由7个系共同参与开设的交叉学科项目,设有MS与PhD两种学位类型。

欲攻读该专业,需先获得这7个参与系之一的录取。

这7个参与系分别是:

化学工程系(Department of Chemical Engineering)

计算机科学系(Department of Computer Science)

地球科学系(Department of Earth Science)

生态、进化与海洋生物学系(Department of Ecology, Evolution and Marine Biology)

电气与计算机工程系(Department of Electrical and Computer Engineering)

数学系(Department of Mathematics)

机械工程系(Department of Mechanical Engineering)。

计算科学导论三PPT文档42页

2021/7/16

20

计算科学各主领域及其基本问题

• 人机交互

̵ 重点在于理解作为交互式对象的人的行为,知道怎样 使用以人为中心的方法来开发和评价交互式软件系统

̵ 基本问题: ̵ ①表示物体和自动产生供阅览的照片的有效方法是什

么?

̵ ②接收输入和给出输出的有效方法是什么? ̵ ③怎样才能减少产生误解和由此产生的人为错误的风

̵ 要精通这个领域,必须有理论和实践两方面的 知识

̵ 实践教学包括:数据收集和综合、建模、源代 码级的协议分析、网络数据包的监控、软件构 造以及对备选设计模型的评估等

2021/7/16

17

计算科学各主领域及其基本问题

• 算法与复杂度

̵ 基本问题: ̵ ①网络中的数据如何进行交换? ̵ ②网络协议如何验证? ̵ ③如何保证网络的安全? ̵ ④分布式计算的性能如何评价? ̵ ⑤分布式计算如何组织才能够使通过通信网连

̵ 为了理解程序设计语言实用的一面,还要求具 有程序设计语言翻译和诸如存储分配等方面的 基础知识

2021/7/16

19

7.4计算科学各主领域及其基本问题

• 程序设计语言

̵ 基本问题: ̵ ①语言(数据类型、操作、控制结构、引进类

型和操作的机制)表示的虚拟机的可能组织结 构是什么? ̵ ②语言如何定义机器?机器如何定义语言? ̵ ③什么样的表示法(语义)可以有效地用于描 述计算机应该做什么?

2021/7/16

14

计算科学各主领域及其基本问题

• 操作系统

̵ 基本问题: ̵ ①在计算机系统操作的每一个级别上,可见的Байду номын сангаас

对象和允许进行的操作各是什么? ̵ ②对每一类资源,能够对其进行有效利用的最

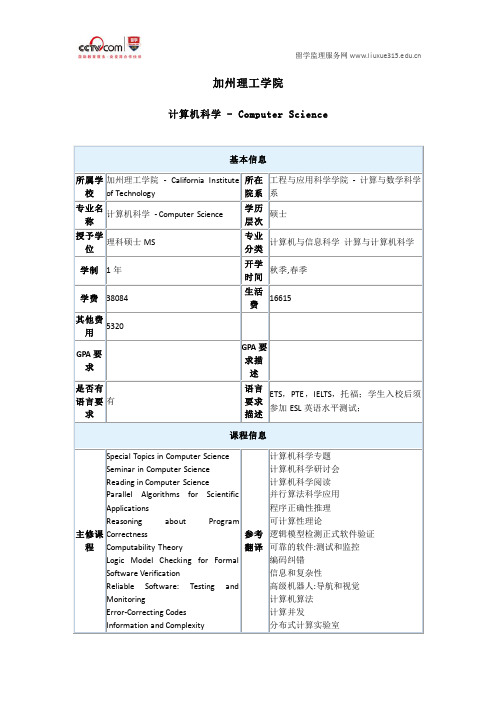

美国加州理工学院计算机科学硕士专业

留学监理服务网 www.li

加州理工学院 California Institute of Technology

综合排名:10 学校类型:私立 - 综合性大学 所在地:美国 加利福尼亚州 帕萨迪纳 录取率:10.55% SAT 统计:2160-2380 每年学费:24 万(人民币) 是否有奖学金:是 在校生人数:2231 开学时间:秋季,春季 学校网址:

每年秋季,

用科学学 $38084

院

约合 24 万

MS

春季

生物工程 (人民币)

学系

应用计算数学 1

Applied / Computational Mathematics

理科硕士 MS

每年秋季, 春季

工程与应 用科学学

院 计算与数 学科学学

系

$38084 约合 24 万 (人民币)

计算机科学 Computer Science

留学监理服务网 www.li

加州理工学院

计算机科学 - Computer Science

基本信息

所属学 加州理工学院 - California Institute 所在 工程与应用科学学院 - 计算与数学科学

校 of Technology

院系 系

专业名 称

计算机科学

- Computer

机械工程

Mechanical

4

Engineering

化学工程

BS in Chemical

4

Engineering

商业经济学与管理 4

Business Economics

授予学位 开学时间

所在院系

学 费 /年

理科学士 BS

工程与应用科学

加州理工学院-计算系统导论 (30)

b bits block offset

¢ Example: direct-mapped cache with 4 sets

2 bits in set index

Direct-Mapped Cache with 4 Sets

¢ Very fast to map an address to a cache set

CS24: INTRODUCTION TO COMPUTING SYSTEMS

Spring 2013 Lecture 15

LAST TIME

¢ Discussed concepts of locality and stride

Spatial locality: programs tend to access values near values they have already accessed

¢ Each cache set has E cache lines in it…

Need to look up cache line using only the block’s tag The cache set is an associative memory

¢ More complicated to find if a block is in the cache

Need to examine all cache-line tags

Also, tag is larger than in a direct-mapped cache

Valid Tag

Avoid conflict misses by having multiple lines per cache-set

Avoid complicated logic to check tags of many lines

《计算机科学导论课件》

编程与算法

学习编程语言和算法设计,提升解决复杂问题的能 力。

人机交互与用户体验

研究如何设计用户友好的界面和交互体验,提升人 机互动效果。

计算机科学的历史

年代 1936 1971 1990 2004

里程碑 图灵机提出,标志着计算机科学的开始。 发明第一台微处理器,开启了个人计算机时代。 万维网诞生,互联网得以普及。 诞生了Facebook,社交媒体的兴起。

计算机科学的基础知识

1 二进制

计算机使用的数字系统,了解其原理对理解计算机工作方式至关重要。

2 逻辑电路

了解计算机内部的电路以及逻辑门的工作原理。

3 操作系统

学习操作系统的功能和作用,了解计算机的基本操作。

4 编程语言

掌握编程语言的基本概念和语法,能够编写简单的程序。

计算机硬件和软件架构

计算机硬件

掌握常见的排序和搜索算法,提高程序的效 率。

计算机网络和通信技术

计算机网络

学习网络基础知识,如TCP/IP协 议、局域网、广域网等。

网络安全

了解网络安全的重要性和常见的 网络攻击方式,学习保护网络的 方法。

通信技术

掌握无线通信和移动通信的原理 和技术,了解通信协议和网络传 输。

人工智能和机器学习

包括中央处理器、内存、硬盘等各 种硬件组件。

软件架构

设计软件的结构和组织方式,实现 程序的功能和目标。

电路板

控制计算机硬件的电路,使其能够 正常工作。

数据结构和算法

1

数据结构

学习数据的存储方式和组织结构,如数组、

算法复杂性

2

链表和树等。

分析算法的时间和空间复杂性,选择合适的

算法解决问题。

加州理工学院-计算系统导论 (18)

UPDATE OUR ISA AND PROCESSOR

¢ Add a new instruction: BRZ A, Addr (Branch if Zero)

If value in slot A is 0, change Prog Ctr to address Addr

¢ New logic to support this instruction:

¢ Branch Logic:

If opcode is BRZ, and memory A outputs 0, then tell multiplexer to load Addr into the Program Counter.

UPDATED PROCESSOR

¢ With updated processor, can reuse instructions by creating loops in our programs

p = p + b;

1001

a = a >> 1;

1010

b = b << 1;

1011

}

1100

return p;

}

1110

¢ Coding is more complex now!

Need to plan out our loops…

Need to know the addresses to jump to!

Operation

ADD

AB

SUB

AB

NEG

A

BRZ

A Addr

AND

AB

OR

AB

XOR

AB

INV

A

SHL

360教育集团:加州理工学院申请之计算机科学

官网: 加州理工学院(Caltech)创建于1891年,是一所位于美国加利福尼亚州帕萨蒂纳的小型私立综合性全国大学,主校区占地面积约124英亩,该校离洛杉矶市仅18公里。

该校由美国企业家、政治家阿默斯·G·史路普(Amos G. Throop)一手建立,当初只是一个职业学校直到1910年,1934年加州理工当选为美国大学联盟成员;在1936年到1943年,该校一直管理运营着美国宇航局喷气推进实验室。

计算机科学360教育集团 (/)介绍加州理工学院计算机科学(Computer Science)与计算与数学科学(Computing & Mathematical Sciences)为同一个专业,开设有以下研究领域:算法经济学(Algorithmic Economics)应用概率论(Applied Probability)形式化方法(Formal Methods)图形与几何(Graphics & Geometry)机器学习与视觉(Machine Learning & Vision)数学信号处理(Mathematical Signal Processing)分子编程(Molecular Programming)网络系统(Networked Systems)优化(Optimization)量子信息与计算(Quantum Information & Computation)机器人与智能机器(Robotics & Intelligent Machines)科学计算(Scientific Computing)理论计算机科学(Theory of Computation)参考资料:(1) Research Areas-CMS Caltech。

麻省理工学院-算法导论

麻省理工学院-算法导论关于课本的介绍如下:本书自第一版出版以来,已经成为世界范围内广泛使用的大学教材和专业人员的标准参考手册。

本书全面论述了算法的内容,从一定深度上涵盖了算法的诸多方面,同时其讲授和分析方法又兼顾了各个层次读者的接受能力。

各章内容自成体系,可作为独立单元学习。

所有算法都用英文和伪码描述,使具备初步编程经验的人也可读懂。

全书讲解通俗易懂,且不失深度和数学上的严谨性。

第二版增加了新的章节,如算法作用、概率分析与随机算法、线性编程等,几乎对第一版的各个部分都作了大量修订。

学过计算机的都知道,这本书是全世界最权威的算法课程的大学课本了,基本上全世界的名牌大学用的教材都是它。

这本书一共四位作者,Thomas H. Cormen,Charles E. Leiserson和Ronald L. Rivest是来自MIT的教授,Clifford Stein是MIT出来的博士,现在哥伦比亚大学做教授,四人姓氏的首字母联在一起即是此书的英文简称(CLRS 2e),其中的第三作者Ronald L. Rivest是RSA算法的老大(算法名字里面的R即是指他),四个超级大牛出的一本书,此书不看人生不能算完整。

再介绍一下课堂录像里面授课的两位MIT的老师,第一位,外表“绝顶聪明”的,是本书的第二作者Charles E. Leiserson,以逻辑严密,风趣幽默享誉MIT。

第二位,留着金黄色的络腮胡子和马尾发的酷哥是Erik Demaine,21岁即取得MIT教授资格的天才,1981出生,今年才25岁,业余爱好是俄罗斯方块、演戏、琉璃、折纸、杂耍、魔术和结绳游戏。

另外,附上该书的中文电子版,pdg转pdf格式,中文版翻译自该书的第一版,中文书名没有使用《算法导论》,而使用的是《现代计算机常用数据结构和算法》,1994年出版时没有得到国外的授权,属于“私自翻译出版”,译者是南京大学计算机系的潘金贵。

课程重点算法导论是麻省理工学院电机工程与计算机科学系“理论计算机科学”集中选修课程的先导科目。

《麻省理工学院-算法导论》(MIT - Introduction to Algorithms)概要

《麻省理工学院-算法导论》(MIT - Introduction to Algorithms)这是麻省理工学院2001年秋季课程《算法导论》的所有课程资料,包括有:课本(含有习题,chm格式),课堂讲稿(ppt转pdf格式),作业及其答案(pdf格式),测验及其答案(pdf格式),教师参考(含习题答案,很难得,pdf格式),课堂录像(rmvb格式)。

关于课本的介绍如下:本书自第一版出版以来,已经成为世界范围内广泛使用的大学教材和专业人员的标准参考手册。

本书全面论述了算法的内容,从一定深度上涵盖了算法的诸多方面,同时其讲授和分析方法又兼顾了各个层次读者的接受能力。

各章内容自成体系,可作为独立单元学习。

所有算法都用英文和伪码描述,使具备初步编程经验的人也可读懂。

全书讲解通俗易懂,且不失深度和数学上的严谨性。

第二版增加了新的章节,如算法作用、概率分析与随机算法、线性编程等,几乎对第一版的各个部分都作了大量修订。

学过计算机的都知道,这本书是全世界最权威的算法课程的大学课本了,基本上全世界的名牌大学用的教材都是它。

这本书一共四位作者,Thomas H. Cormen,Charles E. Leiserson和Ronald L. Rivest是来自MIT的教授,Clifford Stein是MIT出来的博士,现在哥伦比亚大学做教授,四人姓氏的首字母联在一起即是此书的英文简称(CLRS 2e),其中的第三作者Ronald L. Rivest是RSA算法的老大(算法名字里面的R即是指他),四个超级大牛出的一本书,此书不看人生不能算完整。

再介绍一下课堂录像里面授课的两位MIT的老师,第一位,外表“绝顶聪明”的,是本书的第二作者Charles E. Leiserson,以逻辑严密,风趣幽默享誉MIT。

第二位,留着金黄色的络腮胡子和马尾发的酷哥是Erik Demaine,21岁即取得MIT教授资格的天才,1981出生,今年才25岁,业余爱好是俄罗斯方块、演戏、琉璃、折纸、杂耍、魔术和结绳游戏。

系统工程(清华大学)

清华大学本科限选课程

钱学森

中国航天之父 中国火箭、导弹和航天技术的重要奠基人。

感动中国2008年度人物。

感动中国推选委员会阎肃: 大千宇宙 浩瀚长空,全纳入赤子心胸。 惊世两弹 冲宵一星,尽凝铸中华豪情,霜鬓不坠青云志。 寿至期颐 回首望去,只付默默一笑中。 钱学森先生引入“不太可靠的元件通过冗余技术可以 组成可靠的系统”的思想,开创了中国的航天领域研究, 是中国导弹航天技术跻身世界前沿。

中国春秋时期老子:“道生一、一生二、二生三、三生 万物” ……

清华大学本科限选课程

系统工程导论

25

系统运动图

自然科学 (生物)

社会科学 (经济)

哲学 (西方)(东方) 东方系统方法论 (1990's)

一般系统理论(1945) 控制论(1948) 信息论(1948) 中国传统系统 思想(公元前 11世纪)、西 方传统系统思 想(公元前 600年)

3、皇宫修好后,把沟水排掉,用建筑垃圾、废弃

杂物填入沟中,恢复原来大街。

启示

皇宫修复全过程看成一个系统,并划分为若干并行 和交叉作业的子系统。蕴含了“系统工程”思想。

清华大学本科限选课程 系统工程导论 14

第二阶段:突然崛起

大体上形成于上世纪50、60年代 经典成功案例(美国)

北极星导弹核潜艇计划

鱼嘴岷江分水工程

飞沙堰分洪排沙工程

宝瓶口引水工程

清华大学本科限选课程

系统工程导论

13

丁渭工程

北宋真宗时期(998-1022年),皇城失火,宫殿 被毁。皇帝任命丁渭负责修复皇宫。丁渭的方案是: 1、皇宫旧址前原有大街处挖一沟渠,挖沟的土烧 砖,解决部分建筑材料问题。 2、开封附近的汴水引入沟内,形成航道,从外地 运输沙石木料。

计算机导论(Introduction to Computers)

(Protocol) URL:

域名

(Domain name)

13

西安电子科技大学计算机学院 - School of Computer Science & Engineering, Xidian University, China

计算机导论 - Introduction to Computers

计算机网络

基本术语: 基本术语:

带宽(Bandwidth):网络数据传输容量(bits/秒,bps) 结点(Node):连接到网络上的设备 客户机(Client):请求并使用其他结点可用资源的结点 服务器(Server):允许其他结点共享自己资源的结点 网络操作系统: 网络操作系统:对网络中结点之间的活动进行控制与协调 的系统软件 分散在不同结点、 分布处理 (Distributed processing): 分散在不同结点 、 可 以被共享的协同计算能力

结点使用公共的信道相互连 可以直接通信。 接,可以直接通信。

西安电子科技大学计算机学院 - School of Computer Science & Engineering, Xidian University, China

8

计算机导论 - Introduction to Computers

环形结构与层次结构

2

计算机导论 - Introduction to Computers

计算机网络与互联网

西安电子科技大学计算机学院 - School of Computer Science & Engineering, Xidian University, China

3

计算机导论 - Introduction to Computers

0引言

计算思维的特征(3)

• 人的,不是计算机的思维

– 计算思维是人类求解问题的一条途径,但决非要使人类像计算机 那样地思考。计算机枯燥且沉闷,人类聪颖且富有想象力。是人 类赋予计算机激情。配置了计算设备,我们就能用自己的智慧去 解决那些计算时代之前不敢尝试的问题,实现―只有想不到,没有 做不到‖的境界。计算机赋予人类强大的计算能力,人类应该好好 的利用这种力量去解决各种需要大量计算的问题。

• 面向所有的人,所有地方

– 当计算思维真正融入人类活动的整体以致不再表现为一种显式之 哲学的时候,它就将成为现实。就教学而言,计算思维作为一个 问题解决的有效工具,应当在所有地方,所有学校的课堂教学中 都得到应用。

18

计算思维对其他学科的影响

• • • • • • •

计算思维+统计学 计算思维+生物学 计算思维+经济学 计算思维+化学 计算思维+物理 计算思维+语言学 ……

– 伽利略就不仅设计和演示了许多实验,而且还亲自研制出不少技 术精湛的实验仪器,如温度计、望远镜、显微镜等

• 以实验为基础的学科有物理、化学、地学、天文学、生物 学、医学、农业科学、冶金、机械,以及由此派生的众多 学科 • 在实验思维中,有一个至关重要的核心内容,那就是实验 思维往往要借助于特定的设备来进行的

Credit: Wikipedia

Credit: Wikipedia

工程 (电气,市政,机械,航空航天……)

- 更高阶的计算意味着更高的精准度,可以减少制造工程

22

的重量,费用和浪费 - 利用计算机模拟对Boeing 777进行测试,而不是风洞

Credit: Boeing

人类社会中的计算思维(1)

计算机导论课程英文简介

-----WORD格式--可编辑--专业资料-----Introduction to Computers B IntroductionIntroduction to Computers BCourse Number:B08010120Course Property:professional basic courseSemester and Periods Allocation :the first semester, 4 hours per weekApplied Specialty:students of Computer Science double majorPrior Courses:noneSucceed Courses:Data Structure Operating Systems Software Engineering Computer NetworkTeaching Material:《Computer Science Conception》(eleven edition),J. GlennBrookshear,People's Posts and Telecommunications Press,2011Recommended References Books :1.《Software Craftsmanship》,Joel spolsky,People's Posts and Telecommunications Press,20092.《Computer Introduction》(third edition),Wangyulong,Fuxiaolong,Publishing House of electronics industry,20093.《Computer Introduction》,Chenming,Tsinghua University press,2009Purpose ,Contents and Requierments of the Course:This course is a pilot introductory course for students of computer science and technology double major, aiming to provide a basic understanding of the main knowledge and skills of the major , and to construct a basic framework of knowledge of subsequent courses and lay a foundation for later professional knowledge learning and scientific research. It also cultivates the students' conceptions of the global and awareness of updating knowledge constantly.This course involves all aspects of computer science and focuses on the basic conception rather than mathematical model and technology details with requirements of “breadth first, wide rather than fine”. The emphasis of the course is to outline the framework of computer science system, lay a foundation of computer science knowledge and pave the way for subsequent learning of the professional theory courses in computer information technology. The course is parallelly opened with the course of Office Automation Technology, letting the students to master the basic operation technique, enhance the perceptual knowledge and lay a solid a foundation for computer using in their own major.author:Caolingauditor--完整版学习资料分享----。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

IMPLEMENTATION ISSUES (2)

¢ CPUs frequently use a Translation Lookaside Buffer (TLB) to cache page table entries Designed to be extremely fast Don’t even want to incur L1 or L2 penalty, if possible!

page table that the MMU uses ¢ Share memory regions between processes, such

as shared libraries, kernel code, working areas ¢ Memory-map disk files into virtual memory, to

Also permission flags, e.g. “read/write,” “supervisor”

¢ Requires both hardware and software support:

CPU performs address translation in hardware to make it as fast as possible

Showed the processor using a single page table Real-world system doesn’t work that way!

¢ Given a 32-bit address space, and pages of 4KB:

Page offsets take 12 bits, page numbers are 20 bits

would still be 4-25ns away

CPU

mov 307, %ebx

Virtual Address = 307

MMU

Physical Address = 7 Page Table

Main Memory 0123 4567 8 9 10 11

¢ Can’t afford memory performance being this bad!

CS24: INTRODUCTION TO COMPUTING SYSTEMS

Spring 2013 Lecture 24

LAST TIME

¢ Extended virtual memory concept to be a cache of memory stored on disk

DRAM becomes L4 cache of data stored on disk

load programs, and to perform fast and easy IO ¢ Set permissions on memory pages to make some

pages read-only, or inaccessible by user code

LAST TIME: IMPLEMENTATION ISSUES

LAST TIME (2)

¢ Can now implement many useful features!

¢ Isolate address spaces of different processes ¢ Perform fast context-switches by changing the

Operating system must handle situations where pages must be moved into and out of memory

CPU raises page fault and general protection fault exceptions when it requires the kernel’s intervention

CPU

mov 307, %ebx

TLB

Virtual Address = 307

MMU

PTE

Physical Address = 7 Page Table

Main Memory 0123 4567 8 9 10 11

TRANSLATION LOOKASIDE BUFFER

¢ Translation lookaside buffer stores one page table entry per cache line

¢ Also added more details to page table entries

Entries have a valid (IA32: “present”) flag specifying if the page is in memory, and if not, where it resides

Input is virtual page number, output is page table entry

¢ TLB typically has a high degree of associativity

Maximize chance that TLB contains needed page table entry!

CPU

TLB

mov 307, %ebx VPN

PTE

Virtual Address = 307

MMU

PTE

Physical Address = 7 Page Table

Main Memory 0123 4567 8 9 10 11

IMPLEMENTATION ISSUES (3)

¢ Issue 2: How laBiblioteka ge are page tables?

¢ Started to look at two implementation issues ¢ Issue 1: Page tables live in main memory

As much as 100ns away from the MMU! Caches would help with this, but page table entries