QD77缓冲区参数表

微秒微电子ZL40200精密1 2 LVPECL双端输出缓冲器数据手册说明书

1FeaturesInputs/Outputs •Accepts differential or single-ended input •LVPECL, LVDS, CML, HCSL, LVCMOS •Two precision LVPECL outputs •Operating frequency up to 750 MHzPower •Options for 2.5 V or 3.3 V power supply •Core current consumption of 49 mA•On-chip Low Drop Out (LDO) Regulator for superior power supply rejectionPerformance •Ultra low additive jitter of 39 fs RMSApplications•General purpose clock distribution •Low jitter clock trees •Logic translation•Clock and data signal restoration•Wired communications: OTN, SONET/SDH, GE, 10 GE, FC and 10G FC•PCI Express generation 1/2/3 clock distribution •Wireless communications•High performance microprocessor clock distributionApril 2014Figure 1 - Functional Block DiagramZL40200Precision 1:2 LVPECL Fanout BufferData SheetOrdering InformationZL40200LDG1 16 Pin QFN TraysZL40200LDF116 Pin QFN Tape and ReelMatte TinPackage size: 3 x 3 mm-40o C to +85o CTable of ContentsFeatures . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1 Inputs/Outputs . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .1 Power . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .1 Performance . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .1 Applications . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1 Change Summary . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 41.0 Package Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .52.0 Pin Description. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .53.0 Functional Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .63.1 Clock Inputs. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .63.2 Clock Outputs . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .113.3 Device Additive Jitter. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .153.4 Power Supply . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .163.4.1 Sensitivity to power supply noise. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .163.4.2 Power supply filtering. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .163.4.3 PCB layout considerations. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .164.0 AC and DC Electrical Characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .175.0 Performance Characterization . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .206.0 Typical Behavior . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .217.0 Package Thermal Characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .238.0 Mechanical Drawing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .24List of FiguresFigure 1 - Functional Block Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1 Figure 2 - Pin Connections . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5 Figure 3 - LVPECL Input DC Coupled Thevenin Equivalent . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6 Figure 4 - LVPECL Input DC Coupled Parallel Termination. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7 Figure 5 - LVPECL Input AC Coupled Termination . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7 Figure 6 - LVDS Input DC Coupled . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8 Figure 7 - LVDS Input AC Coupled . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8 Figure 8 - CML Input AC Coupled . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9 Figure 9 - HCSL Input AC Coupled . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9 Figure 10 - CMOS Input DC Coupled Referenced to VDD/2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10 Figure 11 - CMOS Input DC Coupled Referenced to Ground . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10 Figure 12 - Simplified Output Driver. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11 Figure 13 - LVPECL Basic Output Termination . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11 Figure 14 - LVPECL Parallel Output Termination. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12 Figure 15 - LVPECL Parallel Thevenin-Equivalent Output Termination. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12 Figure 16 - LVPECL AC Output Termination for Externally Terminated LVPECL Inputs . . . . . . . . . . . . . . . . . . . . 13 Figure 17 - LVPECL AC Output Termination for Internally Terminated LVPECL Inputs. . . . . . . . . . . . . . . . . . . . . 13 Figure 18 - LVPECL AC-Coupled Output Termination for CML Inputs. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14 Figure 19 - Additive Jitter. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 15 Figure 20 - Decoupling Connections for Power Pins. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 16 Figure 21 - Differential Voltage Parameter. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 18 Figure 22 - Input To Output Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 19Change SummaryPage ItemChange1Applications Added PCI Express clock distribution.5Pin Description Added exposed pad to Pin Description.Removed 22 O hm series resistors from Figure 3 and 4.These resistor s are not required; however there is no impact to performance if the resistors are included.6, 7Figure 3 and Figure 413Figure 16Corrected LVPECL interface circuit.18Figure 21Below are the changes from the February 2013 ti the April 2014 issue:Page Item Change7Figure 4Changed text to indicate the circuit is not recommended for VDD_driver=2.5V.7Figure 5Changed pull-up and pull-down resistors from 2kOhm to 100 Ohm.Below are the changes from the November 2012 issue to the February 2013 issue:Clarification of V ID and V OD.The device is packaged in a 16 pin QFN1416642NCvddNCN Cc l k _pvddgndNCo u t 1_no u t 1_po u t 0_n81210o u t 0_pc l k _nN CNCgndFigure 2 - Pin Connections2.0 Pin DescriptionPin Description Pin # Name Description1, 4clk_p, clk_n,Differential Input (Analog Input). Differential input signals.12, 11, 10, 9out0_p, out0_n out1_p, out1_n Differential Output (Analog Output). Differential outputs.8, 13vdd Positive Supply Voltage. 2.5V DC or 3.3 V DC nominal.5, 16gnd Ground. 0 V.2, 3, 6, 7, 14, 15NCNo Connection. Leave unconnected.Exposed Pad Device GND .The ZL40200 is an LVPECL clock fanout buffer with two identical output clock drivers capable of operating at frequencies up to 750MHz.Inputs to the ZL40200 are externally terminated to allow use of precision termination components and to allow full flexibility of input termination. The ZL40200 can accept DC coupled LVPECL or LVDS and AC coupled LVPECL, LVDS, CML or HCSL input signals; single ended input signals can also be accepted. A pin compatible device with internal termination is also available.The ZL40200 is designed to fan out low-jitter reference clocks for wired or optical communications applications while adding minimal jitter to the clock signal. An internal linear power supply regulator and bulk capacitors minimize additive jitter due to power supply noise. The device operates from 2.5V+/-5% or 3.3V+/-5% supply. Its operation is guaranteed over the industrial temperature range -40°C to +85°C.The device block diagram is shown in Figure 1; its operation is described in the following sections.3.1 Clock InputsThe device can accept LVPECL, LVDS, CML, HCSL and single-ended inputs.Figure 3 - LVPECL Input DC Coupled Thevenin EquivalentFigure 4 - LVPECL Input DC Coupled Parallel TerminationFigure 5 - LVPECL Input AC Coupled TerminationFigure 6 - LVDS Input DC CoupledFigure 7 - LVDS Input AC CoupledFigure 8 - CML Input AC CoupledFigure 9 - HCSL Input AC CoupledFigure 10 - CMOS Input DC Coupled Referenced to VDD/2Figure 11 - CMOS Input DC Coupled Referenced to GroundVDD_driver R1 (kΩ)R2 (kΩ)R3 (kΩ)RA (kΩ) C (pF) 1.5 1.25 3.075open10101.81 3.8open10102.50.33 4.2open10103.30.75open4.21010Table 1 - Component Values for Single Ended Input Reference to Ground * For frequencies below 100 MHz, increase C to avoid signal integrity issues.3.2 Clock OutputsLVPECL has a very low output impedance and a differential signal swing between 1V and 1.6 V. A simplified diagram for the output stage is shown in Figure 12.The LVPECL to LVDS output termination is not shown since there is a separate device that has the same input and LVDS outputs.out_pout_nFigure 12 - Simplified Output DriverThe methods to terminate the ZL40200 LVPECL drivers are shown in the following figures.Figure 15 - LVPECL Parallel Thevenin-Equivalent Output TerminationFigure 16 - LVPECL AC Output Termination for Externally Terminated LVPECL InputsFigure 17 - LVPECL AC Output Termination for Internally Terminated LVPECL InputsFigure 18 - LVPECL AC-Coupled Output Termination for CML Inputs3.3 Device Additive JitterThe ZL40200 clock fan out buffer is not intended to filter clock jitter. The jitter performance of this type of device is characterized by its additive jitter. Additive jitter is the jitter the device would add to a hypothetical jitter-free clock as it passes through the device. The additive jitter of the ZL40200 is random and as such it is not correlated to the jitter of the input clock signal.The square of the resultant random RMS jitter at the output of the ZL40200 is equal to the sum of the squares of the various random RMS jitter sources including: input clock jitter; additive jitter of the buffer; and additive jitter due to power supply noise. There may be additional deterministic jitter sources that are not shown in Figure 19.Figure 19 - Additive Jitter3.4 Power SupplyThis device operates with either a 2.5V supply or 3.3V supply.3.4.1 Sensitivity to power supply noisePower supply noise from sources such as switching power supplies and high-power digital components such as FPGAs can induce additive jitter on clock buffer outputs. The ZL40200 is equipped with a low drop out (LDO) power regulator and on-chip bulk capacitors to minimize additive jitter due to power supply noise. The LDO regulator on the ZL40200 allows this device to have superior performance even in the presence of external noise sources. The on-chip regulation, recommended power supply filtering, and good PCB layout all work together to minimize the additive jitter from power supply noise.The performance of these clock buffers in the presence of power supply noise is detailed in ZLAN-403, “Power Supply Rejection in Clock Buffers” which is available from Applications Engineering.3.4.2 Power supply filteringFor optimal jitter performance, the device should be isolated from the power planes connected to its power supply pins as shown in Figure 20.•10 µF capacitors should be size 0603 or size 0805 X5R or X7R ceramic, 6.3 V minimum rating•0.1 µF capacitors should be size 0402 X5R ceramic, 6.3 V minimum rating•Capacitors should be placed next to the connected device power pins• a 0.3 Ohm resistor is recommended for the filter shown in Figure 20Figure 20 - Decoupling Connections for Power Pins3.4.3 PCB layout considerationsThe power nets in Figure 20 can be implemented either as a plane island or routed power topology without changing the overall jitter performance of the device.Absolute Maximum Ratings*Parameter Sym.Min.Max.Units 1Supply voltage V DD_R-0.5 4.6V 2Voltage on any digital pin V PIN-0.5V DD V 3LVPECL output current I out30mA 4Soldering temperature T260 °C 5Storage temperature T ST-55125 °C 6Junction temperature T j125 °C 7Voltage on input pin V input V DD V 8Input capacitance each pin C p500fF 4.0 AC and DC Electrical Characteristics* Exceeding these values may cause permanent damage. Functional operation under these conditions is not implied.* Voltages are with respect to ground (GND) unless otherwise statedRecommended Operating Conditions*Characteristics Sym.Min.Typ.Max.Units1Supply voltage 2.5 V mode V DD25 2.375 2.5 2.625V2Supply voltage 3.3 V mode V DD33 3.135 3.3 3.465V3Operating temperature T A-402585°C* Voltages are with respect to ground (GND) unless otherwise statedDC Electrical Characteristics - Current ConsumptionCharacteristics Sym.Min.Typ.Max.Units Notes 1Supply current LVPECL drivers -unloadedI dd_unload49mA Unloaded2Supply current LVPECL drivers - loaded (all outputs are active)I dd_load88mA Including powerto R L = 50DC Electrical Characteristics - Inputs and Outputs - for 3.3 V SupplyCharacteristics Sym.Min.Typ.Max.Units Notes 1Differential input common modevoltageV CM 1.1 2.0V2Differential input voltage difference V ID0.251V3LVPECL output high voltage V OH V DD-1.40V Measured at 10MHz4LVPECL output low voltage V OL V DD-1.62V Measured at 10MHz*The VOD parameter was measured from 125 MHz to 750 MHz.*The VOD parameter was measured from 125 MHz to 750 MHz.Figure 21 - Differential Voltage Parameter*Supply voltage and operating temperature are as per Recommended Operating Conditions5LVPECL output differential voltageV OD0.50.9VDC Electrical Characteristics - Inputs and Outputs - for 2.5 V SupplyCharacteristicsSym.Min.Typ.Max.Units Notes1Differential input common mode voltageV CM 1.1 1.6V 2Differential input voltage difference V ID 0.251V 3LVPECL output high voltage V OH V DD -1.40V 4LVPECL output low voltage V OL V DD -1.62V 5LVPECL output differential voltage*V OD0.40.9VAC Electrical Characteristics* - Inputs and Outputs (see Figure 22) - for 3.3 V supply.CharacteristicsSym.Min.Typ.Max.Units Notes1Maximum Operating Frequency 1/t p 750MHz 2input to output clock propagation delay t pd 012ns 3output to output skew t out2out 50100ps 4part to part output skewt part2part 80300ps 5Output clock Duty Cycle degradation t PWH / t PWL-2%0%2%Duty Cycle 6LVPECL Output Slew Rater sk0.75 1.2V/nsDC Electrical Characteristics - Inputs and Outputs - for 3.3 V SupplyCharacteristicsSym.Min.Typ.Max.Units NotesAC Electrical Characteristics* - Inputs and Outputs (see Figure 22) - for 2.5 V supply.Characteristics Sym.Min.Typ.Max.Units Notes 1Maximum Operating Frequency1/t p750MHz2input to output clock propagation delay t pd012ns3output to output skew t out2out50100ps4part to part output skew t part2part80300ps5Output clock Duty Cycle degradation t PWH/ t PWL-202Percent6LVPECL Output Slew Rate r sk0.75 1.2ps* Supply voltage and operating temperature are as per Recommended Operating ConditionsInputt Pt PWL t pdt PWHOutputFigure 22 - Input To Output TimingAdditive Jitter at 2.5 V*Output Frequency (MHz)Jitter MeasurementFilterTypical RMS (fs)Notes112512 kHz - 20 MHz 1122212.512 kHz - 20 MHz 803311.0412 kHz - 20 MHz 70442512 kHz - 20 MHz 65550012 kHz - 20 MHz 566622.0812 kHz - 20 MHz 43775012 kHz - 20 MHz39Additive Jitter at 3.3 V*Output Frequency (MHz)Jitter MeasurementFilterTypical RMS (fs)Notes112512 kHz - 20 MHz 1122212.512 kHz - 20 MHz 823311.0412 kHz - 20 MHz 72442512 kHz - 20 MHz 63550012 kHz - 20 MHz 526622.0812 kHz - 20 MHz 43775012 kHz - 20 MHz395.0 Performance Characterization*The values in this table were taken with an approximate slew rate of 0.8 V/ns.*The values in this table were taken with an approximate slew rate of 0.8 V/ns.* The values in this table are the additive periodic jitter caused by an interfering tone typically caused by a switching power supply. For this test, measurements were taken over the full temperature and voltage range for V DD = 3.3 V. The magnitude of the interfering tone is measured at the DUT.Additive Jitter from a Power Supply Tone*CarrierFrequency (MHz)ParameterTypicalUnitsNotes125MHz 25 mV at 100 kHz 159fs RMS 750MHz25 mV at 100 kHz82fs RMS6.0 Typical BehaviorTypical Phase Noise at 622.08 MHzTypical Waveform at 155.52 MHzInput Slew Rate versus Additive Jitter Propagation Delay versus TemperatureNote:This is for a single device. For more details see thecharacterization section.V ODversus FrequencyPower Supply Tone Magnitude versus PSRR (at 100 kHz) at 125 MHz Power Supply Tone Magnitude versus Additive Jitter (at 100 kHz) at 125 MHzPower Supply Tone Frequency (at 25 mV) versus PSRR at 125 MHz Power Supply Tone Frequency (at 25 mV) versus Additive Jitter at 125 MHz7.0 Package Thermal Characteristics*Proper thermal management must be practiced to ensure that T jmax is not exceeded.Thermal DataParameterSymbolTest ConditionValue UnitJunction to Ambient Thermal ResistanceΘJAStill Air 1 m/s 2 m/s 67.961.658.1oC/WJunction to Case Thermal Resistance ΘJC Still Air 44.1o C/W Junction to Board Thermal Resistance ΘJB Still Air23.2oC/WMaximum Junction Temperature*T jmax 125o C Maximum Ambient TemperatureT A85oC© 2014 Microsemi Corporation. All rights reserved. Microsemi and the Microsemi logo are trademarks of Microsemi Corporation. All other trademarks and service marks are the property of their respective owners.Microsemi Corporation (NASDAQ: MSCC) offers a comprehensive portfolio of semiconductor and system solutions for communications, defense and security, aerospace and industrial markets. Products include high-performance and radiation-hardened analog mixed-signal integrated circuits, FPGAs, SoCs and ASICs; power management products; timing and synchronization devices and precise time solutions, setting the world’s standard for time; voice processing devices; RF solutions; discrete components; security technologies and scalable anti-tamper products; Power-over-Ethernet ICs and midspans; as well as custom design capabilities and services. Microsemi is headquartered in Aliso Viejo, Calif. and has approximately 3,400 employees globally. Learn more at .Microsemi Corporate Headquarters One One Enterprise, Aliso Viejo CA 92656 USA Within the USA: +1 (800) 713-4113Outside the USA: +1 (949) 380-6100Sales: +1 (949) 380-6136Fax: +1 (949) 215-4996E-mail: ***************************Information relating to products and services furnished herein by Microsemi Corporation or its subsidiaries (collectively “Microsemi”) is believed to be reliable. However, Microsemi assumes no liability for errors that may appear in this publication, or for liability otherwise arising from the application or use of any such information, product or service or for any infringement of patents or other intellectual property rights owned by third parties which may result from such application or use. Neither the supply of such information or purchase of product or service conveys any license, either express or implied, under patents or other intellectual property rights owned by Microsemi or licensed from third parties by Microsemi, whatsoever. Purchasers of products are also hereby notified that the use of product in certain ways or in combination with Microsemi, or non-Microsemi furnished goods or services may infringe patents or other intellectual property rights owned by Microsemi.This publication is issued to provide information only and (unless agreed by Microsemi in writing) may not be used, applied or reproduced for any purpose nor form part of any order or contract nor to be regarded as a representation relating to the products or services concerned. The products, their specifications, services and other information appearing in this publication are subject to change by Microsemi without notice. No warranty or guarantee express or implied is made regarding the capability, performance or suitability of any product or service. Information concerning possible methods of use is provided as a guide only and does not constitute any guarantee that such methods of use will be satisfactory in a specific piece of equipment. It is the user’s responsibility to fully determine the performance and suitability of any equipment using such information and to ensure that any publication or data used is up to date and has not been superseded. Manufacturing does not necessarily include testing of all functions or parameters. These products are not suitable for use in any medical and other products whose failure to perform may result in significant injury or death to the user. All products and materials are sold and services provided subject to Microsemi’s conditions of sale which are available on request.For more information about all Microsemi productsvisit our website at TECHNICAL DOCUMENTATION – NOT FOR RESALE。

QD77MS16定位例子教学教材

Q D77M S16定位例子QD77MS16定位例子这里是为了方便,是用WORKS2写定位标识符那些(也可以用顺控写),直接把位置和速度写入缓存区,把定位数据和速度数据写入缓存区,可以在说明书上找,但是QD77MS16还有一个好处就是可以在软件上找,打开MR configurator2软件,版本不能低于1.130L,然后依次在界面左上方点击“帮助”,“缓冲存储地址一览表”可以看到。

QD75或者QD70是没有的。

M12 ON时数据定位。

上面程序用到块定位当M13 ON时。

启用块定位时,必须要写入7000到g4300,时启动块定位标识,g4301是定位块的启动点,用哪个就写入哪个,这里是用第一个。

上面是点动程序,77ms2和77ms4是用Y8和Y9启动,77ms16是用缓存地址启动点动。

原点复位程序。

轴启动程序,原点复位,数据定位,块定位都是Y10启动。

查看状态,M50后面相应的点对象相应的内容,具体查看说明书的缓存地址的G2417解释。

当前的状态,有无报警都可以监控。

所有轴的伺服准备和伺服ON都是Y0和Y1控制,也就是Y0和Y1接通后,所有轴的伺服准备和伺服ON都接通。

如果要分别控制,就要查看说明书的缓冲存储地址,这里不多说明。

前后限位和近点狗等外部输入功能是缓冲存储地址G5928的位控制,还是一句话,看说明书。

此处,停止和重启程序,当电机运行时,需要暂时停下来,但是暂停解除后,要求把剩余的距离走完,此处可以用重启功能。

但是当出现了某些错误后,重启功能无效,具体参考说明书重启那一节的讲解。

监控当前位置和当前速度。

监控错误报警,报警依次分为轴号报警,模块报警,伺服报警三个。

(1)这是在works2上写的定位数据,当执行NO.1动作时,因为是连续轨迹运动,停止时必须要走到第一个结束的定位数据号,此处第一个结束的定位数据号NO.2,所以运动轨迹是执行NO.1完成后,速度不减为0,而直接跳到NO.2的速度,执行完NO.2的定位才停止。

三菱QD75系列地址表

470 471 472 473 474 475 476 477 478 479 480 481 482

109页

double word word word double word

111页

word word word word word

113页

word word word

184 186 187 188 189

加速时间 1000 减速时间 减速时间 减速时间 JOG 速度极限值 JOG 运行加速时间选择 JOG 运行减速时间选择 加速/减速处理选择 S 形比例 突然停止减速时间 停止组 1 突然停止选择 停止组 2 突然停止选择 停止组 3 突然停止选择 定位完成信号输出时间 容许环形插补出错宽度 300 100 0 20000 0 0 0 100 1000

340 341 342 343 344 345 346 347 348 349 350 351 352 353 354 355 356 357 358 359 360 361

490 491 492 493 494 495 496 497 498 499 500 501 502 503 504 505 506 507 508 509 510 511 123页 117页

定位参数的设置项目 必须设 置

默认值

Pr.1 Pr.2 基 本 参 数 1 Pr.3 Pr.4 Pr.5 Pr.6 Pr.7 基 本 参 数 2 Pr.8 Pr.9 Pr.10 Pr.11 Pr.12

单位设置 每一转的脉冲数( Ap) (单位:脉冲) 每一转的位移量( Al) 单位放大倍率( Am) 脉冲输出模式 旋转方向设置 起动时的偏置速度 速度极限值 加速时间 0 减速时间 0 反向间隙补偿量 软件行程极限上限值

微赛米精密LVDS双倍输出缓冲器数据手册说明书

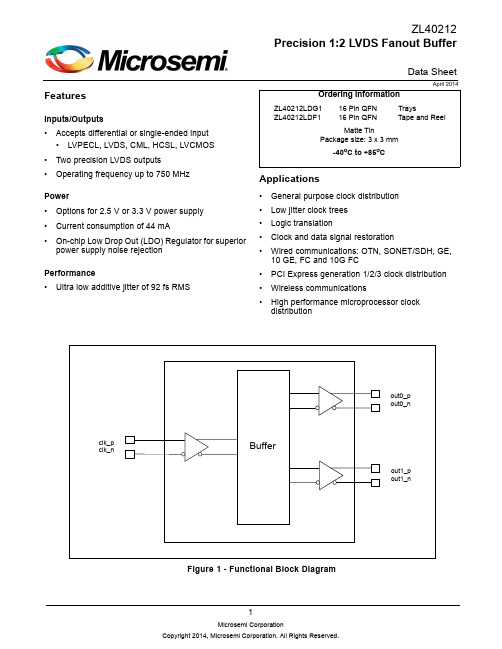

1FeaturesInputs/Outputs •Accepts differential or single-ended input •LVPECL, LVDS, CML, HCSL, LVCMOS •Two precision LVDS outputs •Operating frequency up to 750 MHzPower •Options for 2.5 V or 3.3 V power supply •Current consumption of 44 mA•On-chip Low Drop Out (LDO) Regulator for superior power supply noise rejectionPerformance •Ultra low additive jitter of 92 fs RMSApplications•General purpose clock distribution •Low jitter clock trees •Logic translation•Clock and data signal restoration•Wired communications: OTN, SONET/SDH, GE, 10 GE, FC and 10G FC•PCI Express generation 1/2/3 clock distribution •Wireless communications•High performance microprocessor clock distributionApril 2014Figure 1 - Functional Block DiagramZL40212Precision 1:2 LVDS Fanout BufferData SheetOrdering InformationZL40212LDG1 16 Pin QFN TraysZL40212LDF116 Pin QFNTape and ReelMatte TinPackage size: 3 x 3 mm-40o C to +85o CTable of ContentsFeatures . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1 Inputs/Outputs . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .1 Power . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .1 Performance . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .1 Applications . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1 Change Summary . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 41.0 Package Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .52.0 Pin Description. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .53.0 Functional Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .63.1 Clock Inputs. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .63.2 Clock Outputs . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .113.3 Device Additive Jitter. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .143.4 Power Supply . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .153.4.1 Sensitivity to power supply noise. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .153.4.2 Power supply filtering. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .153.4.3 PCB layout considerations. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .154.0 AC and DC Electrical Characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .165.0 Performance Characterization . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .186.0 Typical Behavior . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .197.0 Package Thermal Characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .208.0 Mechanical Drawing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .21List of FiguresFigure 1 - Functional Block Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1 Figure 2 - Pin Connections . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5 Figure 3 - LVPECL Input DC Coupled Thevenin Equivalent . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6 Figure 4 - LVPECL Input DC Coupled Parallel Termination. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7 Figure 5 - LVPECL Input AC Coupled Termination . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7 Figure 6 - LVDS Input DC Coupled . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8 Figure 7 - LVDS Input AC Coupled . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8 Figure 8 - CML Input AC Coupled . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9 Figure 9 - HCSL Input AC Coupled . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9 Figure 10 - CMOS Input DC Coupled Referenced to VDD/2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10 Figure 11 - CMOS Input DC Coupled Referenced to Ground . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10 Figure 12 - Simplified LVDS Output Driver. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11 Figure 13 - LVDS DC Coupled Termination (Internal Receiver Termination). . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11 Figure 14 - LVDS DC Coupled Termination (External Receiver Termination) . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12 Figure 15 - LVDS AC Coupled Termination . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12 Figure 16 - LVDS AC Output Termination for CML Inputs . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13 Figure 17 - Additive Jitter. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14 Figure 18 - Decoupling Connections for Power Pins. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 15 Figure 19 - Differential Voltage Parameter. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 17 Figure 20 - Input To Output Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 17Change SummaryBelow are the changes from the February 2013 issue to the April 2014 issue:Page Item Change1Applications Added PCI Express clock distribution.5Pin Description Added exposed pad to Pin Description.6, 7Figure 3 and Figure 4Removed 22 ohm series resistors from Figure 3 and 4. Theseresistors are not required; however, there is no impact toperformance if the resistors are included.17Figure 19Clarification of V ID and V OD.Below are the changes from the November 2012 issue to the February 2013 issue:Page Item Change7Figure 4Changed text to indicate the circuit is not recommended forVDD_driver=2.5V.7Figure 5Changed pull-up and pull-down resistors from 2kOhm to100Ohm.11Figure 12Changed gate values to +/+ on the left and -/- on the right.The device is packaged in a 16 pin QFN1416642NCvddNCN Cc l k _pvddgndNCo u t 1_no u t 1_po u t 0_n81210o u t 0_pc l k _nN CNCgndFigure 2 - Pin Connections2.0 Pin DescriptionPin # Name Description1, 4clk_p, clk_n,Differential Input (Analog Input). Differential (or singled ended) input signals. For all input signal configuration see “Clock Inputs” on page 612, 11, 10, 9out0_p, out0_n out1_p, out1_n Differential Output (Analog Output). Differential outputs.8, 13vdd Positive Supply Voltage. 2.5 V DC or 3.3 V DC nominal.5, 16gnd Ground. 0 V.2, 3, 6, 7, 14, 15NCNo Connection. Leave unconnected.Exposed Pad Device GND.The ZL40212 is an LVDS clock fanout buffer with two identical output clock drivers capable of operating at frequencies up to 750MHz.Inputs to the ZL40212 are externally terminated to allow use of precision termination components and to allow full flexibility of input termination. The ZL40212 can accept DC coupled LVPECL or LVDS and AC coupled LVPECL, LVDS, CML or HCSL input signals; single ended input signals can also be accepted. A pin compatible device with internal termination is also available.The ZL40212 is designed to fan out low-jitter reference clocks for wired or optical communications applications while adding minimal jitter to the clock signal. An internal linear power supply regulator and bulk capacitors minimize additive jitter due to power supply noise. The device operates from 2.5V+/-5% or 3.3V+/-5% supply. Its operation is guaranteed over the industrial temperature range -40°C to +85°C.The device block diagram is shown in Figure 1; its operation is described in the following sections.3.1 Clock InputsThe ZL40212 is adaptable to support different types of differential and single-ended input signals depending on the passive components used in the input termination. The application diagrams in the following figures allow the ZL40212 to accept LVPECL, LVDS, CML, HCSL and single-ended inputs.Figure 3 - LVPECL Input DC Coupled Thevenin EquivalentFigure 4 - LVPECL Input DC Coupled Parallel TerminationFigure 5 - LVPECL Input AC Coupled TerminationFigure 6 - LVDS Input DC CoupledFigure 7 - LVDS Input AC CoupledFigure 8 - CML Input AC CoupledFigure 9 - HCSL Input AC CoupledFigure 10 - CMOS Input DC Coupled Referenced to VDD/2Figure 11 - CMOS Input DC Coupled Referenced to GroundVDD_driver R1 (kΩ)R2 (kΩ)R3 (kΩ)RA (kΩ) C (pF) 1.5 1.25 3.075open10101.81 3.8open10102.50.33 4.2open10103.30.75open4.21010Table 1 - Component Values for Single Ended Input Reference to Ground * For frequencies below 100 MHz, increase C to avoid signal integrity issues.3.2 Clock OutputsLVDS has lower signal swing than LVPECL which results in a low power consumption. A simplified diagram for the LVDS output stage is shown in Figure 12.Figure 12 - Simplified LVDS Output DriverThe methods to terminate the ZL40212 drivers are shown in the following figures.Figure 15 - LVDS AC Coupled TerminationFigure 16 - LVDS AC Output Termination for CML Inputs3.3 Device Additive JitterThe ZL40212 clock fanout buffer is not intended to filter clock jitter. The jitter performance of this type of device is characterized by its additive jitter. Additive jitter is the jitter the device would add to a hypothetical jitter-free clock as it passes through the device. The additive jitter of the ZL40212 is random and as such it is not correlated to the jitter of the input clock signal.The square of the resultant random RMS jitter at the output of the ZL40212 is equal to the sum of the squares of the various random RMS jitter sources including: input clock jitter; additive jitter of the buffer; and additive jitter due to power supply noise. There may be additional deterministic jitter sources, but they are not shown in Figure 17.Figure 17 - Additive Jitter3.4 Power SupplyThis device operates with either a 2.5V supply or 3.3V supply.3.4.1 Sensitivity to power supply noisePower supply noise from sources such as switching power supplies and high-power digital components such as FPGAs can induce additive jitter on clock buffer outputs. The ZL40212 is equipped with a low drop out (LDO) power regulator and on-chip bulk capacitors to minimize additive jitter due to power supply noise. The LDO regulator on the ZL40212 allows this device to have superior performance even in the presence of external noise sources. The on-chip regulation, recommended power supply filtering, and good PCB layout all work together to minimize the additive jitter from power supply noise.The performance of these clock buffers in the presence of power supply noise is detailed in ZLAN-403, “Power Supply Rejection in Clock Buffers” which is available from Applications Engineering.3.4.2 Power supply filteringFor optimal jitter performance, the device should be isolated from the power planes connected to its power supply pins as shown in Figure 18.•10 µF capacitors should be size 0603 or size 0805 X5R or X7R ceramic, 6.3 V minimum rating•0.1 µF capacitors should be size 0402 X5R ceramic, 6.3 V minimum rating•Capacitors should be placed next to the connected device power pins• a 0.3 Ohm resistor is recommended for the filter shown in Figure 18Figure 18 - Decoupling Connections for Power Pins3.4.3 PCB layout considerationsThe power nets in Figure 18 can be implemented either as a plane island or routed power topology without changing the overall jitter performance of the device.4.0 AC and DC Electrical CharacteristicsAbsolute Maximum Ratings*Parameter Sym.Min.Max.Units 1Supply voltage V DD_R-0.5 4.6V 2Voltage on any digital pin V PIN-0.5V DD V 3Soldering temperature T260 °C 4Storage temperature T ST-55125 °C 5Junction temperature T j125 °C 6Voltage on input pin V input V DD V 7Input capacitance each pin C p500fF * Exceeding these values may cause permanent damage. Functional operation under these conditions is not implied.* Voltages are with respect to ground (GND) unless otherwise statedRecommended Operating Conditions*Characteristics Sym.Min.Typ.Max.Units 1Supply voltage 2.5 V mode V DD25 2.375 2.5 2.625V 2Supply voltage 3.3 V mode V DD33 3.135 3.3 3.465V 3Operating temperature T A-402585°C* Voltages are with respect to ground (GND) unless otherwise statedDC Electrical Characteristics - Current ConsumptionCharacteristics Sym.Min.Typ.Max.Units Notes 1Supply current LVDS drivers - loadedI dd_load44mA(all outputs are active)DC Electrical Characteristics - Inputs and Outputs - for 2.5/3.3 V SupplyCharacteristics Sym.Min.Typ.Max.Units Notes1Differential input common modeV ICM 1.1 1.6V for 2.5 V voltageV ICM 1.1 2.0V for 3.3 V2Differential input common modevoltage3Differential input voltage V ID0.251V4LVDS output differential voltage*V OD0.250.300.40V5LVDS output common mode voltage V CM 1.1 1.25 1.375V* The VOD parameter was measured from 125 to 750 MHz.AC Electrical Characteristics* - Inputs and Outputs (see Figure 20) - for 2.5/3.3 V supply.Characteristics Sym.Min.Typ.Max.Units Notes 1Maximum Operating Frequency1/t p750MHz2Input to output clock propagation delay t pd012ns3Output to output skew t out2out50100ps4Part to part output skew t part2part80300ps5Output clock Duty Cycle degradation t PWH/ t PWL-505Percent6LVDS Output clock slew rate r sl0.55V/nsFigure 19 - Differential Voltage Parameter* Supply voltage and operating temperature are as per Recommended Operating ConditionsInputt Pt PWL t pdt PWHOutputFigure 20 - Input To Output TimingAdditive Jitter at 2.5 V*Output Frequency (MHz)Jitter MeasurementFilterTypical (fs)Notes112512 kHz - 20 MHz 1342212.512 kHz - 20 MHz 1203311.0412 kHz - 20 MHz 104442512 kHz - 20 MHz 105550012 kHz - 20 MHz 916622.0812 kHz - 20 MHz 91775012 kHz - 20 MHz92Additive Jitter at 3.3 V*Output Frequency (MHz)Jitter MeasurementFilterTypical (fs)Notes112512 kHz - 20 MHz 1352212.512 kHz - 20 MHz 1223311.0412 kHz - 20 MHz 106442512 kHz - 20 MHz 106550012 kHz - 20 MHz 946622.0812 kHz - 20 MHz 92775012 kHz - 20 MHz935.0 Performance Characterization*The values in this table were taken with an approximate input slew rate of 0.8 V/ns*The values in this table were taken with an approximate input slew rate of 0.8 V/nsAdditive Jitter from a Power Supply Tone*Carrier frequency Parameter Typical Units Notes125MHz 25 mV at 100 kHz 48fs RMS 750MHz25 mV at 100 kHz53fs RMS* The values in this table are the additive periodic jitter caused by an interfering tone typically caused by a switching power supply. For this test, measurements were taken over the full temperature and voltage range for V DD = 3.3 V. The magnitude of the interfering tone is measured at the DUT.6.0 Typical BehaviorTypical Waveform at 155.52 MHzV OD versus FrequencyPower Supply Tone Frequency versus PSRRPower Supply Tone Magnitude versus PSRRPropagation Delay versus TemperatureNote:This is for a single device. For more details see the characterization section.7.0 Package Thermal Characteristics* Proper thermal management must be practiced to ensure that T jmax is not exceeded.Thermal DataParameterSymbol Test ConditionValue UnitJunction to Ambient Thermal ResistanceΘJAStill Air 1 m/s 2 m/s 67.961.658.1oC/WJunction to Case Thermal Resistance ΘJC Still Air 44.1o C/W Junction to Board Thermal Resistance ΘJB Still Air23.2oC/WMaximum Junction Temperature*T jmax 125o C Maximum Ambient TemperatureT A85oCZL40212 Data Sheet 8.0 Mechanical Drawing21Microsemi Corporation© 2014 Microsemi Corporation. All rights reserved. Microsemi and the Microsemi logo are trademarks of Microsemi Corporation. All other trademarks and service marks are the property of their respective owners.Microsemi Corporation (NASDAQ: MSCC) offers a comprehensive portfolio of semiconductor and system solutions for communications, defense and security, aerospace and industrial markets. Products include high-performance and radiation-hardened analog mixed-signal integrated circuits, FPGAs, SoCs and ASICs; power management products; timing and synchronization devices and precise time solutions, setting the world’s standard for time; voice processing devices; RF solutions; discrete components; security technologies and scalable anti-tamper products; Power-over-Ethernet ICs and midspans; as well as custom design capabilities and services. Microsemi is headquartered in Aliso Viejo, Calif. and has approximately 3,400 employees globally. Learn more at .Microsemi Corporate Headquarters OneOne Enterprise, Aliso Viejo CA 92656 USAWithin the USA: +1 (800) 713-4113Outside the USA: +1 (949) 380-6100Sales: +1 (949) 380-6136Fax: +1 (949) 215-4996E-mail: ***************************ZL40212Information relating to products and services furnished herein by Microsemi Corporation or its subsidiaries (collectively “Microsemi”) is believed to be reliable. However, Microsemi assumes no liability for errors that may appear in this publication, or for liability otherwise arising from the application or use of any such information, product or service or for any infringement of patents or other intellectual property rights owned by third parties which may result from such application or use. Neither the supply of such information or purchase of product or service conveys any license, either express or implied, under patents or other intellectual property rights owned by Microsemi or licensed from third parties by Microsemi, whatsoever. Purchasers of products are also hereby notified that the use of product in certain ways or in combination with Microsemi, or non-Microsemi furnished goods or services may infringe patents or other intellectual property rights owned by Microsemi.This publication is issued to provide information only and (unless agreed by Microsemi in writing) may not be used, applied or reproduced for any purpose nor form part of any order or contract nor to be regarded as a representation relating to the products or services concerned. The products, their specifications, services and other information appearing in this publication are subject to change by Microsemi without notice. No warranty or guarantee express or implied is made regarding the capability, performance or suitability of any product or service. Information concerning possible methods of use is provided as a guide only and does not constitute any guarantee that such methods of use will be satisfactory in a specific piece of equipment. It is the user’s responsibility to fully determine the performance and suitability of any equipment using such information and to ensure that any publication or data used is up to date and has not been superseded. Manufacturing does not necessarily include testing of all functions or parameters. These products are not suitable for use in any medical and other products whose failure to perform may result in significant injury or death to the user. All products and materials are sold and services provided subject to Microsemi’s conditions of sale which are available on request.For more information about all Microsemi productsvisit our website atTECHNICAL DOCUMENTATION – NOT FOR RESALE。

上海欧际 液压软管 样本

公司全系列生产符合 ISO、DIN、JIS 标准的管路附件。符合 GB、GB/T、JB/ZQ、 JB、JB/T 等国家或行业标准的系列管路附件,旋转接头、快换接头、不锈钢金属 软管总成、液压胶管总成、铠装液压胶管总成、干稀油润滑设备。设计生产各种 非标的管路附件、液压系统等。

如:25-200(16M3K)-2000 B1+N-R1=B3+N-φ30*3 0° K1 S 7、当对胶管接头的型式没有严格要求时,用户可只提供外接口尺寸订货,

如:25-200-2000 N-R1= N-φ30*3 以上型号表示一端为外螺纹 R1,另一端为φ30*3 与钢管焊接。 我方将首选 24°锥 O 形圈密封胶管接头提供给用户。 8、为了代号的统一性,本样本中胶管接头的代号延用了灰色样本中的代号。 9、过渡接头的代号(如 N-R、N-G 等)在样本中重复使用,它不具体代表哪一类过渡接头,而 表示外接口的形式:

12 8 160 180 275 180 425 230

165 178 280 178

350 178 420 178 210 89 280 89

16 10 130 200 250 200 400 250 450 250 135 203 255 203

280 102 350 203 420 203 210 102 280 102

2

有限公司,中国二重集团(德阳)重型装备有限责任公司,大连重工集团有限公 司,大连华锐股份有限公司,上海重型机器厂有限公司,中华沪船新事业发展有 限公司,沈阳重型机器有限责任公司,陕西液压设备厂,宝钢集团常州冶金机械 厂、苏州冶金机械厂,衡冶重型机械有限公司,西安冶金机械有限公司,太原矿 山机械集团有限公司,济南重工股份有限公司等全国大型主机厂。公司产品出厂 合格率为 99.8%已在全国 19 个省市(自治区)66 个大型冶金及主机企业中占有一 席之地,抽样调查客户满意率为 99%,赢得了冶金企业,主机行业的国内外专家 及监制商的认可和好评。

QD77缓冲区参数表

Cd.148 连续运行控制模式时加速时间 Cd.149 连续运行控制模式时减速时间 Cd.150 连续运行控制模式时目标转矩 Cd.151 连续运行控制模式时转矩时间常数 Cd.152 连续运行控制模式时转矩时间常数 Cd.153 连续运行控制模式时切换条件

Cd.154 连续运行控制模式时切换条件参数

Un\G4300 Un\G4301 Un\G4302 Un\G4303 Un\G4304 Un\G4305 Un\G4306 Un\G4307 Un\G4308 Un\G4309 Un\G4310 Un\G4311 Un\G4312 Un\G4313 Un\G4314

Un\G1515 Un\G1516 Un\G1517 Un\G1518

Cd.24 速度·位置切换允许标志 Cd.25 位置·速度切换控制速度更改寄存器

Cd.26 位置·速度切换允许标志 Cd.27 目标位置更改值 ( 地址)

Cd.28 目标位置更改值 ( 速度)

Cd.29 Cd.43 Cd.30

Cd.31

Cd.32

Cd.33

Cd.34 Cd.35 Cd.36 Cd.37 Cd.38 Cd.39

同时启动对象轴 3启动数据号 步模式 步有效标志 步启动信息 跳过指令 示教数据选择 示教定位数据号

QD77MS2 Un\G1900 Un\G1901 Un\G1905 Un\G1907 Un\G1926

Un\G1928

Un\G1909 Un\G1932

QD77MS2 Un\G1500 Un\G1501 Un\G1502 Un\G1503 Un\G1504 Un\G1505 Un\G1506 Un\G1507 Un\G1508 Un\G1509 Un\G1510 Un\G1511 Un\G1512 Un\G1513 Un\G1514 Un\G1515 Un\G1516 Un\G1517 Un\G1518 Un\G1519 Un\G1520 Un\G1521 Un\G1522 Un\G1523 Un\G1524 Un\G1525 Un\G1526 Un\G1527 Un\G1528 Un\G1530 Un\G1531 Un\G1532 Un\G1534 Un\G1535 Un\G1536 Un\G1537 Un\G1538

QD77缓冲区参数表

1

QD77GF16 Un\G4300 Un\G4301 Un\G4302 Un\G4303 Un\G4304 Un\G4305 Un\G4306 Un\G4307 Un\G4308 Un\G4309 Un\G4310 Un\G4311 Un\G4312 Un\G4313 Un\G4314 Un\G4315 Un\G4316 Un\G4317 Un\G4318 Un\G4319 Un\G4320 Un\G4321 Un\G4322 Un\G4323 Un\G4324 Un\G4325 Un\G4326 Un\G4327 Un\G4328 Un\G4330 Un\G4331 Un\G4332 Un\G4334 Un\G4335 Un\G4336 Un\G4337 Un\G4338 Un\G4339

Un\G4395

缓冲存储器地址Un\G■

QD77MS4

QD77MS16

-

Un\G30120

-

Un\G30121

-

Un\G30122

-

Un\G30123

轴号

QD77GF16 Un\G4351 Un\G4352

-

-

-

Un\G4359 Un\G4363 Un\G4364 Un\G4365 Un\G4374 Un\G4375 Un\G4376 Un\G4377 Un\G4378 Un\G4379 Un\G4380 Un\G4381 Un\G4382 Un\G4384 Un\G4385

Un\G1521

Un\G4321

Un\G1522

Un\G4322

Un\G1523

Un\G4323

Un\G1524

Un\G4324

Un\G1525

通力KDM参数表

通力KDM参数表设定LCE参数参看LCE用户界面菜单813131,更改任何参数时记录下它的原始值。

1.电梯处于RDF状态。

2.接通主电源。

3.设置1-71=3,使检修运行能到达端站平层位置。

4.设置1-62=0,取消消防功能。

5.设置1-77=0,取消照明监察。

6.设置1-95=1。

7.如果LCEOPT板连线未接,设置7-91=0。

8.设置1-60消防基站设置: 1……=电梯消防运行时返回的消防基站9.设置1-61地区代码:0=不用11=香港,(国内设置成香港模式)10.设置1-62消防类型:0=取消消防功能1=消防运行功能3=消防迫降功能,电梯停在消防楼层不能使用。

5=消防迫降 + 消防员可使用电梯。

11.关闭主电源,等待15秒钟后再接通主电源。

设定驱动参数以下步骤必须执行。

1.检查6-0显示的文档ID应与附件的参数表里的文档ID一致。

2.设置6-95=0,再设置6-98=1恢复默认参数。

3.设置马达型号6-60,参看下表。

设置马达型号会同时把6-6,6-33,6-61,6-64,6-66,4.参看电梯布局图,设置加速度6-2,额定速度6-3,额定载重6-4,曳引轮直径6-6(参看马达铭牌),绕绳比6-7。

5.预设置KTW/Q 6-25参数为2.8(行程<=30米)或5.0(行程<=80米)或8.0(行程<=240米)6.设置6-61,参看上表。

7.马达转一圈编码器脉冲数6-64是默认值。

8.6-80、6-81、6-82、6-83、6-84参看马达铭牌。

9.6-99设1保存参数。

检查编码器极性1.设置6-75=1,实时显示电梯速度(参看附件)。

并切换到实时显示模式下(在默认显示楼层时按“Select/Accept”键进入,按Menu键退出)。

2.手动松开制动器,空载轿厢应向上移动。

实时显示上的速度上行是正值,下行为负值。

3.如果极性反了,更改参数6-65值(比如1改为-1,或-1改为1)。

QD77MS16模块参数

信号名称对应地址轴一轴二轴三轴四轴五轴六轴七轴八可编程控制器就绪Y0全部伺服ON Y1准备完毕X0发脉冲置ON X10X11X12X13X14X15X16X17定位启动Y10Y11Y12Y13Y14Y15Y16Y17出错检测G 2417.D G 2517.D G 2617.D G 2717.D G 2817.D G 2917.D G3017.D G3117.D 启动完成G 2417.E G 2517.E G 2617.E G 2717.E G 2817.E G 2917.E G3017.E G3117.E 定位完成G 2417.F G 2517.F G 2617.F G 2717.F G 2817.F G 2917.F G3017.F G3117.F 轴停止G30100.0G30110.0G30120.0G30130.0G30140.0G30150.0G30160.0G30170.0JOG 正转G30101.0G30111.0G30121.0G30131.0G30141.0G30151.0G30161.0G30171.0JOG 反转G30102.0G30112.0G30122.0G30132.0G30142.0G30152.0G30162.0G30172.0信号名称对应地址轴九轴十轴十一轴十二轴十三轴十四轴十五轴十六可编程控制器就绪Y0全部伺服ON Y1准备完毕X0发脉冲置ON X18X19X1A X1B X1C X1D X1E X1F 定位启动Y18Y19Y1A Y1B Y1C Y1D Y1E Y1F 出错检测G3217.D G3317.D G3417.D G3517.D G3617.D G3717.D G3817.D G3917.D 启动完成G3217.E G3317.E G3417.E G3517.E G3617.E G3717.E G3817.E G3917.E 定位完成G3217.F G3317.F G3417.F G3517.F G3617.F G3717.F G3817.F G3917.F 轴停止G30180.0G30190.0G30200.0G30210.0G30220.0G30230.0G30240.0G30250.0JOG 正转G30181.0G30191.0G30201.0G30211.0G30221.0G30231.0G30241.0G30251.0JOG 反转G30182.0G30192.0G30202.0G30212.0G30222.0G30232.0G30242.0G30252.0QD77MS16手动数据表(1)项目设置值设置范围默认值设置值缓冲存储器地址轴一轴二轴三轴四轴五轴六轴七轴八JOG正转0至1 (状态)0G30101.0G30111.0G30121.0G30131.0G30141.0G30151.0G30161.0G30171.0 JOG反转0至1 (状态)0G30102.0G30112.0G30122.0G30132.0G30142.0G30152.0G30162.0G30172.0JOG速度JOG速度限制范围内0G4318G4319G4418G4419G4518G4519G4618G4619G4718G4719G4818G4819G4918G4919G5018G5019微动移动量0至65535 (pulse)0G4317G4417G4517G4617G4717G4817G4917G5017加速时间10至8388608(pulse)1000G36G37G186G187G336G337G486G487G636G637G786G787G936G937G1086G1087加速时间20至8388608(pulse)1000G38G39G188G189G338G339G488G489G638G639G788G789G938G939G1088G1089加速时间30至8388608(pulse)1000G40G41G190G191G340G341G490G491G640G641G790G791G940G941G1090G1091减速时间10至8388608(pulse)1000G42G43G192G193G342G343G492G493G642G643G792G793G942G943G1092G1093减速时间20至8388608(pulse)1000G44G45G194G195G344G345G494G495G644G645G794G795G944G945G1094G1095减速时间30至8388608(pulse)1000G46G47G196G197G346G347G496G497G646G647G796G797G946G947G1096G1097JOG速度限制0至200000(pulse)20000G48G49G198G199G348G349G498G499G648G649G798G799G948G949G1098G1099QD77MS16手动数据表(1)项目设置值设置范围默认值设置值缓冲存储器地址轴一轴二轴三轴四轴五轴六轴七轴八JOG运行加速时间选择K0:加速时间00G50G200G350G500G650G800G950G1100 K1:加速时间1K2:加速时间2K3:加速时间3JOG运行减速时间选择K0:减速时间00G51G201G351G501G651G801G951G1101 K1:减速时间1K2:减速时间2k3:减速时间3QD77MS16手动数据表(2)项目设置值设置范围默认值设置值缓冲存储器地址轴九轴十轴十一轴十二轴十三轴十四轴十五轴十六JOG正转0至1 (状态)0G30181.0G30191.0G30201.0G30211.0G30221.0G30231.0G30241.0G30251.0 JOG反转0至1 (状态)0G30182.0G30192.0G30202.0G30212.0G30222.0G30232.0G30242.0G30252.0JOG速度JOG速度限制范围内0G5118G5119G5218G5219G5318G5319G5418G5419G5518G5519G5618G5619G5718G5719G5818G5819微动移动量0至65535 (pulse)0G5117G5217G5317G5417G5517G5617G5717G5817加速时间10至8388608(pulse)1000G1236G1237G1386G1387G1536G1537G1686G1687G1836G1837G1986G1987G2136G2137G2286G2287加速时间20至8388608(pulse)1000G1238G1239G1388G1389G1538G1539G1688G1689G1838G1839G1988G1989G2138G2139G2288G2289加速时间30至8388608(pulse)1000G1240G1241G1390G1391G1540G1541G1690G1691G1840G1841G1990G1991G2140G2141G2290G2291减速时间10至8388608(pulse)1000G1242G1243G1392G1393G1542G1543G1692G1693G1842G1843G1992G1993G2142G2143G2292G2293减速时间20至8388608(pulse)1000G1244G1245G1394G1395G1544G1545G1694G1695G1844G1845G1994G1995G2144G2145G2294G2295减速时间30至8388608(pulse)1000G1246G1247G1396G1397G1546G1547G1696G1697G1846G1847G1996G1997G2146G2147G2296G2297JOG速度限制0至200000(pulse)20000G1248G1249G1398G1399G1548G1549G1698G1699G1848G1849G1998G1999G2148G2149G2298G2299QD77MS16手动数据表(2)项目设置值设置范围默认值设置值缓冲存储器地址轴九轴十轴十一轴十二轴十三轴十四轴十五轴十六JOG运行加速时间选择K0:加速时间00G1250G1400G1550G1700G1850G2000G2150G2300 K1:加速时间1K2:加速时间2K3:加速时间3JOG运行减速时间选择K0:减速时间00G1251G1401G1551G1701G1851G2001G2151G2301 K1:减速时间1K2:减速时间2k3:减速时间3QD77MS16OPR数据表格(1)项目设置值设置范围默认值设置值缓冲存储器地址轴一轴二轴三轴四轴五轴六轴七轴八回原方法K0:近点狗方法0G70G220G370G520G670G820G970G1120 K1:限位器1K2:限位器2K3:限位器3K4:计数1K5:计数2回原复归方向K0:正向0G71G221G371G521G671G821G971G1121 K1:反向原点完成地址-2147483648至2147483647(脉冲)0G72G73G222G223G372G373G522G523G672G673G822G823G972G973G1122G1123回原高速 1 至 200000 pulse/s1G74G75G224G225G374G375G524G525G674G675G824G825G974G975G1124G1125爬行速度 1 至 200000 pulse/s1G76G77G226G227G376G377G526G527G676G677G826G827G976G977G1126G1127原点复归重试K0:不通过极限开关进行原点复归重试0G78G228G378G528G678G828G978G1128 k1:通过极限开关进行原点复归重试QD77MS16OPR数据表格(1)项目设置值设置范围默认值设置值缓冲存储器地址轴一轴二轴三轴四轴五轴六轴七轴八近点狗ON后的移动量设置0~2147483647(pulse)0G80 G81G230G231G380G381G530G531G680G681G830G831G980G981G1130G1131原点复归加速时间选择K0:加速时间00G82G232G382G532G682G832G982G1132 K1:加速时间1K2:加速时间2K3:加速时间3原点复归减速时间选择K0:减速时间00G83G233G383G533G683G833G983G1133 K1:减速时间1K2:减速时间2k3:减速时间3QD77MS16OPR数据表格(2)项目设置值设置范围默认值设置值缓冲存储器地址轴九轴十轴十一轴十二轴十三轴十四轴十五轴十六回原方法K0:近点狗方法0G1270G1420G1570G1720G1870G2020G2170G2320 K1:限位器1K2:限位器2K3:限位器3K4:计数1K5:计数2回原复归方向K0:正向0G1271G1421G1571G1721G1871G2021G2171G2321 K1:反向原点完成地址-2147483648至2147483647(脉冲)0G1272G1273G1422G1423G1572G1573G1722G1723G1872G1873G2022G2023G2172G2173G2322G2323回原高速 1 至 200000 pulse/s1G1274G1275G1424G1425G1574G1575G1724G1725G18G674G1875G2024G2025G2174G2175G2324G2325爬行速度 1 至 200000 pulse/s1G1276G1277G1426G1427G1576G1577G1726G1727G1876G1877G2026G2027G2176G2177G2326G2327原点复归重试K0:不通过极限开关进行原点复归重试0G1278G1428G1578G1728G1878G2028G2178G2328 k1:通过极限开关进行原点复归重试QD77MS16OPR数据表格(2)项目设置值设置范围默认值设置值缓冲存储器地址轴九轴十轴十一轴十二轴十三轴十四轴十五轴十六近点狗ON后的移动量设置0~2147483647(pulse)0G1280G1281G1430G1431G1580G1581G1730G1731G1880G1881G2030G2031G2180G2181G2330G2331原点复归加速时间选择K0:加速时间00G1282G1432G1582G1732G1882G2032G2182G2332 K1:加速时间1K2:加速时间2K3:加速时间3原点复归减速时间选择K0:减速时间00G1283G1433G1583G1733G1883G2033G2183G2333 K1:减速时间1K2:减速时间2k3:减速时间3项目控制模式设置值默认值轴一轴二轴三轴四轴五轴六轴七轴八运行模式定位结束000000H G6000G7000G8000G9000G10000G11000G12000G13000连续定位控制01连续轨迹控制11控制方法ABS 直线 101H INC 直线02定距进给 103H 正转 速度 104H 反转 速度 105H 正转 速·位06H反转 速·位07H正转 位·速08H反转 位·速09HABS 直线 20AHINC 直线 20BH定距进给 20CHABS 圆弧插补0DH项目控制模式设置值默认值轴一轴二轴三轴四轴五轴六轴七轴八控制方法INC 圆弧插补0EH0000H G6000G7000G8000G9000G10000G11000G12000G13000 ABS 圆弧右0FHABS 圆弧左10HINC 圆弧右11HINC 圆弧左12H正转速度 213H反转速度 214HABS 直线 315HINC 直线 316H定距进给 317H正转速度 318H反转速度 319HABS 直线 41AHINC 直线 41BH定距进给 41CH正转速度 41DH项目控制模式设置值默认值轴一轴二轴三轴四轴五轴六轴七轴八控制方法反转 速度 41EH 0000H G6000G7000G8000G9000G10000G11000G12000G13000NOP80H 当前值更改81H JUMP 指令82H LOOP(次数)83H LEND84H 加速时间加速时间 000加速时间 101加速时间 110加速时间 311减速时间减速时间 000减速时间 101减速时间 210减速时间 311项目控制模式设置值默认值轴九轴十轴十一轴十二轴十三轴十四轴十五轴十六运行模式定位结束000000H G14000G15000G16000G17000G18000G19000G20000G21000连续定位控制01连续轨迹控制11控制方法ABS 直线 101H INC 直线02定距进给 103H 正转 速度 104H 反转 速度 105H 正转 速·位06H反转 速·位07H正转 位·速08H反转 位·速09HABS 直线 20AHINC 直线 20BH定距进给 20CHABS 圆弧插补0DH项目控制模式设置值默认值轴九轴十轴十一轴十二轴十三轴十四轴十五轴十六控制方法INC 圆弧插补0EH0000H G14000G15000G16000G17000G18000G19000G20000G21000 ABS 圆弧右0FHABS 圆弧左10HINC 圆弧右11HINC 圆弧左12H正转速度 213H反转速度 214HABS 直线 315HINC 直线 316H定距进给 317H正转速度 318H反转速度 319HABS 直线 41AHINC 直线 41BH定距进给 41CH正转速度 41DH项目控制模式设置值默认值轴九轴十轴十一轴十二轴十三轴十四轴十五轴十六控制方法反转 速度 41EH 0000H G14000G15000G16000G17000G18000G19000G20000G21000NOP80H 当前值更改81H JUMP 指令82H LOOP(次数)83H LEND84H 加速时间加速时间 000加速时间 101加速时间 110加速时间 311减速时间减速时间 000减速时间 101减速时间 210减速时间 311项目指定插补轴设置值默认值轴一轴二轴三轴四轴五轴六轴七轴八插补对象轴轴 1 指定0H0000H G6003G7003G8003G9003G10003G11003G12003G13003轴 2 指定1H轴 3 指定2H轴 4 指定3H轴 5 指定4H轴 6 指定5H轴 7 指定6H轴 8 指定7H轴 9 指定8H轴 10 指定9H轴 11 指定AH轴 12 指定BH轴 13 指定CH轴 14 指定DH轴 15 指定EH轴 16 指定FH项目指定插补轴设置值默认值轴九轴十轴十一轴十二轴十三轴十四轴十五轴十六插补对象轴轴 1 指定0H0000H G14003G15003G16003G17003G18003G19003G20003G21003轴 2 指定1H轴 3 指定2H轴 4 指定3H轴 5 指定4H轴 6 指定5H轴 7 指定6H轴 8 指定7H轴 9 指定8H轴 10 指定9H轴 11 指定AH轴 12 指定BH轴 13 指定CH轴 14 指定DH轴 15 指定EH轴 16 指定FH轴一启动编号定位编号运行模式控制方法加速时间减速时间插补对象指令速度定位地址圆弧地址G43001G6000G6003G6004 (双字)G6006 (双字)G6008 (双字) 2G6010G6013G6014 (双字)G6016 (双字)G6018 (双字) 3G6020G6023G6024 (双字)G6026 (双字)G6028 (双字) 4G6030G6033G6034 (双字)G6036 (双字)G6038 (双字) 5G6040G6043G6044 (双字)G6046 (双字)G6048 (双字) 6G6050G6053G6054 (双字)G6056 (双字)G6058 (双字) 7G6060G6063G6064 (双字)G6066 (双字)G6068 (双字) 8G6070G6073G6074 (双字)G6076 (双字)G6078 (双字) 9G6080G6083G6084 (双字)G6086 (双字)G6088 (双字) 10G6090G6093G6094 (双字)G6096 (双字)G6098 (双字)轴一启动编号定位编号运行模式控制方法加速时间减速时间插补对象指令速度定位地址圆弧地址G430011G6100G6103G6104 (双字)G6106 (双字)G6108 (双字) 12G6110G6113G6114 (双字)G6116 (双字)G6118 (双字) 13G6120G6123G6124 (双字)G6126 (双字)G6128 (双字) 14G6130G6133G6134 (双字)G6136 (双字)G6138 (双字) 15G6140G6143G6144 (双字)G6146 (双字)G6148 (双字) 16G6150G6153G6154 (双字)G6156 (双字)G6158 (双字) 17G6160G6163G6164 (双字)G6166 (双字)G6168 (双字) 18G6170G6173G6174 (双字)G6176 (双字)G6178 (双字) 19G6180G6183G6184 (双字)G6186 (双字)G6188 (双字) 20G6190G6193G6194 (双字)G6196 (双字)G6198 (双字)轴二启动编号定位编号运行模式控制方法加速时间减速时间插补对象指令速度定位地址圆弧地址G44001G7000G7003G7004 (双字)G7006 (双字)G7008 (双字) 2G7010G7013G7014 (双字)G7016 (双字)G7018 (双字) 3G7020G7023G7024 (双字)G7026 (双字)G7028 (双字) 4G7030G7033G7034 (双字)G7036 (双字)G7038 (双字) 5G7040G7043G7044 (双字)G7046 (双字)G7048 (双字) 6G7050G7053G7054 (双字)G7056 (双字)G7058 (双字) 7G7060G7063G7064 (双字)G7066 (双字)G7068 (双字) 8G7070G7073G7074 (双字)G7076 (双字)G7078 (双字) 9G7080G7083G7084 (双字)G7086 (双字)G7088 (双字) 10G7090G7093G7094 (双字)G7096 (双字)G7098 (双字)轴二启动编号定位编号运行模式控制方法加速时间减速时间插补对象指令速度定位地址圆弧地址G440011G7100G7103G7104 (双字)G7106 (双字)G7108 (双字) 12G7110G7113G7114 (双字)G7116 (双字)G7118 (双字) 13G7120G7123G7124 (双字)G7126 (双字)G7128 (双字) 14G7130G7133G7134 (双字)G7136 (双字)G7138 (双字) 15G7140G7143G7144 (双字)G7146 (双字)G7148 (双字) 16G7150G7153G7154 (双字)G7156 (双字)G7158 (双字) 17G7160G7163G7164 (双字)G7166 (双字)G7168 (双字) 18G7170G7173G7174 (双字)G7176 (双字)G7178 (双字) 19G7180G7183G7184 (双字)G7186 (双字)G7188 (双字) 20G7190G7193G7194 (双字)G7196 (双字)G7198 (双字)轴三启动编号定位编号运行模式控制方法加速时间减速时间插补对象指令速度定位地址圆弧地址G45001G8000G8003G8004 (双字)G8006 (双字)G8008 (双字) 2G8010G8013G8014 (双字)G8016 (双字)G8018 (双字) 3G8020G8023G8024 (双字)G8026 (双字)G8028 (双字) 4G8030G8033G8034 (双字)G8036 (双字)G8038 (双字) 5G8040G8043G8044 (双字)G8046 (双字)G8048 (双字) 6G8050G8053G8054 (双字)G8056 (双字)G8058 (双字) 7G8060G8063G8064 (双字)G8066 (双字)G8068 (双字) 8G8070G8073G8074 (双字)G8076 (双字)G8078 (双字) 9G8080G8083G8084 (双字)G8086 (双字)G8088 (双字) 10G8090G8093G8094 (双字)G8096 (双字)G8098 (双字)轴三启动编号定位编号运行模式控制方法加速时间减速时间插补对象指令速度定位地址圆弧地址G450011G8100G8103G8104 (双字)G8106 (双字)G8108 (双字) 12G8110G8113G8114 (双字)G8116 (双字)G8118 (双字) 13G8120G8123G8124 (双字)G8126 (双字)G8128 (双字) 14G8130G8133G8134 (双字)G8136 (双字)G8138 (双字) 15G8140G8143G8144 (双字)G8146 (双字)G8148 (双字) 16G8150G8153G8154 (双字)G8156 (双字)G8158 (双字) 17G8160G8163G8164 (双字)G8166 (双字)G8168 (双字) 18G8170G8173G8174 (双字)G8176 (双字)G8178 (双字) 19G8180G8183G8184 (双字)G8186 (双字)G8188 (双字) 20G8190G8193G8194 (双字)G8196 (双字)G8198 (双字)轴四启动编号定位编号运行模式控制方法加速时间减速时间插补对象指令速度定位地址圆弧地址G46001G9000G9003G9004 (双字)G9006 (双字)G9008 (双字) 2G9010G9013G9014 (双字)G9016 (双字)G9018 (双字) 3G9020G9023G9024 (双字)G9026 (双字)G9028 (双字) 4G9030G9033G9034 (双字)G9036 (双字)G9038 (双字) 5G9040G9043G9044 (双字)G9046 (双字)G9048 (双字) 6G9050G9053G9054 (双字)G9056 (双字)G9058 (双字) 7G9060G9063G9064 (双字)G9066 (双字)G9068 (双字) 8G9070G9073G9074 (双字)G9076 (双字)G9078 (双字) 9G9080G9083G9084 (双字)G9086 (双字)G9088 (双字) 10G9090G9093G9094 (双字)G9096 (双字)G9098 (双字)轴四启动编号定位编号运行模式控制方法加速时间减速时间插补对象指令速度定位地址圆弧地址G460011G9100G9103G9104 (双字)G9106 (双字)G9108 (双字) 12G9110G9113G9114 (双字)G9116 (双字)G9118 (双字) 13G9120G9123G9124 (双字)G9126 (双字)G9128 (双字) 14G9130G9133G9134 (双字)G9136 (双字)G9138 (双字) 15G9140G9143G9144 (双字)G9146 (双字)G9148 (双字) 16G9150G9153G9154 (双字)G9156 (双字)G9158 (双字) 17G9160G9163G9164 (双字)G9166 (双字)G9168 (双字) 18G9170G9173G9174 (双字)G9176 (双字)G9178 (双字) 19G9180G9183G9184 (双字)G9186 (双字)G9188 (双字) 20G9190G9193G9194 (双字)G9196 (双字)G9198 (双字)轴五启动编号定位编号运行模式控制方法加速时间减速时间插补对象指令速度定位地址圆弧地址G47001G10000G10003G10004 (双字)G10006 (双字)G10008 (双字) 2G10010G10013G10014 (双字)G10016 (双字)G10018 (双字) 3G10020G10023G10024 (双字)G10026 (双字)G10028 (双字) 4G10030G10033G10034 (双字)G10036 (双字)G10038 (双字) 5G10040G10043G10044 (双字)G10046 (双字)G10048 (双字) 6G10050G10053G10054 (双字)G10056 (双字)G10058 (双字) 7G10060G10063G10064 (双字)G10066 (双字)G10068 (双字) 8G10070G10073G10074 (双字)G10076 (双字)G10078 (双字) 9G10080G10083G10084 (双字)G10086 (双字)G10088 (双字) 10G10090G10093G10094 (双字)G10096 (双字)G10098 (双字)轴五启动编号定位编号运行模式控制方法加速时间减速时间插补对象指令速度定位地址圆弧地址G470011G10100G10103G10104 (双字)G10106 (双字)G10108 (双字) 12G10110G10113G10114 (双字)G10116 (双字)G10118 (双字) 13G10120G10123G10124 (双字)G10126 (双字)G10128 (双字) 14G10130G10133G10134 (双字)G10136 (双字)G10138 (双字) 15G10140G10143G10144 (双字)G10146 (双字)G10148 (双字) 16G10150G10153G10154 (双字)G10156 (双字)G10158 (双字) 17G10160G10163G10164 (双字)G10166 (双字)G10168 (双字) 18G10170G10173G10174 (双字)G10176 (双字)G10178 (双字) 19G10180G10183G10184 (双字)G10186 (双字)G10188 (双字) 20G10190G10193G10194 (双字)G10196 (双字)G10198 (双字)轴六启动编号定位编号运行模式控制方法加速时间减速时间插补对象指令速度定位地址圆弧地址G48001G11000G11003G11004 (双字)G11006 (双字)G11008 (双字) 2G11010G11013G11014 (双字)G11016 (双字)G11018 (双字) 3G11020G11023G11024 (双字)G11026 (双字)G11028 (双字) 4G11030G11033G11034 (双字)G11036 (双字)G11038 (双字) 5G11040G11043G11044 (双字)G11046 (双字)G11048 (双字) 6G11050G11053G11054 (双字)G11056 (双字)G11058 (双字) 7G11060G11063G11064 (双字)G11066 (双字)G11068 (双字) 8G11070G11073G11074 (双字)G11076 (双字)G11078 (双字) 9G11080G11083G11084 (双字)G11086 (双字)G11088 (双字) 10G11090G11093G11094 (双字)G11096 (双字)G11098 (双字)轴六启动编号定位编号运行模式控制方法加速时间减速时间插补对象指令速度定位地址圆弧地址G480011G11100G11103G11104 (双字)G11106 (双字)G11108 (双字) 12G11110G11113G11114 (双字)G11116 (双字)G11118 (双字) 13G11120G11123G11124 (双字)G11126 (双字)G11128 (双字) 14G11130G11133G11134 (双字)G11136 (双字)G11138 (双字) 15G11140G11143G11144 (双字)G11146 (双字)G11148 (双字) 16G11150G11153G11154 (双字)G11156 (双字)G11158 (双字) 17G11160G11163G11164 (双字)G11166 (双字)G11168 (双字) 18G11170G11173G11174 (双字)G11176 (双字)G11178 (双字) 19G11180G11183G11184 (双字)G11186 (双字)G11188 (双字) 20G11190G11193G11194 (双字)G11196 (双字)G11198 (双字)轴七启动编号定位编号运行模式控制方法加速时间减速时间插补对象指令速度定位地址圆弧地址G49001G12000G12003G12004 (双字)G12006 (双字)G12008 (双字) 2G12010G12013G12014 (双字)G12016 (双字)G12018 (双字) 3G12020G12023G12024 (双字)G12026 (双字)G12028 (双字) 4G12030G12033G12034 (双字)G12036 (双字)G12038 (双字) 5G12040G12043G12044 (双字)G12046 (双字)G12048 (双字) 6G12050G12053G12054 (双字)G12056 (双字)G12058 (双字) 7G12060G12063G12064 (双字)G12066 (双字)G12068 (双字) 8G12070G12073G12074 (双字)G12076 (双字)G12078 (双字) 9G12080G12083G12084 (双字)G12086 (双字)G12088 (双字) 10G12090G12093G12094 (双字)G12096 (双字)G12098 (双字)轴七启动编号定位编号运行模式控制方法加速时间减速时间插补对象指令速度定位地址圆弧地址G490011G12100G12103G12104 (双字)G12106 (双字)G12108 (双字) 12G12110G12113G12114 (双字)G12116 (双字)G12118 (双字) 13G12120G12123G12124 (双字)G12126 (双字)G12128 (双字) 14G12130G12133G12134 (双字)G12136 (双字)G12138 (双字) 15G12140G12143G12144 (双字)G12146 (双字)G12148 (双字) 16G12150G12153G12154 (双字)G12156 (双字)G12158 (双字) 17G12160G12163G12164 (双字)G12166 (双字)G12168 (双字) 18G12170G12173G12174 (双字)G12176 (双字)G12178 (双字) 19G12180G12183G12184 (双字)G12186 (双字)G12188 (双字) 20G12190G12193G12194 (双字)G12196 (双字)G12198 (双字)轴八启动编号定位编号运行模式控制方法加速时间减速时间插补对象指令速度定位地址圆弧地址G50001G13000G13003G13004 (双字)G13006 (双字)G13008 (双字) 2G13010G13013G13014 (双字)G13016 (双字)G13018 (双字) 3G13020G13023G13024 (双字)G13026 (双字)G13028 (双字) 4G13030G13033G13034 (双字)G13036 (双字)G13038 (双字) 5G13040G13043G13044 (双字)G13046 (双字)G13048 (双字) 6G13050G13053G13054 (双字)G13056 (双字)G13058 (双字) 7G13060G13063G13064 (双字)G13066 (双字)G13068 (双字) 8G13070G13073G13074 (双字)G13076 (双字)G13078 (双字) 9G13080G13083G13084 (双字)G13086 (双字)G13088 (双字) 10G13090G13093G13094 (双字)G13096 (双字)G13098 (双字)轴八启动编号定位编号运行模式控制方法加速时间减速时间插补对象指令速度定位地址圆弧地址G500011G13100G13103G13104 (双字)G13106 (双字)G13108 (双字) 12G13110G13113G13114 (双字)G13116 (双字)G13118 (双字) 13G13120G13123G13124 (双字)G13126 (双字)G13128 (双字) 14G13130G13133G13134 (双字)G13136 (双字)G13138 (双字) 15G13140G13143G13144 (双字)G13146 (双字)G13148 (双字) 16G13150G13153G13154 (双字)G13156 (双字)G13158 (双字) 17G13160G13163G13164 (双字)G13166 (双字)G13168 (双字) 18G13170G13173G13174 (双字)G13176 (双字)G13178 (双字) 19G13180G13183G13184 (双字)G13186 (双字)G13188 (双字) 20G13190G13193G13194 (双字)G13196 (双字)G13198 (双字)轴九启动编号定位编号运行模式控制方法加速时间减速时间插补对象指令速度定位地址圆弧地址G51001G14000G14003G14004 (双字)G14006 (双字)G14008 (双字) 2G14010G14013G14014 (双字)G14016 (双字)G14018 (双字) 3G14020G14023G14024 (双字)G14026 (双字)G14028 (双字) 4G14030G14033G14034 (双字)G14036 (双字)G14038 (双字) 5G14040G14043G14044 (双字)G14046 (双字)G14048 (双字) 6G14050G14053G14054 (双字)G14056 (双字)G14058 (双字) 7G14060G14063G14064 (双字)G14066 (双字)G14068 (双字) 8G14070G14073G14074 (双字)G14076 (双字)G14078 (双字) 9G14080G14083G14084 (双字)G14086 (双字)G14088 (双字) 10G14090G14093G14094 (双字)G14096 (双字)G14098 (双字)轴九启动编号定位编号运行模式控制方法加速时间减速时间插补对象指令速度定位地址圆弧地址G510011G14100G14103G14104 (双字)G14106 (双字)G14108 (双字) 12G14110G14113G14114 (双字)G14116 (双字)G14118 (双字) 13G14120G14123G14124 (双字)G14126 (双字)G14128 (双字) 14G14130G14133G14134 (双字)G14136 (双字)G14138 (双字) 15G14140G14143G14144 (双字)G14146 (双字)G14148 (双字) 16G14150G14153G14154 (双字)G14156 (双字)G14158 (双字) 17G14160G14163G14164 (双字)G14166 (双字)G14168 (双字) 18G14170G14173G14174 (双字)G14176 (双字)G14178 (双字) 19G14180G14183G14184 (双字)G14186 (双字)G14188 (双字) 20G14190G14193G14194 (双字)G14196 (双字)G14198 (双字)轴十启动编号定位编号运行模式控制方法加速时间减速时间插补对象指令速度定位地址圆弧地址G52001G15000G15003G15004 (双字)G15006 (双字)G15008 (双字) 2G15010G15013G15014 (双字)G15016 (双字)G15018 (双字) 3G15020G15023G15024 (双字)G15026 (双字)G15028 (双字) 4G15030G15033G15034 (双字)G15036 (双字)G15038 (双字) 5G15040G15043G15044 (双字)G15046 (双字)G15048 (双字) 6G15050G15053G15054 (双字)G15056 (双字)G15058 (双字) 7G15060G15063G15064 (双字)G15066 (双字)G15068 (双字) 8G15070G15073G15074 (双字)G15076 (双字)G15078 (双字) 9G15080G15083G15084 (双字)G15086 (双字)G15088 (双字) 10G15090G15093G15094 (双字)G15096 (双字)G15098 (双字)轴十启动编号定位编号运行模式控制方法加速时间减速时间插补对象指令速度定位地址圆弧地址G520011G15100G15103G15104 (双字)G15106 (双字)G15108 (双字) 12G15110G15113G15114 (双字)G15116 (双字)G15118 (双字) 13G15120G15123G15124 (双字)G15126 (双字)G15128 (双字) 14G15130G15133G15134 (双字)G15136 (双字)G15138 (双字) 15G15140G15143G15144 (双字)G15146 (双字)G15148 (双字) 16G15150G15153G15154 (双字)G15156 (双字)G15158 (双字) 17G15160G15163G15164 (双字)G15166 (双字)G15168 (双字) 18G15170G15173G15174 (双字)G15176 (双字)G15178 (双字) 19G15180G15183G15184 (双字)G15186 (双字)G15188 (双字) 20G15190G15193G15194 (双字)G15196 (双字)G15198 (双字)轴十一启动编号定位编号运行模式控制方法加速时间减速时间插补对象指令速度定位地址圆弧地址G53001G16000G16003G16004 (双字)G16006 (双字)G16008 (双字) 2G16010G16013G16014 (双字)G16016 (双字)G16018 (双字) 3G16020G16023G16024 (双字)G16026 (双字)G16028 (双字) 4G16030G16033G16034 (双字)G16036 (双字)G16038 (双字) 5G16040G16043G16044 (双字)G16046 (双字)G16048 (双字) 6G16050G16053G16054 (双字)G16056 (双字)G16058 (双字) 7G16060G16063G16064 (双字)G16066 (双字)G16068 (双字) 8G16070G16073G16074 (双字)G16076 (双字)G16078 (双字) 9G16080G16083G16084 (双字)G16086 (双字)G16088 (双字) 10G16090G16093G16094 (双字)G16096 (双字)G16098 (双字)轴十一启动编号定位编号运行模式控制方法加速时间减速时间插补对象指令速度定位地址圆弧地址G530011G16100G16103G16104 (双字)G16106 (双字)G16108 (双字) 12G16110G16113G16114 (双字)G16116 (双字)G16118 (双字) 13G16120G16123G16124 (双字)G16126 (双字)G16128 (双字) 14G16130G16133G16134 (双字)G16136 (双字)G16138 (双字) 15G16140G16143G16144 (双字)G16146 (双字)G16148 (双字) 16G16150G16153G16154 (双字)G16156 (双字)G16158 (双字) 17G16160G16163G16164 (双字)G16166 (双字)G16168 (双字) 18G16170G16173G16174 (双字)G16176 (双字)G16178 (双字) 19G16180G16183G16184 (双字)G16186 (双字)G16188 (双字) 20G16190G16193G16194 (双字)G16196 (双字)G16198 (双字)轴十二启动编号定位编号运行模式控制方法加速时间减速时间插补对象指令速度定位地址圆弧地址G54001G17000G17003G17004 (双字)G17006 (双字)G17008 (双字) 2G17010G17013G17014 (双字)G17016 (双字)G17018 (双字) 3G17020G17023G17024 (双字)G17026 (双字)G17028 (双字) 4G17030G17033G17034 (双字)G17036 (双字)G17038 (双字) 5G17040G17043G17044 (双字)G17046 (双字)G17048 (双字) 6G17050G17053G17054 (双字)G17056 (双字)G17058 (双字) 7G17060G17063G17064 (双字)G17066 (双字)G17068 (双字) 8G17070G17073G17074 (双字)G17076 (双字)G17078 (双字) 9G17080G17083G17084 (双字)G17086 (双字)G17088 (双字) 10G17090G17093G17094 (双字)G17096 (双字)G17098 (双字)轴十二启动编号定位编号运行模式控制方法加速时间减速时间插补对象指令速度定位地址圆弧地址G540011G17100G17103G17104 (双字)G17106 (双字)G17108 (双字) 12G17110G17113G17114 (双字)G17116 (双字)G17118 (双字) 13G17120G17123G17124 (双字)G17126 (双字)G17128 (双字) 14G17130G17133G17134 (双字)G17136 (双字)G17138 (双字) 15G17140G17143G17144 (双字)G17146 (双字)G17148 (双字) 16G17150G17153G17154 (双字)G17156 (双字)G17158 (双字) 17G17160G17163G17164 (双字)G17166 (双字)G17168 (双字) 18G17170G17173G17174 (双字)G17176 (双字)G17178 (双字) 19G17180G17183G17184 (双字)G17186 (双字)G17188 (双字) 20G17190G17193G17194 (双字)G17196 (双字)G17198 (双字)轴十三启动编号定位编号运行模式控制方法加速时间减速时间插补对象指令速度定位地址圆弧地址G55001G18000G18003G18004 (双字)G18006 (双字)G18008 (双字) 2G18010G18013G18014 (双字)G18016 (双字)G18018 (双字) 3G18020G18023G18024 (双字)G18026 (双字)G18028 (双字) 4G18030G18033G18034 (双字)G18036 (双字)G18038 (双字) 5G18040G18043G18044 (双字)G18046 (双字)G18048 (双字) 6G18050G18053G18054 (双字)G18056 (双字)G18058 (双字) 7G18060G18063G18064 (双字)G18066 (双字)G18068 (双字) 8G18070G18073G18074 (双字)G18076 (双字)G18078 (双字) 9G18080G18083G18084 (双字)G18086 (双字)G18088 (双字) 10G18090G18093G18094 (双字)G18096 (双字)G18098 (双字)轴十三启动编号定位编号运行模式控制方法加速时间减速时间插补对象指令速度定位地址圆弧地址G550011G18100G18103G18104 (双字)G18106 (双字)G18108 (双字) 12G18110G18113G18114 (双字)G18116 (双字)G18118 (双字) 13G18120G18123G18124 (双字)G18126 (双字)G18128 (双字) 14G18130G18133G18134 (双字)G18136 (双字)G18138 (双字) 15G18140G18143G18144 (双字)G18146 (双字)G18148 (双字) 16G18150G18153G18154 (双字)G18156 (双字)G18158 (双字) 17G18160G18163G18164 (双字)G18166 (双字)G18168 (双字) 18G18170G18173G18174 (双字)G18176 (双字)G18178 (双字) 19G18180G18183G18184 (双字)G18186 (双字)G18188 (双字) 20G18190G18193G18194 (双字)G18196 (双字)G18198 (双字)轴十四启动编号定位编号运行模式控制方法加速时间减速时间插补对象指令速度定位地址圆弧地址G56001G19000G19003G19004 (双字)G19006 (双字)G19008 (双字) 2G19010G19013G19014 (双字)G19016 (双字)G19018 (双字) 3G19020G19023G19024 (双字)G19026 (双字)G19028 (双字) 4G19030G19033G19034 (双字)G19036 (双字)G19038 (双字) 5G19040G19043G19044 (双字)G19046 (双字)G19048 (双字) 6G19050G19053G19054 (双字)G19056 (双字)G19058 (双字) 7G19060G19063G19064 (双字)G19066 (双字)G19068 (双字) 8G19070G19073G19074 (双字)G19076 (双字)G19078 (双字) 9G19080G19083G19084 (双字)G19086 (双字)G19088 (双字) 10G19090G19093G19094 (双字)G19096 (双字)G19098 (双字)轴十四启动编号定位编号运行模式控制方法加速时间减速时间插补对象指令速度定位地址圆弧地址G560011G19100G19103G19104 (双字)G19106 (双字)G19108 (双字) 12G19110G19113G19114 (双字)G19116 (双字)G19118 (双字) 13G19120G19123G19124 (双字)G19126 (双字)G19128 (双字) 14G19130G19133G19134 (双字)G19136 (双字)G19138 (双字) 15G19140G19143G19144 (双字)G19146 (双字)G19148 (双字) 16G19150G19153G19154 (双字)G19156 (双字)G19158 (双字) 17G19160G19163G19164 (双字)G19166 (双字)G19168 (双字) 18G19170G19173G19174 (双字)G19176 (双字)G19178 (双字) 19G19180G19183G19184 (双字)G19186 (双字)G19188 (双字) 20G19190G19193G19194 (双字)G19196 (双字)G19198 (双字)轴十五启动编号定位编号运行模式控制方法加速时间减速时间插补对象指令速度定位地址圆弧地址G57001G20000G20003G20004 (双字)G20006 (双字)G20008 (双字) 2G20010G20013G20014 (双字)G20016 (双字)G20018 (双字) 3G20020G20023G20024 (双字)G20026 (双字)G20028 (双字) 4G20030G20033G20034 (双字)G20036 (双字)G20038 (双字) 5G20040G20043G20044 (双字)G20046 (双字)G20048 (双字) 6G20050G20053G20054 (双字)G20056 (双字)G20058 (双字) 7G20060G20063G20064 (双字)G20066 (双字)G20068 (双字) 8G20070G20073G20074 (双字)G20076 (双字)G20078 (双字) 9G20080G20083G20084 (双字)G20086 (双字)G20088 (双字) 10G20090G20093G20094 (双字)G20096 (双字)G20098 (双字)。

西门子特殊存储器标志位一览表

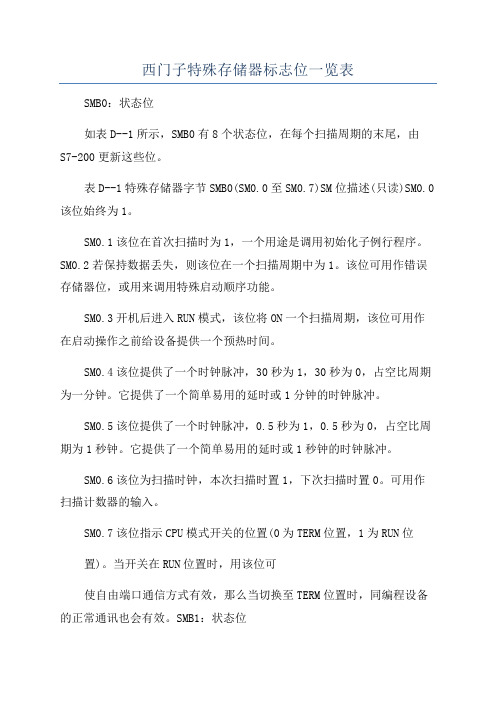

西门子特殊存储器标志位一览表SMB0:状态位如表D--1所示,SMB0有8个状态位,在每个扫描周期的末尾,由S7-200更新这些位。

表D--1特殊存储器字节SMB0(SM0.0至SM0.7)SM位描述(只读)SM0.0该位始终为1。

SM0.1该位在首次扫描时为1,一个用途是调用初始化子例行程序。

SM0.2若保持数据丢失,则该位在一个扫描周期中为1。

该位可用作错误存储器位,或用来调用特殊启动顺序功能。

SM0.3开机后进入RUN模式,该位将ON一个扫描周期,该位可用作在启动操作之前给设备提供一个预热时间。

SM0.4该位提供了一个时钟脉冲,30秒为1,30秒为0,占空比周期为一分钟。

它提供了一个简单易用的延时或1分钟的时钟脉冲。

SM0.5该位提供了一个时钟脉冲,0.5秒为1,0.5秒为0,占空比周期为1秒钟。

它提供了一个简单易用的延时或1秒钟的时钟脉冲。

SM0.6该位为扫描时钟,本次扫描时置1,下次扫描时置0。

可用作扫描计数器的输入。

SM0.7该位指示CPU模式开关的位置(0为TERM位置,1为RUN位置)。

当开关在RUN位置时,用该位可使自由端口通信方式有效,那么当切换至TERM位置时,同编程设备的正常通讯也会有效。

SMB1:状态位如表D--2所示,SMB1包含了各种潜在的错误提示。

这些位可由指令在执行时进行置位或复位。

表D--2特殊存储器字节SMB1(SM1.0至SM1.7)SM位描述(只读)SM1.0当执行某些指令,其结果为0时,将该位置1。

SM1.1当执行某些指令,其结果溢出或查出非法数值时,将该位置1。

SM1.2当执行数学运算,其结果为负数时,将该位置1。

SM1.3试图除以零时,将该位置1。

SM1.4当执行ATT(添加到表格)指令时,试图超出表范围时,将该位置1。

SM1.5当执行LIFO或FIFO指令,试图从空表中读数时,将该位置1。

SM1.6当试图把一个非BCD数转换为二进制数时,将该位置1。

胆缓冲

胆缓冲-- 调音的利器胆缓冲??嗯,这是HiFiZone准备推出的一个胆前级套件。

它确实是一个实实在在的胆前级,只是它的放大倍数略小于1,也就是说它的增益约等于0db,但它却能够有效的降低输出阻抗,提高输出电电流,起到阻抗匹配的作用,能够更好的驱动后级扩大器。

同时,它又是一个相当不错的音色调教器,你可以相当轻松的更换管子来达到调音的目的,从低价的国产6N11到飞利浦的6922、E88CC、6DJ8,甚至苏制的6H30pi。

您可以用电子管圆润温暖的声音来虑掉原有系统中的毛刺(这是大多数低价CD或电脑声卡的通病),使原系统混浊不清的声音变得更清晰、圆润且温暖,变得更耐听。

下面我们来看看这个胆前级缓冲器的主要线路(两个声道):这是一个非常典型的阴极跟随器,两个声道只需一个电子管,在这里采用MOSFET IRF63 0作为恒流源,令整个跟随器的输出阻抗更低,性能更好,使用MOSFET做恒流源是最好不过的器件了,它具有更优异的电流恒定效果,音色更接近电子管,声音柔美醇厚。

我们特别设了两个200欧姆的BOCHEX 高精度多圈可调电阻,你可以通过这个高精度多圈可调电阻轻松调出你认为最佳的工作点,可调范围为0.6V/10欧姆=60mA至0.6V/210欧姆=2.85mA,这个电流范围因该能够应付所有的同类型的电子管了,当然也包括屏流达20mA的苏制6H30pi。

这个线路的工作电压很低只需+-24V,在这样的低压下,线路具有更佳的信噪比,像6DJ8这样的管子在60-80V都有非常优秀的线性了。

我们曾使用过6N11、6922、E88CC这些管子试听,整个线路都能非常好地工作且都能得到很不错的声音表现。

我们来看看电源部分的线路:在这里我们选用高精度可调稳压集成LM317、LM337组成的+-24V稳压线路,该线路具有软启动功能,从0V上升至+-24V的时间设定在约8秒钟的时间,这样可以使管子在接入高压前得到预热,从而使你昂贵的管子老化得更慢、使用寿命更长。

Devicelist_QD77MS

参数区

Un\G31549 Un\G31300 Un\G31549 Un\G899 Un\G1999 Un\G1599 Un\G800 Un\G1900 Un\G1500 ― Un\G899 Un\G1999 Un\G1599

使用GX Works2 进行设置 Un\G22000 Un\G221919625.xls/缓冲存储区配置一览

缓冲存储区配置一览 关于输入输出信号(XY),请点击这里

缓冲存储器地址Un\G■ 缓冲存储区配置 最小 基本参数区 详细参数区 原点回归基本参数区 原点回归详细参数区 扩展参数区 系统监视区 监视数据区 轴监视区 系统控制数据区 控制数据区 轴控制数据区 扩展轴控制数据区 定位数据区 基本参数1 基本参数2 详细参数1 详细参数2 原点回归基本参数 原点回归详细参数 扩展参数 系统监视数据 轴监视数据[Md.20~] 轴监视数据[Md.100~] 系统控制数据 轴控制数据[Cd.3~] 轴控制数据[Cd.100~] 扩展轴控制数据 定位数据区(No.1~No.100) 定位数据区(No.101~No.600) (块No.7000~块No.7001) 块启动数据区 (块No.7002~块No.7004) 可编程控制器CPU记录区 块启动数据区 条件数据区 块启动数据区 条件数据区 Un\G2000 Un\G3000 Un\G26000 Un\G26100 Un\G26400 Un\G26500 Un\G30000 Un\G0 Un\G17 Un\G70 Un\G79 Un\G100 Un\G1200 Un\G31300 Un\G800 Un\G1900 Un\G1500 ― Un\G2999 Un\G7999 Un\G2000 Un\G3000 QD77MS2 最大 Un\G15 Un\G69 Un\G78 Un\G89 Un\G106 Un\G1499 最小 Un\G0 Un\G17 Un\G70 Un\G79 Un\G100 Un\G1200 QD77MS4 最大 Un\G15 Un\G69 Un\G78 Un\G89 Un\G106 Un\G1499 轴号 QD77MS16 最小 Un\G0 Un\G17 Un\G70 Un\G79 Un\G100 Un\G4000 Un\G31300 Un\G2400 Un\G5900 Un\G4300 Un\G30100 Un\G2999 Un\G7999 Un\G6000 最大 Un\G15 Un\G69 Un\G78 Un\G89 Un\G106 Un\G4299 Un\G31549 Un\G2499 Un\G5999 Un\G4399 Un\G30109 Un\G6999 1

海康网络高清前端解码和存储设备参数指标

海康网络高清前端、解码和存储设备技术参数一、DS-2DF1-671 130万像素网络高清球系列主要特性●采用1/3” 130万像素逐行扫描CCD,最大可到1280x960输出●基于以太网控制,同时支持模拟接入●可通过IE浏览器观看图像并实现控制●采用H.264视频压缩算法和TI高性价比的最新达芬奇处理芯片和平台,性能可靠稳定●一体化集成设计,结构紧凑,内部设置数据断电不丢失●精密电机驱动,反应灵敏,运转平稳,在任何速度下操作平滑无抖动●水平360°连续旋转无监视盲区,可设定手动限位●完全实现对HIKVISION、Pelco-P/D协议、安防行业协议的自动识别●三维智能定位功能,配合客户端软件或DVR可实现点击跟踪和放大●旋转速度根据镜头变倍倍数自动调整●自动光圈、自动聚焦、自动白平衡●具有背光补偿和低照度(彩色/黑白)自动/手动转换功能●屏幕中英文菜单功能及屏幕操作提示功能,可用密码保护设置数据●支持预置点/巡航扫描/花样扫描/自动扫描/随机扫描/帧扫描/全景扫描等自动模式,可设定手动限位●4个花样扫描功能,花样扫描总记录操作时间可达10分钟以上●内置1个报警输入,可在报警后调用预置点或花样扫描功能●自动归位和空闲动作功能,以及上电动作功能●具有防雷、防浪涌保护功能●机件密封设计,室外罩通过IP66检测●1个辅助开关控制,可被报警联动输出应用场景可广泛应用于需要大范围监控的场所,如:河流、森林、公路、铁路、机场、港口、油田、岗哨、广场、公园、景区、街道、车站、大型场馆、小区外围监控等要求高清画质的大范围监控场所。

技术参数外形尺寸建议配件DS-1611ZJ(白色)长壁装支架二、DS-2CD852MF-E/DX 200万像素网络高清摄像机系列主要特点●采用先进的视频压缩技术,压缩比高,且处理非常灵活●采用TI高性价比的达芬奇处理芯片和平台,性能可靠稳定●200万像素逐行扫描CMOS,捕捉运动图像无锯齿,同时输出1600×1200超凡色彩表现力的图像●支持SD/SDHC卡本地存储●支持双向语音●支持电子云台(ePTZ)功能●支持PoE网络供电●支持双码流,支持手机监控●支持OSD菜单控制,适合客户自定义设置●功能齐全:PTZ控制,报警应用场景适用于金融、电信、政府、学校、机场、工厂、酒店、博物馆、交通监控等要求高清画质的场所。

机械搅拌澄清池设计参数表

机械搅拌澄清池设计参数表Q 设计规模 m^3/s 0.2900A1 第⼆反应室内导流板截⾯积 m^20.0450u1 第⼆反应室及导流室内流速 mm/s 50.0000D1 第⼆反应室内径 m 6.0812 反应室壁厚 m0.2500t1 第⼆反应室内停留时间 s60.0000H1 选⽤值 m3.0000ω2 导流室截⾯积 m^229.0000D2 实际取⽤导流室直径 m 9.5000 导流室壁厚 m 0.1000H2 第⼆反应室出⽔窗⾼度 m 1.4594u6 导流室出⼝流速m/s 0.0400H3 实际取⽤出⼝截⾯宽 m 1.4500H'3 出⼝垂直⾼度 m 2.0503u2 分离室上升流速 m/s 0.0010ω池总⾯积 m^2363.8981D 池直径m21.5251D 实际取池直径 m 21.5000R 半径 m10.7500T 池中停留时间 h 1.5000H0 取池⼦的超⾼ m 0.3000H4 池⼦直壁⾼ m2.0000W2+W3902.5394H5 圆台⾼度 m4.2000 池圆台斜边倾⾓ °45.0000Dt 池底部直径13.1000H6 球壳式结构冠⾼ m 1.0500W2 圆台容积 m^31006.6558R球球冠半径 m 20.9548W3 球冠体积 m71.3668V 池⼦实际有效容积 m^31804.1232V' m^31734.7338T 实际总停留时间 h 1.6616H 池⼦总⾼ m7.5500u3 配⽔槽内流速(进⽔流量增加10%的排泥⽔量) m/s 0.4500B1 三⾓槽直⾓边长 m 0.8420B1 实际取值 m0.8500三⾓槽孔⼝流速 m/s 0.4500出⽔孔总⾯积 m^20.7089d 孔⼝直径 m 0.1000孔⼝⾯积 m^20.0079δ出⽔孔数90.2585⾓度4.0000实际孔数90.0000u3 孔⼝实际流速 m/s 0.4513 ⼆反应室板底厚 m 0.1500D3 第⼀反应室上端直径 m 8.5812H7 第⼀反应室⾼ m3.0500D4 伞形板延长线与池壁交点处直径(m)13.8906u4 泥渣回流缝流速 m/s 0.1500Q'' 泥渣回流量 m^3 1.1600B2 回流缝宽度 m0.1772B2 实际取值 m 0.1700 裙板厚 m0.0500D5 伞形板下端圆柱直径 m 13.3098H8 伞形板下端圆柱体⾼度 m 0.5808H10 伞形板离池底⾼度 m 0.1049H9 伞形板锥部⾼度 m 2.4692V1 第⼀反应室容积 m^3402.4915V2 第⼆反应室加导流室容积 m^3166.3940V3 分离室容积 m^31165.8483实际各室容积⽐第⼆反应室 1.0000 第⼀反应室 2.4200 分离室7.0100 第⼆反应室停留时间9.5629 第⼀反应室停留时间23.1422 分离室停留时间67.0357d 进⽔管管径 mm 600.0000v6 进⽔管流速 m/s 1.0000d 出⽔管管径 mm600.0000 集⽔槽:采⽤辐射式和环形集⽔槽集⽔槽根数12.0000q1 单根集⽔槽流量 m^3/s 0.0242b1 辐射槽宽 m0.2500v51 槽内⽔流流速 m/s 0.5000il 槽底坡降 m0.1000h2 槽内终点⽔深 m 0.1933hl 槽内起点⽔深 m 0.1217hk0.0984v'51 m/s0.8000 h2 槽内终点⽔深 m 0.2417 hk0.1562 h1 槽内起点⽔⾝ m 0.2071 设计取槽内起点⽔深m 0.2000 槽内终点⽔深m0.3000 孔⼝出流孔⼝前⽔位m 0.0500 孔⼝出流跌路m 0.0700 槽超⾼m0.2000 槽起点断⾯⾼0.5200 槽终点断⾯⾼0.6200q2 环形集⽔槽 m^3/s 0.1450v52 m/s 0.6000b2 槽宽 m 0.5000il 平底m0.0000δδh4 槽内终点⽔深m0.4833 h3 槽内起点⽔深m0.5187 hk m0.2047 v52' 流量增加⼀倍时流速m/s0.8000 hk m0.2579 h4m0.7250 h3 m0.7569 设计取⽤环槽内⽔深m0.8000 槽超⾼m0.3000 槽断⾯⾼m 1.2200 Q 总出⽔槽设计流量m^3/s0.2900 b3设计槽宽m0.7000 v53 槽内⽔流流速 m/s 1.0000 il 槽底坡降 m0.2000 槽长m 5.5000 h6 槽内终点⽔深m0.4143 n0.0130 Am^20.2900 R 0.1897 y0.1505 C59.9015 i0.0015 fh5 槽内起点⽔深m0.2224 Q 流量增加⼀倍时总出⽔流量m^3/s0.5800 b3 设计槽宽m0.7000 v'53 取槽内流速 m/s 1.2000 h'6 槽内终点⽔深 m0.6905 A m^20.4833 R 0.2323 y0.1500 C61.7972 i0.0016 h'5 槽内起点⽔深m0.4815 设计取⽤槽内起点⽔深m0.5000 设计取⽤槽内终点⽔深m0.7000 槽超⾼m0.3000 h 从辐射起点⾄⽔槽终点的⽔⾯坡降m0.0718 设计流量增加⼀倍时m0.0885 辐射集⽔槽采⽤三⾓堰⼝C 堰⾼ m0.1000 b 堰宽 m0.2000 h 堰上⽔头m0.0500 q0 单堰流量 m^3/s0.00078262 n 辐射集⽔槽每侧三⾓堰数⽬15.4395叶轮直径 m 4.56091.2~1.5h 0.4m左右0.1~0.2m/s 1m/s。

QD77MS_Devicelist

轴号 QD77MS16 Un\G100 Un\G101 Un\G102 Un\G103 Un\G105 Un\G106

1

-3-

219044805.xls/参数区

参数区

返回一览

基本参数1 Pr.□ Pr.1 单位设置 Pr.4 单位倍率(AM) Pr.2 每转脉冲数(AP) Pr.3 每转移动量(AL) Pr.7 启动时偏置速度 项目 QD77MS2 Un\G0 Un\G1 Un\G2 Un\G3 Un\G4 Un\G5 Un\G6 Un\G7 缓冲存储器地址Un\G■ QD77MS4 Un\G0 Un\G1 Un\G2 Un\G3 Un\G4 Un\G5 Un\G6 Un\G7 轴号 QD77MS16 Un\G0 Un\G1 Un\G2 Un\G3 Un\G4 Un\G5 Un\G6 Un\G7 1

Hale Waihona Puke -2-219044805.xls/参数区

原点回归基本参数 Pr.□ Pr.43 原点回归方式 Pr.44 原点回归方向 Pr.45 原点地址 Pr.46 原点回归速度 Pr.47 爬行速度 Pr.48 原点回归重试 原点回归详细参数 Pr.□ 项目 QD77MS2 Un\G80 Un\G81 Un\G82 Un\G83 Un\G84 Un\G85 Un\G86 Un\G87 Un\G88 Un\G89 Un\G90 Un\G91 缓冲存储器地址Un\G■ QD77MS4 Un\G80 Un\G81 Un\G82 Un\G83 Un\G84 Un\G85 Un\G86 Un\G87 Un\G88 Un\G89 Un\G90 Un\G91 项目 QD77MS2 Un\G70 Un\G71 Un\G72 Un\G73 Un\G74 Un\G75 Un\G76 Un\G77 Un\G78 缓冲存储器地址Un\G■ QD77MS4 Un\G70 Un\G71 Un\G72 Un\G73 Un\G74 Un\G75 Un\G76 Un\G77 Un\G78

Devicelist_QD77

缓冲存储器地址Un\G■

QD77MS4

QD77MS16

Un\G36 Un\G37 Un\G38 Un\G39 Un\G40 Un\G41 Un\G42 Un\G43 Un\G44 Un\G45 Un\G46 Un\G47 Un\G48 Un\G49 Un\G50 Un\G51 Un\G52 Un\G53 Un\G54 Un\G55 Un\G56 Un\G57 Un\G58 Un\G59 Un\G60 Un\G61 Un\G62 Un\G63 Un\G64 Un\G65 Un\G67 Un\G68.4-7 Un\G68.8-B Un\G68.C-F

Un\G30 Un\G31.0 Un\G31.1 Un\G31.3 Un\G31.4 Un\G31.6 Un\G31.8

Un\G32 Un\G33 Un\G34 Un\G35

-1-

856730851.xls/参数区

详细参数2 Pr.□

项目

Pr.25 加速时间1

Pr.26 加速时间2

Pr.27 加速时间3

-

缓冲存储器地址Un\G■

QD77MS4

QD77MS16

Un\G70

Un\G70

Un\G71

Un\G71

Un\G72

Un\G72

Un\G73

Un\G73

Un\G74

Un\G74

Un\G75

Un\G75

Un\G76

Un\G76

Un\G77 Un\G78

Un\G77 Un\G78

缓冲存储器地址Un\G■

Un\G11

Un\G12

Un\G12

Un\G13

Un\G13

Un\G14 Un\G15

微晟半导体 ZL40200 低噪声高频精密 LVPECL 双输出时钟缓冲器数据表说明书