STM32--中断向量表

关于STM32中断向量表的位置 、重定向问题

关于STM32 中断向量表的位置、重定向问题首先我们需要跳到main 函数,这个就不多说了。

那么,中断发生后,又是怎么跑到中断入口地址的呢?从stm32f10x.s 可以看到,已经定义好了一大堆的中断响应函数,这就是中断向量表,标号__Vectors,表示中断向量表入口地址,例如:AREA RESET, DATA, READONLY ; 定义只读数据段,实际上是在CODE 区(假设STM32 从FLASH 启动,则此中断向量表起始地址即为0x8000000)EXPORT __Vectors IMPORT OS_CPU_SysTickHandler IMPORT OS_CPU_PendSVHandler__Vectors DCD __initial_sp ; Top of Stack DCD Reset_Handler ; Reset Handler DCD NMI_Handler ; NMI Handler DCD HardFault_Handler ; Hard Fault Handler DCD MemManage_Handler ; MPU Fault Handler DCD BusFault_Handler ; Bus Fault Handler DCD UsageFault_Handler ; Usage Fault Handler 这个向量表的编写是有讲究的,跟硬件一一对应不能乱写的,CPU 找入口地址就靠它了,bin 文件开头就是他们的地址,参考手册RM0008 的10.1.2 节可以看到排列。

我们再结合CORTEX-M3的特性,他上电后根据boot 引脚来决定PC 位置,比如boot 设置为flash 启动,则启动后PC 跳到0x08000000。

此时CPU 会先取2 个地址,第一个是栈顶地址,第二个是复位异常地址,故有了上面的写法,这样就跳到reset_handler。

那么这个reset_handler 的实际地址是多少.?下面的一堆例如Nmi_handler 地址又是多少呢?发生中断是怎么跑到这个地址的呢?下面挨个讲解。

STM32学习笔记:读写内部Flash(介绍+附代码)

STM32学习笔记:读写内部Flash(介绍+附代码)⼀、介绍⾸先我们需要了解⼀个内存映射:stm32的flash地址起始于0x0800 0000,结束地址是0x0800 0000加上芯⽚实际的flash⼤⼩,不同的芯⽚flash⼤⼩不同。

RAM起始地址是0x2000 0000,结束地址是0x2000 0000加上芯⽚的RAM⼤⼩。

不同的芯⽚RAM也不同。

Flash中的内容⼀般⽤来存储代码和⼀些定义为const的数据,断电不丢失,RAM可以理解为内存,⽤来存储代码运⾏时的数据,变量等等。

掉电数据丢失。

STM32将外设等都映射为地址的形式,对地址的操作就是对外设的操作。

stm32的外设地址从0x4000 0000开始,可以看到在库⽂件中,是通过基于0x4000 0000地址的偏移量来操作寄存器以及外设的。

⼀般情况下,程序⽂件是从 0x0800 0000 地址写⼊,这个是STM32开始执⾏的地⽅,0x0800 0004是STM32的中断向量表的起始地址。

在使⽤keil进⾏编写程序时,其编程地址的设置⼀般是这样的:程序的写⼊地址从0x08000000(数好零的个数)开始的,其⼤⼩为0x80000也就是512K的空间,换句话说就是告诉编译器flash的空间是从0x08000000-0x08080000,RAM的地址从0x20000000开始,⼤⼩为0x10000也就是64K的RAM。

这与STM32的内存地址映射关系是对应的。

M3复位后,从0x08000004取出复位中断的地址,并且跳转到复位中断程序,中断执⾏完之后会跳到我们的main函数,main函数⾥边⼀般是⼀个死循环,进去后就不会再退出,当有中断发⽣的时候,M3将PC指针强制跳转回中断向量表,然后根据中断源进⼊对应的中断函数,执⾏完中断函数之后,再次返回main函数中。

⼤致的流程就是这样。

1.1、内部Flash的构成:STM32F429 的内部 FLASH 包含主存储器、系统存储器、 OTP 区域以及选项字节区域,它们的地址分布及⼤⼩如下:STM32F103的中容量内部 FLASH 包含主存储器、系统存储器、 OTP 区域以及选项字节区域,它们的地址分布及⼤⼩如下:注意STM32F105VC的是有64K或128页x2K=256k字节的内置闪存存储器,⽤于存放程序和数据。

STM32常见问题解析(论文资料)

STM32常见问题解析1、时钟安全系统(CSS)时钟安全系统被激活后,时钟监控器将实时监控外部高速振荡器;如果HSE时钟发生故障,外部振荡器自动被关闭,产生时钟安全中断,该中断被连接到Cortex‐M3的NMI的中断;同时CSS将内部RC振荡器切换为STM32的系统时钟源(对于STM32F103,时钟失效事件还将被送到高级定时器TIM1的刹车输入端,用以实现电机保护控制)。

操作流程:1)、启动时钟安全系统CSS: RCC_ClockSecuritySystemCmd(ENABLE); (NMI中断是不可屏蔽的!)2)外部振荡器失效时,产生NMI中断,对应的中断程序:void NMIException(void){if (RCC_GetITStatus(RCC_IT_CSS) != RESET){ // HSE、PLL已被禁止(但是PLL设置未变)…… // 客户添加相应的系统保护代码处// 下面为HSE恢复后的预设置代码RCC_HSEConfig(RCC_HSE_ON); // 使能HSERCC_ITConfig(RCC_IT_HSERDY, ENABLE); // 使能HSE就绪中断RCC_ITConfig(RCC_IT_PLLRDY, ENABLE); // 使能PLL就绪中断RCC_ClearITPendingBit(RCC_IT_CSS); // 清除时钟安全系统中断的挂起位// 至此,一旦HSE时钟恢复,将发生HSERDY中断,在RCC中断处理程序里, 系统时钟可以设置到以前的状态}}3)、在RCC的中断处理程序中,再对HSE和PLL进行相应的处理。

注意:一旦CSS被激活,当HSE时钟出现故障时将产生CSS中断,同时自动产生 NMI。

NMI 将被不断执行,直到CSS中断挂起位被清除。

因此,在NMI的处理程序中 必须通过设置时钟中断寄存器(RCC_CIR)里的CSSC位来清除CSS中断。

奋斗STM32V3版按键中断_EXTI_例程

按键中断(EXTI)例程实验

实验平台:奋斗版STM32开发板V2、V2.1、V3 实验内容:板子加电后,按动板子上K1-K3按键,可控制对应的LED1-LED3的亮 灭,该实验学习了外部中断(EXTI)程序的编制及控制流程。

4.2 硬件电路设计

在开发板上V6、V7、V8分别与MCU的PB5、PD6、PD3相连,如下图所示

淘宝店铺:

11

奋斗版 STM32 开发板例程详解———按键中断实验

键盘部分如下图所示: 例程所用到的列扫描线:PC5,PC2,PC3。 例程所用到的行扫描线(EXTI中断线):PE2。

上升沿触发选择寄存器(EXTI_RTSR) 偏移地址:08H 复位值:0000 0000h

注意: 外部唤醒线是边沿触发的,这些线上不能出现毛刺信号。 在写EXTI_RTSR 寄存器时在外部中断线上的上升沿信号不能被识别,挂起位不会被置 位。在同一中断线上,可以同时设置上升沿和下降沿触发。即任一边沿都可触发中断。

1.2 外部中断配置寄存器2(AFIO_EXTICR2)

地址偏移:0Ch 复位值:0000h

淘宝店铺:

1

奋斗版 STM32 开发板例程详解———按键中断实验

1.3 外部中断配置寄存器3(AFIO_EXTICR3)

地址偏移:10h 复位值:0000h

1.4 外部中断配置寄存器4(AFIO_EXTICR4)

地址偏移:14h 复位值:0000h

淘宝店铺:

2

奋斗版 STM32 开发板例程详解———按键中断实验

2.1 嵌套向量中断控制器(NVIC)

淘宝店铺:

7

STM32中用到的Cortex-m3寄存器说明

STM32中用到的Cortex-M3寄存器说明在STM32中用到了Cortex-M3定义的三组寄存器,有关这三组寄存器的说明不在STM32的技术手册中,需要参考ARM公司发布的Cortex-M3 Technical Reference Manual (r2p0)。

在STM32的固件库中定义了三个结构体与这三个寄存器组相对应,这三个结构体与ARM手册中寄存器的对应关系如下:一、NVIC寄存器组STM32的固件库中有如下定义:typedef struct{vu32 ISER[2];u32 RESERVED0[30];vu32 ICER[2];u32 RSERVED1[30];vu32 ISPR[2];u32 RESERVED2[30];vu32 ICPR[2];u32 RESERVED3[30];vu32 IABR[2];u32 RESERVED4[62];vu32 IPR[11];} NVIC_TypeDef;它们对应ARM手册中的名称为ISER = Interrupt Set-Enable RegistersICER = Interrupt Clear-Enable RegistersISPR = Interrupt Set-Pending RegisterICPR = Interrupt Clear-Pending RegisterIABR = Active Bit RegisterIPR = Interrupt Priority Registers每个寄存器有240位,以Interrupt Set-Enable Registers说明,ISER[0]对应中断源0~31,ISER[1]对应中断源32~63,STM32只有60个中断源,所以没有ISER[2:7]。

参考STM32技术参考手册中的中断向量表,中断源的位置为:位置0 - WWDG = Window Watchdog interrupt位置1 - PVD = PVD through EXTI Line detection interrupt位置2 - TAMPER = Tamper interrupt......位置58 - DMA2_Channel3 = DMA2 Channel3 global interrupt位置59 - DMA2_Channel4_5 = DMA2 Channel4 and DMA2 Channel5 global interrupts二、系统控制寄存器组STM32的固件库中有如下定义:typedef struct{vuc32 CPUID;vu32 ICSR;vu32 VTOR;vu32 AIRCR;vu32 SCR;vu32 CCR;vu32 SHPR[3];vu32 SHCSR;vu32 CFSR;vu32 DFSR;vu32 MMFAR;vu32 BFAR;vu32 AFSR;} SCB_TypeDef; /* System Control Block Structure */它们对应ARM手册中的名称为CPUID = CPUID Base RegisterICSR = Interrupt Control State RegisterVTOR = Vector Table Offset RegisterAIRCR = Application Interrupt/Reset Control Register SCR = System Control RegisterCCR = Configuration Control RegisterSHPR = System Handlers Priority RegisterSHCSR = System Handler Control and State Register CFSR = Configurable Fault Status RegistersHFSR = Hard Fault Status RegisterDFSR = Debug Fault Status RegisterMMFAR = Mem Manage Address RegisterBFAR = Bus Fault Address RegisterAFSR = Auxiliary Fault Status Register三、系统时钟寄存器组STM32的固件库中有如下定义:typedef struct{vu32 CTRL;vu32 LOAD;vuc32 CALIB;} SysTick_TypeDef;它们对应ARM手册中的名称为CTRL = SysTick Control and Status Register LOAD = SysTick Reload Value RegisterVAL = SysTick Current Value RegisterCALIB = SysTick Calibration Value Register TAG: 寄存器。

stm32标准库函数手册

stm32标准库函数手册STM32标准库函数是一种由ST公司推出的一套用于STM32微控制器编程的开发工具,它能够帮助开发者快速地进行芯片的开发、调试和测试。

本文将对STM32标准库函数进行详细的介绍,并提供中文手册,帮助开发者更好地掌握这个工具。

一、STM32标准库函数概述STM32标准库函数是一套由ST公司提供的软件库,包括了一系列用于STM32微控制器的常用功能函数,例如GPIO、USART、SPI、I2C等,这些函数可以用于快速实现各种应用。

同时,ST公司也提供了一些示例代码,可以方便开发者进行学习和参考。

STM32标准库函数可以与各种不同的开发环境集成,例如Keil、IAR、STM32Cube等,方便开发者进行开发。

在使用STM32标准库函数时,可以通过库函数的方式来调用硬件资源,比如设置GPIO口的状态、使用USART进行通信、配置外部中断等。

1. 系统初始化函数:这些函数包括了芯片系统时钟的初始化、中断优先级的设置、时钟输出的配置等,必须在主函数前进行调用。

2. GPIO和外部中断函数:这些函数用于对GPIO口状态的配置和读取,以及对外部中断的控制。

3. USART函数:这些函数用于对串口进行配置和读写操作。

8. DAC函数:这些函数用于对模拟量进行输出。

以下是STM32标准库函数的中文手册,包含了常用函数的介绍和使用方法。

1. 系统初始化函数1.1. RCC配置函数函数原型:void RCC_Configuration(void)函数功能:配置STM32的时钟源和时钟分频系数。

函数说明:在函数内部,首先对PLL时钟源进行配置,然后根据系统时钟的需要选择PLL时钟的分频系数,然后对AHB、APB1、APB2的分频系数进行配置。

最后,开启相应时钟使能位。

函数功能:对STM32的中断向量表进行重定位,并设置各个中断的优先级。

函数说明:中断向量表的地址是由SCB_VTOR寄存器来控制的。

Stm32之寄存器列表

USGFAULTENA BUSFAULTENA MEMFAULTENA SVCALLPENDED

R/W R/W R/W R/W

0 0 0 0 R/W R/W R/W

Usage fault handler enable Bus fault handler enable Memory management fault enable SVC pended; SVCall was started but was replaced by a higher-priority exception 0 0 0 Bus fault pended; bus fault handler was started but was replaced by a higher-priority exception Memory management fault pended; memory management fault started but was replaced by a higher-priority exception Usage fault pended; usage fault started but was replaced by a higher-priority exception

5 31 30 29 28 27

NVIC_IABR 0/1(中断激活标志寄存器0/1)

26 25 24 23 22 21 20 19 18 17

IABR[31:16] 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1

IABR[15:0]

IABR0/1[31:0]: 中断激活标志位。只读。如果为1,表示中断正在执行。 读 该寄存器可以知道当前正在执行的是哪一个中断,当中断执行完毕后,对应位自动硬件清0,

STM32外设使用要点

STM32外设使用要点1、时钟安全系统(CSS)时钟安全系统被激活后,时钟监控器将实时监控外部高速振荡器;如果HSE时钟发生故障,外部振荡器自动被关闭,产生时钟安全中断,该中断被连接到Cortex-M3的NMI的中断;同时CSS将内部RC振荡器切换为STM32的系统时钟源(对于STM32F103,时钟失效事件还将被送到高级定时器TIM1的刹车输入端,用以实现电机保护控制)。

操作流程:1)、启动时钟安全系统CSS: RCC_ClockSecuritySystemCmd(ENABLE); (NMI中断是不可屏蔽的!)2)外部振荡器失效时,产生NMI中断,对应的中断程序:void NMIException(void){if (RCC_GetITStatus(RCC_IT_CSS) != RESET){ // HSE、PLL已被禁止(但是PLL设置未变)…… // 客户添加相应的系统保护代码处// 下面为HSE恢复后的预设置代码RCC_HSEConfig(RCC_HSE_ON); // 使能HSERCC_ITConfig(RCC_IT_HSERDY, ENABLE); // 使能HSE就绪中断RCC_ITConfig(RCC_IT_PLLRDY, ENABLE); // 使能PLL就绪中断RCC_ClearITPendingBit(RCC_IT_CSS); // 清除时钟安全系统中断的挂起位// 至此,一旦HSE时钟恢复,将发生HSERDY中断,在RCC中断处理程序里,系统时钟可以设置到以前的状态}}3)、在RCC的中断处理程序中,再对HSE和PLL进行相应的处理。

注意:一旦CSS被激活,当HSE时钟出现故障时将产生CSS中断,同时自动产生 NMI。

NMI将被不断执行,直到CSS中断挂起位被清除。

因此,在NMI的处理程序中必须通过设置时钟中断寄存器(RCC_CIR)里的CSSC位来清除CSS中断。

2、SysTick工作原理Cortex-M3的内核中包含一个SysTick时钟。

STM32 中断向量表的位置 、重定向

STM32 中断向量表的位置、重定向我们也知道怎么跳到main 函数了,那么,中断发生后,又是怎么跑到中断入口地址的呢?从stm32f10x.s 可以看到,已经定义好了一大堆的中断响应函数,这就是中断向量表,标号__Vectors,表示中断向量表入口地址,例如:AREA RESET, DATA, READONLY ;定义只读数据段,实际上是在CODE区(假设STM32 从FLASH 启动,则此中断向量表起始地址即为0x8000000)EXPORT __VectorsIMPORT OS_CPU_SysTickHandler IMPORTOS_CPU_PendSVHandler__Vectors DCD __initial_sp ; Top of Stack DCD Reset_Handler ; Reset Handler DCD NMI_Handler ; NMI Handler DCD HardFault_Handler ; Hard Fault Handler DCD MemManage_Handler ; MPU Fault Handler DCD BusFault_Handler ; Bus Fault Handler DCD UsageFault_Handler ; Usage Fault Handler这个向量表的编写是有讲究的,跟硬件一一对应不能乱写的,CPU 找入口地址就靠它了,bin 文件开头就是他们的地址,参考手册RM0008 的10.1.2 节可以看到排列。

我们再结合CORTEX-M3 的特性,他上电后根据boot 引脚来决定PC 位置,比如boot 设置为flash 启动,则启动后PC 跳到0x08000000。

此时CPU 会先取2 个地址,第一个是栈顶地址,第二个是复位异常地址,故有了上面的写法,这样就跳到reset_handler。

那么这个reset_handler 的实际地址是多少.?下面的一堆例如Nmi_handler 地址又是多少呢?发生中断是怎么跑到这个地址的呢?下面挨个讲解。

STM32学习记录12 中断向量表

STM32 学习记录12 中断向量表从stm32f10x.s 可以看到,已经定义好了一大堆的中断响应函数,这就是中断向量表,标号__Vectors,表示中断向量表入口地址,例如:AREA RESET, DATA, READONLY ;定义只读数据段,实际上是在CODE 区(假设STM32 从FLASH 启动,则此中断向量表起始地址即为0x8000000)EXPORT__VectorsIMPORT OS_CPU_SysTickHandler IMPORTOS_CPU_PendSVHandler__Vectors DCD __initial_sp ; Top of Stack DCD Reset_Handler ; Reset Handler DCD NMI_Handler ; NMI Handler DCD HardFault_Handler ; Hard Fault Handler DCD MemManage_Handler ; MPU Fault Handler DCD BusFault_Handler ; Bus Fault Handler DCD UsageFault_Handler ; Usage Fault Handler这个向量表的编写是有讲究的,跟硬件一一对应不能乱写的,CPU 找入口地址就靠它了,bin 文件开头就是他们的地址,参考手册RM0008 的10.1.2 节可以看到排列。

我们再结合CORTEX-M3 的特性,他上电后根据boot 引脚来决定PC 位置,比如boot 设置为flash 启动,则启动后PC 跳到0x08000000。

此时CPU 会先取2 个地址,第一个是栈顶地址,第二个是复位异常地址,故有了上面的写法,这样就跳到reset_handler。

那么这个reset_handler 的实际地址是多少.?下面的一堆例如Nmi_handler 地址又是多少呢?发生中断是怎么跑到这个地址的呢?下面挨个讲解。

关于STM32的IAP与APP互相跳转常见问题分析

关于STM32的IAP与APP互相跳转常见问题分析关于STM32 的IAP 与APP 互相跳转之前做了一个不带系统的IAP 与APP 互相跳转,在网上找了资料后,很顺畅就完成了,后来在IAR 集成开发环境下,IAP 无系统,APP 用UCOS 系统做互相跳转出现了很多问题。

现将IAP 学习过程和实际遇到问题总结一下。

首先说一下什么是IAP。

IAP(In Application Programming)即在应用编程,IAP 是用户自己的程序在运行过程中对User Flash 的部分区域进行烧写,目的是为了在产品发布后可以方便地通过预留的通信口对产品中的固件程序进行更新升级。

通常实现IAP 功能时,即用户程序运行中作自身的更新操作,需要在设计固件程序时编写两个项目代码,第一个项目程序不执行正常的功能操作,而只是通过某种通信方式(如USB、USART)接收程序或数据,执行对第二部分代码的更新;第二个项目代码才是真正的功能代码。

以上内容摘自原子的开发指南。

说的通俗一点,要做IAP 功能(也可以说成是远程升级功能),需要有两段程序一个是IAP 程序(也可以称为BootLoader),另一个是APP 程序(主应用程序)。

通过USB、串口、CAN 等通讯方式向STM32 发送要升级的程序文件数据(按自定的协议),IAP 程序中将接收到的数据写到APP 程序的地址实现将APP 程序的升级。

这是大致的流程。

此文档只做互相跳转的总结不包含接收数据、FLASH 写入等操作。

说到IAP 升级不得不说两个图(图片引自原子的开发指南)第一个是正常运行时的流程图STM32 的FLASH 地址起始于0x08000000,程序文件就从此地址开始写入。

此外STM32 内部通过“中断向量表”来响应中断,程序启动后,将首先从“中断向量表”取出复位中断向量执行复位中断程序完成启动,而“中断向量表”的起始。

stm32定时器中断配置

stm32 定时器中断配置

stm32 中断

stm32 的Cortex 内核具有强大的异常响应系统,它把能够打断当前代码执行流程的事件分为异常(excepTIon)和中断(terryp),并把它们用二个表管理起来,编号为0~15 的称为内核异常,而16 以上的则称为外部中断(外,相对内核而言),这个表就称为中断向量表。

而STM32 对这个表重新进行了编排,把编号从-3 至6 的中断向量定义为系统异常,编号为负的内核异常不能被设置优先级,如复位(Reset)、不可屏蔽中断(NMI)、硬错误(Hardfault)。

从编号7 开始的为外部中断,这些中断的优先级都是可以自行设置的。

STM32 的中断如此之多,配置起来并不容易,因此,我们需要一个

强大而方便的中断控制器NVIC,NVIC 是属于Cortex 内核的器件。

stm32 中断配置

配置STM32 的中断只需要理解2 个内容,配置4 个变量即可。

第5章 stm32单片机外部中断1

5.3.3 相关功能寄存器

EXTI_IMR(Interrupt mask register )中断屏蔽寄存器

5.3.3 相关功能寄存器

EXTI_EMR( Event mask register )中断事件屏蔽寄存器

5.3.3 相关功能寄存器

EXTI_RTSR(Rising trigger selection register)上升沿触发寄存器

5.3.2 中断控制器

具体有哪些外部中断,在“stm32f10x_nvic.h”这个头文件中 已经定义

5.3.2 中断控制器

5.3.2 中断控制器

ICER[2]:全称Interrupt Clear-Enable Registers,是 一个中断清除使能寄存器组。 该寄存器组与ISER寄存器功能相反,用来清除某个 中断的使能位。由于NVIC的这些寄存器都是写1有 效的,写0是无效的。设置一组ICER 寄存器来清除 相应中断使能位。 ISPR[2]:全称Interrupt Set-Pending Registers,是 一个中断挂起控制寄存器组。 每个位对应的外部中断和ISER内容是一样的。通过 向相应的位写1,可以将正在执行的中断挂起,去执 行同级或更高级别的中断。向这个寄存器组写0是无 效的。

抢占优先级和响应优先级

假定设置中断优先级为组2,然后设置: 中断3(RTC中断)的抢占优先级为2,响应优先级为1。 中断6(外部中断0)的抢占优先级为3,响应优先级为0。 中断7(外部中断1)的抢占优先级为2,响应优先级为0。 求这3个中断的优先级顺序? 上面例子中的中断3和中断7都可以打断中断6 的中断。而中 断7和中断3却不可以相互打断(这是因为他们的抢占优先级 是相同的)。

5.3.2 中断控制器

STM32在SRAM、FLASH中调试代码的配置方法

STM32的FLASH擦写次数有限(大概为1万次),所以为了延长FLASH的使用时间,我们平时调试时可以选择在SRAM中进行硬件调试。

除此之外,SRAM 存储器的写入速度比在内部FLASH 中要快得多,所以下载程序到SRAM中的速度较快。

所以我们很有必要建立两个版本的工程配置,在SRAM中调试程序完毕后,再把代码下载到FLASH中即可。

这篇笔记主要分享在keil5中配置FLASH调试与SRAM调试的详细配置方法及如何切换两种配置。

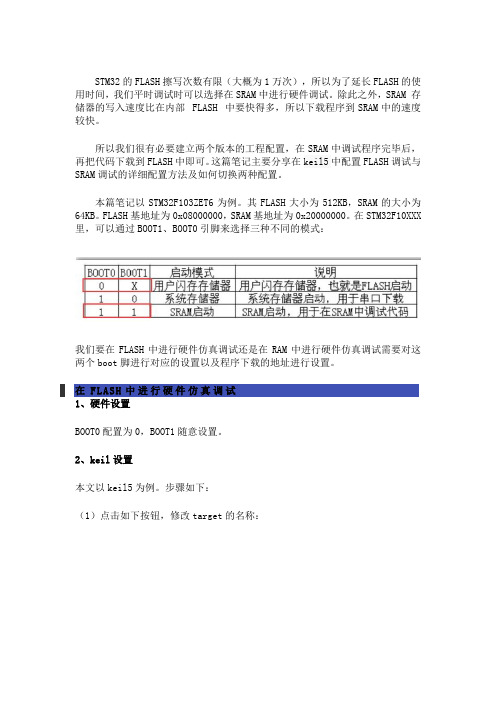

本篇笔记以STM32F103ZET6为例。

其FLASH大小为512KB,SRAM的大小为64KB。

FLASH基地址为0x08000000,SRAM基地址为0x20000000。

在STM32F10XXX 里,可以通过BOOT1、BOOT0引脚来选择三种不同的模式:我们要在FLASH中进行硬件仿真调试还是在RAM中进行硬件仿真调试需要对这两个boot脚进行对应的设置以及程序下载的地址进行设置。

在F L A S H中进行硬件仿真调试1、硬件设置BOOT0配置为0,BOOT1随意设置。

2、keil设置本文以keil5为例。

步骤如下:(1)点击如下按钮,修改target的名称:target的名称是可以随意更改的,这里我们改为FLASH。

(2)点击Project->Options for Target Flash...(也可以点击魔术棒那个图标)进行配置。

首先对Target选项卡设置:设置IROM1的起始地址为0x8000000,大小为0x80000,即FLASH的基地址与大小。

设置IRAM1为0x20000000,大小为0x10000,即SRAM的基地址与大小。

(3)Debug选项设置:调试器根据实际进行选择,我们这里使用的调试器是ULINK2。

其它的按默认设置即可,然后点击Settings:(4)编译,然后按Ctrl+F5进入调试界面:然后点击全速运行:在Disassembly窗口中可看到地址为0x0800xxxx,说明代码烧进了FLASH中,这时候就可以像使用其他C语言IDE调试C语言程序一样打断点、单步运行我们的STM32程序啦。

查看stm32的SysTick中断的优先级,比外设中断优先级高吗?

查看stm32的SysTick中断的优先级,⽐外设中断优先级⾼吗?默认SysTick中断优先级1//core_cm4.h23 __STATIC_INLINE uint32_t SysTick_Config(uint32_t ticks)4 {5if ((ticks - 1UL) > SysTick_LOAD_RELOAD_Msk) { return (1UL); } /* Reload value impossible */67 SysTick->LOAD = (uint32_t)(ticks - 1UL); /* set reload register */8 NVIC_SetPriority (SysTick_IRQn, (1UL << __NVIC_PRIO_BITS) - 1UL); /* set Priority for Systick Interrupt */9 SysTick->VAL = 0UL; /* Load the SysTick Counter Value */10 SysTick->CTRL = SysTick_CTRL_CLKSOURCE_Msk |11 SysTick_CTRL_TICKINT_Msk |12 SysTick_CTRL_ENABLE_Msk; /* Enable SysTick IRQ and SysTick Timer */13return (0UL); /* Function successful */14 }第8⾏设置了SysTick中断的优先级,#define __NVIC_PRIO_BITS 4 /*!< STM32F4XX uses 4 Bits for the Priority Levels */在看NVIC_SetPriority函数:NVIC_SetPriority对中断分了类,分内核中断和外设中断,内核外设中断枚举值⼩于0,普通外设>=0。

stm32中断(NVIC与EXTI)

stm32中断(NVIC与EXTI) D部有4个从优先级(00 01 10 11)。

1.中断输入与悬起当中断输入脚被置为有效后,该中断就被“悬起”。

所谓“悬起”,也就是等待、就绪的意思。

即使后来中断源撤消了中断请求,已经被标记成悬起的中断也被记录下来。

当某中断的服务程序开始执行时,就称此中断进入了“活跃”状态,并且其悬起位会被硬件自动清除。

在一个中断活跃后,直到其服务例程执行完毕,并且返回后,才能对该中断的新请求予以响应。

当NVIC响应一个中断时,会自动完成以下三项工作,以便安全、准确地跳转到相应的中断服务程序:入栈:把8个寄存器的值压入栈。

当响应中断时,如果当前的代码正在使用PSP,则压入PSP(进程堆栈),否则就压入MSP(主堆栈)。

一旦进入了服务例程,就一直使用主堆栈。

在自动入栈的过程中,将寄存器写入堆栈的顺序与时间顺序无关,CM3会保证正确的寄存器被保存到正确的位置。

取向量:当数据总线(系统总线)进行入栈操作时,指令总线(I-Code总线)正在从向量表中找出正确的中断向量与对应的服务程序入口地址。

更新寄存器。

注意:①如果在某个中断得到响应之前,其悬起状态被清除了,则中断被取消。

②新请求在得到响应时,由硬件自动清零其悬起标志位。

③如果中断源咬住请求信号不放,该中断就会在其上次服务例程返回后再次被置为悬起状态。

④如果某个中断在得到响应之前,其请求信号以若干的脉冲的方式呈现,则被视为只有一次中断请求⑤如果在服务例程执行时,中断请求释放了,但是在服务例程返回前又重新被置为有效,则NVIC会记住此动作,重新悬起该中断。

2.中断返回当中断完成,返回主程序时,NVIC自动完成以下两步:①出栈:先前压入栈中的寄存器在这里恢复。

内部的出栈顺序与入栈时的相对应,堆栈指针的值也改回先前的值。

②更新NVIC 寄存器:伴随着中断的返回,它的活动位也被硬件清除。

对于外部中断,倘若中断输入再次被置为有效,则悬起位也将再次置位,新一次的中断响应序列也会再次开始。

STM32手册中找不到的寄存器说明

STM32手册中找不到的寄存器说明在STM32中用到了Cortex-M3定义的三组寄存器,有关这三组寄存器的说明不在STM32的技术手册中,需要参考ARM公司发布的Cortex-M3 Technical Reference Manual (r2p0)。

在STM32的固件库中定义了三个结构体与这三个寄存器组相对应,这三个结构体与ARM手册中寄存器的对应关系如下:一、NVIC寄存器组STM32的固件库中有如下定义:typedef struct{vu32 ISER[2];u32 RESERVED0[30];vu32 ICER[2];u32 RSERVED1[30];vu32 ISPR[2];u32 RESERVED2[30];vu32 ICPR[2];u32 RESERVED3[30];vu32 IABR[2];u32 RESERVED4[62];vu32 IPR[11];} NVIC_TypeDef;它们对应ARM手册中的名称为ISER = Interrupt Set-Enable RegistersICER = Interrupt Clear-Enable RegistersISPR = Interrupt Set-Pending RegisterICPR = Interrupt Clear-Pending RegisterIABR = Active Bit RegisterIPR = Interrupt Priority Registers每个寄存器有240位,以Interrupt Set-Enable Registers说明,ISER[0]对应中断源0~31,ISER[1]对应中断源32~63,STM32只有60个中断源,所以没有ISER[2:7]。

参考STM32技术参考手册中的中断向量表,中断源的位置为:位置0 - WWDG = Window Watchdog interrupt位置1 - PVD = PVD through EXTI Line detection interrupt位置2 - TAMPER = Tamper interrupt......位置58 - DMA2_Channel3 = DMA2 Channel3 global interrupt位置59 - DMA2_Channel4_5 = DMA2 Channel4 and DMA2 Channel5 global interrupts二、系统控制寄存器组STM32的固件库中有如下定义:typedef struct{vuc32 CPUID;vu32 ICSR;vu32 VTOR;vu32 AIRCR;vu32 SCR;vu32 CCR;vu32 SHPR[3];vu32 SHCSR;vu32 CFSR;vu32 HFSR;vu32 DFSR;vu32 MMFAR;vu32 BFAR;vu32 AFSR;} SCB_TypeDef; /* System Control Block Structure */它们对应ARM手册中的名称为CPUID = CPUID Base RegisterICSR = Interrupt Control State RegisterVTOR = Vector Table Offset RegisterAIRCR = Application Interrupt/Reset Control Register SCR = System Control RegisterCCR = Configuration Control RegisterSHPR = System Handlers Priority RegisterSHCSR = System Handler Control and State Register CFSR = Configurable Fault Status RegistersHFSR = Hard Fault Status RegisterDFSR = Debug Fault Status RegisterMMFAR = Mem Manage Address RegisterBFAR = Bus Fault Address RegisterAFSR = Auxiliary Fault Status Register三、系统时钟寄存器组STM32的固件库中有如下定义:typedef struct{vu32 CTRL;vu32 LOAD;vu32 VAL;vuc32 CALIB;} SysTick_TypeDef;它们对应ARM手册中的名称为CTRL = SysTick Control and Status Register LOAD = SysTick Reload Value Register VAL = SysTick Current Value Register CALIB = SysTick Calibration Value Register。

STM32 硬件IIC中断使用方法

STM32 硬件IIC中断使用方法--中北大学:马政贵本文详细描述了STM32硬件IIC的中断使用方法,包含流程图和对应代码,以及调试过程中的问题记录和分析解决。

之前,一直听说STM32的硬件IIC有问题,加之以前写好的模拟IIC模块用着一直没问题,就没有去使用STM32的硬件IIC。

后面项目中需要实时读取三个传感器的数据,三个传感器并在一起共用一个IIC口,通过地址进行区分通信,一个传感器要读取8字节数据。

采用模拟IIC方式,很多时间都浪费在高低电平的等待时间上,导致其他任务时间很紧迫。

于是想到使用硬件IIC的中断方式,来提升效率。

查看了下库自带的例程,使用的是查询方式,使用了大量的while来等待状态标志完成。

移植过来,虽然可以跑通,但使用的是查询方式,效率本质上和模拟IIC是一样的。

于是自己便把手册里的IIC模块看了一遍,自己根据手册来写硬件IIC的中断模式。

上图是传感器的通讯时序,属于标准的IIC通信,这里不做进一步展开,详细可以参看IIC总线规范。

应用中,MCU做主机,传感器做从机。

MCU先工作在主发送器模式,然后工作在主接收器模式。

在默认状态下,MCU接口工作于从模式。

接口在生成起始条件后自动地从从模式切换到主模式;当仲裁丢失或产生停止信号时,则从主模式切换到从模式。

在应用手册中,详细给出了IIC主模式的操作要求及顺序:这里需要注意的是怎样结束通信,然后重启通信,以便获取下一个传感器的数据。

应用手册根据情况分为了三种,我这里使用的是第一种方式,也就是把IIC的中断优先级设置为最高。

下面我以流程图的方式,把整个过程表示出来,然后再据此给出相应的代码,代码在中断中以状态机的方式进行。

先进行IIC管脚GPIO的配置:接着进行IIC的配置(中断先不使能,在初始化完传感器之后再使能。

我这里把IIC的事件中断优先级设置为最高,若不是,IIC的结束操作需参照应用手册中相应的情况进行):中断中的状态机如下:void I2C2_EV_IRQHandler(void){switch(IIC2_State){case 0:if(I2C_GetINTStatus(I2C2, I2C_INT_STARTF)){I2C_ClearITPendingBit(I2C2, I2C_INT_STARTF);(void)(I2C2->STS1);I2C_Send7bitAddress(I2C2, ALS31300_ADR[IIC_Device], I2C_Direction_Transmit);IIC2_State++;}else{I2C2->STS1 = 0;}break;case 1:if(I2C_GetINTStatus(I2C2, I2C_INT_ADDRF)){I2C_ClearITPendingBit(I2C2, I2C_INT_ADDRF);(void)(I2C2->STS1);(void)(I2C2->STS2);I2C_SendData(I2C2, 0x28);IIC2_State++;}else{I2C2->STS1 = 0;}break;case 2:if(I2C_GetINTStatus(I2C2, I2C_INT_TDE)){I2C_ClearITPendingBit(I2C2, I2C_INT_TDE);I2C_ClearITPendingBit(I2C2, I2C_INT_BTFF);(void)(I2C2->STS1);I2C_GenerateSTART(I2C2, ENABLE); /* Send STRAT condition a second time */IIC2_State++;}else{I2C2->STS1 = 0;}break;case 3:if(I2C_GetINTStatus(I2C2, I2C_INT_STARTF)){I2C_ClearITPendingBit(I2C2, I2C_INT_STARTF);(void)(I2C2->STS1);I2C_Send7bitAddress(I2C2, ALS31300_ADR[IIC_Device],I2C_Direction_Receive);IIC2_State++;}else{I2C2->STS1 = 0;}break;case 4:if(I2C_GetINTStatus(I2C2, I2C_INT_ADDRF)){I2C_ClearITPendingBit(I2C2, I2C_INT_ADDRF);(void)(I2C2->STS1);(void)(I2C2->STS2);IIC2_State++;}else{I2C2->STS1 = 0;}break;case 5:if(I2C_GetINTStatus(I2C2, I2C_INT_RDNE)){I2C_ClearITPendingBit(I2C2, I2C_INT_RDNE);(void)(I2C2->STS1);ALS31300_Reg_Data[IIC_Device][IIC_Rec_Num] = I2C_ReceiveData(I2C2);IIC_Rec_Num++;if(IIC_Rec_Num >= 6){IIC2_State++;}}else{I2C2->STS1 = 0;}break;case 6:if(I2C_GetINTStatus(I2C2, I2C_INT_RDNE)){I2C_ClearITPendingBit(I2C2, I2C_INT_RDNE);(void)(I2C2->STS1);ALS31300_Reg_Data[IIC_Device][IIC_Rec_Num] = I2C_ReceiveData(I2C2);I2C_AcknowledgeConfig(I2C2, DISABLE);I2C_GenerateSTOP(I2C2, ENABLE);IIC_Rec_Num++;IIC2_State++;}else{I2C2->STS1 = 0;}break;case 7:if(I2C_GetINTStatus(I2C2, I2C_INT_RDNE)){I2C_ClearITPendingBit(I2C2, I2C_INT_RDNE);(void)(I2C2->STS1);ALS31300_Reg_Data[IIC_Device][IIC_Rec_Num] =I2C_ReceiveData(I2C2);IIC_Device++;if(IIC_Device >= 3){IIC_Device = 0;IIC_Rec_OK = 1;}I2C_AcknowledgeConfig(I2C2, ENABLE);I2C_GenerateSTART(I2C2, ENABLE);IIC_Rec_Num = 0;IIC2_State = 0;}else{I2C2->STS1 = 0;}break;default:I2C2->STS1 = 0;break;}}初始化之后,产生开始信号之后,使能中断,此后就一直在中断的状态机中往复进行了:#define IIC_TIMEOUT 1000IIC2_GPIO_Config();IIC2_Config();time_count = IIC_TIMEOUT;while(I2C_GetFlagStatus(I2C2, I2C_FLAG_BUSYF)){time_count--;if(0 == time_count){IIC_Wrong_Count++;return;}}I2C_AcknowledgeConfig(I2C2, ENABLE);I2C_GenerateSTART(I2C2, ENABLE);//初始化之后再开中断,只在读操作中使用中断I2C_INTConfig(I2C2, I2C_INT_EVT | I2C_INT_BUF | I2C_INT_ERR, ENABLE);编译调试,咦,状态机一直停留在0状态,也就是卡在总线一直BUSY。

stm32中断优先级的处理原则

STM32中断优先级的处理原则1. 引言在嵌入式系统中,中断是一种常用的机制,用于在特定事件发生时打断CPU的正常执行流程,转而执行特定的中断处理程序。

STM32系列微控制器提供了丰富的中断控制功能,并支持多个优先级的中断。

正确设置中断优先级是确保系统稳定性和可靠性的重要步骤。

本文将介绍STM32中断优先级处理原则,包括如何设置优先级、不同类型中断之间的关系以及注意事项等内容。

2. 中断优先级概述STM32微控制器支持多个优先级的中断,其中数字越小表示优先级越高。

当多个中断同时发生时,只有具有最高优先级的中断会被响应。

其他低优先级的中断将被挂起,等待当前正在处理的高优先级中断完成后再进行处理。

每个STM32微控制器都有一个向量表(Vector Table),其中存储了各个中断向量及其对应的ISR(Interrupt Service Routine)。

在初始化过程中,需要将需要使用到的ISR函数指针写入向量表相应位置。

3. 中断优先级设置原则在STM32微控制器上配置和设置各个外设的中断优先级时,需要遵循以下原则:3.1 高优先级中断的响应时间高优先级中断的响应时间应尽量短,以确保系统对紧急事件的及时响应。

通常情况下,系统启动和初始化过程中会配置一些必要的高优先级中断,如系统滴答定时器(SysTick)等。

3.2 低优先级中断的执行时间低优先级中断可能会被高优先级中断打断,在高优先级中断执行期间无法得到处理。

因此,低优先级中断的执行时间应尽量短,以减少对系统性能和实时性的影响。

STM32微控制器支持不同外设之间和相同外设内部的中断嵌套。

在设置嵌套中断时,需要注意以下原则: - 外设之间:不同外设之间的中断嵌套顺序应根据具体需求和业务逻辑进行设置。

- 外设内部:在具有多个可触发相同类型中断源的外设上,需要根据业务需求设置不同源之间的触发次序。

3.4 中断抢占与屏蔽STM32微控制器支持中断的抢占和屏蔽功能。