Makefile两个实验教案

Makefile编程实验

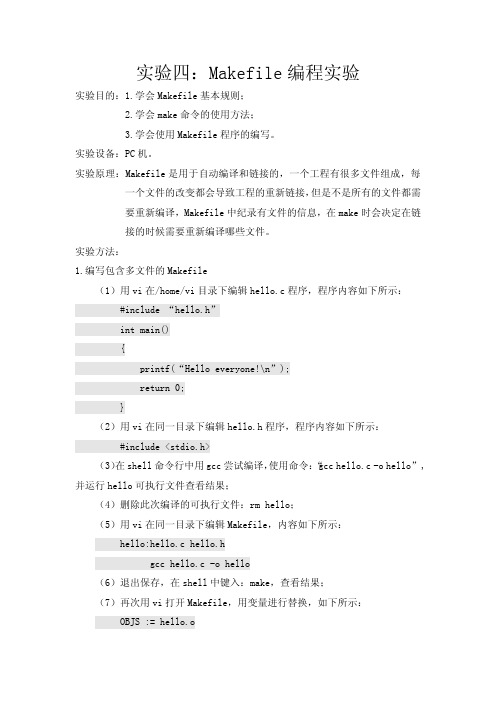

实验四:Makefile编程实验实验目的:1.学会Makefile基本规则;2.学会make命令的使用方法;3.学会使用Makefile程序的编写。

实验设备:PC机。

实验原理:Makefile是用于自动编译和链接的,一个工程有很多文件组成,每一个文件的改变都会导致工程的重新链接,但是不是所有的文件都需要重新编译,Makefile中纪录有文件的信息,在make时会决定在链接的时候需要重新编译哪些文件。

实验方法:1.编写包含多文件的Makefile(1)用vi在/home/vi目录下编辑hello.c程序,程序内容如下所示:#include“hello.h”int main(){printf(“Hello everyone!\n”);return0;}(2)用vi在同一目录下编辑hello.h程序,程序内容如下所示:#include<stdio.h>(3)在shell命令行中用gcc尝试编译,使用命令:“gcc hello.c-o hello”,并运行hello可执行文件查看结果;(4)删除此次编译的可执行文件:rm hello;(5)用vi在同一目录下编辑Makefile,内容如下所示:hello:hello.c hello.hgcc hello.c-o hello(6)退出保存,在shell中键入:make,查看结果;(7)再次用vi打开Makefile,用变量进行替换,如下所示:OBJS:=hello.oCC:=gcchello:$(OBJS)$(CC)$^-o$@(8)退出保存,在shell中键入make,查看结果;(9)用vi在同一目录下编辑makefile1,内容如下所示:hello:hello.ogcc hello.o-o hellohello.o:hello.c hello.hgcc-c hello.c-o hello.o(10)退出保存,在shell中键入:make-f makefile1,查看结果;(11)再次用vi编辑makefile1,内容如下所示:OBJS1:=hello.oOBJS2:=hello.c hello.hCC:=gcchello:$(OBJS1)$(CC)$^-o$@$(OBJS1):$(OBJS2)$(CC)-c$<-o$@在这里请注意区别“$^”和“$<”;(12)退出保存,在shell中键入:make-f makefile1,查看结果;2.使用autotools生成包含多文件的Makefile(1)在/home/vi目录下新建文件夹auto:#mkdir./auto(2)将/home/vi目录下的hello.c和hello.h文件复制到/home/vi/auto 目录下,然后进入到/home/vi/auto目录里面:#cp/home/vi/hello.*/home/vi/auto#cd/home/vi/auto(3)执行命令:#autoscan(4)使用vi编辑当前目录下的configure.scan文件为,主要是蓝色部分:#-*-Autoconf-*-#Process this file with autoconf to produce a configure script.AC_PREREQ(2.59)AC_INIT(hello, 1.0)AM_INIT_AUTOMAKE(hello,1.0)AC_CONFIG_SRCDIR([hello.h])AC_CONFIG_HEADER([config.h])#Checks for programs.AC_PROG_CC#Checks for libraries.#Checks for header files.#Checks for typedefs,structures,and compiler characteristics.#Checks for library functions.AC_OUTPUT(makefile)(5)保存退出,并重命名为configure.in;(6)执行命令:#aclocal(7)执行命令:#autoconf并用ls或ll命令查看是否生成了configure可执行文件;(8)执行命令:#autoheader(9)在当前目录下用vi创建makefile.am文件为:AUTOMAKE_OPTIONS=foreignbin_PROGRAMS=hellohello_SOURCES=hello.c hello.h(10)执行命令:#automake然后再执行下面的命令:#automake-a(11)执行命令:#./configure(12)执行命令:#make(13)执行命令:#./hello查看结果是否正确;(14)执行命令:#Make install(15)执行命令:#hello查看结果是否正确;(16)执行命令:#make dist(17)在当前目录下解压文件hello-1.0.tar.gz:#tar-zxvf hello-1.0.tar.gz(18)进入解压目录:#cd./hello-1.0(19)下面开始Linux下常见的安装软件步骤:#./configure(20)执行命令:#make(21)执行命令:#./hello注意:在正常安装时这一步可省略;(22)执行命令:#make install(23)执行命令:#hello查看结果是否正确。

Makefile两个实验

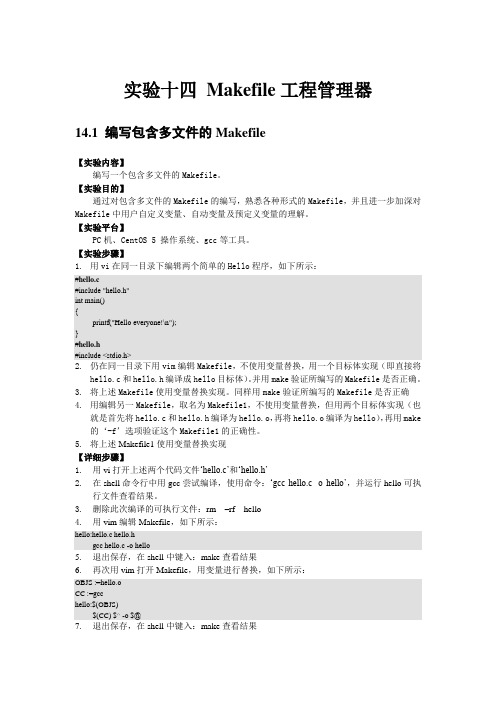

实验十四Makefile工程管理器14.1 编写包含多文件的Makefile【实验内容】编写一个包含多文件的Makefile。

【实验目的】通过对包含多文件的Makefile的编写,熟悉各种形式的Makefile,并且进一步加深对Makefile中用户自定义变量、自动变量及预定义变量的理解。

【实验平台】PC机、CentOS 5 操作系统、gcc等工具。

【实验步骤】1.用vi在同一目录下编辑两个简单的Hello程序,如下所示:#hello.c#include "hello.h"int main(){printf("Hello everyone!\n");}#hello.h#include <stdio.h>2.仍在同一目录下用vim编辑Makefile,不使用变量替换,用一个目标体实现(即直接将hello.c和hello.h编译成hello目标体)。

并用make验证所编写的Makefile是否正确。

3.将上述Makefile使用变量替换实现。

同样用make验证所编写的Makefile是否正确4.用编辑另一Makefile,取名为Makefile1,不使用变量替换,但用两个目标体实现(也就是首先将hello.c和hello.h编译为hello.o,再将hello.o编译为hello),再用make 的‘-f’选项验证这个Makefile1的正确性。

5.将上述Makefile1使用变量替换实现【详细步骤】1.用vi打开上述两个代码文件‘hello.c’和‘hello.h’2.在shell命令行中用gcc尝试编译,使用命令:‘gcc hello.c -o hello’,并运行hello可执行文件查看结果。

3.删除此次编译的可执行文件:rm –rf hello4.用vim编辑Makefile,如下所示:hello:hello.c hello.hgcc hello.c -o hello5.退出保存,在shell中键入:make查看结果6.再次用vim打开Makefile,用变量进行替换,如下所示:OBJS :=hello.oCC :=gcchello:$(OBJS)$(CC) $^ -o $@7.退出保存,在shell中键入:make查看结果8.用vim编辑Makefile1,如下所示:hello:hello.ogcc hello.o -o hellohello.o:hello.c hello.hgcc -c hello.c -o hello.o9.退出保存,在shell中键入:make –f Makefile1查看结果10.再次用vi编辑Makefile1,如下所示:OBJS1 :=hello.oOBJS2 :=hello.c hello.hCC :=gcchello:$(OBJS1)$(CC) $^ -o $@$(OBJS1):$(OBJS2)$(CC) -c $< -o $@在这里请注意区别‘$^’和‘$<’。

linux实验二交叉编译和Makefile实验报告

[root @localhost hehui]# ./hmily

④使用交叉编译器编译并运行。

A.[root @localhost hehui]# arm-linux-gcc -o hmily ji_oushu.c

B.打开另外一个终端,输入minicom进入板子里去。

C.操作一下命令。

[root @localhost ~]# cd 2008550533

[root @localhost 2008550533]# mkdir hehui

[root @localhost ~]# cd hehui

[root @localhost hehui]# vi ji_oushu.c

/*输出50以内的奇数和偶数*/

④使用gcc编译,查看运行结果。

[root @localhost prime]# gcc prime.c -oprime_hehui

[root @localhost prime]# ./prime_hehui

⑤编写Makefile文件实现第④步功能,并使用make工具生成这个可执行文件。

[root @localhost prime]# rm -r prime_hehui

all:prime

prime:prime.o main.o

$(CC) $(CFLAGS) $^ -o $@

prime.o:prime.c

$(CC) $(CFLAGS) -c $< -o $@

main.o:main.c prime.h

$(CC) $(CFLAGS) -c $< -o $@

clean:

rm -fr prime_hehui *.o

clean: 37

实验二 Makefile实验

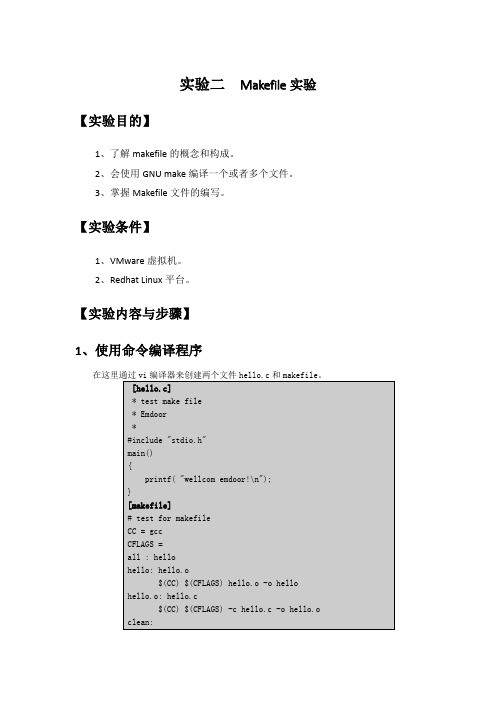

实验二M akefile实验【实验目的】1、了解makefile的概念和构成。

2、会使用GNU make编译一个或者多个文件。

3、掌握Makefile文件的编写。

【实验条件】1、VMware虚拟机。

2、Redhat Linux平台。

【实验内容与步骤】1、使用命令编译程序在这里通过vi编译器来创建两个文件hello.c和makefile。

[hello.c]* test make file* Emdoor*#include "stdio.h"main(){printf( "wellcom emdoor!\n");}[makefile]# test for makefileCC = gccCFLAGS =all : hellohello: hello.o$(CC) $(CFLAGS) hello.o -o hellohello.o: hello.c$(CC) $(CFLAGS) -c hello.c -o hello.o clean:在将上述Makefile文件与源文件hello.c保存到同一目录之后,就可以在命令行中输入“make”命令来编译整个项目了。

make在执行过程中,首先会查找到Makefile文件第一条规则中的目标,即上述文件中的all。

根据设定好的规则,该目标需要依赖于hello。

由于all并不是一个已经存在的文件,所以每次在make被调用的时候,显然都需要先检查hello。

继续往下不难发现,hello目标是依赖于hello.o。

当make处理到目标hello.o时,会先查看其对应的依赖对象,这个以来对象是hello.c,此时就会对hello.c进行编译,得到目标文件hello.o,然后是目标文件hello.o被连接,得到可执行文件hello。

先后执行如下命令:可以看到输出结果:在Makefile中,并不是所有的目标都对应于磁盘上的文件。

有的目标存在只是为了形成一条规则,从而完成特定的工作,并不生成新的目标文件,这样的目标称为伪目标。

实验二 Makefile实验

6

Makefile主要预定义变量及隐含 规则

预定义变量及其含义 CC CCFLAGS …… GNU make 支持两种类型的隐含规则: 后缀规则(Suffix Rule) 模式规则(pattern rules)

亿道电子有限公司出品

亿道电子有限公司出品

4

Makefile的基本结构

目标 --- 需要由 make 工具创建的项目, 通常是目标文件和可执行文件 。 依赖 ---要创建的项目依赖于哪些文件 命令 ---创建每个项目时需要运行的命令 target : dependency ...

make编译一个或者多个文件

亿道电子有限公司出品

3

Makefile的规则

如果这个工程没有编译过,那么我们的所 有C文件都要编译并被链接。 如果这个工程的某几个C文件被修改,那 么我们只编译被修改的C文件,并链接目 标程序。 如果这个工程的头文件被改变了,那么我 们需要编译引用了这几个头文件的C文件, 并链接目标程序。

亿道电子有限公司出品

12

思考与习题

工程中多级目录中存在着多个makefile时, 编译的顺序如何? 如果要编译生成的文件能够在EELIOD实验 平台上面使用,应该怎么对makefile修改?

亿道电子有限公司出品

13

亿道电子有限公司出品

10

使用wildcard对多个.c文件编译

wildcard’函数的一个功能是找出目录中所 有的’.c’文件: $(wildcard *.c) SOURCES = $(wildcard *.c) 这行会产生一个所有以 '.c' 结尾的文件 的列表,然后存入变量 SOURCES 里。 当然你不需要一定要把结果存入一个变量。

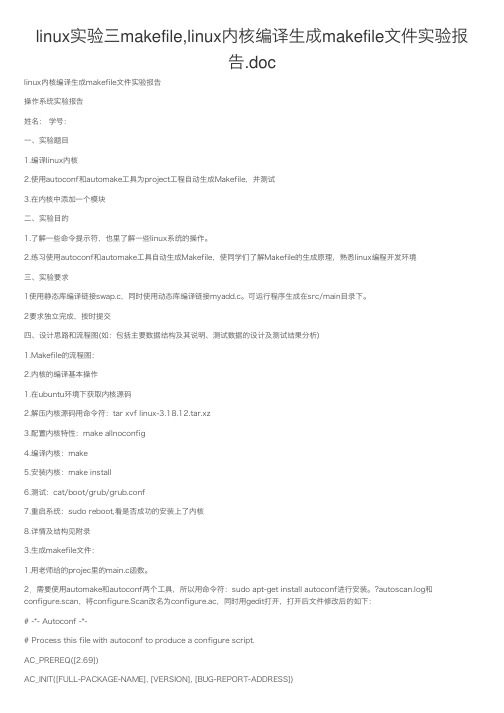

linux实验三makefile,linux内核编译生成makefile文件实验报告.doc

linux实验三makefile,linux内核编译⽣成makefile⽂件实验报告.doclinux内核编译⽣成makefile⽂件实验报告操作系统实验报告姓名: 学号:⼀、实验题⽬1.编译linux内核2.使⽤autoconf和automake⼯具为project⼯程⾃动⽣成Makefile,并测试3.在内核中添加⼀个模块⼆、实验⽬的1.了解⼀些命令提⽰符,也⾥了解⼀些linux系统的操作。

2.练习使⽤autoconf和automake⼯具⾃动⽣成Makefile,使同学们了解Makefile的⽣成原理,熟悉linux编程开发环境三、实验要求1使⽤静态库编译链接swap.c,同时使⽤动态库编译链接myadd.c。

可运⾏程序⽣成在src/main⽬录下。

2要求独⽴完成,按时提交四、设计思路和流程图(如:包括主要数据结构及其说明、测试数据的设计及测试结果分析)1.Makefile的流程图:2.内核的编译基本操作1.在ubuntu环境下获取内核源码2.解压内核源码⽤命令符:tar xvf linux-3.18.12.tar.xz3.配置内核特性:make allnoconfig4.编译内核:make5.安装内核:make install6.测试:cat/boot/grub/grub.conf7.重启系统:sudo reboot,看是否成功的安装上了内核8.详情及结构见附录3.⽣成makefile⽂件:1.⽤⽼师给的projec⾥的main.c函数。

2.需要使⽤automake和autoconf两个⼯具,所以⽤命令符:sudo apt-get install autoconf进⾏安装。

?autoscan.log和configure.scan,将configure.Scan改名为configure.ac,同时⽤gedit打开,打开后⽂件修改后的如下:# -*- Autoconf -*-# Process this file with autoconf to produce a configure script.AC_PREREQ([2.69])AC_INIT([FULL-PACKAGE-NAME], [VERSION], [BUG-REPORT-ADDRESS])AC_CONFIG_SRCDIR([main.c])AC_CONFIG_HEADERS([config.h])AM_INIT_AUTOMAKE(main,1.0)# Checks for programs.AC_PROG_CC# Checks for libraries.# Checks for header files.# Checks for typedefs, structures, and compiler characteristics.# Checks for library functions.AC_OUTPUT(Makefile)4.新建Makefile⽂件,如下:AUTOMAKE_OPTIONS=foreignbin_PROGRAMS=mainfirst_SOURCES=main.c5.运⾏命令aclocal命令成功之后,在⽬录下会产⽣aclocal.m4和autom4te.cache两个⽂件。

实验三 Makefile的编写及应用

闽江学院电子系实验报告2、手动编译hello 应用程序在hello.c 的目录的终端下输入:#gcc -c hello.c#gcc hello.o -o hello通过ls 命令查看当前目录下是否生成源代码hello.c 的object 文件hello.o 和可执行文件hello,运行可执行文件hello。

查看一下运行结果。

3、修改hello.c 文件,重新手动编译应用程序。

4、删除hello.o 和hello 文件#rm -f hello.o#rm -f hello(2) 利用GNU make 自动编译应用程序方法1、利用文本编辑器创建一个Makefile 文件,并将其保存到与hello.c 相同的目录下。

2、先执行如下命令。

#make#ls#./hello查看并记录所生成的文件和运行的结果。

3、执行make clean 命令:4、修改hello.c 文件,重复第2、3 步操作,查看并记录所生成的文件和运行结果,并与手动编译进行比较,写出你的结论。

5、重新编辑Makefile 文件(斜黑体表示修改部分)6、重复第2,3 步操作,查看并记录所生成的文件和运行的结果。

比较这两种操作,写出你的结论。

同时指出$^ 、$@、$<在上述Makefile 中的含义。

说明: $@ 规则目标文件名$< 规则第一个依赖文件名$^ 规则的所有文件列表使用自动化变量可以不必写出目标文件名及依赖文件表列。

尤其在生成多个目标文件生成一个可执行文件中优点更加突出。

(3)多个.c 文件的编译1、创建文件hello1.c、hello2.c、hello.h2、参考前文Makefile样例,动手编写编译多文档的Makefile文件。

3、先后执行如下命令#make -f Makefile1#ls#./hello4、修改Makefile 文件,添加两个变量定义,并修改相应的规则及指令。

5、重复第3 步操作,查看并记录所生成的文件和运行的结果, 写出你的结论。

makefile工具的使用实验原理

makefile工具的使用实验原理一、Makefile工具概述Makefile是一种自动化编译工具,用于管理程序的编译和链接过程。

它可以根据程序的依赖关系,自动判断哪些文件需要重新编译,从而提高程序的编译效率。

二、Makefile工具的基本语法Makefile文件由一系列规则组成,每个规则包含一个目标、依赖关系和命令。

其中,目标指的是要生成的文件,依赖关系指的是生成该文件所需要依赖的其他文件或目标,命令指的是生成该目标文件所需要执行的命令。

三、Makefile工具中变量和函数在Makefile中可以定义变量和函数来简化代码和提高可维护性。

变量可以用来存储常量或计算结果,函数可以用来处理字符串等操作。

四、Makefile工具中常见命令1. 编译命令:gcc -c source.c -o object.o2. 链接命令:gcc object.o -o target3. 清除命令:rm -f target object.o五、Makefile工具实验步骤1. 创建源代码文件和头文件。

2. 创建Makefile文件,并定义变量和函数。

3. 定义规则,并设置目标、依赖关系和命令。

4. 执行make命令进行编译链接。

5. 执行make clean命令清除生成的目标文件。

六、Makefile工具实验注意事项1. Makefile文件中的变量和函数必须使用$符号进行引用。

2. 目标文件和依赖关系之间必须使用冒号分隔符。

3. 命令必须以Tab键开头,否则会报错。

4. Makefile文件中的注释可以使用#符号。

七、Makefile工具实验示例以下是一个简单的Makefile示例,用于编译一个C语言程序:```# 定义变量CC = gccCFLAGS = -Wall -g# 定义规则target: main.o func.o$(CC) main.o func.o -o targetmain.o: main.c func.h$(CC) $(CFLAGS) -c main.cfunc.o: func.c func.h$(CC) $(CFLAGS) -c func.cclean:rm -f target *.o```在该示例中,定义了两个变量CC和CFLAGS,分别表示编译器和编译选项。

实验八 makefile

实验四Makefile一、实验目的1、了解和掌握makefile文件的编写;2、学会使用交叉编译工具和make工具。

二、实验环境预装Fedora10的pc机一台,CVT-A8系列实验箱,以太网线一根,串口线一根。

三、实验步骤1、连接主机和目标板;(三根线,注意网线和串口线是否连接正常)2、Makefile文件的编写a) 编写一个文件prime.h,包含一个判断unsigned int是否为素数的函数定义。

b) 编写一个文件prime.c,实现上面的那个函数。

c) 编写一个文件main.c,实现用户输入整数,程序告诉用户这个数是否为素数,直到用户输入0结束。

d) 使用gcc编译,查看运行结果。

e) 编写makefile文件实现第d步的功能,并使用make工具编译生成这个可执行文件;运行。

f) 使用定义宏来改写makefile,实现第d步的功能,并使用make工具编译生成这个可执行文件;运行。

g) 使用对依赖文件的预定义变量改写makefile,实现第d 步的功能,并使用make工具编译生成这个可执行文件;运行。

h) 使用标签改写makefile,此标签功能为删除项目编译生成中的所有中间文件,并使用make工具删除项目编译生成中的所有中间文件。

i) 使用CC宏指代编译器命令gcc,修改makefile文件,实现第d步的功能,并使用make工具编译生成这个可执行文件;运行。

j) 使用CC宏指代编译器命令arm-linux-gcc,修改makefile 文件,实现第d步的功能,并使用make工具编译生成这个可执行文件;下载到目标板运行。

k) 使用make CC=gcc 命令生成可执行文件,使用file查看可执行文件信息。

再查看makefile文件。

四、实验要求1、要求随时观察记录实验结果;2、保留编写的源文件和每一步的makefile;3、掌握makefile文件的三种编写方法。

五、实验报告要求1、每人一份实验报告;2、实验报告中要求对每一步操作和出现的结果详细记录并解释;3、你认为做好本实验应该注意哪些方面?六、思考题makefile文件的作用?。

嵌入式编程基础实验报告之Makefile文件的使用

实验内容与分析设计:(1)用Vi打开上述两个代码文件“hello.c”和“hello.h”。

(2)在shell命令行中用Gcc尝试编译,使用命令:”Gcc hello.c –o hello”,并运行hello可执行文件查看结果。

(3)删除此次编译的可执行文件:rm hello。

(4)用Vi编辑Makefile,如下所示:hello:hello.c hello.hGcc hello.c -o hello(5)退出保存,在shell中键入:make,查看结果。

(6)再次用Vi打开Makefile,用变量进行替换,如下所示:OBJS :=hello.oCC :=Gcchello:$(OBJS)$(CC) $^ -o $@(7)退出保存,在shell中键入:make,查看结果。

(8)用Vi编辑Makefile1,如下所示:hello:hello.oGcc hello.o -o hellohello.o:hello.c hello.hGcc -c hello.c -o hello.o(9)退出保存,在shell中键入:make -f Makefile1,查看结果。

(10)再次用Vi编辑Makefile1,如下所示:OBJS1 :=hello.oOBJS2 :=hello.c hello.hCC :=Gcchello:$(OBJS1)$(CC) $^ -o $@$(OBJS1):$(OBJS2)$(CC) -c $< -o $@在这里请注意区别“$^”和“$<”。

退出保存,在shell中键入:make -f Makefile1,查看结果实验结果:各种不同形式的makefile都能完成其正确的功能疑难与小节:通过对包含多文件的Makefile的编写,熟悉各种形式的Makefile,并且进一步加深对Makefile 中用户自定义变量、自动变量及预定义变量的理解主要算法和程序清单:#hello.c#include "hello.h"int main(){printf("Hello everyone!\n"); }#hello.h#include <stdio.h> Makefile:hello:hello.c hello.hGcc hello.c -o hello Makefile:OBJS :=hello.oCC :=Gcchello:$(OBJS)$(CC) $^ -o $@Makefile1:hello:hello.oGcc hello.o -o hello hello.o:hello.c hello.hGcc -c hello.c -o hello.o Makefile1:OBJS1 :=hello.oOBJS2 :=hello.c hello.hCC :=Gcchello:$(OBJS1)$(CC) $^ -o $@ $(OBJS1):$(OBJS2)$(CC) -c $< -o $@。

辽宁工程技术大学linux实验makefile实验

6、重复第2,3步操作,查看并记录所生成的文件和运行的结果。比较这两种操作,写出你的结论。同时指出$^、$@、$<在上述Makefile中的含义。

三、多个.c文件的编译。

1、创建文件hello1.c、hello2.c、hello.h和makefile。

2、先后执行如下命令:[root@local]$make,[root@local]$ls,[root@local]$./hello。

2、XSBase270或XSBase255 ARM实验开发平台一套。

实验

进度

本次共有1个练习,完成1个。

实验

内容

一、用命令行的方式手动编译程序方法

1、利用文本编辑器创建hello.c文件。

2.手动编译hello应用程序。

在hello.c的目录的终端下输入:[root@local]$ gcc –c hello.c,[root@local]$gcc hello.o –o hello。通过ls命令查看当前目录下是否生成源代码hello.c的object文件hello.o和可执行文件hello,运行可执行文件hello。结果[root@local]$./hello

3、修改hello.c文件,重新手动编译应用程序。

4、删除hello.o和hello文件。[root@local]$rm –f hello.o,[root@local]$rm –f hello。

二、利用GNU make自动编译应用程序方法

1、用文本编辑器创建一个makefile文件,保存到与hello.c相同的目录下。

成绩

辽宁工程技术大学上机实验报告

实验名称

makefile实验

院系

软件学院

makefile工具的使用实验原理

makefile工具的使用实验原理1. 引言makefile是一种程序构建工具,它的作用是根据源代码文件之间的依赖关系,自动化地生成可执行文件、库文件或者其他类型的文件。

makefile工具的使用可以大大简化软件开发过程,提高代码的编译效率。

本文将详细介绍makefile工具的原理以及如何使用它进行实验。

2. makefile的原理2.1 什么是makefilemakefile是一个文本文件,它包含了一系列的规则,用于描述源文件之间的依赖关系以及如何生成目标文件。

makefile的格式和语法都是根据约定俗成的规则来定义的,因此可以在不同的平台和编译环境中使用。

2.2 makefile的工作原理makefile的工作原理可以简单概括为以下几个步骤:1.读取makefile文件,解析其中的规则。

2.检查目标文件是否需要重新生成。

如果目标文件不存在、源文件有修改或者依赖文件有修改,则需要重新生成目标文件。

3.根据规则中描述的依赖关系,递归地生成依赖文件及其依赖文件的目标文件。

4.根据生成的依赖文件和目标文件,生成最终的目标文件。

3. makefile的语法makefile的语法可以分为三个部分:变量定义、规则定义和命令定义。

3.1 变量定义在makefile中,变量用来存储一些常用的配置信息,例如编译器的路径、编译选项等。

变量可以使用赋值语句进行定义,例如:CC = gccCFLAGS = -Wall -O23.2 规则定义规则定义了目标文件和依赖文件之间的关系,以及如何生成目标文件。

规则的格式如下:target: dependency1 dependency2 ...command1command2...目标文件(target)是规则中要生成的文件,依赖文件(dependency)是目标文件生成所需要的原始文件或者其他目标文件。

命令(command)是生成目标文件的具体操作。

3.3 命令定义命令定义了如何生成目标文件。

Makefile两个实验

Makefile两个实验实验⼗四Makefile⼯程管理器14.1 编写包含多⽂件的Makefile【实验内容】编写⼀个包含多⽂件的Makefile。

【实验⽬的】通过对包含多⽂件的Makefile的编写,熟悉各种形式的Makefile,并且进⼀步加深对Makefile中⽤户⾃定义变量、⾃动变量及预定义变量的理解。

【实验平台】PC机、CentOS 5 操作系统、gcc等⼯具。

【实验步骤】1.⽤vi在同⼀⽬录下编辑两个简单的Hello程序,如下所⽰:#hello.c#include "hello.h"int main(){printf("Hello everyone!\n");}#hello.h#include2.仍在同⼀⽬录下⽤vim编辑Makefile,不使⽤变量替换,⽤⼀个⽬标体实现(即直接将hello.c和hello.h编译成hello⽬标体)。

并⽤make验证所编写的Makefile是否正确。

3.将上述Makefile使⽤变量替换实现。

同样⽤make验证所编写的Makefile是否正确4.⽤编辑另⼀Makefile,取名为Makefile1,不使⽤变量替换,但⽤两个⽬标体实现(也就是⾸先将hello.c和hello.h编译为hello.o,再将hello.o编译为hello),再⽤make 的‘-f’选项验证这个Makefile1的正确性。

5.将上述Makefile1使⽤变量替换实现【详细步骤】1.⽤vi打开上述两个代码⽂件…hello.c?和…hello.h?2.在shell命令⾏中⽤gcc尝试编译,使⽤命令:…gcc hello.c -o hello?,并运⾏hello可执⾏⽂件查看结果。

3.删除此次编译的可执⾏⽂件:rm –rf hello4.⽤vim编辑Makefile,如下所⽰:hello:hello.c hello.hgcc hello.c -o hello5.退出保存,在shell中键⼊:make查看结果6.再次⽤vim打开Makefile,⽤变量进⾏替换,如下所⽰:OBJS :=hello.oCC :=gcchello:$(OBJS)$(CC) $^ -o $@7.退出保存,在shell中键⼊:make查看结果8.⽤vim编辑Makefile1,如下所⽰:hello:hello.ogcc hello.o -o hellohello.o:hello.c hello.hgcc -c hello.c -o hello.o9.退出保存,在shell中键⼊:make –f Makefile1查看结果10.再次⽤vi编辑Makefile1,如下所⽰:OBJS1 :=hello.oOBJS2 :=hello.c hello.hCC :=gcchello:$(OBJS1)$(CC) $^ -o $@$(OBJS1):$(OBJS2)$(CC) -c $< -o $@在这⾥请注意区别…$^?和…$11.退出保存,在shell中键⼊:make –f Makefile1查看结果14.2嵌套Makefile实验【实验⽬的】1、读懂makefile⽂件,能根据makefile⽂件理清程序结构2、能编写简单makefile3、掌握嵌套执⾏makefile【实验环境】PC机、CentOS 5 操作系统,gcc等⼯具。

Linux系统Makefile编写与GCC编译实验报告

实验报告实验题目Linux系统Makefile编写与GCC编译实验姓名:学号:课程名称:所在学院:专业班级:任课教师:四、实验过程、步骤及内容(一)GCC编译1、准备环境2、建立相关目录$ cd workdir/linux/application$ mkdir 6-gcc3、将代码从共享目录拷入虚拟机L inux 操作系统下;(可使用【crtl+空格】切换输入法)$ cp /mnt/hgfs/share/实验代码/03.\ Linux 系统GCC 编译器的使用实验/实验代码/* 6-gcc/ -a$ cd 6-gcc/4、编译代码$ arm-none-linux-gnueabi-gcc helloworld.c -o hello$ mkdir /source/rootfs/app$ cp hello /source/rootfs/app/5、执行代码通过tftp 下载内核,nfs 挂载文件系统,启动开发板。

在开发板串口终端执行应用程序。

# cd /app# ./hello6、相关代码:#include <stdio.h>int main (int argc,char **argv){printf("hello,world!\n");return 0;}(二)Makefile编程1、环境准备2、建立相关目录$ cd workdir/linux/application$ mkdir 7-Makefile3、将代码从共享目录拷入虚拟机L inux 操作系统下;(可使用【crtl+空格】切换输入法)$ cp /mnt/hgfs/share/实验代码/05.\ Linux 系统Makefile 编写实验/实验代码/5.2/makefileTest/* 7-Makefile/ -a$ cd 7-Makefile/4、执行代码进入makefileTest 目录,执行make。

$ make CLEAN$ make会出现如下信息:5、在开发板上执行通过tftp下载内核,nfs挂载文件系统,启动开发板6、相关代码:CC = arm-none-linux-gnueabi-gcc SUBDIRS = f1 \f2 \main \objOBJS = f1.o f2.o main.oBIN = myappOBJS_DIR = objBIN_DIR = binexport CC OBJS BIN OBJS_DIR BIN_DIRall : CHECK_DIR $(SUBDIRS)cp bin/myapp /source/rootfs/app CHECK_DIR :mkdir -p $(BIN_DIR) $(SUBDIRS) : ECHOmake -C $@ECHO:@echo $(SUBDIRS)@echo begin compileCLEAN :@$(RM) $(OBJS_DIR)/*.o@rm -rf $(BIN_DIR)五、实验数据(现象)处理分析实验现象如下:(一)GCC编译(二)Makefile编程。

操作系统实验二指导书

实验二:Linux编程-makefile文件基础1 预备知识✓Linux的编程初步✓Linux编辑器Vim或gedit的使用✓Linux编译器GCC的使用2 实验目的✓熟悉makefile文件规则✓编写和编译简单makefile文件✓运行makefile文件3 Makefile文件✓使用GCC命令行进行程序编译在单个文件下是比较方便的,当工程中的文件逐渐增多,甚至变得十分庞大的时候,使用GCC命令编译就会变得力不从心;✓Linux中的make工具提供了一种管理工程的功能,可以方便的进行程序编译,对更新的文件进行重新定义。

4 Makefile的规则Makefile的框架是由规则构成的。

make命令执行时先在makefile文件中查找各种规则,对各种规则进行解析后运行规则。

规则:TARGET…. : DEPENDEDS….<TAB> COMMAND✓TARGET:规则定义目标。

可执行文件或者依赖的目标文件;✓DEPENDEDS:执行此规则所必需的依赖条件;✓COMMAND:规则执行的命令;5 Makefile文件的使用5.1 建立makefile文件注意事项✓放置的目录最好为可以编辑的目录,如可以存放在home目录下;✓文件的命名为makefile;✓对与command可以用连接符\ 来进行连接;✓命令行分隔符号为<Tab>键;5.2 makefile的编辑与运行✓makefile文件编辑:gedit makefile;✓确保编程代码无误的情况下开始运行makefile;✓进入终端makefile存放目录输入命令:make;✓如果成功就会生成相应的可执行文件;✓在该目录下的终端运行可执行文件:./文件名,得到结果;✓使用命令:make clean对make产生的文件进行清除;6 实验用例一个工程文件有个五个文件:✓主函数为main.c✓add目录中用add_int.c和add_float.c,两个文件分别计算整型和浮点型的相加;✓sub目录中用sub_int.c和sub_float.c,两个文件分别计算整型和浮点型的相减;7 实验任务✓根据实例,编写makefile文件;✓使用make命令进行编译运行:make注:实验用例源文件,见文件夹Lab2:包含五个工程文件以及makefile文件;✓运行编译后的可执行文件:./cacu参考代码:见附件Lab2。

Makefile入门实验

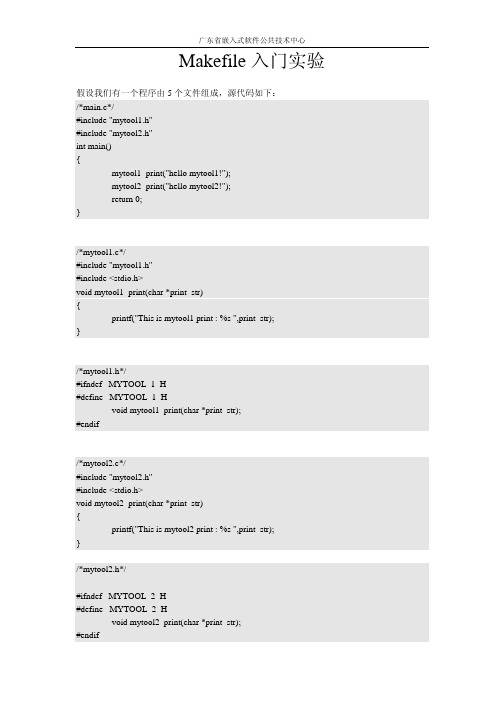

Makefile入门实验假设我们有一个程序由5个文件组成,源代码如下:/*main.c*/#include"mytool1.h"#include"mytool2.h"int main(){mytool1_print("hello mytool1!");mytool2_print("hello mytool2!");return0;}/*mytool1.c*/#include"mytool1.h"#include<stdio.h>void mytool1_print(char*print_str){printf("This is mytool1print:%s",print_str);}/*mytool1.h*/#ifndef_MYTOOL_1_H#define_MYTOOL_1_Hvoid mytool1_print(char*print_str);#endif/*mytool2.c*/#include"mytool2.h"#include<stdio.h>void mytool2_print(char*print_str){printf("This is mytool2print:%s",print_str);}/*mytool2.h*/#ifndef_MYTOOL_2_H#define_MYTOOL_2_Hvoid mytool2_print(char*print_str);#endif首先了解一下make和Makefile。

GNU make是一个工程管理器,它可以管理较多的文件。

使用make的最大好处就是实现了“自动化编译”。

如果有一个上百个文件的代码构成的项目,其中一个或者几个文件进行了修改,make就能够自动识别更新了的文件代码,不需要输入冗长的命令行就可以完成最后的编译工作。

W2 实验二 Makefile实验

实验一 Makefile实验【实验目的】1、了解Makefile的基本概念和基本结构2、初步掌握编写简单Makefile的方法3、了解递归Make的编译过程4、初步掌握利用GNU Make编译应用程序的方法【实验原理】在Linux或Unix环境下,对于只含有几个源代码文件的小程序(如hello.c)的编译,可以手工键入gcc命令对源代码文件逐个进行编译;然而在大型的项目开发中,可能涉及几十到几百个源文件,采用手工键入的方式进行编译,则非常不方便,而且一旦修改了源代码,尤其头文件发生了的修改,采用手工方式进行编译和维护的工作量相当大,而且容易出错。

所以在Linux或Unix环境下,人们通常利用GNU make工具来自动完成应用程序的维护和编译工作。

实际上,GNU make工具通过一个称为Makefile的文件来完成对应用程序的自动维护和编译工作。

Makefile是按照某种脚本语法编写的文本文件,而GNU make能够对Makefile中指令进行解释并执行编译操作。

Makefile文件定义了一系列的规则来指定哪些文件需要先编译,哪些文件需要后编译,哪些文件需要重新编译,甚至于进行更复杂的功能操作。

GNU make工作时的执行步骤如下:1、读入所有的Makefile。

2、读入被include的其它Makefile。

3、初始化文件中的变量。

4、推导隐晦规则,并分析所有规则。

5、为所有的目标文件创建依赖关系链。

6、根据依赖关系,决定哪些目标要重新生成。

7、执行生成命令。

1-5步为第一个阶段,6-7为第二个阶段。

第一个阶段中,如果定义的变量被使用了,那么,make会把其展开在使用的位置。

但make并不会完全马上展开,make使用的是拖延战术,如果变量出现在依赖关系的规则中,那么仅当这条依赖被决定要使用了,变量才会在其内部展开。

下面对makefile的相关问题进行简单介绍:1、Makefile的基本结构Makefile的一般结构:target……:dependency……command……结构中各部分的含义:(1)、target(目标):一个目标文件,可以是Object文件,也可以是执行文件。

实验3 Makefile使用

实验3 Makfile的使用【实验目的】1.了解Makfile 编写;2.了解Makefile语法;【实验内容】1.用Makefile对实验内容1的hello.c文件进行编译。

(1) 在目录(/mnt/nfs)建立helloMake文件夹, gedit编辑hello.c(2) 输入hello.c文件源代码(可复制)#include<stdio.h>int main(){printf("hello! This is our embeded world! \n");return 0;}((4) 输入一下内容,并保存注意文件名必须是Makefile,注意大小写.以及命令行开始必须用TAB键。

(5) Makefile 文件编写完成后,让hello 目录下面只有Makfile 文件和(2.Makefile文件自动变量的使用。

(1) 修改一下,添加自动变量。

(2(3.多文件编译的Makefile 文件编写(1) 创建helloMake2文件夹,并在该目录下面建立hello1.c、hello2.c、(2) 分别输入源代码hello1.c、hello2.c、hello2.hhello1.c代码:#include <stdio.h>#include "hello2.h"int main(int argc, char* argv[]){printf("hello! embeded world!\n");test2();return 0;}hello2.c代码:#include <stdio.h>#include "hello2.h"void test2(void){printf("Welcome embeded world! -hello2\n");}hello2.h代码:void test2(void);(4) 输入一下内容,并保存注意文件名必须是Makefile,注意大小写.以及命令行开始必须用TAB键。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

Makefile工程管理器14.1 编写包含多文件的Makefile【实验内容】编写一个包含多文件的Makefile。

【实验目的】通过对包含多文件的Makefile的编写,熟悉各种形式的Makefile,并且进一步加深对Makefile中用户自定义变量、自动变量及预定义变量的理解。

【实验平台】PC机、CentOS 5 操作系统、gcc等工具。

【实验步骤】1.用vi在同一目录下编辑两个简单的Hello程序,如下所示:#hello.c#include "hello.h"int main(){printf("Hello everyone!\n");}#hello.h#include <stdio.h>2.仍在同一目录下用vim编辑Makefile,不使用变量替换,用一个目标体实现(即直接将hello.c和hello.h编译成hello目标体)。

并用make验证所编写的Makefile是否正确。

3.将上述Makefile使用变量替换实现。

同样用make验证所编写的Makefile是否正确4.用编辑另一Makefile,取名为Makefile1,不使用变量替换,但用两个目标体实现(也就是首先将hello.c和hello.h编译为hello.o,再将hello.o编译为hello),再用make的‘-f’选项验证这个Makefile1的正确性。

5.将上述Makefile1使用变量替换实现【详细步骤】1.用vi打开上述两个代码文件‘hello.c’和‘hello.h’2.在shell命令行中用gcc尝试编译,使用命令:‘gcc hello.c -o hello’,并运行hello可执行文件查看结果。

3.删除此次编译的可执行文件:rm –rf hello4.用vim编辑Makefile,如下所示:hello:hello.c hello.hgcc hello.c -o hello5.退出保存,在shell中键入:make查看结果6.再次用vim打开Makefile,用变量进行替换,如下所示:OBJS :=hello.oCC :=gcchello:$(OBJS)$(CC) $^ -o $@7.退出保存,在shell中键入:make查看结果8.用vim编辑Makefile1,如下所示:hello:hello.ogcc hello.o -o hellohello.o:hello.c hello.hgcc -c hello.c -o hello.o9.退出保存,在shell中键入:make –f Makefile1查看结果10.再次用vi编辑Makefile1,如下所示:OBJS1 :=hello.oOBJS2 :=hello.c hello.hCC :=gcchello:$(OBJS1)$(CC) $^ -o $@$(OBJS1):$(OBJS2)$(CC) -c $< -o $@在这里请注意区别‘$^’和‘$<’。

11.退出保存,在shell中键入:make –f Makefile1查看结果14.2嵌套Makefile实验【实验目的】1、读懂makefile文件,能根据makefile文件理清程序结构2、能编写简单makefile3、掌握嵌套执行makefile【实验环境】PC机、CentOS 5 操作系统,gcc等工具。

【实验步骤】我们要创建的目录结构如下:顶层Makefile1.创建顶层目录我们首先在用户目录下创建一个makefileTest的文件夹:#cd /opt#mkdir makefileTest#cd makefileTest创建好需要用到的文件夹#mkdir f1 f2 main obj include进入include文件夹创建一个共用头文件#cd include#vim myinclude.h输入如下内容:#include <stdio.h>保存退出返回顶层目录:#cd ..2.创建顶层Makefile文件#vim Makefile输入以下内容:CC = gccSUBDIRS = f1 \f2 \main \objOBJS = f1.o f2.o main.oBIN = myappOBJS_DIR = objBIN_DIR = binexport CC OBJS BIN OBJS_DIR BIN_DIRall : CHECK_DIR $(SUBDIRS)CHECK_DIR :mkdir -p $(BIN_DIR) $(SUBDIRS) : ECHOmake -C $@ECHO:@echo $(SUBDIRS)@echo begin compileCLEAN :@$(RM) $(OBJS_DIR)/*.o@rm -rf $(BIN_DIR)3.进入在f1目录下创建makefile #cd f1#vim f1.c输入如下测试代码:#include “../include/myinclude.h”void print1(){printf("Message from f1.c...\n");return;}保存退出。

#vim Makefile输入如下内容:../$(OBJS_DIR)/f1.o: f1.c$(CC) -c $^ -o $@保存退出。

进入f2目录#cd ../f2#vim f2.c输入如下测试代码:#include “../include/myinclude.h”void print2(){printf("Message from f2.c…\n");return;}保存退出。

#vim Makefile输入如下内容:../$(OBJS_DIR)/f2.o: f2.c$(CC) -c $^ -o $@保存退出。

进入main目录#cd ../main#vim main.c输入如下内容:#include <stdio.h>int main(){print1();print2();return 0;}保存退出。

#vim Makefile输入如下内容:../$(OBJS_DIR)/main.o: main.c$(CC) -c $^ -o $@保存退出。

进入obj目录#cd ../obj#vim Makefile输入如下内容:../$(BIN_DIR)/$(BIN) : $(OBJS)$(CC) -o $@ $^好了,到此准备工作已经完毕,然我们来测试一下写的makefile是否好用。

进入顶层Makefile所在目录,即makefileTest目录。

#make会出现如下信息:目录树结构如下:我们看到在bin目录下生成了我们的目标文件myapp,在obj目录下生成了.o的中间文件。

让我们运行下myapp看下结果吧。

#bin/myapp我们也可以用如下命令清除中间文件和目标文件,恢复make之前的状态:#make CLEAN我们可以看到已经变为make之前的目录状态了。

大功告成。

最后给大家解释一下顶层makefile中一些命令的的含义吧。

a)我们注意到有一句@echo $(SUBDIRS)@echo其实是一句显示命令通常,make会把其要执行的命令行在命令执行前输出到屏幕上。

当我们用“@”字符在命令行前,那么,这个命令将不被make显示出来,最具代表性的例子是,我们用这个功能来像屏幕显示一些信息。

如:@echo 正在编译XXX模块......当make执行时,会输出“正在编译XXX模块......”字串,但不会输出命令,如果没有“@”,那么,make将输出:echo 正在编译XXX模块......正在编译XXX模块......如果make执行时,带入make参数“-n”或“--just-prin t”,那么其只是显示命令,但不会执行命令,这个功能很有利于我们调试我们的Makefile,看看我们书写的命令是执行起来是什么样子的或是什么顺序的。

而make参数“-s”或“--slient”则是全面禁止命令的显示。

b)@(RM)并不是我们自己定义的变量,那它是从哪里来的呢?通常在清除文件的伪目标所定义的命令中“rm”使用选项“–f”(--force)来防止在缺少删除文件时出错并退出,使“make clean”过程失败。

也可以在“rm”之前加上“-”来防止“rm”错误退出,这种方式时 make 会提示错误信息但不会退出。

为了不看到这些讨厌的信息,需要使用上述的第一种方式。

另外 make存在一个内嵌隐含变量“RM”,它被定义为:“RM = rm –f”。

因此在书写“clean”规则的命令行时可以使用变量“$(RM)”来代替“rm”,这样可以免出现一些不必要的麻烦!这是我们推荐的用法。

c)make -C $@这是一句嵌套makefile的语法,在一些大的工程中,我们会把我们不同模块或是不同功能的源文件放在不同的目录中,我们可以在每个目录中都书写一个该目录的Makefile,这有利于让我们的Makefile变得更加地简洁,而不至于把所有的东西全部写在一个Makefile中,这样会很难维护我们的Makefile,这个技术对于我们模块编译和分段编译有着非常大的好处。

例如,我们有一个子目录叫subdir,这个目录下有个Makefile文件,来指明了这个目录下文件的编译规则。

那么我们总控的Makefile可以这样书写:subsystem:cd subdir && $(MAKE)其等价于:subsystem:$(MAKE) -C subdir定义$(MAKE)宏变量的意思是,也许我们的make需要一些参数,所以定义成一个变量比较利于维护。

这两个例子的意思都是先进入“subdir”目录,然后执行make命令。

d)export CC OBJS BIN OBJS_DIR BIN_DIR我们把这个Makefile叫做“总控Makefile”,总控Makefile的变量可以传递到下级的Makefile中(如果你显示的声明),但是不会覆盖下层的Makefile中所定义的变量,除非指定了“-e”参数。

如果你要传递变量到下级Makefile中,那么你可以使用这样的声明:export <variable ...>。