时钟数据恢复(CDR)

时钟与数据恢复(CDR)技术在高速串行通信链路中的应用

时钟数据恢复(CDR)电路广泛应用于电信、光收发器、数据存储局域网以及无线产品中,随着对于带宽的要求越来越高,以及分配和占用频谱的增加,因而在设计中,CDR技术的优势将日益突出。

与此同时,供应商的产品都将系统或板级接口从并行方式转换成串行方式。

时钟数据恢复(CDR)技术的产生近几年,CDR技术的应用大为增长,已超出了在处理较宽并行数据总线跨背板连接时对接收端时钟管理和数据偏斜的需求。

由于这些并行数据总线信号占用较大的板尺寸并消耗较大的功率,因而它们之间的路由非常困难,故需要采用多层路由结构来处理信号和总线端接问题。

除此之外,还必需解决高位宽数据总线所产生的EMI(电磁干扰)问题。

随着通信新技术的出现和电信号处理技术的改进以及要求通过FR(帧中继)-4背板、光纤和无线媒介发送电信号技术问题的问世,从而使CDR技术尤为显得重要。

为确保证时钟和数据相组合的信号能同时到达,在发送端首先将时钟和数据复合的通信技术已广泛被采用并不稀罕,而关键在于如何在接收端将时钟和数据能分离开来,而这项工作须由CDR电路完成。

此时,将数据从并行格式转换到串行格式或实现相反转换的产品又称为串行器/解串器。

这些串行器/解串器的产品通常包含有CDR电路,用于对串行数据流的解串。

本文论述的是:在高速串行通信应用中成功实现CDR技术、功能的电路结构;而在典型高速串行通信链路的概述中,又对数据是如何传输及如何从链路中重新捕获数据作分析;而在通用CDR拓扑中将讨论CDR的不同结构并分折数据链路发送端和接收端时钟基准振荡器的设计要领。

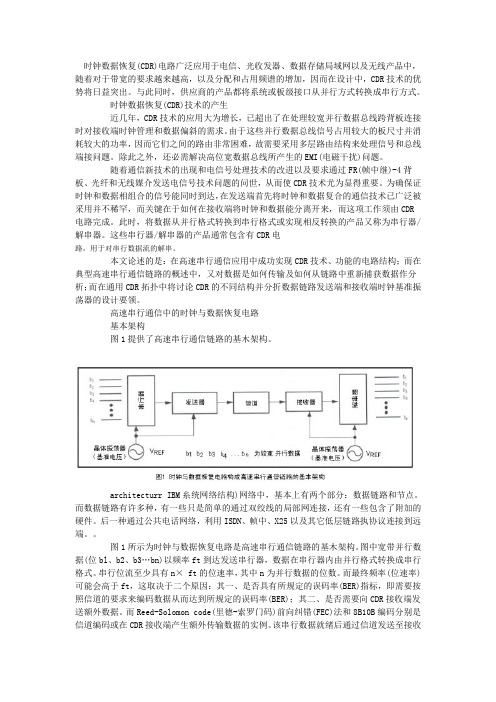

高速串行通信中的时钟与数据恢复电路基本架构图1提供了高速串行通信链路的基木架构。

architecturr IBM糸统网络结构)网络中,基本上有两个部分:数据链路和节点。

而数据链路有许多种,有一些只是简单的通过双绞线的局部网连接,还有一些包含了附加的硬件。

后一种通过公共电话网络,利用ISDN、帧中、X25以及其它低层链路执协议连接到远端。

时钟数据恢复(CDR)

时钟数据恢复(CDR)时钟数据恢复(CDR)引言概述:时钟数据恢复(Clock Data Recovery, CDR)是一种数字通信领域中常用的技术,用于从接收到的信号中恢复出时钟信息,并将其用于数据采样和解码。

本文将介绍时钟数据恢复的工作原理以及其在通信系统中的应用。

一、时钟数据恢复的原理1.1 时钟信号的重要性时钟信号在数字通信系统中起着至关重要的作用,它用于同步发送和接收端的数据采样和解码过程。

时钟信号的准确性和稳定性直接影响到通信系统的性能。

1.2 时钟数据恢复的需求在数字通信中,接收到的信号可能会受到传输介质、噪声等因素的影响,导致时钟信号的失真和抖动。

因此,需要一种方法来从接收到的信号中恢复出准确的时钟信息。

1.3 时钟数据恢复的原理时钟数据恢复的原理是基于接收到的信号中的边缘信息来恢复时钟信号。

通过比较信号的上升沿和下降沿的时间间隔,可以推测出时钟信号的频率和相位,从而实现时钟数据的恢复。

二、时钟数据恢复的应用2.1 数字通信系统时钟数据恢复在数字通信系统中广泛应用,用于恢复接收端的时钟信号,以确保数据的准确采样和解码。

它可以应对传输介质的噪声和失真,提高通信系统的可靠性和性能。

2.2 光纤通信在光纤通信中,时钟数据恢复被用于恢复接收端的光信号的时钟信息。

光信号在传输过程中可能会受到光纤的色散和衰减等影响,导致时钟信号的失真。

时钟数据恢复技术可以有效地恢复出准确的时钟信号,提高光纤通信系统的性能。

2.3 高速串行通信在高速串行通信中,时钟数据恢复被用于恢复接收端的时钟信号。

高速串行通信中的时钟信号往往由数据信号中的边缘信息推测而来,因此时钟数据恢复技术对于保证数据的准确采样和解码至关重要。

三、时钟数据恢复的算法3.1 相位锁定环路(Phase Locked Loop, PLL)相位锁定环路是一种常用的时钟数据恢复算法。

它通过不断调整本地时钟的相位和频率,使其与接收到的信号的相位和频率保持同步,从而实现时钟数据的恢复。

时钟数据恢复(CDR)

时钟数据恢复(CDR)时钟数据恢复(CDR)是一种用于恢复数字信号中时钟信息的技术,它在数字通信系统中起着至关重要的作用。

本文将从时钟数据恢复的定义、原理、应用、发展和未来趋势等方面进行探讨。

一、时钟数据恢复的定义1.1 时钟数据恢复是指在数字通信系统中从接收到的信号中提取出时钟信息的过程。

1.2 时钟数据恢复技术通过对接收到的信号进行处理,从中提取出时钟信号,以确保信号的正确接收和处理。

1.3 时钟数据恢复技术可以应用于各种数字通信系统中,如光纤通信、无线通信等。

二、时钟数据恢复的原理2.1 时钟数据恢复的原理是通过对接收到的信号进行采样和重构,从中提取出时钟信息。

2.2 时钟数据恢复技术通常包括时钟信号提取、时钟信号重构和时钟信号同步等过程。

2.3 时钟数据恢复的原理是基于数字信号处理和时钟同步技术,通过对信号进行分析和处理实现时钟信息的提取和恢复。

三、时钟数据恢复的应用3.1 时钟数据恢复技术广泛应用于数字通信系统中,如光纤通信、无线通信等。

3.2 时钟数据恢复技术可以提高系统的稳定性和可靠性,确保信号的正确接收和处理。

3.3 时钟数据恢复技术还可以用于信号的重构和同步,以确保系统的正常运行和数据的准确传输。

四、时钟数据恢复的发展4.1 随着数字通信技术的不断发展,时钟数据恢复技术也在不断完善和提升。

4.2 新的时钟数据恢复算法和技术不断涌现,为数字通信系统的性能提升提供了有力支持。

4.3 时钟数据恢复技术的发展趋势是向着更高的精度、更低的功耗和更广泛的应用领域发展。

五、时钟数据恢复的未来趋势5.1 未来时钟数据恢复技术将更加注重对复杂信号环境下的时钟信息提取和恢复。

5.2 时钟数据恢复技术将不断融合新的技术手段,如人工智能、深度学习等,以提高系统的性能和稳定性。

5.3 时钟数据恢复技术的未来趋势是向着更智能、更高效和更可靠的方向发展。

总结:时钟数据恢复技术在数字通信系统中具有重要作用,通过对接收到的信号进行处理,提取出时钟信息,确保信号的正确接收和处理。

无参考时钟的cdr原理

无参考时钟的cdr原理

无参考时钟的CDR(时钟数据恢复)原理是指在没有外部时钟

参考信号的情况下,通过接收到的数据信号中的时钟信息来恢复时钟。

这种技术通常用于接收端需要从数据流中恢复时钟信号的情况,例如在数字通信系统中。

无参考时钟的CDR原理基于数据信号本身所携带的时钟信息。

当数据信号到达接收端时,CDR电路会通过内部的相位锁定环(PLL)或其他方法来提取出数据中的时钟信号,并将其用于恢复接收端的

时钟。

这样可以确保接收端的时钟与发送端的时钟保持同步,从而

正确地解析数据。

在实际应用中,无参考时钟的CDR需要考虑多种因素,例如数

据信号的抖动、噪声、时钟频率漂移等。

因此,CDR电路通常会结

合使用数字信号处理技术和模拟电路技术,以确保高精度和稳定性

的时钟恢复。

另外,无参考时钟的CDR原理也可以应用于一些特定的通信标

准和接口,例如高速串行接口(如PCIe、SATA、USB等)。

通过合

理设计和实现CDR电路,可以在没有外部时钟参考的情况下,实现

可靠的时钟恢复和数据解析。

总之,无参考时钟的CDR原理是一种重要的时钟恢复技术,通过有效地利用数据信号中的时钟信息,实现接收端时钟的恢复和同步,从而确保数据的可靠传输和解析。

时钟数据恢复(CDR)

时钟数据恢复(CDR)时钟数据恢复(CDR)是一种重要的通信技术,用于在数字通信系统中恢复时钟信号。

在数字通信系统中,时钟信号是非常关键的,它用于同步发送和接收数据,确保数据的准确传输。

本文将介绍时钟数据恢复的原理、应用、技术和发展趋势。

一、时钟数据恢复的原理1.1 时钟信号的重要性:时钟信号用于同步发送和接收数据,确保数据的准确传输。

1.2 时钟信号的失真:在数字通信系统中,时钟信号可能因为传输距离、噪声等原于是失真。

1.3 CDR的作用:CDR可以通过对接收到的数据进行分析和处理,恢复出准确的时钟信号。

二、时钟数据恢复的应用2.1 光通信系统:在光通信系统中,CDR可以用于恢复光信号的时钟信号。

2.2 高速数据传输:在高速数据传输系统中,CDR可以用于恢复数据的时钟信号,确保数据传输的准确性。

2.3 无线通信系统:在无线通信系统中,CDR可以用于恢复无线信号的时钟信号,提高数据传输的稳定性。

三、时钟数据恢复的技术3.1 相位锁定环(PLL):PLL是一种常用的时钟数据恢复技术,通过反馈控制相位差,使得输出的时钟信号与输入的时钟信号同步。

3.2 等化器:等化器可以对接收到的信号进行处理,去除噪声和失真,从而恢复出准确的时钟信号。

3.3 自适应滤波器:自适应滤波器可以根据接收到的信号的特点自动调整滤波器的参数,提高时钟数据恢复的准确性。

四、时钟数据恢复的发展趋势4.1 高速化:随着通信技术的发展,时钟数据恢复技术也在不断提高传输速度。

4.2 高精度:时钟数据恢复技术将会越来越精确,以应对复杂的通信环境。

4.3 低功耗:未来的时钟数据恢复技术将会越来越注重低功耗,以满足节能环保的需求。

五、结论时钟数据恢复是数字通信系统中非常重要的技术,它可以确保数据的准确传输。

随着通信技术的不断发展,时钟数据恢复技术也在不断提高,未来将会在高速化、高精度和低功耗方面取得更大的突破。

cdr芯片

cdr芯片CDR芯片,即时钟数据恢复芯片(Clock and Data Recovery),是一种用于从串行数据流中恢复时钟信号和数据信息的集成电路。

它常用于高速串行接口中,例如光纤通信、高速以太网、PCI Express等。

下面将对CDR芯片进行详细介绍。

首先,CDR芯片的工作原理是通过对串行数据信号进行采样、时钟恢复、信号解调等一系列处理来恢复出正常的时钟和数据信息。

在高速串行通信中,由于传输信号的衰减、失真等因素,使得时钟信号和数据信号受到严重干扰和变形。

CDR芯片通过内部的电路设计和算法,对接收到的数据进行时钟提取和恢复,并在正确的时刻对数据进行采样和解调,使其恢复到原始的时钟和数据信息。

其次,CDR芯片具有以下几个关键的性能指标:1. 时钟恢复精度:即CDR芯片对时钟信号的恢复准确度。

通常用来评估CDR芯片的抗噪声能力和抗干扰能力。

2. 数据恢复速度:即CDR芯片从接收到数据到恢复出正确的数据信息所需的时间。

这个指标通常用来评估CDR芯片的处理速度和实时性。

3. 电源噪声:即CDR芯片对电源噪声的敏感度。

高电源噪声会导致CDR芯片的工作不稳定,影响时钟和数据的恢复效果。

4. 功耗:CDR芯片在工作过程中所消耗的功率。

功耗低的CDR芯片可以减少系统的能耗。

此外,CDR芯片还具有以下几个特点和应用:1. 兼容性:CDR芯片通常支持多种串行数据接口和协议,使其能够广泛应用于不同的通信系统和设备中。

2. 自适应能力:CDR芯片通过采用自适应算法和引入反馈机制,能够根据不同的信号情况进行自动校正和优化,提高接收信号的质量。

3. 抗干扰能力:CDR芯片通过采用差分输入和输出、滤波电路等设计和技术手段,能够有效抑制噪声和干扰信号,提高信号的抗干扰能力。

4. 高速传输:CDR芯片通常能够支持高速的数据传输,例如多Gbps的速率,满足现代通信系统对高速传输的需求。

总而言之,CDR芯片作为一种用于串行数据恢复的关键集成电路,具有时钟恢复精度、数据恢复速度、电源噪声和功耗等重要性能指标,同时还具有兼容性、自适应能力、抗干扰能力和高速传输等特点。

cdr时钟恢复原理

cdr时钟恢复原理CDR时钟恢复原理CDR(Clock and Data Recovery)时钟恢复电路是高速通信系统中一个重要的模块,它是将来自外部世界的串行数据流和时钟信号恢复出来的模块,以保证高速通信系统的可靠性和稳定性。

CDR时钟恢复原理主要有以下几点:1. 时钟信号恢复CDR时钟恢复电路的核心是时钟信号恢复电路,其中包括相锁环(PLL)电路、延迟锁定环(DLL)电路等。

时钟信号恢复电路的作用是通过对输入数据的采样和调整来恢复数据中的时钟信号。

PLL电路是最常用的时钟恢复电路,它通过对输入数据的采样,检测数据中的时钟信号,通过反馈控制电路调节本地时钟的频率和相位,实现时钟恢复的目的。

2. 数据恢复CDR时钟恢复电路中的数据恢复模块主要是通过对采样到的数据进行判决,恢复出原始的数字信号。

数据恢复模块的设计决定了整个CDR 时钟恢复电路的性能和稳定性。

3. 自适应算法当外界环境发生变化时,CDR时钟恢复电路需要具备自适应能力,使其能够及时调整自己的参数,以保持良好的性能。

常用的自适应算法包括自适应等化算法、自适应滤波算法、自适应决策反馈等。

4. 抗噪性能CDR时钟恢复电路中的抗噪性能直接影响到它在高速通信系统中的可靠性和稳定性。

在设计CDR时钟恢复电路时,需要考虑到外界噪声对系统性能的影响,并采用一些措施来提高系统抗噪性能,例如滤波器、前置放大器等。

5. 稳定性和可靠性CDR时钟恢复电路在高速通信系统中是一个核心模块,它需要具备高度的稳定性和可靠性。

稳定性和可靠性取决于电路中各个模块的设计和参数选择,需要在实际应用中进行充分调试和测试,以确保系统的稳定性和可靠性。

综上所述,CDR时钟恢复原理涉及到多个方面,包括时钟信号恢复、数据恢复、自适应算法、抗噪性能、稳定性和可靠性等,需要在设计和应用中综合考虑,以保证高速通信系统的正常运行和性能指标的达标。

时钟数据恢复(CDR)

时钟数据恢复(CDR)时钟数据恢复(CDR)引言概述:时钟数据恢复(Clock Data Recovery, CDR)是一种用于恢复传输信号中的时钟信息的技术。

在数字通信中,信号传输过程中可能会受到噪声、失真等干扰,导致时钟信息的丢失或者不稳定。

CDR技术通过对传输信号进行采样和重构,恢复出准确的时钟信号,确保数据的可靠传输。

本文将从原理、应用、算法、性能和未来发展等五个方面详细介绍时钟数据恢复技术。

一、原理:1.1 时钟信号的重要性:时钟信号在数字通信中起到同步和定时的作用,确保数据的准确传输。

1.2 时钟信号的丢失和不稳定性原因:传输信号受到噪声、失真、衰减等干扰因素影响,导致时钟信息的丢失或者不稳定。

1.3 CDR的作用:CDR技术通过采样和重构传输信号,恢复出准确的时钟信号,保证数据的可靠传输。

二、应用:2.1 光纤通信中的CDR:光纤通信中,光信号在传输过程中容易受到衰减、色散等影响,导致时钟信息的丢失。

CDR技术可以恢复出准确的时钟信号,提高光纤通信的性能。

2.2 高速串行通信中的CDR:高速串行通信中,时钟信号的恢复对于数据的传输速率和稳定性至关重要。

CDR技术可以在高速串行通信中实时恢复时钟信号,确保数据的可靠传输。

2.3 高频信号处理中的CDR:在高频信号处理中,时钟信号的准确性对于信号处理算法的性能有着重要影响。

CDR技术可以提供准确的时钟信号,提高高频信号处理的精度和效果。

三、算法:3.1 时钟恢复算法的分类:时钟恢复算法可以分为基于锁相环(PLL)的算法和基于非锁相环的算法两类。

3.2 基于PLL的时钟恢复算法:基于PLL的时钟恢复算法通过不断调整反馈环路的相位和频率,使得恢复的时钟信号与原始时钟信号同步。

3.3 基于非锁相环的时钟恢复算法:基于非锁相环的时钟恢复算法通过统计和估计传输信号的特征,恢复出准确的时钟信号。

四、性能:4.1 时钟恢复的误差和抖动:时钟恢复算法的性能可以通过误差和抖动来评估,误差指恢复的时钟信号与原始时钟信号之间的差距,抖动指时钟信号的不稳定性。

时钟数据恢复(CDR)

时钟数据恢复(CDR)2009-11-01 21:40 5887人阅读评论(5) 收藏举报测试图形ui产品工作任务近年来,芯片功能的增强和数据吞吐量要求推动了芯片产业从低速率数据并行连接转变到高速串行连接。

这个概念被称为SERDES(Serializer-Deserializer),包括在高速差分对上串行地传送数据,而不是用低速的并行总线。

一个典型例子是用单个PCI-Express通道取代数据速率达2.112Gbps的传统32位66MHz PCI总线,PCI-Express可达到4Gbps的数据速率,但仅使用了工作在2.5GHz的4条线。

简而言之,SERDES协议允许用较少的引脚实现较高的数据速率。

图1给出了各种可能的SERDES接口。

这个例子展示了一个网络处理器位于系统中心的高性能电路板。

SERDES应用用紫色标明,可以用FPGA实现的芯片用黄色标明。

图1:典型的SERDES应用。

SERDES的类型有两种基本类型的SERDES接口:源同步(SS)协议和时钟数据恢复(CDR)协议。

这两种类型的主要差别是如何实现时钟控制。

源同步接口拥有一个伴随传送数据的时钟信号;CDR 没有单独的时钟信号,而是把时钟嵌入在数据中。

即CDR接收器将相位锁定在数据信号本身以获取时钟。

表1概括了这两种接口的基本差别。

表1:源同步和时钟数据恢复SERDES接口的比较。

通常CDR协议运行在较高的数据速率和较长的传送距离,因此带来很大的设计挑战。

时钟数据恢复的基础顾名思义,CDR接收器必须从数据中恢复嵌入的时钟。

更准确地说,是从数据信号的交换中获取时钟。

CDR发送器首先串行发送数据,然后将数据转换成8b/10b编码方案。

编码处理获得8位数据并将其转换成10位符号。

8b/10b编码方式可以在数据线上传送相等数目的0和1,从而减少码间干扰,并提供足够多的数据边沿,以便接收器在收到的数据流上锁定相位。

发送器将系统时钟倍频至传送比特率,并以该速率在TX差分对上发送8b/10b数据。

时钟数据恢复(CDR)

时钟数据恢复(CDR)时钟数据恢复(CDR)引言概述:时钟数据恢复(Clock Data Recovery, CDR)是一种用于恢复数字信号中的时钟信息的技术。

在数字通信中,时钟信号的准确性对于数据的传输和解析至关重要。

CDR技术可以通过对接收到的数字信号进行采样和重构,从而恢复出准确的时钟信息,保证数据的稳定传输和正确解析。

本文将介绍CDR的原理和应用,并详细阐述其在时钟恢复、数据传输和通信系统中的重要性。

一、CDR的原理和工作方式:1.1 采样和重构:CDR通过对接收到的数字信号进行采样,即在固定的时间间隔内对信号进行取样。

采样的目的是获取信号的瞬时状态,并将其转换为离散的数字值。

接着,CDR使用这些采样值来重构时钟信号,即通过插值和滤波等技术将离散的采样值转换为连续的时钟信号。

1.2 相位锁定环路(Phase Locked Loop, PLL):PLL是CDR的核心组成部分,用于将重构的时钟信号与接收到的信号进行比较和调整,以保持两者的相位同步。

PLL通过不断调整重构时钟信号的相位,使其与接收到的信号相位保持一致,从而实现时钟数据的恢复。

1.3 时钟频率调整:CDR还可以根据接收到的信号的频率特性来调整时钟的频率。

通过对信号进行频率分析和比较,CDR可以自动调整时钟频率,以适应信号的变化,确保数据的稳定传输和正确解析。

二、CDR在时钟恢复中的应用:2.1 光纤通信系统:在光纤通信系统中,光信号在传输过程中会受到光纤的衰减和色散等影响,导致信号的失真和时钟信息的丢失。

CDR技术可以通过恢复时钟信息,减小信号失真,提高数据传输的可靠性和稳定性。

2.2 高速串行通信接口:在高速串行通信接口中,时钟信号的准确性对于数据的传输速率和可靠性至关重要。

CDR技术可以通过恢复时钟信号,使接收端能够正确解析数据并保持与发送端的同步,实现高速数据传输。

2.3 数字存储系统:在数字存储系统中,时钟信号的准确性对于数据的读取和写入至关重要。

时钟数据恢复(CDR)

时钟数据恢复(CDR)时钟数据恢复(CDR)是一种用于恢复时钟信号的技术,它在现代通信和数据传输领域中起着重要的作用。

CDR技术可以有效地提取出传输信号中的时钟信息,使得接收端能够正确地解读数据。

本文将介绍CDR的基本原理、应用场景、性能指标、实现方式和未来发展方向。

一、CDR的基本原理1.1 时钟信号的重要性:时钟信号在数据传输中起着同步和定时的作用,是确保数据准确传输的关键。

1.2 时钟偏移和抖动:在数据传输中,时钟信号可能会受到噪声、失真等因素的影响,导致时钟偏移和抖动。

1.3 时钟恢复技术:CDR技术通过采样、滤波、锁相环等方法,对接收到的信号进行处理,恢复出准确的时钟信息。

二、CDR的应用场景2.1 光纤通信:在光纤通信中,CDR技术可以解决光纤传输中的时钟漂移和抖动问题,提高传输质量和稳定性。

2.2 高速串行链路:在高速串行链路中,CDR技术可以对传输信号进行时钟恢复,保证数据的准确性和可靠性。

2.3 无线通信:在无线通信中,CDR技术可以对接收到的信号进行时钟恢复,提高信号解调的效果,提升通信质量。

三、CDR的性能指标3.1 抖动容限:CDR技术的性能可以通过抖动容限来评估,即在不同信号条件下,CDR能够恢复出稳定的时钟信号的最大抖动范围。

3.2 时钟恢复时间:CDR技术的性能还可以通过时钟恢复时间来评估,即从接收到信号到恢复出稳定的时钟信号所需的时间。

3.3 误码率:CDR技术的性能还可以通过误码率来评估,即在时钟恢复后,数据传输中出现的错误比特率。

四、CDR的实现方式4.1 采样和保持:CDR技术中的采样和保持电路可以对传输信号进行采样,以获取时钟信息。

4.2 相位锁定环:CDR技术中的相位锁定环可以通过调整相位来实现时钟恢复,保证接收到的信号与本地时钟同步。

4.3 时钟恢复算法:CDR技术中的时钟恢复算法可以通过对采样数据进行处理,恢复出准确的时钟信号。

五、CDR的未来发展方向5.1 高速率:随着通信和数据传输领域的发展,对高速率的需求越来越大,CDR技术需要不断提高性能,以适应高速率传输的要求。

时钟数据恢复(CDR)

时钟数据恢复(CDR)时钟数据恢复(CDR)是一种重要的数字通信技术,用于在高速数据传输中恢复时钟信号。

本文将介绍时钟数据恢复的基本概念、工作原理、应用领域、优势以及发展趋势。

一、基本概念1.1 时钟数据恢复是指在数字通信系统中,通过采样和重构技术,从接收到的数据流中提取出时钟信号。

1.2 时钟数据恢复通常用于高速串行通信系统,以确保数据传输的稳定性和准确性。

1.3 时钟数据恢复可以根据不同的传输标准和速率进行调整和优化,以适应不同的应用场景。

二、工作原理2.1 时钟数据恢复的工作原理主要包括信号采样、时钟提取和时钟重构三个步骤。

2.2 信号采样是通过对接收到的数据流进行采样,获取数据的波形信息。

2.3 时钟提取是从采样的数据中提取出时钟信号,以确定数据的传输速率和时序关系。

2.4 时钟重构是根据提取出的时钟信号,对接收到的数据进行重新定时,以恢复原始的时钟信号。

三、应用领域3.1 时钟数据恢复广泛应用于高速数字通信系统,如光纤通信、高速总线、数据存储等领域。

3.2 在光纤通信系统中,时钟数据恢复可以提高数据传输的稳定性和可靠性,减少误码率。

3.3 在数据存储系统中,时钟数据恢复可以确保数据的读写速度和准确性,提高系统性能和可靠性。

四、优势4.1 时钟数据恢复可以有效解决高速数据传输中时钟漂移和时钟颤动等问题,提高系统的稳定性和可靠性。

4.2 时钟数据恢复可以适应不同的传输标准和速率,具有较强的通用性和灵便性。

4.3 时钟数据恢复技术不断发展和优化,可以满足不断增长的数据传输需求和挑战。

五、发展趋势5.1 随着数字通信技术的不断发展,时钟数据恢复技术将继续向更高速、更稳定、更智能的方向发展。

5.2 时钟数据恢复技术将与其他数字通信技术相结合,实现更高效的数据传输和处理。

5.3 时钟数据恢复技术将在5G通信、物联网、人工智能等领域发挥越来越重要的作用,推动数字化社会的发展和进步。

总结:时钟数据恢复是一种重要的数字通信技术,通过采样和重构技术,可以提取出时钟信号,确保高速数据传输的稳定性和准确性。

时钟恢复电路cdr技术

时钟恢复电路cdr技术时钟恢复电路(CDR)技术是一种用于恢复数字信号中的时钟信息的技术。

在数字通信中,时钟是保证数据传输准确性的关键因素之一。

由于传输线路中存在着各种噪声和干扰,数字信号的时钟信息可能会被损坏或失真。

CDR技术通过对接收到的信号进行时钟恢复和重构,有效地解决了时钟漂移和时钟抖动等问题,提高了数据传输的可靠性和稳定性。

CDR技术的核心思想是通过对接收到的信号进行采样和比较,恢复出信号中的时钟信息。

具体而言,CDR技术包括两个主要部分:时钟恢复和时钟重构。

时钟恢复的过程是通过对信号进行采样,利用采样点之间的差异来恢复出时钟信息。

而时钟重构的过程则是根据恢复出的时钟信号,重新生成时钟边沿,并对信号进行对齐和重构。

在时钟恢复的过程中,CDR技术需要解决的一个关键问题是时钟漂移。

时钟漂移是指由于传输线路的不稳定性或噪声干扰等原因,信号中的时钟边沿发生了偏移。

为了解决这个问题,CDR技术采用了自适应的时钟恢复算法。

这种算法可以根据信号的实际情况,动态地调整采样点的位置,以最大限度地减小时钟漂移对信号恢复的影响。

另外一个需要解决的问题是时钟抖动。

时钟抖动是指由于传输线路中存在的干扰和噪声,信号的时钟边沿发生了不规则的波动。

CDR 技术通过引入抖动抑制电路,可以有效地减小时钟抖动对信号恢复的影响。

抖动抑制电路一般采用锁相环(PLL)或相关器(correlator)等技术,可以根据信号的实际情况,动态地调整时钟边沿的位置,以最小化时钟抖动对信号恢复的影响。

除了时钟漂移和时钟抖动,CDR技术还需要解决的一个关键问题是时钟失步。

时钟失步是指由于传输线路中的干扰和噪声等原因,信号的时钟边沿发生了偏移或丢失。

CDR技术通过引入失步检测电路,可以及时地检测出时钟失步的情况,并采取相应的措施进行修正。

失步检测电路一般采用比较器或计数器等技术,可以根据信号的实际情况,动态地检测和纠正时钟失步,以保证数据传输的准确性和稳定性。

时钟数据恢复(CDR)

时钟数据恢复(CDR)引言概述:时钟数据恢复(CDR)是一种电子设备中常见的技术,它的主要作用是将传输过程中的时钟信号从输入数据中恢复出来。

CDR技术在通信、计算机和数据存储等领域中起着重要的作用。

本文将从四个方面详细介绍CDR技术的原理、应用、优势和未来发展。

一、CDR技术的原理1.1 时钟信号的重要性:时钟信号在数字系统中起着同步和定时的作用,是数据传输的基础。

没有准确的时钟信号,数据传输可能会出现错误。

1.2 时钟数据恢复的需求:在长距离传输、高速传输和复杂信道环境中,时钟信号可能会受到噪声、失真和抖动等干扰,导致时钟信号的丢失或变形。

1.3 CDR技术的原理:CDR技术通过采样、检测和锁定的方式,从输入数据中恢复出准确的时钟信号。

具体而言,CDR技术会对输入数据进行采样,检测采样点的时钟相位误差,并通过反馈机制调整本地时钟信号,最终实现时钟数据的恢复。

二、CDR技术的应用2.1 通信领域:CDR技术在光纤通信和高速数据传输中广泛应用。

它可以恢复出光纤通信中的时钟信号,保证数据的传输质量和可靠性。

2.2 计算机领域:CDR技术在计算机内部的总线、接口和芯片中使用。

它可以恢复出高速总线和接口中的时钟信号,确保数据的同步和稳定传输。

2.3 数据存储领域:CDR技术在硬盘驱动器和固态硬盘中起着重要的作用。

它可以恢复出存储介质中的时钟信号,确保数据的读取和写入的准确性和稳定性。

三、CDR技术的优势3.1 自适应性:CDR技术具有自适应性,可以根据输入数据的特性和环境条件自动调整时钟恢复的参数,适应不同的传输场景。

3.2 高精度:CDR技术能够实现高精度的时钟恢复,可以达到纳秒级的时钟相位误差,确保数据传输的准确性和稳定性。

3.3 抗干扰能力:CDR技术具有较强的抗干扰能力,可以有效抑制噪声、失真和抖动等干扰信号,提高数据传输的可靠性和鲁棒性。

四、CDR技术的未来发展4.1 高速传输:随着数据传输速率的不断提高,CDR技术将面临更高的挑战。

数据时钟恢复(CDR)工作原理及Altera的ASI、SDI IPcore应用

Tx(Cable Driver and decoder integrate $40 Total $90

$50 *:base fpga resource(800LES)

© 2004 Altera Corporation - Confidential 4

FPGA Soluiton Vs ASIC Solution1(ASI)

© 2004 Altera Corporation - Confidential 16

SVDB Board Overview

1SGX25FF1020 chip 2 SDI IO interfaces

3 VCXOs (27MHz, 74.25MHz (not installed)and 74.175MHz installed) 1 crystals (27MHz)

Pathological Case of 44 bits during Vertical Interval

© 2004 Altera Corporation - Confidential 8

Standards-SDI

© 2004 Altera Corporation - Confidential 9

ALTERA SDI/HD-SDI and DVB-ASI solution

Cytech FAE Robin luo

Oct,2004

© 2004 Altera Corporation

Agenda

SDI/HD-SDI and ASI application SDI interfaces DVB-ASI interface HD-SDI interface Altera FPGA Solution Reference design

光模块中cdr的作用

光模块中cdr的作用光模块中的CDR(Clock and Data Recovery)是一种时钟和数据恢复技术,它是光通信系统中非常重要的组成部分。

CDR的作用是在光信号传输过程中,实时提取出光信号中的时钟信号和数据信号,确保信号的传输质量和稳定性。

一、CDR的原理在光通信中,信号的传输是基于调制的方式进行的,调制后的信号包含了信号的时钟和数据信息。

在信号传输过程中,由于各种因素的干扰,信号会发生时钟抖动、相位偏移等问题,这会导致数据的丢失和错误。

为了解决这些问题,CDR采用了时钟恢复和数据恢复两个步骤。

首先,CDR会通过自适应电路提取出信号中的时钟信息,并通过时钟恢复电路产生一个稳定的时钟信号。

然后,CDR会根据该时钟信号对信号进行采样和重新定时,从而恢复出原始的数据信号。

二、CDR的作用1.信号时钟恢复:光信号在传输过程中容易受到信号衰减、传播延迟、多径效应等因素的影响,导致信号的时钟波形变形、抖动等问题。

CDR能够提取出信号中的时钟信息,并通过自适应电路消除时钟波形变形、抖动等问题,恢复出一个稳定的信号时钟。

2.数据恢复:光通信中的数据信号经过光纤的传输会发生衰减、相位偏移、时延等问题,导致数据的丢失和错误。

CDR能够根据恢复的信号时钟对光信号进行重新定时,从而恢复出原始的数据信号。

CDR通过数据恢复,提高了光通信系统中数据传输的可靠性和稳定性。

3.自适应功能:CDR具有自适应功能,能够根据实际的信号情况对时钟恢复和数据恢复进行动态调整。

当信号受到干扰或损耗较大时,CDR能够自动调整信号的采样时机和时钟恢复算法,提高信号的恢复质量。

4.兼容性:CDR能够适应不同的光模块和传输速率,具有很强的兼容性。

不同的光模块可能采用不同的调制方式和传输速率,CDR能够自动适应这些不同的参数,并进行相应的时钟恢复和数据恢复。

5.抗噪性能:光信号在传输过程中易受噪声和干扰的影响,导致信号的质量下降。

CDR具有较强的抗噪性能,能够消除信号中的噪声和干扰,提高信号的传输质量。

时钟数据恢复(CDR)

时钟数据恢复(CDR)引言概述:时钟数据恢复(Clock Data Recovery,CDR)是一种常见的数字信号处理技术,用于在数字通信系统中恢复丢失或损坏的时钟信号。

CDR技术在高速通信领域具有重要的应用价值,能够提高数据传输的可靠性和稳定性。

本文将从五个大点来详细阐述CDR技术的原理、应用、算法和发展趋势。

正文内容:1. CDR技术的原理1.1 时钟信号的重要性1.2 时钟信号的损失与恢复1.3 CDR技术的基本原理2. CDR技术的应用2.1 高速通信系统2.2 光纤通信系统2.3 无线通信系统3. CDR技术的算法3.1 直接数字控制(DDC)3.2 预估与补偿(Feedforward and Feedback)3.3 相位锁定环(Phase-Locked Loop,PLL)4. CDR技术的发展趋势4.1 高速率与低功耗4.2 自适应与自校准4.3 多通道与多模式5. CDR技术的挑战与解决方案5.1 噪声与抖动的影响5.2 时钟频率偏移的补偿5.3 多通道干扰的抑制总结:CDR技术作为一种重要的数字信号处理技术,在高速通信领域发挥着关键的作用。

本文从CDR技术的原理、应用、算法和发展趋势进行了详细阐述。

CDR技术的原理包括时钟信号的重要性、损失与恢复以及CDR技术的基本原理。

CDR技术在高速通信系统、光纤通信系统和无线通信系统等领域具有广泛的应用。

CDR 技术的算法包括直接数字控制、预估与补偿和相位锁定环等。

CDR技术的发展趋势主要包括高速率与低功耗、自适应与自校准以及多通道与多模式等方面。

然而,CDR技术也面临着一些挑战,如噪声与抖动的影响、时钟频率偏移的补偿和多通道干扰的抑制等。

未来,CDR技术将继续发展,以应对不断增长的通信需求。

时钟数据恢复(CDR)

时钟数据恢复(CDR)时钟数据恢复(CDR)是一种重要的数字信号处理技术,用于恢复由于传输过程中引起的时钟偏移或抖动而导致的数据失真。

本文将介绍时钟数据恢复的原理、应用、算法、性能和发展趋势。

一、时钟数据恢复的原理1.1 时钟数据恢复的基本概念时钟数据恢复是指通过对接收到的数字信号进行时钟提取和重构,以确保数据在接收端正确解调和处理的过程。

1.2 时钟信号的重要性时钟信号是数字通信系统中的关键信号,它决定了数据信号的采样时刻和速率,直接影响系统的性能和稳定性。

1.3 时钟数据恢复的原理时钟数据恢复通过采用PLL(锁相环)或者其他算法对接收到的信号进行时钟提取和重构,使得接收端的时钟与发送端的时钟保持同步。

二、时钟数据恢复的应用2.1 数字通信系统中的应用时钟数据恢复广泛应用于数字通信系统中,如光纤通信、无线通信、卫星通信等领域。

2.2 数据存储系统中的应用时钟数据恢复也被应用于数据存储系统中,如硬盘驱动器、固态硬盘等设备,以确保数据的读取和写入的准确性和稳定性。

2.3 其他领域的应用时钟数据恢复还被广泛应用于音频处理、视频处理、雷达系统等领域,以提高系统的性能和可靠性。

三、时钟数据恢复的算法3.1 PLL算法PLL算法是时钟数据恢复中常用的算法之一,通过不断调整本地时钟的频率和相位,使其与接收到的信号保持同步。

3.2 时域插值算法时域插值算法通过对信号进行插值处理,补偿传输过程中的时钟偏移和抖动,以恢复原始数据信号。

3.3 频域分析算法频域分析算法通过对信号进行频谱分析,提取信号的频率信息,从而实现时钟数据恢复。

四、时钟数据恢复的性能4.1 误码率时钟数据恢复的性能可以通过误码率来评估,误码率越低,说明时钟数据恢复的效果越好。

4.2 抖动抑制能力时钟数据恢复的性能还可以通过抖动抑制能力来评估,抖动抑制能力越强,说明时钟数据恢复对传输过程中的抖动影响越小。

4.3 鲁棒性时钟数据恢复的性能还可以通过其对噪声和干扰的抵抗能力来评估,鲁棒性越强,说明时钟数据恢复对环境变化的适应能力越强。

本科优秀毕业论文(时钟数据恢复)

摘要摘要本论文主要提供了一种实用的方式从数据流中恢复时钟,并以此时钟来恢复出原始数据,并且设计产生系统自检所需的信号。

本设计基于如今已经非常成熟的FPGA技术,采用一种非常新颖的方法成功实现了从数据流中同步恢复出时钟,并且采用纯数字电路的方法,利用EDA平台设计出了恢复原始数据的译码电路,此外,本设计还实现了系统自检;设计从实际应用的角度出发,旨在解决现实生活中的车载电子设备的通信问题,切合实际,同时,对现有的时钟同步数据恢复的方法进行学习与改进。

论文涵盖了模拟电路设计,数字电路设计,硬件编程,调试,软件仿真,逻辑综合各个方面,具有很大的现实意义。

关键词:时钟数据恢复,FPGA,锁相环,状态机IABSTRACTABSTRACTThis paper aims at providing a practical method to recovery the clock transformed by the data stream, through which it can decode the original data stream and it can create the self-checking signal needed by the system.My design succeeds to recovery the clock through the data stream based on the technology of mature FPGA and I achieve to design the decoding circuit by digital circuit on the platform of EDA. The research is from the practical point of view, aiming to solve communication problems in real life in-vehicle electronic devices. Also, we learn and improve on existing methods of clock and data recovery. The design contains analogy circuit design, digital circuit design, hardware programming, debug, simulation and logical synthesis and so on.Key Words: Clock and Data Recovery, FPGA, PLL, State MachineII目录第1章引言 (1)1.1数据恢复的同步设计和系统自检的概况和发展现状 (1)1.1.1时钟数据同步恢复电路的简介 (1)1.1.2系统自检的简介 (2)1.1.3时钟数据恢复电路的发展趋势 (2)1.2时钟数据恢复电路以及系统自检的必要性和挑战 (3)1.3本课题的研究目的和研究内容 (4)1.3.1研究目的 (4)1.3.2研究内容 (5)1.3.3论文的结构安排 (6)第2章传统的时钟数据恢复电路 (7)2.1概述 (7)2.2传统的时钟数据恢复电路的方法 (8)2.2.1前馈相位跟踪型CDR (8)2.2.2反馈相位跟踪型CDR (11)第3章基于FPGA的时钟数据恢复电路 (16)3.1设计任务概述 (16)3.2各模块电路设计 (16)3.2.1毛刺消除电路的设计 (16)3.2.2时钟恢复电路的设计 (18)3.2.3译码电路的设计 (24)3.2.3.1有限状态机的介绍 (25)3.2.3.2序列检测器的设计 (26)3.2.3.3时钟数据恢复电路 (29)第4章系统自检的设计以及电路中各个时钟的设计 (31)III4.1系统自检的设计 (31)4.1.1自检信号序列发生器的设计 (31)4.2时钟数据恢复电路中的时钟 (34)4.2.1时钟数据恢复电路系统的总体电路图 (34)4.3锁相环技术 (35)4.3.1锁相环简介 (35)4.3.1.1鉴相器 (36)4.3.1.2环路滤波器 (36)4.3.1.3压控振荡器 (37)4.3.2锁相环倍频获得所需时钟信号 (37)第5章结束语 (40)参考文献 (41)致谢 (42)外文资料原文 (43)外文资料翻译 (53)IV第1章引言第1章引言在高速串行数据通信中,为了节省开销,一般只传送数据信号而不传送与数据信号同步的时钟信号。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

时钟数据恢复(CDR)

2009-11-01 21:40 5887人阅读评论(5) 收藏举报测试图形ui产品工作任务

近年来,芯片功能的增强与数据吞吐量要求推动了芯片产业从低速率数据并行连接转变到高速串行连接。

这个概念被称为SERDES(Serializer-Deserializer),包括在高速差分对上串行地传送数据,而不就是用低速的并行总线。

一个典型例子就是用单个PCI-Express通道取代数据速率达2、112Gbps的传统32位66MHz PCI总线,PCI-Express可达到4Gbps的数据速率,但仅使用了工作在2、5GHz的4条线。

简而言之,SERDES协议允许用较少的引脚实现较高的数据速率。

图1给出了各种可能的SERDES接口。

这个例子展示了一个网络处理器位于系统中心的高性能电路板。

SERDES应用用紫色标明,可以用FPGA实现的芯片用黄色标明。

图1:典型的SERDES应用。

SERDES的类型

有两种基本类型的SERDES接口:源同步(SS)协议与时钟数据恢复(CDR)协议。

这两种类型的主要差别就是如何实现时钟控制。

源同步接口拥有一个伴随传送数据的时钟信号;CDR没有单独的时钟信号,而就是把时钟嵌入在数据中。

即CDR接收器将相位锁定在数据信号本身以获取时钟。

表1概括了这两种接口的基本差别。

表1:源同步与时钟数据恢复SERDES接口的比较。

通常CDR协议运行在较高的数据速率与较长的传送距离,因此带来很大的设计挑战。

时钟数据恢复的基础

顾名思义,CDR接收器必须从数据中恢复嵌入的时钟。

更准确地说,就是从数据信号的交换中获取时钟。

CDR发送器首先串行发送数据,然后将数据转换成8b/10b编码方案。

编码处理获得8位数据并将其转换成10位符号。

8b/10b编码方式可以在数据线上传送相等数目的0与1,从而减少码间干扰,并提供足够多的数据边沿,以便接收器在收到的数据流上锁定相位。

发送器将系统时钟倍频至传送比特率,并以该速率在TX差分对上发送8b/10b数据。

CDR接收器的任务首先就是在RX差分位流上锁定相位,然后接收器按照恢复的时钟进行数据位对齐,接着用接收器的参考时钟进行字对齐。

最后,将数据进行8b/10b解码,供系统使用。

在CDR系统中,发送与接收系统通常拥有完全独立的系统时钟。

这两个时钟在一个特定的变化范围内非常关键,这个范围大约就是数百个PPM。

CDR电路与抖动

CDR接口的主要设计挑战就是抖动,即实际数据传送位置相对于所期望位置的偏移。

总抖动(TJ)由确定性抖动与随机抖动组成。

大多数抖动就是确定的,其分量包括码间干扰、串扰、占空失真与周期抖动(例如来自开关电源的干扰)。

而通常随机抖动就是半导体发热问题的副产品,且很难预测。

传送参考时钟、传送PLL、串化器与高速输出缓冲器都对会传送抖动造成影响。

对于给定的比特周期或者数据眼,传送抖动通常用单位间隔的百分比或UI(单位间隔)来说明。

例如,、2 UI 的传送抖动表示抖动由比特周期的20%组成。

对于传送抖动而言,UI数值越低越好,因为它们代表较少的抖动。

同样地,CDR接收器将指定在给定比特率时所能容忍的最大抖动量。

典型的比特误码率(BET)标准就是1e-12。

接收抖动仍然用UI来指定。

较大的UI表明接收器可以容忍更多的抖动。

典型的接收器规格就是、8 UI,这意味着80%的比特周期可以就是噪声,此时接收器将仍然能够可靠地接收数据。

抖动通常用统计钟形分布来量化,该分布在其定点处有理想的边沿位置。

SERDES测试与眼图

由于抖动就是SERDES系统中的一个主要挑战,因此它也就是测试与测量的关键所在。

通过把高性能的示波器连接到SERDES信号来测量抖动,并观察“数据眼图”(或眼图)。

对于一个给定的差分对,眼图仅仅就是由多个状态转换的波形图叠加而成。

采样窗应足够宽,能够包含图中的两个交叉点。

最终得到的画面就象一个眼睛,它提供了信号质量与抖动的直观形象。

通常眼睛张得越开,信号就越好。

图2就是一个在示波器上显示的典型眼图。

图中,用V度量眼睛张开的高度,该值与1、2V

的总电压摆幅(从逻辑0到逻辑1)相对。

有三个宽度(或者时间)度量值:UI度量整个比特率周期,H度量在共模电压下的张开度,T度量最小跳变电压与最大跳变电压下的宽度。

较大的H、T与V值代表眼睛较宽,这说明信号较好、抖动较小。

图2:一个数据眼图示例。

抖动测量设置

为检测传送抖动,用误码率测试器(BERT)产生测试图形,并送入评估板的SERDES接收端口。

同样地,将时钟产生器连接到评估板的SERDES时钟。

在测试中,FPGA被配置成内部环回这个通道,因此接收到的测试图形通过TX引脚传送。

将示波器连接到TX SERDES连接器,这样就可以对传送抖动眼图进行分析。

所有的评估板SERDES连接都采用的就是50欧姆SMA连接器。

整体结构如图3所示。

图3:抖动测试设备的配置。

通过在FPGA SERDES接收端口引入抖动,并监控环回SERDES输出的比特误差来测量接收抖动容限。

如图3所示,首先将抖动发生器连接到BERT图形产生器。

然后BERT产生器将伪随机图形序列(PRBS)发送到评估板的SERDES SMA输入。

这种配置允许工程师以一种受控的方式将抖动引入到SERDES RX端口。

FPGA被配置成环回,SERDES TX端口连接到BERT的比特误差检测端口。

然后工程师就可以引入抖动并观察由FPGA产生的比特误码率(BER)。

当BER超出规定时,工程师就知道已经超过抖动容限域值。

这个数值应该等于或大于针对FPGA所指定的接收抖动容限。

高速背板性能测量

通过背板配置驱动FPGA的TX信号,工程师可以测量FPGA的背板SERDES链路传输特性,然后分析背板输出的眼图。

首先使用BERT图形产生器把PRBS位流馈送入FPGA评估板的SMA RX端口。

通过把FPGA配置成环回,PRBS将出现在评估板的TX端口,并将被驱动至同轴电缆,馈入诸如XAUI Z-Pack HM-Zd的背板。

然后背板将位流馈送入连接到示波器的另一长度的同轴电缆。

系统要求规定了测试参数,例如PRBS图形选择、背板与FPGA评估板的走线长度、同轴电缆的长度、预加重与均衡设置、工作电压以及VCC。

图4展示了采用LatticeSC FPGA的测试设备采样到的9个眼图。

每个眼图下的数值就是测量到的眼睛高度(图2中的V度量)。

注意增加预加重在每个比特率上改善了眼图。

预加重就是SERDES发送器针对电缆与背板中信号衰减的补偿。

LatticeSC要求的眼睛高度就是

85mV,因此在3、8Gbps下16%的预加重就是唯一不满足要求的采样。

本文小结

值得一提的就是,SERDES接口为FPGA产品的选择过程增加了一个参数。

当选择FPGA

时工程师应该考虑可能的信道数目、信道的配置灵活性、接口速度、SERDES IP(即PCS)、传输规范与电气要求。

FPGA产品与SERDES接口的速度与市场规模都在增长。

通过理解两者功能与挑战,设计团队可以提升产品的可靠性与功能,并加快产品上市时间。