16X16点阵显示综合实验eda

16x16点阵显示实验报告

16*16点阵显示实验报告一、实验目的(1)学习点阵显示字符的基本原理。

(2)掌握用数控分频控制速度,实现点阵扫描的基本方式。

(3)会使用Quartus II软件中的Verilog HDL语言实现点真的行列循环显示。

二、实验设备与器件Quartus II 软件、EP2C8Q208C8实验箱三、实验方案设计1.实验可实现的功能可通过编写Verilog HDL语言,实现点阵的行列交替扫描。

先是行扫描,扫描间隔为1s,16行都扫描完之后开始列扫描,扫描间隔仍然为1s,16列扫描完之后,行继续扫描,依次循环。

2.点阵基本知识16*16扫描LED点阵只要其对应的X、Y轴顺向偏压,即可使LED发亮。

例如如果想使左上角LED点亮,则Y0=1,X0=0即可。

应用时限流电阻可以放在X轴或Y轴。

它有16个共阴极输出端口,每个共阴极对应有16个LED显示灯。

LED点阵每个点都有一个红色的发光二极管。

点阵内的二极管间的连接都是行共阳,列共阴。

本实验采用共阴,当二极管的共阳极为高电平,共阴极为低电平时,所接点发光;反之处于截止状态,不放光。

3.系统工作原理本系统用了两个模块,其中dianzhen.v是顶层文件,而hangsaomiao.v和liesaomiao.v是两个子模块,总体的系统功能框图如图3.3.1所示。

图3.3.1 系统功能图示通过流程图可以看到,体统是先将试验箱的50MHz时钟信号分频为1s,因为要实现16*16的点阵扫描,所以用一个16s的计时器计时,每经过16s行扫描与列扫描的状态转换一次,通过点阵显示出来。

4.模块化程序设计(1)点阵显示顶层程序设计module dianzhen (clk50mhz,row,sel0,sel1,sel2,sel3,line);input clk50mhz; //实验箱提供50MHz时钟信号output sel0,sel1,sel2,sel3; //设置引脚选通点阵output reg [15:0] row; //行output reg [3:0] line; //列wire [15:0] row1,row2;wire [3:0] line1,line2;reg [24:0] cnt=0; //1Hz计数子reg [4:0] cnt1=0; //16s计数子assign sel0=1'b0;assign sel1=1'b1;assign sel2=1'b0;assign sel3=1'b0;always@(posedge clk50mhz)beginif(cnt>=25'd5*******)begincnt<=25'b0; //1Hz计时器cnt1<=cnt1+1; //16s计时器endelsecnt<=cnt+1;endhangsaomiao u1(.clk50mhz(clk50mhz),.row(row1),.line(line1)); liesaomiao u2(.clk50mhz(clk50mhz),.row(row2),.line(line2));always@(*)if(cnt1<=5'd15)beginrow<=row1; //行扫描line<=line1;endelsebeginrow<=row2; //列扫描line<=line2;endendmodule(2)行扫描模块hangsaomiao.v程序设计module hangsaomiao(clk50mhz,line,row);input clk50mhz; //实验箱输入50MHz时钟信号output reg [15:0] row; //列output reg [3:0] line; //行reg [24:0] cnt1,cnt2; //计数子reg clkrow,clkline; //行脉冲、列脉冲always@(posedge clk50mhz)beginif(cnt1>=25'd5*******)begincnt1<=25'b0;clkrow=~clkrow; //1s列脉冲endelsecnt1<=cnt1+1;endalways@(posedge clk50mhz)beginif(cnt2>=25'd500)begincnt2<=25'b0;clkline=~clkline; //50KHz行脉冲endelsecnt2<=cnt2+1;endalways@(posedge clkline)begincase(line)4'd0:line<=4'd1; //高速行扫描4'd1:line<=4'd2;4'd2:line<=4'd3;4'd3:line<=4'd4;4'd4:line<=4'd5;4'd5:line<=4'd6;4'd6:line<=4'd7;4'd7:line<=4'd8;4'd8:line<=4'd9;4'd9:line<=4'd10;4'd10:line<=4'd11;4'd11:line<=4'd12;4'd12:line<=4'd13;4'd13:line<=4'd14;4'd14:line<=4'd15;4'd15:line<=4'd0;default:line<=4'd0;endcaseendalways@(posedge clkrow) //时间间隔为1s的列扫描begincase(row)16'b0000000000000001: row<=16'b0000000000000010;16'b0000000000000010: row<=16'b0000000000000100;16'b0000000000000100: row<=16'b0000000000001000;16'b0000000000001000: row<=16'b0000000000010000;16'b0000000000010000: row<=16'b0000000000100000;16'b0000000000100000: row<=16'b0000000001000000;16'b0000000001000000: row<=16'b0000000010000000;16'b0000000010000000: row<=16'b0000000100000000;16'b0000000100000000: row<=16'b0000001000000000;16'b0000001000000000: row<=16'b0000010000000000;16'b0000010000000000: row<=16'b0000100000000000;16'b0000100000000000: row<=16'b0001000000000000;16'b0001000000000000: row<=16'b0010000000000000;16'b0010000000000000: row<=16'b0100000000000000;16'b0100000000000000: row<=16'b1000000000000000;16'b1000000000000000: row<=16'b0000000000000001;default : row<=16'b0000000000000001;endcaseendendmodule(3)列扫描模块liesaomiao.v程序设计module liesaomiao(clk50mhz,row,line);input clk50mhz; //实验箱输入50MHz 时钟信号output reg [15:0] row; //行output reg [3:0] line; //列reg [24:0] cnt; //计数子reg clk;always@(posedge clk50mhz)beginif(cnt>=25'd5*******)begincnt<=25'b0;clk=~clk; //1sendelsecnt<=cnt+1;endalways @ (posedge clk) //列扫描begincase(line)4'h0:begin row=16'b1111111111111111;line<=4'h1; end4'h1:begin row=16'b1111111111111111;line<=4'h2; end4'h2:begin row=16'b1111111111111111;line<=4'h3; end4'h3:begin row=16'b1111111111111111;line<=4'h4; end4'h4:begin row=16'b1111111111111111;line<=4'h5; end4'h5:begin row=16'b1111111111111111;line<=4'h6; end4'h6:begin row=16'b1111111111111111;line<=4'h7; end4'h7:begin row=16'b1111111111111111;line<=4'h8; end4'h8:begin row=16'b1111111111111111;line<=4'h9; end4'h9:begin row=16'b1111111111111111;line<=4'ha; end4'ha:begin row=16'b1111111111111111;line<=4'hb; end4'hb:begin row=16'b1111111111111111;line<=4'hc; end4'hc:begin row=16'b1111111111111111;line<=4'hd; end4'hd:begin row=16'b1111111111111111;line<=4'he; end4'he:begin row=16'b1111111111111111;line<=4'hf; end4'hf:begin row=16'b1111111111111111;line<=4'h0; enddefault:line<=4'h0;endcaseendendmodule5.下载电路及引脚分配设计设计中用实验箱自带的50MHz时钟信号作为输入端,用sel0、sel1、sel2、sel3四个使能端选通点阵,EP2C8Q208C8就会工作在给点阵下命令的状态,并用line和row分别作为点阵的行、列选通端,最终使得点阵正常工作,如图3.5.1所示。

16×16点阵显示实验 实验报告

1.实验现象

当设计文件加载到目标器件后,将数字信号源模块的时钟选择为1KHZ,按下矩阵键盘的某一个键,则在数码管上显示对应的这个键标识的键值,当再按下第二个键的时候前一个键的键值在数码管上左移一位。按下“*”键则在数码管是显示“E”键值。按下“#”键在数码管上显示“F”键值。

2.实验图片记录

2)新建VHDL File(程序)

3)编译仿真

4)管脚分配

5)下载调试

2)加强对总线产生地址定位的CPLD实现方法的理解

3)掌握在FPGA中调用ROM的方法

成绩: 教师:

实验报告

一、实验内容及步骤

1.实验内容

1)通过编程实现对16×16点阵的控制

2)在点阵循环中显示“欢迎使用嵌入式SDC开发系统”这几个汉字和字符

3)运用软件对程序进行编译和仿真

2.实验步骤:

1)新建工程

成绩: 教师: 批改日期:

பைடு நூலகம்湖南科技大学

物理与电子科学学院专业实验报告

实验课程:FPGA实验原理

实验项目:16×16点阵显示实验

专 业:物理与电子科学学院

班 级:电子信息科学与技术3班

***********

学 号:**********

实验日期: 年 月 日

实验预习报告

一、实验目的及要求

1)加强点阵字符产生的显示原理和系统的16×16点阵的工作原理

单片机16×16点阵显示实验总结400字

单片机16×16点阵显示实验总结400字单片机16×16点阵显示实验总结这次实验我们使用单片机设计了16×16点阵显示器的驱动电路,并成功实现了在点阵上显示字符、数字和图案的功能。

下面是对本次实验的总结。

首先,我们按照实验手册的指示,采用逐行扫描的方式驱动16×16点阵显示器。

通过设置接口电路和引脚连接,将单片机与点阵电路相连,实现数据和控制信号的传输。

接着,我们编写了相应的程序代码,在单片机上进行编译和烧录,并使用示波器进行调试。

在调试过程中,我们发现了一些常见的问题,比如接口线连接错误、引脚配置错误等,及时解决这些问题,确保了实验的顺利进行。

接下来,我们开始编写点阵显示的控制程序。

通过对点阵每一个LED灯珠的亮灭状态进行控制,我们可以实现在点阵上显示不同的字符、数字和图案。

我们编写了一个字符库,其中包含了常用字符和数字的点阵码。

通过查表的方式,我们可以根据需要在点阵上显示相应的内容。

在编写程序的过程中,我们充分利用了单片机的IO口和定时器的功能,并采用了合理的算法,提高了程序的执行效率。

在实验过程中,我们遇到了一些困难和挑战。

首先,点阵显示器的像素较多,对于单片机的计算能力和IO口的数量有一定要求。

因此,在编写程序的过程中,我们需要注意内存和资源的使用,避免发生卡顿或者无法正常显示的情况。

其次,点阵显示器的扫描速度要求较高,需要通过设置定时器的中断来实现,以确保显示的稳定性和清晰度。

通过本次实验,我们不仅掌握了单片机的基本原理和编程技巧,还深入了解了点阵显示器的工作原理和驱动方式。

通过自主设计和编写代码,我们成功实现了在16×16点阵上显示字符、数字和图案的功能。

这不仅加深了我们对嵌入式系统的理解,还提高了我们的动手实践能力和问题解决能力。

总之,通过这次实验,我们不仅学到了很多知识,还锻炼了自己的动手能力和团队合作能力。

虽然在实验过程中遇到了一些困难,但通过不懈努力和团队合作,我们最终取得了成功。

16X16点阵显示综合实验new

EDA 综合课程设计(四)——16X16点阵显示综合实验16X16点阵控制接口一、 实验要求设计一个共阴16X16点阵控制接口,要求:在时钟信号的控制下,使点阵动态点亮,点亮方式自行设计,其中列选信号为16-4编码器编码输出。

控制器的引脚功能图如上图所示,其中:DIN[3..0]为显示花样模式选择,高电平有效;CLK 为时钟输入端;DOTOUT[15..0]为行驱动信号输出;SELOUT[3..0]为列选信号输出,为16-4编码信号。

图案1实现16X16点阵的16列同时从上往下依次点亮,全亮后16列又同时从下往上依次熄灭。

列选信号:采用与7段数码管的位选信号一样的处理方法,即列扫描信号频率大于24HZ 。

行驱动信号:可以采用移位的方法,可先定义一个16位的信号,若最高位置为‘1’,我们采用右移的方法,使每一位都置‘1’,这就实现依次点亮;当第0位也置‘1’后,给第0位置‘0’,二、实验内容16X16点阵控制接口引脚功能再采用左移的方法将每一位又重新置‘0’,这样就实现了反相依次熄灭,等第15位为‘0’时,又重新开始,以此循环。

对于其他的显示花样,请自行设计。

三、实验连线将CP端接时钟输出,并使输入频率约为1MHZ,DIN[3..0]分别接4位拨码开关,DOTOUT[15..0]分别接显示模块的L15~L0,SELOUT[3..0]分别接显示模块的SEL3~SEL0。

16X16点阵字符发生器一、实验目的:1、了解点阵字符的产生和显示原理。

2、了解E2PROM和16×16点阵LED的工作机理。

3、加强对于总线产生,地址定位的CPLD实现的理解。

二、硬件要求:1.主芯片EPF10K10LC84-4。

2.可变时钟源。

3.带有事先编程好字库/字符的E2PROM 2864。

4.16×16扫描LED点阵。

三、实验原理:16×16扫描LED点阵的工作原理同8位扫描数码管类似。

它有16个共阴极输出端口,每个共阴极对应有16个LED显示灯。

16×16 LED点阵显示实验

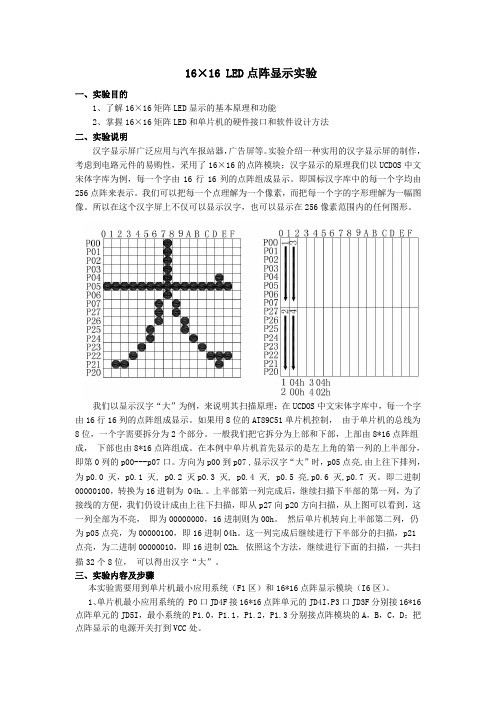

16×16 LED点阵显示实验一、实验目的1、了解16×16矩阵LED显示的基本原理和功能2、掌握16×16矩阵LED和单片机的硬件接口和软件设计方法二、实验说明汉字显示屏广泛应用与汽车报站器,广告屏等。

实验介绍一种实用的汉字显示屏的制作,考虑到电路元件的易购性,采用了16×16的点阵模块;汉字显示的原理我们以UCDOS中文宋体字库为例,每一个字由16行16列的点阵组成显示。

即国标汉字库中的每一个字均由256点阵来表示。

我们可以把每一个点理解为一个像素,而把每一个字的字形理解为一幅图像。

所以在这个汉字屏上不仅可以显示汉字,也可以显示在256像素范围内的任何图形。

我们以显示汉字“大”为例,来说明其扫描原理:在UCDOS中文宋体字库中,每一个字由16行16列的点阵组成显示。

如果用8位的AT89C51单片机控制,由于单片机的总线为8位,一个字需要拆分为2个部分。

一般我们把它拆分为上部和下部,上部由8*16点阵组成,下部也由8*16点阵组成。

在本例中单片机首先显示的是左上角的第一列的上半部分,即第0列的p00---p07口。

方向为p00到p07 ,显示汉字“大”时,p05点亮,由上往下排列,为p0.0 灭,p0.1 灭, p0.2 灭p0.3 灭, p0.4 灭, p0.5 亮,p0.6 灭,p0.7 灭。

即二进制00000100,转换为16进制为 04h.。

上半部第一列完成后,继续扫描下半部的第一列,为了接线的方便,我们仍设计成由上往下扫描,即从p27向p20方向扫描,从上图可以看到,这一列全部为不亮,即为00000000,16进制则为00h。

然后单片机转向上半部第二列,仍为p05点亮,为00000100,即16进制04h。

这一列完成后继续进行下半部分的扫描,p21点亮,为二进制00000010,即16进制02h. 依照这个方法,继续进行下面的扫描,一共扫描32个8位,可以得出汉字“大”。

16x16点阵-EDA课程设计

应用科学学院SOPC/EDA综合课程设计报告设计题目:设计者:学号:班级:指导老师:完成时间:目录第1章总体设计原理及原理框图 (1)1.1 设计原理 (1)1.2顶层文件设计 (2)1.3总体仿真图 (2)第2章单元电路设计 (4)2.1时序控制模块设计 (4)2.1.1时序控制模块的源程序及其实体图 (4)2.1.2时序控制模块仿真 (5)2.2扫描控制模块设计 (5)2.2.1扫描控制模块源程序及其实体图 (5)2.2.2扫描控制模块仿真 (6)2.3显示控制模块源程序及其实体图 (6)2.3.1显示控制模块 (6)2.3.2显示控制模块仿真 (21)第3章心得体会 (22)参考文献 (23)1第1章 总体设计原理及原理框图1.1 设计原理首先我们设计要正确显示这些字,显示屏上的灯的亮暗情况具体应如何。

如第一个字‘江’:第一种方案 第二种方案如果高电平‘1 时表示灯是亮的,低电平‘0’时灯是暗的,这样上面的灯呈现在我们眼前的就是‘江’字了。

依次类推,我们就可以设计出所有要显示的字了。

使用FPGA 设计一个16×16的点阵显示的控制器,使点阵显示器以两种花样显示“江西理工大学应用科学学院欢迎您”第一种花样是用亮着的灯组合所要显示的字,第二种方案是用暗着的灯组成所需要的字。

这样这些字就好象是被我们当作了固定模型了。

但如何点亮这些灯呢,这就要求有一个脉冲循环扫描的电路,我们采用列扫描,当扫描的和我们先设计好的字模型的高电平相匹配时,灯就相应的点亮。

由于扫描的速度很快,我们人的眼睛并不会感到灯的闪烁,所以每扫描完16列就会显示在我们眼中一个字了。

但要所有的字母就可以依次的显示出来并不停的循环显示,就还要再有一个时序控制电路来控制。

此时序控制电路象一个计数器,有自动清零的功能,这样就可以实现循环的效果了。

其设计原理图框图如下图1.1 总体设计框图1.2顶层文件设计顶层文件来实现循环显示各个字的功能。

vhdl实验报告_16乘16点阵_列选_显示

综合实践总结报告综合实践名称: EDA技术与实践综合实践地点、时间一.题目功能分析和设计实验的要求有如下三点:1.用16*16点阵的发光二极管显示字符;2.可显示字符为0~9的数字字符与A~F英文字母的大写;3.输入为四位二进制矢量;按照要求可知,LED点阵模块,共由16×16=256个LED发光二极管组成,如何在该点阵模块上显示数字和字母是本实验的关键。

先将要显示的每一幅图像画在一个16×16共256个小方格的矩形框中,再在有笔划下落处的小方格里填上“1”,无笔划处填上“0”,这样就形成了与这个汉字所对应的二进制数据在该矩形框上的分布以数字8为例,点阵分布为:0000000000000000000000000000000000011111111110000001111111111000000110000001100000011000000110000001100000011000000111111111100000011111111110000001100000011000000110000001100000011000000110000001111111111000000111111111100000000000000000000000000000000000考虑到实际物理实验平台上点阵发光二极管的原理,以下为16×16点阵LED外观图,只要其对应的X、Y轴顺向偏压,即可使LED 发亮。

例如如果想使左上角LED点亮,则Y0=1,X0=0即可。

所以我采用行列扫描的方法,用四位二进制数做列选信号(总共16列),如选中第一列,则扫描第一列之中哪些行是高电平(1),哪些行是低电平(0);为高电平的则点亮,为低电平的不亮。

(列信号都接地)。

如此,列选信号由“0000”变到“1111”时,16列扫描完毕,一个字也就出来了,列选信号重新由“0000”开始扫描。

注意扫描频率必须要足够快,才能保证显示一个数字或字母时所有灯在肉眼看来是同时在闪烁的。

16×16点阵EDA课程设计报告

EDA 综合实践总结报告一、综合实践的目的 (3)二、综合实践理论基础和核心内容 (3)三、综合实践具体内容和记录 (3)四、综合实践总结及分析 (7)五、综合实践所需仪器设备 (7)六、参考资料 (7)七、成绩评定表 (8)一、综合实践的目的1.熟悉MAX+PLUSⅡ编程环境。

2.掌握MAX+PLUSⅡ原理图输入和文本输入。

3.掌握MAX+PLUSⅡ对设计文件的编译和仿真。

4.掌握VHDL语言中的顺序语句和并行语句以及程序的基本结构。

5.了解点阵屏显示字符的原理与过程。

二、综合实践理论基础和核心内容1. 给点阵24HZ以上的列扫描信号,同时给行不同的字符编码,从而让点阵显示不同的花色和字符2. 用两个三八译码器对四位二进制数进行译码从而实现16位二进制数的循环移位,以此作为16位列扫描信号。

3. 点阵控制器的rst时钟输入用来控制行依次亮灭的速度,因此其频率必须小于24HZ以保证人眼能够区分。

4. din用来控制点阵显示不同的字符和花色,应当在实验开始前就接高电平或低电平,当din给低电平时,点阵的行从上往下依次点亮后又从下往上依次熄灭;当din给高电平时,点阵屏上循环显示“中”“国”“人”三个字。

三、综合实践具体内容和记录程序清单如下所示library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;entity X16 isport(clk,rst:in std_logic;dout:out std_logic_vector(15 downto 0);hl:buffer std_logic_vector(3 downto 0)); end X16;architecture A of X16 issignal row:std_logic_vector(15 downto 0);signal dow:std_logic_vector(4 downto 0);beginA:process(hl)begincase hl iswhen "0000"=>row<="1000000000000000";when "0001"=>row<="0100000000000000";when "0010"=>row<="0010000000000000";when "0011"=> row<="0001000000000000";when "0100"=> row<="0000100000000000";when "0101"=> row<="0000010000000000";when "0110"=> row<="0000001000000000";when "0111"=> row<="0000000100000000";when "1000"=> row<="0000000010000000";when "1001"=> row<="0000000001000000"; when "1010"=> row<="0000000000100000"; when "1011"=> row<="0000000000010000"; when "1100"=> row<="0000000000001000"; when "1101"=> row<="0000000000000100"; when "1110"=> row<="0000000000000010"; when "1111"=> row<="0000000000000001"; when others=> row<="0000000000000000"; END case;end process A;B:process(clk,rst,dow)variable m:integer:=0;beginif rst='1' then dout<="0000000000000000"; hl<="0000"; dow<="00000";elsif clk'event and clk='1' thenm:=m+1;if dow="10100" thendow<="00000";elsif m=300 thendow<=dow+1;m:=0;end if;if hl>15 thenhl<="0000";else hl<=hl+1;end if;case dow iswhen "00000"=>case hl iswhen "0000" =>dout<="0000000000000000"; when "0001" =>dout<="0000000000000000"; when "0010" =>dout<="0000000000000000"; when "0011" =>dout<="0000000000000000"; when "0100" =>dout<="0000000000000000"; when "0101" =>dout<="0000000000000000"; when "0110" =>dout<="0000000000000000"; when "0111" =>dout<="0000000000000000"; when "1000" =>dout<="0000000000000000"; when "1001" =>dout<="0000000000000000"; when "1010" =>dout<="0000000000000000"; when "1011" =>dout<="0000000000000000"; when "1100" =>dout<="0000000000000000";when "1110" =>dout<="0000000000000000"; when "1111" =>dout<="1111111111111111"; when others=>dout<=null;end case;when "00001"=>case hl iswhen "0000" =>dout<="1111111111111111"; when "0001" =>dout<="0000000000000000"; when "0010" =>dout<="0000000000000000"; when "0011" =>dout<="0000000000000000"; when "0100" =>dout<="0000000000000000"; when "0101" =>dout<="0000000000000000"; when "0110" =>dout<="0000000000000000"; when "0111" =>dout<="0000000000000000"; when "1000" =>dout<="0000000000000000"; when "1001" =>dout<="0000000000000000"; when "1010" =>dout<="0000000000000000"; when "1011" =>dout<="0000000000000000"; when "1100" =>dout<="0000000000000000"; when "1101" =>dout<="0000000000000000";when "1111" =>dout<="1111111111111111"; when others=>dout<=null;end case;when "00010"=>case hl iswhen "0000" =>dout<="1111111111111111"; when "0001" =>dout<="1111111111111111"; when "0010" =>dout<="0000000000000000"; when "0011" =>dout<="0000000000000000"; when "0100" =>dout<="0000000000000000"; when "0101" =>dout<="0000000000000000"; when "0110" =>dout<="0000000000000000"; when "0111" =>dout<="0000000000000000"; when "1000" =>dout<="0000000000000000"; when "1001" =>dout<="0000000000000000"; when "1010" =>dout<="0000000000000000"; when "1011" =>dout<="0000000000000000"; when "1100" =>dout<="0000000000000000"; when "1101" =>dout<="0000000000000000"; when "1110" =>dout<="0000000000000000"; when "1111" =>dout<="1111111111111111";when others=>dout<=null;end case;when "00011"=>case hl iswhen "0000" =>dout<="1111111111111111"; when "0001" =>dout<="1111111111111111"; when "0010" =>dout<="1111111111111111"; when "0011" =>dout<="0000000000000000"; when "0100" =>dout<="0000000000000000"; when "0101" =>dout<="0000000000000000"; when "0110" =>dout<="0000000000000000"; when "0111" =>dout<="0000000000000000"; when "1000" =>dout<="0000000000000000"; when "1001" =>dout<="0000000000000000"; when "1010" =>dout<="0000000000000000"; when "1011" =>dout<="0000000000000000"; when "1100" =>dout<="0000000000000000"; when "1101" =>dout<="0000000000000000"; when "1110" =>dout<="0000000000000000"; when "1111" =>dout<="1111111111111111"; when others=>dout<=null;end case;when "00100"=>case hl iswhen "0000" =>dout<="1111111111111111"; when "0001" =>dout<="1111111111111111"; when "0010" =>dout<="1111111111111111"; when "0011" =>dout<="1111111111111111"; when "0100" =>dout<="0000000000000000"; when "0101" =>dout<="0000000000000000"; when "0110" =>dout<="0000000000000000"; when "0111" =>dout<="0000000000000000"; when "1000" =>dout<="0000000000000000"; when "1001" =>dout<="0000000000000000"; when "1010" =>dout<="0000000000000000"; when "1011" =>dout<="0000000000000000"; when "1100" =>dout<="0000000000000000"; when "1101" =>dout<="0000000000000000"; when "1110" =>dout<="0000000000000000"; when "1111" =>dout<="1111111111111111"; when others=>dout<=null;end case;when "00101"=>case hl iswhen "0000" =>dout<="1111111111111111"; when "0001" =>dout<="1111111111111111"; when "0010" =>dout<="1111111111111111"; when "0011" =>dout<="1111111111111111"; when "0100" =>dout<="1111111111111111"; when "0101" =>dout<="0000000000000000"; when "0110" =>dout<="0000000000000000"; when "0111" =>dout<="0000000000000000"; when "1000" =>dout<="0000000000000000"; when "1001" =>dout<="0000000000000000"; when "1010" =>dout<="0000000000000000"; when "1011" =>dout<="0000000000000000"; when "1100" =>dout<="0000000000000000"; when "1101" =>dout<="0000000000000000"; when "1110" =>dout<="0000000000000000"; when "1111" =>dout<="1111111111111111"; when others=>dout<=null;end case;when "00110"=>case hl iswhen "0000" =>dout<="1111111111111111"; when "0001" =>dout<="1111111111111111";when "0011" =>dout<="1111111111111111"; when "0100" =>dout<="1111111111111111"; when "0101" =>dout<="1111111111111111"; when "0110" =>dout<="0000000000000000"; when "0111" =>dout<="0000000000000000"; when "1000" =>dout<="0000000000000000"; when "1001" =>dout<="0000000000000000"; when "1010" =>dout<="0000000000000000"; when "1011" =>dout<="0000000000000000"; when "1100" =>dout<="0000000000000000"; when "1101" =>dout<="0000000000000000"; when "1110" =>dout<="0000000000000000"; when "1111" =>dout<="1111111111111111"; when others=>dout<=null;end case;when "00111"=>case hl iswhen "0000" =>dout<="1111111111111111"; when "0001" =>dout<="1111111111111111"; when "0010" =>dout<="1111111111111111"; when "0011" =>dout<="1111111111111111";when "0101" =>dout<="1111111111111111"; when "0110" =>dout<="0000000000000000"; when "0111" =>dout<="0000000000000000"; when "1000" =>dout<="0000000000000000"; when "1001" =>dout<="0000000000000000"; when "1010" =>dout<="0000000000000000"; when "1011" =>dout<="0000000000000000"; when "1100" =>dout<="0000000000000000"; when "1101" =>dout<="0000000000000000"; when "1110" =>dout<="0000000000000000"; when "1111" =>dout<="1111111111111111"; when others=>dout<=null;end case;when "01000"=>case hl iswhen "0000" =>dout<="1111111111111111"; when "0001" =>dout<="1111111111111111"; when "0010" =>dout<="1111111111111111"; when "0011" =>dout<="1111111111111111"; when "0100" =>dout<="1111111111111111"; when "0101" =>dout<="1111111111111111";when "0111" =>dout<="0000000000000000"; when "1000" =>dout<="0000000000000000"; when "1001" =>dout<="0000000000000000"; when "1010" =>dout<="0000000000000000"; when "1011" =>dout<="0000000000000000"; when "1100" =>dout<="0000000000000000"; when "1101" =>dout<="0000000000000000"; when "1110" =>dout<="0000000000000000"; when "1111" =>dout<="1111111111111111"; when others=>dout<=null;end case;when "01001"=>case hl iswhen "0000" =>dout<="1111111111111111"; when "0001" =>dout<="1111111111111111"; when "0010" =>dout<="1111111111111111"; when "0011" =>dout<="1111111111111111"; when "0100" =>dout<="1111111111111111"; when "0101" =>dout<="1111111111111111"; when "0110" =>dout<="1111111111111111"; when "0111" =>dout<="1111111111111111";when "1001" =>dout<="0000000000000000"; when "1010" =>dout<="0000000000000000"; when "1011" =>dout<="0000000000000000"; when "1100" =>dout<="0000000000000000"; when "1101" =>dout<="0000000000000000"; when "1110" =>dout<="0000000000000000"; when "1111" =>dout<="1111111111111111"; when others=>dout<=null;end case;when "01010"=>case hl iswhen "0000" =>dout<="1111111111111111"; when "0001" =>dout<="1111111111111111"; when "0010" =>dout<="1111111111111111"; when "0011" =>dout<="1111111111111111"; when "0100" =>dout<="1111111111111111"; when "0101" =>dout<="1111111111111111"; when "0110" =>dout<="1111111111111111"; when "0111" =>dout<="1111111111111111"; when "1000" =>dout<="1111111111111111"; when "1001" =>dout<="0000000000000000";when "1011" =>dout<="0000000000000000"; when "1100" =>dout<="0000000000000000"; when "1101" =>dout<="0000000000000000"; when "1110" =>dout<="0000000000000000"; when "1111" =>dout<="1111111111111111"; when others=>dout<=null;end case;when "01011"=>case hl iswhen "0000" =>dout<="1111111111111111"; when "0001" =>dout<="1111111111111111"; when "0010" =>dout<="1111111111111111"; when "0011" =>dout<="1111111111111111"; when "0100" =>dout<="1111111111111111"; when "0101" =>dout<="1111111111111111"; when "0110" =>dout<="1111111111111111"; when "0111" =>dout<="1111111111111111"; when "1000" =>dout<="1111111111111111"; when "1001" =>dout<="1111111111111111"; when "1010" =>dout<="0000000000000000"; when "1011" =>dout<="0000000000000000";when "1101" =>dout<="0000000000000000"; when "1110" =>dout<="0000000000000000"; when "1111" =>dout<="1111111111111111"; when others=>dout<=null;end case;when "01100"=>case hl iswhen "0000" =>dout<="1111111111111111"; when "0001" =>dout<="1111111111111111"; when "0010" =>dout<="1111111111111111"; when "0011" =>dout<="1111111111111111"; when "0100" =>dout<="1111111111111111"; when "0101" =>dout<="1111111111111111"; when "0110" =>dout<="1111111111111111"; when "0111" =>dout<="1111111111111111"; when "1000" =>dout<="1111111111111111"; when "1001" =>dout<="1111111111111111"; when "1010" =>dout<="1111111111111111"; when "1011" =>dout<="0000000000000000"; when "1100" =>dout<="0000000000000000"; when "1101" =>dout<="0000000000000000";when "1111" =>dout<="1111111111111111";when others=>dout<=null;end case;when "01101"=>case hl iswhen "0000" =>dout<="1111111111111111";when "0001" =>dout<="1111111111111111";when "0010" =>dout<="1111111111111111";when "0011" =>dout<="1111111111111111";when "0100" =>dout<="1111111111111111";when "0101" =>dout<="1111111111111111";when "0110" =>dout<="1111111111111111";when "0111" =>dout<="1111111111111111";when "1000" =>dout<="1111111111111111";when "1001" =>dout<="1111111111111111";when "1010" =>dout<="1111111111111111";when "1011" =>dout<="1111111111111111";when "1100" =>dout<="0000000000000000";when "1101" =>dout<="0000000000000000";when "1110" =>dout<="0000000000000000";when "1111" =>dout<="1111111111111111";when others=>dout<=null;end case;when "01110"=>case hl iswhen "0000" =>dout<="1111111111111111"; when "0001" =>dout<="1111111111111111"; when "0010" =>dout<="1111111111111111"; when "0011" =>dout<="1111111111111111"; when "0100" =>dout<="1111111111111111"; when "0101" =>dout<="1111111111111111"; when "0110" =>dout<="1111111111111111"; when "0111" =>dout<="1111111111111111"; when "1000" =>dout<="1111111111111111"; when "1001" =>dout<="1111111111111111"; when "1010" =>dout<="1111111111111111"; when "1011" =>dout<="1111111111111111"; when "1100" =>dout<="1111111111111111"; when "1101" =>dout<="0000000000000000"; when "1110" =>dout<="0000000000000000"; when "1111" =>dout<="1111111111111111"; when others=>dout<=null;end case;when "01111"=>case hl iswhen "0000" =>dout<="1111111111111111"; when "0001" =>dout<="1111111111111111"; when "0010" =>dout<="1111111111111111"; when "0011" =>dout<="1111111111111111"; when "0100" =>dout<="1111111111111111"; when "0101" =>dout<="1111111111111111"; when "0110" =>dout<="1111111111111111"; when "0111" =>dout<="1111111111111111"; when "1000" =>dout<="1111111111111111"; when "1001" =>dout<="1111111111111111"; when "1010" =>dout<="1111111111111111"; when "1011" =>dout<="1111111111111111"; when "1100" =>dout<="1111111111111111"; when "1101" =>dout<="1111111111111111"; when "1110" =>dout<="0000000000000000"; when "1111" =>dout<="1111111111111111"; when others=>dout<=null;end case;when "10000"=>case hl iswhen "0000" =>dout<="1111111111111111"; when "0001" =>dout<="1111111111111111"; when "0010" =>dout<="1111111111111111"; when "0011" =>dout<="1111111111111111"; when "0100" =>dout<="1111111111111111"; when "0101" =>dout<="1111111111111111"; when "0110" =>dout<="1111111111111111"; when "0111" =>dout<="1111111111111111"; when "1000" =>dout<="1111111111111111"; when "1001" =>dout<="1111111111111111"; when "1010" =>dout<="1111111111111111"; when "1011" =>dout<="1111111111111111"; when "1100" =>dout<="1111111111111111"; when "1101" =>dout<="1111111111111111"; when "1110" =>dout<="1111111111111111"; when "1111" =>dout<="1111111111111111"; when others=>dout<=null;end case;when "10001"=>case hl iswhen "0000" =>dout<="0000000000000000"; when "0001" =>dout<="0000000000000000";when "0011" =>dout<="0000010000010000"; when "0100" =>dout<="0000010000010000"; when "0101" =>dout<="0000010000010000"; when "0110" =>dout<="0000010000010000"; when "0111" =>dout<="1111111111111111"; when "1000" =>dout<="0000010000010000"; when "1001" =>dout<="0000010000010000"; when "1010" =>dout<="0000010000010000"; when "1011" =>dout<="0000010000010000"; when "1100" =>dout<="0000010000010000"; when "1101" =>dout<="0000011111110000"; when "1110" =>dout<="0000000000000000"; when "1111" =>dout<="0000000000000000"; when others=>dout<=null;end case;when "10010"=>case hl iswhen "0000" =>dout<="0000000000000000"; when "0001" =>dout<="0111111111111100"; when "0010" =>dout<="0100000000000100"; when "0011" =>dout<="0101000000010100";when "0101" =>dout<="0101010100010100"; when "0110" =>dout<="0101001100010100"; when "0111" =>dout<="0101111111110100"; when "1000" =>dout<="0101000100010100"; when "1001" =>dout<="0101000100010100"; when "1010" =>dout<="0101000100010100"; when "1011" =>dout<="0101000100010100"; when "1100" =>dout<="0101000000010100"; when "1101" =>dout<="0100000000000100"; when "1110" =>dout<="0111111111111100"; when "1111" =>dout<="0000000000000000"; when others=>dout<=null;end case;when "10011"=>case hl iswhen "0000" =>dout<="1000000000000000"; when "0001" =>dout<="0100000000000000"; when "0010" =>dout<="0010000000000000"; when "0011" =>dout<="0001000000000000"; when "0100" =>dout<="0000100000000000"; when "0101" =>dout<="0000010000000000";when "0111" =>dout<="0000000111111111";when "1000" =>dout<="0000000100000000";when "1001" =>dout<="0000001000000000";when "1010" =>dout<="0000010000000000";when "1011" =>dout<="0000100000000000";when "1100" =>dout<="0001000000000000";when "1101" =>dout<="0010000000000000";when "1110" =>dout<="0100000000000000";when "1111" =>dout<="1000000000000000";when others=>dout<=null;end case;when others=>null;end case;end if;end process;end A;gdf原理图如下图所示:四、综合实践总结及分析1.通过软件的仿真和硬件的验证,实验结果准确无误,点阵屏显示效果良好。

实验四 16X16点阵LED实验

实验四 16X16点阵LED实验一.实验目的1.了解点阵显示的原理及控制方法;2.学会使用16X16点阵LED,通过编程显示不同的字符。

二.实验原理及相关电路16X16点阵了的由16X16列共256个发光二极管紧密排在一起构成,程序控制每个像素点(发光二极管)的亮灭,就能用来显示汉字或者图形。

LED的每一行的16列发光二极管都由一个4位的16进制数来控制,从左往右由低位到高位。

将每一个字的显示都用16个16位进制数表示,称为字模。

本实验,分别控制LED灯行的动态扫描,高电平为灭低电平为点亮;用16进制数控制LED灯每一列的亮灭,高电平为亮,低电平为灭。

为了实现显示屏上字的滚动显示,则需要将所显示的字向右移,并取下一个字的最右边一位补充到显示屏的最左边,形成动态滚动的效果。

三.实验内容及程序1.用单片机的端口控制16*16点阵的行与列,在点阵LED显示屏上显示“单”。

#include <p24FJ64GA006.h>void Delayms(unsigned int del){unsigned int j;while(del--)for(j=0;j<1000;j++); } //定义Delaym函数void IOInit() //初始化端口{AD1PCFG= 0xFFFF; //全部设置为数字TRISD=TRISB= 0x0000; //D和B端口全部设为输出TRISE=TRISF= 0x0000; //E和F端口全部设为输出}int main(void){unsigned int state_E,state_F,temp_E,temp_F; IOInit();state_F = 0xFFFE; //初始化F端口状态unsigned int i=0;unsigned int dan[]={0x0410,0x0C60,0x0220,0x1FFC,0x1084,0x1FFC,0x1084,0x1084,0x1FFC,0x1084,0x0080,0x7FFF,0x0080,0x0080,0x0080,0x0080}; //单while(1){PORTD = dan[i];PORTB = dan[i]; //将字模同时赋给B和D端口PORTF = state_F; //将行状态的低8位赋给F端口低8位state_E=temp_E=temp_F=state_F;state_E <<= 8;state_E = (state_F&0xFF00)|((temp_E>>8)&0x00FF); //行状态左移8位PORTE = state_E; //将行状态高8位赋给E端口低8位Delayms( 1 );state_F <<= 1;state_F = (state_F&0xFFFE)|((temp_F>>15)&0x0001);//将行状态左移一位,动态扫描i++;if(i==16)i=0;}}显示结果:注:中间空出一行是因为PORTF的第8位为空,不影响显示效果2.在点阵LED显示屏上滚动显示“单片机实验室欢迎您”。

EDA 16x16点阵显示.

课程设计报告课程名称数字系统与逻辑设计课题名称16*16点阵显示专业通信工程班级学号姓名指导教师乔汇东胡瑛2012年7月2日湖南工程学院课程设计任务书课程名称数字系统与逻辑设计课题16*16点阵显示专业班级通信工程1001班学生姓名学号指导老师乔汇东胡瑛审批乔汇东任务书下达日期2012 年6月23日任务完成日期2012 年7月2日《数字系统与逻辑设计》课程设计任务书一、设计目的全面熟悉、掌握VHDL语言基本知识,掌握利用VHDL语言对常用的的组合逻辑电路和时序逻辑电路编程,把编程和实际结合起来,熟悉编制和调试程序的技巧,掌握分析结果的若干有效方法,进一步提高上机动手能力,培养使用设计综合电路的能力,养成提供文档资料的习惯和规范编程的思想。

二、设计要求1、设计正确,方案合理。

2、程序精炼,结构清晰。

3、设计报告5000字以上,含程序设计说明,用户使用说明,源程序清单及程序框图。

4、上机演示。

5、有详细的文档。

文档中包括设计思路、设计仿真程序、仿真结果及相应的分析与结论。

三、进度安排第二十周星期一:课题讲解,查阅资料星期二:总体设计,详细设计星期三:编程,上机调试、修改程序星期四:上机调试、完善程序星期五:答辩星期六-星期天:撰写课程设计报告附:课程设计报告装订顺序:封面、任务书、目录、正文、评分、附件(A4大小的图纸及程序清单)。

正文的格式:一级标题用3号黑体,二级标题用四号宋体加粗,正文用小四号宋体;行距为22。

正文的内容:一、课题的主要功能;二、课题的功能模块的划分(要求画出模块图);三、主要功能的实现;四、系统调试与仿真;五、总结与体会;六、附件(所有程序的原代码,要求对程序写出必要的注释);七、评分表。

目录一. 16*16点阵显示的总体设计 (1)1.116*16点阵显示 (1)1.2基本设计思想 (1)二. 16*16点阵显示的功能实现 (3)2.1系统的总体框图 (3)2.2系统的流程图 (3)2.3系统各功能模块实现 (4)三.系统的调试与仿真 (8)四.总体与体会 (9)五附件 (10)六评分表 (16)一. 16*16点阵显示的总体设计1.1 16*16点阵显示本实验主要完成汉字字符在LED 上的显示,16*16 扫描LED 点阵的工作原理与8 位扫描数码管类似,只是显示的方式与结果不一样而已。

EDA技术综合设计课程设计-基于VHDL的16×16汉字 点阵动态显示系统的设计

《EDA技术综合设计》课程设计报告报告题目:基于VHDL的16×16汉字点阵动态显示系统的设计作者所在系部:电子工程系作者所在专业:电子信息工程摘要随着电子技术的不断革新,以二极管为基础的LED点阵随之获得了广泛的应用。

在日常生活中,点阵随处可见。

通过多种控制手段,点阵还可以实现各种文字和图案的动态显示。

而在不同的应用场合,点阵的设计要求是不同的。

传统的思路一般是应用单片机实现点阵控制,但这种方法会受到一定的硬件资源限制。

随着电子设计自动化技术的进展,基于可编程逻辑器件进行系统芯片集成的点阵控制不失为一种新的设计思路。

本设计以电子设计自动化(EDA)技术为核心,运用硬件描述语言(VHDL),在MAX+plus Ⅱ环境下进行编程并下载到可编程逻辑器件中实现LED点阵的控制电路。

主要程序除了常用的译码器、计数器之外,还包括了自定义功能的控制模块。

通过编程、调试、仿真、下载完成了汉字的动态显示。

彰显了EDA技术在当今电子领域中的重要地位。

关键词:EDA、可编程逻辑器件、计数器、点阵、动态目录一、概述 (5)二、方案设计与论证 (5)1、点亮点阵中一个点的原理 (5)2、点亮一个字的原理 (5)3、动态显示不同汉字的原理 (5)三、底层文件与程序设计 (6)1.十六进制计数器 (6)2.八进制计数器 (7)3.字显示控制模块 (8)四、系统调试与仿真 (12)1、开发环境介绍 (12)2、新建项目 (12)3、输入程序 (12)4、编译 (13)5、时序仿真 (13)6、设计顶层文件 (14)7、选择器件 (14)8、设置管脚 (14)9、下载 (14)五、硬件调试 (15)六、心得体会 (15)七、参考文献 (15)八、指导教师及评语 (16)课程设计任务书课题名称基于VHDL的16×16点阵汉字动态显示系统的设计完成时间指导教师职称学生姓名班级总体设计要求和技术要点1.在时钟信号的控制下,使点阵动态点亮,点亮方式自行设计,其中位选信号为16-4编码器编码输出。

SOPCEDA综合课程设计---1616的点阵显示设计

SOPC/EDA综合课程设计报告设计题目:16*16的点阵显示设计设计者:学号:班级:指导老师:完成时间:目录绪论 (1)第一章设计项目与分析 (2)1.1设计要求: (2)1.2设计原理 (2)1.3设计框图 (3)1.4顶层文件设计 (3)第二章一屏一屏亮灯显示 (5)2.1时序控制模块设计 (5)2.2扫描控制模块设计 (6)2.3显示控制模块设计 (7)2.4显示控制模块仿真 (15)第三章暗灯显示 (16)3.1暗灯控制模块设计 (16)3.2扫描控制模块设计 (17)3.3暗灯显示控制模块设计 (18)第四章心得体会 (27)参考文献 (28)绪论1 在信息产业中EDA产生的影响随着大规模集成电路技术和计算机技术的不断发展,在设计通信,国防,航天医学工业自动化计算机应用仪器仪表等领域的电子系统设计工作中,EDA技术的含量正以惊人的速度上升;电子类的高新技术项目的开发也逾益依赖于EDA技术的应用,即使是普通的电子产品的开发,EDA技术常常使一些原来的技术瓶颈得以轻松突破,从而使得产品的开发周期大为缩短,性能价格大幅度提高。

不言而喻。

EDA技术将迅速成为电子设计领域中的极其重要的组成部分。

2 中国国内EDZ发展情况从目前的EDA技术来看,其发展趋势是政府重视使用普及应用广泛工具多样软件功能强大。

中国EDA市场已渐趋成熟,不过大部分设计工程师面向的是PC主板的小型ASIC领域,仅有小部分的设计人工发复杂片上系统器件,为了与台湾和美国的设计工程师形成更有力的竞争,中国的设计队伍有必要购入一些最新的EDA技术。

在信息通信领域,优先发展高速宽带信息网,深亚微米集成电路,新型元器件,计算机及软件技术,第三代移动通信技术。

信息管理,信息安全技术,积极开拓以数字技术,网络技术为基础的新一代产品,发展新兴产业,培育新的经济增长点。

要大力推进制造业信息化,积极开展计算机辅助设计(CAD),计算机辅助工程(CAE),计算机辅助工艺(CAPP),j计算机辅助制造(CAM),产品数据管理(PDM),制造资源计划(MRPII),以及企业管理资源(ERP)等。

EDA实验 16×16点阵字符显示设计

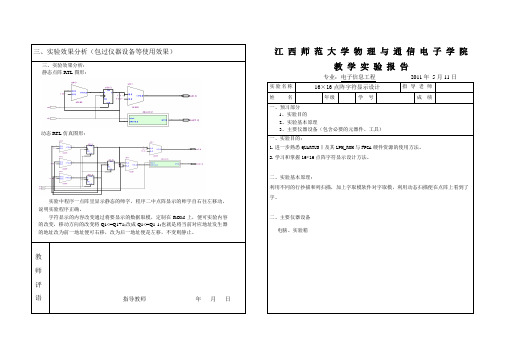

三、实验效果分析(包过仪器设备等使用效果)三、实验效果分析:静态点阵RTL图形:动态RTL仿真图形:实验中程序一点阵里显示静态的师字,程序二中点阵显示的师字自右往左移动,说明实验程序正确。

字符显示的内容改变通过将要显示的数据取模,定制在ROM上,便可实验内容的改变,移动方向的改变将Q1<=Q1+1;改成Q1<=Q1-1;也就是将当前对应地址发生器的地址改为前一地址便可右移,改为后一地址便是左移,不变则静止。

教师评语指导教师年月日江西师范大学物理与通信电子学院教学实验报告专业:电子信息工程2011年5月11日实验名称16×16点阵字符显示设计指导老师姓名年级学号成绩一、预习部分1、实验目的2、实验基本原理3、主要仪器设备(包含必要的元器件、工具)一、实验目的:1.进一步熟悉QUARTUS‖及其LPM_ROM与FPGA硬件资源的使用方法。

2.学习和掌握16*16点阵字符显示设计方法。

二、实验基本原理:利用不同的行抄描和列扫描,加上字取模软件对字取模,利用动态扫描便在点阵上看到了字。

二、主要仪器设备电脑、实验箱二、实验操作步骤1.实验数据、表格及数据处理2.实验操作过程(可以用图表示)3.结论1.实验数据、表格及数据处理如下:library ieee; if rst='1'thenuse ieee.std_logic_1164.all; qa<=(others=>'0');use ieee.std_logic_unsigned.all; elsif clk'event and clk='1' thenentity sy12 is qa<=qa+1;port(clk,rst:in std_logic; end if;sel:out std_logic_vector(3 downto 0); end process;dout:out std_logic_vector(15 downto 0)); process(qa,rst)end ; beginarchitecture one of sy12 is if rst='1' thencomponent data_rom q1<=(others=>'0');port (address:in std_logic_vector(4 downto 0); elsif qa(10)'event and qa(10)='1' then inclock:in std_logic; q1<=q1+1; --当前所有地址改为对应的下一q:out std_logic_vector(15 downto 0)); end if; 地址,即整体左移end component; end process;signal qa:std_logic_vector(10 downto 0); sel<=not(q0-2);signal q0:std_logic_vector(3 downto 0); qq<=q1+q0;signal qq:std_logic_vector(4 dow u1: data_rom port map(address=>qq,q=>dout,inclock=>clk); signal q1:std_logic_vector(4 downto 0); end;beginprocess(clk,rst)beginif rst='1' thenq0<=(others=>'0');elsif clk'event and clk='1' thenq0<=q0+1;end if ;end process;process(clk,rst)begin 2、实验操作过程如下:library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;entity sy11 isport(clk,rst:in std_logic;sel:out std_logic_vector(3 downto 0);dout:out std_logic_vector(15 downto 0));end ;architecture one of sy11 iscomponent data_romport (address:in std_logic_vector(4 downto 0);inclock:in std_logic;q:out std_logic_vector(15 downto 0));end component;signal qq:std_logic_vector(4 downto 0);signal q1:std_logic_vector(4 downto 0);beginprocess(clk,rst)beginif rst='1' thenq1<=(others=>'0');elsif clk'event and clk='1' thenq1<=q1+1; end if ;end process;qq<=q1-1;sel<=not qq(3 downto 0);u1:data_rom port map(address=>q1,q=>dout,inclock=>clk); end;。

16X16点阵显示实验

实验报告实验名称: [16X16点阵显示实验]姓名:学号:指导教师:实验时间: [2013年6月15日]信息与通信工程学院16X16点阵显示实验1、实验要求:理解并掌握点阵显示符号的原理,理解原有程序,会使用动态扫描的方式使点阵显示汉字,明白点阵滚动显示的原理。

根据原有程序,掌握LPM_ROM的应用,会应用LPM_ROM存储需要显示的内容。

参照液晶显示程序,编写16*16点阵显示程序。

任务一:实现点阵列扫描。

点亮点阵的一列,并让其不断的向右移动。

任务二:在点阵上循环滚动显示“嵌入式系统设计”。

2、实验原理:2.1点阵基本原理本实验对点阵的扫描使用列扫描的方式。

就是将要显示的数据分成16列,在某一时刻只选中一列,并向点阵传送该列需要显示的数据,那么如果从左往右依次循环选中所有列,并且循环的速度足够快,因为视觉停留效应,我们就能看到完整的显示了。

如果要显示大于16列的信息,比如要显示多个汉字,由于只能同时显示16列,那么就需要在一个比较慢的时钟的指挥下,不断更新要显示的连续的16列数据,使用这样的方法就能实现滚动显示。

2.2任务原理8*8LED点阵共由64个发光二极管组成,每个发光二极管放置在行线和列线的交叉点上,当对应的某一行高电平(置1),且某一列低电平(置0),则相应的发光二极管就亮;因此要用8*8LED点阵来显示一个字符或汉字,只需要根据字符或汉字图形中的线条或笔画,通过点亮多个发光二极管来勾勒出字符或汉字的线条或笔画就行了。

当要比较完美的显示一般的汉字,单个8*8LED点阵模块很难做到,因为LED的点数(也称为像素点)不够多,因此要显示汉字的话,需要多个8*8LED点阵拼合成一个显示屏。

假如用4个8*8LED点阵模块拼成16*16的点阵,即能满足一般汉字的显示。

16×16扫描LED点阵的工作原理同8位扫描数码管类似。

它有16个共阴极输出端口,每个共阴极对应有16个LED显示灯,所以其扫描译码地址需4位信号线(SEL0-SEL3),其汉字扫描码由16位段地址(0-15)输入。

16x16 LED点阵实验

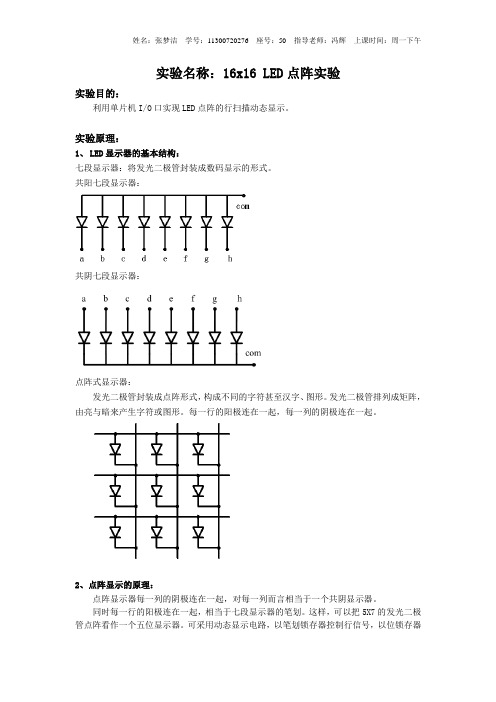

实验名称:16x16 LED点阵实验实验目的:利用单片机I/O口实现LED点阵的行扫描动态显示。

实验原理:1、LED显示器的基本结构:七段显示器:将发光二极管封装成数码显示的形式。

共阳七段显示器:共阴七段显示器:点阵式显示器:发光二极管封装成点阵形式,构成不同的字符甚至汉字、图形。

发光二极管排列成矩阵,由亮与暗来产生字符或图形。

每一行的阳极连在一起,每一列的阴极连在一起。

2、点阵显示的原理:点阵显示器每一列的阴极连在一起,对每一列而言相当于一个共阴显示器。

同时每一行的阳极连在一起,相当于七段显示器的笔划。

这样,可以把5X7的发光二极管点阵看作一个五位显示器。

可采用动态显示电路,以笔划锁存器控制行信号,以位锁存器控制列信号。

3、实验原理图使用两片8位输出锁存移位寄存器74HC595(三态输出、串入并出),将单片机I/O口发出的串行数据转换为并行数据LD_QA~LD_QP,作为16×16 LED点阵显示器的行线,使用另外两片8位74HC595作为 16×16 LED点阵显示器的列线LD_1~LD_16。

当行输出高电平、列输出低电平时,可以点亮点阵。

74HC595:LD-QA~LD-QP:点阵行控制信号LD-1~LD-16:点阵列控制信号SER(14脚):串行数据输入端-SCLR(10脚):低电平时将移位寄存器的数据清零。

通常将它接Vcc。

SCK(11脚):上升沿时将串行数据移入移位寄存器。

RCK(12脚):上升沿时移位寄存器的数据锁存入数据寄存器。

-G(13脚): 高电平时禁止输出(高阻态)时序图:实验内容:在16×16LED点阵上分别用静态方式和滚屏方式显示自己的姓(行扫描)。

实验步骤:使用导线将A2区的P10~P14与C3区的L_DAT_H 、L_DAT_L、L_CLK、L_OE 、 L_STR实验设计:电路图:(修改后加上了74HC595输出端口与LED点阵相连的端口名称)1、静态方式:流程图:代码及注释:HL EQU 70H ;行信号低位内存地址LL EQU 72H ;列信号低位内存地址HD EQU P1.0 ;p1.0口连行信号输入端LD EQU P1.1 ;P1.1口连列信号输入端SCK EQU P1.2 ;P1.2口连移位寄存器OE EQU P1.3 ;P1.3口连使能端RCK EQU P1.4 ;P1.4口连锁存器ORG 8000H ;硬件仿真程序LJMP MAINORG 8100H ;硬件仿真程序MAIN:MOV DPTR,#DISPLAY ;字模表地址MOV R1,#00H ;字模表起始地址偏移量MOV HL,#01H ;行扫描信号的初值0001HMOV HL+1,#00HLOOP:MOV A,R1MOVC A,@A+DPTRMOV LL,A ;找到列低位数据,存入内存地址中INC R1MOV A,R1MOVC A,@A+DPTRMOV LL+1,A ;找到列高位数据,存入内存地址中LCALL SENDD ;调用传输数据的程序LCALL DELAY ;调用延时程序CLR C ;位处理累加器清零MOV A,HLRLC A ;左移行扫描信号低8位MOV HL,AMOV A,HL+1RLC A ;左移行扫描信号高8位MOV HL+1,AINC R1CJNE R1,#20H,LOOP ;判断一轮扫描是否结束LJMP MAINSENDD:CLR OE ;使能信号低电平有效CLR RCK ;RCK信号置0MOV R2,#08HMOV R3,LL+1 ;列信号高八位地址MOV R4,HL+1 ;行信号高八位地址BACK:CLR SCK ;SCK信号置0MOV A,R3RLC AMOV R3,AMOV LD,C ;列信号逐位传输MOV A,R4RLC AMOV R4,AMOV HD,C ;行信号逐位传输SETB SCK ;SCK信号上升沿到来,将串行数据移入移位寄存器DJNZ R2,BACK ;判断高8位信号是否传输完毕MOV R2,#08HMOV R3,LL ;列信号低8位地址MOV R4,HL ;行信号低8位地址BACK1:CLR SCK ;SCK信号置0MOV A,R3RLC AMOV R3,AMOV LD,C ;列信号逐位传输MOV A,R4RLC AMOV R4,AMOV HD,C ;行信号逐位传输SETB SCK ;SCK信号上升沿到来,将串行数据移入移位寄存器DJNZ R2,BACK1 ;判断低8位信号是否传输完毕SETB RCK ;RCK信号上升沿到来,移位寄存器的数据锁存入数据寄存器RETDELAY: ;延时子程序MOV R7,#50DELAY1:MOV R6,#10DELAY2:DJNZ R6,$DJNZ R7,DELAY1RETDISPLAY:DB 0xFF,0xFE,0xE0,0xEE,0xEF,0xCE,0xEF,0xF6,0xE1,0xFA,0xFD,0xFC,0xFD,0xFE,0x3D,0x80;DB 0xE0,0xFA,0xED,0xFA,0xEF,0xF6,0xEF,0xF6,0xEF,0xEE,0xEF,0x9A,0x6B,0xDC,0xF7,0xFE;"张" END2、滚屏方式流程图:代码及注释:HL EQU 70H ;行信号低位内存地址LL EQU 72H ;列信号低位内存地址HD EQU P1.0 ;p1.0口连行信号输入端LD EQU P1.1 ;P1.1口连列信号输入端SCK EQU P1.2 ;P1.2口连移位寄存器OE EQU P1.3 ;P1.3口连使能端RCK EQU P1.4 ;P1.4口连锁存器ORG 8000H ;硬件仿真程序LJMP MAINORG 8100H ;硬件仿真程序MAIN:MOV DPTR,#DISPLAY ;字模表地址MOV R1,#00HMOV R7,#00H ;R7用来表示字模表起始位置偏移量LOOP:MOV R5,#20 ;R5用来表示延时,改变R5的值可改变滚屏速度LOOP1:MOV R6,#10H ;R6用来判断是否扫描完一轮MOV A,R7 ;将R7的值赋值给R1MOV R1,AMOV HL,#01H ;行扫描信号的初值0001HMOV HL+1,#00HLOOP2:MOV A,R1MOVC A,@A+DPTRMOV LL,A ;找到列低位数据,存入内存地址中INC R1MOV A,R1MOVC A,@A+DPTRMOV LL+1,A ;找到列高位数据,存入内存地址中LCALL SENDD ;调用传输数据的程序LCALL DELAY ;调用延时程序CLR C ;位处理累加器清零MOV A,HLRLC A ;左移行扫描信号低八位MOV HL,AMOV A,HL+1RLC A ;左移行扫描信号高八位MOV HL+1,AINC R1DEC R6CJNE R6,#00H,LOOP2 ;通过R6判断是否扫描完一轮,R6减为0,一轮扫描结束DJNZ R5,LOOP1 ;通过R5判断一帧的延时是否达到INC R7 ;改变字模表的偏移量INC R7 ;R7连续加2,相当于换行CJNE R7,#40H,LOOP ;判断字模表是否结束LJMP MAINSENDD:CLR OE ;使能信号低电平有效CLR RCK ;RCK信号置0MOV R2,#08HMOV R3,LL+1 ;列信号高8位地址MOV R4,HL+1 ;行信号高8位地址BACK:CLR SCK ;SCK信号置0MOV A,R3RLC AMOV R3,AMOV LD,C ;列信号逐位传输MOV A,R4RLC AMOV R4,AMOV HD,C ;行信号逐位传输SETB SCK ;SCK信号上升沿到来,将串行数据移入移位寄存器DJNZ R2,BACK ;判断高八位信号是否传输完毕MOV R2,#08HMOV R3,LL ;列信号低八位地址MOV R4,HL ;行信号低八位地址BACK1:CLR SCK ;SCK信号置0MOV A,R3RLC AMOV R3,AMOV LD,C ;列信号逐位传输MOV A,R4RLC AMOV R4,AMOV HD,C ;行信号逐位传输SETB SCK ;SCK信号上升沿到来,将串行数据移入移位寄存器DJNZ R2,BACK1 ;判断低八位信号是否传输完毕SETB RCK ;RCK信号上升沿到来,移位寄存器的数据锁存入数据寄存器RETDELAY: ;延时子程序MOV R2,#50DELAY1:MOV R3,#10DELAY2:DJNZ R3,$DJNZ R2,DELAY1RETDISPLAY:DB 0xFF,0xFF,0xFF,0xFF,0xFF,0xFF,0xFF,0xFF,0xFF,0xFF,0xFF,0xFF,0xFF,0xFF,0xFF,0xFFDB 0xFF,0xFF,0xFF,0xFF,0xFF,0xFF,0xFF,0xFF,0xFF,0xFF,0xFF,0xFF,0xFF,0xFF,0xFF,0xFF;预留空白DB 0xFF,0xFE,0xE0,0xEE,0xEF,0xCE,0xEF,0xF6,0xE1,0xFA,0xFD,0xFC,0xFD,0xFE,0x3D,0x80;DB 0xE0,0xFA,0xED,0xFA,0xEF,0xF6,0xEF,0xF6,0xEF,0xEE,0xEF,0x9A,0x6B,0xDC,0xF7,0xFE;"张" END实验结果与分析:1、程序正确运行后,可看到16x16 LED点阵显示屏上显示“张”,LED灯的亮暗程度有些不均匀。

EDA16x16点阵滚动+动画显示【范本模板】

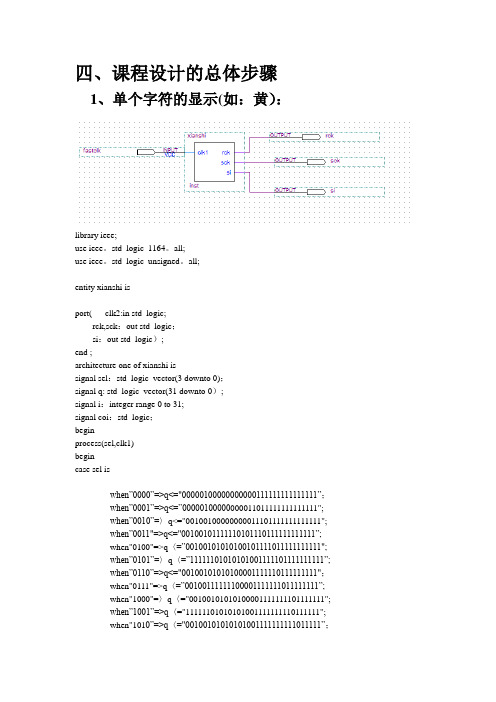

四、课程设计的总体步骤1、单个字符的显示(如:黄):library ieee;use ieee。

std_logic_1164。

all;use ieee。

std_logic_unsigned。

all;entity xianshi isport( clk2:in std_logic;rck,sck:out std_logic;si:out std_logic);end ;architecture one of xianshi issignal sel:std_logic_vector(3 downto 0);signal q: std_logic_vector(31 downto 0);signal i:integer range 0 to 31;signal coi:std_logic;beginprocess(sel,clk1)begincase sel iswhen”0000”=>q<="00000100000000000111111111111111”;when”0001”=>q<=”00000100000000011011111111111111";when”0010”=〉q<="00100100000000011101111111111111";when”0011"=>q<="00100101111110101110111111111111”;when"0100"=>q〈=”00100101010100101111011111111111";when”0101”=〉q〈=”11111101010101001111101111111111”;when”0110”=>q<="00100101010100001111110111111111";when"0111"=>q〈=”00100111111100001111111011111111”;when"1000"=〉q〈="00100101010100001111111101111111";when”1001”=>q〈="11111101010101001111111110111111";when"1010”=>q〈="00100101010101001111111111011111”;when”1011"=>q〈="01100111111100101111111111101111”;when"1100”=〉q<=”00100100100000101111111111110111";when"1101"=>q<=”00001100000000011111111111111011";when”1110"=>q〈=”00000100000000001111111111111101”;when”1111”=〉q<="00000000000000001111111111111110”;when others =〉null;end case;if clk1'event and clk1=’1’thensi<=q(i);i<=i+1;coi<=’0’;if i=31 then i〈=0;coi<='1';sel<=sel+'1';end if;rck<=not coi;end if;end process;sck〈=clk1;end ;时序仿真:从图中可以看出,当clk1在第32个上升沿rck变为低电频,sck与clk1是同一电频,故此程序满足要求。

EDA课程设计16X16点阵程序

《EDA技术与应用》课程设计报告题目:LED点阵显示屏控制系统设计院(系):专业班级:学生姓名:学号:指导教师:2017年6月 19日至2017年 6 月23 日《EDA技术及应用》课程设计任务书摘要主要研究基于VHDL的LED点阵汉字滚动显示。

首先描述了基于现场可编程门阵(FPGA)的硬件电路,以及点阵显示汉字的原理;然后在单个16x16LED发光二极管点阵上滚动显示汉字的原理;最后给出了描述其功能的VHDL语言程序设计方法。

通过编程、调试、仿真、下载正确的实现了汉字的滚动显示扫描结果,其硬件系统的实验验证也获得了与软件仿真结论吻合的结果。

关键词:LED点阵;FPGA;VHDL语言;汉字滚动显示。

目录1.实验要求及总体方案............................................................ 错误!未定义书签。

1.1 实验要求....................................................................... 错误!未定义书签。

1.2 扫描显示....................................................................... 错误!未定义书签。

1.3 滚动显示....................................................................... 错误!未定义书签。

2.LED点阵显示原理............................................................... 错误!未定义书签。

2.1 LED点阵原理............................................................... 错误!未定义书签。

16×16点阵显示设计

课程设计课程名称嵌入式系统课程设计课题名称16X16的点阵显示设计专业班级学号姓名指导老师2016年12月20日电气信息学院课程设计任务书课题名称16×16的点阵显示设计姓名专业班级学号指导老师课程设计时间2016年12月18日-2016年12月30日〔17、18周〕教研室意见意见:同意审核人:X望军一、任务与要求CPLD为复杂可编程逻辑器件,通过EDA技术对其进行编程,可将一个较复杂的数字系统集成于一个芯片中,制成专用集成电路芯片,并可随时在系统修改其逻辑功能.并最终完成电路的编程调试.具体要求如下:用一个16×16的点阵使用逐列循环扫描的方式不间断的显示你##的全部大写拼音字母.二、进度安排第一周:周一:集中布置课程设计相关事宜.周二~周三:子模块程序设计,顶层电路程序设计.周四~周日:子模块,顶层电路仿真.第二周:周一~周三:编程下载,系统调试.周四~周五:设计报告撰写.周五进行答辩和设计结果检查.三、参考资料1. X 原编著,可编程逻辑器件设计与应用,机械工业.2.荀殿栋,徐志军编著,数字电路设计实用手册,电子工业.3. X洪喜,陆颖编著. VHDL电路设计实用教程清华大学.目录1.总体设计思路与功能设计11.1.基本原理11.2.总体设计框图21.3.顶层文件设计22.单元电路设计32.1列循环扫描模块3.2.2字符样式设计模块32.3循环扫描与延时模块42.4整个程序53.系统调试与仿真93.1 开发环境介绍93.2.1 创建工程93.2.2 编译前设计93.2.3 全程编译113.2.4时序仿真124.下载调试135.心得体会146.参考文献14一、总体设计思路1.1基本原理LED 就是Light Emitting Diode〔发光二极管〕的缩写.在某些半导体材料的PN结中,注入的少数载流子与多数载流子复合时会把多余的能量以光的形式释放出来,从而把电能直接转换为光能.PN结加反向电压,少数载流子难以注入,故不发光.这种利用注入式电致发光原理制作的二极管叫发光二极管,通称LED.LED显示屏是一种通过控制半导体发光二极管的显示方式,用来显示文字、图形、图像、动画、行情、视频、录像信号等各种信息的显示屏幕.16×16扫描LED点阵的工作原理同8位扫描数码管类似.它有16个共阴极输出端口,每个共阴极对应有16个LED显示灯,所以其扫描译码地址需4位信号线〔SEL0-SEL3〕,其汉字扫描码由16位段地址〔0-15〕输入. 通过时钟的每列扫描显示完整汉字.点阵LED一般采用扫描式显示,实际运用分为三种方式:〔1〕点扫描〔2〕行扫描〔3〕列扫描若使用第一种方式,其扫描频率必须大于16×64=1024Hz,周期小于1ms即可.若使用第二和第三种方式,则频率必须大于16×8=128Hz,周期小于7.8ms即可符合视觉暂留要求.此外一次驱动一列或一行〔8颗LED〕时需外加驱动电路提高电流,否则LED亮度会不足.实验箱上为我们提供了16*16的点阵显示模块.通过观察,我们可以看到,此点阵显示屏即为16行、16列的LED显示灯.那么控制这些灯的亮暗分布,就能达到字符显示的目的.首先输出预定义"吕、苏、田、口〞四个汉字,显示屏上的灯的亮暗情况具体应如何.如第一个汉字吕:00000000000000000000000000000000000000000111110000000000010001000000000001111100000000000000000000000000000000000000000000000000如果高电平‘1’时表示灯是亮的,低电平‘0’时灯是暗的,这样上面的灯呈现在我们眼前的就是吕字了.依次类推,我们就可以设计出所有要显示的汉字了.这样这些汉字就好象是被我们当作了固定模型了.但如何点亮这些灯呢,这就要求有一个脉冲循环扫描的电路,我们采用列扫描,当扫描的和我们先设计好的汉字模型的高电平相匹配时,灯就相应的点亮.由于扫描的速度很快,我们人的眼睛并不会感到灯的闪烁,所以每扫描完16列就会显示在我们眼中一个汉字了.但要所有的汉字就可以依次的显示出来并不停的循环显示,就还要再有一个时序控制电路来控制.此时序控制电路象一个计数器,有自动清零的功能,这样就可以实现循环的效果了.1.2设计框图图1.2 总体设计框图1.3顶层文件设计图1.3顶层文件设计 时序控制 扫描控制显示控制 译码输出二、单元电路设计2.1列循环扫描通过对每一列的扫描来完成对字母的现实,只要扫描的频率足够快,就能给人以连续的感觉.因此要控制扫描的频率,不能太低,否则,就会造成视觉上的不连续,输入一个时钟信号,输出为4位二进制〔用sel表示〕列选信号,用来选中列,进行扫描,扫描程序如下:Library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;Entity dz_xs isPort<enable,clk:in std_logic; --端口定义输入信号Sel:out std_logic_vector<3 downto 0>>; --端口定义输出信号End dz_xs;Architecture count of dz_xs isSignal lie:std_logic_vector<3 downto 0>;BeginProcess<clk,enable> --脉冲、使能信号beginIf clk'event and clk='1'thenIf enable='1' thenIf lie>"0000" thenLie<=lie-"0001";ElseLie<="1111";End if;End if;End if;Sel<=lie;End process;2.2字符样式设计本环节是建立一个数据库,使之能在扫描的同时读取所需要的信息,从而完成汉字的显示.本次设计"吕、苏、田、口〞汉字样式设计程序如下:Library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;Entity dz_xs isPort<enable,clk:in std_logic; --端口定义输入信号h0,h8:out std_logic_vector<7 downto 0>>; --端口定义输出信号〔h0-列数据输出,h8-代表行数据输出〕End dz_xs;Architecture count of dz_xs isSignal lie:std_logic_vector<3 downto 0>; --信号标志Signal past1:std_logic_vector<1 downto 0>;BeginProcess<enable,clk> --脉冲、使能信号BeginIf clk'event and clk='1'thenIf enable='1' thenCase lie isWhen "00"=>Case lie is --"吕〞字设计When "0011"=>h0<="00000000";h8<="01111110";When "0101"=>h0<="01000010";h8<="01000010"; When "0110"=>h0<="01000010";h8<="01000010"; When "0111"=>h0<="01000010";h8<="01000010"; When "1000"=>h0<="01000010";h8<="01000010"; When "1001"=>h0<="01000010";h8<="01000010"; When "1010"=>h0<="01000010";h8<="01000010"; When "1011"=>h0<="01000010";h8<="01000010"; When "1100"=>h0<="01111110";h8<="01000010"; When "1101"=>h0<="00000000";h8<="01111110"; When others=>h0<="00000000";h8<="00000000"; End case;When "01"=>Case lie is --"苏〞字设计When "0011"=>h0<="00100000";h8<="00000000"; When "0100"=>h0<="00100000";h8<="00000000"; When "0101"=>h0<="00100000";h8<="10001100"; When "0110"=>h0<="01110000";h8<="10000000"; When "0111"=>h0<="00101000";h8<="10000000"; When "1000"=>h0<="00100011";h8<="11111100"; When "1001"=>h0<="00100000";h8<="10000000"; When "1010"=>h0<="00101000";h8<="10001100"; When "1011"=>h0<="01110000";h8<="10000110"; When "1100"=>h0<="00100000";h8<="11111110"; When "1101"=>h0<="00100000";h8<="00001100";End case;When "10"=>Case lie is --"田〞字设计When"0100"=>h0<="00011111";h8<="11110000"; When"0101"=>h0<="00010001";h8<="00010000"; When"0110"=>h0<="00010001";h8<="00010000"; When"0111"=>h0<="00010001";h8<="00010000"; When"1000"=>h0<="00011111";h8<="11110000"; When"1001"=>h0<="00010001";h8<="00010000"; When"1010"=>h0<="00010001";h8<="00010000"; When"1011"=>h0<="00010001";h8<="00010000"; When"1100"=>h0<="00011111";h8<="11110000"; When others=>h0<="00000000";h8<="00000000"; End case;When "11"=>Case lie is --"口〞字设计When"0101"=>h0<="00011111";h8<="11100000"; When"0110"=>h0<="00010000";h8<="00100000"; When"0111"=>h0<="00010000";h8<="00100000"; When"1000"=>h0<="00010000";h8<="00100000"; When"1001"=>h0<="00010000";h8<="00100000"; When"1010"=>h0<="00010000";h8<="00100000"; When"1011"=>h0<="00011111";h8<="11100000"; When others=>h0<="00000000";h8<="00000000";End case;End if;End if;End process;2.3循环扫描与期间的延时环节为使汉字不断地循环显示,并且使每个汉字之间有停顿,就需要在中间加一定的延时和循环环节.在这一环节中,可以通过修改其数值来控制每个字母的显示时间,其程序如下:process<clk>variable int: integer range 0 to 10000;beginif clk’event and clk=’1’thenif int<10000 thenint:=int+1;elseint:=0;if next1=〞11〞thennext1<=〞00〞;elsenext1<= next1+’1’;end if;end if;end if;end process;2.4总程序library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;entity yz_ok isport<enable,clk:in std_logic;sel:out std_logic_vector<3 downto 0>; h0,h8:out std_logic_vector<7 downto 0>>;end yz_ok;architecture count of yz_ok issignal lie:std_logic_vector<3 downto 0>;signal next1: std_logic_vector<1 downto 0>;begina1:process<clk,enable>beginIf clk'event and clk='1'thenIf enable='1' thenIf lie>"0000" thenLie<=lie-"0001";ElseLie<="1111";End if;End if;End if;Sel<=lie;End process;a2:process<enable,clk>beginIf clk'event and clk='1'thenIf enable='1' thenCase next1 isWhen "00"=>Case lie isWhen "0011"=>h0<="00000000";h8<="01111110"; When "0100"=>h0<="01111110";h8<="01000010"; When "0101"=>h0<="01000010";h8<="01000010"; When "0110"=>h0<="01000010";h8<="01000010"; When "0111"=>h0<="01000010";h8<="01000010"; When "1000"=>h0<="01000010";h8<="01000010"; When "1001"=>h0<="01000010";h8<="01000010"; When "1010"=>h0<="01000010";h8<="01000010"; When "1011"=>h0<="01000010";h8<="01000010"; When "1100"=>h0<="01111110";h8<="01000010"; When "1101"=>h0<="00000000";h8<="01111110"; When others=>h0<="00000000";h8<="00000000"; End case;When "01"=>Case lie isWhen "0011"=>h0<="00100000";h8<="00000000"; When "0100"=>h0<="00100000";h8<="00000000"; When "0101"=>h0<="00100000";h8<="10001100";When "0111"=>h0<="00101000";h8<="10000000"; When "1000"=>h0<="00100011";h8<="11111100"; When "1001"=>h0<="00100000";h8<="10000000"; When "1010"=>h0<="00101000";h8<="10001100"; When "1011"=>h0<="01110000";h8<="10000110"; When "1100"=>h0<="00100000";h8<="11111110"; When "1101"=>h0<="00100000";h8<="00001100"; When others=>h0<="00000000";h8<="00000000"; End case;When "10"=>Case lie isWhen"0100"=>h0<="00011111";h8<="11110000"; When"0101"=>h0<="00010001";h8<="00010000"; When"0110"=>h0<="00010001";h8<="00010000"; When"0111"=>h0<="00010001";h8<="00010000"; When"1000"=>h0<="00011111";h8<="11110000"; When"1001"=>h0<="00010001";h8<="00010000"; When"1010"=>h0<="00010001";h8<="00010000"; When"1011"=>h0<="00010001";h8<="00010000"; When"1100"=>h0<="00011111";h8<="11110000"; When others=>h0<="00000000";h8<="00000000";End case;When "11"=>Case lie isWhen"0110"=>h0<="00010000";h8<="00100000"; When"0111"=>h0<="00010000";h8<="00100000"; When"1000"=>h0<="00010000";h8<="00100000"; When"1001"=>h0<="00010000";h8<="00100000"; When"1010"=>h0<="00010000";h8<="00100000"; When"1011"=>h0<="00011111";h8<="11100000"; When others=>h0<="00000000";h8<="00000000";End case;When others=>h0<="00000000";h8<="00000000";End case;End if;End if;End process;a3:process<clk>variable int: integer range 0 to 10000;beginif clk'event and clk='1'thenif int<10000 thenint:=int+1;elseint:=0;if next1="11"thennext1<="00";elsenext1<= next1+'1';end if;end if;end if;end process;end count;第三章系统调试与仿真3.1开发环境介绍Quartus II 是Altera公司的综合性PLD开发软件,支持原理图、VHDL、Veril-ogHDL 以与AHDL〔Altera Hardware Description Language〕等多种设计输入形式,内嵌自有的综合器以与仿真器,可以完成从设计输入到硬件配置的完整PLD设计流程.Quartus II支持Altera的IP核,包含了LPM/MegaFunction宏功能模块库,使用户可以充分利用成熟的模块,简化了设计的复杂性、加快了设计速度.对第三方EDA工具的良好支持也使用户可以在设计流程的各个阶段使用熟悉的第三方EDA 工具.此外,Quartus II 通过和DSP Builder工具与Matlab/Simulink相结合,可以方便地实现各种DSP应用系统;支持Altera的片上可编程系统〔SOPC〕开发,集系统级设计、嵌入式软件开发、可编程逻辑设计于一体,是一种综合性的开发平台.3.2调试与仿真3.2.1 创建工程在Quartus II 中新建一个VHDL File文件,将VHDL代码输入这个文件,并保存到工作目录,名为yz_ok.vhd.利用new preject wizard 工具创建一个工程,工程名为yz_ok,顶层文件实体名为yz_ok,并将上面创建的yz_ok.vhd文件加入到工程中.3.2.2 编译前设置〔1〕选择目标芯片.用assignmemts- settings命令,弹出settings对话框,选择目标芯片为EP1C3T144C8.图3-1 选择目标器件〔2〕选择工作方式,编程方式,与闲置引脚状态单击上图中的device&pin options按钮,弹出device&pin options窗口. 在General项中选中auto-restart configuration after error,使对FPGA的配置失败后能自动重新配置,并加入JTAG用户编码.图3-2 选择配置器件工作方式在configuration项中,其下方的Generate compressed bitstreams处打勾,这样就能产生用于EPCS的POF压缩配置文件.在Configuration 选项页,选择配置器件为EPCS1,其配置模式选择为active serial.图3-3选择编程方式在Unused pins项,将目标器件闲置引脚状态设置高阻态,即选择As input,tri-stated.图3-4 设置闲置引脚状态3.2.3 全程编译设置好前面的内容之后,就可以进行编译了.选择Processing菜单中start compilation,在窗口的下方processing栏中显示编译信息.图3-5 全程编译成功完成完成后在工程管理窗口左是角显示了工程yz_ok 的层次结构和其中结构模块耗用的逻辑宏单元数.此栏的右边是编译处理流程,包括数据网表建立、逻辑综合、适配、配置文件装配和时序分析等.3.2.4时序仿真〔1〕新建一个矢量波形文件,同时打开波形编辑器.设置仿真时间为50us,保存波形文件为yz_ok.vwf.〔2〕将工程yz_ok的端口信号名选入波形编辑器中,所选的端口有clk,enable 与总线h0和h8.设置clk的时钟周期为2us,占空比为50%.图3-6 选择仿真控制仿真器参数设置.选择菜单Assignment中的Settings,在Settings窗口下选择Simulator,在右侧的simulation mode项下选择timing,即选择时序仿真,并选择仿真激励文件名yz_ok.vwf.选择simulation options栏,确认选定simulation coverage reporting; 毛刺检测Glitch detection 为1ns 宽度;选中Run simulation until all vector stimuli 全程仿真.现在所有设置进行完毕,在菜单processing项下选择start simulation,直到出现simulation was successful,仿真结束 .仿真文件simulation report 通常会自动弹出,否则选择processing simulation report .图3-7 仿真波形输出四、下载调试选择tools菜单中programmer,点击左上角的Hardware Setup,选择USB,点击start即可连接硬件,进行调试 .连接成功后,即可在实验箱中LED屏循环显示字母.如下图汉字的显示:图4-1调试结果图图4-2调试结果图五、心得体会为期两周的嵌入式课程设计完成了.整过设计过程虽然不是很顺利.不过我认真对待老师给我们的课题,中间虽然也有不少挫折,但不经历挫折怎么见风雨,在我四处查看资料,请教同学下终于完成.经过这两周的课程设计,我加深了对PLD的认识,学到了很多以前不知道的东西,也明白也PLD在现实生活中的重要应用和它的发展趋势.以前在书本上学到的东西总是不能够很好地运用到现实当中去,现在终于得到了改善,这让我感到非常的高兴.从这次实习中,我体会到,如果将我们在大学里所学的知识与更多的实践结合在一起,用实践来检验真理,使一个本科生具备较强的处理基本实务的能力与比较系统的专业知识,这才是我们学习与实习的真正目的.让我们不再是一个沉睡的孩子,让我们的无知渐渐远去,把我们所学的知识运用到实际中去,为社会出上我们的一份力.感谢老师给的这次让我们自行设计的机会,通过这次设计通过这次课程设计使我懂得了理论与实际相结合是很重要的,只有理论知识是远远不够的,只有把所学的理论知识与实践相结合起来,从理论中得出结论,才能真正为社会服务,从而提高自己的实际动手能力和独立思考的能力.在设计的过程中遇到问题,可以说得是困难重重,这毕竟第一次做的,难免会遇到过各种各样的问题,同时在设计的过程中发现了自己的不足之处,对以前所学过的知识理解得不够深刻,掌握得不够牢固.总的来说,这次设计的16×16点阵显示控制还是比较成功的,在设计中遇到了很多问题,最后在老师的辛勤的指导下,终于游逆而解,有点小小的成就感,终于觉得平时所学的知识有了实用的价值,达到了理论与实际相结合的目的,不仅学到了不少知识,而且锻炼了自己的能力,使自己对以后的路有了更加清楚的认识,同时,对未来有了更多的信心.最后,对给过我帮助的所有同学和指导老师再次表示忠心的感谢.六、参考文献1. X原编著,可编程逻辑器件设计与应用,机械工业.2.荀殿栋,徐志军编著,数字电路设计实用手册,电子工业.3. X洪喜,陆颖编著. VHDL电路设计实用教程,清华大学.电气信息学院课程设计评分标准。

16X16点阵显示设计

实验报告课程名称EDA技术使用教程实验名称16*16点阵显示综合实验实验类型验证(验证、综合、设计、创新)学院名称专业年级班级开出学期实验四、16*16点阵显示综合实验一、实验要求设计一个共阴16X16点阵控制接口,要求:在时钟信号的控制下,使点阵动态点亮,点亮方式为使点阵显示器显示自己的名字,其中列选信号为16-4编码器编码输出。

二、实验目的1、了解点阵字符的产生和显示原理。

2、了解E2PROM和16×16点阵LED的工作机理。

3、加强对于总线产生,地址定位的CPLD实现的理解。

三、硬件要求1.主芯片。

2.可变时钟源。

3.带有事先编程好字库/字符的E2PROM 2864。

4.16×16扫描LED点阵。

四、实验原理16×16扫描LED点阵的工作原理同8位扫描数码管类似。

它有16个共阴极输出端口,每个共阴极对应有16个LED显示灯。

所以其扫描译码地址需4位信号线。

要使16点阵上某个点亮,如第10行第4列的LED点亮,只要让列选信号为“0100”,从而选中第4列,再给第10行一个高电平,即可点亮该LED。

本实验通过FPGA芯片写入字形,产生扫描信号。

为了显示整个汉字,首先分布好汉字的排列,以行给汉字信息;然后以大于24HZ的频率扫描列,即每行逐一加高电平,根据人眼的视觉残留特性,使之形成整个汉字的显示。

五、VHDL语言程序代码library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;entity dots_test isport ( clk:in std_logic;dotout:out std_logic_vector(15 downto 0);selout:out std_logic_vector(3 downto 0);M :out std_logic_vector(3 downto 0));end dots_test;architecture a of dots_test issignal sel_tmp:std_logic_vector(3 downto 0);signal dot_tmp:std_logic_vector(15 downto 0);type dot_type is array (0 to 15) of std_logic_vector(15 downto 0);--定义16个长度为16位的数组,用来存放每一行的显示值signal dotout_tmp:dot_type;constant dotout_tmp1:dot_type:= --陶(x"0100",x"7904",x"49FE",x"5204",x"5524",x"61F4",x"5524",x"4854",x"4FFC",x"4844",x"6954",x"5154",x"41F4",x"4004",x"4014",x"4008");constant dotout_tmp2:dot_type:= --军(x"0000",x"7FFE",x"4202",x"8214",x"3FF8",x"0400",x"0900",x"1110",x"3FF8",x"0100",x"0104",x"FFFE",x"0100",x"0100",x"0100",x"0100");constant dotout_tmp3:dot_type:= --喜(x"0108",x"7FFC",x"0100",x"3FF8",x"0000",x"1FF0",x"1010",x"1FF0",x"0444",x"FFFE",x"0010",x"1FF8",x"1010",x"1010",x"1FF0",x"1010");signal scan_sel:std_logic_vector(3 downto 0);signal clk_value:std_logic_vector(2 downto 0):=(others => '1');constant clk_value_store:std_logic_vector(2 downto 0):=(others => '1');signal key_tmp:std_logic_vector(3 downto 0);beginM <= "0110"; --功能选择位选择16x16点阵功能connection:blockbegindotout <= dotout_tmp(conv_integer(scan_sel));selout <= scan_sel;end block connection;scan_display:block --扫描显示及时钟分频beginclock_divisor:process(clk)beginif rising_edge(clk) thenif (clk_value = clk_value_store) thenscan_sel <= scan_sel + 1;end if;clk_value <= clk_value + 1;end if;end process clock_divisor;end block scan_display;Free_Counter : Block -- 计数器-- 产生扫描信号Signal Q : STD_LOGIC_VECTOR(40 DOWNTO 0);Signal S : STD_LOGIC_VECTOR(2 DOWNTO 0); Begint1: PROCESS (clk) -- 计数器计数BeginIF clk'Event AND clk='1' thenQ <= Q+1;END IF;S <= Q(28 DOWNTO 26);if ( s=0) thenfor i in 0 to 15 loopdotout_tmp(i) <= dotout_tmp1(i);end loop;elsif ( s=1) thenfor i in 0 to 15 loopdotout_tmp(i) <= dotout_tmp2(i);end loop;elsif ( s=2) thenfor i in 0 to 15 loopdotout_tmp(i) <= dotout_tmp3(i);end loop;end if;END PROCESS t1;End Block Free_Counter;end a;六、实验结果七、结论和总结通过这次对16*16点阵字符发生器的设计与实践,让我加深了对VHDL语言的了解。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

北华航天工业学院《EDA技术综合设计》课程设计报告报告题目:16X16点阵显示综合实验作者所在系部:电子工程系作者所在专业:自动化作者所在班级:B08221作者姓名:王建超指导教师姓名:崔瑞雪完成时间:2010-11-30内容摘要EDA技术是现代电子信息工程领域的一门新兴技术,它是在现代先进的计算机工作平台上开发出来的一整套电子系统设计的软硬件工具,并提供了先进的电子系统设计方法。

随着EDA技术的不断发展,开发人员完全可以通过自己的电子系统设计来定制其芯片内部的的电路功能,使之成为设计者自己的专门集成电路芯片。

在本次课设中,设计一个共阴16X16点阵控制接口,要求:在时钟信号的控制下,使点阵动态点亮,点亮方式为使点阵显示器显示“沈小兰王建超袁利宏”九个字和一种花样,其中列选信号为16-4编码器编码输出。

列选信号采用与7段数码管的位选信号一样的处理方法,即列扫描信号频率大于24HZ。

字体、格式,注意本次为课设报告、不是实验报告关键词:EDA、可编程逻辑器件、时钟信号、16*16点阵字符发生器目录一、设计要求 (1)二、实验目的 (1)三、硬件要求 (1)四、实验原理 (1)五、程序设计 (2)16进制计数器 (2)16*16点阵的行列驱动器 (2)六、原理图 (12)七、仿真波形 (12)八、实验总结 (13)参考文献 (13)课程设计任务书一、实验要求设计一个共阴16X16点阵控制接口,要求:在时钟信号的控制下,使点阵动态点亮,点亮方式为使点阵显示器显示“沈小兰王建超袁利宏”九个字和一种花样,其中列选信号为16-4编码器编码输出。

二、实验目的1、了解点阵字符的产生和显示原理。

2、了解E2PROM和16×16点阵LED的工作机理。

3、加强对于总线产生,地址定位的CPLD实现的理解。

三、硬件要求1.主芯片EPF10K10LC84-4。

2.可变时钟源。

3.带有事先编程好字库/字符的E2PROM 2864。

4.16×16扫描LED点阵。

四、实验原理16×16扫描LED点阵的工作原理同8位扫描数码管类似。

它有16个共阴极输出端口,每个共阴极对应有16个LED显示灯。

所以其扫描译码地址需4位信号线。

要使16点阵上某个点亮,如第10行第4列的LED点亮,只要让列选信号为“0100”,从而选中第4列,再给第10行一个高电平,即可点亮该LED。

本实验通过FPGA芯片写入字形,产生扫描信号。

为了显示整个汉字,首先分布好汉字的排列,以行给汉字信息;然后以大于24HZ的频率扫描列,即每行逐一加高电平,根据人眼的视觉残留特性,使之形成整个汉字的显示。

由于要显示不同的字,需要给一个信DIN,对不同字不同花样进行选择。

而该信号的产生可以通过一个16进制计数器完成。

本设计由16进制计数器,行驱动和列驱动组成。

输出包括了如下图所示的列选信号SEL0—SEL3。

五、程序设计1.16进制计数器:LIBRARY ieee;USE ieee.std_logic_1164.all;USE ieee.std_logic_unsigned.all;ENTITY JISHU ISPORT(CLK,RST,LOAD:IN STD_LOGIC;DIN:IN STD_LOGIC_VECTOR(3 DOWNTO 0);DOUT:BUFFER STD_LOGIC_VECTOR(3 DOWNTO 0));END JISHU;ARCHITECTURE SHILIU OF JISHU ISBEGINPROCESS(CLK,RST,LOAD,DIN)BEGINIF (CLK'EVENT AND CLK='1') THENIF(RST='1')THEN DOUT<=(OTHERS=>'0');ELSIF (LOAD='1') THEN DOUT<=DIN;ELSIF (DOUT=15) THENDOUT<="0000";ELSEDOUT<=DOUT+1;END IF;END IF;END PROCESS;END SHILIU;2.16*16点阵的行列驱动器library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;entity zhi isport( din : in std_logic_vector(3 downto 0);selout : buffer std_logic_vector(3 downto 0);clk,rst: in std_logic;dotout : out std_logic_vector(15 downto 0));end zhi;architecture one of zhi isbeginprocess(clk,rst,din,selout)variable b:std_logic_vector(15 downto 0);beginif rst='1'then selout<="0000";elsif clk'event and clk='1' thencase din iswhen "0000"=>selout<=selout+1;case selout iswhen "1111" =>b:="0000000000000000";when "0000" =>b:="0010001000011100";when "0001" =>b:="0001000100001000";when "0010" =>b:="0000100010010000";when "0011" =>b:="0000000000100010";when "0100" =>b:="0011100001000100";when "0101" =>b:="0001000000001000";when "0110" =>b:="0001000000010000";when "0111" =>b:="0111111111100000";when "1000" =>b:="0111111111111100";when "1001" =>b:="0001000000000100";when "1010" =>b:="0001010000000100";when "1011" =>b:="0001100000000100";when "1100" =>b:="0011000000000100";when "1101" =>b:="0000000000011100";when others =>b:="0000000000000000";end case;when"0001"=>selout<=selout+1;case selout iswhen "1111" =>b:="0000000000000000";when "0000" =>b:="0000000000000000";when "0001" =>b:="0000000110000000";when "0010" =>b:="0000001100000000";when "0011" =>b:="0000011000000000";when "0101" =>b:="0000000000001000";when "0110" =>b:="0111111111111100";when "0111" =>b:="0111111111111110";when "1000" =>b:="0000000000000000";when "1001" =>b:="0000110000000000";when "1010" =>b:="0000011000000000";when "1011" =>b:="0000001100000000";when "1100" =>b:="0000000110000000";when "1101" =>b:="0000000000000000";when others =>b:="0000000000000000";end case;when"0010"=> selout<=selout+1;case selout iswhen "1111" =>b:="0000000000000000";when "0000" =>b:="0000000000000110";when "0001" =>b:="0001100000000110";when "0010" =>b:="1001100000000110";when "0011" =>b:="1101100110000110";when "0100" =>b:="0111100110000110";when "0101" =>b:="0011100110000110";when "0110" =>b:="0001100110000110";when "0111" =>b:="0001100110000110";when "1000" =>b:="0011100110000110";when "1001" =>b:="0111100110000110";when "1010" =>b:="1101100110000110";when "1011" =>b:="1001100000000110";when "1100" =>b:="0001100000000110";when "1101" =>b:="0000000000000110";when others =>b:="0000000000000000";end case;when "0011"=> selout<=selout+1;case selout iswhen "0000" =>b:="0000000000000100";when "0001" =>b:="0000000000001100";when "0010" =>b:="0001000000011100";when "0011" =>b:="0101011011110000";when "0100" =>b:="0101011101100000";when "0101" =>b:="0101010110000000";when "0110" =>b:="1111010111111111";when "0111" =>b:="0101010111111110";when "1000" =>b:="0101010101100100";when "1001" =>b:="0101011000110000";when "1010" =>b:="0001000000011000";when "1011" =>b:="0000000000001100";when "1100" =>b:="0000000000000100";when "1101" =>b:="0000000000000000";when others =>b:="0000000000000000";end case;when"0100"=> selout<=selout+1;case selout iswhen "0000" =>b:="0000000000011000";when "0001" =>b:="0000011000110000";when "0010" =>b:="0110011011000000";when "0011" =>b:="0111111111111100";when "0100" =>b:="0111111111111110";when "0101" =>b:="0110011110000000";when "0110" =>b:="0000011011100000";when "0111" =>b:="0000000001100000";when "1000" =>b:="0000000000000000";when "1001" =>b:="0000011111110000";when "1010" =>b:="0000011111100000";when "1011" =>b:="0000000000001000";when "1100" =>b:="0111111111111100";when "1101" =>b:="0111111111111110";when "1110" =>b:="0000000000000000";when others =>b:="0000000000000000";end case;when"0101"=> selout<=selout+1;case selout iswhen "0000" =>b:="0000000000000000";when "0001" =>b:="0000111000000010";when "0010" =>b:="0000111000000110";when "0011" =>b:="0000100110001000";when "0100" =>b:="0000100110010110";when "0101" =>b:="0000100110101110";when "0110" =>b:="0110100111010110";when "0111" =>b:="0110101110100110";when "1000" =>b:="0110100110000110";when "1001" =>b:="0000100110010110";when "1010" =>b:="0000100110001110";when "1011" =>b:="0000100110000110";when "1100" =>b:="0000111000000110";when "1101" =>b:="0000111000000010";when "1110" =>b:="0000000000000000";when others =>b:="0000000000000000";end case;when"0110"=> selout<=selout+1;case selout iswhen "1111" =>b:="0000000000000000";when "0000" =>b:="0000000000000010";when "0001" =>b:="0110000000000110";when "0010" =>b:="0110000110000110";when "0011" =>b:="0110000110000110";when "0100" =>b:="0110000110000110";when "0101" =>b:="0110000110000110";when "0110" =>b:="0111111111111110";when "0111" =>b:="0111111111111110";when "1000" =>b:="0110000110000110";when "1001" =>b:="0110000110000110";when "1011" =>b:="0110000110000110";when "1100" =>b:="0110000000000110";when "1101" =>b:="0000000000000010";when others =>b:="0000000000000000";end case;when "0111"=> selout<=selout+1;case selout iswhen "0000" =>b:="0000000000100100";when "0001" =>b:="0010001000011000";when "0010" =>b:="0010010100011000";when "0011" =>b:="0010110010100100";when "0100" =>b:="0011000001001010";when "0101" =>b:="0010010010101010";when "0110" =>b:="0010010010101010";when "0111" =>b:="0010010010101010";when "1000" =>b:="0111111111111110";when "1001" =>b:="0010010010101010";when "1010" =>b:="0010010010101010";when "1011" =>b:="0010010010101010";when "1100" =>b:="0011111110001010";when "1101" =>b:="0000010000001010";when "1110" =>b:="0000010000000010";when others =>b:="0000000000000000";end case;when"1000"=> selout<=selout+1;case selout iswhen "0000" =>b:="0000000001111100";when "0001" =>b:="0000100011000000";when "0010" =>b:="0010100100100000";when "0011" =>b:="0010101000010000";when "0100" =>b:="0111111111001000";when "0101" =>b:="0010100100000100";when "0110" =>b:="0010100100000010";when "0111" =>b:="0000100000000010";when "1001" =>b:="0100010001110010";when "1010" =>b:="0100100010001010";when "1011" =>b:="0101000010001010";when "1100" =>b:="0110010010001010";when "1101" =>b:="0111111001110010";when "1110" =>b:="0000000000000000";when others =>b:="0000000000000000";end case;when"1001"=>selout<=selout+1;case selout iswhen "1111" =>b:="0000111100001111";when "0000" =>b:="0000111100001111";when "0001" =>b:="0000111100001111";when "0010" =>b:="0000111100001111";when "0011" =>b:="1111000011110000";when "0100" =>b:="1111000011110000";when "0101" =>b:="1111000011110000";when "0110" =>b:="1111111111110000";when "0111" =>b:="0000111100001111";when "1000" =>b:="0000111100001111";when "1001" =>b:="0000111100001111";when "1010" =>b:="0000111100001111";when "1011" =>b:="1111000011110000";when "1100" =>b:="1111000011110000";when "1101" =>b:="1111000011110000";when "1110" =>b:="1111000011110000";when others =>null;end case;when"1010"=>selout<=selout+1;case selout iswhen "1111" =>b:="1111000011110000";when "0000" =>b:="1111000011110000";when "0001" =>b:="1111000011110000";when "0010" =>b:="1111000011110000";when "0100" =>b:="0000111100001111";when "0101" =>b:="0000111100001111";when "0110" =>b:="0000111100001111";when "0111" =>b:="1111000011110000";when "1000" =>b:="1111000011110000";when "1001" =>b:="1111000011110000";when "1010" =>b:="1111000011110000";when "1011" =>b:="0000111100001111";when "1100" =>b:="0000111100001111";when "1101" =>b:="0000111100001111";when "1110" =>b:="0000111100001111";when others =>null;end case;when"1011"=>selout<=selout+1;case selout iswhen "1111" =>b:="0000000011111111";when "0000" =>b:="0000000011111111";when "0001" =>b:="0000000011111111";when "0010" =>b:="0000000011111111";when "0011" =>b:="0000000011111111";when "0100" =>b:="0000000011111111";when "0101" =>b:="0000000011111111";when "0110" =>b:="0000000011111111";when "0111" =>b:="1111111100000000";when "1000" =>b:="1111111100000000";when "1001" =>b:="1111111100000000";when "1010" =>b:="1111111100000000";when "1011" =>b:="1111111100000000";when "1100" =>b:="1111111100000000";when "1101" =>b:="1111111100000000";when "1110" =>b:="1111111100000000";when others =>null;end case;when"1100"=> selout<=selout+1;case selout iswhen "1111" =>b:="1111111100000001";when "0000" =>b:="0111111100000011";when "0001" =>b:="0011111100000111";when "0010" =>b:="0001111100001111";when "0011" =>b:="0000111100011111";when "0100" =>b:="0000011100111111";when "0101" =>b:="0000001101111111";when "0110" =>b:="0000000111111111";when "0111" =>b:="1111111110000000";when "1000" =>b:="1111111011000000";when "1001" =>b:="1111110011100000";when "1010" =>b:="1111100011110000";when "1011" =>b:="1111000011111000";when "1100" =>b:="1110000011111100";when "1101" =>b:="1100000011111110";when "1110" =>b:="1000000011111111";when others =>null;end case;when"1101"=> selout<=selout+1;case selout iswhen "1111" =>b:="1111111111111111";when "0000" =>b:="1111111111111111";when "0001" =>b:="1111110011111111";when "0010" =>b:="1111000011111111";when "0011" =>b:="1110000011111111";when "0100" =>b:="1111100011111111";when "0101" =>b:="1111110011001111";when "0110" =>b:="1111111001000111";when "0111" =>b:="1100000000000011";when "1000" =>b:="1110001100111111";when "1001" =>b:="1110011100011111";when "1010" =>b:="1111111100000111";when "1011" =>b:="1111111100001111";when "1101" =>b:="1111111111111111";when "1110" =>b:="1111111111111111";when others =>null;end case;when"1110"=> selout<=selout+1;case selout iswhen "1111" =>b:="1111111111111111";when "0000" =>b:="1111111111111111";when "0001" =>b:="1111111111111111";when "0010" =>b:="1111111111111111";when "0011" =>b:="1111000000001111";when "0100" =>b:="1111011100001111";when "0101" =>b:="1111001101101111";when "0110" =>b:="1111000111101111";when "0111" =>b:="1111011110001111";when "1000" =>b:="1111011011001111";when "1001" =>b:="1111000011101111";when "1010" =>b:="1111000000001111";when "1011" =>b:="1111111111111111";when "1100" =>b:="1111111111111111";when "1101" =>b:="1111111111111111";when "1110" =>b:="1111111111111111";when others =>null;end case;when"1111"=> selout<=selout+1;case selout iswhen "1111" =>b:="1111111111111111";when "0000" =>b:="1111111111111111";when "0001" =>b:="1111111111111111";when "0010" =>b:="1111111111111111";when "0011" =>b:="1111111111111111";when "0100" =>b:="1111111111111111";when "0101" =>b:="1111111111111111";when "0110" =>b:="1111111111111111";when "1000" =>b:="1111111111111111";when "1001" =>b:="1111111111111111";when "1010" =>b:="1111111111111111";when "1011" =>b:="1111111111111111";when "1100" =>b:="1111111111111111";when "1101" =>b:="1111111111111111";when "1110" =>b:="1111111111111111";when others =>null;end case;when others=>null;end case;end if;dotout<=b;end process;end one;六、原理图七、仿真波形1. 16进制计数器的仿真波形2.总体仿真波形八、实验总结通过这次对16*16点阵字符发生器的设计与实践,让我加深了对VHDL语言的了解。