DSP课件 第八章 AD转换器

《AD转换及其原理》PPT课件

一.A/D转换的基本概念 二.ADC的主要技术参数 三.A/D转换的一般步骤和基本原理 四.集成A/D转换器及应用

概述

• 计算机能够处理的是数字量信息。然而在现实世界中有很 多信息并不都是数字量的,例如声音、电压、电流、流量、 压力、温度、位移和速度等,它们都是连续变化的物理量。 这些连续变化的物理量称为模拟量。 • 计算机是处理数字量信息的设备,要处理这些模拟量信息 就必须有一个模拟接口,通过这个模拟接口,将模拟量信 息转换成数字量信息,以供计算机运算和处理。 • 然后,再把计算机处理过的数字量信息转换为模拟量信息, 以实现对被控制量的控制。

ADC0809应用

ADC0809与51单片机组成的AD转换电路原理图

二.ADC的主要技术参数

1. 分辨率

• 对于ADC来说,分辨率表示输出数字量变化一个相邻数码 所需要输入模拟电压的变化量。通常定义为满刻度电压与 2n的比值,其中n为ADC的位数。例如具有12位分辨率的 ADC能够分辨出满刻度的1/212(0.0244%)。 • 有时分辨率也用A/D转换器的位数来表示,如ADC0809的分 辨率为8位,AD574的分辨率为12位等。 2. 量化误差 • 量化误差是由于ADC 的有限分辨率引起的误差,这是连续 的模拟信号在整数量化后的固有误差。对于四舍五入的量 化法,量化误差在±1/2 LSB之间。

逐次逼近式A/D转换器

逐次逼近型ADC电路框图

基准电压UREF

实例

8位A/D转换器,输入模拟量uI=6.84V,D/A转换器 基准电压 UREF=10V。

CP 0 1 2 3 4 5 6 7

10 5 21 10 2.5 22 10 1.25 23 10 0.625 24 10 0.3125 25 10 0.15625 26 10 0.078125 27 10 0.0390625 28

《AD及DA转换》课件

《AD及DA转换》PPT课件

本PPT课件将深入介绍AD及DA转换的原理、分类、工作模式,以及采样率、 量化精度等关键概念。我们还会探讨信号处理技术、硬件实现和电路设计等 重要话题。

什么是AD和DA转换

AD(模数)转换将模拟信号转换为数字信号,DA(数模)转换将数字信号转换为模拟信号。这两种转换器 在许多电子系统中起着关键作用。

AD转换器可根据工作原理和特性进行分类,如逐次逼近型、积分型、双斜率 型和ΔΣ型等。每种类型都有其适用的应用场景和性能特点。

DA转换器的分类

DA转换器可以按照数字信号转换为模拟信号的方法进行分类,如加权电阻型、 串行型、并行型和PDM型等。不同类型的转换器适用于不同的应用需求。

AD转换器的工作模式

AD转换的原理和作用

AD转换器使用采样和量化技术将连续的模拟信号转换为离散的数字信号。它 在信号处理、通信系统和传感器中都有广泛应用。

DA转换的原理和作用

DA转换器将数字信号转换为模拟信号,使其能够在模拟电路中进行进一步处 理和传输。它在音频、视频和通信等领域中扮演着核心角色。

AD转换器的分类

AD转换器课件

6)输出逻辑电平 )

多数A/D 转换器的输出逻辑电平与 转换器的输出逻辑电平与TTL 电平兼容。在考虑 电平兼容。 多数 数字量输出与微处理的数据总线接口时, 数字量输出与微处理的数据总线接口时,应注意是否要三态逻 辑输出,是否要对数据进行锁存等。 辑输出,是否要对数据进行锁存等。

7)工作温度范围 )

由于温度会对比较器、运算放大器、电阻网络等产生影响, 由于温度会对比较器、运算放大器、电阻网络等产生影响, 故只在一定的温度范围内才能保证额定精度指标。一般 故只在一定的温度范围内才能保证额定精度指标。一般A/D 转 换器的工作温度范围为( ),军用品的工作温度范围为 换器的工作温度范围为(0~70C),军用品的工作温度范围为 ), (-55~+125C)。 )。

2)逐次逼近型的A/D 转换器 )逐次逼近型的

逐次逼近式的A/D 转换器的主要特点是: 逐次逼近式的 转换器的主要特点是:

转换速度较快, 以内,分辨率可以达18 转换速度较快,在1—100/µs 以内,分辨率可以达 位,特 别适用于工业控制系统。转换时间固定, 别适用于工业控制系统。转换时间固定,不随输入信号的变化 而变化。抗干扰能力相对积分型的差。例如,对模拟输入信号 而变化。抗干扰能力相对积分型的差。例如, 采样过程中,若在采样时刻有一个干扰脉冲迭加在模拟信号上, 采样过程中,若在采样时刻有一个干扰脉冲迭加在模拟信号上, 则采样时,包括干扰信号在内,都被采样和转换为数字量, 则采样时,包括干扰信号在内,都被采样和转换为数字量,这 就会造成较大的误差,所以有必要采取适当的滤波措施。 就会造成较大的误差,所以有必要采取适当的滤波措施。

1)双积分型的A/D 转换器 )双积分型的

由于双积分型A/D 转换是测量输入电压 在T。 转换是测量输入电压Vi 由于双积分型 。 时间内的平均值,所以对常态干扰(串模干扰 串模干扰)有很强 时间内的平均值,所以对常态干扰 串模干扰 有很强 的抑制作用,尤其对正负波形对称的干扰信号, 的抑制作用,尤其对正负波形对称的干扰信号,抑 制效果更好。 制效果更好。 双积分型的A/D 转换器电路简单,抗干扰能力强, 转换器电路简单,抗干扰能力强, 双积分型的 精度高,这是突出的优点。但转换速度比较慢, 精度高,这是突出的优点。但转换速度比较慢,常 用的A/D 转换芯片的转换时间为毫秒级。因此适用于 转换芯片的转换时间为毫秒级。 用的 模拟信号变化缓慢,采样速率要求较低, 模拟信号变化缓慢,采样速率要求较低,而对精度 要求较高,或现场干扰较严重的场合。 要求较高,或现场干扰较严重的场合。例如在数字 电压表中常被采用。 电压表中常被采用。

AD转换模块课件

为了提高能效,需要合理地管理电源,如使用开关电源和动态电压 调节技术。

CHAPTER

04

AD转换模块的接口与编程

硬件接口

模拟信号输入接口

用于连接模拟信号源,如传感器等,将模拟信号传输到AD转换 模块。

数字信号输出接口

将转换后的数字信号输出,通常连接微控制器或其他数字设备。

控制信号接口

逐次逼近型AD转换器

总结词

逐次逼近的方式将输入模拟信号转换为数字输出。

详细描述

逐次逼近型AD转换器采用逐次逼近的方式将输入模拟信号转换为数字输出。它通过不断调整比较器的参考电压 ,逐渐逼近输入模拟信号,最终得到数字输出。逐次逼近型AD转换器具有分辨率高、线性度好、转换速度快等 优点,但功耗较大。

并行比较/串并行型AD转换器

总结词

采用并行比较或串并行方式将输入模拟信号转换为数字输出。

详细描述

并行比较/串并行型AD转换器采用并行比较或串并行方式将输入模拟信号转换为数字输出。它通过多 个比较器同时比较输入模拟信号与多个参考电压,得到数字输出。并行比较/串并行型AD转换器具有 转换速度快、分辨率高等优点,但电路复杂度较高。

压频转换型AD转换器

AD转换模块的应用场景

信号处理

在信号处理系统中,AD转换模块 用于将模拟信号转换为数字信号 ,便于进行进一步的处理和分析

。

控制系统

在控制系统中,AD转换模块用于 将传感器的模拟信号转换为数字信 号,便于控制器进行数据处理和控 制。

数据采集

在数据采集系统中,AD转换模块用 于将模拟信号转换为数字信号,便 于计算机或其他数据处理设备进行 存储和处理。

AD转换模块PPT课件

CONTENTS

ADDA转换器原理及控制电路设计PPT课件

8

8

电子设计创新开放实验讲义

2.5 DAC的转换精度与转换速度

1. 转换精度

①分辨率:表示DAC对模拟量的分辨能力,它是最低有效位(LSB)所对应模拟 量的值。由于满度值所代表的模拟值在不同的应用中是可变的,因 此分辨率通常用DAC二进制的位数来表示,如8位、10位、12位,有 时也表示成:分辨 1率 LSB1 FSR2n1

电子设计创新开放实验讲义

D/A、A/D转换器原理及控制电路设计

1、 概述 2、 D/A转换器 3、 A/D转换器

22.11.2020

1

1

电子设计创新开放实验讲义

1、 概述

能将模拟量转换为数字量的电路称为模数转换器,简称 A/D转换器或ADC;能将数字量转换为模拟量的电路称为 数模转换器,简称D/A转换器或DAC。ADC和DAC是沟通 模拟电路和数字电路的桥梁,也可称之为两者之间的接口。

②转换误差:指实际输出模拟电压与理想值之间的最大偏差。

通常有两种表示方法,即绝对误差、相对误差。

绝对误差:用最低有效位的分数形式表示,如±(1/2)LSB,则它表示最大误差:

VE

1 VFS 2 2n 1

相对误差:用最大误差与满量程电压VFS的百分数表示。例如相对误差为±0.1%,

则表示最大误差:VE=±0.1%·VFS,如果VFS=10V,VE=±10mV。

22.11.2020

17

17

③取样—保持电路

电子设计创新开放实验讲义

原理:

①S(t)=1,T٧,VI对CH充电,VO=VI 采样

保持

,VO=VC不变S(t)=0,T②

22.11.2020

18

18

电子设计创新开放实验讲义

DSP-的Adc

DSP 的A/D 转换器本章主要内容:➢ F281x 的A/D 转换器的特点(Features of F281x ADC)➢ 自动排序器原理(Autoconversion Sequencer Principle)➢ 不间断的自动排序模式(Uninterrupt Autosequenced Mode)➢ ADC 时钟定标(ADC Clock Prescaler )➢ ADC 寄存器(ADC Registers)➢ ADC 的C 语言编程实例(ADC C Programing Examples)F281x 的A/D 转换器的特点TMS320F281x DSP 内部有一个12 位模/数转换器(Analog to Digital Converter, ADC),可有16 通道模拟输入信号, 转换时间可以在80ns 以内。

16 个结果寄存器ADCRESULT0~ ADCRESULT15 存储转换结果。

ADC 模块可以设置为两个独立的8 通道转换器,将一系列转换自动排序,每个模块可以从8 个输入通道中任意选择输入。

ADC 模块也可以工作在级联模式(Cascaded Sequencer Mode),自动排序器(Sequencer)就变成一个单16 通道的排序器。

该A/D 转换器的功能包括:• 12 位ADC 模块,内含采样/保持(Sample/Hold, S/H)电路。

• 同时采样或顺序采样模式。

• 模拟电压输入范围0~3V。

• 25 MHz 的ADC 时钟频率,转换时间短。

• 16 通道,多路选通输入。

• 可在一次采样中同时实现16 路自动转换的自动排序。

每个转换可以从1~16 输入通道中任意选择。

• 排序器可以作为两个独立的8 通道排序器或一个16 通道排序器即级联模式。

• 16 个结果寄存器存储转换结果,每个寄存器可独立寻址。

输入模拟电压和采样结果的关系为:数字结果=4095×(输入模拟电压-ADCLO)/3。

DSP课件-ADC模块

u1 输入模 拟信号

u2பைடு நூலகம்样/保持器 输出信号

A/D转 换命令

高电平期间 u2跟随u1

t

低电平期间u2保持不变,

同时A/D进行转换

4

在计算机屏幕上波形的恢复显示

提示:因为计算机屏幕波形显示是用不连续的点 组成,所以,若将被采样波形恢复显示,必须有 足够高的采样率。

频率为1kHz的正弦波

采样率 每周期采样点数

SEQ1和SEQ2同时运行,转换结果如下:

ADCINA0--》ADCRESULT0;ADCINB0--》ADCRESULT1;

ADCINB3--》ADCRESULT3。

先转换排序器1,后转换排序器2中的设定的通道。

14

模式2:同步采样模式

同步模式下,CONVxx的低3位确定采样与转换的模拟输入通 道对(SHA、SHB的输入通道序号相同),最高位不起作用。

例如:CONVxx=X110B, 选择ADCINA6和ADCINB6,依次转换SHA、SHB 中保持的电压量,结果存至ADCRESULTn、 ADCRESULT(n+1) 中。

ADCCHSELSEQ1.bit.CONV00=0x00; //设置ADCINA0和ADCINB0

ADCCHSELSEQ1.bit.CONV01=0x01; //设置ADCINA1和ADCINB1

ADCCHSELSEQ3.bit.CONV08=0x02; //设置ADCINA2和ADCINB2

ADCCHSELSEQ3.bit.CONV09=0x03; //设置ADCINA3和ADCINB3

CONVxx位确定采样与转换的模拟输入通道,最高位确定采用 SHA或SHB,其余3位定义通道号。例如:CONVxx=0101B, 选择ADCINA5; CONVxx=1011B, 选择ADCINB3。

《AD转换的过程》PPT课件

2

0100

3

0110

4

0101

转换结果:(0100)2

CP SAR

1

1000

vO / V 2.5

2

0100

1.25

3

0110

1.875

4

0101

1.5625

转换结果:(0101)2

vO /V 2.5 1. 25 1.875 1.5625

比较结果

vI<vO vI>vO vI<vO vI<vO

量化误差为1LSB

VREF=1V

7.3.2 并行比较型A / D转换器

如何同时比较?

3 R 13 V

2

16

R

11 V

16

R

9V

16

R

7V

16

R

5V

16

R

3V

16

+ -

C6

0

+ -

C5

0

+ -

C4

0

+ -

C3

10

+ -

C2

1

+ -

C1

1

每个电压刻度使用一个比较器。

7/16V<vI≤9/16V 5/16V<vI≤7/16V

DAC

VREF=-5V

D3

D2 D1 D0

vI

+ -

C

逐次逼近 寄存器(SAR)

CP

h

31

7.3.3 逐次逼近型A / D转换器

解: 1.量化单位为:

5V0.312V 5 16

D 1.5 4.8 0.3125

转换结果D=(0100)2 2.转换误差为:

AD转换器.ppt

模数转换器ADC的输入方式

单边输入方式 差分输入方式

单边输入和差分输入也可以混合使用, 例如:

AN0和AN1差分输入,AN2和AN3单边输入; AN4和AN5差分输入,AN6和AN7单边输入。

单边输入方式

ADC是12位精度的,其转换的最大值是 4096,但12位转换结果被左移了3位பைடு நூலகம்再

加 上一个符号位,所以最大值是32760

低域值寄存器ADLLMT0-7(ADC_BASE+$11-ADC_BASE+$18)

高域值寄存器ADHLMT0-7(ADC_BASE+$19-ADC_BASE+$20)

控制寄存器ADCR1

STOP:=1 停止A/D转换,SYNC信号和STAR信写操作无效。 START:=1开始A/D转换。 SYNC:=1使用SYNC输入或START位触发A/D转换;

通道列表寄存器保存通道被转换的顺序。如果所有的 采样都打开,顺序扫描的次序为SAMPLE0到 SAMPLE7。如果同时扫描,次序为SAMPLE0、 SAMPLE4、 SAMPLE1、 SAMPLE5、SAMPLE2、 SAMPLE6、 SAMPLE3、 SAMPLE7。

采样允许寄存器ADSDIS

1234

Freescale(Motorola) 16位DSP原理及开发技术

9.模数转换器ADC

模数转换器ADC组成框图

ADC包括8个输入通道、两个独立的采样保持电路、两个独 立

转换器,转换精度为12位,结果存储在数字输出存储器中。

转换过程可以被SYNC或控制寄存器ADCR1的STAR位触发。

模数转换器ADC的特点

状态寄存器ADSTAT

1234

域值状态寄存器ADLSTAT

第8章 DA、AD转换

第八章D/A、A/D转换及应用(DA,AD and applications)§8.1 概述(summarize)在实际控制系统中会大量遇到从时间到数值都连续变化的物理量,称为模拟量,如温度、压力、流量、位移、电压、电流等微机只能接收数字量处理,处理结果也只能以数字量输出实际控制系统过程:(见P267,F11-1)传感器——采集或检测现场模拟信号,并且转换为电信号放大器——将传感器信号(通常为mV~ V级)放大到A/D转换所需范围低通滤波器——抑制干扰,提高信噪比多路开关——实现用一个A/D转换器处理多个现场参数的切换装置采样—保持电路——用于提高转换精度和消除转换时间的不确定性§8.2 D/A转换(digital-analog conversion)一.D/A电路·数模转换器通常由四个部分组成,即权电阻网络、模拟开关、基准电源、运算放大器·数字量输入D/A转换器后,模拟开关根据二进制数的“1”或“0”状态来控制接基准电源或接地,权电阻网络通过模拟开关连接到基准电源上或接地转换成相应的电流输出,运算放大器则对各电流输出分量按权求和而输出模拟电压·集成的DAC器件主要用电流模拟开关电流相加型,不管哪种形式都需要一个数字变电流的电路D/I,然后将I变为电压,若I正比D,则V正比D1.权电阻网络D/A转换器(P270,F11-3)R i =2n-1-i ·R (n 为位数)ii R E I = i1n 0i i 1n 0i i R E b I I ∑∑-=-=== b i =1,接-Eb i =0,接地运算放大器的两个基本特点是:① 放大倍数很大,反相输入端电平接近于“地”(即虚地) ② 输入阻抗很高,输入电流接近0,有I f =I输出电压为V OUT =I f ·R f =I ·R fN 2E R R 2b 2E R R R E 22b R R2E b R R E b R R I V 1n f 1n 0i i i 1n f 1n 0i 1n i if 1n 0i i 1n if 1n 0i i if f f OUT ⋅⋅=⋅⋅=⋅⋅=⋅⋅=⋅=⋅=--=--=--=---=∑∑∑∑其中二进制数∑-=⋅=1n 0i i i 2bN 即是输入的二进制数字量即一个数字量N 经D/A 转换后可得到与N 成正比的模拟量V OUT ·电路缺点:位数越多,权电阻的阻值越多,精度要求很高2.T 型R-2R 电阻网络D/A 转换器(P270,F11-4)运算放大器反相输入端相当于地,故不管开关在哪个位置,各电阻上电流都不变T 型网络特点是,对其中任意一个节点,向右看去电阻都为2R ,所以2R E I 3=,R2E I 21I 2432-== ∵I 2+I 1+2I 0=I 3又I 1+2I 0=I 2∴2I 2=I 3,即I 2=I 3/2R 2E I 21I 1421⋅==-,R2E I 21I 0410⋅==-,即 R 2E I i n i ⋅=- 总电流(基准电流)不变,为 ∑-==1n 0i i I I对于R f 上的电流I f 为 N R2E 2b R 2E R 2E b I b I n 1n 0i 1n 0i i i n i n i 1n 0i i i f ⋅⋅=⋅⋅=⋅=⋅=∑∑∑-=-=--= E N R2R I R V n f f f OUT ⋅⋅=⋅= 即数字量N 经D/A 转换后可得到与N 成正比的模拟量调整R f 可得输出模拟量的范围,通常取R f =R ,有NE 21V n OUT = ·电路优点:电阻只有两种阻值,容易生产二.DAC0832芯片8位数模转换芯片,20脚,可直接与系统总线连接1.组成(P272,F11-5)由8位输入寄存器、8位DAC 寄存器和8位D/A 转换器组成,可进行两次缓冲(LE=1时Q输出随D输入,LE=0时D端被锁存)8位D/A转换器即上述R-2R的T型电流型开关(还未经变换成电压)①特点输入8位二进制码数字量可选用二级缓冲型、单级缓冲型、直通型三种工作方式电流稳定时间为1μs,线性度可调增益温度补偿0.002%FS/︒C(FS——Full Scale满刻度)可与所有8位微处理机直接相连,所有电平与TTL兼容单一电源5~15V,功耗20mW②引脚D0~D7:8位输入数字信号,来自系统输入不足8位时,未用端应接地,否则悬空DAC识别为“1”CS:片选信号,输入低电平有效CS、ILE、WR1同时有效时,输入数字锁存到8位输入寄存器中ILE:允许输入锁存,与CS、WR1同时控制输入寄存器WR1:写信号1,对应输入寄存器WR2:写信号2,对应DAC寄存器XFER:传输控制信号,输入低电平有效XFER与WR2同时有效时,将输入寄存器中的数字再传送到8位D/A寄存器中锁存起来I out1:输出电流1,当DAC寄存器全“1”最大,全“0”为0I out2:输出电流2,与I out1相加为一常数(总电流不变)R fb:反馈电阻,作为直流运放反馈电阻V REF:参考电压输入,作为基准电压,要求高精度、高稳定性可在+10V~-10V范围选择Vcc:电源电压(数字量电源),在+5V~+15V选择,Vcc=15V状态最佳AGND:模拟量地DGND:数字量地一般情况下两地端相连,高要求场合应分开,两地分开可避免出现较大的接地电流和感应噪声2.DAC0832的三种工作方式①双缓冲工作方式(P274,F11-6)利用两个地址码进行二次输出完成转换REF REFfb OUT V R R 256N V ⋅-=,N 为二进制数字量 如:MOV AL ,DA TAOUT 20H ,ALOUT 21H ,ALOUT 信号使LE=1,Q=DOUT 信号过后LE=0,D 输入端被锁存② 单缓冲工作方式i .一个寄存器直通,另一个受控如:XFER 和WR 2同时接地,DAC 寄存器直通MOV AL ,DA TAOUT 20H ,AL又如:CS 和WR 1同时接地,输入寄存器直通MOV AL ,DA TAOUT 21H ,ALii .两个寄存器同时选通(合用一个地址)及锁存,即CS 和XFER 同时接地址端,WR 1和WR 2同时接CPU 的WR③ 直通型工作方式将CS 、WR 1、WR 2和XFER 同时接地,ILE 接高电平成直通方式,D/A 转换器的输出随输入变化常用于连续反馈控制系统中三CPU 与不带输入寄存器的D/A 芯片的连接1.8位D/A 转换器可用8212、74LS273、8255A 等作锁存器2.10位D/A 转换器对于大于8位的D/A 转换器与8位数据总线的系统连接,应使用两级缓冲设上次转换的数据为0011110000下次要转换的数据为010*******,在单级缓冲下,送出低8位时, 与上次的高2位组成0000001011,D/A 转换器瞬间输出低电压 等高2位送出后才得010*******使用两级缓冲可消除毛刺现象(7475——4位双稳态锁存器,74100——8位双稳态锁存器) 每级需用2个锁存器,在第一级分二次送低8位和高2位,第二级再一次送给D/A 器件,所以10位D/A 转换要执行三次输出命令 MOV AL ,DA TAL ;数据低8位OUT 54H ,ALMOV AL ,DA TAH ;数据高2位OUT 55H ,ALOUT 56H ,AL ;送往第二级进行D/A 转换(该指令并不是把AL 送56H ,而是打开第二级缓冲器去D/A 转换)四.D/A 转换器的主要技术指标1.分辨率:通常用数字量的位数表示,如:分辨率为10位表示它可以对满量程的102412110 增量作出反应也可定义为转换的最小电压与最大电压之比,如121 n 2.转换时间:数字量输入到完成转换输出达到稳定值所需时间 常为几十纳秒到几微秒3.转换线性:数字量与模拟量按比例关系变化的程度,通常给出在一定温度下的最大非线性度,一般为0.01~0.03%4.输出电平:大部分为电压输出,一般5~10V ,高压输出型为24~30V 。

第八章AD和DA转换器

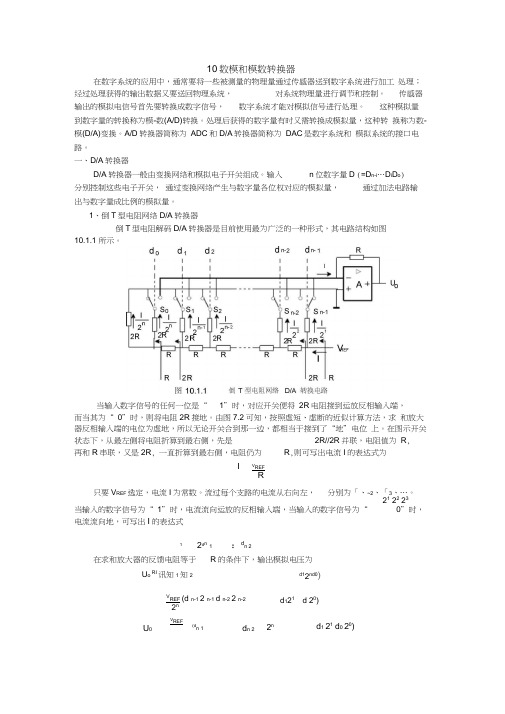

VREF (dn-1 2 n-1 d n-2 2 n-22nd 121 d °20)U 0V REF(d n 1d n 22nd 1 21 d 0 20)10数模和模数转换器在数字系统的应用中,通常要将一些被测量的物理量通过传感器送到数字系统进行加工 处理;经过处理获得的输出数据又要送回物理系统, 对系统物理量进行调节和控制。

传感器 输出的模拟电信号首先要转换成数字信号,数字系统才能对模拟信号进行处理。

这种模拟量到数字量的转换称为模-数(A/D)转换。

处理后获得的数字量有时又需转换成模拟量,这种转 换称为数-模(D/A)变换。

A/D 转换器简称为 ADC 和D/A 转换器简称为 DAC 是数字系统和 模拟系统的接口电路。

一、D/A 转换器D/A 转换器一般由变换网络和模拟电子开关组成。

输入 n 位数字量D (=D n-i …D i D o )分别控制这些电子开关, 通过变换网络产生与数字量各位权对应的模拟量,通过加法电路输出与数字量成比例的模拟量。

1、倒T 型电阻网络D/A 转换器倒T 型电阻解码D/A 转换器是目前使用最为广泛的一种形式,其电路结构如图10.1.1 所示。

当输入数字信号的任何一位是“ 1”时,对应开关便将 2R 电阻接到运放反相输入端, 而当其为“ 0”时,则将电阻2R 接地。

由图7.2可知,按照虚短、虚断的近似计算方法,求 和放大器反相输入端的电位为虚地,所以无论开关合到那一边,都相当于接到了“地”电位 上。

在图示开关状态下,从最左侧将电阻折算到最右侧,先是 2R//2R 并联,电阻值为 R , 再和R 串联,又是2R , 一直折算到最右侧,电阻仍为 R ,则可写出电流I 的表达式为IV REFR只要V REF 选定,电流I 为常数。

流过每个支路的电流从右向左,分别为「、~2、「3、…。

21 22 23当输入的数字信号为“ 1”时,电流流向运放的反相输入端,当输入的数字信号为“ 0”时, 电流流向地,可写出I 的表达式12d n 1:d n 2在求和放大器的反馈电阻等于R 的条件下,输出模拟电压为U o RI 讯知1知2d12nd0)2、权电流型D/A转换器倒T型电阻变换网络虽然只有两个电阻值,有利于提高转换精度,但电子开关並非理想器件,模拟开关的压降以及各开关参数的不一致都会引起转换误差。

AD转换器

双积分型ADC • 双积分型ADC:是1种V—T型A/D转换器,

• 由积分器、比较器、计数器和部分控制电路组成。

• 最大优点:是工作稳定,抗干扰能力强。 • 最大缺点:是速度较慢,所以主要用于数字电压

表等低速测试系统中。 • 转换精度主要取决于位数、运算放大器和比较器 的灵敏度和零点漂移等因素,高精度的价格较贵。

• 自电子管ADC面世以来,经历了分立半导体、集成 电路数据转换器的发展历程。

• ADC的生产已进入全集成化阶段,同时在转换速度 和转换精度等主要指标上有了重大突破,还开发了 一些具有与计算机直接接口功能的芯片。在集成 技术中,又发展了模块、混合和单片机集成数据转 换器技术。

• ADC主要的应用领域不断拓宽,广泛应用于多媒体、 通讯、自动化、仪器仪表等领域。对不同的领域 的不同要求,例如接口、电源、通道、内部配置的 要求,每一类ADC都有相应的优化设计方法;同时, 用户不仅要考虑到ADC本身的工艺和电路结构,而 且还应考虑到ADC的外围电路,如相应的信号调理 电路等模拟电路的设计。

• 各种技术和工艺的相互渗透,扬长避短,开发出 适合各种应用场合,能满足不同需求的A/D转换器, 将是模拟/数字转换技术的未来发展趋势;高速、 高精度、低功耗A/D转换器将是今后数据转换器发 展的重点。

全并行模拟/数字转换

• 它的工作原理非常简单,模拟输入信号同时与2N1个参考电压进行比较,只需一次转换就可以同时 产生n位数字输出。它是迄今为止速度最快的A/D 转换器,最高采样速率可以达到500MSPS。

• A/D转换器(ADC)是将模拟信号转换成数 字信号的电路 • A/D转换过程包括取样、保持、量化和编码 4个步骤,一般,前2个步骤在取样-保持电 路中1次性完成,后2个步骤在A/D转换电路 中1次性完成。

AD DA转换PPT

30-Aug-11

18

2、逐次比较型A/D转换器

(1)逐次比较型A/D转换器由控制电路、数码寄存器、 逐次比较型A/D转换器由控制电路、数码寄存器、 A/D转换器由控制电路 D/A转换器和电压比较器组成。 D/A转换器和电压比较器组成。 转换器和电压比较器组成

30-Aug-11

当 R

F

= 3 R 时: I 2

REF n −1

vo = −

30-Aug-11

R

∑

n −1 i= 0

Di × 2

i

31

DAC芯片的选择 芯片的选择

1.输入数字量的特征 2.负载特性 3.参考电源的特性 4.动态特性 5.接口特性 6.工作条件、环境条件

30-Aug-11

30-Aug-11

26

D/A转换技术主要类型 三、D/A转换技术主要类型 1.权电阻网络DAC

当RF = R / 2时: VREF n−1 vo = − n ∑Di × 2i 2 i=0

特点:电阻取值太多。

30-Aug-11

27

2.T型电阻网络 2.T型电阻网络DAC 型电阻网络DAC

,表明实际输出的数字量和理

论输出的数字量之间的误差小于最低有效位 的一半。

30-Aug-11

11

3、转换速度

ADC的转换速度主要取决于转换电路的类。 一个八位的计较器: 并联比较型 50ns之内 逐次比较型 在10~100us之间 双积分型 在数十到数百ms之间。

30-Aug-11

30-Aug-11 29

3.倒 型电阻网络DAC 3.倒T型电阻网络DAC

特点:开关 的接触电阻 影响转换精 度。

《AD转换和DA转换》PPT课件

h9章 A/D转换与D/A转换

41

3位逐次渐近型A/D转换器的电路框图

h9章 A/D转换与D/A转换

42

➢ 3个同步RS触发器FA、FB、FC作为寄存器 ➢ F1~F5构成的环形计数器作为顺序脉冲发生器 ➢ 控制电路由门电路组成。

h9章 A/D转换与D/A转换

43

➢ 设参考电压VR=-5V,则对应不同输入DAC的输出 为:

➢ 组成:寄存器、D/A转换器、电压比较器、顺序 脉冲发生器及相应的控制电路。

h9章 A/D转换与D/A转换

39

h9章 A/D转换与D/A转换

40

➢ 转换开始前将寄存器清零 ➢ 转换时,逐位改变寄存器的数字代码 ➢ 将此代码经D/A转换器转换成模拟电压vO ➢ vO与输入电压vI进行比较,以判断此数字位是否保留 ➢ 逐位比较下去,直到最低位为止。

9

2. 模拟开关

➢ 模拟开关又称为模拟电子开关。 ➢ 在D/A转换器中使用的模拟开关受输入数字信号

的控制。 ➢ 模拟开关分为CMOS型和双极型两类。 ➢ CMOS型模拟开关转换速度较低,转换时间较

长,但其功耗低 。

h9章 A/D转换与D/A转换

10

5G7520D/A转换器采用的CMOS型模拟开关

voV2RE nFD 25 3D

vo 2534V2.5V

vo 253 6V3.75V

vo 25 35V3.125V

h9章 A/D转换与D/A转换

44

➢ 设待转换的模拟电压vI=3.2V。工作前先将寄存器 清零,同时将环形计数器置成F1F2F3F4F5=00001。

h9章 A/D转换与D/A转换

➢ 按工作原理可以分成直接A/D转换器和间接A/D 转换器两大类。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

灵活的中断控制,允许每一个或每隔一个序列结束 产生中断Flexible interrupt control 排序器可工作在启/停方式

Sequencer can operate in start/stop mode

3

8.1概述Features

EVA和EVB可独立触发SEQ1和SEQ2 采样和保持时间窗口有独立的预定标控制

8

8.1.2 连续自动排序模式

例1,在双排序模式下用SEQ1来完成7个通道的转换(按照通道 2,3,2,3,6,7,12的顺序),则MAX CONV1设为6,CHSELSEQn寄存器的 值按照下表来设置。

9

8.1.2 连续自动排序模式

ADCTRL1中连续运行位(CONT RUN)置1,排序器收 到转换触发信号SOC 转换开始, MAX CONV1的值6装入SEQ CNTRn。按CHSELSEQn顺序转换。每次转换后SEQ CNTRn 自动减1。直到SEQ CNTRn为0。其后,转换排序自动重新 开始,(MAX CONV1的值6装入SEQ CNTRn, SEQ1的通道指 针指向CONV00).用户在下一个转换序列开始之前读取结果 寄存器的值; 每次SEQ CNTRn到达0时,中断标志都被置1。 连续自动排序方式的流程图如下图示:

Two independent 8-state sequencers (SEQ1 and SEQ2) or cascaded into one large 16-state sequencer (SEQ)

4个排序控制寄存器

Four Sequencing Control Registers (CHSELSEQn)

5

6

7

8.1.2 连续自动排序模式

适用排序器(SEQ1和SEQ2). 在该模式下, SEQ1/SEQ2一次排序可对多达8个转换通 道。转换结果依次保存到8个结果寄存器中(SEQ1为 RESULT0-7, SEQ2为RESULT8-15)。 一次排序转换的个数由MAX CONVn控制,该值在排序 转换开始时被自动装载到排序计数器状态位(SEQ CNTR3-0) 。排序器从通道CONV00开始有序地转换( CONV01, CONV02…… )时, SEQ CNTRn减1计数,直到SEQ CNTRn 为0。一次排序转换个数为MAX CONVn+1

26

8.3.2 ADC控制寄存器2

Bit 13 SOC SEQ1.排序器1启动转换位 以下触发源可引起此位置位:软件,EVA,EVB(级连时),ADC SOC引脚

当一个触发信号到达排序器1时,有以下3种情况发生: 1: SEQ1 处于空闲状态且 SOC位为0,在判优仲裁控制下, SEQ1立刻启动,SOC被置1后自动清0; 2: SEQ1 忙但 SOC位为0,该位置1表示一个触发源请求正 被悬挂,SEQ1完成当前转换又重新开始时,该位自动清0 3: SEQ1 忙且 SOC位被置1,这时后来的触发源将被忽略 0 清除一个悬挂的中断请求 Clears a pending SOC trigger. 1 软件启动 SEQ1 Software trigger

15

8.1.5 排序转换中的中断操作

排序器有两种产生中断方式,由ADCTRL2中断模式控 制位来决定。 例:对两个序列(1序列为X1,X2,2序列为Y1,Y2,Y3) 转换,在中断模式1下,转换步骤如下: 1 排序器设置MAX CONVn=1来转换X1和X2, 2 在中断服务子程序“a”中,通过软件将MAX CONVn=2 ,以转换Y1,Y2和Y3 3 在中断服务子程序“b”中,完成以下操作 • MAX CONVn再改为1,以转换X1和X2 • 从ADC结果寄存器中读取X1,X2 和Y1,Y2,Y3 • 排序器被复位 4 重复第2步和第3步。

注:每次SEQ CONTRn到0时,中断标志位被置1,且中断被识别

16

8.1.5 排序转换中的中断操作

在中断模式2下,第1序列和第2序列的采样个数均 为3个,转换步骤如下: 1 排序器置MAX CONVn=2; 2 触发源1启动转换X1,X2,X3; 3 触发源2启动转换Y1,Y2,Y3; 4在中断服务子程序“b” 中完成以下操作: (1) 从ADC结果寄存器中读取X1,X2 ,X3和 Y1,Y2,Y3 (2)排序器被复位 5 重复第2-4步

20

8.3.1 ADC控制寄存器1

Bit 14 RESET. ADC 模块软件复位 0 1 不起作用 复位ADC模块,所有寄存器和排序器指针都复位到初始状态

Bits 13, 12 SOFT and FREE:当有仿真悬挂时ADC模块的相应方式位 Soft Free 0 1 X 0 0 1 一旦仿真悬挂立刻停止转换 完成当前转换后停止转换 不管仿真悬挂继续转换

10

SEQ CNT Rn SEQ CNT Rn

SEQ CNT Rn=0?

转换结束

11

8.1.3 排序器的启动/停止模式

适用于排序器(SEQ1,SEQ2,SEQ)。 这种模式下CONT RUN必须设为0。排序器完成一个转 换序列后,排序器的指针指向当前通道,排序器指针不需 要指向CONV00就可以被重新触发。 例2,排序器工作在启动/停止模式下,用触发信号1(定时 器下溢)启动3个自动转换(I1,I2,I3),用触发信号2(定时器周期 匹配)启动3个自动转换(V1,V2,V3).这两个触发信号的时间 间隔是25μs,EVA设置。 在这种情况下只有SEQ1被用到。 MAX CONV1的值设 为2,ADC输入通道选择排序控制寄存器(CHSELSEQn)的 设置如下表所示:

8.1.4 输入触发信号

输入触发信号到达时,如果排序器处于空闲状态,则 马上开始排序,如果排序器处于排序状态,则将寄存 器ADCTRL2中的SOC SEQn位置1,这时,如果又有一个 新的触发信号到达,则将会被忽略。 一旦被触发,排序器无法在中途被停止或中断。 排序器在级联方式下,SEQ1可看作是一个最多可以转 换16路通道的排序器,排序器SEQ2的触发源被忽略。

27

8.3.2 ADC控制寄存器2

Bit 12 SEQ1 BSY (SEQ1忙状态位) 0 SEQ1 处于空闲状态

1 SEQ1 转换序列正在进行 Bits 11–10 INT ENA SEQ1(SEQ1 的中断方式控制位) 0 0 0 1 0 1 1 1 中断禁止 中断方式1,当中断标志位(INT FLAGSEQ1)置1时立 刻产生中断 中断方式2, 仅当中断标志位(INT FLAGSEQ1)已经被 置1时产生中断请求 保留

24

8.3.2 ADC控制寄存器2

ADC Control Register 2 (ADCTRL2)

25

8.3.2 ADC控制寄存器2

Bit 15 EVB SOC SEQ. EVB 触发级联排序器使能位 (注:该位仅能在级联模式下使能.) 0 不起作用 1 允许EVB启动级联排序器 Bit 14 RST SEQ1 / STRT CAL.复位排序器1/启动校准 在禁止校准方式情况下: 0 不起作用No action 1 立即复位排序器 Immediately reset sequencer to state CONV00

12

13

8.1.3 排序器的启动/停止模式

SEQ1复位和初始化后,就开始等待SOC转换触发信号的 到来。排序器接收到触发信号之后,转换就开始。 通道选择 值为CONV00(I1)、 CONV01(I2)、 CONV02(I3)的3个转换被 执行。25μs之后,第2个触发信号到来,另外3个通道选择值 为CONV03(V1)、 CONV04(V2)、 CONV05(V3)的转换开始 执行。 两种触发信号,MAX CONV1的值2都自动装入SEQ CNTR1中。如果第2个触发源要求转换的个数和第1个不同, 用户必须在第2个触发到达之前通过软件修改MAX CONV1的 值。 当SEQ1完成第2个序列的转换之后,用户可以通过软件 复位SEQ1,将排序器指针指向CONV00,重复同样的触发源1 、2的操作。 14

EVA and EVB can independently trigger SEQ1 and SEQ2, respectively.

Sample-and-hold acquisition time window has separate prescale control

4

8.1.1 工作原理

Principle of Operation

28

8.3.2 ADC控制寄存器2

Bit 9 INT FLAG SEQ1. SEQ1中断标志位(向该位写1清0)

0 无中断请求

1 有中断请求 Bit 8 EVA SOC SEQ1 EVA启动SEQ1位 0 禁止EVA启动SEQ1 1 允许EVA启动SEQ1/SEQ Bit 7 EXT SOC SEQ1 外部信号启动SEQ1位 0 不起作用

1

Low priority (低级,六级)

23

8.3.1 ADC控制寄存器1

Bit 4 SEQ CASC . 级连排序器方式位Cascaded sequencer operation 0:双排序器模式 Dual-sequencer mode. 1:级连模式 Cascaded mode. Bit 3 CAL ENA.偏差校准使能位 Offset calibration enable 0 禁止校准模式 1 使能校准模式 Bit 2 BRG ENA .桥使能位 Bridge enable. 0 全参考电压接到ADC 1 参考电压的中点接到ADC Bit 1 HI/LO. 参考电压高低选择位 VREFHI/VREFLO selection 0 校准或自测试时用VREFLO作为ADC的输入 0 校准或自测试时用VREFHI作为ADC的输入 Bit 0 STEST ENA. 自测试使能位 Self-test function enable 0 禁止自测试 1允许自测试