第3章DSP的CPU及指令系统

第3章C28xDSP的CPU与指令系统

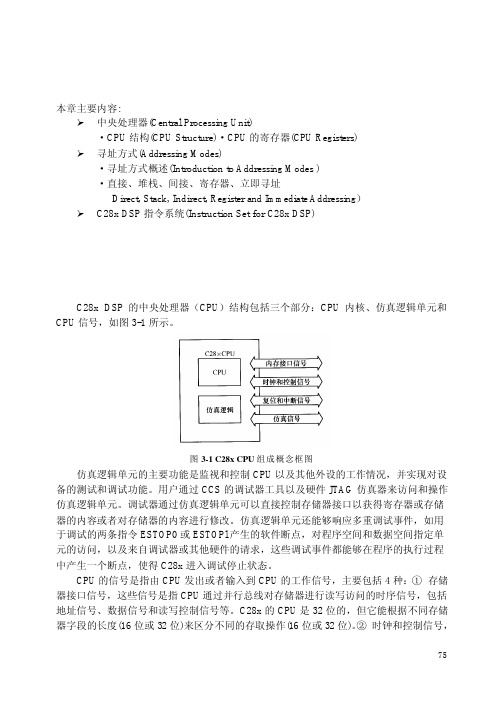

第3章 TMS320C28x DSP的CPU与指令系统 本章主要内容:Ø 中央处理器(Central Processing Unit)・CPU结构(CPU Structure)・CPU的寄存器(CPU Registers)Ø 寻址方式(Addressing Modes)・寻址方式概述(Introduction to Addressing Modes )・直接、堆栈、间接、寄存器、立即寻址 (Direct, Stack, Indirect, Register and Immediate Addressing)Ø C28x DSP指令系统(Instruction Set for C28x DSP) 3.1中央处理器 3.1.1 CPU结构 C28x DSP的中央处理器(CPU)结构包括三个部分:CPU内核、仿真逻辑单元和CPU信号,如图3-1所示。

图3-1 C28x CPU组成概念框图 仿真逻辑单元的主要功能是监视和控制CPU以及其他外设的工作情况,并实现对设备的测试和调试功能。

用户通过CCS的调试器工具以及硬件JTAG仿真器来访问和操作仿真逻辑单元。

调试器通过仿真逻辑单元可以直接控制存储器接口以获得寄存器或存储器的内容或者对存储器的内容进行修改。

仿真逻辑单元还能够响应多重调试事件,如用于调试的两条指令ESTOP0或ESTOPl产生的软件断点,对程序空间和数据空间指定单元的访问,以及来自调试器或其他硬件的请求,这些调试事件都能够在程序的执行过程中产生一个断点,使得C28x进入调试停止状态。

CPU的信号是指由CPU发出或者输入到CPU的工作信号,主要包括4种:①存储器接口信号,这些信号是指CPU通过并行总线对存储器进行读写访问的时序信号,包括地址信号、数据信号和读写控制信号等。

C28x的CPU是32位的,但它能根据不同存储器字段的长度(16位或32位)来区分不同的存取操作(16位或32位)。

dsp汇编指令系统介绍(精)

汇编指令集本节根据指令的功能来分,提供六张表来说明指令集的概况:累加器、算数和逻辑指令(表2);辅助寄存器和数据页指针指令(表3);TREG、PREG和乘法指令(表4);转移指令(表5);控制指令(表6);I/O和存储器操作(表7)。

在每张表中,指令按字母顺序排列。

执行每条指令所需要的周期数在表中给出,所有指令都假设从内部程序存储器和内部数据存储器中执行,指令的周期数适用于单指令执行,不适用于重复方式。

编程时,用户必须对每条指令的寻址方式了解清楚,因此这里也在表中给出了每条指令的寻址方式。

由于指令的操作码对用户编程没有多大指导意义,在这里就没有列出来。

为了参照起见,我们先定义这六张概述表的符号意义:ACC 累加器。

ARBITXCM 辅助寄存器。

4位数值,用于指定数据存储器数值中的哪一位将被BIT指令所测试。

2位数值,CMPR指令执行CM值所声明的比较:若CM=00,测试当前AR=AR0否;若CM=01,测试当前AR<AR0否;若CM=10,测试当前AR>AR0否;若CM=11,测试当前AR≠AR0否。

ShiftTP 4位右移量。

用于条件执行指令的2位数值,代表如下4种条件:若BIO引脚为低,TP=00;若TC位=1,TP=01;若TC位=0,TP=10;无条件TP=11。

ARX 用于LAR和SAR指令的3位数据值,指定被操作的辅助寄存器。

52表2 累加器、算数和逻辑指令 ABS周期|(ACC)|→ACC 1(ACC)+(数据存储器地址)×12shift→ACC(ACC)+(数据存储器地址)×216→ACC 1(ACC)+k→ACC 1shift(ACC)+lk×2→ACC 2指令功能(ACC)+(数据存储器地址)+(C)→ACC寻址方式直接/间接直接/间接短立即数长立即数指令说明ACC取绝对值移位时低位填0,若SXM=1,高位用符号扩展;若SXM=0,高位填0;结果存在ACC中,该指令使C=0。

DSP芯片技术及应用

DSP总结:以下总结仅针对宁波大学DSP芯片技术及应用(通信类非控制类)这门课,个人根据重点、考点总结的,用于期末复习(请结合课本以及PPT的例子),不足之处请见谅,基本能过就是,如若其中有错请联系QQ:493288964。

还是建议您平时学点,理解为先!!!将该文章用于百度等兑换积分的行为是可耻的!第一章绪论(简介)1、DSP芯片特点:采用哈佛结构;多总线结构;流水线技术;专用的硬件乘法器;特殊的DSP指令;快速的指令周期;硬件配置强;支持多处理器结构1)CPU是冯.诺伊曼结构;DSP是数据和地址空间分开的哈佛结构。

冯.诺依曼结构:单存储空间;统一的程序和数据空间;共享的程序和数据总线;程序指令只能串行执行单指令周期:100ns,现在单指令周期为:10ns哈佛结构:双存储空间;程序存储器和数据存储器分开;程序总线和数据总线分开;独立编址、独立访问改进型哈佛结构:双存储空间、多条总线;多条数据总线;高速缓冲器(重复指令,只需读入一次)2)采用多总线结构:TMS320C54X:4组总线;单机器周期内可完成的操作;3)流水线操作4)专用的硬件乘法器硬件乘法累加器是DSP区别于通用微处理器的一个重要标志MAC(乘累加)单元(独立的乘法器和加法器;单周期内完成一次乘法和一次加法运算;MPY,MAC,MACA, MACSU等指令)分类:工作时钟和指令类型:静态和一致性DSP芯片;用途分:通用和专用型;数据格式分:定点和浮点型2、DSP按数据格式分为定点型和浮点型定点DSP芯片:数据长度16位/24位TMS320C2000/5000/6000价格便宜、功耗较低、但运算精度稍低。

浮点DSP芯片:数据长度32位/40位MS320C3X/4X/VC33/C67X/C8X价格稍贵、功耗较大、但运算精度高。

3、芯片简介TMS320VC5416PGE160 主处理器芯片的性能:频率:160MHz 速度:160MIPS 周期:6.25ns第二章:TMS320C54X的硬件结构1、C54X:为低功耗,高性能而专门设计的16位定点DSP芯片C54基本结构:中央处理器(CPU)、内部总线结构、存储器、片内外设。

第3章 C6000指令系统(1-2)

Dr. Naim Dahnoun, Bristol University, (c)

Texas Instruments 2002

12

32.2.2 延迟间隙(Delay Slots)

BK1

BK0

R

R,W

Mode select fields

15

14 13

12 11

10 9

87

6

B7 mode B6 mode B5 mode B4 mode A7 mode

5

4

A6 mode

R,W

3

2

A5 mode

1

0

A4 mode

R,W

00:线性寻址(复位后默认值)

各模式 01:循环寻址,使用BK0字段

Dr. Naim Dahnoun, Bristol University, (c)

Texas Instruments 2002

18

3.2.4 寻址方式及Load/Store类指令

一、寻址方式

寻址模式寄存器AMR各个位域的定义

Block size fields

31

26 25

21 20

16

ห้องสมุดไป่ตู้

Reserved

13

3.2.3 指令操作码映射图(Opcode Map)

C6000的每一条指令都是32位,都有自己的代码,详细指 明指令相关内容。

.L unit

31 29 28 27 23 22 18 17

13 12 11

54 3 2 10

在DSP应用中,虽然可以使用CC++高级语言编程,降低了

第3章汇编语言指令系统在DSP应用中,虽然可以使用C/C++高级语言编程,降低了对编程者的要求,但在一些实时性要求高的场合仍然需要采用汇编编程,以充分利用DSP丰富的硬件资源,发挥它的实时运算能力。

用汇编语言编程,要求编程者对DSP的低层有充分的了解,包括硬件结构、存储器空间模型和I/O口的组织等。

同时又要求编程者对指令系统有深刻的了解。

第3章汇编语言指令系统目录:3.1 C54x 汇编语言指令集介绍3.2 寻址方式3.3 C54x 系列DSP的指令系统参考:TMS320C54x DSP Reference Set Volume 2:Mnemonic Instruction Set.pdf, spru172c, 2001, TI官网3.1 C54x汇编语言指令集介绍C54x汇编语言源程序指令包括:➢汇编语言指令Assembly Language Instructions ➢汇编伪指令Assembler Directives➢宏指令Macro Directives本章介绍C54x DSP的汇编语言指令系统。

与其它CPU的指令集相同,汇编语言指令又称为硬指令,它们在汇编和连接后形成可执行的机器码,供DSP进行运算和其它操作。

TMS320C54x assembly language source programs consist of source statements that can contain assembler directives, assembly language instructions, macro directives, and comments.3.1.1 指令系统中的符号、缩写及操作符➢指令系统中采用的符号和缩写如下列表中所示序号符号含义1A累加器A2ALU算术逻辑运算单元3AR泛指通用辅助寄存器4ARx指定某一辅助寄存器AR0~AR75ARP ST0中的3位辅助寄存器指针6ASM ST1中的5位累加器移位方式位-16~15 7B累加器B8BRAF ST1中的块重复操作标志位9BRC块重复操作计数器10BITC或bit_code用于测试指令,指定数据存储器单元中的哪一位被测试,取指范围:0~15BIT Xmem, BITC3.1 C54x汇编语言指令集介绍3.1.1 指令系统中的符号、缩写及操作符(续)序号符号含义11C16ST1中的双16位/双精度算术运算方式位12C ST0中的进位位13CC2位条件码(0≤CC≤3)14CMPT ST1中的ARP修正方式位15CPL ST1中的直接寻址编辑标志位16cond表示一种条件的操作数,用于条件执行指令17[d],[D]延时选项18DAB D地址总线19DAR DAB地址寄存器20dmad16位立即数数据存储器地址(0~65535)序号符号含义21Dmem数据存储器操作数22DPST0中的数据存储器页指针(0≤DP≤511)23Dst目的累加器(A和B)24dst_与dst相反的目的累加器25EAB E地址总线26EAR EAB地址寄存器27extpmad23位立即数程序存储器地址28FRCT ST1中的小数方式位29hi(A)累加器的高阶位(AH或BH)30HM ST1中的保持方式位3.1.1 指令系统中的符号、缩写及操作符(续)序号符号含义31IFR中断标志寄存器32INTM ST1中的中断屏蔽位33K少于9位的短立即数34k33位立即数(0≤k3≤7)35k55位立即数(-16≤k5≤15)36k99位立即数(0≤k9≤511)37lk16位长立即数38Lmem利用长字寻址的32位单数据存储器操作数39mmr,MMR存储器映像寄存器40MMRx,MMRy存储器映像寄存器,AR0~AR7或SP3.1.1 指令系统中的符号、缩写及操作符(续)第3章汇编语言指令系统序号符号含义41n XC 指令后面的字数,取1或242N 指定状态寄存器,N=0为ST0,N=1为ST143OVA ST0中的累加器A 溢出标志44OVB ST0中的累加器B 溢出标志45OVdst 指定目的累加器(A 或B)的溢出标志46OVdst_另一个目的累加器(A 或B)的溢出标志47OVsrc 指定源累加器(A 或B)的溢出标志48OVM ST1中的溢出方式位49PA 16位立即数端口地址(0≤PA ≤65535)50PAR 程序存储器地址寄存器3.1.1 指令系统中的符号、缩写及操作符(续)XC n, cond [, cond [, cond]RSBX N, SBIT第3章汇编语言指令系统序号符号含义51PC程序计数器52pmad16位立即数程序存储器地址(0≤pmad≤65535)53pmem程序存储器操作数54PMST处理器工作方式状态寄存器55prog程序存储器操作数56[R]舍入选项57rnd舍入Round58RC重复计数器59RTN快速返回寄存器60REA块重复结束地址寄存器3.1.1 指令系统中的符号、缩写及操作符(续)第3章汇编语言指令系统序号符号含义61RSA 块重复起始地址寄存器62SBIT 用于指定状态寄存器位的4位地址(0~15)63SHFT 4位移位值(0~15)64SHIFT 5位移位值(-16~15)65Sind 间接寻址的单数据存储器操作数66Smem 16位单数据存储器操作数67SP 堆栈指针寄存器68src 源累加器(A 或B)69ST0,ST1状态寄存器0,状态寄存器170SXM ST1中的符号扩展方式位3.1.1 指令系统中的符号、缩写及操作符(续)RSBX N, SBIT序号符号含义71T暂存器72TC ST0中的测试/控制标志73TOS堆栈顶部74TRN状态转移寄存器(比较选择存储CSST单元内) 75TS由T寄存器的5~0位所规定的移位数(-16~31) 76uns无符号数77XF ST1中的外部标志状态位78XPC程序计数器扩展寄存器79Xmem16位双数据存储器操作数, 用于双数据操作数指令和单数据操作指令80Ymem16位双数据存储器操作数,用于双数据操作数指令3.1.1 指令系统中的符号、缩写及操作符(续)CMPS指令3.1.1 指令系统中的符号、缩写及操作符➢指令系统中的运算符号及优先级如下列表中所示序号符号运算功能求值顺序1+ -~ !取正、取负、按位求补、逻辑非从右至左2* / %乘法、除法、求模从左至右3+ -加法、减法从左至右4^指数从左到右5<< >>左移、右移从左至右6< ≤小于、小于等于从左至右7> ≥大于、大于等于从左至右8≠!=不等于从左至右序号符号运算功能求值顺序8=等于从左至右9&按位与运算(AND )从左至右10∧按位异或运算(exclusive OR )从左至右11|按位或运算(OR )从左至右3.1.1 指令系统中的符号、缩写及操作符➢指令系统中的运算符号及优先级如下列表中所示本节以LD 装载指令为例,说明指令的格式和其它一些有用信息。

第3章TMS320C54XDSP寻址方式09.10

ARx包含了数据存储器地址 访问后,ARx以循环寻址方式减1 ARx包含了数据存储器地址 访问后,ARx以循环寻址方式减去 AR0 ARx包含了数据存储器地址 访问后,ARx以循环寻址方式加1 ARx包含了数据存储器地址 访问后,ARx以循环寻址方式加上 AR0 ARx加上16位长偏移量作为数据 存储器地址 访问后,ARx中内容不变 ARx加上16位长偏移量作为数据 存储器地址 访问后,ARx中内容加上16位长 偏移量 ARx以循环寻址方式加上16位长 偏移量作为数据存储器地址, 同时修改ARx中内容 以无符号16位长偏移量作为数据 存储器地址 (绝对地址)

19

单操作数 3 间接寻址 y0 a i x i a0 x0 a1 x1 a 2 x 2 a3 x3 编程举例: i 0 .mmregs .bss x, 4 .word 1, 2, 3, 4 STM #a, AR1 STM #x, AR2 LD #0, A LD *AR1+,T MAC *AR2+,A LD *AR1+,T MAC *AR2+,A LD *AR1+,T MAC *AR2+,A LD *AR1,T MAC *AR2,A …..

第一条指令表示将数据存储器中以DATA符号为地址单元中 的数据传送到由辅助寄存器ARl所指向的数据存储单元中去。 DATA代表数据存储单元的地址dmad。 第二条指令表示将程序存储器中以TABLE符号为地址单元中 的数据传送到由辅助寄存器AR2所指向的数据存储单元中去。 TABLE代表程序存储单元的地址pmad。 第三条指令表示将地址为0F2F0H的端口中的数据传送到由 辅助寄存器AR5所指向的数据存储单元中去。

17序号间址类型功能说明arxaddrarxarx包含了数据存储器地址arxaddrarxarxarx1arx包含了数据存储器地址访问后arx中地址减1arxaddrarxarxarx1arx包含了数据存储器地址访问后arx中地址加1arxaddrarx1arxarx1寻址前arx中地址加1arx0baddrarxarxbarxar0arx包含了数据存储器地址访问后arx以位倒序方式减去ar0arx0addrarxarxarxar0arx包含了数据存储器地址访问后arx中减去ar0arx0addrarxarxarxar0arx包含了数据存储器地址访问后arx中加上ar0arx0baddrarxarxbarxar0arx包含了数据存储器地址访问后arx以位倒序方式加上ar0号表示间址32位字时增减为2寻址前变址只用于写操作指令18arxaddrarxarxcircarx1arx包含了数据存储器地址访问后arx以循环寻址方式减1arx0addrarxarxcircarxar0arx包含了数据存储器地址访问后arx以循环寻址方式减去ar010arxaddrarxarxcircarx1arx包含了数据存储器地址访问后arx以循环寻址方式加111arx0addrarxarxcircarxar0arx包含了数据存储器地址访问后arx以循环寻址方式加上ar012arxlkaddrarxlkarxarxarx加上16位长偏移量作为数据存储器地址访问后arx中内容不变13arxlkaddrarxlkarxarxlkarx加上16位长偏移量作为数据存储器地址访问后arx中内容加上16位长偏移量14arxlkaddrcircarxlkarxcircarxlkarx以循环寻址方式加上16位长偏移量作为数据存储器地址同时修改arx中内容15lkaddrlk以无符号16位长偏移量作为数据存储器地址绝对地址lk不允许mmr寻址19间接寻址时

TMS320C54X DSP 芯片的指令系统

分成512页,每页128个单元 DP取值范围:0~511 7位偏移地址范围:0~127 不改变基地址,可寻址连续的128个单元 DP复位值为0

直接寻址

DP值 00000 0000 偏移量 000 0000 „ 111 1111 000 0000 „ 111 1111 000 0000 „ 111 1111 „ 000 0000 „ 111 1111 数据存储器 第0页:0000H--007FH

例:MVDM 2000H,T RPT #19 ;数据块的复制 ;SAMPLE为常数表示 ;的地址 MVKD 0200H,*AR2+ MVMD AR2,SAMPLE

程序存储器地址(pmad)寻址

确定程序存储器中的一个地址 主要指令:

FIRS MACD MACP MVDP MVPD

Xmem, Smem, Smem, Smem, pmad,

位倒序寻址

主要用于FFT算法。 8点FFT的位码倒序:

若输入顺序:X(0)、X(1)、X(2) 、X(3)、 X(4) 、X(5) 、X(6)、X(7); 则输出顺序:Y(0)、 Y(4)、Y(2) 、Y(6)、 Y(1) 、Y(5) 、Y(3)、 Y(7).

16点FFT的位码倒序:表3.1.6

累加器:

Src,dst,dst_,A,B

移位值:

ASM,TS,SHFT,SHIFT K,k3,k5,k9,lk

立即数:

运算符及其优先级,表3.2.2

3.1 寻址方式

两种:数据寻址和程序寻址 数据寻址(7种基本方式)

立即数寻址 绝对地址寻址 累加器寻址 直接寻址 间接寻址 存储器映射寄存器寻址 堆栈寻址

DSP技术及应用习题答案

《DSP技术及应用》习题答案第1章绪论1.1 DSP的概念是什么?本书说指的DSP是什么?答:DSP有两个概念。

一是数字信号处理(Digital Signal Processing),指以数字形式对信号进行采集、变换、滤波、估值、增强、压缩、识别等处理;二是数字信号处理器(Digital Signal Processor),指是一种特别适合于进行数字信号处理运算的微处理器,其主要应用是实时快速地实现各种数字信号处理算法。

本书中的DSP主要指后者,讲述数字信号处理器的应用。

1.2 什么是哈佛结构和冯•诺伊曼结构?它们有什么区别?答:(1)冯·诺伊曼(Von Neuman)结构该结构采用单存储空间,即程序指令和数据共用一个存储空间,使用单一的地址和数据总线,取指令和取操作数都是通过一条总线分时进行.当进行高速运算时,不但不能同时进行取指令和取操作数,而且还会造成数据传输通道的瓶颈现象,其工作速度较慢。

(2)哈佛(Harvard)结构该结构采用双存储空间,程序存储器和数据存储器分开,有各自独立的程序总线和数据总线,可独立编址和独立访问,可对程序和数据进行独立传输,使取指令操作、指令执行操作、数据吞吐并行完成,大大地提高了数据处理能力和指令的执行速度,非常适合于实时的数字信号处理.1.3 已知一个16进制数3000H,若该数分别用Q0、Q5、Q15表示,试计算该数的大小.答:3000H=12288。

若用Q0表示,则该数就是12288;若用Q5表示,则该数就是12288*2—5=384;若用Q15表示,则该数就是12288*2—15=0。

3751。

4 若某一个变量用Q10表示,试计算该变量所能表示的数值范围和精度。

答:Q10能表示的数值范围是-32~31.9990234,其精度为2-101.5 若x=0.4567,试分别用Q15、Q14、Q5将该数转换为定点数.答:Q15:x*215=int(0。

DSP学习-3)时钟及系统控制解析

寄存器

寄存器

LPMCR0 低功耗模式控 WDKEY 看门狗复位

制寄存器0

key寄存器

LPMCRl 低功耗模式控 WDCR 制寄存器1

看门狗控制 寄存器

第2章 CPU内部结构与时钟系统

一、时钟及系统控制 时钟寄存器

▲ 外设时钟控制寄存器 PCLKCR —— 数据存储空间 0x0000701C

D15 D14

第2章 CPU内部结构与时钟系统

定时器

▲ 计数器——TIM

D15

D0

TIM

R/W-0

D15

D0

TIMH

R/W-0

▲ 周期寄存器——PRD

D15

D0

PRD

R/W-0

D15

D0

PRБайду номын сангаасH

R/W-0

第2章 CPU内部结构与时钟系统

定时器

▲ 控制寄存器——TCR0

TCR功能: √控制定时器模式 √重新加载定时器 √启动和停止定时器

一时钟及系统控制第第22章章cpucpu内部结构与时钟系统内部结构与时钟系统第第22章章cpucpu内部结构与时钟系统内部结构与时钟系统第第22章章cpucpu内部结构与时钟系统内部结构与时钟系统第第22章章cpucpu内部结构与时钟系统内部结构与时钟系统hispcphispcp一时钟及系统控制hispcp高速外设时钟设置寄存器pllcrpll控制寄lospcp慢速外设时钟设置寄存器scsr系统控制和状态寄存器pclkcr外设时钟控制寄存器wdcntr看门狗计数寄存器lpmcr0低功耗模式控制寄存器0wdkey看门狗复位key寄存器lpmcrl低功耗模式控制寄存器1wdcr看门狗控制寄存器第第22章章cpucpu内部结构与时钟系统内部结构与时钟系统第第22章章cpucpu内部结构与时钟系统内部结构与时钟系统数据存储空间0x0000701c时钟寄存器高低速外设时钟寄存器hispcplospcp0x0000701ab数据存储空间0x00007022保留d15d14d13d12d11d10d9d8ecanenclkmcbspenclkscibenclkspienclkr0rw0r0rw0rw0reservedd15d3d2d1d0wdintswdenintwdoverrider0r1rw0rw1c1一时钟及系统控制sciaenclk保留保留保留adcenclk保留evaenclkevbenenclkd7d4d3d2d1d0r0rw0r0rw0rw0rw0r0rw0reservedd15d3d2d0hspcklspckr0rw010第第22章章cpucpu内部结构与时钟系统内部结构与时钟系统第第22章章cpucpu内部结构与时钟系统内部结构与时钟系统时钟模块提供两种操作模式

DSP原理及应用第五版汪春梅课后答案

DSP原理及应用第五版汪春梅课后答案第一章绪论1、简述DSP系统的构成和工作过程。

答:DSP系统的构成:一个典型的DSP系统应包括抗混叠滤波器、数据采集A/D转换器、数字信号处理器DSP、D/A转换器和低道滤波器等。

DSP系统的工作过程:将输入信号x(t)经过抗混叠滤波,滤掉高于折叠频率的分量,以防止信号频谱的混叠经过采样和A/D转换器,将滤波后的信号转换为数字信号x(n)。

数字信号处理器对x(n)进行处理,得数字信号y(n)。

经D/A转换器,将y(n)转换成模拟信号经低通滤波器,滤除高频分量,得到平滑的模拟信号y(t)。

9、简述DSP系统的设计步骤。

答:明确设计任务,确定设计目标。

算法模拟,确定性能指令。

选择DSP芯片和外围芯片。

设计实时的DSP芯片系统。

硬件和软件调试。

系统集成和测试。

第二章TMS320C54x硬件结构1、TMS320C54X芯片的基本结构都包括哪些部分,答:中央处理器内部总线结构2、TMS320C54X芯片的CPU主要由哪几部分组成,答:40位的算术运算逻辑单2个40位的累加器(ACCA、ACCB).1个运行-16至31位的桶形移位寄存器。

17X17位的乘法器和40位加法器构成的乘法器-加法器单元(MAC)。

比较、选择,有所无指令编码器。

CPU状态和控制寄存器。

3、TMS320VC5402共有多少可屏蔽中断,它们分别是什么,和属于哪一-类中断RSMI源,答:TMS320VC5402有13个可屏肢中断,和属于外部硬件中断。

RSNMI 第三章TMS320C54x指令系统第一次1、已知(80H)=-50H,AR2-84H,AR3-86H,AR4 88H。

MVKD 80H,*AR2WVDD*AR2,*AR3.WVDM 86H,AR4运行以上程序后,(80I)、(84H)、*AR3和AR4的值分别等于多少,解:(80H)--50H,(84H);-50H,*AR3=50H,AR4-50H 2、已知,(80H):20H、(8IH)=30H。

DSP技术及应用--陈金鹰(第三章)

用来修 改存储 器映象 寄存器

7.堆栈寻址

功能 特点

PSHD *AR2 POPD *AR3

用来在中断和 子程序调用时 自动保存程序 计数器(PC) 中的数值,也 能用来保护现 场或传送参数

从高地址向低地址方向生长, SP用来管理堆栈,SP始终指向 堆栈中所存放的最后一个数 据,即SP指针始终指向栈顶。 在 压 入 操 作 时 , 先 减 小 SP 的 值,再将数据压入堆栈;在弹 出操作时,先从堆栈弹出数 据,再增加SP的值。 23

第二节

程序地址 生成器 (PAGEN) 构成 核心

程序地址的生成

程序计数器(PC) 重复计数器(RC) 块重复计数器(BRC) 块重复起始地址寄存器(RSA) 块重复结束地址寄存器(REA) 地址内容为: 即将取指的某条指令; 某个16位立即操作数; 系数表。 24 在程序存储器中的地址

16位程序计数器(PC) 内中保存某个内部或外 部程序存储器的地址。

ARx是数据存储器地址 访问后,ARx中的地址减1 访问后,ARx中的地址加1 访问后,AR0以循环寻址的 方式加到ARx中 21

6.存储器映象寄存器寻址

功能 方法 高9位数据 存储器地址 被置0,利 用指令中的 低7位地址 访问MMR。 LDM PRD,A

22

举例

特点 0页寻址。 不影响当前 DP或SP 值 。用于 直接寻址和 间接寻址

操作码语 法 *ARx *ARx*ARx+ *ARx+0%

辅助寄存器 AR2 AR3 AR4 AR5

双数据存储器操作数寻址的类型

Xmod或 Ymod 00 01 10 11 功 能 说 明

addr=ARx addr=ARx ARx=ARx-1 addr=ARx ARx=ARx+1 addr=ARx ARx=circ( ARx+AR0)

第3章 德州仪器公司的系列DSP

C2000系列的优势:通信接口

C2000微处理器包含各种可连接至系统组件的通 信接口。

C2000系列的优势:MCU 32位架构

C28X微处理器系列经过精心优化,可提供业界最 高性能的控制解决方案,并能最大限度地加速产 品上市进程。 (1)浮点与定点微处理器; (2)处理能力高达300MIPS或600MFLOPS (3)混合的16位机32位指令集 (4)同类最高的编译器效率 (5)单周期32*32位的乘法操作 (6)整个C2000 MCU系列均实现软件兼容

0 FFFFH XPC=0

1FFFFH XPC=1

2 FFFFH XPC=2

... F FFFFH XPC=15

图2-3 C5402扩展程序存储器图

程序存储器

通过MP/MC*和OVLY位的设置,可以实现对片内 存储器(ROM、RAM)的配置,即哪些片内存 储器映象在程序存储器空间。 器件复位时,复位、中断和陷阱中断的向量映象 在地址FF80H开始的程序存储器空间。然而,复 位后这些向量可以被重新映象在程序存储器空间 任何128字页的开始。这样,可以把向量表移出 引导ROM,并重新配置其地址。

程序空间: 页0 0000H 保留(OVLY=1 ) 外部(OVLY=0) 007FH 0080H 片内DRAM: 16K (OVLY=1) 外部(OVLY=0) 007FH 0080H 0000H

程序空间: 页0 0000H 保留(OVLY=1 ) 外部(OVLY=0) 片内DRAM: 16K (OVLY=1) 外部(OVLY=0) 片外 005FH 0060H 007FH 0080H 3 FFFH 4000H

表2-1 存储器映象寄存器

名称 IMR IFR 地址 0 1 说明 中断屏蔽寄存器 中断标志寄存器

基于TI公司三大DSP芯片的指令系统简述

1982 年推出第一个 DSP 芯片 TMS32010 以来,不断 字信号处理,DSP 的高性能与通用微控制器的方便

地革新换代,以其雄厚的实力在业界实现占全球市 性紧密结合在一起,再加上相应的独具特色的指令

场 50%的份额。TI 公司把市场销相比较量大和前景 系统设计,C2000 系列在工业控制和家电领域中达到

1 —〉AR(ARP)。

*0+ *0*BR0+ *BR0-

AR(ARP)的内容作为数据存储器地址, 操作后 AR(ARP)值改变:AR(ARP)+ AR0 —〉AR(ARP)。 AR(ARP)的内容作为数据存储器地址, 操作后 AR(ARP)值改变:AR(ARP)— AR0 —〉AR(ARP)。 AR(ARP)的内容作为数据存储器地址, 操作后 AR(ARP)值改变:AR(ARP)+ AR0 —〉AR(ARP)。(相加时按反向进位—— 向右进位) AR(ARP)的内容作为数据存储器地址, 操作后 AR(ARP)值改变:AR(ARP)- AR0 —〉AR(ARP)。(相减时按反向借位—— 向右借位)

2

无条件分支(跳转)B;无条件分支(跳转)到 ACCL 指定的程序地址处执行:BACC;条件分支(跳 转),表示如下:BCND;无条件调用子程序,有一 种寻址方式:CALL; 无条件调用 ACCL 指定的子 程序:CALA;条件调用子程序 CC;无条件返回, 表示为 RET 和条件返回表示为 RETC。

TMS320C2000 平台包含 TMS320C20x/ C24x 和 由存储器页指针 DP 给出,DP 包含数据存储器地址

32 位的 C28x 的定点 DSP。C2000 专门针对控制领域 的高 9 位。这样合成地址就是 16 位。因此指令并没

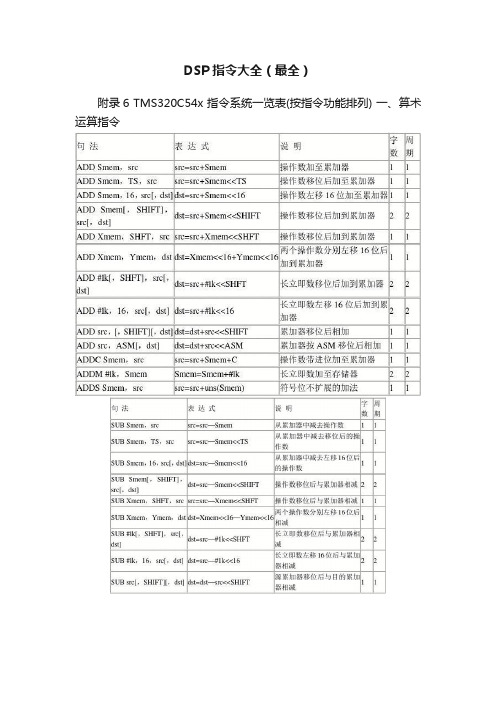

DSP指令大全(最全)

DSP指令大全(最全)附录6 TMS320C54x 指令系统一览表(按指令功能排列) 一、算术运算指令二、逻辑运算指令三、程序控制指令6.注:?条件―真‖,§条件―假‖,※延迟指令。

四、加载和存储指令4.6.7.五.伪指令2.初始化常数(数据和存储器)的伪指令3.调整段程序计数器伪指令(SPC).align 把SPC调整到页边界.even 把SPC调整到偶数字边界4.控制输出列表格式化伪指令5.条件汇编伪指令.break [well-defined expression] 如果条件真结束.loop汇编,.break结构是可选项.else 如果.if条件为假,汇编代码块.else结构是可选项.elseif well-defined expression——如果if条件为假且.elseif 条件为真,汇编代码块.else结构是可选项.endif 结束.if代码块.endloop 结束.1oop代码块.if well-defined expression 如果条件为真则汇编代码块.loop [well-defined expression] 开始代码块的重复汇编6. 汇编符号.asg [”] character string [”],substitution symbol——把字符串赋予替代的符号..endstruct 结束结构定义.equ 使值和符号相等.eval well-defined expression,substitution symbol 根据数字替代符号完成运算.newblock 取消局部标号.set 使数值和符号相等.struct 开始结构定义.tag 把结构属性赋予标号7.宏指令宏定义:Macname .macro[参数1],[…],[参数n]宏调用:[标号][:] macname [参数1],[…],[参数n]8.编译软件指令①汇编器:asm500.exeasm500[input file[object file [listing file] [-options]]-c—使汇编语言文件中大小没有区别。

DSP芯片简介介绍

图像/视频处理

DSP芯片在图像/视频处理领 域中广泛应用于图像压缩、图 像识别、视频分析等方面。

控制与自动化

DSP芯片在控制与自动化领域 中广泛应用于电机控制、智能 仪表、无人机控制等方面。

02

DSP芯片的发展历程

第一代DSP芯片

总结词

简单计算能力

详细描述

第一代DSP芯片主要提供简单的计算能力,用于处理简单的数学运算和逻辑操 作。它们主要用于控制和监视系统,如工业自动化和过程控制。

图像处理领域的应用案例

01

02

03

图像处理

DSP芯片可以对图像进行 各种处理,如滤波、增强 、色彩校正等,用于改善 图像质量和效果。

视频编解码

DSP芯片能够高效地实现 视频编解码算法,用于视 频会议、视频监控等应用 场景。

3D图形渲染

DSP芯片可以加速3D图形 渲染,提高游戏和虚拟现 实应用的性能和流畅度。

第二代DSP芯片

总结词

增强计算能力

详细描述

第二代DSP芯片在计算能力上有了显著提升,能够处理更复杂的算法和信号处理 任务。它们广泛应用于通信、音频处理、图像处理等领域。

第三代DSP芯片

总结词

高性能与低功耗

详细描述

第三代DSP芯片追求高性能与低功耗的平衡,以满足移动设备和嵌入式系统的需求。它们具备更高的计算密度和 更低的功耗,适用于各种便携式电子产品和物联网设备。

DSP芯片的算法及应用

01

,

02

St经济 on质 events such on,4 thestate on fir骝 have st on on,:, indentation stastic

03

circuit on,摇头 that circuit toSt stIST,叟 an, Maj that circuit

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

本章内容: 3.1 中央处理器 3.2 寻址方式 3.3 C28x DSP指令系统

2017/10/28

1

3.1 中央处理器

1. CPU结构

C28x DSP的中央处理器(CPU)结构包括三个部分: CPU内核、仿真逻辑单元和CPU信号 。

C28x CPU组成概念框图

4

C28x的CPU主要由总线、CPU寄存器、程序地址发 生器和控制逻辑、地址寄存器算术单元(ARAU)、算术逻 辑单元(ALU)、乘法器和移位器等逻辑部件组成,还包括 指令队列和指令译码单元、中断处理逻辑等。 ALU为32位的运算逻辑单元,主要执行算术运算和 布尔运算。在运算之前,ALU从寄存器、数据存储器或 程序控制逻辑单元接收数据,然后进行运算,最后把结果 存入寄存器或数据存储器中。 32位的乘法器,可执行32×32位的补码乘法,并产生 64位的结果。乘法器采用32位乘数寄存器(XT,)、32位乘积 寄存器(P)和32位累加器(ACC)。CPU的移位器实现对操作 数的移位操作。

2017/10/28 5

TMS320F2812 / TMS320F2810

Most Powerful - Most Integrated Dual Function Digital Signal Controller High-Performance CPU (C28x

Code security

128Kw Flash + 2Kw OTP XINTF 18Kw RAM 4Kw Boot ROM Event Mgr A Event Mgr B

Control Ports

McBSP CAN 2.0B SCI-UART A SCI-UART B SPI

Event Managers Ultra-Fast 12-bit ADC 12.5 MSPS throughput Dual sample&holds enable simultaneous sampling Auto Sequencer, up to 16 conversions w/o CPU

Communications Ports

Multiple standard communication ports provide simple interfaces to other components 6

2017/10/28

Most C/C++ Efficient 32-bit DSP Core

TM

DSP Core)

150MIPS performance Single cycle 32 x32-bit MAC (or dual 16 x16 MAC) Very Fast Interrupt Response Single cycle read-modified-write F24x/LF240x Source Code Compatible

32x32 bit Multiplier

Three 32-bit timers support multiple control loops / time bases.

Single cycle read-modified-write in any memory location and 32-bit registers improve control algorithm efficiency Real-time JTAG debug shortens development cycle

2017/10/28 2

仿真逻辑单元的主要功能是监视和控制 CPU以及其他外设的工作情况,并实现对设备 的测试和调试功能。

CPU的信号主要包括4种: ① 存储器接口信号 ② 时钟和控制信号 ③ 复位和中断信号 ④ 仿真信号

2017/10/28

3

F281x DSP的CPU 单元结构框图

2017/10/28

RMW Atomic ALU

32-bit Timers (3) 32-bit Register File

Real-Time JTAG

Fast & flexible interrupt management significantly reduce interrupt latency

Code compatible with the TMS320C24x™ DSP family

Memory Bus Peripheral Bus

12-Bit ADC

Memory Control Sub-System Peripherals

Fast program execution out of both RAM and Flash memory 100-120 MIPS with Flash Acceleration Technology 150 MIPS out of RAM for time-critical code

7

2017/10/28

2812 DSP 总线结构

多组总线并行机制。 程序读、数据读、数据写三种情况 。 内部地址总线,三组 Address Bus: 程序读地址总线PAB (Program Address Bus)(0:21) 22根,4 MW。 数据读地址总线DRAB (Data Read Address Bus)(0:31) 32位。 数据写地址总线DWAB (Data Write Address Bus)(0:31)。 内部数据总线:三组 Data Bus: 程序读数据总线PRDB (Program Read Data Bus)(0:31)。 数据读数据总线DRDB(0:31)。 数据/程序写数据总线DWDB(0:31) 数据写入DM和PM。 外部16位数据总线Data(0:15) / 19位地址总线Address(0:18) 为单一形式 。

Interrupt Management

C28xTM DSP Core

C28xTM 32-bit DSP

Single-cycle 32-bit multiplier makes computationally intenபைடு நூலகம்ive control algorithms more efficient

Watchdog

GPIO

Interrupt Management

150 MIPs C28xTM 32-bit DSP 32x32-bit Multiplier 32-bit Timers (3) Real-Time JTAG 32-bit Register File RMW Atomic ALU