电子信息_ 基于verilog两位LED数码管显示译码电路设计

数电实验报告2.1—基于Verilog HDL显示译码器设计

<基于Verilog HDL显示译码器设计>实验报告学生姓名:班级学号:指导老师:<实验报告内容>一、实验名称:基于Verilog HDL 显示译码器设计二、实验学时:4学时 三、实验目的:进一步掌握QuartusII 软件逻辑电路设计环境及Verilog HDL 的基本语法,熟悉设计流程及思路。

掌握显示译码器的工作原理及应用。

(提示:本实验将涉及到verilog 的条件语句(如if …else, case ….end case, for ….等)、赋值语句(如assign 等)和二进制变量位宽的定义等内容,请大家实验前做好本部分预习和自学,可参考本课本第九章内容,也可自行查找有关Verilog 设计基础的相关内容,推荐参考书:北京航空航天出版社,夏宇闻编著 )。

通过对所设计逻辑电路功能仿真,分析所设计电路逻辑功能是否正确,掌握逻辑功能仿真的方法。

四、实验内容:基于verilog 的显示译码器逻辑设计及功能仿真五、实验原理:(1)半导体发光二极管(LED )数码显示器:半导体发光二极管数码显示器由7(或8)个LED 排成“日”字形,称为七段(或八段),封装成数码管,如错误!未找到引用源。

所示。

LED 数码管内部有共阴极和共阳极两种接法。

如错误!未找到引用源。

(2)常用显示译码器管脚功能(74LS148):LCD —七段显示译码器:介绍常用的74LS148七段显示译码器,图 3为74LS4874LS48(a )图 1 图 2 CC fg a bcd e BI 7123456图 3(3)74LS48的逻辑功能:如表1:表1其译码器输出(Ya~Yg)是高电平有效,适用于驱动共阴极LED数码管,显示的字形表中所示。

因其译码器输出端的内部有上拉电阻(是2K的限流电阻),因此在与LED管连接时无需再外接限流电阻。

具体功能介绍及内部设计图,请自行上网查阅74LS48的DATASHEET。

EDA实验FPGAvhdl两个数码管显示12进制

EDA实验FPGAvhdl两个数码管显⽰12进制⼀、实验⽬的学习时序电路的设计,特别是计数器的设计、仿真和硬件测试,进⼀步熟悉VHDL设计技术。

⼆、实验要求1、⽤VHDL语⾔设计4位加法计数器为同步⼗⼆进制计数器,并具有异步清零,同步使能的功能。

2、⽤EDA6000实验仪进⾏实验结果的验证。

三、实验原理设计带有异步复位和同步时钟使能的4位加法计数器,所谓同步或异步都是相对时钟⽽⾔的。

不依赖于时钟⽽有效的信号称为异步信号,反之为同步信号。

因此,在使⽤VHDL语⾔设计该电路时,要注意时钟的使能信号发⽣时刻,以及进程语句的启动信号处理。

四、实验内容1、⽤VHDL语⾔编写出含异步清零和同步时钟使能的加法器电路程序;通过QuartysⅡ进⾏编辑、编译、综合、适配、仿真测试,给出其所有的信号的时序仿真波形。

2、按实验要求锁定管脚,重新综合。

3、在EDA6000软件中建⽴实验模式。

4、下载设计⽂件;硬件验证计数器的⼯作性能。

5、熟悉嵌⼊式逻辑分析仪,使⽤Signaltag 2对此计数器进⾏实时测试。

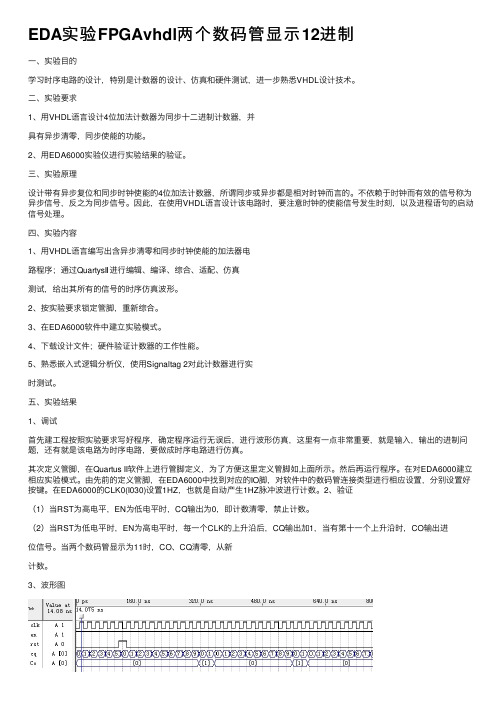

五、实验结果1、调试⾸先建⼯程按照实验要求写好程序,确定程序运⾏⽆误后,进⾏波形仿真,这⾥有⼀点⾮常重要,就是输⼊,输出的进制问题,还有就是该电路为时序电路,要做成时序电路进⾏仿真。

其次定义管脚,在Quartus II软件上进⾏管脚定义,为了⽅便这⾥定义管脚如上⾯所⽰。

然后再运⾏程序。

在对EDA6000建⽴相应实验模式。

由先前的定义管脚,在EDA6000中找到对应的IO脚,对软件中的数码管连接类型进⾏相应设置,分别设置好按键。

在EDA6000的CLK0(I030)设置1HZ,也就是⾃动产⽣1HZ脉冲波进⾏计数。

2、验证(1)当RST为⾼电平,EN为低电平时,CQ输出为0,即计数清零,禁⽌计数。

(2)当RST为低电平时,EN为⾼电平时,每⼀个CLK的上升沿后,CQ输出加1,当有第⼗⼀个上升沿时,CO输出进位信号。

当两个数码管显⽰为11时,CO、CQ清零,从新计数。

两位数码管显示电路

EDA设计论文题目学院专业班级学生姓名指导教师2016年 1 月10 日目录摘要 (3)Abstract (4)第1章绪论 (5)1.1 概述 (5)1.2 设计的目的 (5)1.3 设计的基本内容 (1)第2章 EDA、Verilog HDL简介 (2)2.1 EDA技术 (2)2.1.1 EDA技术的概念 (2)2.1.2 EDA技术的特点 (2)2.1.3 EDA设计流程 (2)2.2 硬件描述语言(Verilog HDL) (7)2.2.1 Verilog HDL简介 (3)2.2.2 Verilog HDL语言的特点 (3)第3章两位数码管的动态显示电路的设计过程 (4)3.1 系统需求分析 (4)3.2 设计原理 (4)3.3 MAXII晶体管说明 (5)3.4 编写代码 (6)3.5 管脚分配 (8)第4章系统仿真 (9)结论 (10)参考文献 (11)附录 (12)致谢 (13)\摘要在信息时代的今天,单片机技术应用越来越广泛,涉及各行各业,也渗透到人们的日常生活之中,如洗衣机、空调、冰箱等的控制系统,就可以用单片机实现。

为了让人们很直观的了解相关设备当前的工作状态,很多时候需要将当前的时间、温度、工作程序等状态通过数码管显示出来,这就涉及到单片机的数码管显示技术。

在实际应用中,单片机的数码管显示,正确、高效应用数码管显示技术设计成功与否的一个关键问题之一。

本文介绍了通过学习版开设计两位数码管的显示十六进制数。

采用汇编进行编程,可以实现从00到FF的十六进制数的循环显示。

在Quartus Ⅱ软件平台上,完成了两位数码管的显示电路的设计。

采用Verilog HDL硬件描述语言描述两位数码管的显示电路,完成对电路的功能仿真。

关键词:两位数码管的显示 Quartus Ⅱ状态机循环AbstractIn the information age today, SCM technology is applied more and more widely, involved in all walks of life, but also penetrate into people's daily life, such as washing machines, air conditioners, refrigerators and other control system, you can with MCU. In order to let people very intuitive understanding of the relevant equipment current state, most of the time to the current time, temperature, and work procedures state through the digital tube display, which involves the MCU digital tube display technology. In practical application, the digital tube display of single chip microcomputer is generally used in dynamic display mode, and it is one of the key problems in the design of dynamic display technology with correct and high efficiency. This paper introduces the dynamic display of the two bit digital tube through the learning version of the sixteen digit number. Assembly for programming, can be achieved from 1 to F sixteen decimal number of automatic display. On Quartus II software platform, the design of dynamic display circuit of two bit digital tube is completed. The HDL Verilog hardware description language is used to describe the dynamic display circuit of two bit digital tube, and the function simulation of the circuit iscompleted.Keywords: Dynamic display of multi bit digital tube Quartus Ⅱ State machine Circulat第1章绪论1.1 概述数码管是一类显示屏通过对其不同的管脚输入相对的电流,会使其发亮,从而显示出数字能够显示时间、日期、温度等所有可用数字表示的参数。

数码管显示的Verilog代码

2'b01: AN<=4'b1011;

2'b10: AN<=4'b1101;

2'b11: AN<=4'b1110;

default:AN<=4'b1111;

endcase

end

always @(*)

begin

case (Data[3:0])

0:seg[7:0]<=8'b00000011;

begin

case(BIT_SEL)

0: Data_4[3:0] <= Data[15:12];

1: Data_4[3:0] <= Data[11:8];

2: Data_4[3:0] <= Data[7:4];

3: Data_4[3:0] <= Data[3:0];

default:Data_4[3:0] <= Data[3:0];

output [7:0] SEG

);

reg[3:0] Data_4;

reg[1:0] BIT_SEL;

reg[15:0] cnt;

SMG_1 SMG_i(SEG,AN,BIT_SEL,Data_4);

always @(posedge CLK or posedge CLR)

if(CLR)

begin

cnt<=16'b0;

控制每个数码管显示对应位的数字begincase

数码管显示的Verilog代码

//用4个数码管显示一个16位二进制数据Data,每个数码管显示各自的数据0.2ms

module SMG_4(

两位数码管显示电路

EDA设计论文题目学院专业班级学生姓名指导教师2016年 1 月10 日目录摘要 (3)Abstract (4)第1章绪论 (5)1.1 概述 (5)1.2 设计的目的 (5)1.3 设计的基本内容 (1)第2章 EDA、Verilog HDL简介 (2)2.1 EDA技术 (2)2.1.1 EDA技术的概念 (2)2.1.2 EDA技术的特点 (2)2.1.3 EDA设计流程 (2)2.2 硬件描述语言(Verilog HDL) (7)2.2.1 Verilog HDL简介 (3)2.2.2 Verilog HDL语言的特点 (3)第3章两位数码管的动态显示电路的设计过程 (4)3.1 系统需求分析 (4)3.2 设计原理 (4)3.3 MAXII晶体管说明 (5)3.4 编写代码 (6)3.5 管脚分配 (8)第4章系统仿真 (9)结论 (10)参考文献 (11)附录 (12)致谢 (13)\摘要在信息时代的今天,单片机技术应用越来越广泛,涉及各行各业,也渗透到人们的日常生活之中,如洗衣机、空调、冰箱等的控制系统,就可以用单片机实现。

为了让人们很直观的了解相关设备当前的工作状态,很多时候需要将当前的时间、温度、工作程序等状态通过数码管显示出来,这就涉及到单片机的数码管显示技术。

在实际应用中,单片机的数码管显示,正确、高效应用数码管显示技术设计成功与否的一个关键问题之一。

本文介绍了通过学习版开设计两位数码管的显示十六进制数。

采用汇编进行编程,可以实现从00到FF的十六进制数的循环显示。

在Quartus Ⅱ软件平台上,完成了两位数码管的显示电路的设计。

采用Verilog HDL硬件描述语言描述两位数码管的显示电路,完成对电路的功能仿真。

关键词:两位数码管的显示 Quartus Ⅱ状态机循环AbstractIn the information age today, SCM technology is applied more and more widely, involved in all walks of life, but also penetrate into people's daily life, such as washing machines, air conditioners, refrigerators and other control system, you can with MCU. In order to let people very intuitive understanding of the relevant equipment current state, most of the time to the current time, temperature, and work procedures state through the digital tube display, which involves the MCU digital tube display technology. In practical application, the digital tube display of single chip microcomputer is generally used in dynamic display mode, and it is one of the key problems in the design of dynamic display technology with correct and high efficiency. This paper introduces the dynamic display of the two bit digital tube through the learning version of the sixteen digit number. Assembly for programming, can be achieved from 1 to F sixteen decimal number of automatic display. On Quartus II software platform, the design of dynamic display circuit of two bit digital tube is completed. The HDL Verilog hardware description language is used to describe the dynamic display circuit of two bit digital tube, and the function simulation of the circuit iscompleted.Keywords: Dynamic display of multi bit digital tube Quartus Ⅱ State machine Circulat第1章绪论1.1 概述数码管是一类显示屏通过对其不同的管脚输入相对的电流,会使其发亮,从而显示出数字能够显示时间、日期、温度等所有可用数字表示的参数。

EDA技术及应用—基于FPGA的电子系统设计:基于Verilog hdl的数字电路设计

10100

1111

15

10101

8421BC 余三码 D码

0000

0011

0001

0100

0010

0101

0011

0110

0100

0111

0101

1000

0110

1001

0111

1010

1000

1011

1001

1100

-

-

-

-

-

-

-

-

-

-

-

-

4位格雷码

0000 0001 0011 0010 0110 0111 0101 0100 1100 1101 1111 1110 1010 1011 1001 1000

4'b0011:a_to_g=7'b1111001; //显示3

4'b0100:a_to_g=7'b0110011; //显示4

4'b0101:a_to_g=7'b1011011; //显示5

4'b0110:a_to_g=7'b1011111; //显示6

4'b0111:a_to_g=7'b1110000; //显示7

4: y= {d[2:0],d[3]}; // rol

5: y= {d[3],d[3:1]}; // asr

6: y= {d[1:0],d[3:2]}; // ror2

7: y= d;

// noshift

default: y = d;

图6-2 基本门电路仿真结果

综合结果如图6-3所示。

图6-3 基本门电路综合结果

2、 三态逻辑电路

两位数码管显示设计

两位数码管显示设计摘要:本设计旨在设计一套能够在两位数码管上显示不同数字的电路。

通过使用逻辑门、计数器和驱动器等组合电路,以及基本的数字逻辑知识,通过编写Verilog代码实现数字的显示和计数。

关键词:两位数码管、逻辑门、计数器、驱动器、Verilog代码一、引言数码管(Digital Display)是一种用于显示数字和字母的设备,它将输入的信号转换为相应的数字或字符,并在屏幕上显示出来。

本设计中,我们使用两位数码管,通过设计适当的电路和使用相应的逻辑门、计数器和驱动器等组合电路,以及编写Verilog代码,实现数字的显示和计数。

二、设计思路1.利用计数器设计模块来实现数字的计数功能。

通过适当的控制信号,将从0计数到9,并在10时重新计数。

计数器的输出作为数码管的输入。

2.设计一个驱动器模块,将计数器模块的输出转换为适合于数码管显示的控制信号。

通过逻辑门的组合,将每个数码管的数码按照不同的段(段是数码管上的一个小灯,用于显示数字的每个部分)进行控制。

3. 编写Verilog代码,将计数器模块和驱动器模块进行组合。

通过适当的端口和输入/输出信号,将两个模块连接在一起,实现数字的显示和计数。

三、设计实现1.计数器模块设计module counterinput clk, // 时钟信号output reg[3:0] count // 计数器的输出beginif (count == 4'b1001) // 9时重新计数count <= 4'b0000;elsecount <= count + 1; // 计数器自增endendmodule2.驱动器模块设计module decoderinput reg[3:0] count, // 指示要显示的数字output reg a, b, c, d, e, f, g // 段待显示数字begincase(count)4'b0000 : begin a = 1; b = 1; c = 1; d = 1; e = 1; f = 1; g = 0; end // 数字04'b0001 : begin a = 0; b = 1; c = 1; d = 0; e = 0; f = 0; g = 0; end // 数字14'b0010 : begin a = 1; b = 1; c = 0; d = 1; e = 1; f = 0; g = 1; end // 数字24'b0011 : begin a = 1; b = 1; c = 1; d = 1; e = 0; f = 0; g = 1; end // 数字34'b0100 : begin a = 0; b = 1; c = 1; d = 0; e = 0; f = 1; g = 1; end // 数字44'b0101 : begin a = 1; b = 0; c = 1; d = 1; e = 0; f = 1; g = 1; end // 数字54'b0110 : begin a = 1; b = 0; c = 1; d = 1; e = 1; f = 1; g = 1; end // 数字64'b0111 : begin a = 1; b = 1; c = 1; d = 0; e = 0; f = 0; g = 0; end // 数字74'b1000 : begin a = 1; b = 1; c = 1; d = 1; e = 1; f = 1; g = 1; end // 数字84'b1001 : begin a = 1; b = 1; c = 1; d = 1; e = 0; f = 1; g = 1; end // 数字9default : begin a = 0; b = 0; c = 0; d = 0; e = 0; f = 0; g = 0; end // 默认显示为空白endcaseendendmodule3.组合计数器和驱动器模块module displayinput clk, // 时钟信号output reg[3:0] count, // 计数器模块的输出output reg a, b, c, d, e, f, g // 驱动器模块的输出counter counter_inst(.clk(clk), .count(count)); // 实例化计数器模块decoderdecoder_inst(.count(count), .a(a), .b(b), .c(c), .d(d), .e(e), . f(f), .g(g)); // 实例化驱动器模块endmodule四、实验结果与分析通过连接计数器和驱动器模块,使用相同的时钟信号,即可实现数字计数和显示的功能。

基于Verilog的数字电路设计与模拟

基于Verilog的数字电路设计与模拟数字电路设计是现代电子领域中至关重要的一部分,它涉及到数字系统中各种逻辑门、寄存器、计数器等元件的设计和实现。

而Verilog作为一种硬件描述语言,被广泛应用于数字电路设计中,能够帮助工程师们更高效地进行数字电路的建模、仿真和验证。

本文将介绍基于Verilog的数字电路设计与模拟的相关内容,包括Verilog语言基础、数字电路设计流程、常用的数字电路元件设计以及Verilog仿真工具的使用等方面。

Verilog语言基础Verilog是一种硬件描述语言(HDL),它可以描述数字系统中的行为和结构,是数字电路设计中常用的编程语言之一。

Verilog包括结构化Verilog和行为Verilog两种描述方式,结构化Verilog主要用于描述数字系统的结构,而行为Verilog则用于描述数字系统的行为。

在Verilog中,最基本的单元是模块(module),一个模块可以包含输入端口、输出端口以及内部逻辑。

示例代码star:编程语言:verilogmodule and_gate(input a, input b, output y);assign y = a & b;endmodule示例代码end上面是一个简单的AND门模块的Verilog描述,其中input表示输入端口,output表示输出端口,assign用于赋值操作。

通过这样的描述,我们可以实现各种逻辑门、寄存器、计数器等数字电路元件。

数字电路设计流程在进行数字电路设计时,通常需要遵循一定的设计流程,以确保设计的正确性和可靠性。

典型的数字电路设计流程包括需求分析、概念设计、详细设计、验证和实现等阶段。

在Verilog中,我们可以通过编写相应的代码来完成这些阶段的工作。

需求分析:明确设计的功能需求和性能指标。

概念设计:根据需求设计数字系统的整体结构和功能模块。

详细设计:对各个功能模块进行详细设计,包括内部逻辑和接口定义。

Verilog?HDL数码管显示

Verilog HDL数码管显示这个没什么说的,2个数码管显示数字一样0~F;特权的程序如下:module led_seg7(clk,rst_n,sm_cs1_n,sm_cs2_n,sm_db);input clk; // 50MHzinput rst_n; // 复位信号,低有效output sm_cs1_n,sm_cs2_n; //数码管片选信号,低有效output[6:0] sm_db; //7段数码管(不包括小数点)reg[24:0] cnt; //计数器,最大可以计数到2的25次方*20ns=640msalways @ (posedge clk or negedge rst_n)if(!rst_n) cnt <= 25'd0;else cnt <= cnt+1'b1; //循环计数reg[3:0] num; //显示数值0000~1111(即:0~F)always @ (posedge clk or negedge rst_n)if(!rst_n) num <= 4'd0; //TZ无论几进制的0都是全0;呵呵else if(cnt == 24'hffffff) num <= num+1'b1; //每640ms增一//---------------设定数码管显示参数-------------------------------parameter seg0 = 7'h3f,seg1 = 7'h06,seg2 = 7'h5b,seg3 = 7'h4f,seg4 = 7'h66,seg5 = 7'h6d,seg6 = 7'h7d,seg7 = 7'h07,seg8 = 7'h7f,seg9 = 7'h6f,sega = 7'h77,segb = 7'h7c,segc = 7'h39,segd = 7'h5e,sege = 7'h79,segf = 7'h71;//-------------------------------------------------------------------------------reg[6:0] sm_dbr; //7段数码管(不包括小数点)always @ (num)case (num) //NUM值显示在两个数码管上4'h0: sm_dbr <= seg0;4'h1: sm_dbr <= seg1;4'h2: sm_dbr <= seg2;4'h3: sm_dbr <= seg3;4'h4: sm_dbr <= seg4;4'h5: sm_dbr <= seg5;4'h6: sm_dbr <= seg6;4'h7: sm_dbr <= seg7;4'h8: sm_dbr <= seg8;4'h9: sm_dbr <= seg9;4'ha: sm_dbr <= sega;4'hb: sm_dbr <= segb;4'hc: sm_dbr <= segc;4'hd: sm_dbr <= segd;4'he: sm_dbr <= sege;4'hf: sm_dbr <= segf;default: ;endcaseassign sm_db = sm_dbr;assign sm_cs1_n = 1'b0; //数码管1常开assign sm_cs2_n = 1'b0; //数码管2常开endmodule。

实验verilogHDL设计编码器译码器

实验六Verilog设计编码器/译码器一、实验目的1、进一步掌握基本组合逻辑电路的实现方法;2、进一步了解always语句的设计方法;3、学习用case语句设计数据优先编码器/译码器的实现方法;4、学习用case语句设计设计总线/缓冲器的实现方法。

二、实验内容(选择其中2个以上完成)1、用always语句设计并仿真2-4译码器d24_seq.v,其真值表如下表所示。

2、用Verilog HDL设计法设计并仿真8-3线优先编码器encode.v,其真值表如下表所示。

3、用Verilog设计双向总线缓冲器电路,当EN=1且DIR=0时输出A=B,EN=1且DIR=1时输出B=A,否则输出高阻‘Z’,文件命名为bibus.v。

4、用Verilog语言编写3-8译码器的程序,符号如图所示,其中g1,g2a,g2b是使能控制输入端,当g1为高电平,g2a,g2b为低电平时,译码器工作,其他状态时,译码器被禁止工作,全部输出均为无效电平(高电平‘1’)。

当CBA=000时,Y0N=0,其余为1;当CBA=001时,Y1N=0,其余为1;依此类推,文件命名为decoder3_8.v。

(选做)5、8段译码器真值表如下所示,其中输入显示字符data为4位二进制,输出seg为8位共阴极码,文件命名为dec7s.v。

(选做)6、3线-8线译码器的元件符号如图所示,ENA是译码器的使能控制输入端,当ENA=1时,译码器不能工作,7线输出Y[7..0]=11111111(译码器的输出有效电平为低电平);当ENA=0时,译码器工作。

C、B、A是3线数据输入端,译码器处于工作状态时,当CBA=000时,Y[7..0]=11111110(即Y[0]=0);当CBA=001时,Y[7..0]=11111101(即Y[1]=0);依此类推,文件命名为decoder.v。

(选做)三、实验步骤1、建立电路的Verilog HDL文件,进行编译,直到编译无误。

项目五 用Verilog HDL实现译码器功能电路教学设计[1页]

![项目五 用Verilog HDL实现译码器功能电路教学设计[1页]](https://img.taocdn.com/s3/m/1664245af342336c1eb91a37f111f18583d00c24.png)

1)参照十六进制数码管的功能,理清输入输出的关系;

2)在Quartus II中,应用Verilog HDL编制译码电路程序实现驱动十六进制数码显示管功能;

3)建立了仿真波形,运行仿真结果并分析;

4)能正确处理调试过程中遇到的问题;

2. 知识与技能准备:

项目一用Verilog HDL实现译码器功能模块教学设计

课程名称

数字电子技术及应用

学习领域五:可编程逻辑控制技术

项目五:用Verilog HDL实现译码器功能

计划学时数:8课时;理论教学3课时,实践教学4课时,汇报与评价1课时

教学目的:以Verilog HDL实现译码器功能为驱动,引导讲授可编程逻辑器件、Quartus II软件的使用、Verilog HDL编程的方法、仿真的实现等,培养学生在Quartus II中实现对电路编程并仿真实现相应的逻辑功能的能力,为CPLD的应用设计打下扎实基础。

教学资源:

1)任务报告;2)多媒体资料;3)数据手册

考核方式:

过程化考核

教学内容:

任务引入:译码器是多输入多输出组合逻辑电路器件。数码显示电路在各种数字测量仪表和各种数字系统中使用广泛,是数字设备不可缺少的部分。可以采用显示译码器将二进制数转换成对应的七段码或八段码,驱动数码管。本项目通过在Quartus II软件中,用Verilog HDL语言编写程序代码,实现这个显示译码器的功能,为今后需要在CPLD上进一步开发复杂功能的电路打下坚实基础。用Verilog HDL实现译码器功能模块的要求如下:

1)译码ห้องสมุดไป่ตู้工作原理;

2)译码显示线路原理分析;

3)Quartus II软件应用;

利用51单片机、BCD译码芯片和两位LED构成一个数码管扫描显示系统,两个数码管同时循环显示0~9。

****** 大学电子设计应用软件训练总结报告学生姓名:*系、专业:*班级学号:*指导教师:*训练时间:*电子信息工程学院电子设计应用软件训练任务【训练任务】:1、熟练掌握PROTEUS软件的使用;2、按照设计要求绘制电路原理图;3、能够按要求对所设计的电路进行仿真;【基本要求及说明】:1、按照设计要求自行定义电路图纸尺寸;2、设计任务如下:利用51单片机、BCD译码芯片和两位LED构成一个数码管扫描显示系统,两个数码管同时循环显示0~9。

3、按照设计任务在Proteus 6 Professional中绘制电路原理图;4、根据设计任务的要求编写程序,在Proteus下进行仿真,实现相应功能。

【按照要求撰写总结报告】指导教师年月日负责教师年月日学生签字年月日成绩评定表摘要该专业是前沿学科,现代社会的各个领域及人们日常生活等都与电子信息技术有着紧密的联系。

全国各地从事电子技术产品的生产、开发、销售和应用的企事业单位很多,随着改革步伐的加快,这样的企事业单位会越来越多。

为促进市场经济的发展,培养一大批具有大专层次学历,能综合运用所学知识和技能,适应现代电子技术发展的要求,从事企事业单位与本专业相关的产品及设备的生产、安装调试、运行维护、销售及售后服务、新产品技术开发等应用型技术人才和管理人才是社会发展和经济建设的客观需要,市场对该类人才的需求越来越大。

为此电子信息工程专业的人才有着广泛的就业前景,毕业生可从事电子设备、信息系统和通信系统的研究、设计、制造、应用和开发工作。

目录一、任务说明 (1)1.1 专业介绍 (1)1.2 专业背景与市场预测 (1)1.3 本课题分析 (1)二、绘制原理图 (2)2.1 Proteus软件介绍 (2)2.2 原理图绘制说明 (2)2.3 原理图绘制步骤 (3)三、程序编译说明及程序流程图 (6)3.1 Main程序说明 (6)3.2 初始化子程序说明 (6)3.3 display(uchar tmp)子程序说明 (7)3.4 延时子程序说明 (8)3.5 中断子程序说明 (9)四、Proteus仿真说明 (11)4.1 导入仿真文件 (11)4.2 进行仿真 (12)五、课程设计体会及合理化建议 (14)致谢 (16)一、任务说明1.1专业介绍电子信息工程是一门应用计算机等现代化技术进行电子信息控制和信息处理的学科,主要研究信息的获取与处理,电子设备与信息系统的设计、开发、应用和集成。

基于Verilog语言方案设计书的数码管电子钟

EDA技术及其嵌入式系统设计课程设计基于MAX+PLUSII平台的多功能数字钟设计报告指导教师:专业:姓名:学号:目录一、序言 (2)二、实验要求及目的 (2)三、实验原理 (3)四、运行环境 (3)五、运行过程 (3)六、实验结果 (8)七、各模块源程序 (8)八、心得体会 (16)参考文献 (16)基于MAX+PLUSII数字钟的实现一序言电子设计自动化(EDA Electronic Design Automation)技术是一种以计算机作为工作平台,以EDA软件工具为开发环境,以硬件描述语言和原理图描述为设计入口,以可编程逻辑器为实验载体,以ASIC、SOC和SOPC嵌入式系统为设计目标,以数字系统系统设计为应用方向的电子产品自动化设计技术。

它是融入了电子技术、计算机技术、信息处理技术、智能化技术等最新成果而开发的高新技术,是现代电子系统设计、制造不可缺少的技术。

EDA技术涉及面广,包括描述语言、软件、硬件等方面知识。

它的电子仿真软件的仿真功能强大,具有完备的文件库,具有选用元器件创建电路、仿真模拟运行电路的功能,并且在输入信号的加入、输出信号的显示上能完全模拟实际和调制过程中的各种波型和操作过程。

因此,EDA可作为辅助实验教育和实验训练的手段之一,以弥补在经费和实验仪器、元器件缺乏情况下的不足,并可节约材料消耗和减少仪器故障,通过仿真可熟悉常用电子仪器的使用方法和测量方法,并锻炼学生电路设计和调试能力,提高学生的分析与解决问题、故障排除的能力,进一步挖掘学生的开发和创新能力。

Verilog HDL是一种优秀的硬件描述语言,尤其在ACIC设计领域更是占主导地位。

Verilog HDL与C语言有许多相似之处,并继承和借鉴了C语言的多种操作符和语法结构,有C语言基础的人很快就能够学习并使用该语言。

目前国外教案将Verilog HDL作为主要的硬件描述语言,在国内,该语言的使用人数也逐渐增多。

自上而下的电子系统设计是一种传统的设计思路。

利用51单片机、BCD译码芯片和两位LED构成一个数码管扫描显示系统,两个数码管同时循环显示0~9。

****** 大学电子设计应用软件训练总结报告学生姓名:*系、专业:*班级学号:*指导教师:*训练时间:*电子信息工程学院电子设计应用软件训练任务【训练任务】:1、熟练掌握PROTEUS软件的使用;2、按照设计要求绘制电路原理图;3、能够按要求对所设计的电路进行仿真;【基本要求及说明】:1、按照设计要求自行定义电路图纸尺寸;2、设计任务如下:利用51单片机、BCD译码芯片和两位LED构成一个数码管扫描显示系统,两个数码管同时循环显示0~9。

3、按照设计任务在Proteus 6 Professional中绘制电路原理图;4、根据设计任务的要求编写程序,在Proteus下进行仿真,实现相应功能。

【按照要求撰写总结报告】指导教师年月日负责教师年月日学生签字年月日成绩评定表摘要该专业是前沿学科,现代社会的各个领域及人们日常生活等都与电子信息技术有着紧密的联系。

全国各地从事电子技术产品的生产、开发、销售和应用的企事业单位很多,随着改革步伐的加快,这样的企事业单位会越来越多。

为促进市场经济的发展,培养一大批具有大专层次学历,能综合运用所学知识和技能,适应现代电子技术发展的要求,从事企事业单位与本专业相关的产品及设备的生产、安装调试、运行维护、销售及售后服务、新产品技术开发等应用型技术人才和管理人才是社会发展和经济建设的客观需要,市场对该类人才的需求越来越大。

为此电子信息工程专业的人才有着广泛的就业前景,毕业生可从事电子设备、信息系统和通信系统的研究、设计、制造、应用和开发工作。

目录一、任务说明 (1)1.1 专业介绍 (1)1.2 专业背景与市场预测 (1)1.3 本课题分析 (1)二、绘制原理图 (2)2.1 Proteus软件介绍 (2)2.2 原理图绘制说明 (2)2.3 原理图绘制步骤 (3)三、程序编译说明及程序流程图 (6)3.1 Main程序说明 (6)3.2 初始化子程序说明 (6)3.3 display(uchar tmp)子程序说明 (7)3.4 延时子程序说明 (8)3.5 中断子程序说明 (9)四、Proteus仿真说明 (11)4.1 导入仿真文件 (11)4.2 进行仿真 (12)五、课程设计体会及合理化建议 (14)致谢 (16)一、任务说明1.1专业介绍电子信息工程是一门应用计算机等现代化技术进行电子信息控制和信息处理的学科,主要研究信息的获取与处理,电子设备与信息系统的设计、开发、应用和集成。

VerilogLED数码管驱动电路设计

!-实训2 LED数码管驱动电路设计与实现、实训设备、工具与要求1实训设备、工具PC电脑、FPGA开发系统、Quartus II 应用软件。

2•实训要求⑴ 每位学生独立完成项目的制作并撰写实训报告;⑵ 项目制作完成后由制作者按“验收标准”测试功能与参数,指导教师验收并登记成绩;⑶ 项目经指导教师验收后,由学生将全部实验设备整理后交指导教师验收并登记;⑷实训结束后1周内交实训报告。

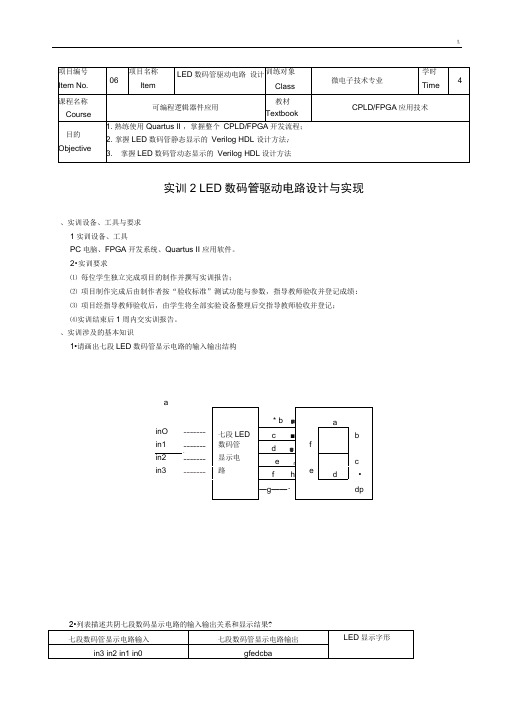

、实训涉及的基本知识1•请画出七段LED数码管显示电路的输入输出结构0000 0111111 0 0001 0000110 1 0010 1011011 2 0011 1001111 3 0100 1100110 4 0101 1101101 5 0110 1111100 6 0111 0000111 7 10001111111 8 100111001119三、实训综合电路(七段译码器电路框图)动态显示电路框图:模10计数单个数码管显示电路框图:四、实训步骤信 号clkrst led[6] led[5] led[4] led[3] led[2] led[1] led[0] sca n[3] sca n[2] sca n[1] scan[0] 引 脚8990 73 74 75 83 85 86 87 97 100 102 104 值868773747515381828396981001022•设计应用工程,将十进制的 0-9的BCD 码转换成七段数码管的显示码(组合逻辑电路)七段LED 数码管显示电路的 Verilog 代码:module qidua n_0(c nt,led );divi4:uOcintO u1 ciif.q ckcnt J O.Jlqidu3n:u2lledliyima u2e«Tiqfenpin25_u0in put [3:0] ent;output [6:0] led;reg [6:0] led;always@(c nt)begincase(c nt)4'b0001:led=7'b0000110;4'b0010:led=7'b1011011;4'b0011:led=7'b1001111;4'b0100:led=7'b1100110;4'b0101:led=7'b1101101;4'b0110:led=7'b1111100;4'b0111:led=7'b0000111;4'b1000:led=7'b1111111;4'b1001:led=7'b1101111;4'b1010:led=7'b1110111;default:led=7'b0111111;endcaseenden dmodule七段3. 设计应用工程,四个数码管依次静态显示“1”、“2”、“ 3”、“4”;module led_1(a,led);in put [1:0] a;output [10:0] led;reg [10:0] led;always@(a)beginif(a==2'b00)led<=11'b00010000110;else if(a==2'b01)led<=11'bOO1O1O11O11;else if(a==2'b10)led<=11'bO1OO1OO1111;elseled<=11'b10001100110;enden dmodule4. 设计应用工程,单个数码管完成从模10计数功能;分频器:module fen pi n25(clk,rst,clk_1hz);in put in put output clk;rst; clk_1h z;reg reg clk_1h z;[23:0] cnt;always@(posedge clk or posedge rst) beginif(rst==1'b1)cnt<=24'd0;else if(cnt==13107119)begi n cnt<=24'd0; clk_1hz<=~clk_1h z;endelsecn t<=c nt+1;enden dmodule十进制计数器:module cnt1O(rst,clk,cnt); in put rst,clk;output [3:0] cnt;reg [3:0] cnt;always@(posedge clk) beginif(rst==1'b0) cnt<=4'b000;else if(cnt==4'd9) cnt<=4'b000;elsecn t<=c nt+1;enden dmodule十进制计数器仿真波形图:LED译码器:module qidua n(cn t,led,sca n); in put [3:0] cnt;output [6:0] led;output [3:0] scan;reg [6:0] led;wire [3:0] sca n;assign scan=4'b0001;always@(c nt)begincase(c nt)4'b0001:led=7'b0000110;4'b0010:led=7'b1011011;4'b0011:led=7'b1001111;4'b0100:led=7'b1100110;4'b0101:led=7'b1101101;4'b0110:led=7'b1111100;4'b0111:led=7'b0000111;4'b1000:led=7'b1111111;4'b1001:led=7'b1101111;4'b1010:led=7'b1110111;default:led=7'b0111111; endcase end en dmoduleV*ln* )PE209 *40? 2609 M309 nENam e 6.35&.3; 1[+j cntB 0C ; ;0D01 X 0010 ) (0011 冥卫100 ) (oioi X ouo ) ;0111 X IODO国ledB Oil 50111liXooooiioXioiioiiXiooiiiiXiiooiioXiioiioiXiiiiiooXooooiiiXuiuif13|±j sc anA [ ■LU顶层电路Verilog HDL 代码: module cn t1Oled(rst,clk,led,sca n); in put rst;in put clk; output [6:0] led; output [3:0] scan; wire [3:0] cnt; wire [6:0] led; wire [3:0] sca n;fenpin25 cn t10 qidua n u0(.clk(clk),.rst(rst),.clk_1hz(clk_1hz));u1(.clk(clk_1hz),.rst(rst),.cnt(c nt));u2(.c nt(c nt),.led(led),.sca n( sca n));en dmodule框图:output scik; wire scik;C]5. 设计应用工程,LED 数码管动态显示“ 1, 2, 3, 4”,完成Verilog HDL 设计;分频器:module div24(clk,rst,sclk); in putrst; in putclk;fenpin25 u0cnilDulqidu8n:u2reg [23:0] cnt;always@(posedge clk) beginif(rst==1'b0) cnt<=24'd0;elsecn t<=c nt+1;endassig n sclk=c nt[23]; en dmodule二位计数器:module cn t2(sclk,rst,c nt);in put sclk;in put rst;output [1:0] cnt;reg [1:0] cnt;always@(posedge sclk) beginif (rst==1'b0) cnt<=2'b00;elsecn t<=c nt+1;enden dmodule位计数器仿真波形图:LED译码器:module ledyima(c nt,led); in put [1:0] cnt;output [10:0] led;reg [10:0] led;always@(c nt)begincase(c nt)2'b00:led=11'b00010000110;2'b01:led=11'b00101011011;2'b10:led=11'b010********;2'b11:led=11'b10001100110;endcaseenden dmoduleLEDVain J ps 10.0 ns ED” ¥ns 30.0 ns 40. □ {n s &.3S A5□rO (2) exit. 田lad BB 0001[ 00X oi X~~ DC n 愆$3〔00010000110 X 001010L1011 X 010******** X 10001100110 Xot1i ■n 顶层电路Verilog HDL代码:module led_0(clk,rst,led);in put clk;in put rst;output [10:0] led;wire sclk;wire [1:0] cnt;div24 u0(.clk(clk),.rst(rst),.sclk(sclk));cn t2 u1(.sclk(sclk),.rst(rst),.cnt(cnt));ledyima u2(.c nt(cnt),.led(led));en dmodule框图:五、验收标准mtledyiirna uJ1)程序运行正常;2)仿真功能和下载功能正常;六、扩展与改进。

电子信息_ 基于verilog两位LED数码管显示译码电路设计

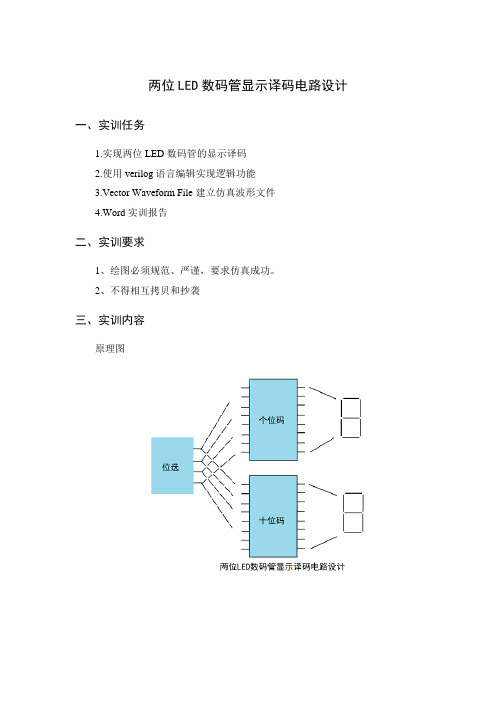

两位LED数码管显示译码电路设计

一、实训任务

1.实现两位LED数码管的显示译码

2.使用verilog语言编辑实现逻辑功能

3.Vector Waveform File建立仿真波形文件

4.Word实训报告

二、实训要求

1、绘图必须规范、严谨,要求仿真成功。

2、不得相互拷贝和抄袭

三、实训内容

原理图

步骤图

四、结果分析

数据结果

通过4个开关控制2个LED数码管显示两位数字

图表形式

仿真结果看附录(图1)

遇到的问题

在书写程序是,代码容易输错,在电脑按装驱动后,还是不能烧录到芯片

解决的方式

仔细核对,分清楚数码管是共阳的还是共阴的,驱动需要安装在cpld/fpga软件文件内才能起作用

五、实训心得

该实验的关键是如何先转化为十进制,转化为二进制后,显示输出。

这个实验编写了很久才出现结果,但是还是很有成就感,通过实验项目觉得在设计中在要多些耐心与毅力

六、附件

仿真图

图1 程序

图2

图3。

verilog 课程设计 数码管亮暗控制 演示文稿4

波形仿真

五、硬件验证

如果编译没有错误,准备下载。 由Tools -> Progammer 硬件设置:Currently selected hardware:usb 设置Mode为“JTAG” 点击“Start”,开始下载 (3)观察DE2开发板,进行验证

占空比为10%时的亮度

静态显示电路

图10-6 四位静态显示电路

动态显示电路

图10-7 四位动态显示的电路

在第一位上显示5

+5V

P2.7

0

P2.6 com1

1

P2.5 com2

1

P2.4 com3

1

P2.3 com4

1

P2.2 com5 com6

1

位驱动P2.7输出0 段驱动P0口输出“5”的 段码“10010010B” 0 1 0 0 1 0 0 1

最后经过向老师请教和咨询,终于有了正确的 方案,那就是通过分频来产生不同的占空比送 数码管来控制亮暗程度。分频可以通过case语 句产生四个档(00,01,10,11)来产生四个不 同的占空比频率,然后送给数码管,通过电平 控制数码管的显示。

经过两个星期的时间,不断地编程、调试、仿 真, 我终于完成了数码管亮度控制器的设计, 并通过下载验证了程序的正确性,这种电路在 频率合成及各类数字逻辑电路中有广泛的应用。

设计方案

一)技术方案 1、通过分频改变占空比来控制数码管的亮暗 程度 二)工作原理 通过分频改变占空比 通过case语句选择不同的占空比方案 通过拨码开关控制和选择执行哪一个case语句 根据选择不同的占空比点亮数码管

三)软件流程:

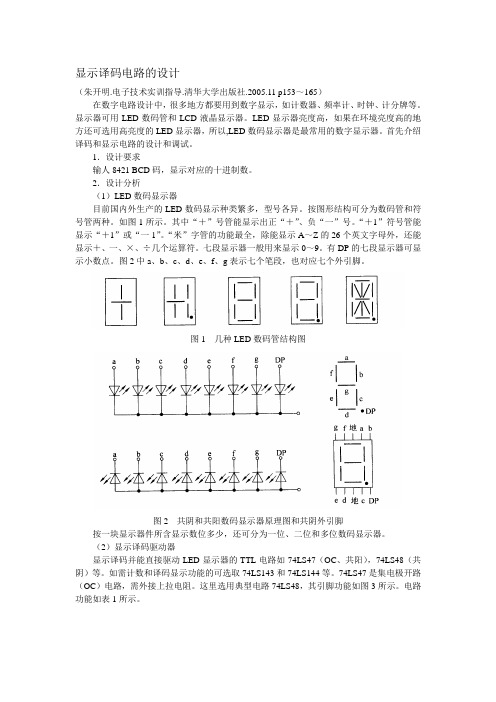

显示译码电路的设计

显示译码电路的设计(朱开明.电子技术实训指导.清华大学出版社.2005.11 p153~165)在数字电路设计中,很多地方都要用到数字显示,如计数器、频率计、时钟、计分牌等。

显示器可用LED数码管和LCD液晶显示器。

LED显示器亮度高,如果在环境亮度高的地方还可选用高亮度的LED显示器,所以,LED数码显示器是最常用的数字显示器。

首先介绍译码和显示电路的设计和调试。

1.设计要求输人8421 BCD码,显示对应的十进制数。

2.设计分析(1)LED数码显示器目前国内外生产的LED数码显示种类繁多,型号各异。

按图形结构可分为数码管和符号管两种。

如图1所示。

其中“+”号管能显示出正“+”、负“一”号。

“+1”符号管能显示“+1”或“一1”。

“米”字管的功能最全,除能显示A~Z的26个英文字母外,还能显示+、一、×、÷几个运算符。

七段显示器一般用来显示0~9。

有DP的七段显示器可显示小数点。

图2中a、b、c、d、e、f、g表示七个笔段,也对应七个外引脚。

图1 几种LED数码管结构图图2 共阴和共阳数码显示器原理图和共阴外引脚按一块显示器件所含显示数位多少,还可分为一位、二位和多位数码显示器。

(2)显示译码驱动器显示译码并能直接驱动LED显示器的TTL电路如74LS47(OC、共阳),74LS48(共阴)等。

如需计数和译码显示功能的可选取74LS143和74LS144等。

74LS47是集电极开路(OC)电路,需外接上拉电阻。

这里选用典型电路74LS48,其引脚功能如图3所示。

电路功能如表1所示。

图3 74LS48引脚功能图表1 74LS48电路功能端为灯测试端,=0时,Ya~Yg全部输出高电平,可驱动共阴数码管七笔都亮。

平时应使=1。

为灭零输人端,设置的目的是为了把不希望显示的零灭掉。

作输人使用时,称灭零输人控制端。

只要加人灭灯控制信号=0,无论A3、A2、A1、A0的状态是什么,都将被驱动的数码管熄灭。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

通过4个开关控制2个LED数码管显示两位数字

图表形式

仿真结果看附录(图1)

遇到的问题

在书写程序是,代码容易输错,在电脑按装驱动后,还是不能烧录到芯片

解决的方式

仔细核对,分清楚数码管是共阳的还是共阴的,驱动需要安装在cpld/fpga软件文件内才能起作用

5Hale Waihona Puke 实训心得该实验的关键是如何先转化为十进制,转化为二进制后,显示输出。这个实验编写了很久才出现结果,但是还是很有成就感,通过实验项目觉得在设计中在要多些耐心与毅力

两位LED数码管显示译码电路设计

一、实训任务

1.实现两位LED数码管的显示译码

2.使用verilog语言编辑实现逻辑功能

3.VectorWaveformFile建立仿真波形文件

4.Word实训报告

二、实训要求

1、绘图必须规范、严谨,要求仿真成功。?

2、不得相互拷贝和抄袭

3、实训内容

原理图

步骤图

4、结果分析

6、附件

仿真图

图1

程序

图2

图3