基于某Verilog地乒乓球游戏电路设计

基于FPGA的乒乓球游戏机设计 毕业论文

存档编号赣南师范学院科技学院学士学位论文基于FPGA的乒乓球游戏机设计系别:数信系届别: 09届专业: 电子信息工程学号: 0920085108姓名:指导老师:完成日期: 2013、5、6目录内容摘要 (1)关键词 (1)Abstract. (1)Key words (1)1引言 (2)2 开发工具简介 (2)2.1硬件描述语言—VHDL概述 (3)2.1.1VHDL语言的特点 (3)2.1.2基于VHDL的自顶向下设计 (4)2.2 Quartus II开发软件概述 (5)2.3本章小结 (6)3基于FPGA的乒乓球游戏机设计与实现 (6)3.1总体设计 (6)3.2电路总原理图 (7)3.3时钟分频设计 (9)3.4状态机设计 (9)3.4.1状态机的7种状态及状态转移 (9)3.4.2状态机/球台控制程序 (10)3.5记分牌显示电路设计 (13)3.6按键消抖、乒乓球路径显示电路设计 (14)3.7顶层实体的描述 (15)3.8本章小结 (16)4系统的调试、仿真、下载、测试 (16)4.1 调试FPGA (16)4.2系统的编译、仿真 (16)4.2.1系统编译 (16)4.2.2系统仿真 (18)4.3系统的适配、编程下载 (19)4.4本章小结 (21)5结论 (21)参考文献 (22)致谢 (23)附件1:硬件实物图 (24)附件2:程序清单 (25)内容摘要:随着电子设计自动化技术的不断发展和应用领域的扩大与深入,EDA技术在电子信息、通信、自动控制及计算机应用领域的重要性日益突出。

本文设计了基于FPGA的乒乓球游戏机设计。

用VHDL语言编程, VHDL是甚高速集成电路硬件描述语言。

目前,VHDL已成为许多设计自动化工具普遍采用的标准化硬件描述语言。

VHDL语言功能性强,覆盖面广,灵活性高,具有很好的实用性。

本文详细的简述了乒乓球游戏机的工作原理,此乒乓球游戏机由状态机、记分器、译码显示器与按键去抖等部分所组成。

乒乓球游戏机EDA课程设计完整版本

乒乓球游戏机EDA课程设计完整版本

本文主要介绍了一款基于FPGA可编程硬件的乒乓球游戏机的设计。

本文将重点介绍

如何利用FPGA技术来搭建可编程硬件电路,如何使用Verilog HDL语言来设计数字电路,如何使用Quartus II环境来实现复杂任务,以及如何利用FPGA来完成乒乓球游戏机的EDA课程设计。

首先,在设计乒乓球游戏机的FPGA可编程硬件系统时,最重要的是硬件架构设计,

选择固定板来作为FPGA控制器,能够有效地根据游戏需求控制其各个功能,保证游戏机

运行稳定性和可靠性。

为了满足乒乓球游戏机的需求,FPGA控制器引入Verilog HDL语言,用数字电路的方式进行设计,从而构建出模拟端口,使用I/O 端口对乒乓球系统进行控制,其内部控制器模块实现了所有的乒乓球游戏逻辑功能。

在设计主板的时候,FPGA

中实现的硬件电路会结合安装在主板上的器件,比如七段LED显示器、微型键盘、LED灯等,从而使乒乓球游戏机更加复杂,实现更多的功能。

接下来,使用Quartus II环境,实现乒乓球游戏机的EDA课程设计。

首先,在Quartus II中编写Verilog HDL语言编程,利用FPGA可编程硬件系统设计乒乓球游戏逻辑,构建出特定的模块,实现系统的功能。

其次,编写控制逻辑,运用Verilog HDL语言

编程,在FPGA硬件中得到设计的图像图案,以及搭建复杂的乒乓球游戏的系统结构,实

现乒乓球游戏的控制逻辑功能。

最后,完成了乒乓球游戏机的EDA课程设计。

基于某Verilog地乒乓球游戏电路设计

大学EDA课程设计:学号:班级:专业:学院:目录0 引言............................................................................................................................. - 1 -1 设计要求..................................................................................................................... -2 -2 设计思路..................................................................................................................... - 2 -3 Verilog程序 ................................................................................................................ - 3 -4 功能仿真..................................................................................................................... - 3 -5 总结........................................................................................................................... - 11 -致...............................................................................................................................- 11 -参考文献.......................................................................................................................- 11 -基于Verilog的乒乓球游戏电路设计0 引言可编程器件的广泛应用,为数字系统的设计带来了极大的灵活性。

fpga 乒乓球游戏机

基于FPGA的乒乓球游戏机设计Design of the table tennis game based on FPGA摘要FPGA在复杂逻辑电路以及数字信号处理领域中扮演越来越重要的角色。

FPGA有很高的数据处理速度,这就为我们处理高速信号提供了便利条件。

本次设计是以示波器为显示器,基于FPGA构造一个乒乓球游戏机。

用FPGA产生两组PWM波,通过两条I/O口线将信号传给RC低通滤波器,取出PWM信号的均值电压,输给示波器的XY模式。

这样我们就可以在示波器上观察到一亮点移动。

同时设置了计分机制,得分在七段数码管上显示双方得分。

关键字:FPGA Verilog 乒乓球游戏机AbstractFPGA in complex logic circuit and digital signal processing technology plays an increasingly important role.FPGA has very high data processing speed, this is for us to deal with high speed signal to provide convenient conditions. The design is based on the oscilloscope display, based on the FPGA structure of a table tennis ball game machine. Using FPGA to generate a two set of PWM wave, by two I / O line transmits a signal to the RC low-pass filter, remove the PWM signal of the average voltage, lost to the XY model. So that we can in the oscilloscope to observe an window mobile. By setting the button to generate the control signal, transmitted to the FPGA and the bright spot motion control. At the same time set a scoring mechanism, scoring in the seven digital tube display the scores of both parties.Keyword: FPGA Verilog table tennis game目录摘要 (2)Abstract (3)第一章设计任务与要求 (5)1.1设计任务 (5)1.2基本要求和扩展指标 (5)第二章系统总体设计 (6)2.1理论分析与计算 (6)2.1.1 PWM 调制原理 (6)2.1.2 理论计算 (6)2.2系统总体框图 (7)第三章电路分析与模块设计 (9)3.1低通滤波电路 (9)3.2增益放大电路 (9)3.3按键击球得分控制 (10)3.4七段数码管显示 (10)第四章系统软件设计 (12)4.1系统软件总体设计 (12)4.2判断显示函数 (13)附录一:硬件原理图 (15)附录二:程序清单 (16)第一章设计任务与要求1.1设计任务通过FPGA开发平台构造一台乒乓球游戏机。

基于verilog 乒乓球游戏机课程设计报告

长沙学院EDA课程设计说明书题目乒乓球游戏电路设计系 (部)专业(班级)姓名学号指导教师起止日期2008电子信息工程专业课程设计任务书系(部):电子与通信工程系专业:电子信息工程长沙学院课程设计鉴定表目录摘要:............................................................................................................................................................ - 6 - 1.设计要求.................................................................................................................................................. - 6 - 2.设计方案...................................................................................................................................................... - 6 -2.1乒乓球游戏机系统组成................................................................................................................... - 6 -2.2 功能模块设计.................................................................................................................................. - 6 -2.2.1 分频模块.............................................................................................................................. - 6 -2.2.2 按键消抖模块...................................................................................................................... - 7 -2.2.3 比赛规则控制(含发球控制器、乒乓球控制器、计分器) .......................................... - 9 -2.3顶层原理图...................................................................................................................................... - 11 -2.4 波形仿真........................................................................................................................................ - 11 -3.心得体会.................................................................................................................................................... - 12 -4.参考文献.................................................................................................................................................... - 12 -乒乓球游戏电路设计摘要:本设计使用FPGA 芯片来模拟实际的乒乓球游戏。

基于FPGA乒乓球游戏机Verilog设计

题目基于FPGA乒乓球游戏机Verilog设计学院通信工程专业班级通信081班学生姓名大彬哥指导教师大力会2013年6月12日摘要本文使用FPGA 芯片来模拟实际的乒乓球游戏。

本设计是基于Altera 公司的FPGA Cyclone II 芯片EP2C5T144C8 的基础上实现,运用Verilog HDL 语言编程,在Quartus II 软件上进行编译、仿真,最终在开发板上成功实现下载和调试关键词:编译仿真AbstractThis paper uses the FPGA chip to simulate the actual table tennis game. The design is based on Altera company Implementation of FPGA Cyclone based on II chip EP2C5T144C8, using Verilog HDL programming language, compile, simulation in Quartus IIsoftware, finally successfully in the development board download and debugKeywords: Compile;Simulation目录摘要 (I)Abstract (II)第1章绪论 (1)1.1 概述 (1)1.2Verilog 语言介绍 (1)1.2.1 Verilog 语言的用途 (2)1.2.2 Verilog 的历史 (2)1.2.3 Verilog 模块 (2)1.3 本文研究的意义 (3)第2章Verilog的基本理论 (4)2.1 Verilog模块的定义 (4)2.2Verilog模块的组成 (4)2.3 EP2C5T144C8芯片简介 (5)2.3.1 EP2C8开发板功能 (5)2.3.2开发板功能描述 (6)2.3.3EP2C5T144C8芯片的引脚图 (6)2.4 Verilog硬件描述语言的主要能力 (6)第3章乒乓球游戏机的软件设计 (8)3.1 乒乓球游戏机系统组成 (8)3.1.2功能模块设计 (8)3.2 发球权控制器 (9)3.3乒乓球位置控制 (10)3.3.1基于FPGA乒乓球比赛游戏机顶层原理图 (12)结论 (13)参考文献 (14)附录 (15)第1章绪论1.1 概述随着低复杂度FPGA器件成本的不断下降,具有灵活性和及时面市优势的FPGA与ASIC相比更有竞争性,在数字消费市场上的应用也急剧增加。

基于FPGA的乒乓球游戏机控制器设计

基于FPGA的乒乓球游戏机设计摘要Verilog是甚高速集成电路硬件描述语言。

目前,verilog已成为许多设计自动化工具普遍采用的标准化硬件描述语言。

verilog语言功能性强,覆盖面广,灵活性高,具有很好的实用性。

本文设计一个基于verilog的乒乓游戏机,乒乓游戏机由状态机、记分器、译码显示器与按键去抖等部分所组成。

通过对各部分编写verilog程序,然后进行编译、仿真、逻辑综合、逻辑适配,最后进行编程下载,并且通过EDA实验箱的验证,实现乒乓游戏机的基本功能。

关键词:verilog;EDA;乒乓游戏机AbstractVERILOG is high speed IC hardware describe language.VERILOG already becomes the language of normalizing hardware describe that a lot of design automation implement adopts commonly at present.The VERILOG language function is strong.The face covering is broad,flexibility high and have the very good pragmatism.One main body of the book is designed waits for what part group is accomplished owing to that VERILOG table tennis game machine,table tennis game machine go to tremble from state machine,marker,decoding display and button.By compiling and composing VERILOG procedure to every part,then compiling, simulate,logic synthesis,logic fitting.Carry out programming time be loaded with finally.Then verification and by GW48type EDA experiment box,realize table tennis game machine’s fundamental function.Key words:VERILOG:EDA;Table tennis game machine目录1绪论 (1)1.1课题的背景和意义 (1)1.2国内外研究现状 (1)1.3本论文的主要内容 (2)2Quartus II与Modelsim软件简介 (3)2.1Quartus II简介 (3)2.2Modelsim简介 (4)3方案选择与系统总体设计 (6)3.1整体方案的选择 (6)3.1.1设计任务与要求 (6)3.1.2设计的原理和方法 (7)3.1.3芯片的选择 (8)3.2系统总体设计 (8)3.2.1乒乓游戏机的组成示意图 (8)3.2.2本系统的逻辑分框图 (9)4系统各部分电路的详细设计 (10)4.1七段数码管显示译码电路 (10)4.2按键去抖电路 (11)4.3状态机设计 (11)4.3.1状态机的6种状态及状态转移 (11)4.3.2状态机/球台控制电路 (13)4.4记分器设计 (15)5系统的整体综合与仿真 (16)5.1顶层文件设计 (16)5.2系统程序框图: (17)5.3整个系统的综合与仿真 (18)5.3.1电路符号 (18)5.3.2系统仿真 (18)6系统的运行与仿真过程 (20)6.1系统程序的编译 (20)6.2系统的仿真 (22)结论 (24)谢辞 (25)参考文献 (26)附录 (27)1绪论1.1课题的背景和意义随着人们的物质生活越来越好了,人们开始对娱乐生活有了新的要求,特别是进入新世纪以来各种电子产品的不断出现,更是促进了我国电子行业的发展,为此,能够推出一款新的游戏产品是非常有前景的,本设计正是考虑了当前的社会现状,想设计出一款“乒乓球”游戏机,以往可能有过这方面的设计出现过,但是那些大多数都是采用的单片机等来实现的,本设计将采用最新的FPGA技术对“乒乓球”游戏机进行实现。

FPGA设计实践简易乒乓游戏机(精选五篇)

FPGA设计实践简易乒乓游戏机(精选五篇)第一篇:FPGA设计实践简易乒乓游戏机课程设计报告课程设计名称:FPGA设计实践设计课题名称:简易乒乓游戏机成绩简易乒乓游戏机设计报告一、设计目的:本课程的授课对象是电子科学与技术专业本科生,是电子类专业的一门重要的实践课程,是理论与实践相结合的重要环节。

本课程有助于培养学生的数字电路设计方法、掌握模块划分、工程设计思想与电路调试能力,为以后从事各种电路设计、制作与调试工作打下坚实的基础。

简易乒乓游戏机的实验目的:1.熟练掌握VHDL 语言和QuartusII 软件的使用;2.理解状态机的工作原理和设计方法;3.掌握利用EDA 工具进行自顶向下的电子系统设计方法;二、实验器材和工具软件:QUARTUS II。

三、设计内容:本课程要求学生以FPGA技术基础,以VHDL为语言,以QUARTUS II为工具,设计一个乒乓球游戏机。

四、设计具体步骤:乒乓球游戏机是一个经典的数字逻辑综合设计的题目,本题目中输入输出的信号较多,控制比较复杂,可以采用自上而下的设计方法。

首先,整体上设计本题目。

在理解题目的基础上,用图示的方法直观描述乒乓游戏机的外观和构成,明确所需要的硬件以及特点。

例乒乓游戏机的组成两人乒乓游戏机是用8个发光二极管代表乒乓球台,中间2发光二极管兼作球网,用点亮的发光二极管按一定的方向移动来表示球的运动。

在游戏机的两侧各设置两个开关,一个是发球开关发A发fB;另一个是击球开关jA,jB。

甲、乙二人按乒乓球比赛规则来操作开关。

当甲方按动发球开关fA时,靠近甲方的第1个发光二极管亮,然后发光二极管的甲向乙依次点亮,代表乒乓球的移动。

当球过网后按设计者规定的球位,乙方就可击球。

若乙方提前击球或没击着球,则判乙方失分,甲方的记分牌自动加分。

然后重新发球,比赛继续进行。

比赛一直要进行到一方记分牌达到11分,该局结束。

(3)完成各模块的代码编写:[1]分频模块,用与生成2HZ的技术频率library ieee;use ieee.std_logic_1164.all;entity clk_2 is port(clkin :in std_logic;clkout:out std_logic);end clk_2;architecture behave_clk_2 of clk_2 is constant N: Integer:=12499999;signal Counter:Integer RANGE 0 TO N;signal Clk: Std_Logic;begin process(clkin)begin if rising_edge(clkin)then if Counter=N then Counter<=0;Clk<=NOT Clk;else Counter<= Counter+1;end if;end if;end process;clkout<= Clk;end behave_clk_2 clk_2clkinclkoutinst7 [2]显示模块: library ieee;use ieee.std_logic_1164.all;entity translate3to7 is port(datain:in std_logic_vector(2 downto 0);dataout:out std_logic_vector(6 downto 0));end translate3to7;architecture behave OF translate3to7 is begin with datain(2 downto 0)select dataout <= “1000000” when “000” ,“1111001” when “001” ,“0100100” when “010” ,“0110000” when “011” ,“0011001” when “100” ,“0010010” when “101” ,“0000010” when “110” ,“1111000” when “111”;end behave;translate3to7datain[2..0]dataout[6..0]inst4 library ieee;use ieee.std_logic_1164.all;entity translate7to14 is port(data:in std_logic_vector(3 downto 0);outputH:out std_logic_vector(6 downto 0);outputL:out std_logic_vector(6 downto 0));end translate7to14;architecture behave_translate OF translate7to14 is begin with data(3 downto 0)select outputL <= “1000000” when “0000” ,“1111001” when “0001” ,“0100100” when “0010” ,“0110000” when “0011” ,“0011001” when “0100” ,“0010010” when “0101” ,“0000010” when “0110” ,“1111000” when “0111” ,“0000000” when “1000” ,“0010000” when “1001” ,“1000000” when “1010”,“1111001” when “1011”,“0100100” when “1100”,“0110000” when “1101”,“0011001” when “1110”,“0010010” when “1111”;wi th data(3 downto 0)select outputh <= “1000000” when “0000”,“1000000” when “0001”,“1000000” when “0010”,“1000000” when “0011”,“1000000” when “0100”,“1000000” when “0101”,“1000000” when “0110”,“1000000” when “0111”,“1000000” when “1000”,“1000000” when “1001”,“1111001” when “1010”,“1111001” when “1011”,“1111001” when “1100”,“1111001” when “1101”,“1111001” when “1110”,“1111001” when “1111”;end behave_translate;translate7to14data[3..0]outputH[6..0]outputL[6 ..0]inst23 library ieee;use ieee.std_logic_1164.all;entity translate3to8 is port(datain:in std_logic_vector(2 downto 0);dataout:out std_logic_vector(7 downto 0));end translate3to8;architecture behave OF translate3to8 is begin when “000”=> dataout <=“11111110”;when “001”=> dataout <=“11111101”;when “010”=> dat aout<=“11111011”;when “011”=> dataout <=“11110111”;when “100”=> dataout <=“11101111”;when “101”=> dataout <=“11011111”;when “110”=> dataout <=“10111111”;when “111”=> dataout <=“01111111”;when others => dataout <=“11111111”;end behave;translate3to8datain[2..0]dataout0dataout1dataout2data out3dataout4dataout5dataout6dataout7inst26(4)各模块调试和波形(5)状态图:五、设计收获以及存在的问题:1在此次实验中要用到计数器编程中往往要学会引用变量,因为信号容易产生延迟。

Verilog HDL乒乓球游戏机

Verilog HDL乒乓球游戏机正文:1:引言本文档旨在提供一个完整的Verilog HDL乒乓球游戏机的设计和实现的文档指南。

乒乓球游戏机被设计为一个经典的游戏,用户可以通过操控乒乓球拍来与计算机对手进行对决。

该游戏机将涵盖从电路设计到硬件实现的所有步骤。

以下将详细介绍每个设计和实现阶段的细节。

2:需求分析在这一部分,我们将详细描述乒乓球游戏机的需求和功能。

主要包括游戏的规则、用户界面的设计以及游戏机的性能要求。

这些需求和功能将为后续的设计和实现提供指导。

3:电路设计本章节将介绍乒乓球游戏机的电路设计。

首先,我们将详细讨论每个组件的功能,包括乒乓球拍、乒乓球、计分系统等。

接下来,我们将确定需要使用的电子元件和电路,包括舵机、传感器、时钟等。

最后,我们将给出整体电路的设计图,并进行仿真和验证。

4:时序控制本章节将重点讨论乒乓球游戏机的时序控制。

我们将详细描述游戏的各类状态和状态转换,以及时钟信号的和分配。

同时,我们还将探讨如何通过状态机来控制游戏的进行,并处理用户输入和计算机对手的决策。

5:界面设计在这一部分,我们将介绍乒乓球游戏机的用户界面设计。

我们将讨论显示器和按键的布局,以及如何实现用户与游戏机的交互。

同时,我们还将探讨音频输出和输入的设计,以提供更好的游戏体验。

6:硬件实现本章节将详细描述乒乓球游戏机的硬件实现。

我们将介绍如何根据电路设计的原理图进行硬件布局和布线。

同时,我们还将涵盖选取适合的硬件平台和开发工具,并进行调试和测试,以确保游戏机的正常运行。

7:性能评估在这一部分,我们将对乒乓球游戏机的性能进行评估。

我们将讨论游戏的稳定性、响应时间和用户体验等方面的指标,并给出相应的测试结果和分析。

8:总结通过本文档,我们详细介绍了Verilog HDL乒乓球游戏机的设计和实现。

每个章节都包含了细致的细节和步骤,以供读者参考和实践。

如果按照本文档所述的步骤进行设计和实现,相信能够顺利完成一个功能完备的乒乓球游戏机。

基于FPGA乒乓球游戏

基于FPGA的乒乓球游戏的设计与实现引言FPGA(FieldProgrammableGateArray),现场可编程门阵列。

它是继PAL、GAL、CPLD等可编程器件的基础上进一步发展的成果。

它作为专用集成电路(ASIC)领域中的一种半定制电路,既解决了定制电路的不足,又克服了原有可编程器件门电路数有限的缺点。

作为一种可编程器件,FPGA与传统的数字电路和门电路相比,它采用逻辑单元阵列的模式,内部包含有可配置逻辑模块、输出输入模块和内部连线三个部分。

通过硬件描述语言(如VHDL语言)完成的电路设计,可以通过综合与布局,快速烧录至FPGA芯片上进行测试。

SOPC(SystemOnProgrammableChip),可编程片上系统。

它是用可编程逻辑技术把整个系统放到一块硅片上,用于从事嵌入式系统的系统研究和电子测量处理等领域。

SOPC是一种特殊的嵌入式系统,它既是片上系统(SOC),即由单个芯片完成整个系统的主要逻辑功能,但它又不是简单的SOC,也是可编程系统,具有灵活的设计方式,可裁剪、可扩充、可升级,并具备软硬件在系统可编程的功能。

1乒乓球游戏玩法介绍将双通道示波器作为显示屏。

将两路信号输入示波器中,让示波器工作在X/Y模式。

单片机实验板上的两个按钮作为控制键分别用于左击球和右击球,当小球接近屏幕左边时按下左击球可将球击回右侧,右侧击球亦然。

小球可以按照一定的抛物线轨迹自动在屏幕上左右运动,连续按下两次击球键能够击出高抛球,使球飞行距离增高。

当球接触到屏幕边沿而未按下击球键则被判定为输球。

2实验器件CycloneIII(EP3C10E144C8)FPGA实验板,单片机P89V51实验板(含按键显示屏等),电阻导线若干。

Altera公司生产的CycloneIIIFPGA芯片具有低功耗、低成本和高性能等特点。

其体系结构包括高达120K的垂直排列逻辑单元(LE)、以9-Kbit(M9K)模块构成的4Mbits嵌入式存储器、200个18x18的嵌入式乘法器。

基于FPGA乒乓球游戏机Verilog设计

基于FPGA乒乓球游戏机Verilog设计整理者:G゛佑咡江西师范大学电子信息工程前言:此类程序鉴于网上大多是VHDL设计,所以我整理一份Verilog设计供初学者参考,因为时间关系,程序没有优化,也没有注释,如有不妥的地方,请大家多提意见。

摘要:本文使用FPGA 芯片来模拟实际的乒乓球游戏。

本设计是基于Altera 公司的FPGA Cyclone II 芯片EP2C5T144C8 的基础上实现,运用Verilog HDL 语言编程,在Quartus II 软件上进行编译、仿真,最终在开发板上成功实现下载和调试。

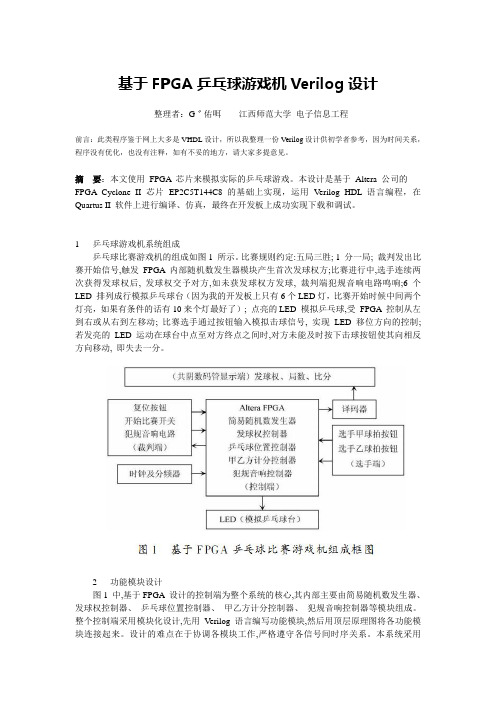

1 乒乓球游戏机系统组成乒乓球比赛游戏机的组成如图1 所示。

比赛规则约定:五局三胜; 1 分一局; 裁判发出比赛开始信号,触发FPGA 内部随机数发生器模块产生首次发球权方;比赛进行中,选手连续两次获得发球权后, 发球权交予对方,如未获发球权方发球, 裁判端犯规音响电路鸣响;6 个LED 排列成行模拟乒乓球台(因为我的开发板上只有6个LED灯,比赛开始时候中间两个灯亮,如果有条件的话有10来个灯最好了); 点亮的LED 模拟乒乓球,受FPGA 控制从左到右或从右到左移动; 比赛选手通过按钮输入模拟击球信号, 实现LED 移位方向的控制; 若发亮的LED 运动在球台中点至对方终点之间时,对方未能及时按下击球按钮使其向相反方向移动, 即失去一分。

2 功能模块设计图1 中,基于FPGA 设计的控制端为整个系统的核心,其内部主要由简易随机数发生器、发球权控制器、乒乓球位置控制器、甲乙方计分控制器、犯规音响控制器等模块组成。

整个控制端采用模块化设计,先用Verilog 语言编写功能模块,然后用顶层原理图将各功能模块连接起来。

设计的难点在于协调各模块工作,严格遵守各信号间时序关系。

本系统采用50MHz系统时钟。

2. 1 简易随机数发生器比赛首次发球权由随机数发生器产生的数据决定,其随机性要求不严, 因此,采用非常简单的模式产生,即一旦FPGA 上电, 系统时钟百分频产生一方波信号square,当裁判闭合开始比赛开关产生start 信号上升沿时,读取此时squar e信号值作为随机数发生器输出data_rand。

verilog乒乓球大作业(仿真成功)

v e r i l o g乒乓球大作业(仿真成功)-标准化文件发布号:(9456-EUATWK-MWUB-WUNN-INNUL-DDQTY-KII一任务描述1 设计要求左、右双方各持一按键作为“球拍”,实验板上一行8只发光二极管为乒乓球台,其中那只发光的发光二极管代表乒乓球所在位置。

设计如图1所示的乒乓球游戏实物图的模拟控制器。

发球方最后一位LED 点亮,按下键表示发球,亮的灯依次向对方移动,当到达对方最后一位时0.5s 内对方必须按下按键表示接球,接球后LED灯向对方移动,否则输球。

接球时,LED没有亮到最后一位时就按下接球按键为犯规。

输球或者犯规,对方加1分,率先加到11分者游戏胜出这一局。

2设计思路考虑到游戏的复杂度,采用状态机来实现这些模式转换。

用到8个状态,如下所示:状态功能S2球从甲方向乙方右移,若此时乙方接球就给甲方加一分,并将球权给甲方S3开始判断乙方是否在0.5S内接球S4乙方发球S5球从乙方向甲方左移,若此时甲方接球就给乙方加一分,并将球权给乙方S7用于接球后判断发球程序还加入了蜂鸣、用数码管显示分数和发球权等功能。

二结构框图1 状态转移图002 程序流程图3 系统模块三系统程序modulepingpangok(state,clk2hz,rst,k_a,k_b,led8s,led7s1,led7s2,led7s3,led7s4,led7s5,speaker );//clk2hz指一个2Hz的时钟输入, rst异步复位, k_a和k_b是比赛双方按键, speaker是蜂鸣器//led8s是一排8个发光二极管代表球场, led7s1~4是4个显示分数的数码管, led7s5是显示发球权的数码管input clk2hz,rst,k_a,k_b;output [7:0] led8s;output [6:0] led7s1,led7s2,led7s3,led7s4,led7s5;output speaker;output [2:0] state;reg [7:0] led8s;reg [6:0] led7s1,led7s2,led7s3,led7s4,led7s5;reg [3:0] score_a,score_b;reg [2:0] state;reg speaker;parameter s0=3'b000,//复位状态,也是判断发球权的状态;s1=3'b001,//甲方发球;s2=3'b010,//球从甲方向乙方右移,若此时乙方接球就给甲方加一分,并将球权给甲方;s3=3'b011,//开始判断乙方是否在0.5S内接球;s4=3'b100,//乙方发球;s5=3'b101,//球从乙方向甲方左移,若此时甲方接球就给乙方加一分,并将球权给乙方;s6=3'b110;//开始判断甲方是否在0.5S内接球;s7=3'b111;//用于判断接球后发球;//----------------游戏逻辑控制核心----------------------------------------------------------------------------always @(posedge clk2hz) begincase(state)s7: beginif(k_a)state<=s1; //甲发球;else if(k_b)state<=s4;//乙发球;else if(speaker)speaker=1'b0;elsespeaker=1'b0;ends0: beginled7s5<=7'b0111111;//第五个数码管显示数字0,表示发球权可以开始判断了;led8s<=7'b00000000;score_a<=0;score_b<=0;//给甲乙双方的分数复位;if(k_a)beginspeaker<=1'b1;//因为按键k_a要持续按着保持高电位'1',蜂鸣器鸣叫是提示可以松手了;state<=s7;endelse if(k_b)beginspeaker<=1'b1;state<=s7;endelsestate<=s0;ends1: beginled7s5<=7'b0000110;//第五个数码管显示数字1,表示发球权现在是甲方的;if(led8s==8'b00000000)led8s<=8'b10000000;//点亮的灯出现在最右边,即甲方发球;state<=s2;if(speaker)speaker<=1'b0;//将刚才鸣叫的蜂鸣器关闭;ends2: beginif(led8s==8'b00000010)beginled8s<=led8s>>1;state<=s3;//进入判断乙方接球的状态;endelsebeginled8s<=led8s>>1;state<=s7;endif(k_b)beginscore_a<=score_a+1;speaker<=1'b1;//若在此期间乙方抢先按键,就判断乙方输,给甲方加1分,并让蜂鸣器鸣叫;state<=s7;led8s<=8'b00000000;endends3: beginif(k_b)beginstate<=s7;//乙方接球成功,并进入乙方发球的s7状态;led8s<=8'b00000000;endelsebeginscore_a<=score_a+1;speaker<=1'b1;state<=s7;//乙方接球不成功,则甲方加一分,并进入甲方发球的s7状态,蜂鸣器鸣叫;led8s<=8'b00000000;endends4: beginled7s5<=7'b1011011;//第五个数码管显示数字2,表示发球权现在是乙方的;if(led8s==8'b00000000)led8s<=8'b00000001;//点亮的灯出现在最左边,即乙方发球;state<=s5;if(speaker)speaker<=1'b0;//将刚才鸣叫的蜂鸣器关闭;ends5: beginif(led8s==8'b01000000)beginled8s<=led8s<<1;state<=s6;//进入判断甲方接球的状态;endelsebeginled8s<=led8s<<1;state<=s7;endif(k_a)beginscore_b<=score_b+1;speaker<=1'b1;//若在此期间甲方抢先按键,就判断甲方输,给乙方加1分,并让蜂鸣器鸣叫;state<=s7;led8s<=8'b00000000;endends6: beginif(k_a)beginstate<=s7;//甲方接球成功,并进入甲方发球的s7状态;led8s<=8'b00000000;endelsebeginscore_b<=score_b+1;speaker<=1'b1;state<=s7;//甲方接球不成功,则乙方加一分,并进入乙方发球的s7状态,蜂鸣器鸣叫;led8s<=8'b00000000;endenddefault: state<=s0;endcase//----------甲乙双方的分数各用2个数码管显示-----------------------------------------------------------------if(score_a==11 & score_b==11)beginscore_a<=0;score_b<=0;//如果任一方得11分,一局结束,计分清零;endcase(score_a)8'b0000: beginled7s1<=7'b0111111;led7s2<=7'b0111111;//数码管显示0分;end8'b0001: beginled7s1<=7'b0111111;led7s2<=7'b0000110;//数码管显示1分;end8'b0010: beginled7s1<=7'b0111111;led7s2<=7'b1011011;//数码管显示2分;end8'b0011: beginled7s1<=7'b0111111;led7s2<=7'b1001111;//数码管显示3分;end8'b0100: beginled7s1<=7'b0111111;led7s2<=7'b1100110;//数码管显示4分;end8'b0101: beginled7s1<=7'b0111111;led7s2<=7'b1101101;//数码管显示5分;end8'b0110: beginled7s1<=7'b0111111;led7s2<=7'b1111101;//数码管显示6分;end8'b0111: beginled7s1<=7'b0111111;led7s2<=7'b0000111;//数码管显示7分;end8'b1000: beginled7s1<=7'b0111111;led7s2<=7'b1111111;//数码管显示8分;end8'b1001: beginled7s1<=7'b0111111;led7s2<=7'b1101111;//数码管显示9分;end8'b1010: beginled7s1<=7'b0000110;led7s2<=7'b0111111;//数码管显示10分;end8'b1011: beginled7s1<=7'b0000110;led7s2<=7'b0000110;//数码管显示11分;enddefault: beginled7s1<=7'b0111111;led7s2<=7'b0111111;//数码管显示0分;endendcasecase(score_b)8'b0000: beginled7s3<=7'b0111111;led7s4<=7'b0111111;//数码管显示0分;end8'b0001: beginled7s3<=7'b0111111;led7s4<=7'b0000110;//数码管显示1分;end8'b0010: beginled7s3<=7'b0111111;led7s4<=7'b1011011;//数码管显示2分;end8'b0011: beginled7s3<=7'b0111111;led7s4<=7'b1001111;//数码管显示3分;end8'b0100: beginled7s3<=7'b0111111;led7s4<=7'b1100110;//数码管显示4分;end8'b0101: beginled7s3<=7'b0111111;led7s4<=7'b1101101;//数码管显示5分;end8'b0110: beginled7s3<=7'b0111111;led7s4<=7'b1111101;//数码管显示6分;end8'b0111: beginled7s3<=7'b0111111;led7s4<=7'b0000111;//数码管显示7分;end8'b1000: beginled7s3<=7'b0111111;led7s4<=7'b1111111;//数码管显示8分;end8'b1001: beginled7s3<=7'b0111111;led7s4<=7'b1101111;//数码管显示9分;end8'b1010: beginled7s3<=7'b0000110;led7s4<=7'b0111111;//数码管显示10分;end8'b1011: beginled7s3<=7'b0000110;led7s4<=7'b0000110;//数码管显示11分;enddefault: beginled7s3<=7'b0111111;led7s4<=7'b0111111;//数码管显示0分;endendcaseend endmodule四仿真结果功能仿真是最基本的仿真验证,它只能仿真设计中的逻辑功能。

基于FPGA的乒乓球游戏设计解读

软件部分 VHDL

--逻辑矢量转换为无符号数以便比较

count_value1<=unsigned(count1); count_value2<=unsigned(count2); compare_value1<=unsigned(compare1); compare_value2<=unsigned(compare2);

软件部分 C语言

int main (void) { Xuint32 Status; //读取GPIO初始化状态 XGpio Push_Bottons_4Bit; //定义GPIO按钮 XGpio Led_8Bit; //定义GPIO Xuint32 DataRead; //读取按钮数据 Xuint32 PWM[256]; //抽样256个点,保存在数组 Xuint32 count=0x0; //定义计分变量 int i,j=2,dir=1,inside_flag,hit_flag; //定义轨迹方向变量、 击球标志、可击球标志

signal divclk : std_logic; --分频时钟 signal count1 : std_logic_vector(0 to 15):=X"0000";--计数器1 signal count_value1: unsigned(0 to 15); --无符号计数值1 signal count2 : std_logic_vector(0 to 15):=X"0000";--计数器2 signal count_value2 : unsigned(0 to 15); --无符号计数值2 signal compare1 : std_logic_vector(0 to 15); --比较匹配值1 signal compare_value1: unsigned(0 to 15); --无符号比较匹配值1 signal compare2 : std_logic_vector(0 to 15); --比较匹配值2 signal compare_value2 : unsigned(0 to 15); --无符号比较匹配值2 signal dir1 : std_logic:='1'; --计数器1计数方向标志1为增计数,0为减计数 signal dir2 : std_logic:='1'; --计数器2计数方向标志1为增计数,0为减计数 signal slv_reg0 : std_logic_vector(0 to C_SLV_DWIDTH-1);

基于FPGA的乒乓球游戏机设计.

摘要在现代电子设计领域,微电子技术迅猛发展,无论是系统设计、电路设计,还是芯片设计,其设计的复杂度都在增加,传统的手工设计方法已经不能满足设计者的要求,急需新的设计工具来解决。

EDA技术的迅速发展顺应了时代的发展,使得电子设计自动化技术有了新的、快的发展,其重要程度日益突出。

本文设计了基于FPGA的,用Verilog HDL语言描述的乒乓球游戏机的设计。

它由控制模块、数码管的片选信号模块、送数据模块和7段译码器模块组成,连接形成乒乓球游戏机的顶层电路。

在QuartusⅡ软件上用Verilog HDL语言分别对每个模块进行描述,然后在软件上进行编译、仿真,最终实现乓乓球比赛的基本过程和规则,并能自动裁判和计分,达到设计的要求。

关键词:EDA ;FPGA ;Verilog HDLAbstractIn the field of modern electronic design, the rapid development of microelectronic technology,whether the system design, circuit design and chip design, the design is more complex, the traditional manual design methods have been unable to meet the requirements of designers,in urgent need of new design tools to solve. The rapid development of EDA technology to the development of the times, the electronic design automation technology has been the development of new, fast, its importance is outstanding day by day. This paper is designed based on FPGA, the design of table tennis game is described with Verilog HDL language. It consists of control module, chip select signal module, digital tube to send data module and the 7 segmentdecoder modules, the top-level circuit connected to form a table tennis game. In the Quartus software by Verilog HDL language for each module are described, and then the compiler, simulation in software, realize the basic process and the rules of tabletennis table tennis competition, and can automatically judge and score, to meet the design requirements.Keywords: EDA; FPGA; Verilog HDL第一章引言1.1课题研究的背景随着微电子技术的飞跃发展,无论是系统级设计、电路设计还是芯片设计,它的复杂程度都在不断的增加,而且它的发展速度也越来越快。

FPGA乒乓球游戏机设计

摘要摘要在电子技术获得了飞速的发展的今天,现代电子产品几乎渗透了社会的各个领域,有力地推动了社会生产力的发展和社会信息化程度的提高,同时也使现代电子产品性能进一步提高,产品更新换代的节奏也越来越快。

而电子游戏因其携带方便、互动性高、无场地限制等优势,成为了人们休闲时很好的选择。

本设计将采用FPGA对“乒乓球”游戏机进行实现。

FPGA具有功能强、可靠性高、使用方便、体积小及重量轻等优点。

近年来,国内的FPGA技术与产品开发应用方面的发展也很快,各种电子产品已越来越多地采用FPGA控制系统且性价比高。

然后以FPGA为平台,VHDL硬件描述语言编程实现,实验箱验证。

最后在硬件上调试并实现实现“乒乓球”游戏机功能。

关键字:EDA,FPGA,VHDL,游戏机ABSTRACTABSTRACTThe electronic technology has obtained the rapid development in the modern, the electronic products penetrated almost every field of the society, a strong impetus to the development of social productive forces and the social informationization degree is improved, simultaneously also makes the modern electronic products to further improve the performance, product replacement are increasingly fast pace. Electronic games because of its portability, interactive high, no site limitation and other advantages, has become the people leisure time very good choice.This design will use the FPGA on the "ping pong" Electronic game machine. FPGA has the advantages of strong function, high reliability, convenient use, small volume and light weight etc.. In recent years, the development of FPGA technology and product development and application of domestic too soon, all kinds of electronic products have been increasingly adopted in FPGA control system and high cost performance. Then taking FPGA as the platform, VHDL hardware description language programming, verification experiment box. Finally, in the hardware debugging and the realization of "ping pong" game computer function.Key Words:EDA, FPGA, VHDL, Game machine目录第1章引言 (1)1.1 选题背景 (1)1.2 研究设计主要内容 (1)第2章开发工具描述 (3)2.1 EDA基础 (3)2.1.1 EDA技术的发展历程 (3)2.1.2 EDA技术的发展趋势 (5)2.1.3 EDA技术的基本工具 (5)2.2 硬件描述语言—VHDL (6)2.3 Quartus Ⅱ简介 (7)第3章功能实现与设计思路 (10)3.1 功能实现 (10)3.2 设计方案 (10)第4章各模块程序设计 (12)4.1 主控制程序设计 (12)4.1.1 桌台模块程序设计 (12)4.1.2 译码模块程序 (13)4.2 分频器模块设计 (14)4.3 防抖动模块设计 (15)4.4 显示控制和输出模块 (17)第5章系统的整合与仿真 (20)5.1 上层模块设计 (20)5.2 系统的仿真 (21)5.3 引脚分配与器件编程 (24)5.3.1 引脚分配 (24)5.3.2 器件编程 (24)第6章总结 (28)参考文献 (29)致谢 (30)附录 (31)附录一:桌台模块程序 (31)附录二:分频器模块程序 (35)附录三:防抖动模块程序 (36)附录四:显示控制和输出模块程序 (37)附录五:上层模块程序 (39)附录六:译码模块程序 (41)外文资料原文 (43)译文 (53)第1章引言第1章引言1.1选题背景电子技术的飞速发展,现代电子产品几乎渗透了社会的各个领域,有力地推动了社会生产力的发展和社会信息化程度的提高,同时也使现代电子产品性能进一步提高,产品更新换代的节奏也越来越快。

基于verilog乒乓球游戏机课程设计报告

基于verilog乒乓球游戏机课程设计报告一、设计背景与目的乒乓球是一项受欢迎的运动项目,可以锻炼身体的协调性和反应能力。

为了进一步提高学生的乒乓球水平,我们决定设计一个乒乓球游戏机,通过模拟真实的乒乓球比赛场景,让学生在娱乐中提高他们的技术。

二、设计原理乒乓球游戏机的设计原理主要是利用数字逻辑电路和FPGA实现。

首先,我们需要定义乒乓球运动的规则。

乒乓球从一个初始位置出发,通过张力和角度来调节球的速度和方向。

球在两个板子之间来回运动,直到有一方无法接到球为止。

为了实现这个设计,我们需要借助FPGA的输入输出端口。

玩家可以通过按钮来控制板子的位置,接收按键信号,并将信号转换为逻辑电平输入到FPGA。

FPGA根据接收到的信号,控制板子的移动。

另外,FPGA还需要处理球的运动轨迹,包括弹跳和反射。

设计过程中,我们需要将整个桌面划分为多个区域,每个区域都与逻辑电路相连。

通过逻辑电路的计算,我们可以实时更新球的位置和速度,判断球是否被接住,球是否出界等。

当球被接住或出界时,游戏将进入新的一轮。

三、设计步骤1.定义乒乓球的运动规则,包括球的起始位置、初始速度、板子的移动范围等。

2.划分整个桌面,并将每个区域与逻辑电路相连。

3.设计输入接口,包括接收按钮信号的接口。

4.设计输出接口,包括控制板子移动的接口。

5.设计逻辑电路,实现球的运动轨迹计算,包括弹跳和反射的计算。

6.实现FPGA的硬件描述,包括输入输出端口的定义和逻辑电路的实现。

7.进行仿真测试,验证设计的正确性。

8.制作PCB板和外围电路,完成整个乒乓球游戏机的制作。

四、实际应用乒乓球游戏机可以应用于学校的体育课程中,帮助学生们提高乒乓球技术。

通过轻松愉快的游戏方式,学生能够更好地理解乒乓球的运动规律,并锻炼乒乓球的技术。

此外,乒乓球游戏机还可以用于比赛和娱乐场所。

人们可以通过挑战乒乓球游戏机,提高乒乓球水平,增加娱乐乐趣。

五、设计总结通过这次课程设计,我们深入学习了数字逻辑电路和FPGA的应用,掌握了乒乓球游戏机的设计原理和实现方法。

基于FPGA“乒乓球比赛游戏机”的设计

《电子设计自动化(EDA)技术》课程设计报告题目: 乒乓球比赛游戏机姓名:院系:应用技术学院专业:电子信息工程学号:指导教师:完成时间:2012年06月25日目录1 课程设计题目、内容与要求………………………………1.1 设计内容………………………………………………1.2 具体要求………………………………………………2 系统设计……………………………………………………2.1 设计思路………………………………………………2.2 系统原理(包含:框图等阐述)与设计说明等内容3 系统实现……………………………………………………注:此部分阐述具体实现,包含主要逻辑单元、模块、源代码等内容4 系统仿真……………………………………………………5 硬件验证(操作)说明……………………………………6 总结………………………………………………………7 参考书目…………………………………………………设计时间:16周、17周组员:1课程设计题目、内容与要求1.1课程设计的题目乒乓球比赛游戏机1.2课程设计目的随着科学技术日益迅速的发展,数字系统已经深入到生活的各个方面。

它具有技术效果好,经济效益高,技术先进,造价较低,可靠性高,维修方便等许多优点。

使我们更加熟练掌握数字系统的设计。

对所学的专业知识有能力更好的应用在实践方面。

1.3课程设计要求(1)使用乒乓球游戏机的双方在不同位置发球或击球。

(2)乒乓球的位置和移动方向由灯亮和依次亮的方向决定。

使用者根据球的位置发出相应的动作(3)比赛用21分为一局来进行,双方设置各自的记分牌,任意一方先记满21分就获胜此局。

当记分牌清零后,开始新的一局比赛。

1.4课程设计内容设计一个由甲乙双方参赛,有裁判的三人乒乓球游戏机。

用8个(或更多个)LED排成一条直线,以中点为界,两边各代表参赛双方的位置,其中一只点亮的LED指示球的当前位置,点亮的LED依次从左到右,或从右到左,其移动的速度应能调节。

基于FPGA的乒乓球游戏参考设计

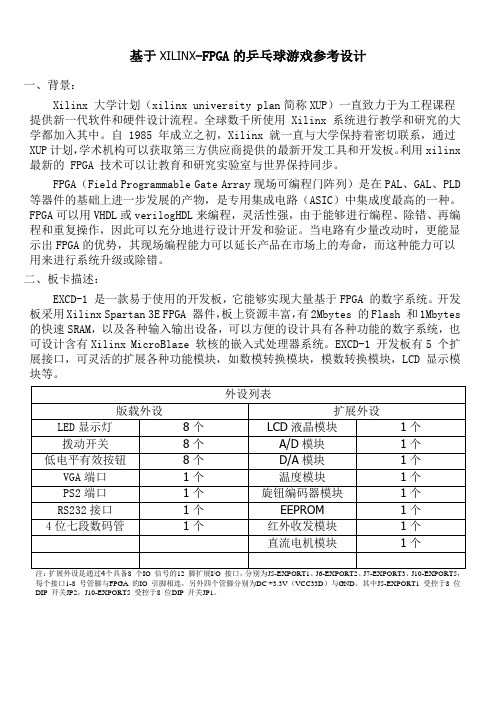

基于XILINX-FPGA的乒乓球游戏参考设计一、背景:Xilinx 大学计划(xilinx university plan简称XUP)一直致力于为工程课程提供新一代软件和硬件设计流程。

全球数千所使用 Xilinx 系统进行教学和研究的大学都加入其中。

自 1985 年成立之初,Xilinx 就一直与大学保持着密切联系,通过XUP计划,学术机构可以获取第三方供应商提供的最新开发工具和开发板。

利用xilinx 最新的 FPGA 技术可以让教育和研究实验室与世界保持同步。

FPGA(Field Programmable Gate Array现场可编程门阵列)是在PAL、GAL、PLD 等器件的基础上进一步发展的产物,是专用集成电路(ASIC)中集成度最高的一种。

FPGA可以用VHDL或verilogHDL来编程,灵活性强,由于能够进行编程、除错、再编程和重复操作,因此可以充分地进行设计开发和验证。

当电路有少量改动时,更能显示出FPGA的优势,其现场编程能力可以延长产品在市场上的寿命,而这种能力可以用来进行系统升级或除错。

二、板卡描述:EXCD-1 是一款易于使用的开发板,它能够实现大量基于FPGA 的数字系统。

开发板采用Xilinx Spartan 3E FPGA 器件,板上资源丰富,有2Mbytes 的Flash 和1Mbytes 的快速SRAM,以及各种输入输出设备,可以方便的设计具有各种功能的数字系统,也可设计含有Xilinx MicroBlaze 软核的嵌入式处理器系统。

EXCD-1 开发板有5 个扩展接口,可灵活的扩展各种功能模块,如数模转换模块,模数转换模块,LCD 显示模块等。

每个接口1-8 号管脚与FPGA 的IO 引脚相连,另外四个管脚分别为DC +3.3V(VCC33D)与GND。

其中J5-EXPORT1 受控于8 位DIP 开关JP2,J10-EXPORT5 受控于8 位DIP 开关JP1。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

大学EDA课程设计:学号:班级:专业:学院:目录0 引言............................................................................................................................. - 2 -1 设计要求..................................................................................................................... -2 -2 设计思路..................................................................................................................... - 2 -3 Verilog程序 ................................................................................................................ - 3 -4 功能仿真..................................................................................................................... - 9 -5 总结........................................................................................................................... - 11 - 致...............................................................................................................................- 11 - 参考文献.......................................................................................................................- 11 -基于Verilog的乒乓球游戏电路设计0 引言可编程器件的广泛应用,为数字系统的设计带来了极大的灵活性。

可编程器件可以通过软件编程对硬件的结构和工作方式进行重构,使得硬件的设计可以如同软件设计那样快捷方便。

高速发展的FPGA、CPLD兼有串、并行工作方式和高速、高可靠性的特点,在电子系统设计中得到了广泛应用。

通常使用硬件描述语言(Hardware Description Language,HDL)进行数字电子系统设计。

目前应用广泛的硬件描述语言有:VHDL语言,Verilog HDL语言,AHDL语言。

Verilog语言由于具有强大的行为描述能力和丰富的仿真语句从而成为系统设计领域最佳的硬件描述语言。

鉴于如上所述,本系统使用Verilog语言进行设计,采用自上向下的设计方法。

利用Quartus II 6.0 进行Verilog程序的编译与综合,然后用Modelism SE 6.0进行功能仿真和时序仿真,并使用GW48系列SOPC/EDA实验开发系统进行下载验证。

1 设计要求图1 乒乓球游戏实物图设计如图1所示的乒乓球游戏实物图的模拟控制器。

发球方最后一位LED点亮,按下键表示发球,亮的灯依次向对方移动,当到达对方最后一位时0.5s对方必须按下按键表示接球,接球后LED灯向对方移动,否则输球。

接球时,LED没有亮到最后一位时就按下接球按键为犯规。

输球或者犯规,对方加1分,率先加到11分者游戏胜出这一局。

2 设计思路考虑到游戏的复杂度,采用状态机来实现这些模式转换。

用到6个状态,如表1所示:状态功能S1 甲方发球S2 球从甲方向乙方右移,若此时乙方接球就给甲方加一分,并将球权给甲方S3 开始判断乙方是否在0.5S接球S4 乙方发球S5 球从乙方向甲方左移,若此时甲方接球就给乙方加一分,并将球权给乙方表1 状态介绍为了美化设计,加入了蜂鸣、用数码管显示分数和发球权等功能。

3 Verilog程序modulepingpangok(state,nextstate,clk2hz,rst,k_a,k_b,led8s,led7s1,led7s2,led7s3,led7s4,led7s5,speaker);//clk2hz指一个2Hz的时钟输入, rst异步复位, k_a和k_b是比赛双方按键, speaker是蜂鸣器//led8s是一排8个发光二极管代表球场, led7s1~4是4个显示分数的数码管, led7s5是显示发球权的数码管input clk2hz,rst,k_a,k_b;output [7:0] led8s;output [6:0] led7s1,led7s2,led7s3,led7s4,led7s5;output speaker;output [2:0] state,nextstate;reg [7:0] led8s;reg [6:0] led7s1,led7s2,led7s3,led7s4,led7s5;reg [3:0] score_a,score_b;reg [2:0] state,nextstate;reg speaker;parameter s0=3'b000,//复位状态,也是判断发球权的状态;s1=3'b001,//甲方发球;s2=3'b010,//球从甲方向乙方右移,若此时乙方接球就给甲方加一分,并将球权给甲方;s3=3'b011,//开始判断乙方是否在0.5S接球;s4=3'b100,//乙方发球;s5=3'b101,//球从乙方向甲方左移,若此时甲方接球就给乙方加一分,并将球权给乙方;s6=3'b110;//开始判断甲方是否在0.5S接球;//----------进程块1:状态交换-------------------------------------------------------------------------------------- always (posedge clk2hz or posedge rst)beginif(rst)state<=s0;//rst上升沿复位elsestate<=nextstate;end//----------进程块2:游戏逻辑控制核心---------------------------------------------------------------------------- always (state or k_a or k_b or score_a or score_b)begincase(state)s0: beginled7s5<=7'b0111111;//第五个数码管显示数字0,表示发球权可以开始判断了;led8s<=7'b00000000;score_a<=0;score_b<=0;//给甲乙双方的分数复位;if(k_a)beginspeaker<=1'b1;//因为按键k_a要持续按着保持高电位'1',蜂鸣器鸣叫是提示可以松手了;nextstate<=s1;endelse if(k_b)beginspeaker<=1'b1;nextstate<=s4;endelsenextstate<=s0;ends1: beginled7s5<=7'b0000110;//第五个数码管显示数字1,表示发球权现在是甲方的;if(led8s==8'b00000000)led8s<=8'b10000000;//点亮的灯出现在最右边,即甲方发球;nextstate<=s2;if(speaker)speaker<=1'b0;//将刚才鸣叫的蜂鸣器关闭;ends2: beginif(led8s==8'b00000010)beginled8s<=led8s>>1;nextstate<=s3;//进入判断乙方接球的状态;endelsebeginled8s<=led8s>>1;nextstate<=s1;endif(k_b)beginscore_a<=score_a+1;speaker<=1'b1;//若在此期间乙方抢先按键,就判断乙方输,给甲方加1分,并让蜂鸣器鸣叫;nextstate<=s1;led8s<=8'b00000000;endends3: beginif(k_b)beginnextstate<=s4;//乙方接球成功,并进入乙方发球的s4状态;led8s<=8'b00000000;endelsebeginscore_a<=score_a+1;speaker<=1'b1;nextstate<=s1;//乙方接球不成功,则甲方加一分,并进入甲方发球的s1状态,蜂鸣器鸣叫;led8s<=8'b00000000;endends4: beginled7s5<=7'b1011011;//第五个数码管显示数字2,表示发球权现在是乙方的;if(led8s==8'b00000000)led8s<=8'b00000001;//点亮的灯出现在最左边,即乙方发球;nextstate<=s5;if(speaker)speaker<=1'b0;//将刚才鸣叫的蜂鸣器关闭;ends5: beginif(led8s==8'b01000000)beginled8s<=led8s<<1;nextstate<=s6;//进入判断甲方接球的状态;endelsebeginled8s<=led8s<<1;nextstate<=s4;endif(k_a)beginscore_b<=score_b+1;speaker<=1'b1;//若在此期间甲方抢先按键,就判断甲方输,给乙方加1分,并让蜂鸣器鸣叫;nextstate<=s4;led8s<=8'b00000000;endends6: beginif(k_a)beginnextstate<=s1;//甲方接球成功,并进入甲方发球的s1状态;led8s<=8'b00000000;endelsebeginscore_b<=score_b+1;speaker<=1'b1;nextstate<=s4;//甲方接球不成功,则乙方加一分,并进入乙方发球的s4状态,蜂鸣器鸣叫;led8s<=8'b00000000;endenddefault: nextstate<=s0;endcase//----------甲乙双方的分数各用2个数码管显示----------------------------------------------------------------- if(score_a==11 & score_b==11)beginscore_a<=0;score_b<=0;//如果任一方得11分,一局结束,计分清零;endcase(score_a)8'b0000: beginled7s1<=7'b0111111;led7s2<=7'b0111111;//数码管显示0分;end8'b0001: beginled7s1<=7'b0111111;led7s2<=7'b0000110;//数码管显示1分;end8'b0010: beginled7s1<=7'b0111111;led7s2<=7'b1011011;//数码管显示2分;end8'b0011: beginled7s1<=7'b0111111;led7s2<=7'b1001111;//数码管显示3分;end8'b0100: beginled7s1<=7'b0111111;led7s2<=7'b1100110;//数码管显示4分;end8'b0101: beginled7s1<=7'b0111111;led7s2<=7'b1101101;//数码管显示5分;end8'b0110: beginled7s1<=7'b0111111;led7s2<=7'b1111101;//数码管显示6分;end8'b0111: beginled7s1<=7'b0111111;led7s2<=7'b0000111;//数码管显示7分;end8'b1000: beginled7s1<=7'b0111111;led7s2<=7'b1111111;//数码管显示8分;end8'b1001: beginled7s1<=7'b0111111;led7s2<=7'b1101111;//数码管显示9分;end8'b1010: beginled7s1<=7'b0000110;led7s2<=7'b0111111;//数码管显示10分;end8'b1011: beginled7s1<=7'b0000110;led7s2<=7'b0000110;//数码管显示11分;enddefault: beginled7s1<=7'b0111111;led7s2<=7'b0111111;//数码管显示0分;endendcasecase(score_b)8'b0000: beginled7s3<=7'b0111111;led7s4<=7'b0111111;//数码管显示0分;end8'b0001: beginled7s3<=7'b0111111;led7s4<=7'b0000110;//数码管显示1分;end8'b0010: beginled7s3<=7'b0111111;led7s4<=7'b1011011;//数码管显示2分;end8'b0011: beginled7s3<=7'b0111111;led7s4<=7'b1001111;//数码管显示3分;end8'b0100: beginled7s3<=7'b0111111;led7s4<=7'b1100110;//数码管显示4分;end8'b0101: beginled7s3<=7'b0111111;led7s4<=7'b1101101;//数码管显示5分;end8'b0110: beginled7s3<=7'b0111111;led7s4<=7'b1111101;//数码管显示6分;end8'b0111: beginled7s3<=7'b0111111;led7s4<=7'b0000111;//数码管显示7分;end8'b1000: beginled7s3<=7'b0111111;led7s4<=7'b1111111;//数码管显示8分;end8'b1001: beginled7s3<=7'b0111111;led7s4<=7'b1101111;//数码管显示9分;end8'b1010: beginled7s3<=7'b0000110;led7s4<=7'b0111111;//数码管显示10分;end8'b1011: beginled7s3<=7'b0000110;led7s4<=7'b0000110;//数码管显示11分;enddefault: beginled7s3<=7'b0111111;led7s4<=7'b0111111;//数码管显示0分;endendcaseendendmodule4功能仿真功能仿真是最基本的仿真验证,它只能仿真设计中的逻辑功能。