实验三数据通路实验

计算机组成原理全部实验

一、实验目的

1.掌握简单运算器的数据传输方式。

3、P0K、P1K、P2K都置成系统方式;

4、信号连接线必须一一对应连接好。即在实验机左上方的信号接口与实验机右下方的信号接口分别一一对应连接。

左上方右下方

地址指针―――――――――――地址指针

地址总线―――――――――――地址总线〔在实验机右侧中部〕

数据总线―――――――――――数据总线〔在实验机右侧中部〕

运算暂存器DR1―――――――――运算暂存器DR1

运算暂存器DR2―――――――――运算暂存器DR2

微地址―――――――――――――微地址

检查完毕可以通电;

注意事项:

1、电脑屏幕上所有的按钮与实验机上的按钮完全对应。

2、在做实验时,要保证总线不发生冲突。即对总线操作时只有一个操作状态有效。

3、运算器、存储器、数据通路,三个实验按操作步骤操作即可

实验前把TJ,DP对应的逻辑开关置成11状态〔高电平输出〕,并预置以下逻辑电平状态:/ALU-BUS=1,/PC-BUS=1,R0-BUS=1,R1-BUS=1,R2-BUS=1时序发生器处于单拍输出状态,实验是在单步状态下进行DR1,DR2的数据写入及运算,以便能清楚地看见每一步的运算过程。

实验步骤按表1进行。实验时,对表中的逻辑开关进行操作置1或清0,在对DR1,DR2存数据时,按单次脉冲P0〔产生单拍T4信号〕。表1中带X的为随机状态,无论是高电平还是低电平,它都不影响运算器的运算操作。总线D7-D0上接电平指示灯,显示参与运算的数据结果。简单运算器的数据传送通路。

实验三数据通路组成实验

实验三数据通路组成实验一实验目的1.进一步熟悉计算机的数据通路2.将双端口通用寄存器堆和双端口存储器模块连接,构成新的数据通路3.掌握数字逻辑电路中的一般规律,以及排除故障的一般原则和方法4.锻炼分析问题和解决问题的能力,在出现故障的情况下,独立分析故障现象,并排除故障.二实验电路数据通路实验电路图如图所示。

它是将双端口存储器模块和双端口通用寄存器堆模块连接在一起形成的。

存储器的指令端口(右端口)不参与本次实验。

通用寄存器堆连接运算器模块,本次实验涉及其中的DRl。

由于双端口存储器是三态输出,因而可以直接连接到DBUS上。

此外,DBUS还连接着通用寄存器堆。

这样,写入存储器的数据由通用寄存器提供,从RAM中读出的数据也可以放到通用寄存器堆中保存。

本实验的各模块在以前的实验中都已介绍,请参阅前面相关章节。

注意实验中的控制信号与模拟它们的二进制开关的连接。

三、实验设备1. TEC-5计算机组成原理实验系统1台2.逻辑测试笔一支(在TEC-5实验台上)3.双踪示波器一台(公用)4.万用表一只(公用)四、实验任务1.将实验电路与控制台的有关信号进行连接。

2.用8位数据开关SW7-SW0向RF中的四个通用寄存器分别置入以下数据:R0=OFH,R1=0F0H,R2=55H,R3=0AAH.3.用8位数据开关向AR送入地址0FH,然后将R0中的数据0FH写入双端口存储器中.用同样的方法,依次将R1,R2,R3中的数据分别置入RAM的0F0H,55H,0AAH单元.4.分别将RAM的0AAH单元数据写入R0,55H单元数据写入R1,0F0H单元数据写入R2,0FH单元数据写入R3.然后将R0-R3中的数据读出,验证数据的正确性,并记录数据.五、实验要求1.做好实验预习,掌握实验电路的数据通路特点和通用寄存器堆的功能特性和使用方法。

2.写出实验报告,内容是:(1)实验目的。

(2)写出详细的实验步骤、记录实验数据及校验结果。

实验03 数据通路实验

实验三数据通路实验一、实验目的1、通过实验进一步熟悉运算器与存储器之间的数据通路的组成结构。

2、通过实验理解顺序节拍发生器的应用和设计方法。

3、通过实验理解系统总线的设计方法。

二、实验步骤1、打开已有的实验工程目录:“DATAPATH”。

通过双击目录中的Quartus II工程文件“DATAPATH.qpf”,利用Quartus II软件打开已经建好的实验工程。

图1打开Quartus II工程2、打开工程后,Quartus II软件的界面如图2所示。

在软件窗口的左边区域的“Project Navigator”列表栏中,选择“files”选项卡,我们可以看到列表栏中列出了这个工程中的设计文件。

本工程的设计文件说明在表1中列举出来。

表1工程设计文件说明表设计文件说明对应组件文件ALU.vhd VHDL设计文件,设计一个四位ALU ALU.bsfMEM.vhd VHDL设计文件,设计一个16*4的ROM存储器用来模拟主存MEM.bsfREG.vhd VHDL设计文件,设计一个带锁存和清零功能的四位寄存器REG.bsf PULSEGEN.vhd VHDL设计文件,设计一个顺序节拍发生器PULSEGEN.bsf DATAPATH.bdf数据通路设计文件其中,设计文件“DATAPATH.bdf”完成了基本功能,实验者首先对其进行验证,需要由实验者在原有设计基础上添加合理设计,完成数据通路时序控制的设计。

图2工程界面图3、如图3上所示,“数据通路”构建在DATAPATH.bdf的设计文件中,除去几个寄存器的脉冲信号,其它模块已经实现连接。

图3数据通路设计图数据通路是数据信号在各个寄存器和存储器之间的传输过程。

这里的设计文件模拟了最简单的数据通路模型。

图3中的“MEM”单元是一个用VHDL语言设计的16*4存储器,为了实验的简便,这里将它设计为ROM,而且从地址0000~1111依次存储的数据也是0~15(比如:地址为0011的存储单元存储的数据也是3)。

数据通路实验

数据通路实验预习报告1数据通路中运算器与存储器协调工作原理是什么?各个数据经过总线连接传输到运算器及存储器,并将运算结果通过数据通路传递到存储器,期间通过每个存储器及运算器的bus输出控制进行协调工作,使得数据不会在总线上冲突。

2、数据及地址在数据通路上传输方法。

通过不同数据控制信号进行传送。

地址信号及数据信号存储地方不同而且控制信号要求不同,通过这样的方法使得总线上数据不会冲突从而达到地址和数据在数据通路上的传输。

3、数据通路中需要注意各种控制信号的作用和设定值,否则不能仿真出正确的波形。

思考题:1、电路的初始状态怎么设置?有几个器件能够发送数据到总线,它们的控制信号是什么?(1)、令bus_sel全部为1,即令输出到总线的所有控制信号无效。

同时运算模块m|cn|s3|s2|s1|s0为000000,lddr信号都为无效,k输入数据为0。

(2)、能够发送数据到总线的器件为PC,R4,R5,,74244,ALU运算单元,RAM存储器单元。

其控制信号分别为PC_BUS,LDDR4,LDDR5,ALU_BUS,RD,WE。

2、画数据通路电路图时,如何连结单一总线?只需将标号标志为相同引脚即可实验数据在总线上的传送。

得到单一总线连接的数据通路电路图3、如何统一两个模块的总线数据输入端k[7..0]及inputd[7..0]?Inputd[7..0]可以不使用,直接将运算模块数据连入到存储器模块的双向输入输出部分,即可将数据送入到存储模块。

实验日志10月5日问题:RAM模块sw_bus为什么没有连接输入端?解决:发现RAM模块的sw_bus是控制inptud输出的信号线,不进行连接一样可以进行总线数据上的传送,其信号线不影响实验结果。

10月9日问题:为何资料上的波形图中ar地址显示与pc地址显示相差一个时间差?解决:通过分析数据通路的电路,发现pc的数据在更新时其之前的地址值已经传送到ar中,因此ar所得到的地址并非pc当时得到的。

计算机组成原理实验说明

实验一运算器组成实验一、实验目的1.熟悉双端口通用寄存器堆(组)的读写操作。

2.熟悉简单运算器的数据传送通路。

3.验证运算器74LS181的算术逻辑功能。

4.按给定数据,完成指定的算术、逻辑运算。

二、实验原理上图是本实验所用的运算器数据通路图。

参与运算的数据首先通过实验台操作板上的八个二进制数据开关SW7-SW0来设置,然后输入到双端口通用寄存器堆RF中。

RF由一个ispLSI1016实现,功能上相当于四个8位通用寄存器,用于保存参与运算的数据,运算后的结果也要送到RF中保存。

双端口寄存器堆模块的控制信号中,RS1、RS0用于选择从B端口(右端口)读出的通用寄存器,RD1、RD0用于选取从A端口(左端口)读出的通用寄存器。

而WR1、WR0用于选择写入的通用寄存器。

LDRi是写入控制信号,当LDRi=1时,数据总线DBUS上的数据在T3写入由WR1、WR0指定的通用寄存器。

RF的A、B端口分别与操作数暂存器DR1、DR2相连:另外,RF的B端口通过一个三态门连接到数据总线DBUS上,因而RF 中的数据可以直接通过B端口送到DBUS上。

DR1和DR2各由1片74LS273构成,用于暂存参与运算的数据。

DR1接ALU 的A输入端口,DR2接ALU的B端口。

ALU由两片74LS181构成,ALU的输出通过一个三态门(74LS244)发送到数据总线DBUS上。

图中尾巴上带粗短线标记的信号都是控制信号,其中S3,S2,Sl,S0,M,Cn#,LDDR2,LDDRl, ALU-BUS#,SW-BUS#、LDRi、RS1、RS0、RD1、RD0、WR1、WR0等是电位信号,用电平开关K0—Kl5来模拟。

T2、T3是脉冲信号,印制板上已连接到实验台的时序电路上。

#为低电平有效。

K0—K15是一组用于模拟各控制电平信号的开关,开关向上时为1,开关向下时为0,每个开关无固定用途,可根据实验具体情况选用。

实验中进行单拍操作,每次只产生一组Tl,T2,T3,T4脉冲,需将实验台上的DP,DB开关进行正确设置。

计算机组成原理实验(接线、实验步骤)方案

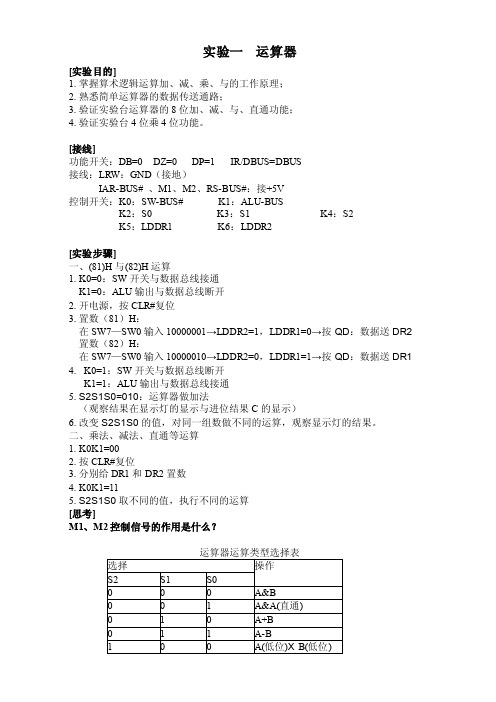

实验一运算器[实验目的]1.掌握算术逻辑运算加、减、乘、与的工作原理;2.熟悉简单运算器的数据传送通路;3.验证实验台运算器的8位加、减、与、直通功能;4.验证实验台4位乘4位功能。

[接线]功能开关:DB=0 DZ=0 DP=1 IR/DBUS=DBUS接线:LRW:GND(接地)IAR-BUS# 、M1、M2、RS-BUS#:接+5V控制开关:K0:SW-BUS# K1:ALU-BUSK2:S0 K3:S1 K4:S2K5:LDDR1 K6:LDDR2[实验步骤]一、(81)H与(82)H运算1.K0=0:SW开关与数据总线接通K1=0:ALU输出与数据总线断开2.开电源,按CLR#复位3.置数(81)H:在SW7—SW0输入10000001→LDDR2=1,LDDR1=0→按QD:数据送DR2置数(82)H:在SW7—SW0输入10000010→LDDR2=0,LDDR1=1→按QD:数据送DR1 4.K0=1:SW开关与数据总线断开K1=1:ALU输出与数据总线接通5. S2S1S0=010:运算器做加法(观察结果在显示灯的显示与进位结果C的显示)6.改变S2S1S0的值,对同一组数做不同的运算,观察显示灯的结果。

二、乘法、减法、直通等运算1.K0K1=002.按CLR#复位3.分别给DR1和DR2置数4.K0K1=115. S2S1S0取不同的值,执行不同的运算[思考]M1、M2控制信号的作用是什么?运算器运算类型选择表选择操作S2 S1 S00 0 0 A&B0 0 1 A&A(直通)0 1 0 A+B0 1 1 A-B1 0 0 A(低位)ΧB(低位)完成以下表格ALU-BUS SW-BUS# 存储器内容S2S1S0 DBUS C输入时:计算时:DR1:01100011DR2:10110100(与)DR1:10110100DR2:01100011(直通)DR1:01100011DR2:01100011(加)DR1:01001100DR2:10110011(减)DR1:11111111DR2:11111111(乘)实验二双端口存储器[实验目的]1.了解双端口存储器的读写;2.了解双端口存储器的读写并行读写及产生冲突的情况。

计算机组成原理 实验3

实验3通用寄存器实验一、实验目的1.熟悉通用寄存器的数据通路。

2.掌握通用寄存器的构成和运用。

二、实验要求在掌握了AX、BX运算寄存器的读写操作后,继续完成CX、DX通用寄存器的数据写入与读出。

三、实验原理实验中所用的通用寄存器数据通路如下图所示。

由四片8位字长的74LS574组成CX(R1 R0)、DX(R3 R2)通用寄存器组。

图中X2 X1 X0定义输出选通使能,SI、XP控制位为源选通选择。

RXW为寄存器数据写入使能,OP、DI为目的寄存器选择。

DRCK信号为寄存器写脉冲,下降沿有效。

准双向I/O输入输出端口用于置数操作,经2片74LS245三态门与数据总线相连。

图2-3-3通用寄存器数据通路四、实验内容五、实验过程 & 实验结果1.寄存器组写操作(1)(2)寄存器组的字写入通过“I/O单元”把CX的地址00打入IR,然后向CX写入2211h,操作步骤如下:按【单拍】按钮通过“I/O单元”把DX的地址02打入IR,然后向DX写入4433h,操作步按【单拍】按钮(3)寄存器组的字节写入通过“I/O单元”把CX的地址00打入IR,然后向CL写入55h,操作步骤按【单拍】按钮按【单拍】按钮K21 K16 K2=000 K21 K6 K2=111在IR保持为“XX00”的条件下,可省略打地址环节,按下流程向CH写入AAh2.寄存器读操作(1)(2)寄存器组字读(3)寄存器组字节读CH。

K7=1K10~K6=00101准双向I/O口实验一、实验目的熟悉与了解准双向I/O口的构成原理。

二、实验要求掌握准双向I/O口的输入/输出特性的运用。

三、实验原理Dais-CMX16+向用户提供的是按准双向原理设计的十六位输入/输出I/O口,当该位为“1”时才能用作输入源,上电或复位(手动态按【返回】键),该十六位I/O口被置位(即为“0FFFFh”)。

通常情况下,在用作输入的时候就不能再有输出定义。

电路结构如图2-3-4所示。

组成原理实验

实验一运算器实验1、实验内容利用两片74LS181以并、串形式构成8位字长的ALU。

运算器的输出经过一个三态门和数据总线相连,运算器的两个数据输入端分别由两个锁存器锁存,锁存器的输入连至数据总线。

数据开关用来给出参与运算的数据,运算结果经过数据线,通过显示灯显示。

内容:1)掌握简单运算器的数据传输方式2)验证运算功能发生器及进位控制的组合功能2、实验目的及要求掌握运算器的数据传送通路;验证运算功能发生器(74LS181)的组合功能。

要求:完成不带进位及带进位算术运算实验、逻辑运算实验,了解算术逻辑运算单元的运用。

3、实验重点运算器的数据传送通路;运算功能发生器(74LS181)的组合功能。

4、实验难点运算器的数据传送通路;运算功能发生器(74LS181)的组合功能。

5、实验时间分配及进度安排3学时6、主要实验环节的组织教师提示实验原理,学生自己设计实验。

实验2.存储器实验内容:1)向静态随机存储器写入数据2)读出数据显示要求:掌握静态随机存储器工作特性及数据的读写方法实验3.数据通路组成实验内容:连接运算器实验模块和存储器实验模块要求:将运算器实验模块和存储器实验模块两部分电路连接在一起,掌握数据通路组成。

实验4.微程序控制器实验内容:1)时序信号产生器、微程序控制电路2)微指令设计格式、微程序编制要求:掌握时序产生器的组成原理、掌握微程序控制器的组成原理、掌握微程序的编制、观察微程序的运行。

实验5.模型机CPU组成与指令周期实验内容:1)连接微程序控制器模拟、运算器模块、存储器模块2)指令周期实验要求:将微程序控制器模拟,运算器模块,存储器模块组合在一起,联成一台简单的计算机,并进行指令周期实验。

实验6.基本模型机设计与实现内容:1)定义机器指令2)编写相应微程序,上机调试要求:在掌握部件单元电路实验的基础上,进一步将其组成系统地构造一台基本模型计算机,编写相应的微程序,上机调试掌握整机概念。

数据通路实验报告121544120

LDZ

LDC

记录

0

1

0

1

1

0

0

是否有效

无效

有效

无效

无效

有效

无效

无效

功能

无

无

无

无

无

无

无

信号

RAMBUS

LAR#

SELAR

LRW

PCINC

LPC#

CLR#

记录

0

1

0

0

0

1

0

是否有效

无效

无效

无效

无效

无效

无效

无效

功能

无

无

无

无

无

无

无

指示灯

μA5-μA0

D7-D0

A7-A0

B7-B0

C

Z

记录

10 0101

0011 0101

有效

有效

有效

有效

有效

有效

有效

功能

无

无

无

无

无

无

无

信号

SEL3

SEL2

SEL1

SEL0

LR

LDZ

LDC

记录

0

0

0

1

0

0

0

是否有效

无效

有效

无效

有效

有效

无效

无效

功能

无

无

无

无

无

无

无

信号

RAMBUS

LAR#

SELAR

LRW

PCINC

LPC#

CLR#

记录

0

0

计算机组成原理全部实验

(2)LDDR1:控制把总线上的数据打入运算暂存器DR1,高电平有效。

(3)LDDR2:控制把总线上的数据打入运算暂存器DR2,高电平有效。

(4)S3,S2,S1,S0:确定执行哪一种算术运算或逻辑运算(运算功能表见附录1或者课本第49页)。

(5)M:M=0执行算术操作;M=1执行逻辑操作。

X

X

1

0

0

1

AAH

AAH

↑

向DR1送数

X X X X

X

X

0

1

0

1

55H

55H

↑

向DR2送数

0 0 0 0

0

1

0

0

1

0

XXH

AAH

算术运算

0 0 0 0

0

0

0

0

1

0

XXH

ABH

算术运算

0 0 0 0

1

X

0

0

1

0

XXH

55H

逻辑运算

0 0 0 1

0

1

0

0

1

0

XXH

FFH

算术运算

0 0 0 1

0

0

0

0

1

0

5.不管是手动方式还是系统方式,31个按钮开关初始状态应为“1”即对应的指示灯处于发光的状态。

6.位于UPC UNIT区的J1跳线开关应在右侧状态。

说明:开关AL-BUS;SW-BUS标识符应为“/AL-BUS;/SW-BUS”

注意事项:

AL-BUS;SW-BUS不能同时按下;因为同时按下会发生总线冲突,损坏器件。

1

数据通路实验

数据通路实验一、实验目的1、进一步熟悉TEC-8模型计算机的数据通路的结构2、进一步掌握数据通路中各个控制信号的作用和用法3、掌握数据通路中数据流动的路径二、实验仪器或设备1、TEC-8计算机硬件综合实验系统2、直流万用表3、逻辑测试笔实验电路数据通路实验的电路图:三、总体设计(设计原理、设计方案及流程等)实验任务(1)将数75H写到寄存器R0,数28H写道寄存器R1,数89H写到寄存器R2,数32H 写到寄存器R3。

(2)将寄存器R0中的数写入存储器20H单元,将寄存器R1中的数写入存储器21H单元,将寄存器R2中的数写入存储器22H单元,将寄存器R3中的数写入存储器23H单元。

(3)从存储器20H单元读出数到存储器R3,从存储器21H单元读出数到存储器R2,从存储器21H单元读出数到存储器R1,从存储器23H单元读出数到存储器R0。

(4)显示4个寄存器R0、R1、R2、R3的值,检查数据传送是否正确。

在进行数据运算操作时,由RD1、RD0选中的寄存器通过4选1选择器A送往ALU 的A端口,由RS1、RS0选中的寄存器通过4选1选择器B送往ALU的B端口;信号M、S3、S2、S1、S1和S0决定ALU的运算类型,ALU对A端口和B端口的两个数连同CIN 的值进行算数逻辑运算,得到的数据运算结果在信号ABUS为1时送往数据总线DBUS;在T3的上升沿,数据总线DBUS上的数据结果写入由RD1、RD0选中的寄存器。

在寄存器之间进行数据传送操作时,由RS1、RS0选中的寄存器通过4选1选择器B 送往ALU的B端口;ALU将B端口的数在信号ABUS为1时送往数据总线DBUS;在T3的上升沿将数据总线上的数写入由RD1、RD0选中的寄存器。

ALU进行数据传送操作由一组特定的M、S3、S2、S1、S0、CIN的值确定。

在进行运算操作时,由RS1、RS0选中的寄存器通过4选1选择器B送往ALU的B端口;由RD1、RD0选中的寄存器通过4选1选择器A送往ALU的A端口;ALU对数A和B进行运算,运算的数据结果在信号ABUS为1时送往数据总线DBUS;在T3 的上升沿将数据总线上的数写入由RD1、RD0选中的寄存器。

实验三16位算术逻辑运算实验

实验三16位算术逻辑运算实验实验三16位算术逻辑运算实验⼀、实验⽬的1、掌握16位算术逻辑运算数据传送通路组成原理。

2、进⼀步验证算术逻辑运算功能发⽣器74L S181的组合功能。

⼆、实验内容1、实验原理实验中所⽤16位运算器数据通路如图3-3所⽰。

其中运算器由四⽚74L S181以并/串形成16位字长的A L U构成。

低8位运算器的输出经过⼀个三态门74L S245(U33)到内部总线,低8位数据总线通过L Z D0~L Z D7显⽰灯显⽰;⾼8位运算器的输出经过⼀个三态门74L S245(U33`)到A L U O1`插座,实验时⽤8芯排线和⾼8位数据总线B U S D8~D15插座K B U S1或K B U S2相连,⾼8位数据总线通过L Z D8~L Z D15显⽰灯显⽰;参与运算的四个数据输⼊端分别由四个锁存器74L S273(U29、U30、U29`、U30、)锁存,实验时四个锁存器的输⼊并联连⾄内部数据总线再⽤8芯线连接到外部数据总线E X D0~D7插座E X J1~E X J3中的任⼀个;参与运算的数据源来⾃于8位数据开并K D0~K D7,并经过⼀三态门74L S245(U51)直接连⾄外部数据总线E X D0~E X D7,输⼊的数据通过L D0~L D7显⽰。

2、实验接线本实验⽤到6个主要模块:⑴低8位运算器模块,⑵数据输⼊并显⽰模块,⑶数据总线显⽰模块,⑷功能开关模块(借⽤微地址输⼊模块),⑸⾼8位运算器模块,⑹⾼8位(扩展)数据总线显⽰模块。

根据实验原理详细接线如下:1、J20,J21,J22,接上短路⽚,图3-1.J20,J21,J22接上短路⽚2、J24,J25,J26接左边;图3-2.J24,J25,J26接左边3、J27,J28 左边图3-3.J27,J28接左边4、J23 置右边T4选“SD”图3-4.J23接右边5、JA5 置“接通”;图3-5.JA5置上⽅“接通”6、JA6 置“⼿动”;图3-6.JA6置下边“⼿动”7、JA3 置“接通”;图3-7.JA3置右边“接通”8、JA1,JA2,JA4置“⾼阻”;图3-8.JA1、JA2接下边“⾼阻”图3-9.JA4置左边“⾼阻”9、JA8 置上⾯“微地址”图3-10.JA8置上⾯“微地址”10、EXJ1接BUS3图3-11.EXJ1接BUS3 11、ALO1'接KBUS1图3-12.ALO1接KBUS1 12、开关CE 、AR 置1图3-13.CE与AR各⾃置113、ZI2,CN4,CN0接上短路⽚图3-14.Z12,CN4和CN0都接上短路⽚3、实验步骤⑴连接线路,仔细查线⽆误后,接通电源。

计组实验数据通路实验报告

存储器实验预习实验报告疑问:1、数据通路是干嘛的?2、数据通路如何实现其功能?3、实验书上的存储器部分总线开关接在高电平上,是不是错了?实验报告一、波形图:参数设置:Endtime:2.0us Gridsize:100.0ns信号设置:clk:时钟信号,设置周期为100ns占空比为50%。

bus_sel: sw|r4|r5|alu|pc_bus的组合,分别代表的是总线(sw_bus)开关,将存储器r4的数据显示到总线上,将存储器r5的数据显示到总线上,将alu的运算结果显示到总线上,将pc的数据打入AR中二进制输入,低电平有效。

alu_sel:m|cn|s[3..0]的组合,代表运算器的运算符号选择,二进制输入,高电平有效。

ld_reg:lddr1|lddr2|ldr4|ldr5|ld_ar的组合,分别表示将总线数据载入寄存器r1,r2,r4, r5或AR中,二进制输入,高电平有效。

pc_sel: pc_clr|ld|en的组合,分别代表地址计数器PC的清零(pc_clr)、装载(pc_ld)和计数使能信号(pc_en),二进制输入,低电平有效。

we_rd:信号we和rd的组合,分别代表对ram的读(we)与写(rd)的操作,二进制输入,高电平有效k:k [7]~ k [0],数据输入端信号,十六进制输入。

d: d[7]~d[0],数据输出中间信号,十六进制双向信号。

d~result: d [7] result ~d[0] result,最终的数据输出信号,十六进制输出。

ar: ar[7]~ ar[0],地址寄存器AR的输出结果,十六进制输出。

pc: pc [7]~ pc [0],地址计数器PC的输出结果,十六进制输出。

仿真波形以在01H单元中写入05H、02H单元中写入0AH并进行【(A加B)减(非A与B)加B】为例:1)初始状态:bus_sel=11111,alu_sel=00000,ld_reg=00000,pc_sel=100,we_rd=00,k=00H,总线上无数据,呈高阻态。

实验三 数据通路(总线)实验

.实验三数据通路(总线)实验一、实验目的(1)将双端口通用寄存器堆和双端口存储器模块联机;(2)进一步熟悉计算机的数据通路;(3)掌握数字逻辑电路中故障的一般规律,以及排除故障的一般原则和方法;(4)锻炼分析问题与解决问题的能力,在出现故障的情况下,独立分析故障现象,并排除故障。

二、实验电路图8示出了数据通路实验电路图,它是将双端口存储器实验模块和一个双端口通用寄存器堆模块(RF)连接在一起形成的。

双端口存储器的指令端口不参与本次实验。

通用寄存器堆连接运算器模块,本实验涉及其中的操作数寄存器DR2。

由于双端口存储器RAM是三态输出,因而可以将它直接连接到数据总线DBUS上。

此外,DBUS上还连接着双端口通用寄存器堆。

这样,写入存储器的数据可由通用寄存器提供,而从存储器RAM读出的数据也可送到通用寄存器堆保存。

双端口存储器RAM已在存储器原理实验中做过介绍,DR2运算器实验中使用过。

通用寄存器堆RF(U32)由一个ISP1016实现,功能上与两个4位的MC14580并联构成的寄存器堆类似。

RF内含四个8位的通用寄存器R0、RI、R2、R3,带有一个写入端口和两个输出端口,从而可以同时写入一路数据,读出两路数据。

写入端口取名为WR端口,连接一个8位的暂存寄存器(U14)ER,这是一个74HC374。

输出端口取名为RS端口(B端口)、RD端口(A端口),连接运算器模块的两个操作数寄存器DR1、DR2。

RS端口(B端口)的数据输出还可通过一个8位的三态门RS0(U15)直接向DBUS输出。

双端口通用寄存器堆模块的控制信号中,RS1、RS0用于选择从RS端口(B 端口)读出的通用寄存器,RD1、RD0用于选择从RD端口(A端口)读出的通用寄存器。

而WR1、WR0则用于选择从WR端口写入的通用寄存器。

WRD是写入控制信号,当WRD=1时,在T2上升沿的时刻,将暂存寄存器ER中的数据写入通用寄存器堆中由WR1、WR0选中的寄存器;当WRD=0时,ER中的数据不写入通用寄存器中。

常规数据通路组成实验3

实验三常规数据通路组成实验一、实验目的1.在线连接双端口通用寄存器和双端口内存模块。

2.熟悉电脑的数据路径。

3.掌握数字逻辑电路故障的一般规律,以及排除故障的一般原则和方法。

4、锻炼分析和解决问题的能力,在出现故障的情况下,独立分析故障现象,并排除故障。

第二,实验类型认证类型。

第三,实验仪器1.TEC-4计算机构成原理实验仪器。

2.一个双踪示波器。

3.一个DC万用表。

4.一支逻辑测试笔。

四、实验原理图3为数据通路实验的电路图,由双端口内存实验模块和双端口通用寄存器模块(RF)连接而成。

本实验不涉及双端口内存的指令端口。

通用寄存器文件连接到运算器模块,这个实验涉及到操作数寄存器DR2。

由于双端口内存RAM是三态输出,因此可以直接连接到数据总线DBUS。

此外,DBUS还连接了一个双端口通用寄存器文件。

这样,写入内存的数据可以由通用寄存器提供,从内存RAM 读取的数据也可以发送到通用寄存器文件保存。

实验2使用了双端口RAM,实验1使用了DR2。

通用寄存器文件RF(U32)由一个ISP1016实现,功能类似于两个4位并行的MC14580组成的寄存器文件。

射频包含四个8位通用寄存器R0、R1、R2和R3,带有一个写端口和两个输出端口,因此一个通道的数据可以同时写入。

读出两种数据。

名为WR端口的写端口连接到一个8位临时寄存器(U14)ER,它是一个74HC374。

名为RS(端口b)和RD(端口a)的输出端口连接到算术单元模块的两个操作数寄存器DR1和DR2。

RS端口(B端口)的数据输出也可以通过8位三态门RSO(U15)直接输出到DBUS。

在双端口通用寄存器文件模块的控制信号中,RS1和RS0用于选择从RS端口(B端口)读取的通用寄存器,RD1和RD0用于选择从RD端口(A端口)读取的通用寄存器。

而WR1和WR0用于选择从WR端口写入的通用寄存器。

WRD是写控制信号。

当WRD=1时,在T2上升沿将临时寄存器er中的数据写入通用寄存器文件中RD1和RD0选择的寄存器;当WRD=0时,电流变位寄存器中的数据不写入通用寄存器,并且电流变位信号控制电流变位寄存器从数据总线写入数据。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

实验三数据通路实验

一、实验目的

1.了解运算模块与存储器模块如何连接;

2.了解各寄存器控制信号作用;

3.掌握数据通路实验的设计方法。

二、实验仪器

COP2000实验仪。

三、实验原理

数据通路实验是将前面进行过的运算器实验模块和存储器实验模块两部分电路连在一起组成的。

数据通路指CPU中各个寄存器之间信息传递的通路,建立数据通路的方法,例如:寄存器X输出控制信号有效,寄存器Y输入控制信号有效,就建立了X—>Y的数据通路。

寄存器部分控制信号:

寄存器选择信号:输出寄存器选择信号:

四、实验内容及步骤

1.自行设计一个寄存器间进行数据传送的实验,并且完成,写明操作步骤和所用到的控制信号状态。

2.下面给出一个例子。

完成R1+R2=R0的实验。

填写表3-1。

表3-1 数据通路实验结果记录表

3.自己设计操作骤,完成A=(B*2+C)/2-D,并设计表格3-2记录操作步骤和实验结果。

其中:A,B分别为存储单元,C、D为寄存器,B、C、D的内容事先自行写入。

五、实验报告要求

1.自己设计例子或使用上面的例子,写在实验报告上。

2.按实验报告上要求,完成实验报告。

六、思考题

说明将运算结果存入寄存器A的方法?。