Lattice Diamond软件安装说明

Lattice编程电缆用户指南说明书

Programming CablesUser’s GuideFeatures•Support for all Lattice programmable products–1.2 V to 3.3 V programming (HW-USBN-2B)–1.2 V to 5 V programming (All other cables)–Ideal for design prototyping and debugging•Connect to multiple PC interfaces–USB (v.1.0, v.2.0)–PC Parallel Port•Easy-to-use programming connectors•Versatile flywire, 2 x 5 (.100”) or 1 x 8 (.100”) connectors•6 feet (2 meters) or more of programming cable length (PC to DUT)•Lead-free/RoHS compliant constructionFigure 1. USB Cable – HW-USBN-2BProgramming CablesLattice Programming Cable products are the hardware connection for in-system programming of all Lattice devices. After completion of the logic design and creation of a programming file with the Lattice Diamond®, ispLEVER® Clas-sic or PAC-Designer® software, the Lattice Diamond Programmer, or Lattice's ispVM™ System software is used to control the programming of devices directly on the PC board. No additional components are required to program a device.After you complete your logic design and create a programming file with the Lattice Diamond/ispLEVER Classic development tools, you can use Diamond Programmer or ispVM™ System software ispVM™ System software or Diamond Programmer to program devices on your board. The ispVM System/Diamond Programmer software auto-matically generates the appropriate programming commands, programming addresses and programming data based on information stored in the programming file and parameters you set in Diamond Programmer/ispVM Sys-tem. Programming signals are then generated from the USB or parallel port of a PC and directed through the Pro-gramming Cable to the device. No additional components are required for programming.Diamond Programmer/ispVM System software is included with all Lattice design tool products and is available for download from the Lattice web site at .Programming Cable Pin DefinitionsThe functions provided by the Programming cables correspond with available functions on Lattice programmable devices. Since some devices contain different programming features, the specific functions provided by the Pro-gramming cable may depend on the selected target device. ispVM System/Diamond Programmer software will automatically generate the appropriate functions based on the selected device. See Table 1 for an overview of the Programming cable functions.Table 1. Programming Cable Pin DefinitionsProgramming Cable Pin NameProgramming CablePin TypeDescriptionVCCProgramming VoltageInputConnect to V CC or V CCJ plane of the target device. T ypical I CC = 10mA. Y our board design supplies the power for V CC . Note: This may not be the same as a target device’s V CCO plane.SDO/TDO Test Data Output Input Used to shift data out via the IEEE1149.1 (JT AG) programming standard.SDI/TDITest Data InputOutput Used to shift data in via the IEEE1149.1 programming standard.ispEN/Enable/PROG/SN EnableOutput Enable device to be programmed.SN = SSPI Chip select for HW-USBN-2B TRST Test Reset Output Optional IEEE 1149.1 state machine reset. DONE DONEInput DONE indicates status of configuration MODE/TMS Test Mode Select Input Output Used to control the IEEE1149.1 state machine.GND GroundInput Connect to ground plane of the target device SCLK/TCK Test Clock Input Output Used to clock the IEEE1149.1 state machineINIT Initialize Input Indicates that ORCA ® device is ready for configuration.I2C: SCL 1I2C SCL Output Provides the I2C signal SCL I2C: SDA 1I2C SDA Output Provides the I2C signal SDA.5V Out 15V OutOutputProvides a 5V signal for the iCEprog M1050 Programmer.1.Only found on the HW-USBN-2B cable.Figure 2. Programming Cable In-System Programming Interface for the PC (HW-USBN-2B)11.Requires Diamond Programmer 3.1 or laterFigure 3. Programming Cable In-System Programming Interface for the PC (HW-USB-1A or HW-USB-2A)1ttice PAC-Designer® software does not support programming with USB cables. To program ispPAC devices with these cables, use the Dia-mond Programmer/ispVM System software.Figure 4. Programming Cable In-System Programming Interface for the PC (HW-DLN-3C and Equivalents)11.HW7265-DL3, HW7265-DL3A, HW-DL-3B, HW-DL-3C and HW-DLN-3C are functionally equivalent products.Figure 5. Programming Cable In-System Programming Interface for the PC (pDS4102-DL2 or pDS4102-DL2A)Figure 6. Programming Cable In-System Programming Interface for the PC (HW7265-DL2 or HW7265-DL2A)1.For reference purposes, the 2x10 connector on the HW7265-DL2 or HW7265-DL2A is equivalent to Tyco 102387-1. This will interface tostandard 100-mil spacing 2x5 headers, or a 2x5 keyed, recessed male connector such as the 3M N2510-5002RB.Programming SoftwareDiamond Programmer and ispVM System for Classic devices is the preferred programming management soft-ware tool for all Lattice devices and download cables. The latest version of Lattice Diamond Program-mer or ispVM System software is available for download from the Lattice web site at /software. Target Board Design ConsiderationsA 4.7K pull-down resistor is recommended on the TCK connection of the target board. This pull-down is recom-mended to avoid inadvertent clocking of the TAP controller induced by fast clock edges or as V CC ramps up. This pull-down is recommended for all Lattice programmable families.The I2C signals SCL and SDA are open drain. A 2.2K pull-up resistor to VCC is required on the target board.For Lattice device families that feature low power, it is recommended to add a 500 ohm resistor between V CCJ and GND during the programming interval when a USB Programming cable is connected to a very low power board design. A FAQ is available that discusses this in more depth at:/en/Support/AnswerDatabase/2/2/0/2205The JTAG programming port speed may need to be governed when using the Programming cables connected to customer PCBs. This is especially important when there is long PCB routing or with many daisy-chained devices. The Lattice programming software can adjust the timing of TCK applied to the JTAG programming port from the cable. This low-precision port setting of TCK depends on many factors, including the PC speed and the type of cable used (parallel port, USB or USB2). This software feature provides an option to slow the TCK for debug or noisy environments. A FAQ is available that discusses this in more depth at:/en/Support/AnswerDatabase/9/7/974.aspxThe USB Download Cable can be used to program Power Manager or ispClock products with Lattice programming software. When using the USB cable with the Power Manager I devices, (POWR604, POWR1208, POWR1208P1), you must slow do TCK by a factor of 2. A FAQ is available that discusses this in more depth at:/en/Support/AnswerDatabase/3/0/306.aspxProgramming Flywire and Connection ReferenceRefer to T able 2 when connecting a flywire download cable to systems that use the 1x8-position or 2x5-position connectors. For newer Lattice FPGA families, a 1x10 connector used in conjunction with the Programming USB cable adds support for the DONE and INITN signals. Both of these signals are inputs to the cable, and can be used to help verify device configuration.Table 2. Flywire Conversion ReferenceFunction FlywireCableWireLabel1x10Connector1x8Connector2x5ConnectorV CC1Red VCC116 TDO/SO/SPI_SO Brown TDO227TDI/SI/SPI_SI Orange TDI335 ispEN2/Enable/PROGRAMN/SN/SPI_SS_B Y ellow ispEN/PROG4410 TRST3/CRESET_B Green TRST/DONE559 TMS/MODE Purple TMS663 GND Black GND77 4 (2 and 8) TCK4/SCLK/CCLK/SPI_SCK White TCK881 DONE3Green TRST/DONE9INITN/CDONE Blue INITN10I2C SCL5, 6Y ellow/White I2C: SCLI2C SDA5,6Green/White I2C: SDATable 3 lists the recommend pin connections. Please contact Lattice technical support for information on unlisted devicefamilies.(e-mail:***************************).Table 3. Recommended Pin ConnectionsDevice FamilyTDITDOTMSTCKispEN/P ROG 1,6TRST 2/D ONE 3,6INITN 3,6VCCGNDSCLSDAECP5™Mandatory Mandatory Mandatory Mandatory Optional Optional Optional Mandatory Mandatory N/A N/A LatticeECP3™Mandatory Mandatory Mandatory Mandatory Optional Optional Optional Mandatory Mandatory N/A N/A LatticeECP2M™/LatticeECP2™Mandatory Mandatory Mandatory Mandatory Optional Optional Optional Mandatory Mandatory N/A N/A LatticeECP™/LatticeEC™Mandatory Mandatory Mandatory Mandatory Optional Optional Optional Mandatory Mandatory N/A N/A LatticeXP2™Mandatory Mandatory Mandatory Mandatory Optional Optional Optional Mandatory Mandatory N/A N/A LatticeXP™Mandatory Mandatory Mandatory Mandatory Optional Optional Optional Mandatory Mandatory N/A N/A LatticeSC™/LatticeSCM™Mandatory Mandatory MandatoryMandatory Optional Optional Optional Mandatory Mandatory N/A N/A iCE40™/iCE40LM/iCE40 Ultra™Mandatory Mandatory N/A Mandatory MandatoryRecom-mended Recom-mended Mandatory Mandatory N/A N/A MachXO2™/MachXO3™Mandatory Mandatory Mandatory Mandatory N/A N/A N/A Mandatory Mandatory Optional Optional MachXO™Mandatory Mandatory Mandatory Mandatory N/A N/A N/A Mandatory Mandatory N/A N/A ORCA ®/FPSC Mandatory Mandatory Mandatory Mandatory Optional Optional Optional Mandatory Mandatory N/A N/A ispXPGA®Mandatory Mandatory Mandatory Mandatory N/A N/A N/A Mandatory Mandatory N/A N/A ispXPLD™Mandatory Mandatory Mandatory Mandatory N/A N/A N/A Mandatory Mandatory N/A N/A ispMACH ®4000Mandatory Mandatory Mandatory Mandatory N/A N/A N/A Mandatory Mandatory N/A N/A ispMACH/ispLSI® 5000Mandatory Mandatory Mandatory Mandatory N/A N/A N/A Mandatory Mandatory N/A N/A MACH ®4A4Mandatory Mandatory Mandatory Mandatory N/A N/A N/A Mandatory Mandatory N/A N/A ispGDX2™Mandatory Mandatory Mandatory Mandatory N/A N/A N/A Mandatory Mandatory N/A N/A ispClock™Mandatory Mandatory Mandatory Mandatory N/A N/A5N/A Mandatory Mandatory N/A N/A Platform Manager™Mandatory Mandatory Mandatory Mandatory N/A Optional 5N/A Mandatory Mandatory N/A N/A Power Manager/Power Manager II Mandatory Mandatory Mandatory Mandatory N/A Optional 5N/A Mandatory Mandatory N/A N/A ispPAC ®MandatoryMandatoryMandatoryMandatoryN/AN/AN/AMandatoryMandatoryN/AN/A1. Refer to the Programming Cable ispEN Pin section below for detailed information on connecting the ispEN/ENABLE pin.2. Refer to the Programming Cable TRST Pin section below for detailed information on connecting the TRST pin.3. The DONE and INITN signals are only available on the Programming USB cable. These signals are inputs to the cable and can be used to help verify deviceconfiguration.4. Please refer to the device data sheet. Not all packages have the ENABLE or TRST pin.5.When using P AC-Designer ® software to program ispPAC devices, do not connect this pin.6.When using these connections, be sure to select the correct settings in the Cable and I/O Port Setup dialog in the ispVM System/Diamond Programmer soft-ware.5V Output 5Red/White5V Out1.For devices that have a V CCJ pin, the V CCJ must be connected to the cable’s V CC, and a 0.1µF decoupling capacitor is required on V CCJ close to the device. Please refer to the device data sheet to determine if the device has a V CCJ pin.2.For older Lattice ISP devices, a 0.01µF decoupling capacitor is required on ispEN/ENABLE of the target board.3.The TRST and DONE pin is multiplexed on the Programming USB cable. If the device TRST signal is available on the board, connect the USB flywire TRST/DONE wire to TRST. If the device DONE signal is available on the board (or if both TRST and DONE are available), con-nect the USB flywire TRST/DONE wire to DONE. Please make sure the correct setting is selected in ispVM/Diamond Programmer (Options, Cable and I/O Port Setup). This will tell ispVM/Diamond Programmer whether the TRST/DONE cable is used as a TRST or a DONE signal.4.A 4.7K pull-down resister is recommended on TCK of the target board.5.Only on the HW-USB2N-2B cable6.Open drain signals. External pull-up ~2.2KOhm resistor to VCC is required.Table 2. Flywire Conversion Reference (Continued)FunctionFlywire Cable Wire Label 1x10 Connector1x8 Connector2x5 ConnectorConnecting the Programming CableThe target board must be un-powered when connecting, disconnecting, or reconnecting the Programming Cable. Always connect the Programming Cable’s GND pin (black wire), before connecting any other JTAG pins. Failure to follow these procedures can result in damage to the target programmable device.Programming Cable TRST PinConnecting the board TRST pin to the cable TRST pin is not recommended. Instead, connect the board TRST pin to Vcc. If the board TRST pin is connected to the cable TRST pin, instruct ispVM/Diamond Programmer to drive the TRST pin high as follows:1.Select the Options menu item.2.Select Cable and I/O Port Setup.3.Check the TRST/Reset Pin Connected checkbox.4.Select the Set High radio button.If the proper option is not selected, the TRST pin will be driven low by ispVM/Diamond Programmer. Consequently, the BSCAN chain will not work because the chain will be locked into RESET state.Programming Cable ispEN PinThe following pins should be grounded:•BSCAN pin of the 2000VE devices•ENABLE pin of MACH4A3/5-128/64, MACH4A3/5-64/64 and MACH4A3/5-256/128 devices.However, the user has the option of having the BSCAN and ENABLE pins driven by the ispEN pin from the cable. In this case, ispVM/Diamond Programmer must be configured to drive the ispEN pin low as follows:1.Select the Options menu item.2.Select Cable and I/O Port Setup.3.Check the ispEN/BSCAN Pin Connected checkbox.4.Select the Set Low radio button.Table 4.Feature HW-USBN-2B HW-USBN-2A HW-USB-2A HW-USB-1A HW-DLN-3CHW7265-DL3,HW7265-DL3A,HW-DL-3B,HW-DL-3C HW7265-DL2HW7265-DL2A PDS4102-DL2PDS4102-DL2AUSB X X X XPC-Parallel X X X X X X 1.2 V Support X X X1.8 V Support X X X X X X X X2.5-3.3 V Support X X X X X X X X X X 5.0 V Support X X X X X X X X X 2x5 Connector X X X X X X X1x8 Connector X X X X X X X Flywire X X X X X XLead-freeConstruction X X XAvailable for order X XProgramming Cable Feature SummaryEach Programming Cable ships with two small connectors that help you keep the flywires organized. The following manufacturer and part number is one possible source for equivalent connectors:•1x8 Connector (e.g. Samtec SSQ-108-02-T-S)•2x5 Connector (e.g. Samtec SSQ-105-02-T-D)The Programming Cable flywire or headers are intended to connect to standard 100-mil spacing headers (pins spaced 0.100 inch apart). Lattice recommends a header with length of 0.243 inches or 6.17 mm. Though, headers of other lengths may work equally well.Ordering InformationDescription Ordering PartNumberChina RoHS Environment-Friendly Use Period (EFUP)Programming cable (USB). Contains 6' USB cable, flywire connectors,8-position (1x8) adapter and 10-position (2x5) adapter, lead-free, RoHScompliant construction.HW-USBN-2BProgramming cable (PC only). Contains parallel port adapter, 6' cable,flywire connectors, 8-position (1x8) adapter and 10-position (2x5) adapter,lead-free, RoHS compliant construction.HW-DLN-3CNote: Additional cables are described in this document for legacy purposes only, these cables are no longer produced. The cables currently available for order are fully equivalent replacement items.Technical Support Assistancee-mail:***************************Internet:Revision HistoryDate Version Change SummaryJanuary 201524.7Updated Programming Cable Pin Definitions section.— In Table 1, Programming Cable Pin Definitions, ispEN/Enable/PROGchanged to ispEN/Enable/PROG/SN and its description revised.— Updated Figure 2, Programming Cable In-System ProgrammingInterface for the PC (HW-USBN-2B).Updated Programming Cable ispEN Pin section.In T able 4, Programming Cable Feature Summary, HW-USBN-2Bmarked as available for order.Updated Ordering Information section. HW-USBN-2A changed to HW-USBN-2BJuly 201424.6Changed document title to Programming Cables User’s GuideChanged ispDOWNLOAD Cables to Programming Cables.Updated Target Board Design Considerations section. Updated FAQlink on ispVM tool control of TCK duty cycle and/or frequency.Updated Table 3, Recommended Pin Connections. Added ECP5,iCE40LM, iCE40 Ultra, and MachXO3 device families.Updated Technical Support Assistance information.October 201224.5Added iCE40 configuration port pin names to the Flywire ConversionReference table.Added iCE40 information to Recommended Cable Connections table.February 201224.4Updated document with new corporate logo.November 201124.3Document transferred to user’s guide format.Added Figure USB Cable – HW-USBN-2A.Updated Recommend Cable Connections table for MachXO2 devices.Updated Target Board Design Considerations section.Added Appendix A.October 200924.2Added information related to the physical specifications of the flywireconnectors.July 200924.1Added Target Board Design Considerations text section.Added Programming Flywire and Connection Reference section head-ing.——Previous Lattice releases.Appendix A. Troubleshooting the USB Driver InstallationIt is essential that you install the drivers before connecting your PC to the USB cable. If the cable is connected before installing the drivers, Windows will try to install its own drivers that may not work.If you have attempted to connect the PC to the USB cable without first installing the appropriate drivers, or have trouble communicating with the Lattice USB cable after installing the drivers, following the steps below:1.Plug in the Lattice USB cable. Choose Start > Settings > Control Panel > System. In the System Propertiesdialog box, click the Hardware tab and Device Manager button. Under Universal Serial Bus controllers, you should see Lattice USB ISP Programmer. If you do not see this, look for the Unknown Device with the yellow flag.2.Double click on the Unknown Device icon.3.Click Reinstall Driver.4.Select Browse for driver software on your computer.For Lattice EzUSB DriverFor FTDI FTUSB Driver5.Browse to the isptools\ispvmsystem directory for the Lattice EzUSB driver or the isptools\ispvmsystem\Drivers\FTDIUSBDriver directory for the FTDI FTUSB driver. For Diamond installations, browse tolscc/diamond/data/vmdata/drivers. Click Next.6.Select Install this Driver software anyway. The system will update the driver.7.Click Close and finish installing the USB driver. Under Control Panel >System >Device Manager > Univer-sal Serial Bus Controllers should include the following:For the Lattice EzUSB Driver: Lattice USB ISP Programmer device installed.For the FTDI FTUSB Driver: USB Serial Converter A and Converter B devices installed.If you are experiencing problems or need additional information, contact Lattice Technical Support.。

diamond1.1基础应用及增量编译

定义顶层模块 参数文件路径

如果有参数文件(宏定义或者参数文件)可以设置索引路径,也可以不设置,那么就 需要把参数文件拷贝到工程目录下,与*.ldf同级。

Diamond1.1设计流程介绍

如何在一个工程下设计多个implementation 步骤五,为新的implementation新建一个strategy,默认为Area优先。当然这个也是可以在新 建implementation时在步骤二可以指定的。不指定,就是面积优先。

project

•如果之前没有使用过 ispLEVER请忽略这小节内容

Diamond1.1设计流程介绍

导入一个ispLEVER工程

第二步, 根据提示找到*.syn的文件,选择*.syn后确认(open),弹出如下对话框。

ispLEVER原工程文件

新工程名称 Diamond新工程目录,用户定义

Diamond工程文件

Agenda

Diamond1.1基本使用方法 1. 设计软件图形用户界面(GUI)介绍 2. 设计流程介绍

– 导入ispLEVER工程 – 新建工程 – 设置strategy – 设置修改约束文件 – 运行布局布线 – 分析报告

Diamond1.1设计流程介绍

为新建工程设置适合的策略-strategy

自定义strategy之Translate Design设置

二个经常使用的属性: Macro Search Path:调用IP所用到的ngo以及网表文件所在路径,如果这里不设置,

需要拷贝相关文件到工程目录下(与*.ldf同级目录) Memory Initial Value File Search Path: RAM,ROM等初始化文件所在路径索引,

LatticeDiamond官方培训演示课件

Page: 3

Lattice Semiconductor Confidential

LATTICE DIAMOND FEATURES & BENEFITS

• Design exploration features

– Implementations & Strategies – Run Manager – Integrated HDL checking – Synthesis Options

Lattice Diamond Seminar – February 2011

Page: 2

Lattice Semiconductor Confidential

WHAT IS LATTICE DIAMOND?

• Built on existing foundation for cost sensitive, low power applications

– Modern GUI – Ease of use – Improved design flow – Better scripting support – Reduced memory footprint – Foundation for future feature expansion

Lattice Diamond Seminar – February 2011

– Implementation engines (MAP, PAR, etc.) – I/O placement – IP reuse – Power calculation – SSO analysis – HW/SW system design – LatticeMico System

• Modern replacement for ispLEVER design environment

LATTICE DIAMOND 软件使用说明

Lattice Diamond TutorialJune 2012CopyrightCopyright © 2012 Lattice Semiconductor Corporation.This document may not, in whole or part, be copied, photocopied, reproduced,translated, or reduced to any electronic medium or machine-readable form withoutprior written consent from Lattice Semiconductor Corporation.TrademarksLattice Semiconductor Corporation, L Lattice Semiconductor Corporation (logo), L (stylized), L (design), Lattice (design), LSC, CleanClock, Custom Movile Device, DiePlus, E2CMOS, Extreme Performance, FlashBAK, FlexiClock, flexiFLASH, flexiMAC, flexiPCS, FreedomChip, GAL, GDX, Generic Array Logic, HDL Explorer, iCE Dice, iCE40, iCE65, iCEcable, iCEchip, iCEcube, iCEcube2, iCEman, iCEprog, i CEsab, iCEsocket, IPexpress, ISP, ispATE, ispClock, ispDOWNLOAD, ispGAL,i spGDS, ispGDX, ispGDX2, ispGDXV, ispGENERATOR, ispJTAG, ispLEVER,i spLeverCORE, ispLSI, ispMACH, ispPAC, ispTRACY, ispTURBO, ispVIRTUALM ACHINE, ispVM, ispXP, ispXPGA, ispXPLD, Lattice Diamond, LatticeCORE,L atticeEC, LatticeECP, LatticeECP-DSP, LatticeECP2, LatticeECP2M, LatticeECP3, L atticeECP4, LatticeMico, LatticeMico8, LatticeMico32, LatticeSC, LatticeSCM,L atticeXP, LatticeXP2, MACH, MachXO, MachXO2, MACO, mobileFPGA, ORCA,P AC, PAC-Designer, PAL, Performance Analyst, Platform Manager, ProcessorPM,P URESPEED, Reveal, SiliconBlue, Silicon Forest, Speedlocked, Speed Locking,S uperBIG, SuperCOOL, SuperFAST, SuperWIDE, sysCLOCK, sysCONFIG, sysDSP, s ysHSI, sysI/O, sysMEM, The Simple Machine for Complex Design, TraceID,T ransFR, UltraMOS, and specific product designations are either registeredt rademarks or trademarks of Lattice Semiconductor Corporation or its subsidiaries in t he United States and/or other countries. ISP, Bringing the Best Together, and More of t he Best are service marks of Lattice Semiconductor Corporation.Other product names used in this publication are for identification purposes only andm ay be trademarks of their respective companies.DisclaimersN O WARRANTIES: THE INFORMATION PROVIDED IN THIS DOCUMENT IS “AS IS”W ITHOUT ANY EXPRESS OR IMPLIED WARRANTY OF ANY KIND INCLUDING WARRANTIES OF ACCURACY, COMPLETENESS, MERCHANTABILITY, NONINFRINGEMENT OF INTELLECTUAL PROPERTY, OR FITNESS FOR ANYP ARTICULAR PURPOSE. IN NO EVENT WILL LATTICE SEMICONDUCTORC ORPORATION (LSC) OR ITS SUPPLIERS BE LIABLE FOR ANY DAMAGESW HATSOEVER (WHETHER DIRECT, INDIRECT, SPECIAL, INCIDENTAL, ORC ONSEQUENTIAL, INCLUDING, WITHOUT LIMITATION, DAMAGES FOR LOSS OF P ROFITS, BUSINESS INTERRUPTION, OR LOSS OF INFORMATION) ARISINGO UT OF THE USE OF OR INABILITY TO USE THE INFORMATION PROVIDED IN T HIS DOCUMENT, EVEN IF LSC HAS BEEN ADVISED OF THE POSSIBILITY OF S UCH DAMAGES. BECAUSE SOME JURISDICTIONS PROHIBIT THE EXCLUSION O R LIMITATION OF CERTAIN LIABILITY, SOME OF THE ABOVE LIMITATIONS MAY N OT APPLY TO YOU.L SC may make changes to these materials, specifications, or information, or to theherein or to advise any user of this document of any correction if such be made. LSCrecommends its customers obtain the latest version of the relevant information toestablish, before ordering, that the information being relied upon is current.ii Lattice Diamond TutorialType Conventions Used in This Document Convention Meaning or UseBold Items in the user interface that you select or click. Text that you type into the user interface.<Italic>Variables in commands, code syntax, and path names.Ctrl+L Press the two keys at the same time.Courier Code examples. Messages, reports, and prompts from the software. ... Omitted material in a line of code.Omitted lines in code and report examples....[ ] Optional items in syntax descriptions. In bus specifications, the brackets are required.( ) Grouped items in syntax descriptions.{ } Repeatable items in syntax descriptions.| A choice between items in syntax descriptions.ContentsLattice Diamond Tutorial 1Learning Objectives 1Time to Complete This Tutorial 2System Requirements 2Accessing Online Help 2About the Tutorial Design 2About the Tutorial Data Flow 2Task 1: Create a New Project 4Task 2: Running Analysis Tools 8Task 3: Inspect Strategy Settings 10Task 4: Examine Resources 11Task 5: Set Timing and Location Assignments 13Task 6: Running Place and Route 17Task 7: Examine Post Place and Route Results 18Task 8: Adjust Static Timing Constraints and Review Results 20 Task 9: Comparing Multiple Place and Route Runs 21Task 10: Running Export Utility Programs 23Task 11: Download a Bitstream to an FPGA 24Task 12: Convert a File Using Deployment Tool 26。

Lattice DDR3教程全攻略之仿真篇

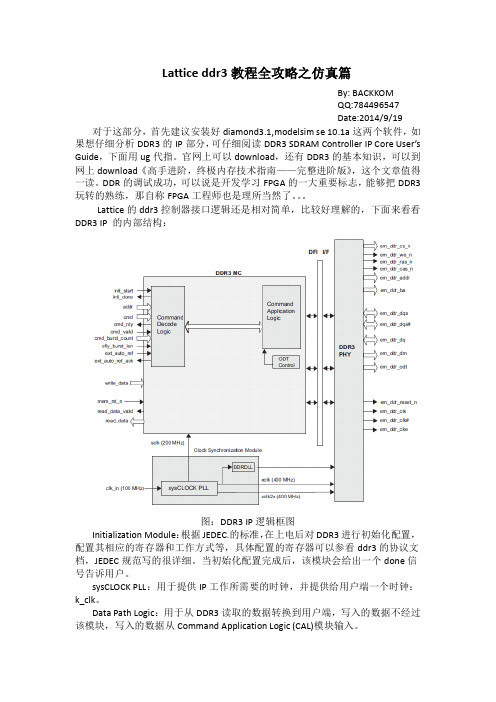

Lattice ddr3教程全攻略之仿真篇By: BACKKOMQQ:784496547Date:2014/9/19 对于这部分,首先建议安装好diamond3.1,modelsim se 10.1a这两个软件,如果想仔细分析DDR3的IP部分,可仔细阅读DDR3 SDRAM Controller IP Core User’s Guide,下面用ug代指。

官网上可以download,还有DDR3的基本知识,可以到网上download《高手进阶,终极内存技术指南——完整进阶版》,这个文章值得一读。

DDR的调试成功,可以说是开发学习FPGA的一大重要标志,能够把DDR3玩转的熟练,那自称FPGA工程师也是理所当然了。

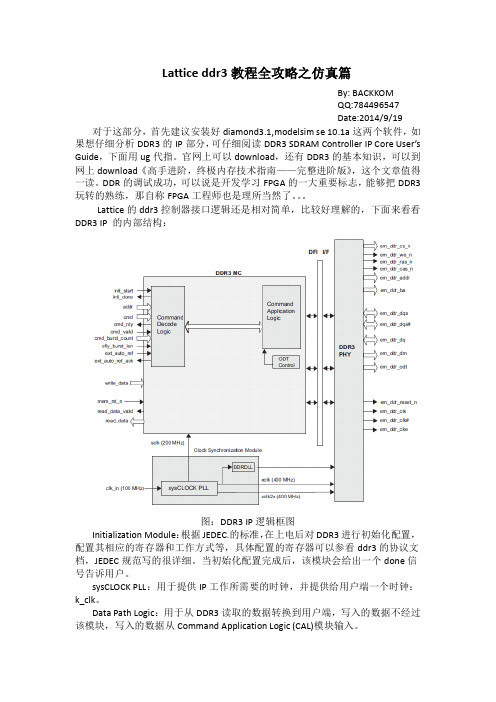

Lattice的ddr3控制器接口逻辑还是相对简单,比较好理解的,下面来看看DDR3 IP 的内部结构:图:DDR3 IP逻辑框图Initialization Module:根据JEDEC.的标准,在上电后对DDR3进行初始化配置,配置其相应的寄存器和工作方式等,具体配置的寄存器可以参看ddr3的协议文档,JEDEC规范写的很详细。

当初始化配置完成后,该模块会给出一个done信号告诉用户。

sysCLOCK PLL:用于提供IP工作所需要的时钟,并提供给用户端一个时钟:k_clk。

Data Path Logic:用于从DDR3读取的数据转换到用户端,写入的数据不经过该模块,写入的数据从Command Application Logic (CAL)模块输入。

Command Decode Logic (CDL) :该模块用于译码命令,控制core按照设定的命令正确的访问ddr3芯片。

DDR3 PHY:用于转换单端的数据转换为差分给到ddr芯片端,和差分转单端输入。

以上部分有基础了解就行,不需要深究。

图:DDR初始化时序当上电后,用户应该将init_start拉高至少200us,直到init_done被拉高一个周期,则将init_start拉低。

晶体结构立体模型建构软件-Diamond的使用指南

晶体结构立体模型建构软件-Diamond的使用吴平伟中国海洋大学材料科学与工程研究院E-mail: wupingwei@晶体结构立体模型建构软件-Diamond的使用在使用Diamond软件构造晶体模型时,需要知道晶体的结构数据,即晶体的空间群、晶胞参数和原子坐标。

晶体结构数据可以手动输入,也可以直接从晶体信息文件中获得。

我们将通过几个例子来说明软件的使用方法。

一、NaCl晶体结构模型的构造下面我们以NaCl为例手动输入晶体结构数据。

NaCl晶体的结构数据为:空间群Fm-3m(225);晶胞参数a=5.64Å;原子坐标Na:4a, Cl:4b。

我们将通过这个例子学会如下操作:1、学会手动输入晶体结构数据;2、学会晶体模型的构造;3、学会旋转晶体模型,从不同的角度观察;4、学会改变背景和原子及晶胞的颜色等参数;5、学会以一种原子为中心,另一种原子为配位原子构造配位多面体;6、学会多面体外观的设计。

打开软件,界面如下图所示:点击“File| New”,出现一对话窗口,如下图,选择第二个选项,按“OK”。

结果生成一个名字为Diamond1的空白的页面,同时弹出一个名字为New Structure的对话窗口,点“下一步”,在新弹出的窗口中确认Crystal Structure with cell and Spacegroup被选中,在Cell length中输入5.64,如下图:注意Space group(空间群)后是否我们需要的NaCl晶体的空间群Fm-3m(225),如果不是,点击Browse钮,在弹出的对话窗口中选中Fm-3m(225),即在Fm-3m(225)上点击使其变蓝色,如下图。

点“OK”回到前面的对话窗口。

点“下一步”(在出现的如下图的对话框中可以输入原子坐标,即在“Atomic parameters“中输入相应的元素符号和原子坐标值,但我们将在其他的地方做这个工作)点“下一步”,在出现的Completing the new structure Assistant窗口中有三个选项:Start structure picture; Launch the structure picture creation assistant;Create structure picture automaticly。

LATTICE DIAMOND 软件使用说明

Lattice Diamond TutorialJune 2012CopyrightCopyright © 2012 Lattice Semiconductor Corporation.This document may not, in whole or part, be copied, photocopied, reproduced,translated, or reduced to any electronic medium or machine-readable form withoutprior written consent from Lattice Semiconductor Corporation.TrademarksLattice Semiconductor Corporation, L Lattice Semiconductor Corporation (logo), L (stylized), L (design), Lattice (design), LSC, CleanClock, Custom Movile Device, DiePlus, E2CMOS, Extreme Performance, FlashBAK, FlexiClock, flexiFLASH, flexiMAC, flexiPCS, FreedomChip, GAL, GDX, Generic Array Logic, HDL Explorer, iCE Dice, iCE40, iCE65, iCEcable, iCEchip, iCEcube, iCEcube2, iCEman, iCEprog, i CEsab, iCEsocket, IPexpress, ISP, ispATE, ispClock, ispDOWNLOAD, ispGAL,i spGDS, ispGDX, ispGDX2, ispGDXV, ispGENERATOR, ispJTAG, ispLEVER,i spLeverCORE, ispLSI, ispMACH, ispPAC, ispTRACY, ispTURBO, ispVIRTUALM ACHINE, ispVM, ispXP, ispXPGA, ispXPLD, Lattice Diamond, LatticeCORE,L atticeEC, LatticeECP, LatticeECP-DSP, LatticeECP2, LatticeECP2M, LatticeECP3, L atticeECP4, LatticeMico, LatticeMico8, LatticeMico32, LatticeSC, LatticeSCM,L atticeXP, LatticeXP2, MACH, MachXO, MachXO2, MACO, mobileFPGA, ORCA,P AC, PAC-Designer, PAL, Performance Analyst, Platform Manager, ProcessorPM,P URESPEED, Reveal, SiliconBlue, Silicon Forest, Speedlocked, Speed Locking,S uperBIG, SuperCOOL, SuperFAST, SuperWIDE, sysCLOCK, sysCONFIG, sysDSP, s ysHSI, sysI/O, sysMEM, The Simple Machine for Complex Design, TraceID,T ransFR, UltraMOS, and specific product designations are either registeredt rademarks or trademarks of Lattice Semiconductor Corporation or its subsidiaries in t he United States and/or other countries. ISP, Bringing the Best Together, and More of t he Best are service marks of Lattice Semiconductor Corporation.Other product names used in this publication are for identification purposes only andm ay be trademarks of their respective companies.DisclaimersN O WARRANTIES: THE INFORMATION PROVIDED IN THIS DOCUMENT IS “AS IS”W ITHOUT ANY EXPRESS OR IMPLIED WARRANTY OF ANY KIND INCLUDING WARRANTIES OF ACCURACY, COMPLETENESS, MERCHANTABILITY, NONINFRINGEMENT OF INTELLECTUAL PROPERTY, OR FITNESS FOR ANYP ARTICULAR PURPOSE. IN NO EVENT WILL LATTICE SEMICONDUCTORC ORPORATION (LSC) OR ITS SUPPLIERS BE LIABLE FOR ANY DAMAGESW HATSOEVER (WHETHER DIRECT, INDIRECT, SPECIAL, INCIDENTAL, ORC ONSEQUENTIAL, INCLUDING, WITHOUT LIMITATION, DAMAGES FOR LOSS OF P ROFITS, BUSINESS INTERRUPTION, OR LOSS OF INFORMATION) ARISINGO UT OF THE USE OF OR INABILITY TO USE THE INFORMATION PROVIDED IN T HIS DOCUMENT, EVEN IF LSC HAS BEEN ADVISED OF THE POSSIBILITY OF S UCH DAMAGES. BECAUSE SOME JURISDICTIONS PROHIBIT THE EXCLUSION O R LIMITATION OF CERTAIN LIABILITY, SOME OF THE ABOVE LIMITATIONS MAY N OT APPLY TO YOU.L SC may make changes to these materials, specifications, or information, or to theherein or to advise any user of this document of any correction if such be made. LSCrecommends its customers obtain the latest version of the relevant information toestablish, before ordering, that the information being relied upon is current.ii Lattice Diamond TutorialType Conventions Used in This Document Convention Meaning or UseBold Items in the user interface that you select or click. Text that you type into the user interface.<Italic>Variables in commands, code syntax, and path names.Ctrl+L Press the two keys at the same time.Courier Code examples. Messages, reports, and prompts from the software. ... Omitted material in a line of code.Omitted lines in code and report examples....[ ] Optional items in syntax descriptions. In bus specifications, the brackets are required.( ) Grouped items in syntax descriptions.{ } Repeatable items in syntax descriptions.| A choice between items in syntax descriptions.ContentsLattice Diamond Tutorial 1Learning Objectives 1Time to Complete This Tutorial 2System Requirements 2Accessing Online Help 2About the Tutorial Design 2About the Tutorial Data Flow 2Task 1: Create a New Project 4Task 2: Running Analysis Tools 8Task 3: Inspect Strategy Settings 10Task 4: Examine Resources 11Task 5: Set Timing and Location Assignments 13Task 6: Running Place and Route 17Task 7: Examine Post Place and Route Results 18Task 8: Adjust Static Timing Constraints and Review Results 20 Task 9: Comparing Multiple Place and Route Runs 21Task 10: Running Export Utility Programs 23Task 11: Download a Bitstream to an FPGA 24Task 12: Convert a File Using Deployment Tool 26。

latticediamond3.7安装破解

latticediamond3.7安装破解lattice diamond 3.7安装破解第⼀步安装:执⾏.EXE⽂件,⼀直下⼀步,最后license 选择没有USB什么的那个(具体记不清了)。

第⼆步破解:安装完成后在环境变量中将license路径指定到license⽂件即可,不⽤改什么虚拟⽹卡啊什么的。

⽤如下内容的license:FEATURE BASIC_ALL lattice 7.0 01-jan-9999 uncounted 0EC5CE7AE0DE \ HOSTID=ANYFEATURELSC_STARTER lattice 7.0 01-jan-9999 uncounted73224EA033EB \ HOSTID=ANYFEATURE LSC_BASE lattice 7.0 01-jan-9999 uncounted 9CE97753891C \HOSTID=ANYFEATURE LSC_ANY_PAC lattice 7.001-jan-9999 uncounted DCF4E89B41D1 \HOSTID=ANYFEATURE LSC_PAC_STARTER lattice 7.0 01-jan-9999 uncounted \ 93096E4F2DD0HOSTID=ANYFEATURE LSC_PAC_SYSTEM lattice 7.0 01-jan-9999 uncounted BF10B454B18D \HOSTID=ANYFEATURE LSC_DUMMY_FEATURE lattice 7.0 01-jan-9999 uncounted \ A0265D023D6FHOSTID=ANYFEATURE 0100 lattice 7.0 01-jan-9999uncounted 841224FE9639 \ HOSTID=ANYFEATURE 0200 lattice 7.0 01-jan-9999 uncounted C47123FB9538 \ HOSTID=ANYFEATURE 0300 lattice 7.0 01-jan-9999 uncounted 9EF02EFCB437 \ HOSTID=ANYFEATURE 0400 lattice 7.0 01-jan-9999 uncounted C4372DF99B2E \ HOSTID=ANYFEATURE LSC_ADVANCED lattice 8.001-jan-9999 uncounted 1C47C70A6ACA \HOSTID=ANYFEATURE LSC_ADVANCED_DSP lattice 10.0 01-jan-9999 uncounted \ CAA8BAA7C278HOSTID=ANYFEATURE LSC_ADVANCED_FLXMC lattice 10.0 01-jan-9999 uncounted \ 6B082DACDAA5HOSTID=ANYFEATURE LSC_ADVANCED_LSCDR lattice 10.0 01-jan-9999 uncounted \ 17865366C30EHOSTID=ANYFEATURE LSC_ADVANCED_LTSSM lattice 10.0 01-jan-9999 uncounted \ 8B6A3666E0EAHOSTID=ANYFEATURE LSC_ADVANCED_MCTL lattice 10.0 01-jan-9999 uncounted \ 7AF5C1DCD5B6HOSTID=ANYFEATURE LSC_ADVANCED_ORCA lattice 9.0 01-jan-9999 uncounted \ 9EA3C938B4C7HOSTID=ANYFEATURE LSC_ADVANCED_ORLI10G lattice 9.0 01-jan-9999 uncounted \ 0BB1D333EF42HOSTID=ANYFEATURE LSC_ADVANCED_ORSO42G5lattice 9.0 01-jan-9999 uncounted \ AB9147E09AC1 HOSTID=ANYFEATURE LSC_ADVANCED_ORSO82G5 lattice 9.0 01-jan-9999 uncounted \ B37D4BDCA6C5 HOSTID=ANYFEATURE LSC_ADVANCED_ORSPI4 lattice 10.0 01-jan-9999 uncounted \ BC81D9589AFD HOSTID=ANYFEATURE LSC_ADVANCED_ORT42G5 lattice 9.0 01-jan-9999 uncounted \ A8267218E893 HOSTID=ANYFEATURE LSC_ADVANCED_ORT82G5 lattice 9.0 01-jan-9999 uncounted \901A5E24E897 HOSTID=ANYFEATURE LSC_ADVANCED_ORT8850 lattice 9.0 01-jan-9999 uncounted \2645BEDC38F6 HOSTID=ANYFEATURE LSC_ADVANCED_PCI lattice 10.0 01-jan-9999 uncounted \ 28737B9BA88B HOSTID=ANYFEATURE LSC_ADVANCED_PCI_MACO lattice 10.0 01-jan-9999 uncounted \ 2C481E792E16 HOSTID=ANYFEATURE LSC_ADVANCED_PLUS lattice 8.0 01-jan-9999 uncounted \ 5D3951FEC095HOSTID=ANYFEATURE LSC_ADVANCED_SPI4 lattice 10.0 01-jan-9999 uncounted \ A3823192B587HOSTID=ANYFEATURELSC_ADVANCED_SPI4_25LLM0 lattice 10.0 01-jan-9999 uncounted \ 738E4582A946 HOSTID=ANYFEATURELSC_CLASSIC lattice 10.0 01-jan-9999 uncounted 275097B247D1 \ HOSTID=ANYFEATURELSC_DIAMOND_A lattice 10.0 01-jan-9999 uncounted 4AAED9D8068E \ HOSTID=ANYFEATURELSC_SYNPLIFY lattice 10.000 1-jan-9999 uncounted8E52C4F86F30 \ HOSTID=ANYFEATURELSC_SYNPLIFYPRO1 lattice 10.000 1-jan-9999 uncounted \ 411DD7556BA8 HOSTID=ANYFEATURE LSC_WARRANTY lattice 10.000 1-dec-9999 uncounted F4620A8B6EA0 \ HOSTID=ANYFEATURELSC_CONTROL_INCFLOW lattice 10.000 1-dec-9999 uncounted \ 31EC2B26739A HOSTID=ANYFEATURELSC_IP_fir_comp_e3_ipe lattice 10.000 31-dec-2025 uncounted \ 3152599ADCC0 HOSTID=ANYFEATURELSC_IP_fir_comp_pm_ipe lattice 10.000 31-dec-2025 uncounted \ B7EFE0974E39 HOSTID=ANYFEATURELSC_IP_fir_comp_x2_ipe lattice 10.000 31-dec-2025 uncounted \ 67F56168DBE8 HOSTID=ANYFEATURELSC_IP_tri_sdi_e3_ipe lattice 10.000 31-dec-2025 uncounted \ F8A64B04F058 HOSTID=ANYFEATURELSC_IP_nco_dds_x2_ipe lattice 10.000 31-dec-2025 uncounted \ C1AA8E1D7667 HOSTID=ANYFEATURELSC_IP_nco_dds_e3_ipe lattice 10.000 31-dec-2025 uncounted \ 9B026E1CD069 HOSTID=ANYFEATURELSC_IP_nco_dds_pm_ipe lattice 10.000 31-dec-2025 uncounted \ A634E3068684 HOSTID=ANYFEATURELSC_IP_cic_filtr_x2_ipe lattice 10.000 31-dec-2025 uncounted \ 5B57318F70B9 HOSTID=ANYFEATURELSC_IP_ts_mac_e3_ipe lattice 10.0 31-dec-2025 uncounted \ 61EB65B1A0D2 HOSTID=ANYFEATURELSC_IP_ts_mac_pm_ipe lattice 10.0 31-dec-2025 uncounted \ D20AAE91B0E8 HOSTID=ANYFEATURELSC_IP_ts_mac_x2_ipe lattice 10.0 31-dec-2025 uncounted \ 5B995171A8CD HOSTID=ANYFEATURELSC_IP_ddr2_p_pm_ipe lattice 10.0 31-dec-2025 uncounted \ B40D56D40196 HOSTID=ANYFEATURELSC_IP_ddr2_p_x2_ipe lattice 10.0 31-dec-2025 uncounted \ 40B2EFD40975 HOSTID=ANYFEATURELSC_IP_ddr2_p_e3_ipe lattice 10.0 31-dec-2025 uncounted \ 593E07CC1180 HOSTID=ANYFEATURELSC_IP_ddr_p_pm_ipe lattice 10.0 31-dec-2025 uncounted \ 79B8888680FF HOSTID=ANYFEATURELSC_IP_ddr_p_x2_ipe lattice 10.0 31-dec-2025 uncounted \ 891CE3B07807 HOSTID=ANYFEATURELSC_IP_ddr_p_e3_ipe lattice 10.0 31-dec-2025 uncounted \ D659459B93EC HOSTID=ANYFEATURELSC_IP_pci_t32_e3_ipe lattice 10.0 31-dec-2025 uncounted \ AB5CF3E89F26 HOSTID=ANYFEATURELSC_IP_pci_mt32_e3_ipe lattice 10.0 31-dec-2025 uncounted \ 9C75314C842C HOSTID=ANYFEATURELSC_IP_pci_t64_e3_ipe lattice 10.0 31-dec-2025 uncounted \ 21E7F1ED7D2E HOSTID=ANYFEATURELSC_IP_pci_mt64_e3_ipe lattice 10.0 31-dec-2025 uncounted \ F98938497F31 HOSTID=ANYFEATURELSC_IP_edge_det_x2_ipe lattice 10.0 31-dec-2025 uncounted \ 2E22250B008C HOSTID=ANYFEATURELSC_IP_edge_det_e3_ipe lattice 10.0 31-dec-2025 uncounted \ C623531BFD9E HOSTID=ANYFEATURELSC_IP_csc_x2_ipe lattice 10.0 31-dec-2025 uncounted \ 666536384764 HOSTID=ANYFEATURELSC_IP_sgmii_e3_ipe lattice 10.0 31-dec-2025 uncounted \ DCD0672C4833 HOSTID=ANYFEATURELSC_IP_pcie_x1_e3_ipe lattice 10.0 31-dec-2025 uncounted \ 307A9A056686 HOSTID=ANYFEATURELSC_IP_pcie_x4_e3_ipe lattice 10.0 31-dec-2025 uncounted \ A940A1006389 HOSTID=ANYFEATURELSC_IP_ddr3_p_e3_ipe lattice 10.0 31-dec-2025 uncounted \ 80BEE8D6FE76 HOSTID=ANYFEATURELSC_IP_scaler_e3_ipe lattice 10.0 31-dec-2025 uncounted \ 44335B509C22 HOSTID=ANYFEATURELSC_IP_scaler_x2_ipe lattice 10.0 31-dec-2025 uncounted \ 34658B6C9425 HOSTID=ANYFEATURELSC_IP_divide_e3_ipe lattice 10.0 31-dec-2025 uncounted \ 003943ABF469 HOSTID=ANYFEATURELSC_IP_divide_x2_ipe lattice 10.0 31-dec-2025 uncounted \ 8BC9A567EC6E HOSTID=ANYFEATURE ACTIVEHDL_LIC_NUMBER ALDEC2014.0500 6-may-2014 uncounted \ 846C8F32A823 VENDOR_STRING=25412 HOSTID=f0def10a5abe \ SIGN2="005E9EDC 0379 C3BA E9F1 2FBB BC19 2800 837C 2F73 CBBD \ A020 B6C8 61DA 1518"FEATUREACTIVEHDL_LATTICE_MIX_LT ALDEC 2014.05006-may-2014 uncounted \ 6188D2E8F535VENDOR_STRING=25412 HOSTID=f0def10a5abe \ SIGN2="0038 73F2 1444 8C29 1329 667A 40F4 1A0087C5 5ED3 8BA0 \ 607D 6BA7 FF66 8324" INCREMENT SSST snpslmd 1.0 06-Aug-2013 uncounted5E40AE66DE224B155B93 \ VENDOR_STRING="22fdb ded7f 205fb fc191 ede96 b96f7 40c19 1ede9 6b96f 74011 \ 01020 0963b eae9b 3db77 9fea2 342f8 9e29f 30fd4d4a12 f199c \ 3520c 72e28 6534c a243a dfd33 b95f7ac1b9 149d0 35264 27b7a \ db0d3 2bd50 85b88 0228a 835e0 2659a 8ae71 6e4c4 415a0 0c5c5 \ 38034 1f532 8750e95a1d ae4eb 8338f 3f03d 43913 8fb1b 5977f \ 42283 c6f6c be3f7 caded 9249a 7b66d fafe1 e3431 5d0ca e7129 \ 1c6df 12108 17608 cf969 c9c63 9f4be 9305fe2dc9 4b5c8 b448d \ a0041 46bf1 a3660 0b61a a0a41f3dd8 a7126 0698c 9dd35 5a22c \ 40ab0 cdf49 7c042d4257 6d65f 84ab1 30aef 61f3e a1863 d277b \ 0065d8ed33 d8744 53ae8 d3376 326fa 1000b 70682 c8b0a33b5c \ 65e9e 59abd ccdcb 307ad fb505 09d59 2b28d 3858c 077d5 1f25a \ 96102 ce4a5 daceb c29" \NOTICE="Licensed to Lattice Semiconductor Corp - OEM [DO NOT DELETE/MODIFY \ SSST OR ANY OTHER KEYS IN THIS FILE]" \ SN=TK:0:0:0 ISSUER="Synopsys, Inc. [8/6/2012 23:40:17 26232]" \ START=06-Aug-2012HOSTID=f0def10a5abeINCREMENT synplifypro_sbt snpslmd 2012.03 06-aug-2013 uncounted \5E406E76E033314007B5 HOSTID=f0def10a5abeISSUED=06-aug-2012 \ ck=9SN=TK:7978-0:477717:971792START=06-aug-2012INCREMENT synplifypro_sbt synplctyd 2012.03 06-aug-2013 uncounted \CE504E066725FBE63F4B VENDOR_STRING=sbt,nl HOSTID=f0def10a5abe \ ISSUED=06-aug-2012 ck=73 SN=TK:7978-0:477718:785300 SIGN="00C2 \ 313A F357 C569 2964 6202 9496 7BE9 A57B CB31 8202 EB25 89BB \ D84C 6714 6456 C54E B9DB 9D62 3B2F 5B18"。

LATTICE的I2C模式下载使用教程说明

LATTICE下载器HW-USBN-2B I2C下载使用说明教程By:翊全EN-WXLATTICE的I 2 C配置模式:要进行对I 2 C Port Devices的操作,首先得是支持I2C的器件。

目前可以支持的器件有:MachXO2/MachXO3/MachXO3D ;Platform Manager II ;L-ASC10 ;CrossLink LIF-MD6000;需要使用lattice的HW-USBN-2B和MTC2 plus才支持I2C配置器件。

I2C (Inter-IC)总线是一种简单的低带宽,短距离协议。

人们常常看到对系统外围设备的访问是间歇的。

在闭环系统中,这也是一个常用的通信解决方案,可实现电路板上最少的走线。

I2C(内部集成的电路)接口也称为两线接口,是最初由Philips开发的一种多主器件串行单端总线。

I2C广泛用于同一块电路板上器件之间的通信。

一.硬件连线LATTICE的I 2 C配置模式用到的信号如下:1.SDA:I 2 C总线数据线2.SCL:I 2 C总线时钟3.GND:连接到目标芯片的接地信号4.VCC(VREF):连接到目标芯片的VCC,提供芯片配置IO的电平参考电压。

注意:I2C总线的信号是漏极开路的,所以默认情况下是,信号线是低电平,需要加上拉电阻,使其默认是高电平。

I2C总线上建议不要挂太多的器件,建议只挂一个芯片,因为需要保证信号质量。

为了能够使用I2C总线进行在线下载(program),I2C_PORT必须要设置为ENABLE。

默认状态在Diamond设计软件中为I2C_PORT设置的设置是将I2C_PORT置于DISABLE状态。

你必须确保将I2C_PORT设置为ENABLE状态,以使I 2 C接口在用户模式下保持使能状态。

支持I2C编程的芯片,如果flash编程过一次,必须擦除程序才能用I2C编程。

且须flash编程以后再擦出,如果擦除次数多了,I2C也将不容易识别。

【精品博文】Diamond的安装与激活教程

【精品博文】Diamond的安装与激活教程软件下载地址:(下载前需要提前注册为latticesemi会员)/en/Products/DesignSoftwareAndIP/FPGAandLDS/LatticeDiamo nd.aspx1、系统配置要求1.1、Windows 7 (32-bit or 64-bit), Windows 8/8.1 (32-bit or 64-bit), or Windows10 (32-bit or 64-bit)1.2、大约5.75GB的硬盘空间1.3、网卡(Network adapter)1.4、1024 X 768 graphics display1.5、推荐有4G以及上的内存(RAM)2、注意2.1、安装前关闭其他的软件,尤其是360等杀毒软件!2.2、注意自己的操作系统与下载的Diamond软件版本是否一致!3、安装过程:3.1、先将下载的zip文件解压:3.2、右键图中exe文件,以管理员权限运行;3.3、点击next;3.4、点击yes3.5选择安装目录(注意不要有中文字符),然后点击next;3.6、默认即可,点击next;3.7、依旧默认,继续next;3.8、选择代码限定版License,然后继续;3.9、点击yes,在桌面创建快捷方式,然后next;3.10、点击yes,安装并口/USB端口驱动,然后next;3.11、默认即可,直接next;3.12、然后出现这个界面,稍微等待一下:3.13、等待大概3-5分钟后,出现安装完成界面,点击finish退出;1、 License说明:可以去Latticesemi的官网免费申请限定代码版本的License:具体的网址为:查询自己电脑的网卡号(物理地址)的方式为:4.1、运行cmd;4.2、输入ipconfig –all4.3、补充说明1:有的朋友的电脑可能有多块网卡(大部分笔记本一般又有两块,一个有线的,一个无线的,建议根据自己的上网习惯选择网卡号,常用有线上网的就选用有线的网卡号申请License)4.4、补充说明2:还有的朋友可能还会出现3个甚至3个以上的网卡号,一般都是由于安装了VMWare之类的虚拟机或者某些WiFi 共享软件之类的,注意区分自己真实的网卡号!4.5、获得License之后,将license.dat文件放到Diamond软件的安装目录下的<path>\license文件夹下面即可。

avhd9.1后仿真Latttice vo文件图文教程(原创)

avhd9.1后仿真Latttice vo文件图文教程原创))(原创文件图文教程(Lattice Diamond软件版本:1.4 Active-HDL版本:9.1操作系统:WIN7_X64 旗舰版作者:abadboy(相对于仿真软件modelsim而言,avhd运行速度要快,工程输出的文件体积也比较小,所以我个人也比较青睐于Active-HDL软件)16.双击Aldec Active-HDL 9.1,运行17.点next18.进行界面如下:19.点never不需要更新,再点OK20.弹出创建工程界面,先点cancel取消21.至此软件打开一切正常,界面如下22.打开Lattice Diamond软件,打开一个设计工程文件fuda_ddr2_eval.ldf23.打开工程后的界面显示如下所示:24.点“process”,勾选”Verilog simulation file”,25.选“Run”26.等待运行,如下所示27.运行完成后,会生成后仿真所需要的.vo和.sdf后缀文件28. Aldec新建一个工程,我们取名为BenthA_vo_FudaLiu29.选”Add existing……”添加我们要仿真的VO文件和测试激励文件(把VO文件和测试激励文件先COPY到工程下面)30.选中后点“打开”,选“下一步“31,Default..选项选择Verilog,点“下一步”(我们的代码是用verilog编写的)32.输入设计名,我们写BenthA_vo_FudaLiu,点下一步33.因为我们要仿真的工程需要添加Lattice XP2的库,所有“compile..”选不要选中编译34.加入了工程文件显示界面如下:35.接下来我们需要建仿真元件库,点“Design”下的“Creat Library”36.我们给库取名为xp2_ao_FudaLiu,路径选Aldec安装目录库文件Vlib下,”CreateEmpty….”不要勾选,因为我们需要添加XP2库文件进去,点下一步37.点Add Files38.全选LATTICE安装XP2库路径..\lscc\diamond\1.4\cae_library\simulation\verilog\xp2下的所有.v文件,点打开39.点下一步,完成40.此时,我们看下方的工作进度条,正在编译XP2库文件到我们刚建好的库里面去,等待库编译完成41.点VIEW里的Library Manadge,点xp2_ao_FudaLiu库,会发现右边窗口已经添加进来很多刚编译进来的LATTICE XP2库文件42.在左侧的FILE工程栏,我们将xp2_ao_FudaLiu库设置为有效状态将默认仿真库删除Benth_vo_Fuda库删除43.选中要仿真的文件,点compile all (全部编译)44.编译成功提示如下:45.接下来我们设置要仿真的顶层文件和verilog simulation仿真库,点Design,Settings,在“top-level”里的”xp2_ao_fudaliu“里面选择benthTp_fudaliu激励文件作为顶层元件,点apply.46.在simulation 里verilog选项下,verilog libraries里添加编译好lattice库xp2_ao_fudaliu库,点OK选中47.点simulation,选择initialize simulation,开始进入仿真48.运行没有问题,进入以下界面(如果出错,根据提示请检查库文件和测试激励文件是否正常)49.选中测试的信号,点add to Wareform,添加到波形查看50.点simulation里的run运行,51运行时间在以下位置查看(与modelsim不同,avhd不能边仿真边查看波形)52测试激励文件仿真时间约10几个ms,等待运行完成53.运行完成,波形如下显示54.可以点缩放按钮查看波形55.点信号右键“属性“可改变输出格式“二进制十进制十六进制”等,也可以改变显示的颜色56.这里我们选十进制,颜色选粉红色,效果如下所示57.保存当前仿真的波形文件,我们取名BenthA_vo_FudaLiu,OK这里主要介绍后仿真vo文件操作步骤,其它简单提起,不作详细说明20131109THE END。

lattice diamond 3.7安装破解

lattice diamond 3.7安装破解第一步安装:执行.EXE文件,一直下一步,最后license选择没有USB什么的那个(具体记不清了)。

第二步破解:安装完成后在环境变量中将license路径指定到license文件即可,不用改什么虚拟网卡啊什么的。

用如下内容的license:FEATURE BASIC_ALL lattice 7.0 01-jan-9999 uncounted0EC5CE7AE0DE \ HOSTID=ANYFEATURE LSC_STARTER lattice 7.0 01-jan-9999 uncounted 73224EA033EB \ HOSTID=ANYFEATURE LSC_BASE lattice 7.0 01-jan-9999 uncounted 9CE97753891C \ HOSTID=ANYFEATURELSC_ANY_PAC lattice 7.0 01-jan-9999 uncountedDCF4E89B41D1 \ HOSTID=ANYFEATURE LSC_PAC_STARTER lattice 7.0 01-jan-9999 uncounted \ 93096E4F2DD0 HOSTID=ANYFEATURE LSC_PAC_SYSTEM lattice 7.0 01-jan-9999 uncounted BF10B454B18D \ HOSTID=ANYFEATURE LSC_DUMMY_FEATURE lattice 7.0 01-jan-9999 uncounted \ A0265D023D6F HOSTID=ANYFEATURE 0100 lattice 7.0 01-jan-9999 uncounted 841224FE9639 \HOSTID=ANYFEATURE 0200 lattice 7.0 01-jan-9999uncounted C47123FB9538 \ HOSTID=ANYFEATURE 0300 lattice 7.0 01-jan-9999 uncounted 9EF02EFCB437 \ HOSTID=ANYFEATURE 0400 lattice 7.0 01-jan-9999 uncounted C4372DF99B2E \ HOSTID=ANYFEATURELSC_ADVANCED lattice 8.0 01-jan-9999 uncounted1C47C70A6ACA \ HOSTID=ANYFEATURELSC_ADVANCED_DSP lattice 10.0 01-jan-9999 uncounted \ CAA8BAA7C278 HOSTID=ANYFEATURELSC_ADVANCED_FLXMC lattice 10.0 01-jan-9999 uncounted \ 6B082DACDAA5 HOSTID=ANYFEATURELSC_ADVANCED_LSCDR lattice 10.0 01-jan-9999 uncounted \ 17865366C30E HOSTID=ANYFEATURELSC_ADVANCED_LTSSM lattice 10.0 01-jan-9999 uncounted \ 8B6A3666E0EA HOSTID=ANYFEATURELSC_ADVANCED_MCTL lattice 10.0 01-jan-9999 uncounted \ 7AF5C1DCD5B6 HOSTID=ANYFEATURELSC_ADVANCED_ORCA lattice 9.0 01-jan-9999 uncounted \ 9EA3C938B4C7 HOSTID=ANYFEATURELSC_ADVANCED_ORLI10G lattice 9.0 01-jan-9999 uncounted \ 0BB1D333EF42 HOSTID=ANYFEATURELSC_ADVANCED_ORSO42G5 lattice 9.0 01-jan-9999 uncounted \ AB9147E09AC1 HOSTID=ANYFEATURELSC_ADVANCED_ORSO82G5 lattice 9.0 01-jan-9999 uncounted \ B37D4BDCA6C5 HOSTID=ANYFEATURELSC_ADVANCED_ORSPI4 lattice 10.0 01-jan-9999 uncounted \ BC81D9589AFD HOSTID=ANYFEATURELSC_ADVANCED_ORT42G5 lattice 9.0 01-jan-9999 uncounted \ A8267218E893 HOSTID=ANYFEATURELSC_ADVANCED_ORT82G5 lattice 9.0 01-jan-9999 uncounted \ 901A5E24E897 HOSTID=ANYFEATURELSC_ADVANCED_ORT8850 lattice 9.0 01-jan-9999 uncounted \ 2645BEDC38F6 HOSTID=ANYFEATURELSC_ADVANCED_PCI lattice 10.0 01-jan-9999 uncounted \ 28737B9BA88B HOSTID=ANYFEATURELSC_ADVANCED_PCI_MACO lattice 10.0 01-jan-9999 uncounted \ 2C481E792E16 HOSTID=ANYFEATURELSC_ADVANCED_PLUS lattice 8.0 01-jan-9999 uncounted \ 5D3951FEC095 HOSTID=ANYFEATURELSC_ADVANCED_SPI4 lattice 10.0 01-jan-9999 uncounted \ A3823192B587 HOSTID=ANYFEATURELSC_ADVANCED_SPI4_25LLM0 lattice 10.0 01-jan-9999 uncounted \ 738E4582A946 HOSTID=ANYFEATURELSC_CLASSIC lattice 10.0 01-jan-9999 uncounted275097B247D1 \ HOSTID=ANYFEATURE LSC_DIAMOND_Alattice 10.0 01-jan-9999 uncounted 4AAED9D8068E \ HOSTID=ANYFEATURE LSC_SYNPLIFY lattice 10.000 1-jan-9999 uncounted 8E52C4F86F30 \ HOSTID=ANYFEATURE LSC_SYNPLIFYPRO1 lattice 10.000 1-jan-9999 uncounted \ 411DD7556BA8 HOSTID=ANYFEATURE LSC_WARRANTY lattice 10.000 1-dec-9999 uncounted F4620A8B6EA0 \ HOSTID=ANYFEATURE LSC_CONTROL_INCFLOW lattice 10.000 1-dec-9999 uncounted \ 31EC2B26739AHOSTID=ANYFEATURE LSC_IP_fir_comp_e3_ipe lattice 10.000 31-dec-2025 uncounted \ 3152599ADCC0 HOSTID=ANYFEATURE LSC_IP_fir_comp_pm_ipe lattice 10.000 31-dec-2025 uncounted \ B7EFE0974E39 HOSTID=ANYFEATURE LSC_IP_fir_comp_x2_ipe lattice 10.000 31-dec-2025 uncounted \ 67F56168DBE8 HOSTID=ANYFEATURE LSC_IP_tri_sdi_e3_ipe lattice 10.000 31-dec-2025 uncounted \ F8A64B04F058HOSTID=ANYFEATURE LSC_IP_nco_dds_x2_ipe lattice 10.000 31-dec-2025 uncounted \ C1AA8E1D7667 HOSTID=ANYFEATURE LSC_IP_nco_dds_e3_ipe lattice 10.000 31-dec-2025 uncounted \ 9B026E1CD069 HOSTID=ANYFEATURE LSC_IP_nco_dds_pm_ipe lattice 10.000 31-dec-2025 uncounted \ A634E306868431-dec-2025 uncounted \ 5B57318F70B9HOSTID=ANYFEATURE LSC_IP_ts_mac_e3_ipe lattice 10.0 31-dec-2025 uncounted \ 61EB65B1A0D2HOSTID=ANYFEATURE LSC_IP_ts_mac_pm_ipe lattice 10.0 31-dec-2025 uncounted \ D20AAE91B0E8HOSTID=ANYFEATURE LSC_IP_ts_mac_x2_ipe lattice 10.0 31-dec-2025 uncounted \ 5B995171A8CDHOSTID=ANYFEATURE LSC_IP_ddr2_p_pm_ipe lattice 10.0 31-dec-2025 uncounted \ B40D56D40196HOSTID=ANYFEATURE LSC_IP_ddr2_p_x2_ipe lattice 10.0 31-dec-2025 uncounted \ 40B2EFD40975HOSTID=ANYFEATURE LSC_IP_ddr2_p_e3_ipe lattice 10.0 31-dec-2025 uncounted \ 593E07CC1180HOSTID=ANYFEATURE LSC_IP_ddr_p_pm_ipe lattice 10.0 31-dec-2025 uncounted \ 79B8888680FFHOSTID=ANYFEATURE LSC_IP_ddr_p_x2_ipe lattice 10.0 31-dec-2025 uncounted \ 891CE3B07807HOSTID=ANYFEATURE LSC_IP_ddr_p_e3_ipe lattice 10.0 31-dec-2025 uncounted \ D659459B93ECHOSTID=ANYFEATURE LSC_IP_pci_t32_e3_ipe lattice 10.0 31-dec-2025 uncounted \ AB5CF3E89F2631-dec-2025 uncounted \ 9C75314C842CHOSTID=ANYFEATURE LSC_IP_pci_t64_e3_ipe lattice 10.0 31-dec-2025 uncounted \ 21E7F1ED7D2EHOSTID=ANYFEATURE LSC_IP_pci_mt64_e3_ipe lattice 10.0 31-dec-2025 uncounted \ F98938497F31HOSTID=ANYFEATURE LSC_IP_edge_det_x2_ipe lattice 10.0 31-dec-2025 uncounted \ 2E22250B008CHOSTID=ANYFEATURE LSC_IP_edge_det_e3_ipe lattice 10.0 31-dec-2025 uncounted \ C623531BFD9EHOSTID=ANYFEATURE LSC_IP_csc_x2_ipe lattice 10.0 31-dec-2025 uncounted \ 666536384764HOSTID=ANYFEATURE LSC_IP_sgmii_e3_ipe lattice 10.0 31-dec-2025 uncounted \ DCD0672C4833HOSTID=ANYFEATURE LSC_IP_pcie_x1_e3_ipe lattice 10.0 31-dec-2025 uncounted \ 307A9A056686HOSTID=ANYFEATURE LSC_IP_pcie_x4_e3_ipe lattice 10.0 31-dec-2025 uncounted \ A940A1006389HOSTID=ANYFEATURE LSC_IP_ddr3_p_e3_ipe lattice 10.0 31-dec-2025 uncounted \ 80BEE8D6FE76HOSTID=ANYFEATURE LSC_IP_scaler_e3_ipe lattice 10.0 31-dec-2025 uncounted \ 44335B509C22dec-2025 uncounted \ 34658B6C9425HOSTID=ANYFEATURE LSC_IP_divide_e3_ipe lattice 10.0 31-dec-2025 uncounted \ 003943ABF469HOSTID=ANYFEATURE LSC_IP_divide_x2_ipe lattice 10.0 31-dec-2025 uncounted \ 8BC9A567EC6E HOSTID=ANYFEATURE ACTIVEHDL_LIC_NUMBER ALDEC 2014.0500 6-may-2014 uncounted \ 846C8F32A823VENDOR_STRING=25412 HOSTID=f0def10a5abe \SIGN2="005E 9EDC 0379 C3BA E9F1 2FBB BC19 2800 837C 2F73 CBBD \ A020 B6C8 61DA 1518"FEATURE ACTIVEHDL_LATTICE_MIX_LT ALDEC 2014.0500 6-may-2014 uncounted \ 6188D2E8F535 VENDOR_STRING=25412 HOSTID=f0def10a5abe \ SIGN2="0038 73F2 1444 8C29 1329 667A 40F4 1A00 87C5 5ED3 8BA0 \ 607D 6BA7 FF66 8324" INCREMENT SSST snpslmd 1.0 06-Aug-2013 uncounted 5E40AE66DE224B155B93 \VENDOR_STRING="22fdb ded7f 205fb fc191 ede96 b96f7 40c19 1ede9 6b96f 74011 \ 01020 0963b eae9b 3db779fea2 342f8 9e29f 30fd4 d4a12 f199c \ 3520c 72e28 6534c a243a dfd33 b95f7 ac1b9 149d0 35264 27b7a \ db0d32bd50 85b88 0228a 835e0 2659a 8ae71 6e4c4 415a0 0c5c5 \ 38034 1f532 8750e 95a1d ae4eb 8338f 3f03d 43913 8fb1b 5977f \ 42283 c6f6c be3f7 caded 9249a 7b66d fafe1 e3431 5d0ca e7129 \ 1c6df 12108 17608 cf969 c9c63 9f4be 9305f e2dc9 4b5c8 b448d \ a0041 46bf1 a3660 0b61a a0a41f3dd8 a7126 0698c 9dd35 5a22c \ 40ab0 cdf49 7c042d4257 6d65f 84ab1 30aef 61f3e a1863 d277b \ 0065d8ed33 d8744 53ae8 d3376 326fa 1000b 70682 c8b0a 33b5c \ 65e9e 59abd ccdcb 307ad fb505 09d59 2b28d 3858c077d5 1f25a \ 96102 ce4a5 daceb c29" \ NOTICE="Licensed to Lattice Semiconductor Corp - OEM [DO NOTDELETE/MODIFY \ SSST OR ANY OTHER KEYS IN THIS FILE]" \ SN=TK:0:0:0 ISSUER="Synopsys, Inc. [8/6/2012 23:40:17 26232]" \ START=06-Aug-2012HOSTID=f0def10a5abeINCREMENT synplifypro_sbt snpslmd 2012.03 06-aug-2013 uncounted \ 5E406E76E033314007B5 HOSTID=f0def10a5abe ISSUED=06-aug-2012 \ ck=9SN=TK:7978-0:477717:971792 START=06-aug-2012INCREMENT synplifypro_sbt synplctyd 2012.03 06-aug-2013 uncounted \ CE504E066725FBE63F4BVENDOR_STRING=sbt,nl HOSTID=f0def10a5abe \ISSUED=06-aug-2012 ck=73 SN=TK:7978-0:477718:785300SIGN="00C2 \ 313A F357 C569 2964 6202 9496 7BE9 A57B CB31 8202 EB25 89BB \ D84C 6714 6456 C54E B9DB 9D62 3B2F 5B18"。

Lattice DDR3教程全攻略之仿真篇

Lattice ddr3教程全攻略之仿真篇By: BACKKOMQQ:784496547Date:2014/9/19 对于这部分,首先建议安装好diamond3.1,modelsim se 10.1a这两个软件,如果想仔细分析DDR3的IP部分,可仔细阅读DDR3 SDRAM Controller IP Core User’s Guide,下面用ug代指。

官网上可以download,还有DDR3的基本知识,可以到网上download《高手进阶,终极内存技术指南——完整进阶版》,这个文章值得一读。

DDR的调试成功,可以说是开发学习FPGA的一大重要标志,能够把DDR3玩转的熟练,那自称FPGA工程师也是理所当然了。

Lattice的ddr3控制器接口逻辑还是相对简单,比较好理解的,下面来看看DDR3 IP 的内部结构:图:DDR3 IP逻辑框图Initialization Module:根据JEDEC.的标准,在上电后对DDR3进行初始化配置,配置其相应的寄存器和工作方式等,具体配置的寄存器可以参看ddr3的协议文档,JEDEC规范写的很详细。

当初始化配置完成后,该模块会给出一个done信号告诉用户。

sysCLOCK PLL:用于提供IP工作所需要的时钟,并提供给用户端一个时钟:k_clk。

Data Path Logic:用于从DDR3读取的数据转换到用户端,写入的数据不经过该模块,写入的数据从Command Application Logic (CAL)模块输入。

Command Decode Logic (CDL) :该模块用于译码命令,控制core按照设定的命令正确的访问ddr3芯片。

DDR3 PHY:用于转换单端的数据转换为差分给到ddr芯片端,和差分转单端输入。

以上部分有基础了解就行,不需要深究。

图:DDR初始化时序当上电后,用户应该将init_start拉高至少200us,直到init_done被拉高一个周期,则将init_start拉低。

第3章常用EDA软件

元件符号;还可以在原理图编辑器中选择Add/New

Block Symbol,然后按提示输入符号的输入输出信号 名;输入完后,按Run键,会自动产生一个元件符号, 并放入元件库中;选择符号并移入原理图中;完成原 理图文件设计。

3.1 ISP Design Expert System

完成下层文件设计: 项目管理器中,源文件左边的“?”图标,提示这个 源文件还是未知数,而且可以看出源文件的层次结构;

3.1.2 原理图源文件输入

添加原理图输入源

3.1.2 原理图源文件输入添加元件符号:A源自D/Symbol,选择相应元件,将鼠标

移到图纸的适当位置,单击鼠标;

添加输入、输出符号(对应外部引脚时需要):从

IOPAD.LIB库选择G-INPUT、G-OUTPUT管脚放到图纸上;

连线:Add/Wire,单击开始画线,随后每次单击鼠

3.1.3 功能时序仿真

仿真分功能仿真和时间仿真 输入波形文件(*.wet)或测试向量文件(*.wdl)

启动仿真。

3.1.3 功能时序仿真

建立测试信号文件(*.wdl) 1.选择Source/New/Waveform Stimulus; 2.选择与测试文件关联的器件或设计文件; 3.输入波形文件名,进入波形编辑窗口。

3.1.4 器件编程(下载)

3.1 ISP Design Expert System

例2:触发器设计计数器 例3:调用宏单元: 计数器CBU14 显示译码器bin27

3.1 ISP Design Expert System 例4:图形层次设计法

建立顶层原理图文件,其中可以调用上面用户创建的

3、修改系统日期到2000年9月以前。

3.1.1 建立设计项目

Lattice Diamond软件安装说明

Diamond软件安装说明安装点击“B1.1.00.50.42.10_Diamond.exe”进行软件安装。

默认安装路径可更改为自己的安装路径。

安装过程中都是默认进行下去,一般不需要修改什么。

Diamond安装成后会提示安装USB驱动。

可以取消以后再安装驱动。

驱动是在:“安装路径\ispvmsystem\Dr iver s\FTDIUSBDr iver”文件夹下。

软件环境变量位置(可以不改动)Diamond的环境变量在软件安装时,就默认建立了。

默认指向license文件夹。

环境变量名:“LM_LICENSE_FILE”。

路径(指变量值)默认为:“\安装路径\ license\license.dat”。

一般不需要改动环境变量,只需要将所给软件光盘里带的“license.dat”拷贝到“\安装路径\license\”文件夹下。

如果安装了Diamond,并设置过环境变量,再安装IspLEVER Classic就不需要再设置环境变量了,证书文件直接使用的是Diamond路径下指定的“license.dat”即可。

我的电脑→属性→高级→环境变量系统变量→LM_LICENSE_FILE\安装路径\license\license.dat建立虚拟网卡使用Lattice软件前,首先需要建立一个虚拟网卡,并使用网卡MAC地址修改软件将虚拟网卡的MAC(Physical Addr ess)值改为“license.dat”中HOSTID对应的值。

(虚拟网卡软件和网卡修改软件网上可以搜索到很多的。

)虚拟网卡MAC设置好了之后,将电脑重新启动,使设置好的MAC生效。

安装完成。

运行软件点击“「开始」菜单\程序\Lattice Diamond1.1”进入到软件界面。

梦幻晶格:E-mail:1162051686@。

lattice-fpga-加密方法

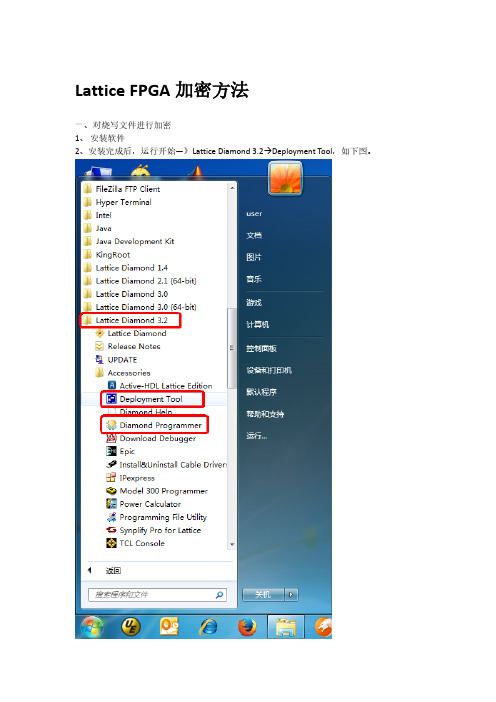

Lattice FPGA加密方法一、对烧写文件进行加密1、安装软件2、安装完成后,运行开始—》Lattice Diamond 3.2→Deployment Tool,如下图。

3、在output File Type选项下,选择Bitstream,然后OK,如下图:4、在File Name下,点击三个点的图片,添加需要加密的烧写文件(示例:tcon_impl1.bit)。

5、添加完成后,会相应显示该烧写文件对应的Device Family和Device,然后,点击next,如下图6、勾选Encryption,在configuration下,选择jtag,点击Edit Key,输入密钥(这就是要固化到FPGA里面的密钥);点击Save Key,保存这个密钥,这里保存为key.bek,(重要:这个密钥要保存好),保存后,软件还需要一个打开这个密钥的密码。

如下图:点击next10、在output File下,选择一个路径用于保存加密后的烧写文件和文件名(文件名要换一个,不然可能会把原先的烧写文件给覆盖掉)点击next11、点击Generate12、完成烧写文件加密!二、烧写密钥1、运行开始—》Lattice Diamond 3.2→ Diamond Programmer2、按默认,选择OK2、将要烧写FPGA 的jtag口和电脑通过烧写器连接;3、点击Scan,下图红框中的图标,扫描FPGA器件。

4、在Device下面选择目标FPGA器件名称(有时候烧写器可能不能识别到具体器件),如下图。

5、双击Operation下面的Fast Program,弹出如下界面在Access mode下面,选择Advanced Security Keys Programming;点击Load Key…,选择密钥(本文是key.bek,上文有提及),在Program key lock Type ‘yes’to confirm下,输入yes;点击OK6、点击Program,下图红框中的图标,将密钥烧写到FPGA7、完成密钥烧写!三、烧写加密文件1、双击Operation下面的Fast Program,弹出如下界面。

Lattice Diamond 一步一步教你学

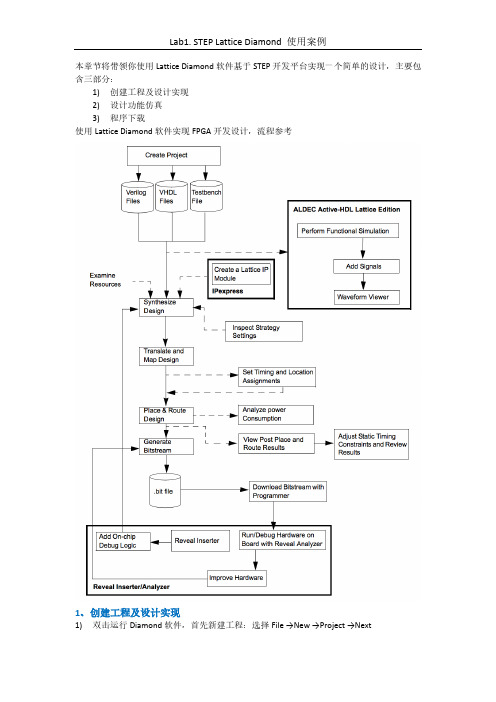

本章节将带领你使用Lattice Diamond软件基于STEP开发平台实现一个简单的设计,主要包含三部分:1)创建工程及设计实现2)设计功能仿真3)程序下载使用Lattice Diamond软件实现FPGA开发设计,流程参考1、创建工程及设计实现1)双击运行Diamond软件,首先新建工程:选择File →New →Project →Next2)工程命名:我们将新工程命名为LED_shining,工程目录G:/LED_shining(注意在工程目录中不要有汉字),然后点击Next3)添加相关设计文件或约束文件(如果已经有设计文件和约束文件,我们可以选择添加进工程):这里我们新建工程,没有相关文件,不需添加,直接Next4)器件选择:按照Step FPGA开发板器件LCMXO2-4000HC-4MG132C配置,Next5)选择综合工具:Synplify Pro(第三方)和Lattice LSE(原厂)都可以,我们就使用LatticeLSE,直接Next6)工程信息确认:上面选择的所有信息都在这里,确认没有问题,直接Finish7)工程已经建好,我们下面添加设计文件, 选择Fi le →New →File8)选择Verilog Files(选择自己使用的硬件描述语言),Name填写LED_shining,然后点击New,这样我们就创建了一个新的设计文件LED_shining.v,然后我们就可以在设计文件中进行编程了9)程序源码已经准备好,如下,将代码复制到设计文件LED_shining.v中,并保存。

10)程序编写完成,需要综合,在软件左侧Process栏,选择Process,双击Synthesis Design,对设计进行综合,综合完成后Synthesis Design显示绿色对勾(如果显示红色叉号,说明代码有问题,根据提示修改代码),如图11)通过综合工具,我们的代码就被综合成了电路,生成的具体电路,我们可以通过选择Tools → Netlist Analyzer查看(仅限Lattice的综合工具,第三方综合工具无法查看),如图12)综合生成电路后,分配管脚,选择Tools → Spreadsheet View,分配管脚,设置IO_TYPE为LVCMOS33,保存,界面如下13)在软件左侧Process栏,选择Process,勾选所有选项,直接双击Export Files,所有布局布线输出依次完成,结束后,所有选项显示绿色对勾。

lattice_fpga 加密方法

Lattice FPGA加密方法兰进城QQ 554215112 2014-6-19一、对烧写文件进行加密1、安装软件下载地址:链接:/s/1qW2UEBi 密码:n9lx下载后有两个安装两个文件,多要安装:(1)3.2.0.134_Diamond.exe、(2)3.2.0.134_Control_Pack_Encryption.exe2、安装完成后,运行开始—》Lattice Diamond 3.2 Deployment Tool,如下图。

3、在output File Type选项下,选择Bitstream,然后OK,如下图:4、在File Name下,点击三个点的图片,添加需要加密的烧写文件(示例:tcon_impl1.bit)。

5、添加完成后,会相应显示该烧写文件对应的Device Family和Device,然后,点击next,如下图6、勾选Encryption,在configuration下,选择jtag,点击Edit Key,输入密钥(这就是要固化到FPGA里面的密钥);点击Save Key,保存这个密钥,这里保存为key.bek,(重要:这个密钥要保存好),保存后,软件还需要一个打开这个密钥的密码。

如下图:点击next点击next11、点击Generate12、完成烧写文件加密!二、烧写密钥1、运行开始—》Lattice Diamond 3.2 Diamond Programmer2、按默认,选择OK2、将要烧写FPGA 的jtag口和电脑通过烧写器连接;3、点击Scan,下图红框中的图标,扫描FPGA器件。

4、在Device下面选择目标FPGA器件名称(有时候烧写器可能不能识别到具体器件),如下图。

5、双击Operation下面的Fast Program,弹出如下界面在Access mode下面,选择Advanced Security Keys Programming;点击Load Key…,选择密钥(本文是key.bek,上文有提及),在Program key lock Type ‘yes’to confirm下,输入yes;点击OK6、点击Program,下图红框中的图标,将密钥烧写到FPGA7、完成密钥烧写!三、烧写加密文件1、双击Operation下面的Fast Program,弹出如下界面。

Diamond用户手册

循序渐进 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 17

连接性与过滤功能 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 18

4. 或许您还想接着浏览一下“DIAMOND 教程 B:高级示例”这一章,以便对接下来 的内容有个印象。

5. 随后,请您坐到计算机前并练习 DIAMOND 教程 B,在这一阶段,您将深入了解 DIAMOND 最精彩的特色功能。

6. 最后,您可以随意地尝试一下本软件的各项功能,就从您自己研究中的实例开始下 手。

使用 POV-RayTM 绘制高质量图片 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 43

使用 DIAMOND 录制视频 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 49

进阶指南:DIAMOND 的理念

17

任务 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 17

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

Diamond软件安装说明

安装

点击“B1.1.00.50.42.10_Diamond.exe”进行软件安装。

默认安装路径可更改为自己的安装路径。

安装过程中都是默认进行下去,一般不需要修改什么。

Diamond安装成后会提示安装USB驱动。

可以取消以后再安装驱动。

驱动是在:“安装路径\ispvmsystem\Dr iver s\FTDIUSBDr iver”文件夹下。

软件环境变量位置(可以不改动)

Diamond的环境变量在软件安装时,就默认建立了。

默认指向license文件夹。

环境变量名:“LM_LICENSE_FILE”。

路径(指变量值)默认为:“\安装路径\ license\license.dat”。

一般不需要改动环境变量,只需要将所给软件光盘里带的“license.dat”拷贝到“\安装路径\license\”文件夹下。

如果安装了Diamond,并设置过环境变量,再安装IspLEVER Classic就不需要再设置环境变量了,证书文件直接使用的是Diamond路径下指定的“license.dat”即可。

我的电脑→属性→高级→环境变量

系统变量→LM_LICENSE_FILE

\安装路径\license\license.dat

建立虚拟网卡

使用Lattice软件前,首先需要建立一个虚拟网卡,并使用网卡MAC地址修改软件将虚拟网卡的MAC(Physical Addr ess)值改为“license.dat”中HOSTID对应的值。

(虚拟网卡软件和网卡修改软件网上可以搜索到很多的。

)

虚拟网卡MAC设置好了之后,将电脑重新启动,使设置好的MAC生效。

安装完成。

运行软件

点击“「开始」菜单\程序\Lattice Diamond1.1”进入到软件界面。

梦幻晶格:

E-mail:1162051686@。