ALTERA FPGA EP2C5Q 开发板用户手册

FPGA_CPLD设计开发流程快速入门指南 ALTERA篇QuartusII 史上最全

对于本工程实例,设置好器件型号后,就可以直接选择【Finish】即可进入“第五节 逻 辑设计”即可,但如果您想了解其它页表项,可继续往下阅读。

(5)选择【Next >】后即可进入 EDA 工具设置页表项。QuartusII 支持很多第三方工具, 比如综合工具、仿真工具等等,第三工具通常在某一方面更为专业,特别 是仿真工具, QuartusII 已经不再提供仿真功能,只能用第三方仿真工具,如 Modelsim 来进行仿真。

在总结中显示了当前工程编译后所占用的资源情况,本工程占用 51 个宏单元,占用总 设计资源的 21%,使用了 2 个引脚(即 clk 与 clk_out),占用总引脚的 3%

九、逻辑下载

逻辑全编译后即可生成下载文件,对于 CPLD 开发平台,通常是.pof 文件,对于 FPGA 开发平台,还可以是.sof、.jic 等文件

完成后此时应如下图所示:

6

All rights reserved, NO Spreading without Authorization

professional products right for you ( / )

六、逻辑综合

逻辑设计完毕后,可以初步对逻辑进行综合,以进行分析

(1)选择菜单【Processing】→【Start】→【Start Analysis & Synthesis】后,即可开始 进行逻辑设计的综合过程,完成后应如下图所示:

(2)菜单选择【Tools】→【Netlist Viewers】→【RTL Viewer】后即可出现 RTL(寄存器 传输级)图,通常,对于简单的逻辑错误,使用 RTL 可以看出来。本文要实现的是 26 位分 频器,下图表示,每到来一个时钟,即使用 Add0 加法器将当前 tmp 寄存器中的值累加 1, 再通过一个 clk_out~reg0 将最高位输出,这正好应证了我们的设计思路。

睿智FPGA开发板用户手册1.5版本最新

伟欣科技®睿智FPGA 2C5/2C8 开发板用户手册更新日期:2011‐12‐10请关注论坛,最新文档及资料、代码将在论坛发布我们的FPGA开发网官方网站:官方淘宝店: /邮箱:OurFPGA@QQ群:155291300提醒:请您在使用此开发板前,认真阅读此说明书,并将此电子书妥善保管,在开发学习中,可能会经常使用查询!欢迎对FPGA、嵌入式、单片机等感兴趣的朋友登陆网站,参加技术交流,下载技术资料。

在普通会员区,提供了约200多门视频教程下载(截止到2011年8月1日的数量,每周会更新添加,数量还在增加中。

),欢迎您来访!现在立即去体验一下:开发板简介FPGA与EDA技术是目前相当热门的技术,翻遍各大招聘网站电子类招聘信息,类似“精通FPGA技术,熟悉Verilog VHDL语言”等字眼已经为应聘者所熟悉;甚至,有的时候,“熟悉FPGA”就意味着高薪!实际上,FPGA技术已经成为目前电子行业应用最为广泛的技术之一,未来的就业和发展前景相当好!目前有众多朋友热切的期望能学习FPGA知识,FPGA技术实践性极强,拥有一块适合学习需求的FPGA开发板是非常有必要的!睿智FPGA开发板正是为此推出的一套高性价比开发板!此开发板由“伟欣科技®”精心设计开发,采用 Altera公司的CycloneII系列芯片EP2C5Q208C8、EP2C8Q208C8作为核心处理器进行设计,CycloneII系列芯片可以说是目前市场上性价比最高的芯片,比第一代芯片设计上、内部的逻辑资源上都有很大的改进,同时价格也可以被广大用户接受。

睿智FPGA开发板采用核心板与接口板分离的方式,核心板上除FPGA、各类存储器以及用户扩展PACK外,还有按键、LED及电源插座等。

因为有用户扩展PACK,核心板完全可以脱离接口板而单独使用,通过PACK,用于自己的设计或电子设计大赛,扩展性极好。

接口板上集成了最常用和经典外围接口,所有的外设经过精心分配及设计,不需要进行任何跳线设置,实验时非常方便!此外,对于重点外设的关键信号都设置了测试点,方便用户使用逻辑分析仪、示波器、万用表等进行信号测量。

EP2C5T144核心板说明

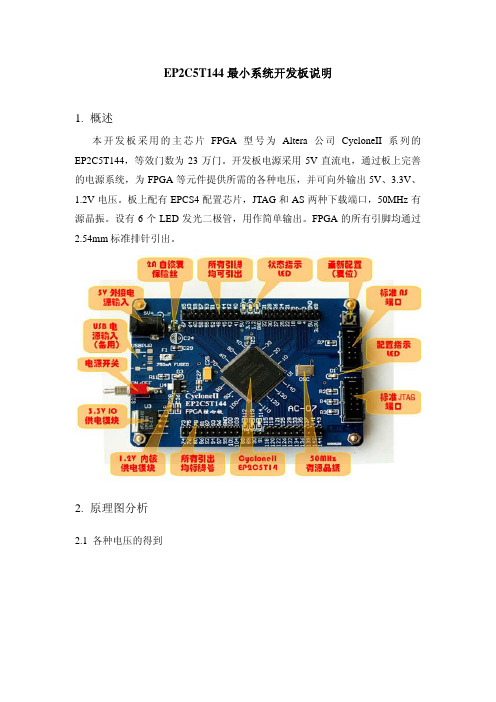

EP2C5T144最小系统开发板说明1.概述本开发板采用的主芯片FPGA型号为Altera公司CycloneII系列的EP2C5T144,等效门数为23万门。

开发板电源采用5V直流电,通过板上完善的电源系统,为FPGA等元件提供所需的各种电压,并可向外输出5V、3.3V、1.2V电压。

板上配有EPCS4配置芯片,JTAG和AS两种下载端口,50MHz有源晶振。

设有6个LED发光二极管,用作简单输出。

FPGA的所有引脚均通过2.54mm标准排针引出。

2.原理图分析2.1各种电压的得到如上图所示,开发板的输入电压是5V 。

通过U3:LM1085-3.3的LDO 芯片,得到3.3V 电压。

此芯片最大电流支持到3A 。

再通过AMS1117-1.2(板上显示REG1117,这只是芯片品牌不同,功能相同),获取1.2V 电压。

3.3V 电压是提供给FPGA 的IO 使用的。

也就是说,FPGA 的IO 引脚电平采用的是3.3V 。

1.2V 电压是提供给FPGA 内核的工作电压,以及FPGA 内部PLL 的工作电压。

1.2V 电压的纯净程度要求比较高,故采用C25钽电容滤波。

2.2 IO 电压、内核电压供电连接如左图,VCCIO1-VCCIO4四组电压均连接3.3V 。

FPGA 有很多的IO ,它们是分组的。

在EP2C5T144芯片中,分为四组(Bank ),每组(每个Bank )的IO 引脚供电是独立的,因此可以采用不同的电平标准。

本开发板的所有IO 脚都采用3.3V 电压标准,所以所有的VCCIO 都连接3.3V 。

VCCINT 为FPGA 内核工作电压输入。

CycloneII 系列的FPGA 均采用1.2V 的内核电压,所以这里连接1.2V 。

2.3 PLL (锁相环)电压供电连接EP2C5T144片内含有2个PLL 。

PLL 的作用是产生各种频率的时钟,在FPGA 中拥有重要的地位。

VCCA_PLL1、VCCD_PLL1和VCCA_PLL2、VCCD_PLL2分别是两个PLL 的模拟电源、数字电源。

Quartus II 9.1 使用教程 ALTERA FPGA 入门教程

liuts 2011-8

Quartus II 9.1 使用教程

设计一个点亮4位LED灯程序

要求: 1、FPGA器件型号:EP2C35F484C8N 2、存储FPGA代码芯片:EPCS16 3、系统输入时钟50MHZ 4、设计一个29位分频计数器 5、将分频器的26-29位用4个LED指示灯显示; 6、系统下载配表管脚:

编辑文本并作必要注释,跟工程文件保存同一文件夹

编译工程

代码有错,编译器提示错误

修改错误(图示:下一页)

1 点击Messages栏中的“Error” 筛选错误 2 双击第一行错误(注意第一行) 3 双击第一行错误后,代码中的错误行会反色显示 ,将多余的”);”删掉 4 重新编译 5 如果还有错误,重复1-4,直到通过编译

添加脚本文件到工程

查看管脚是否指定成功(此过程可以忽略) 路径:Assignments->Pins

重新编译

用JTAG模式,直接下载程序到FPGA运行 掉电后程序不保存

掉电存储方式 将程序下载到EPCS存储芯片

见 “使用JTAG下载EPCS器件的方法.pdf”

TCL脚本文件

#指定系统时钟输入管脚从L1输入 set_location_assignment PIN_L1 -to sys_clk #指定复位信号输入管脚从U12输入 set_location_assignment PIN_U12 -to rst_n #****************************************************** #指定LED灯闪动信号从D15 E14 C14 D14输出 set_location_assignment PIN_D15 -to LED\[0\] set_location_assignment PIN_E14 -to LED\[1\] set_location_assignment PIN_C14 -to LED\[2\] set_location_assignment PIN_D14 -to LED\[3\] #******************************************************

21EDA-Altera-FPGA开发板使用入门

在自己做这个实验的时候,需要确认自己的开发软件是否已经安装好了,确认自己的下载器是否已经可以使用了。

如果还不熟悉的,可以看看下面两个文件QuartusII 9.0破解全过程.pdf下载器的安装.pdf实验要求:PC电脑一台,配置越高越好。

开发软件:QuartusII9.0SP2开发板型号:A-C8V4实验结果:学习Altera公司的FPGA开发软件QuartusII入门使用。

首先打开QuartusII9.0SP2的开发软件。

你有三种方法可以打开。

第一:如下图,桌面上有快捷图标。

双击就可以了。

第二:如下图,在开始菜单里面可以找到。

第三:如下图,在开始菜单里面也可以找到。

如下图:打开QII软件了如下图:我们可以把这个关闭了。

如下图:新建一个工程File->New Project Wizrd….如下图:点击Next如下图:这里我们要设置工程路径,工程名和顶层名。

点第一排三个点点那里如下图:我们把工程路径放在J盘下面FPGA_TEST文件夹;J:\FPGA_TEST设置好了,点击Next如下图:直接点击Next如下图:这里我们需要对CPU进行设置,也就是设置成和我们开发板对应的芯片。

Family 要选择Cyclone II如下图:如下图:选择芯片的封装,PQFP如下图:如下图:选择芯片的管教数目,我们这里是208个脚如下图:如下图:选择速度等级,我们这里选择8如下图:如下图:选择我们最后设置好的芯片。

然后点击Next如下图:然后点击Next如下图:然后点击Finish如下图:如下图:然后点击Next如下图:点击File->New 新建一个我们用来编写程序的窗口。

如下图:如果你使用Verilog语言,就选择Verilog HDL File 然后点击OK如下图:如果你使用VHDL语言,就选择VHDL File 然后点击OK 我们这里用VHDL作为演示如下图:会在右边出现程序编写的空白窗口。

如下图:假设我们已经编写了程序A-C8V4-开发板资料A\A-C8V4开发板资料\A-C8V4开发板-整理的VHDL程序\ 15实验十五:LED流水灯A (用这个里面的程序)如下图:我们的程序编写了,要保存File -> Save如下图:如下图:保存了之后,就要编译,如下图:我们编译的时候出错了。

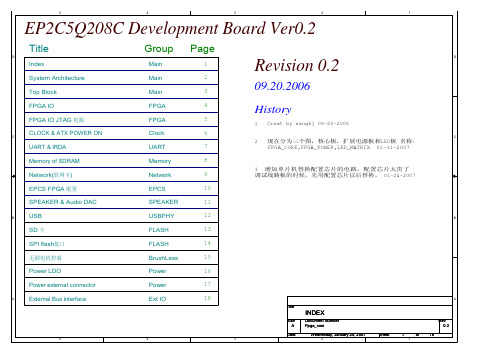

EP2C5Q208C开发板

B

USB SD 卡 SPI flash接口 无刷电机控制 Power LDO Power external connector

B

A

External Bus interface

A

Title

INDEX

Size A Date:

5 4 3

Document Number Fpga_core Wednesday, January 24, 2007

134 135 137 138 139 141 142 143 144 146 147 149 150

IO_D50 IO_D52 PQFP208 IO_D51 IO_D53 IO_D54 IO_D55 IO_D56 IO_D57 IO_D58 IO_D59 IO_D60 IO_D61 IO_D62

Version = 1.0 15 U2

80 81 82 84 86 87 88 90 92 94 95 96 97 99 101 102 103 104

A9 A10 A11 A14 A12 A13 SD_D0 SD_D1 SD_D2 SD_D3 IO_D63 IO_D64 IO_D65 SPK_L__SDA SPK_R__SCL 11 11

IO_VB2N0_182 IO_VB2N1_185 IO_VB2N1_187 IO_VB2N1_188 IO_VB2N1_189 IO_VB2N1_191 IO_VB2N1_193 IO_VB2N1_195 IO_VB2N1_197 IO_VB2N1_198 IO_VB2N1_199 IO_VB2N1_200 IO_VB2N1_201 IO_VB2N1_203 IO_VB2N1_205 IO_VB2N1_207 IO_VB2N1_208

nWBE1 SDCLK SDCKE

Altera公司FPGA的配置

10

(4)PCB电路板上的10针连接插头

PCB板上的10针插头连接到FPGA器件的编程 或配置引脚上,ByteBlaster下载电缆的10针插座 连接到PCB板上的10针插头,ByteBlaster电缆通 过10针插头获得电源并下载数据到FPGA器件上。

编辑ppt

11

2. ByteBlasterMV并行下载电缆

编辑ppt

4

(2)电缆插头与插座

ByteBlaster与PC机并口相连的是25针插头,与FPGA 应用电路PCB电路板相连的是10针插座。编程数据从PC机 并口通过ByteBlaster电缆下载到电路板。连接示意图如 图6.1所示。

注意:利用 ByteBlaster下载电缆配置/编程3.3V器 件(如FLEX10KA、MAX7000A器件)时,要将电缆的VCC脚 连到5.0V电源,而器件的VCC脚连到3.3V电源。FLEX10KA 和 MAX7000A器件能够耐压到 5.0V,因此,ByteBlaster 电缆的5.0 V输出不会对 3.3 V器件造成损害,但5.0V电 源中应连接上拉电阻。

编辑ppt

15

(3)电缆插头与插座

ByteBlasterMV的25针插头,与ByteBlaster 下载电缆的区别仅是第15脚不同,ByteBlaster 连到GND,而ByteBlasterMV连到VCC。

ByteBlasterMV的10针插座与ByteBlaster电 缆的10针插座完缆

针对FPGA器件不同的内部结构,Altera公司 提供了不同的器件配置方式。Altera FPGA的配 置可通过编程器、JATG接口在线编程及Altera在 线配置等方式进行。

Altera器件编程下载电缆的有: ByteBlaster并行下载电缆,ByteBlasterMV并行 下载电缆,MasterBlaster串行/USB通信电缆, BitBlaster串口下载电缆。

FPGA开发板使用说明书(二版)

目 录第一章综述 (1)核心板介绍EP1C12核心板资源介绍 (1)EP2C35核心板资源介绍 (2)FPGA开发板介绍FPGA开发板资源介绍 (4)第二章 系统模块功能介绍 (7)EP1C12核心板模块说明EP1C12F324C8芯片说明 (9)NOR FLASH模块说明 (10)SRAM模块说明 (11)FPGA接口I/O说明 (12)EP2C35核心板模块说明EP2C35F484C8芯片说明 (19)NOR FLASH模块说明 (20)SRAM模块说明 (21)S D R A M模块说明 (22)NAND FLASH模块说明 (23)FPGA接口I/O说明 (24)核心板使用注意事项 (29)FPGA开发平台模块说明液晶显示模块 (31)RTC实时时钟模块 (33)USB接口模块 (33)音频CODEC接口模块 (34)EEPROM存储模块 (35)数字温度传感器模块 (36)其它功能模块 (37)FPGA开发平台使用注意事项 (38)第三章 软件的安装 (39)QUARTUSII的安装 (39)QUARTUSII的授权 (46)NIOSII IDE的安装 (51)附表一核心板载资源与FPGAEP1C12I/O接口对照表 (55)附表二核心板载资源与FPGAEP2C35I/O接口对照表 (60)附表三EP1C12/ EP2C35与开发板硬件资源I/O接口对照表 (66)第一章综述FPGA开发平台是根据现代电子发展的方向,集EDA和SOPC系统开发为一体的综合性实验开发系统,除了满足高校专、本科生和研究生的SOPC教学实验开发之外,也是电子设计和电子项目开发的理想工具。

整个开发系统由核心板、SOPC开发平台和扩展板构成,根据用户不同的需求配置成不同的开发系统。

系统根据用户不同的设计需求来更换其它不同系列的核心板,如: EP1C12、EP2C20、EP3C25等。

所以,不管从性能上而言,还是从系统灵活性上而言,无论您是初学者,还是资深硬件工程师,它都会成为您的好帮手。

FPGA黑金开发板用户手册

Black Gold 黑金动力II代用户手册v1.0修订历史目录内容介绍:本手册包括以下部分第一部分, 主要器件及特性第二部分, 开关,按键及数码管第三部分, VGA接口Chapter 1 主要器件及特性本手册中描述了”黑金动力”系列开发板的设计原理和使用方法,作为开发板的配套说明材料.这套开发板主要是面向FPGA的初级,中级开发人员,或者对FPGA感兴趣的爱好者,偏向个人用户.这套开发板采用核心板与扩展板分离的方式,简单实用,扩展性好,特别适合爱好者的快速入门和开发人员的产品开发验证,也适合做更深入的IC前端设计.在这套开发板上,一切皆有可能.同时,这套开发板也提供了一个SOPC平台,可以实现嵌入式的软核,如NIOSII,Open RISC等,为嵌入式电子产品的设计开发提供了又一种选择.主要元器件介绍●Altera Cyclone Ⅱ系列 FPGA核心板配置的FPGA芯片是Cyclone Ⅱ系列的EP2C8Q208C更详细可到:/literature/lit-cyc2.jsp下载官方手册●64Mbit的SDRAM核心板同时配备了高达64Mbit的SDRAM,对于运行NIOS的软核提供了有力的保障,这款芯片的时钟频率有143MHz,实验证明,NIOSⅡ可以稳定地运行120MHz,速度还是相当快的.●16Mbit的配置芯片核心板还配备了16Mbit的配置芯片,不仅可以储存配置信息,同时可以实现NIOSⅡ软件程序存储.●20MHz的有源晶振20M的有源晶振为整个系统提供了时钟源泉.●ENC28J60网口芯片实现开发板与以太网之间的通信实验.●USB 2.0高速数据接口采用应用广泛,性能稳定的CH376芯片,实现了开发板USB接口的扩展,便于与计算机进行高速数据通信.●板载128*64的点阵LCD采用ST7565P控制芯片,内置DC/DC电路,可以通过串行,并行进行通信.●实时时钟芯片(RTC)配置DS1302芯片,增加了主电源/后背电源双电源引脚,同时提供了对后背电源进行涓细电流充电的能力.●EEPROM配置24LC04芯片,24LC04是512*8bit的EEPROM,支持IIC接口.●PS/2鼠标,键盘接口标准的鼠标,键盘接口,支持3.3V和5V设备,可以用来验证PS/2接口协议.●9针RS-232串口实现与计算机的数据通信,辅助调试.●VGA接口标准VGA接口,可直接与显示器连接,用于验证VGA时序.●5个独立按键可以与液晶配合,实现完美的人机界面.开发板示意图核心板扩展板-Chapter 2 开关,按键与数码管按键在绝大多数电子电气设备中都存在身影,可以说,如果说显示屏是人与机器之间沟通的窗户的话,按键就是沟通的桥梁,通过按键,可以方便快捷地对机器进行操作控制.在黑金开发板中,我们设置了5个按键,分别为上,下,左,右,确认,用户可以自行设定按键的功能.电源开关电源接口及开关位于核心板左上方,如图其中F1为限流1.1A的F110保险管,在电源的保护上起到了很大的作用按键核心板上的复位电路该复位电路可以实现对开发板的初始化作用,防止程序陷入死循环.扩展板上的按键扩展板上搭配有5个按键,可以满足大多数场合的设计需要,采用低电平闭合电路.按键开关管脚映射表LEDs在核心板上设置了4个LED,可以作为测试使用,电路如图LED管脚映射表数码管在扩展板上并设有6位独立共阳数码管,实验证明数码管在诸多设计开发中起到了不可代替的作用.数码管的电路如图该电路图为第一位数码管的电路,其他的电路与之类似.其中,每个数码管都通过一个9012三极管放大电流,保证其亮度均匀.数码管管脚映射表Chapter 3 点阵型液晶显示器(LCD)在扩展板的右方包括了一块128*64像素的液晶显示器,带有少见的白色背光.常见的LCD模块有LCM(玻璃),背光,PCB板,三种之中LCM(玻璃)模块必不可少,有无背光,有无PCB用户可以根据需要自行选择.点阵的LCD模块按驱动控制器的集成方式分成两种:COB和COG,COG是将驱动控制芯片集成到了玻璃里面,用户只需在电路板上加上无法集成的电阻电容即可实现对LCD的控制;而COB则需要将驱动芯片焊接在LCD模块后面的PCB板上.黑金开发板上提供的LCD使用的是COG液晶,它将驱动控制IC集成到了LCM上,这样就省去了PCB底板,节省了很大的空间.该LCD的驱动芯片为ST7565P,支持三种接口方式,通常采用串行时序方式,接口简单,使用方便.LCD的原理图LCD的管脚映射表LCD参数注意:该LCD的显存存在8(page)*8+1行,即65行,s0-s131列,即132列,与标准的128*64液晶有的差异,该LCD的最后一行(page8的D0)和最后三列(ADC为正常时,s129,s130,s131;ADC为反向时,s0,s1,s2)是不能显示的,而显存上其他数据与LCD上的点一一对应,具体如下图红圈所示显示屏上的每个点都对应控制器片内显示缓存RAM中的一个位,显示屏上的64*128个点分别对应显示RAM的8个Page,每个Page有128 Byte的空间对应,如图所示用户如果要点亮LCD屏幕上的某一个点时,实际上就是对该点所对应的显示RAM区中的某一个位进行置1操作;所以就要确定该点所在的行地址,列地址.由上图可以看出,液晶的行地址实际上就是Page的信息,每个Page应有8行;而列地址表示该点的横坐标,在屏上为从左到右排列,Page中的一个Byte对应的是一列(8行,即8个点),一共128列.可以根据这样的关系在程序中控制LCD屏幕的显示.在LCD上显示字符,不管是中文还是英文,都需要字库的支持,在有些LCD模块中,已经将字库烧写在芯片当中,这样的字库有优点也有缺点.优点是操作简单,而缺点是不灵活,显示效果不好,扩展性差,而且性价比不高.黑金开发板所选用的COG屏幕是不带字库的.Chapter 4 VGA接口VGA(Video Graphics Array)接口,也叫D-Sub接口,是显示卡上输出模拟信号的接口,显卡所处理的信息最终都要输出到显示屏上显示,显卡的输出接口就是电脑与显示屏之间桥梁,它负责向显示器输出相应的图像信号.CRT显示器因为设计制造上的原因,只能接受模拟信号,这就需要显卡能够输入模拟信号,于是就有了VGA接口.虽然液晶显示器可以直接接接收数字信号,但是为了兼容性,大多数液晶显示器也配备了VGA接口模块.VGA是IBM在1987年随PS/2机一起推出的一种视频传输标准,具有分辨率高,显示速率快,颜色丰富等优点,在彩色显示器领域得到了广泛的应用.目前VGA技术的应用还主要基亍VGA显示卡的计算机,笔记本等设备.根据分辨率不同,VGA分为VGA (640x480),SVGA(800x600),XGA(1024x768),SXGA(1280x1024)等.虽然说VGA的标准对于现在的个人计算机市场十分过时,但是VGA仍然是所有制造商所支持的最低标准,例如不管所有厂商的显卡,在不安装自己驱动的情况下,都是支持VGA 标准显示的.VGA接口是一种D型接口(D-SUB),上面共有15个针孔,分成三排,每排五个,如图所示.VGA引脚定义引脚1,2,3分别为红绿蓝三基色模拟电压,为0~0.714V peak-peak(峰-峰值),0V代表无色,0.714V代表满色.一些非标准显示器使用的是 1Vpp的满色电平.HSYNC与VSYNC 分别为行数据同步与帧数据同步,为TTL电平.黑金开发板的扩展板上配备了一个VGA接口,其电路为VGA管脚映射表VGA的时序介绍VGA的时序如图所示,它分为行数据时序和帧数据时序行数据时序为显示一行数据的时序,由上图可看出,显示一行数据需要处理两件事情:第一,产生行同步HSYNC.不难看出HSYNC是一个脉冲信号,该信号周期为:e=a+b+c+d,低电平时间为a.其中a,b,c,d均为时间信号,这些信号根据需要显示的分辨率的不同而不同.第二,产生显示的数据(DATA)信号,此信号为模拟信号,当在显示有效数据(Active Video)内,DATA信号为0~0.714Vpp的模拟电压(R,G,B),根据分辨率的不同,DATA的采样率,点数也不同.帧数据时序与行数据时序类似,是显示一个屏数据的时序.只是这里的基本单位为每行数据,而行数据里面的最基本单位为每个点.下表列出常用分辨率及时间参数Chapter 5 PS/2 鼠标键盘接口PS/2 原是“Personal System 2”的意思,“个人系统2”,是IBM公司在上个世纪80年代推出的一种个人电脑。

EP2C5开发板用户手册V2

开发板硬件手册--FPGA开发板配套教程(一)SOPC技术前沿目 录第一节手册指南 (1)1.1如何使用该手册 (1)1.2相关说明 (2)1.3联系我们 (2)第二节 开发板资源简介 (3)2.1NIOSII-EP2C5核心板资源 (3)2.2核心板系统功能 (3)2.3EDA/SOPC系统板资源介绍 (4)第三节 核心板模块说明 (6)3.1C YCLONE II EP2C5Q208FPGA (8)3.2JTAG调试接口 (8)3.3存储单元 (9)3.3.1 EPCS4 配置芯片 (9)3.3.2 SDRAM (10)3.3.3 Nor-FLASH (12)3.4输入/输出设备 (14)3.4.1 晶振 (14)3.4.2 用户自定义LED (14)3.4.3 复位按键 (15)3.5电源管理接口 (16)3.6扩展接口 (17)第四节 系统板功能模块说明 (22)4.1显示及显示控制 (23)4.1.1 数码管显示模块 (23)4.1.2 八位LED功能模块 (24)4.1.3 1602LCD显示模块 (25)4.2按键开关输入模块 (27)4.3功能接口模块 (28)4.3.1 串行通信接口模块 (28)4.3.2 PS/2鼠标键盘接口 (28)4.3.3 SD/MMC SD卡接口 (30)4.3.4 VGA显示接口 (31)4.4控制模块及传感器 (32)4.4.1 RTC实时时钟 (32)4.4.2 数字温度传感器 (33)4.4.3 EEPROM存储模块 (34)4.4.3 蜂鸣器 (34)4.5FPGA扩展接口 (35)第五节 软件的安装与授权 (37)5.1QUARTUSII的安装与授权 (38)5.1.1 PC机的系统配置 (38)5.1.2 QUARTUSII软件的安装 (38)5.1.3 QUARTUSII软件的授权 (45)5.2NIOSII软件的安装 (51)附表一:核心板上资源模块与FPGA的管脚连接表 (57)附表二:系统板上资源模块与FPGA的管脚连接表 (61)第一节手册指南非常感谢选用本公司开发研制的HH-FPGAB系列EDA/SOPC开发平台产品。

Altera开发工具手册_宋伟

Altera开发工具手册Cytech-XAVincent SongQ2 2008目录一、Quartus II的设计流程 (3)二、Quartus II软件介绍和使用 (4)2.1 Quartus II的用户界面 (4)2.1.1标题栏 (5)2.1.2 菜单栏 (5)2.1.3 工具栏(Tool Bar) (7)2.1.4 资源管理窗 (7)2.1.5 工程工作区 (8)2.1.6 编译状态显示窗 (8)2.1.7 信息显示窗(Messages) (8)2.2设计输入 (8)2.2.1 创建工程 (8)2.2.2 设计输入方式 (13)2.2.3 编译和综合 (15)2.2.4引脚分配 (17)2.3仿真 (18)2.3.1 使用Quartus II仿真器进行仿真 (18)2.3.2 使用ModelSim-SE进行仿真 (23)2.4时序约束 (28)2.4.1设计时序约束的常用方法 (29)2.4.2指定工程范围的时序设置 (30)2.4.3指定个别时序分配 (30)2.4.4进行时序分析 (31)2.5使用Synplify Pro做综合 (32)2.5.1在Synplify Pro下建立工程 (32)2.5.2在Quartus II下编译工程 (35)2.6器件编程 (36)2.6.1简介 (36)2.6.2完成器件编程 (36)三、高级功能的应用 (40)3.1 TimeQuest时序分析器 (40)3.1.1 优势 (40)3.1.2 软件及器件支持 (40)3.1.3 软件应用 (41)3.2 SignalTap II分析器 (43)3.2.1 SignalTap II的特点 (44)3.2.2 SignalTap II的使用 (49)在可编程逻辑器件行业,主要有Altera、Xilinx和Lattice三大生产厂家,不同厂家生产的芯片所使用的开发工具也不同,本文主要介绍了Altera的FPGA/CPLD开发工具Quartus II 在进行FPGA设计时的使用方法。

FPGA开发入门教程

Altera FPGA开发入门教程目录目录第一章 Altera FPGA 开发流程概述 (1)1.1 你需要准备的 (1)1.2 Altera FPGA 基本开发流程 (1)第二章 QuartusII 软件安装教程 (4)第三章 完成第一个FPGA设计 (20)3.1 启动和建立QuartusII工程 (20)3.2 编辑我们的设计文件 (27)3.3 综合、布局布线 (30)3.4 引脚约束 (34)3.5 再次综合、布局布线 (37)第四章 配置FPGA (38)4.1 JTAG配置 (38)4.2 JIC烧写 (42)第一章Altera FPGA 开发流程概述本章介绍Altera FPGA的最基本最简单的开发流程,目的在于让您更直观了解FPGA开发设计过程,最快上手FPGA开发,最快找到感觉:-)1.1你需要准备的●兴趣无需多言,兴趣是最好的老师!●基本电路知识学习FPGA最好能懂一些模拟电路和数字电路的基础知识,比如知道什么是高电平、低电平、逻辑门、触发器、电阻电容、发光二极管等。

只需基本概念即可,不要求你是专家。

当然,如果你有单片机之类的开发经验,那会更好!●Verilog语言是的,我们用Verilog进行FPGA设计。

因为近年来,Verilog的使用率已经远远超过VHDL。

你不需要太精通Verilog的语法,但是你需要用硬件的思维来学习和使用Verilog。

在接下来的FPGA学习中,我们会反复强调这一点,以便带给你更深的体会。

●硬件平台纸上得来终觉浅。

一块优秀而又易用的入门级FPGA开发板,会祝您一臂之力!1.2A ltera FPGA 基本开发流程图1- 1展示了Altera FPGA的基本开发流程。

12图1- 1 Altera FPGA 基本开发流程这个流程可能是你看过类似教程中最简单的流程。

是的,为了让学者能直观了解FPGA 设计流程、快速入门,我们简化了一些东西,但它已经基本完整了。

FPGA 开发板用户手册

FPGA_Cyclone_I_EP1C3 核心板一、FPGA_Cyclone_EP1C3 核心板特点:1.系统采用双层PCB板设计,高密度走线,完善的电源和时钟设计,性能稳定可靠、结构紧凑美观。

支持FPGA开发,提供引脚信息和预留PLL资源,支持扩展设计;2.该核心板适合于快速产品原型开发、学生各种电子设计大赛、学习FPGA设计技术等,亦可用于系统设计前期快速评估设计方案;3.例程模块化设计,简单明了,上手容易。

亦可作为以后系统的模块选用,加快项目系统搭建速度,实用性强;4.可持续性学习。

该FPGA开发板中FPGA的所有I/O口全部引出来,均可用于扩展。

用户可以根据自己的需要,设计实际电路,然后通过这些I/O连接到FPGA上,完成所需功能;5.性价比高,针对于学生用户定价,让更多的学生加入学习FPGA的行列。

二、FPGA_Cyclone_EP1C3 核心板配置:1. FPGA芯片:EP1C3T144C8 含2,910 Les;59,904bits(13个4Kbit存储块);1 PLL;104 I/O口2. 配置芯片:EPCS1 FPGA串行配置芯片含1 M bit Flash3. I2C存储器电路:24LC16B 16K bit(8 Blocks×256×8 Bit)4. SPI存储器电路:93LC46B 1K bit(64×16 Bit)5. 有源晶振:50 MHz6. 电源芯片:LM1117-3.3V、LM1117-1.5V7. AS、JTAG调试接口8. 核心板尺寸:100mm×79mm套件包括:1. 一块已测试好的FPGA_Cyclone_EP1C3 核心板2. 配套光盘一张(模块例程,PDF格式原理图,相关技术文档,数据手册)可选配 ByteBlaster II 下载线Periphery_For_FPGA外设板Periphery_For_FPGA外设板特点:1. 该外设板是基于FPGA的硬件描述语言和软内核嵌入式系统的SOPC开发平台。

FPGA开发板使用说明书-20页精选文档

目录第一章综述 (1)第二章系统模块 (2)第三章软件的介绍 (10)第四章USB 电缆的安装与使用 (15)第一章综述THSOPC-3型FPGA开发板是根据现代电子发展的方向,集EDA和SOPC系统开发为一体的综合性实验开发板,除了满足高校专、本科生和研究生的SOPC教学实验开发之外,也是电子设计和电子项目开发的理想工具。

一、实用范围:●自主创新应用开发;●单片机与FPGA联合开发;●IC设计硬件仿真;●科研项目硬件验证与开发;●高速高档自主知识产权电子产品开发;●毕业设计平台;●研究生课题开发;●电子设计竞赛培训;●现代DSP开发应用;●针对各类CPU IP核的片上系统开发;●DSP Biulder系统设计。

二、硬件配置:THSOPC-3型FPGA开发板基于Altera Cyclone II 器件的嵌入式系统开发提供了一个很好的硬件平台,它可以为开发人员提供以下资源:●支持+5V 电源适配器直接输入或者USB接口供电,5V、3.3V、1.2V混合电压源;●FPGACycloneII FPGA EP2C8,40万门,2个锁相环;●isp单片机AT89S8253。

isp单片机AT89S8253及开发编程工具,MCS51兼容,12KB isp可编程Flash ROM,2KB ispEEPROM,都是10万次烧写周期;2.7-5.5V工作电压;0-24MHz工作时钟;可编程看门狗;增强型SPI串口,9个中断源等。

此单片机可与FPGA联合开发,十分符合实现当今电子设计竞赛项目的功能与指标实现;●EPM3032 CPLD;● 4 Mbits 的EPCS4 配置芯片;●512KB高速SRAM;●20MHz 高精度时钟源(可倍频到300MHz);● 4 个用户自定义按键;●8 个用户自定义开关;●8 个用户自定义LED;● 2 个七段码LED;●标准AS 编程接口和JTAG调试接口;●两个标准2.54mm扩展接口,供用户自由扩展;●RS-232 DB9串行接口;●PS/2键盘接口;●VGA接口;●4X4键盘;●液晶显示屏20字X4行;●USB-Blaster编程器,可对FPGA通过JTAG口编程、调试、测试;单片机编程ByterBlasreMV 编程器;●光盘:配套子程序库、资料、编程软件、实验指导书。

第六章Altera编程与配置

PS:单片机软件方式配置

单片机产生配置时序、读 取EPROM中的配置数据

EPROM中 放置多个不 同功能的配 置文件

对FPGA进行配置

PS:使用下载电缆配置

FLEX、ACEX、 APEX系列FPGA 配置电路

对FPGA配置

注意: 1、不要忘了将多片配 置 控制信号nCE 引 脚接地! 2、作为PS配置模式, 不要忘了将配置模式 控制信号脚MSEL1和 MSEL0都接地!

FPP:使用增强型配置器件

被动并行同步( PPS)

只有较老的器件支持这种模式,如APEX20K、 Mercury、ACEX1K和FLEX10K。可由智能主机(如 微处理器和CPLD)来配置。在做PPS配置时, FPGA配置数据从存储器中读出,写入到FPGA的 DATA[7:0]输入接口上。在第一个DCLK时钟信号的 上升沿处,将一个字节的数据锁存到FPGA中,然后 由随后的8个DCLK时钟的下降沿将该字节数据一位 一位移到FPGA中。

FPGA的配置过程

在FPGA的配置之前,首先要借助于FPGA 开发系统,按某种文件格式要求描述设计系统,编译 仿真通过后,将描述文件转换成FPGA芯片的配置数 据文件。选择一种FPGA的配置模式,将配置数据装 载到FPGA芯片内部的可配置存储器( SRAM单 元),FPGA芯片才会成为满足要求的芯片系统。 FPGA的配置流程包括复位、芯片配置芯片初始化、 等几个过程。

通过配置电路后 与PC机的并行 接口相接

10针标准 配置/下载接口

主系统通用 10针标准 配置/下载接口

PIN1目标板10针标准 源自置接口OTP配置器件插座PS:使用专用配置芯片配置

PS:ASIC/CPLD硬件高速配置方案

缺点: 1、电路面积比较大

21EDA-Altera-FPGA开发板使用入门

21EDA-Altera-FPGA开发板使用入门在自己做这个实验的时候,需要确认自己的开发软件是否已经安装好了,确认自己的下载器是否已经可以使用了。

如果还不熟悉的,可以看看下面两个文件QuartusII 9.0破解全过程.pdf下载器的安装.pdf实验要求:PC电脑一台,配置越高越好。

开发软件:QuartusII9.0SP2开发板型号:A-C8V4实验结果:学习Altera公司的FPGA开发软件QuartusII入门使用。

首先打开QuartusII9.0SP2的开发软件。

你有三种方法可以打开。

第一:如下图,桌面上有快捷图标。

双击就可以了。

第二:如下图,在开始菜单里面可以找到。

第三:如下图,在开始菜单里面也可以找到。

如下图:打开QII软件了如下图:我们可以把这个关闭了。

如下图:新建一个工程File->New Project Wizrd….如下图:点击Next如下图:这里我们要设置工程路径,工程名和顶层名。

点第一排三个点点那里如下图:我们把工程路径放在J盘下面FPGA_TEST文件夹;J:\FPGA_TEST设置好了,点击Next如下图:直接点击Next如下图:这里我们需要对CPU进行设置,也就是设置成和我们开发板对应的芯片。

Family 要选择Cyclone II如下图:如下图:选择芯片的封装,PQFP如下图:如下图:选择芯片的管教数目,我们这里是208个脚如下图:如下图:选择速度等级,我们这里选择8如下图:如下图:选择我们最后设置好的芯片。

然后点击Next如下图:然后点击Next如下图:然后点击Finish如下图:如下图:然后点击Next如下图:点击File->New 新建一个我们用来编写程序的窗口。

如下图:如果你使用Verilog语言,就选择Verilog HDL File 然后点击OK如下图:如果你使用VHDL语言,就选择VHDL File 然后点击OK 我们这里用VHDL作为演示如下图:会在右边出现程序编写的空白窗口。

第二章 ALTERA可编程逻辑器件

第二章 ALTERA 可编程逻辑器件

本章主要讲述了 ALTERA 公司 PLD 芯片的特点和性能,初学者可以跳过,等你需 要考虑设计的效率和可靠性时,需要仔细了解,并且那时候你最好参考相关的英

文手册原文。

ALTERA 在 20 世界 90 年代以后发展很快,是最大的可编程逻辑器件供应商 之一,总部设在位于硅谷圣侯塞,其主要产品有:属于 CPLD 的 MAX3000/5000/7000/9000 和 CLASSIC 系列;属于 FPGA 的 FLEX6K/8K/10K、 APEX20K/ACE1K/APEXII/MERCURY/EXCALICUR 和 STRATIC 系列。ALTERA 公司的开 发软件 MAX+PLUSII 被普遍认为是最优秀的 PLD 开发平台之一,适合开发中小规 模 PLD/FPGA;软件 QuartusII 是新一代 FPGA/PLD 开发软件,适合新器件和大规 模 FPGA 的开发,将逐步取代 MaxplusII。目前 MAXPLUS 软件的资料比较多,但 QUARTUS 软件讲的很少,我们的教程上两种都讲了,但我们强烈建议使用 QUARTUS,我们的例子也基本以 QUARTUS 为主,为什么呢?因为现在单位开发项目 基本都用 QUARTUS 软件,你直接学习 QUARTUS 以后就可以直接使用上了;另外 QUARTUS 性能远比 MAXPLUS 好。

5v

3.3v

3.3v

2.5v

宏单元 备注

EPM7032S EPM7032AE EPM3032A EPM7032B 32

EPM7064S EPM7064AE EPM3064A EPM7064B 64

EPM7128S EPM7128AE EPM3128A EPM7128B 128

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

ALTERA FPGA EP2C5Q 开发板用户手册上海亿家网络有限公司版权所有 © 上海亿家网络有限公司 2013。

保留一切权利。

非经上海亿家网络有限公司书面同意,任何单位和个人不得擅自摘抄、复制本手册内容的部分或全部,并不得以任何形式传播。

本手册中描述的产品中,可能包含上海亿家网络有限公司及其可能存在的许可人享有版权的软件,除非获得相关权利人的许可,否则,任何人不能以任何形式对前述软件进行复制、分发、修改、摘录、反编译、反汇编、解密、反向工程、转让、分许可以及其他侵犯软件版权的行为。

本手册描述了ALTERA FPGA EP2C5Q开发板的硬件资源、安装、使用和设计原理,用以指导开发板使用。

本手册对应开发板的主要用户为高校学生、电子爱好者、科研单位、企事业单位的开发设计人员,适合于产品原型的快速开发、学生参加各种电子设计大赛、学习FPGA技术入门、课程设计及毕业设计等,亦可用于系统设计前期快速评估,特别适合于FPGA、NIOSII、SOPC 快速入门和产品开发及验证。

1 安全警告和注意事项 (5)2开发板主要器件及硬件资源 (7)2.1 主要器件 (7)2.2 硬件资源 (7)2.3 PCB和尺寸 (9)3 开发板的安装和使用 (10)3.1 开发板安装 (10)3.2 开发板的使用 (11)4开发板设计详细说明 (17)4.1 电源电路 (17)4.2 时钟电路 (17)4.3 复位电路 (18)4.4 JTAG接口电路 (18)4.5 AS接口电路 (19)4.6 LED电路 (19)4.7 存储器SDRAM电路 (19)4.8外部扩展IO (21)5技术支持与保修 (23)5.1关于技术支持 (23)5.2 关于产品保修 (23)附录常见问题解答 (24)1安全警告和注意事项为正确、安全地使用本开发板,请您在使用前仔细阅读本安全警告和注意事项,并在使用时严格遵循。

说明如无特别说明,本节描述的“开发板”包含开发板本身及其配件。

基本要求z请勿自行拆卸或焊接开发板,开发板发生故障时请联系本公司。

z未经授权,任何单位和个人不得对开发板进行结构、安全和性能设计等方面的改动。

使用要求z插拔线缆前,请先停止使用开发板,并断开电源。

z若有异物或液体进入开发板,请立刻停止使用并断开电源,拔出连接在开发板上的所有线缆。

z如有异常现象出现,如设备冒烟、有异味等,请立刻停止使用并断开电源。

z长时间不使用时,请断开电源。

静电安全与防护人体可以产生几千甚至上万伏的静电,特别是在冬天或干燥的情况下,静电更严重。

静电有可能损坏开发板上的芯片,所以在接触开发板前要做好相应的防护。

对于个人用户,用手摸下自来水管的金属部分,可以消除静电。

不要用手直接接触开发板上的芯片。

移动开发板时,用防静电袋托着。

下载线的插拔安全z插拔下载线时,要注意扁平电缆的方向,严禁接错,以免烧坏逻辑芯片或下载线。

z严禁带电拔插JTAG下载线!带电操作容易对逻辑芯片的内部配置电路造成致命损坏!这与平时大家插拔电脑主板的板卡差不多。

外接电源使用开发板支持DC 5V电源输入。

使用DC电源接口时,要确认您的电源适配器输出为5V,且内正外负,以免因电压不同或极性接反造成开发板损坏!开发板也支持USB电源供电。

使用标准手机充电器和Mini USB线可以给开发板供电。

给开发板供电时,可使用DC接口,也可以使用Mini USB接口,任意使用其中一个即可。

开发板与接口板连接开发板与接口板是通过3排接插口相连的。

开发板上是排针,接口板上是排座。

如果您不单独使用本板,请不要将本板拔下。

尽量避免频繁插拔。

即使要插拔时,请尽量小心谨慎。

取下本板时,建议一手固定接口板,另一手拿住本板四周,用适度的力取下,不时调整四周用力力度。

安装本板时,注意本板方向,保证插座和插针一一对应,确认无误后,方可用力按下安装,并不时调整四周用力力度。

2开发板主要器件及硬件资源2.1 主要器件开发板的核心芯片使用ALTREA Cyclone Ⅱ系列FPGA EP2C5Q208。

该芯片资源丰富,价格适中,非常适合 FPGA 初中级学习使用,同时兼容 EP2C8Q208C8N。

芯片提供的资源如图所示。

对于FPGA,逻辑芯片的逻辑门数和RAM bit数是重要的参考指标,IO数就没那么重要了,其他的可关注PLL、serdes等。

2.2 硬件资源z主芯片使用ALTERA公司高性价比FPGA:CycloneII系列EP2C5Q208C8N;z50MHz有源晶振,提供系统工作主时钟;z板载EPCS4N或EPCS16N串行配置芯片,可以存储FPGA逻辑,也可以存储 NIOSⅡ程序。

z板载64Mbit的SDRAM(HY57V64162),可胜任NIOSII设计;z使用大功率LDO电源管理芯片LM1085-3.3V,最大支持3A的3.3V电压输出;z使用AMS1117-1.2V稳压芯片,提供FPGA内核电压;z IN5819高速肖特基二极管,防电源反接设计;z1个自锁电源开关;z提供5V直流电源插座,可使用电源适配器供电;z提供MINI USB插座,可使用手机标准充电器供电;z1个红色高亮LED,用以电源指示;z2个蓝色高亮LED,可做LED闪烁实验;z1个复位键,也可做为用户输入按键;z提供重配置按键,用作FPGA的逻辑重配。

z支持JTAG接口;z支持AS接口;z精心的去耦设计,采用大量去耦电容;z精心设计分配IO口,使用3个扩展接口插座,通用2.54mm间距; 电路板实物如图所示。

2.3 PCB和尺寸PCB尺寸:3346.457*2952.756 (单位:mil) J1.1位置:(2219.685,-77.953); (单位:mil) J2.1位置:(77.953,-319.685); (单位:mil) J3.1位置:(2461.417,-2219.685); (单位:mil)3开发板的安装和使用本开发板最小包装为:z1块开发板z1条Mini USB线z4个铜柱和螺丝z包装清单3.1 开发板安装在您收到开发板后,请您z将铜柱安装到开发板上的安装孔中;z将下载线连接到开发板上(注意方向:扁平电缆红色的一边连接电路板插件1脚);z将Mini USB连接到开发板,以便给单板供电;z将安装完成的开发板平整放置桌面上;z在电脑上安装所需要的软件,如综合布线软件Quartus/ISE/ispLEVER、仿真软件Modelsim、文本编辑软件UltraEdit、代码检查软件Nlint等。

开发板连接示意图,如下图所示。

以下是下载线与开发板连接细节图(严禁左右或上下错位)。

注意连接下载线时,请注意下载线的方向,不要接错,以免烧坏开发板!以下是与接口板连接后的实物图,接口板上插了一个1602A液晶屏。

3.2 开发板的使用开发板安装完成,确认连接正常后,就可以对开发板上电。

在开发板使用之前,先介绍一下逻辑开发流程,这将有助于您清晰的了解您在逻辑开发中要做的工作。

这也是所有逻辑开发的流程,适用于CPLD和FPGA。

3.2.1逻辑开发流程简介进行逻辑开发,包括硬件设计和软件设计两部分。

硬件包括逻辑芯片电路、JTAG、时钟、复位、存储器、输入输出接口电路以及其他接口。

这部分,我们已经帮您完成了。

软件部分即相应的HDL程序,这部分需要根据您的要求,由您自行设计。

在这里,我们提供了部分例程,供您参考。

逻辑设计流程就是利用EDA开发软件和编程工具对逻辑芯片进行开发的过程。

典型 逻辑的开发流程一般如下图所示,包括功能定义/器件选型、设计输入、功能仿真、综合优化、综合后仿真、实现、布线后仿真、板级仿真、芯片编程与调试等主要步骤。

功能定义:定义您要实现的功能,如将开发板上的2个LED闪烁;设计输入:用硬件描述语言(HDL)将您的功能描述出来,即在文本编辑软件UltraEdit 中使用HDL语言描述。

不建议使用原理图方式,因为原理图方式效率低,不易维护,不利于模块构造和重用,更主要的缺点是可移植性差。

一个LED闪烁的设计描述如下所示,LED每50000000个clk闪烁一次。

功能仿真:也称为前仿真,在编译之前对用户所设计的电路进行逻辑功能验证。

一般使用Modelsim或Questa 进行仿真。

一个LED闪烁的仿真波形如下。

可以看出led_flash的值每隔一段时间就为1,点亮LED。

综合优化:指将设计输入编译成由与门、或门、非门、RAM、触发器等基本逻辑单元组成的逻辑连接网表,而并非真实的门级电路。

真实具体的门级电路需要利用 FPGA制造商软件的布局布线功能,根据综合后生成的标准门级结构网表来产生。

对于ALTERA公司的器件,将设计导入到Quartus中,使用Quartus软件进行综合。

综合后仿真:检查综合结果是否和原设计一致。

在仿真时,把综合生成的标准延时文件反标注到综合仿真模型中去,可估计门延时带来的影响。

这个过程一般不做。

布局布线与实现:布局布线可理解为利用FPGA制造商软件把逻辑映射到目标器件结构的资源中,决定逻辑的最佳布局,选择逻辑与输入输出功能链接的布线通道进行连线,并产生相应文件 ( 如配置文件与相关报告 ),实现是将综合生成的逻辑网表配置到具体的逻辑芯片上。

对于ALTERA公司的器件,将设计导入到Quartus中,使用Quartus软件进行布局布线,并生成配置文件。

一个LED闪烁进行布局布线的例子,如下图所示。

时序仿真:也称为后仿真,是指将布局布线的延时信息反标注到设计网表中来检测有无时序违规 ( 即不满足时序约束条件或器件固有的时序规则,如建立时间、保持时间等 ) 现象。

时序仿真包含的延迟信息最全,也最精确,能较好地反映芯片的实际工作情况。

这个过程一般也不做。

板级仿真:主要应用于高速电路设计中,对高速系统的信号完整性、电磁干扰等特征进行分析,一般都以第三方工具进行仿真和验证。

这个过程一般也不做。

芯片编程和调试:芯片编程指将布局布线和实现后生成的bit文件下载到FPGA芯片或配置芯片中,实现定义的功能,调试指利用FPGA 芯片内嵌的在线逻辑分析仪 (如XILINX ISE 中的ChipScope、ALTERA Quartus中的 SignalTap、LATTICE没研究过) 来采样波形,并进行分析的过程。

3.2.2配置FPGA逻辑本开发板支持JTAG模式和AS模式。

在调试阶段,多使用JTAG模式。

下面分别对这2种模式分别进行描述。

a 通过JTAG模式配置FPGA对应的下载文件是SOF文件,下载速度快。

通过JTAG接口,将逻辑下载到FPGA内的SRAM中。

但掉电后会SRAM中的内容会丢失,上电后要重新下载。

学习和调试时,推荐使用JTAG模式,调试成功后再通过AS模式将逻辑下载到配置芯片中。