基于VerilogHDL的万年历(20210311075245)

【优秀WORD论文】基于FPGA的全功能万年历电子钟的设计

基于FPGA的全功能万年历电子钟的设计提要本文主要介绍了基于FPGA的万年历电子钟的设计方案,从而介绍了可编程逻辑器件的发展及应用。

基于FPGA的电子钟的设计与实现介绍了基于FPGA芯片的系统设计,并对系统的软硬件构成、FPGA内部逻辑设计工作原理等进行了详细说明。

论文第一部分对FPGA进行概述,讲述了可编程逻辑器件的发展与应用及论文题目的意义、目的和内容编排;第二部分:叙述了系统设计方案,介绍了FPGA应用的特点和电子钟的方案概述及实现语言和调试平台MAX+plusⅡ开发工具;第三部分:叙述了基于FPGA的电子钟系统的设计的硬件设计和软件设计;第四部分:对系统实现的外围电路进行概述。

第五部分:再次说明本设计的系统方案和得到的结论。

目录第一章序论 (1)1.1研究目的和意义: (1)1.2可编程逻辑器件的发展与应用: (1)1.2.1可编程逻辑单元CLB (3)1.2.2输入/输出模块IOB (3)1.2.3可编程内部连线PI (4)1.2.4 FPGA芯片的特点 (4)1.3FPGA国内外的发展状况及应用 (5)1.4本课题所能实现的功能: (8)第二章总体方案的设计 (9)2.1万年历电子钟的设计原理: (9)2.2FPGA的设计方法 (11)2.2.1 FPGA的器件设计流程 (11)2.2.2 MAX+plusⅡ开发工具 (13)2.2.3 VHDL语言 (17)2.3系统设计方案 (18)第三章系统的硬件设计与实现 (19)3.1功能模块设计 (19)3.2系统功能实现 (21)3.2.1底层元件设计 (22)3.2.2顶层元件设计 (32)3.3芯片的选择 (41)第四章设计应用电路 (45)4.1整体电路 (45)4.2电源电路 (46)4.3键盘部分 (49)4.4主动配置电路 (53)第五章总结 (61)5.1概述: (61)5.2设计方案: (62)参考文献 (64)致谢 (67)摘要 (I)ABSTRACT (II)第一章序论1.1研究目的和意义:通过对FPGA的了解,我们要应用FPGA来设计全功能万年历的设计,主要实现电子钟的所有功能,万年历是一种应用非常广泛的日常计时工具,具有时分秒计时功能,还有日历、年历功能,涉及计数、显示、参数输入技术,能够实时显示年、月、日和时间,并具有校准和闹铃等功能。

毕业论文基于veriloghdl万年历说明书

基于Verilog HDL的万年历设计与总结报告题目名称:基于Verilog HDL的万年历研究设计报告人:___________________________________________ 院系/年级/专业:________________________指导教师:________________________________________ 制作日期:_____________________________基于Verilog HDL 的万年历摘要基于Verilog HDL的万年历设计,主要完成的任务是使用Verilog语言,在Quartus2 上完成电路设计,程序开发模拟,基于功能是能够显示/ 修改年月日时分秒。

电路设计模块:分频、控制、时间显示调整、时分秒、年月日、显示控制、译码器。

各个模块完成不同的任务,合在一起就构成了万年历电路设计。

软件模拟直接在Quartus2 上进行。

随着科学技术的发展,时间观念越来越重,但是老式的钟表以及日历等时间显示工具已不合时宜。

对此,数字钟表的设计有了用武之地。

基于Verilog 的万年历设计,采用软件开发模拟,开发成本低,而且在功能设计上有了很大的灵活度。

同时,该设计的精度远远超过钟表,并且不需要维修。

综上所述,本设计具有设计方便、功能多样、电路简洁、成本低廉等优点。

符合社会发展趋势,前景广阔。

关键词:万年历,Verilog HDL ,Quartus2Based on the design of the calendar Verilog HDL circuitAbstractThe calendar based on FPGA design, the main task is to use eVrilog language, in the Quartus2 complete circuit design module is divided into several modules: point frequency, control and time display adjustment, arc, date, display, when control, decoder. Each module complete different tasks, together they form a calendar system circuit design. Software simulation on directly in Quartus2.With the development of technology and science, the concept of time is more and more heavey, but old-fashioned clock and calendar etc time display tools are not very good.Key words: Calendar,Verilog HDL ,Quartus2目录摘要......................................................... ..1Abstract .......................................................................................................... .2第一章万年历发展介绍及Verilog HDL 简介.. (3)1.1万年历的发展.................................................. ..31.2Verilog HDL 简介 (4)第二章设计原理................................................ ..52.1组成模块...................................................... ..62.2系统设计图.................................................... ..7第三章各功能模块介绍 (8)第四章模拟仿真 (11)4.1年月日仿真 (12)4.2时分秒仿真 (13)总结结论 (14)参考文献 (15)第一章万年历的发展介绍及Verilog HDL简介1.1万年历的发展钟表、日历等的数字化大大方便了我们的日常生活,同时大大扩展了其功能,而这些功能的实现,均以钟表的数字化为基础的。

vhdl万年历

FPGA——VHDL万年历LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_UNSIGNED.ALL;ENTITY TIMER ISPORT(CLK,RES,XUAN,JIA_SEC1,JIA_SEC2,JIA_MIN1,JIA_MIN2,JIA_HOUR1,JIA_HOUR2:IN STD_LOGIC;HOUR2,HOUR1,MIN2,MIN1,SEC2,SEC1:OUT STD_LOGIC_VECTOR(3 DOWNTO 0);COUT:OUT STD_LOGIC);END;ARCHITECTURE ONE OF TIMER ISSIGNAL HOUR11,HOUR22,SEC11,SEC22,MIN11,MIN22:STD_LOGIC_VECTOR(3 DOWNTO 0);BEGINPROCESS(CLK,RES,XUAN,JIA_SEC1,JIA_SEC2,JIA_MIN1,JIA_MIN2,JIA_HOUR1,JIA_HOUR2)BEGINIF(XUAN='0')THEN----------------------自动计时IF(CLK'EVENT AND CLK='1')THENIF(RES='0')THENIF(HOUR22<"0010")THENIF(HOUR11<"1001")THEN ------<19 HOURSIF(MIN22<"0101")THENIF(MIN11<"1001")THENIF(SEC22<"0101")THENIF(SEC11<"1001")THENSEC11<=SEC11+1;ELSE SEC11<="0000";SEC22<=SEC22+1;END IF;ELSIF(SEC22="0101") THENIF(SEC11<"1001")THENSEC11<=SEC11+1;ELSE SEC11<="0000";SEC22<="0000";MIN11<=MIN11+1;END IF;END IF;ELSIF(MIN11="1001")THENIF(SEC22<"0101")THENIF(SEC11<"1001")THENSEC11<=SEC11+1;ELSE SEC11<="0000";SEC22<=SEC22+1;END IF;ELSIF(SEC22="0101") THENIF(SEC11<"1001")THENSEC11<=SEC11+1;ELSE SEC11<="0000";SEC22<="0000";MIN11<="0000";MIN22<=MIN22+1;END IF;END IF;ELSIF(MIN22="0101")THENIF(MIN11<"1001")THENIF(SEC22<"0101")THENIF(SEC11<"1001")THENSEC11<=SEC11+1;ELSE SEC11<="0000";SEC22<=SEC22+1;END IF;ELSIF(SEC22="0101") THENIF(SEC11<"1001")THENSEC11<=SEC11+1;ELSE SEC11<="0000";SEC22<="0000";MIN11<=MIN11+1;END IF;END IF;ELSIF(MIN11="1001")THENIF(SEC22<"0101")THENIF(SEC11<"1001")THENSEC11<=SEC11+1;ELSE SEC11<="0000";SEC22<=SEC22+1;END IF;ELSIF(SEC22="0101") THENIF(SEC11<"1001")THENSEC11<=SEC11+1;ELSE SEC11<="0000";SEC22<="0000";MIN11<="0000";MIN22<="0000";HOU R11<=HOUR11+1;END IF;END IF;END IF;END IF;ELSIF(HOUR11="1001")THENIF(MIN22<"0101")THENIF(MIN11<"1001")THENIF(SEC22<"0101")THENIF(SEC11<"1001")THENSEC11<=SEC11+1;ELSE SEC11<="0000";SEC22<=SEC22+1;END IF;ELSIF(SEC22="0101") THENIF(SEC11<"1001")THENSEC11<=SEC11+1;ELSE SEC11<="0000";SEC22<="0000";MIN11<=MIN11+1;END IF;ELSIF(MIN11="1001")THENIF(SEC22<"0101")THENIF(SEC11<"1001")THENSEC11<=SEC11+1;ELSE SEC11<="0000";SEC22<=SEC22+1;END IF;ELSIF(SEC22="0101") THENIF(SEC11<"1001")THENSEC11<=SEC11+1;ELSE SEC11<="0000";SEC22<="0000";MIN11<="0000";MIN22<=MIN22+1;END IF;END IF;END IF;ELSIF(MIN22="0101")THENIF(MIN11<"1001")THENIF(SEC22<"0101")THENIF(SEC11<"1001")THENSEC11<=SEC11+1;ELSE SEC11<="0000";SEC22<=SEC22+1;END IF;ELSIF(SEC22="0101") THENIF(SEC11<"1001")THENSEC11<=SEC11+1;ELSE SEC11<="0000";SEC22<="0000";MIN11<=MIN11+1;END IF;END IF;ELSIF(MIN11="1001")THENIF(SEC22<"0101")THENIF(SEC11<"1001")THENSEC11<=SEC11+1;ELSE SEC11<="0000";SEC22<=SEC22+1;END IF;ELSIF(SEC22="0101") THENIF(SEC11<"1001")THENSEC11<=SEC11+1;ELSE SEC11<="0000";SEC22<="0000";MIN11<="0000";MIN22<="0000";HOU R11<="0000";HOUR22<=HOUR22+1;END IF;END IF;END IF;END IF;END IF;ELSIF(HOUR22="0010")THEN -----20--23 hoursIF(MIN22<"0101")THENIF(MIN11<"1001")THENIF(SEC22<"0101")THENIF(SEC11<"1001")THENSEC11<=SEC11+1;ELSE SEC11<="0000";SEC22<=SEC22+1;END IF;ELSIF(SEC22="0101") THENIF(SEC11<"1001")THENSEC11<=SEC11+1;ELSE SEC11<="0000";SEC22<="0000";MIN11<=MIN11+1;END IF;END IF;ELSIF(MIN11="1001")THENIF(SEC22<"0101")THENIF(SEC11<"1001")THENSEC11<=SEC11+1;ELSE SEC11<="0000";SEC22<=SEC22+1;END IF;ELSIF(SEC22="0101") THENIF(SEC11<"1001")THENSEC11<=SEC11+1;ELSE SEC11<="0000";SEC22<="0000";MIN11<="0000";MIN22<=MIN22+1;END IF;END IF;END IF;ELSIF(MIN22="0101")THENIF(MIN11<"1001")THENIF(SEC22<"0101")THENIF(SEC11<"1001")THENSEC11<=SEC11+1;ELSE SEC11<="0000";SEC22<=SEC22+1;END IF;ELSIF(SEC22="0101") THENIF(SEC11<"1001")THENSEC11<=SEC11+1;ELSE SEC11<="0000";SEC22<="0000";MIN11<=MIN11+1;END IF;END IF;ELSIF(MIN11="1001")THENIF(SEC22<"0101")THENIF(SEC11<"1001")THENELSE SEC11<="0000";SEC22<=SEC22+1;END IF;ELSIF(SEC22="0101") THENIF(SEC11<"1001")THENSEC11<=SEC11+1;ELSE SEC11<="0000";SEC22<="0000";MIN11<="0000";MIN22<="0000";HOUR11<=HOUR11+1;END IF;END IF;END IF;END IF;ELSIF(HOUR11="0100")THEN------------------------------------20--23HOURSIF(MIN22<"0101")THENIF(MIN11<"1001")THENIF(SEC22<"0101")THENIF(SEC11<"1001")THENSEC11<=SEC11+1;ELSE SEC11<="0000";SEC22<=SEC22+1;END IF;ELSIF(SEC22="0101") THENIF(SEC11<"1001")THENSEC11<=SEC11+1;ELSE SEC11<="0000";SEC22<="0000";MIN11<=MIN11+1;END IF;END IF;ELSIF(MIN11="1001")THENIF(SEC22<"0101")THENIF(SEC11<"1001")THENSEC11<=SEC11+1;ELSE SEC11<="0000";SEC22<=SEC22+1;END IF;ELSIF(SEC22="0101") THENIF(SEC11<"1001")THENSEC11<=SEC11+1;ELSE SEC11<="0000";SEC22<="0000";MIN11<="0000";MIN22<=MIN22+1;END IF;END IF;END IF;ELSIF(MIN22="0101")THENIF(MIN11<"1001")THENIF(SEC22<"0101")THENIF(SEC11<"1001")THENELSE SEC11<="0000";SEC22<=SEC22+1;END IF;ELSIF(SEC22="0101") THENIF(SEC11<"1001")THENSEC11<=SEC11+1;ELSE SEC11<="0000";SEC22<="0000";MIN11<=MIN11+1;END IF;END IF;ELSIF(MIN11="1001")THENIF(SEC22<"0101")THENIF(SEC11<"1001")THENSEC11<=SEC11+1;ELSE SEC11<="0000";SEC22<=SEC22+1;END IF;ELSIF(SEC22="0101") THENIF(SEC11<"1001")THENSEC11<=SEC11+1;ELSE SEC11<="0000";SEC22<="0000";MIN11<="0000";MIN22<="0000";HOUR11<="0000";HOUR22<="0000";END IF;END IF;END IF;END IF;END IF;END IF;ELSE SEC11<="0000";SEC22<="0000";MIN11<="0000";MIN22<="0000";HOUR11<="0000";HOUR22<="0000";END IF;END IF;ELSE------------------------------------------进行手动调整IF(RES='0')THENIF(JIA_SEC1'EVENT AND JIA_SEC1='1')THEN------------------调整秒1IF(SEC11<"1001")THENSEC11<=SEC11+1;ELSE SEC11<="0000";END IF;END IF;IF(JIA_SEC2'EVENT AND JIA_SEC2='1')THEN------------------调整秒2IF(SEC22<"0101")THENSEC22<=SEC22+1;ELSE SEC22<="0000";END IF;END IF;IF(JIA_MIN1'EVENT AND JIA_MIN1='1')THEN------------------调整分1IF(MIN11<"1001")THENMIN11<=MIN11+1;ELSE MIN11<="0000";END IF;END IF;IF(JIA_MIN2'EVENT AND JIA_MIN2='1')THEN------------------调整分2IF(MIN22<"0101")THENMIN22<=MIN22+1;ELSE MIN22<="0000";END IF;END IF;IF(JIA_HOUR1'EVENT AND JIA_HOUR1='1')THEN----------------调整时1IF(HOUR11<"1001")THENHOUR11<=HOUR11+1;ELSE HOUR11<="0000";END IF;END IF;IF(JIA_HOUR2'EVENT AND JIA_HOUR2='1')THEN----------------调整时2IF(HOUR22<"0010")THENHOUR22<=HOUR22+1;ELSE HOUR22<="0000";END IF;END IF;ELSE SEC11<="0000";SEC22<="0000";MIN11<="0000";MIN22<="0000";HOUR11<="0000";HOUR22<="0000";END IF;END IF;END PROCESS;PROCESS(SEC11,SEC22,MIN11,MIN22)BEGINIF(MIN11="0000" AND MIN22="0000")THENIF(SEC11<"1010" AND SEC22<"0011")THENCOUT<='1';ELSE COUT<='0';END IF;ELSIF(MIN11="0000" AND MIN22="0011")THENIF(SEC11<"1010" AND SEC22<"0011")THENCOUT<='1';ELSE COUT<='0';END IF;ELSE COUT<='0';END IF;END PROCESS;HOUR2<=HOUR22;HOUR1<=HOUR11;SEC1<=SEC11;SEC2<=SEC22;MIN1<=MIN11;MIN2<=MIN22;END;。

FPGA万年历程序

modulealarmclock(clk_200Hz,EN,SW1,SW2,hour1,hour0,minute1,minute0,second1,second0,alarm,alar mclock_disp_select);output alarm;//闹钟时间到的提示信号输出output[5:0]alarmclock_disp_select;//闹钟设置中位选信号input EN;//闹钟的设置使能input SW1,SW2;input clk_200Hz;//设置中的闪烁显示的时钟input[3:0]hour1,hour0,minute1,minute0,second1,second0;//当前时间reg[5:0]alarmclock_disp_select;reg alarm;reg[3:0]hour_set1,hour_set0;//存放设置的小时reg[3:0]minute_set1,minute_set0;//存放设置的分reg[3:0]second_set1,second_set0;//存放设置的秒reg[2:0]disp_drive;//设置闹钟时间时,数码管显示的动态位选择(即显示当前位置)/*闹钟一直工作(与当前时间比较)*/alwaysbeginif((hour_set1==hour1)&&(hour_set0==hour0)&&(minute_set1==minute1)&&(minute_set0==mi nute0)&&(second_set1==second1)&&(second_set0==second0))alarm<=1'b1;elsealarm<=1'b0;end/*闹钟设置中,按SW1一次,将移位一次,闪烁显示当前设置位数字*/always@(posedge SW1)beginif(EN==1'b1)beginif(disp_drive!=3'b101)disp_drive<=disp_drive+3'b1;elsedisp_drive<=3'b000;endend/*当前位的闹钟数字设置,按SW2一次,数字增加1*/always@(posedge SW2)begincase(disp_drive)3'b000:beginif(hour_set1<4'b0010)hour_set1<=hour_set1+4'b1;elsehour_set1<=4'b0;end3'b001:beginif((hour_set1<4'b0010)&&(hour_set0<4'b1001))hour_set0<=hour_set0+4'b1;else if((hour_set1==4'b0010)&&(hour_set0<4'b0100))hour_set0<=hour_set0+4'b1;elsehour_set0<=4'b0;end3'b010:beginif(minute_set1<4'b0101)minute_set1<=minute_set1+4'b1;elseminute_set1<=4'b0;end3'b011:beginif(minute_set0<4'b1001)minute_set0<=minute_set0+4'b1;elseminute_set0<=4'b0;end3'b100:beginif(second_set1<4'b0101)second_set1<=second_set1+4'b1;elsesecond_set1<=4'b0;end3'b101:beginif(second_set0<4'b1001)second_set0<=second_set0+4'b1;elsesecond_set0<=4'b0;enddefault:beginendendcaseend/*闪烁显示*/always@(posedge clk_200Hz)begincase(disp_drive)3'b000:alarmclock_disp_select<=6'b100000;3'b001:alarmclock_disp_select<=6'b010000;3'b010:alarmclock_disp_select<=6'b001000;3'b011:alarmclock_disp_select<=6'b000100;3'b100:alarmclock_disp_select<=6'b000010;3'b101:alarmclock_disp_select<=6'b000001;default:alarmclock_disp_select<=6'b000000;endcaseendEndmodulemoduledisp_data_mux(Timepiece_EN,TimeSet_EN,Stopwatch_EN,time_disp_select,Alarmclock_EN,ala rmclock_disp_select,hour1,hour0,minute1,minute0,second1,second0,Date_EN,DateSet_EN,date_ disp_select,year3,year2,year1,year0,month1,month0,day1,day0,disp_select,disp_data);output[7:0]disp_select;output[6:0]disp_data;input Timepiece_EN;input TimeSet_EN;input Stopwatch_EN;input[5:0]time_disp_select;input Alarmclock_EN;input[5:0]alarmclock_disp_select;input[3:0]hour1,hour0,minute1,minute0,second1,second0;input Date_EN;input DateSet_EN;input[7:0]date_disp_select;input[3:0]year3,year2,year1,year0,month1,month0,day1,day0;reg[5:0]disp_select;reg[6:0]disp_data;reg[3:0]Data;always@(Timepiece_EN,TimeSet_EN,Stopwatch_EN,time_disp_select,Alarmclock_EN,alarmclo ck_disp_select,hour1,hour0,minute1,minute0,second1,second0,Date_EN,DateSet_EN,date_disp_s elect,month1,month0,day1,day0,disp_select)begin/*时钟、秒表显示*/if((Timepiece_EN||TimeSet_EN||Stopwatch_EN)==1'b1)begindisp_select<=time_disp_select;case(time_disp_select)6'b100000:Data<=hour1;6'b010000:Data<=hour0;6'b001000:Data<=minute1;6'b000100:Data<=minute0;6'b000010:Data<=second1;6'b000001:Data<=second0;default:Data<=4'b0;endcaseend/*闹钟设置显示*/else if(Alarmclock_EN==1'b1)begindisp_select<=alarmclock_disp_select;case(alarmclock_disp_select)6'b100000:Data<=hour1;6'b010000:Data<=hour0;6'b001000:Data<=minute1;6'b000100:Data<=minute0;6'b000010:Data<=second1;6'b000001:Data<=second0;default:Data<=4'b0;endcaseend/*日期以及日期设置显示*/else if((Date_EN||DateSet_EN)==1'b1)begindisp_select<=date_disp_select;case(date_disp_select)8'b10000000:Data<=year3;8'b01000000:Data<=year2;8'b00100000:Data<=year1;8'b00010000:Data<=year0;8'b00001000:Data<=month1;8'b00000100:Data<=month0;8'b00000010:Data<=day1;8'b00000001:Data<=day0;default:Data<=4'b0;endcaseend/*显示数据译码*/case(Data)4'b0000:disp_data<=8'hc0;4'b0001:disp_data<=8'hf9;4'b0010:disp_data<=8'ha4;4'b0011:disp_data<=8'hb0;4'b0100:disp_data<=8'h99;4'b0101:disp_data<=8'h92;4'b0110:disp_data<=8'h82;4'b0111:disp_data<=8'hf8;4'b1000:disp_data<=8'h80;4'b1001:disp_data<=8'h90;default:disp_data<=8'h0;endcaseendendmodulemoduledate_disp_select(clk_1kHz,clk_200Hz,Date_EN,DateSet_EN,DateSet_disp_drive,Date_disp_sele ct);output[7:0]Date_disp_select;input clk_1kHz;input clk_200Hz;input Date_EN;input DateSet_EN;input[3:0]DateSet_disp_drive;reg[7:0]Date_disp_select;reg[3:0]auto_disp_drive;reg clk;reg[3:0]disp_drive;always@(posedge clk_1kHz)/*实现自动运行模式中的动态显示“位选的驱动”*/ beginif(auto_disp_drive<4'b0111)auto_disp_drive<=auto_disp_drive+4'b1;elseauto_disp_drive<=4'b0;endalways@(Date_EN or DateSet_EN)/*实现自动运行模式中时间动态显示位选驱动与时间设置中的时间动态显示位选驱动的二选一*/beginif(Date_EN==1'b1)beginclk<=clk_1kHz;disp_drive<=auto_disp_drive;endelse if(DateSet_EN==1'b1)beginclk<=clk_200Hz;disp_drive<=DateSet_disp_drive;endendalways@(posedge clk)/*实现时间的动态位选*/begincase(disp_drive)4'b0000:Date_disp_select<=8'b10000000;4'b0001:Date_disp_select<=8'b01000000;4'b0010:Date_disp_select<=8'b00100000;4'b0011:Date_disp_select<=8'b00010000;4'b0100:Date_disp_select<=8'b00001000;4'b0101:Date_disp_select<=8'b00000100;4'b0110:Date_disp_select<=8'b00000010;4'b0111:Date_disp_select<=8'b00000001;default:Date_disp_select<=8'b00000000;endcaseendendmodulemodule stopwatch(clk1,clk2,EN,F_out);output F_out;input EN;input clk1,clk2;reg F_out;always@(EN,clk1,clk2)begincase(EN)1'b0:F_out<=clk1;1'b1:F_out<=clk2;default:F_out<=1'b0;endcaseendEndmodulemoduletime_disp_select(clk_1kHz,clk_200Hz,Time_EN,TimeSet_EN,timeset_disp_drive,time_disp_sele ct);output[5:0]time_disp_select;input clk_1kHz;input clk_200Hz;input Time_EN;input TimeSet_EN;input[2:0]timeset_disp_drive;reg[5:0]time_disp_select;reg[2:0]auto_disp_drive;reg clk;reg[2:0]disp_drive;always@(posedge clk_1kHz)/*实现自动运行模式中的动态显示“位选的驱动”*/ beginif(auto_disp_drive<3'b101)auto_disp_drive<=auto_disp_drive+3'b1;elseauto_disp_drive<=3'b0;endalways/*实现自动运行模式中时间动态显示位选驱动与时间设置中的时间动态显示位选驱动的二选一*/beginif(Time_EN==1'b1)beginclk<=clk_1kHz;disp_drive<=auto_disp_drive;endelse if(TimeSet_EN==1'b1)beginclk<=clk_200Hz;disp_drive<=timeset_disp_drive;endendalways@(posedge clk)/*实现时间的动态位选*/begincase(disp_drive)3'b000:time_disp_select<=6'b100000;3'b001:time_disp_select<=6'b010000;3'b010:time_disp_select<=6'b001000;3'b011:time_disp_select<=6'b000100;3'b100:time_disp_select<=6'b000010;3'b101:time_disp_select<=6'b000001;default:time_disp_select<=6'b000000;endcaseendendmodulemoduleDate_mux(year_3,year_2,year_1,year_0,month_1,month_0,date_1,date_0,DateSet_EN,year_data3, year_data2,year_data1,year_data0,month_data1,month_data0,date_data1,date_data0,yeardata_set3,yeardata_set2,yeardata_set1,yeardata_set0,monthdata_set1,monthdata_set0,datedata_set1,datedata _set0);output[3:0]year_3;output[3:0]year_2;output[3:0]year_1;output[3:0]year_0;output[3:0]month_1;output[3:0]month_0;output[3:0]date_1;output[3:0]date_0;input DateSet_EN;//时间设置使能信号input[3:0]year_data3;//自动模式中当前时间的小时输入input[3:0]year_data2;//自动模式中当前时间的分钟输入input[3:0]year_data1;//自动模式中当前时间的秒输入input[3:0]year_data0;//时间设置后的小时输入input[3:0]month_data1;//时间设置后的分钟输入input[3:0]month_data0;input[3:0]date_data1;input[3:0]date_data0;input[3:0]yeardata_set3;input[3:0]yeardata_set2;input[3:0]yeardata_set1;input[3:0]yeardata_set0;input[3:0]monthdata_set1;input[3:0]monthdata_set0;input[3:0]datedata_set1;input[3:0]datedata_set0;reg[3:0]year_3;reg[3:0]year_2;reg[3:0]year_1;reg[3:0]year_0;reg[3:0]month_1;reg[3:0]month_0;reg[3:0]date_1;reg[3:0]date_0;always@(year_3,year_2,year_1,year_0,month_1,month_0,date_1,date_0,DateSet_EN,year_data3, year_data2,year_data1,year_data0,month_data1,month_data0,date_data1,date_data0,yeardata_set3, yeardata_set2,yeardata_set1,yeardata_set0,monthdata_set1,monthdata_set0,datedata_set1,datedata _set0)beginif(DateSet_EN==1'b1)beginyear_3<=yeardata_set3;year_2<=yeardata_set2;year_1<=yeardata_set1;year_0<=yeardata_set0;month_1<=monthdata_set1;month_0<=monthdata_set0;date_1<=datedata_set1;date_0<=datedata_set0;endelsebeginyear_3<=year_data3;year_2<=year_data2;year_1<=year_data1;year_0<=year_data0;month_1<=month_data1;month_0<=month_data0;date_1<=date_data1;date_0<=date_data0;endendEndmodulemoduletime_mux(TimeSet_EN,hour1,hour0,minute1,minute0,second1,second0,hour_set1,hour_set0,minu te_set1,minute_set0,second_set1,second_set0,hour_1,hour_0,minute_1,minute_0,second_1,second _0);output[3:0]hour_1,hour_0;//当前需要显示的小时输出output[3:0]minute_1,minute_0;//当前需要显示的分钟输出output[3:0]second_1,second_0;//当前需要显示的秒输出input TimeSet_EN;//时间设置使能信号input[3:0]hour1,hour0;//自动模式中当前时间的小时输入input[3:0]minute1,minute0;//自动模式中当前时间的分钟输入input[3:0]second1,second0;//自动模式中当前时间的秒输入input[3:0]hour_set1,hour_set0;//时间设置后的小时输入input[3:0]minute_set1,minute_set0;//时间设置后的分钟输入input[3:0]second_set1,second_set0;//时间设置后的秒输入reg[3:0]hour_1,hour_0;reg[3:0]minute_1,minute_0;reg[3:0]second_1,second_0;/*时间自动显示与时间调整与设置中显示数据的多路选择*/always@(TimeSet_EN,hour1,hour0,minute1,minute0,second1,second0,hour_set1,hour_set0,minut e_set1,minute_set0,second_set1,second_set0)beginif(TimeSet_EN==1'b1)beginhour_1<=hour_set1;hour_0<=hour_set0;minute_1<=minute_set1;minute_0<=minute_set0;second_1<=second_set1;second_0<=second_set0;endelsebeginhour_1<=hour1;hour_0<=hour0;minute_1<=minute1;minute_0<=minute0;second_1<=second1;second_0<=second0;endendEndmodulemoduleanjiandate(DateSet_EN,sw1,sw2,year_data3,year_data2,year_data1,year_data0,month_data1,mont h_data0,date_data1,date_data0,yeardata_set3,yeardata_set2,yeardata_set1,yeardata_set0,monthdat a_set1,monthdata_set0,datedata_set1,datedata_set0,Disp_drive);input DateSet_EN;input sw1;input sw2;input[3:0]year_data3;input[3:0]year_data2;input[3:0]year_data1;input[3:0]year_data0;input[3:0]month_data1;input[3:0]month_data0;input[3:0]date_data1;input[3:0]date_data0;output[3:0]yeardata_set3;output[3:0]yeardata_set2;output[3:0]yeardata_set1;output[3:0]yeardata_set0;output[3:0]monthdata_set1;output[3:0]monthdata_set0;output[3:0]datedata_set1;output[3:0]datedata_set0;output[3:0]Disp_drive;reg[3:0]yeardata_set3;reg[3:0]yeardata_set2;reg[3:0]yeardata_set1;reg[3:0]yeardata_set0;reg[3:0]monthdata_set1;reg[3:0]monthdata_set0;reg[3:0]datedata_set1;reg[3:0]datedata_set0;reg[3:0]Disp_drive;initialbeginyeardata_set3<=year_data3;yeardata_set2<=year_data2;yeardata_set1<=year_data1;yeardata_set0<=year_data0;monthdata_set1<=month_data1;monthdata_set0<=month_data0;datedata_set1<=date_data1;datedata_set0<=date_data0;endalways@(posedge sw1)beginif(DateSet_EN==1)beginif(Disp_drive<4'b0111)Disp_drive<=Disp_drive+3'b1;elseDisp_drive<=3'b0;endendalways@(posedge sw2)beginif(DateSet_EN==1)begincase(Disp_drive)4'b0000:beginif(yeardata_set3<4'b1001)yeardata_set3<=yeardata_set3+4'b1;elseyeardata_set3<=4'b0;end4'b0001:beginif(yeardata_set2<4'b1001)yeardata_set2<=yeardata_set2+4'b1;elseyeardata_set2<=0;end4'b0010:beginif(yeardata_set1<4'b1001)yeardata_set1<=yeardata_set1+4'b1;elseyeardata_set1<=4'b0;end4'b0011:beginif(yeardata_set0<4'b1001)yeardata_set0<=yeardata_set0+4'b1;elseyeardata_set0<=4'b0;end4'b0100:beginif(monthdata_set1<4'b0001)monthdata_set1<=monthdata_set1+4'b1;elsemonthdata_set1<=4'b0;end4'b0101:beginif((monthdata_set1<4'b0001)&&(monthdata_set0<4'b1001))monthdata_set0<=monthdata_set0+4'b1;else if((monthdata_set1==4'b0001)&&(monthdata_set0<4'b0010)) monthdata_set0<=monthdata_set0+4'b1;elsemonthdata_set0<=4'b0;end4'b0110:beginif(datedata_set1<4'b1001)datedata_set1<=datedata_set1+4'b1;elsedatedata_set1<=4'b0;end4'b0111:beginif(datedata_set0<4'b1001)datedata_set0<=datedata_set0+4'b1;elsedatedata_set0<=4'b0;endendcaseendendendmodulemoduleanjian(TimeSet_EN,sw1,sw2,hour1,hour0,minute1,minute0,second0,second1,hour_set1,hour_set0, minute_set1,minute_set0,second_set1,second_set0,disp_drive);input TimeSet_EN;input sw1;input sw2;input[3:0]hour1;input[3:0]hour0;input[3:0]minute1;input[3:0]minute0;input[3:0]second1;input[3:0]second0;output[3:0]hour_set1;output[3:0]hour_set0;output[3:0]minute_set1;output[3:0]minute_set0;output[3:0]second_set1;output[3:0]second_set0;output[2:0]disp_drive;reg[3:0]hour_set1;reg[3:0]hour_set0;reg[3:0]minute_set1;reg[3:0]minute_set0;reg[3:0]second_set1;reg[3:0]second_set0;reg[2:0]disp_drive;initialbeginhour_set1<=hour1;hour_set0<=hour0;minute_set1<=minute1;minute_set0<=minute0;second_set1<=second1;second_set0<=second0;endalways@(posedge sw1)beginif(TimeSet_EN==1)beginif(disp_drive<3'b101)disp_drive<=disp_drive+3'b1;elsedisp_drive<=3'b0;endendalways@(posedge sw2)beginif(TimeSet_EN==1)begincase(disp_drive)3'b000:beginif(hour_set1<4'b0010)hour_set1<=hour_set1+4'b1;elsehour_set1<=4'b0;end3'b001:beginif((hour_set1<4'b0010)&&(hour_set0<4'b1001))hour_set0<=hour_set0+4'b1;else if((hour_set1==4'b0010)&&(hour_set0<4'b0100))hour_set0<=hour_set0+4'b1;elsehour_set0<=4'b0;end3'b010:beginif(minute_set1<4'b0101)minute_set1<=minute_set1+4'b1;elseminute_set1<=4'b0;end3'b011:beginif(minute_set0<4'b1001)minute_set0<=minute_set0+4'b1;elseminute_set0<=4'b0;end3'b100:beginif(second_set1<4'b0101)second_set1<=second_set1+4'b1;elsesecond_set1<=4'b0;end3'b101:beginif(second_set0<4'b1001)second_set0<=second_set0+4'b1;elsesecond_set0<=4'b0;endendcaseendendendmodulemodulemaincontrol(SW3,Timepiece_EN,TimeSet_EN,Stopwatch_EN,Alarmclock_EN,Date_EN,DateSet _EN,led);output[7:0]led;output Timepiece_EN;//时间自动显示使能output TimeSet_EN;//时间调整与设置使能output Stopwatch_EN;//秒钟功能使能output Alarmclock_EN;//闹钟时间设置使能output Date_EN;//时期显示使能output DateSet_EN;//日期调整与设置使能input SW3;//功能号选择reg[7:0]led;reg Timepiece_EN;reg TimeSet_EN;reg Stopwatch_EN;reg Alarmclock_EN;reg Date_EN;reg DateSet_EN;reg[2:0]Function;always@(posedge SW3)/*实现对时间显示与调整,日期显示与调整,闹钟显示与调整,秒表操作等的控制*/begin//功能号的产生以及其自动循环if(Function<3'b101)Function<=Function+3'b1;elseFunction<=3'b0;case(Function)//各个分功能的控制和实现//时钟自动显示3'b000:beginled=8'b01111111;Timepiece_EN<=1'b1;TimeSet_EN<=1'b0;Stopwatch_EN<=1'b0;Alarmclock_EN<=1'b0;Date_EN<=1'b0;DateSet_EN<=1'b0;end//时钟调整与设置3'b001:beginled=8'b10111111;Timepiece_EN<=1'b0;TimeSet_EN<=1'b1;Stopwatch_EN<=1'b0;Alarmclock_EN<=1'b0;Date_EN<=1'b0;DateSet_EN<=1'b0;end//秒表3'b010:beginled=8'b11011111;Timepiece_EN<=1'b0;TimeSet_EN<=1'b0;Stopwatch_EN<=1'b1;Alarmclock_EN<=1'b0;Date_EN<=1'b0;DateSet_EN<=1'b0;end//闹钟时间设置3'b011:beginled=8'b11101111;Timepiece_EN<=1'b0;TimeSet_EN<=1'b0;Stopwatch_EN<=1'b0;Alarmclock_EN<=1'b1;Date_EN<=1'b0;DateSet_EN<=1'b0;end//日期显示3'b100:beginled=8'b11110111;Timepiece_EN<=1'b0;TimeSet_EN<=1'b0;Stopwatch_EN<=1'b0;Alarmclock_EN<=1'b0;Date_EN<=1'b1;DateSet_EN<=1'b0;end//日期调整与设置3'b101:beginled=8'b11111011;Timepiece_EN<=1'b0;TimeSet_EN<=1'b0;Stopwatch_EN<=1'b0;Alarmclock_EN<=1'b0;Date_EN<=1'b0;DateSet_EN<=1'b1;enddefault:beginled=8'b0;Timepiece_EN<=1'b0;TimeSet_EN<=1'b0;Stopwatch_EN<=1'b0;Alarmclock_EN<=1'b0;Date_EN<=1'b0;DateSet_EN<=1'b0;endendcaseendendmodulemodule fdiv(clk,f200Hz,f60Hz,f1Hz);output f200Hz,f60Hz,f1Hz;input clk;reg f200Hz,f60Hz,f1Hz;integer CNT1=0,CNT2=0,CNT3=0;/*实现将全局时钟分频得到200Hz时钟信号*/always@(posedge clk)beginif(CNT1<4)beginCNT1=CNT1+1;f200Hz<=1'b0;endelsebeginCNT1=0;f200Hz<=1'b1;endend/*实现将200Hz时钟分频得到60Hz时钟信号*/always@(posedge f200Hz)beginif(CNT2<2)beginCNT2=CNT2+1;f60Hz<=1'b0;endelsebeginCNT2=0;f60Hz<=1'b1;endend/*实现将200Hz时钟分频得到1Hz时钟信号*/always@(posedge f200Hz)beginif(CNT3<199)beginCNT3=CNT3+1;f1Hz<=1'b0;endelsebeginCNT3=0;f1Hz<=1'b1;endendendmodulemodule year_counter(EN,clk,year_data3,year_data2,year_data1,year_data0);output[3:0]year_data3,year_data2,year_data1,year_data0;input clk,EN;reg[3:0]year_data3,year_data2,year_data1,year_data0;reg E0;always@(posedge clk)beginif(EN==1'b1)beginyear_data3<=4'b0010;//年的最高位表示2year_data2<=4'b0000;//年的第三位表示0year_data1<=4'b0001;//年的第二位表示1year_data0<=4'b0010;//年的最低位表示0endif(year_data0<4'b1001)//年的最低位小于9year_data0<=year_data0+4'b1;//年的最低位进一elsebeginyear_data0<=4'b0;//年的最低位清零if(year_data1<4'b1001)//判断年的第二位是否大于9year_data1<=year_data1+4'b1;//年的第二位表达方式elsebeginyear_data1<=4'b0;//年的第二位清零if(year_data2<4'b1001)//判断年的第二位是否小于9year_data2<=year_data2+4'b1;//年的第二位进一elsebeginyear_data2<=4'b0;//年的第二位清零if(year_data3<4'b1001)//判断年的最高位是否小于9year_data3<=year_data3+4'b1;//年的最高位进一elseyear_data3<=0;//清零year_data2<=0;//清零year_data1<=0;//清零year_data0<=0;//清零endendendendendmodulemodule date_counter(EN,clk,date_data1,date_data0,E0);output[3:0]date_data1,date_data0;output E0;input clk,EN;reg[3:0]date_data1,date_data0;reg E0;always@(posedge clk)beginif(EN==1'b1)beginif(date_data0<4'b1001)date_data0<=date_data0+4'b1;elsebeginE0<=1'b0;date_data0<=4'b0;if(date_data1<4'b00010)date_data1<=date_data1+4'b1;elsebegindate_data1<=4'b0;E0<=1'b1;endendendendEndmodulemodule month_counter(EN,clk,month_data1,month_data0,E0);output[3:0]month_data1,month_data0;output E0;input clk,EN;reg[3:0]month_data1,month_data0;reg E0;always@(posedge clk)beginif(EN==1'b1)beginmonth_data0<=4'b0001;month_data1<=4'b0;endif(month_data0<4'b1001)month_data0<=month_data0+4'b1;elsebeginE0<=1'b0;month_data0<=4'b0;if(month_data1<4'b0001)month_data1<=month_data1+4'b1;elsebeginif((month_data1==4'b0001)&&(month_data0==4'b0010))beginmonth_data1<=4'b0;month_data0<=4'b1;E0<=1'b1;endendendendEndmodulemodule hour_counter(EN,clk,hour_data1,hour_data0,E0);output[3:0]hour_data1,hour_data0;output E0;input clk,EN;reg[3:0]hour_data1,hour_data0;reg E0;always@(posedge clk)beginif(EN==1'b1)beginif(hour_data0<4'b1001)hour_data0<=hour_data0+4'b1;elsebeginE0<=1'b0;hour_data0<=4'b0;if(hour_data1<4'b00010)hour_data1<=hour_data1+4'b1;elsebeginhour_data1<=4'b0;E0<=1'b1;endendendendEndmodulemodule minute_counter(EN,clk,minute_data1,minute_data0,E0);output[3:0]minute_data1,minute_data0;output E0;input clk,EN;reg[3:0]minute_data1,minute_data0;reg E0;always@(posedge clk)beginif(EN==1'b1)beginif(minute_data0<4'b1001)minute_data0<=minute_data0+4'b1;elsebeginE0<=1'b0;minute_data0<=4'b0;if(minute_data1<4'b0101)minute_data1<=minute_data1+4'b1;elsebeginminute_data1<=4'b0;E0<=1'b1;endendendendEndmodulemodule second_counter(Timepiece_EN,clk,second_data1,second_data0,E0);output[3:0]second_data1,second_data0;output E0;input clk,Timepiece_EN;reg[3:0]second_data1,second_data0;reg E0;always@(posedge clk)beginif(Timepiece_EN==1'b1)beginif(second_data0<4'b1001)second_data0<=second_data0+4'b1;elsebeginE0<=1'b0;second_data0<=4'b0;if(second_data1<4'b0101)second_data1<=second_data1+4'b1;elsebeginsecond_data1<=4'b0;E0<=1'b1;endendendendEndmodule。

基于fpga的LCD显示万年历

接着我的上一篇博文,终于完善好了,前几天太忙了,没有及时上传,呵呵,今天晚上刚比较早刚好凌晨,及时上传一下,实现了从0000---9999年的时钟,其实万年历和十万年历,都是差不多,等到地球能转到9999年再改代码也不迟,哈哈!!我这里有顶层和底层文件,顶层主要是调用模块和做按键处理,具体按键防抖动原理,参见偶的以前的博文,我写完这个万年历的代码,还没来得及优化,占用了太多了逻辑门,可以进一步优化。

大致思路是:第一次按下KEY1 的时候,所有计时停止,再按KEY1,年就闪烁,按下KEY2和KEY3 进行加减。

再按KEY1,月就闪烁,按下KEY2和KEY3 进行加减........依次为调年-月-日-星期-时分秒,再次按一下KEY1,进入正常运行模式。

好了先上顶层模块module LCD(rst,clk,rw,rs,en,data,key1,key2,key3);input clk,rst;input key1,key2,key3;output rs,en,rw;output [7:0] data;reg key1_out,key2_out,key3_out;wire clk,rst;wire rs,en,rw;wire [7:0] data;disp U1(.clk(clk),.rst(rst),.rs(rs),.en(en),.rw(rw),.data(data),.key1(key1_out),.key2(key2_out),.key3(key3_out));//=============key1,key2,key3 按键防抖动================// reg key1_reg1,key1_reg2;reg key2_reg1,key2_reg2;reg key3_reg1,key3_reg2;reg [31:0] count;always @(posedge clk)begincount<=count+1;if(count==500000)begincount<=0;key1_reg1<=key1;key2_reg1<=key2;key3_reg1<=key3;endkey1_reg2<=key1_reg1;key2_reg2<=key2_reg1;key3_reg2<=key3_reg1;key1_out <= key1_reg2 & (!key1_reg1);key2_out <= key2_reg2 & (!key2_reg1);key3_out <= key3_reg2 & (!key3_reg1);endendmodule底层模块:module disp(rst,clk,rw,rs,en,data,key1,key2,key3);input clk,rst;input key1,key2,key3;output rs,en,rw;output [7:0] data;reg rs,en_sel;reg [7:0] data;reg [14:0] year;reg [7:0] shi,fen,miao,month,dat;reg [31:0]count,count1; //LCD CLK 分频计数器reg lcd_clk;//2行32个数据寄存器reg [7:0]one_1,one_2,one_3,one_4,one_5,one_6,one_7,one_8,one_9,one_10,one_11,one_12,on e_13,one_14,one_15,one_16;reg [7:0]two_1,two_2,two_3,two_4,two_5,two_6,two_7,two_8,two_9,two_10,two_11,two_12,two_ 13,two_14,two_15,two_16;reg [7:0] next;parameter state0 =8'h00, //设置8位格式,2行,5*7 8'h38;state1 =8'h01, //整体显示,关光标,不闪烁8'h0C 闪烁8'h0estate2 =8'h02, //设定输入方式,增量不移位8'h06state3 =8'h03, //清除显示8'h01state4 =8'h04, //显示第一行的指令80Hstate5 =8'h05, //显示第二行的指令80H+40Hscan =8'h06,nul =8'h07;parameter data0 =8'h10, //2行32个数据状态data1 =8'h11,data2 =8'h12,data3 =8'h13,data4 =8'h14,data5 =8'h15,data6 =8'h16,data7 =8'h17,data8 =8'h18,data9 =8'h19,data10 =8'h20,data11 =8'h21,data12 =8'h22,data13 =8'h23,data14 =8'h24,data15 =8'h25,data16 =8'h26,data17 =8'h27,data18 =8'h28,data19 =8'h29,data20 =8'h30,data21 =8'h31,data22 =8'h32,data23 =8'h33,data24 =8'h34,data25 =8'h35,data26 =8'h36,data27 =8'h37,data28 =8'h38,data29 =8'h39,data30 =8'h40,data31 =8'h41;initialbegin//第一行显示年-月-日星期//Mon Tue Wed Thur Fri Sat Sunone_1<=" "; one_2<=" "; one_3<=" "; one_4<=" "; one_5<="-"; one_6<=" "; one_7<=" "; one_8<="-";one_9<=" ";one_10<=" ";one_11<=" ";one_12<=" ";one_13<=" ";one_14<="";one_15<=" ";one_16<=" ";//第二行显示Clock:00-00-00two_1<="C"; two_2<="l"; two_3<="o"; two_4<="c"; two_5<="k"; two_6<=":"; two_7<=" "; two_8<=" ";two_9<="-";two_10<=" ";two_11<=" ";two_12<="-";two_13<=" ";two_14<="";two_15<=" ";two_16<=" ";shi<=8'd0;fen<=8'd0;miao<=8'd0;end//======================产生LCD 时序脉冲=========================== always @ (posedge clk ) //获得LCD时钟begincount<=count+1;if(count==32'd50000)begincount<=32'b0;lcd_clk<=~lcd_clk;endend//=====================产生闪烁扫描时钟===========================reg [31:0] count2;reg scan_flag;always @ (posedge clk or negedge rst) //获得校准时间选中闪烁状态beginif(!rst)beginscan_flag<=1'b0;endelsebegincount2<=count2+1;if(count2==32'd1*******)begincount2<=32'b0;scan_flag<=~scan_flag;endendend//====================产生按键标志位================================= reg [3:0] flag;always @ (posedge clk or negedge rst )beginif(!rst)beginflag<=4'b0;endelseif(key1)beginflag<=flag+1'b1;if(flag==4'b1000)flag<=4'b0000;endend//===================计时以及校准=======================================reg[3:0] week;reg[7:0] dat_flag;always @ (posedge clk or negedge rst ) //时钟计数器beginif(!rst)begin //初始化显示第一行2012-05-19 Sat 第二行:Clock:00-00-00 shi<=8'b0;fen<=8'b0;miao<=8'b0;month<=8'd5;dat<=8'd19;year<=16'd2012;week<=4'd5;count1<=1'b0;two_7<= (shi/8'd10)+8'b00110000;two_8<= (shi%8'd10)+8'b00110000;two_10<=(fen/8'd10)+8'b00110000;two_11<=(fen%8'd10)+8'b00110000;two_13<=(miao/8'd10)+8'b00110000;two_14<=(miao%8'd10)+8'b00110000;one_1<=(year/16'd1000)+8'b00110000;one_2<=((year%16'd1000)/16'd100)+8'b00110000;one_3<=((year%16'd100)/8'd10)+8'b00110000;one_4<=(year%8'd10)+8'b00110000;one_6<=(month/8'd10)+8'b00110000;one_7<=(month%8'd10)+8'b00110000;one_9<=(dat/8'd10)+8'b00110000;one_10<=(dat%8'd10)+8'b00110000;endelsebegintwo_7<= (shi/8'd10)+8'b00110000;two_8<= (shi%8'd10)+8'b00110000;two_10<=(fen/8'd10)+8'b00110000;two_11<=(fen%8'd10)+8'b00110000;two_13<=(miao/8'd10)+8'b00110000;two_14<=(miao%8'd10)+8'b00110000;one_1<=(year/16'd1000)+8'b00110000;one_2<=((year%16'd1000)/16'd100)+8'b00110000;one_3<=((year%16'd100)/8'd10)+8'b00110000;one_4<=(year%8'd10)+8'b00110000;one_6<=(month/8'd10)+8'b00110000;one_7<=(month%8'd10)+8'b00110000;one_9<=(dat/8'd10)+8'b00110000;one_10<=(dat%8'd10)+8'b00110000;// 判断是否为31天的月份if(month==8'd1||month==8'd3||month==8'd5||month==8'd7||month==8'd8||month==8'd10|| month==8'd12)dat_flag<=8'd31;// 判断是否为30天的月份else if(month==8'd4||month==8'd6||month==8'd9||month==8'd11)dat_flag<=8'd30;// 判断是否为闰年和平年else if(month==8'd2)beginif(year % 4 == 0 && year % 100 != 0 || year % 400 == 0)dat_flag<=28;else dat_flag<=27;endcase (week)//星期//Mon Tue Wed Thu Fri Sat Sun4'b0000 : //1beginone_13<="M";one_14<="o";one_15<="n";end4'b0001 : //2beginone_13<="T";one_14<="u";one_15<="e";end4'b0010 : //3beginone_13<="W";one_14<="e";one_15<="d"; end4'b0011 : //4beginone_13<="T";one_14<="h";one_15<="u"; end4'b0100 : //5beginone_13<="F";one_14<="r";one_15<="i"; end4'b0101 : //6beginone_13<="S";one_14<="a";one_15<="t"; end4'b0110 : //7beginone_13<="S";one_14<="u";one_15<="n"; endendcasecase(flag)4'b0000 :beginen_sel<=1'b1;count1<=count1+1'b1;if(count1==32'd4*******)begincount1<=1'b0;miao<=miao+1'b1;if(miao==8'd59)beginmiao<=1'b0;fen<=fen+1'b1;if(fen==8'd59)beginfen<=1'b0;shi<=shi+1'b1;if(shi==8'd23)beginshi<=1'b0;dat<=dat+1'b1;week<=week+1'b1;if(week==4'b0110)week<=1'b1;if(dat==dat_flag)begindat<=8'd1;month<=month+1'b1;if(month==8'd12)beginmonth<=8'd1;year<=year+1'b1;if(year==16'd9999)year<=16'd0; //可以计1万年endendendendendendend4'b0001 :begincount1<=32'b0;//shi<=shi;fen<=fen;miao<=miao;year<=year;month<=month;dat<=dat;week<=week;end4'b0010 : //调年begincase(scan_flag)1'b0:begincount1<=32'b0; //shi<=shi;fen<=fen;miao<=miao;one_1<=8'd20;one_2<=8'd20;one_3<=8'd20;one_4<=8'd20;end1'b1:begincount1<=32'b0; //shi<=shi;fen<=fen;miao<=miao;endendcaseif(key2) //加数beginyear<=year+1'b1;if(year==16'd9999)year<=16'd0;endif(key3) //减数beginyear<=year-1'b1;if(year==16'd0)year<=16'd9999;endend4'b0011 : //调月begincase(scan_flag)1'b0:begincount1<=32'b0; //shi<=shi;fen<=fen;miao<=miao;one_6<=8'd20;one_7<=8'd20;end1'b1:begincount1<=32'b0; //shi<=shi;fen<=fen;miao<=miao;endcaseif(key2) //加数beginmonth<=month+1'b1;if(month==8'd12)month<=8'd0;endif(key3) //减数beginmonth<=month-1'b1;if(month==8'd0)month<=8'd12;endend4'b0100 : //调日begincase(scan_flag)1'b0:begincount1<=32'b0; //shi<=shi;fen<=fen;miao<=miao;one_9<=8'd20;one_10<=8'd20;end1'b1:begincount1<=32'b0; //shi<=shi;fen<=fen;miao<=miao;endendcaseif(key2) //加数begindat<=dat+1'b1;if(dat==dat_flag)dat<=8'd0;endif(key3) //减数dat<=dat-1'b1;if(dat==8'd0)dat<=dat_flag;endend4'b0101 : //调星期begincase(scan_flag)1'b0:begincount1<=32'b0; //shi<=shi;fen<=fen;miao<=miao;one_13<=8'd20;one_14<=8'd20;one_15<=8'd20;end1'b1:begincount1<=32'b0; //shi<=shi;fen<=fen;miao<=miao;endendcaseif(key2) //加数beginweek<=week+1'b1;if(week==4'd6)week<=4'd0;endif(key3) //减数beginweek<=week-1'b1;if(week==4'd0)week<=4'd7;endend4'b0110 : //调时begincase(scan_flag)begincount1<=32'b0; //shi<=shi;fen<=fen;miao<=miao;two_7<= 8'd20;two_8<= 8'd20;end1'b1:begincount1<=32'b0; //shi<=shi;fen<=fen;miao<=miao;endendcaseif(key2) //加数beginshi<=shi+8'b00000001;if(shi==8'd23)shi<=8'b0;endif(key3) //减数beginshi<=shi-8'b00000001;if(shi==8'b0)shi<=23;endend4'b0111 : //调分begincase(scan_flag)1'b0:begincount1<=32'b0; //shi<=shi;fen<=fen;miao<=miao;two_10<=8'd20;two_11<=8'd20;end1'b1:begincount1<=32'b0; //shi<=shi;fen<=fen;miao<=miao;endendcaseif(key2) //加数beginfen<=fen+8'b00000001;if(fen==8'd59)fen<=8'b0;endif(key3) //减数beginfen<=fen-8'b00000001;if(fen==8'b0)fen<=59;endend4'b1000 : //调秒begincase(scan_flag)1'b0:begincount1<=32'b0; //shi<=shi;fen<=fen;miao<=miao;two_13<=8'd20;two_14<=8'd20;end1'b1:begincount1<=32'b0; //shi<=shi;fen<=fen;miao<=miao;endendcaseif(key2) //加数beginmiao<=miao+8'b00000001;if(miao==8'd59)miao<=8'b0;endif(key3) //减数beginmiao<=miao-8'b00000001;if(miao==8'b0)miao<=59;endendendcaseendendalways @(posedge lcd_clk )begincase(next)state0 :begin rs<=1'b0; data<=8'h38; next<=state1; endstate1 :begin rs<=1'b0; data<=8'h0e; next<=state2; endstate2 :begin rs<=1'b0; data<=8'h06; next<=state3; endstate3 :begin rs<=1'b0; data<=8'h01; next<=state4; endstate4 :begin rs<=1'b0; data<=8'h80; next<=data0; end //显示第一行data0 :begin rs<=1'b1; data<=one_1; next<=data1 ; enddata1 :begin rs<=1'b1; data<=one_2; next<=data2 ; enddata2 :begin rs<=1'b1; data<=one_3; next<=data3 ; enddata3 :begin rs<=1'b1; data<=one_4; next<=data4 ; enddata4 :data5 :begin rs<=1'b1; data<=one_6; next<=data6 ; enddata6 :begin rs<=1'b1; data<=one_7; next<=data7 ; enddata7 :begin rs<=1'b1; data<=one_8; next<=data8 ; enddata8 :begin rs<=1'b1; data<=one_9; next<=data9 ; enddata9 :begin rs<=1'b1; data<=one_10; next<=data10 ; enddata10 :begin rs<=1'b1; data<=one_11; next<=data11 ; enddata11 :begin rs<=1'b1; data<=one_12; next<=data12 ; enddata12 :begin rs<=1'b1; data<=one_13; next<=data13 ; enddata13 :begin rs<=1'b1; data<=one_14; next<=data14 ; enddata14 :begin rs<=1'b1; data<=one_15; next<=data15 ; enddata15 :begin rs<=1'b1; data<=one_16; next<=state5 ; endstate5:begin rs<=1'b0;data<=8'hC0; next<=data16; end //显示第二行data16 :begin rs<=1'b1; data<=two_1; next<=data17 ; enddata17 :begin rs<=1'b1; data<=two_2; next<=data18 ; enddata18 :begin rs<=1'b1; data<=two_3; next<=data19 ; enddata19 :begin rs<=1'b1; data<=two_4; next<=data20 ; enddata20 :data21 :begin rs<=1'b1; data<=two_6; next<=data22 ; enddata22 :begin rs<=1'b1; data<=two_7; next<=data23 ; enddata23 :begin rs<=1'b1; data<=two_8; next<=data24 ; enddata24 :begin rs<=1'b1; data<=two_9; next<=data25 ; enddata25 :begin rs<=1'b1; data<=two_10; next<=data26 ; end data26 :begin rs<=1'b1; data<=two_11; next<=data27 ; end data27 :begin rs<=1'b1; data<=two_12; next<=data28 ; end data28 :begin rs<=1'b1; data<=two_13; next<=data29 ; end data29 :begin rs<=1'b1; data<=two_14; next<=data30 ; end data30 :begin rs<=1'b1; data<=two_15; next<=data31 ; end data31 :begin rs<=1'b1; data<=two_16; next<=scan ; endscan : //交替更新第一行和第二行数据beginnext<=state4;enddefault: next<=state0;endcaseendassign en=lcd_clk && en_sel;assign rw=1'b0;endmodule。

基于FPGA的万年历程序设计

library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;entity clock isport(rst:in std_logic;clk:in std_logic;clr:in std_logic;display_mode: in std_logic;inc:in std_logic;mode:in std_logic;seg8:out std_logic_vector(7 downto 0);scan:out std_logic_vector(7 downto 0);led:out std_logic_vector(3 downto 0) );end;architecture one of clock is--signal state:std_logic_vector(2 downto 0);--signal dis_mode:std_logic_vector(1 downto 0);signal state:integer range 0 to 7;signal dis_mode:integer range 0 to 3;--signal qhh,qhl,qmh,qml,qsh,qsl,qy1,qy2,qy3,qy4,qm1,qm2,qd1,qd2:std_logic_vector(3 downto 0);signal qhh,qhl,qmh,qml,qsh,qsl,qy1,qy2,qy3,qy4,qmonl,qmonh,qdl,qdh:integer range 0 to 15; signal data:integer range 0 to 15 ;signal cnt:integer range 0 to 7;signal clk1khz,clk1hz,clk2hz,clk5ms:std_logic;--signal blink:std_logic_vector(2 downto 0);--signal inc_reg:std_logic;signal sec,min:integer range 0 to 59;signal hour:integer range 0 to 23;signal year:integer range 1 to 9999;signal month:integer range 1 to 12;signal day,day_limit:integer range 1 to 31;beginprocess(clk)variable count:integer range 0 to 30000;beginif clk'event and clk='1' thenif count=25000 then clk1khz<=not clk1khz;count:=0;else count:=count+1;end if;end if;end process;-------------------------------------------------------process (clk)variable cnte:integer range 0 to 30000000;beginif clk'event and clk ='1' thenif cnte=25000000 then clk1hz<=not clk1hz; cnte:=0;else cnte:=cnte+1;end if ;end if ;end process ;-----------------------------------------------------process (clk)variable cnt2:integer range 0 to 25000000;beginif clk'event and clk='1' thenif cnt2=12500000 then clk2hz<=clk2hz;cnt2:=0;else cnt2:=cnt2+1;end if ;end if ;end process;-----------------------------------------------------process(clk)variable cnnt:integer range 0 to 600000;beginif clk'event and clk='1' thenif cnnt=500000 then clk5ms<=clk5ms;cnnt:=0;else cnnt:=cnnt+1;end if ;end if ;end process;-----------------------------------------------------------------------------------------process(display_mode , clk1hz)beginif display_mode'event and display_mode='0' then dis_mode<=dis_mode+1;if dis_mode=1 thendis_mode<=0;end if;end if;end process;-------------------------------------------process(clk)beginyear<=year;month<= month;day<=day;hour<=hour;min<=min;sec<=sec;end process;-----------------------------------------process(mode , clr,clk1hz)beginif clr='0' thenstate<=0;elsif mode'event and mode='0' thenstate<=state+1;if state=6 thenstate<=0;end if;end if ;end process;----------------------------------------------------------------------------------- process(clk1hz,state,dis_mode,inc,clr,hour,sec,min,rst,year,month,day) beginif rst='0' thenyear<=2000;month<=2;day<=25;hour<=0;min<=0;sec<=0;--state<=0;--dis_mode<=0;elsif clr='0' thenhour<=23;min<=59;sec<=55;year<=4164;month<=1;day<=25;elsif clk1hz'event and clk1hz='1' thencase state iswhen 0 => led<="0000";if((month=1)or(month=3)or(month=5)or(month=7)or(month=8)or(month=10)or(month=12)) thenday_limit<=31;end if;if month=2 then----if((year%4==0&&year%100!=0)||(year%400==0))if ((((year rem 4)=0) and ((year rem 100)/=0)) or ((year rem 400=0))) thenday_limit<=29;elseday_limit<=28;end if;end if;if((month=4)or(month=6)or(month=9)or(month=11)) thenday_limit<=30;end if;sec<=sec+1;if sec=59 thensec<=0;min<=min+1;if min=59 thenmin<=0;hour<=hour+1;if hour =23 thenhour<=0;day<=day+1;if day=day_limit thenday<=1;month<=month+1;if month=12 thenmonth<=1;year<=year+1;if year=9999 thenyear<=1;end if;end if;end if;end if;end if;end if;--if sec=59 then sec<=0;--if min=59 then min<=0;--if hour=23 then hour<=0;--else--hour<=hour+1;--end if;--else--min<=min+1;--end if;--else--sec<=sec+1;--end if;when 1=> led<="0001";if inc='0' thenif hour=23 thenhour<=0;else hour<=hour+1;end if;end if;when 2=>led<="0010" ;if inc='0' thenif min=59 thenmin<=0;elsemin<=min+1;end if;end if;when 3=>led<="0011" ;if inc='0' thenif sec=59 thensec<=0;elsesec<=sec+1;end if;end if;when 4 =>led<="0100";if inc='0' thenif year=9999 thenyear<=1;elseyear<=year+1;end if;end if;when 5=> led <="0101";if inc='0' thenif month=12 thenmonth<=1;elsemonth<=month+1;end if;end if;when 6 =>led <="0110";if inc='0' thenif day=day_limit thenday<=1;elseday<=day+1;end if;end if;when others =>null;end case;end if;--end if;end process;---------------------------------------------------------------------- process(sec)begincase sec iswhen 0|10|20|30|40|50 => qsl<=0;when 1|11|21|31|41|51 => qsl<=1;when 2|12|22|32|42|52 => qsl<=2;when 3|13|23|33|43|53 => qsl<=3;when 4|14|24|34|44|54 => qsl<=4;when 5|15|25|35|45|55 => qsl<=5;when 6|16|26|36|46|56 => qsl<=6;when 7|17|27|37|47|57 => qsl<=7;when 8|18|28|38|48|58 => qsl<=8;when 9|19|29|39|49|59 => qsl<=9;when others =>null;end case;case sec iswhen 0|1|2|3|4|5|6|7|8|9 => qsh<=0;when 10|11|12|13|14|15|16|17|18|19 => qsh<=1;when 20|21|22|23|24|25|26|27|28|29 => qsh<=2;when 30|31|32|33|34|35|36|37|38|39 => qsh<=3;when 40|41|42|43|44|45|46|47|48|49 => qsh<=4;when 50|51|52|53|54|55|56|57|58|59 => qsh<=5;when others =>null;end case;end process;-------------------------------------------------------------------- process(min)begincase min iswhen 0|10|20|30|40|50 => qml<=0;when 1|11|21|31|41|51 => qml<=1;when 2|12|22|32|42|52 => qml<=2;when 3|13|23|33|43|53 => qml<=3;when 4|14|24|34|44|54 => qml<=4;when 5|15|25|35|45|55 => qml<=5;when 6|16|26|36|46|56 => qml<=6;when 7|17|27|37|47|57 => qml<=7;when 8|18|28|38|48|58 => qml<=8;when 9|19|29|39|49|59 => qml<=9;when others =>null;end case;case min iswhen 0|1|2|3|4|5|6|7|8|9 => qmh<=0;when 10|11|12|13|14|15|16|17|18|19 => qmh<=1;when 20|21|22|23|24|25|26|27|28|29 => qmh<=2;when 30|31|32|33|34|35|36|37|38|39 => qmh<=3;when 40|41|42|43|44|45|46|47|48|49 => qmh<=4;when 50|51|52|53|54|55|56|57|58|59 => qmh<=5;when others =>null;end case;end process;----------------------------------------------------------------------- process(hour)begincase hour iswhen 0|10|20 => qhl<=0;when 1|11|21 => qhl<=1;when 2|12|22 => qhl<=2;when 3|13|23 => qhl<=3;when 4|14 => qhl<=4;when 5|15 => qhl<=5;when 6|16 => qhl<=6;when 7|17 => qhl<=7;when 8|18 => qhl<=8;when 9|19 => qhl<=9;when others =>null;end case;case hour iswhen 0|1|2|3|4|5|6|7|8|9 => qhh<=0;when 10|11|12|13|14|15|16|17|18|19 => qhh<=1;when 20|21|22|23 => qhh<=2;when others => null;end case;end process;---------------------------------------------------------------process(year)beginqy1<=year/1000;qy2<=(year rem 1000)/100;qy3<=((year rem 1000)rem 100)/10;qy4<=((year rem 1000)rem 100) rem 10;--qy1<=year/1000;--qy2<=(year rem 1000)/100;--qy3<=((year-(year/1000)*1000)-((year-(year/1000)*1000)/100)*100)/10; --qy4<=((year rem 1000)rem 100)rem 10;end process;----------------------------------------------------------------process(month)beginqmonh<=month/10;qmonl<=month rem 10;end process;-----------------------------------------------------------------process(day)beginqdh<=day/10;qdl<=day rem 10;end process;----------------------------------------------------------------process(clk1khz)beginif clk1khz'event and clk1khz='1' thenif cnt=7 thencnt<=0;else cnt<=cnt+1;end if;end if;end process;----------------------------------------------------------process (cnt,qhh,qhl,qmh,qml,qsh,qsl,dis_mode)begincase dis_mode iswhen 0 => case cnt iswhen 0 => data<=qsl; scan<="11111110";when 1 => data<=qsh; scan<="11111101";when 2 => data<=15 ; scan<="11111111";when 3 => data<=qml; scan<="11110111";when 4 => data<=qmh; scan<="11101111";when 5 => data<=15; scan<="11111111";when 6 => data<=qhl; scan<="10111111";when 7 => data<=qhh; scan<="01111111";when others => null;end case;when 1=> case cnt iswhen 0 => data<=qdl; scan<="11111110";when 1 => data<=qdh; scan<="11111101";when 2 => data<=qmonl ; scan<="11111011";when 3 => data<=qmonh; scan<="11110111";when 4 => data<=qy4; scan<="11101111";when 5 => data<=qy3; scan<="11011111";when 6 => data<=qy2; scan<="10111111";when 7 => data<=qy1; scan<="01111111";when others =>null;end case;when others => null;end case;end process;----------------------------------------------------------------------------------process(data)begincase data iswhen 0 =>seg8<="11000000";when 1 =>seg8<="11111001";when 2 =>seg8<="10100100";when 3 =>seg8<="10110000";when 4 =>seg8<="10011001";when 5 =>seg8<="10010010";when 6 =>seg8<="10000010";when 7 =>seg8<="11111000";when 8 =>seg8<="10000000";when 9 =>seg8<="10010000";when others =>seg8<="11111111";end case ;end process;end;。

vhdl万年历

FPGA——VHDL历万年LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_UNSIGNED.ALL;ENTITY TIMER ISPORT(CLK,RES,XUAN,JIA_SEC1,JIA_SEC2,JIA_MIN1,JIA_MIN2,JIA_HOUR1,JIA_HOUR2:IN STD_LOGIC;HOUR2,HOUR1,MIN2,MIN1,SEC2,SEC1:OUT STD_LOGIC_VECTOR(3 DOWNTO 0);COUT:OUT STD_LOGIC);END;ARCHITECTURE ONE OF TIMER ISSIGNAL HOUR11,HOUR22,SEC11,SEC22,MIN11,MIN22:STD_LOGIC_VECTOR(3 DOWNTO 0);BEGINPROCESS(CLK,RES,XUAN,JIA_SEC1,JIA_SEC2,JIA_MIN1,JIA_MIN2,JIA_HOUR1,JIA_HOUR2)BEGINIF(XUAN='0')THEN----------------------自动计时IF(CLK'EVENT AND CLK='1')THENIF(RES='0')THENIF(HOUR22<"0010")THENIF(HOUR11<"1001")THEN ------<19 HOURSIF(MIN22<"0101")THENIF(MIN11<"1001")THENIF(SEC22<"0101")THENIF(SEC11<"1001")THENSEC11<=SEC11+1;ELSE SEC11<="0000";SEC22<=SEC22+1;END IF;ELSIF(SEC22="0101") THENIF(SEC11<"1001")THENSEC11<=SEC11+1;ELSE SEC11<="0000";SEC22<="0000";MIN11<=MIN11+1;END IF;END IF;ELSIF(MIN11="1001")THENIF(SEC22<"0101")THENIF(SEC11<"1001")THENSEC11<=SEC11+1;ELSE SEC11<="0000";SEC22<=SEC22+1;END IF;ELSIF(SEC22="0101") THENIF(SEC11<"1001")THENSEC11<=SEC11+1;ELSE SEC11<="0000";SEC22<="0000";MIN11<="0000";MIN22<=MIN22+1;END IF;END IF;ELSIF(MIN22="0101")THENIF(MIN11<"1001")THENIF(SEC22<"0101")THENIF(SEC11<"1001")THENSEC11<=SEC11+1;ELSE SEC11<="0000";SEC22<=SEC22+1;END IF;ELSIF(SEC22="0101") THENIF(SEC11<"1001")THENSEC11<=SEC11+1;ELSE SEC11<="0000";SEC22<="0000";MIN11<=MIN11+1;END IF;END IF;ELSIF(MIN11="1001")THENIF(SEC22<"0101")THENIF(SEC11<"1001")THENSEC11<=SEC11+1;ELSE SEC11<="0000";SEC22<=SEC22+1;END IF;ELSIF(SEC22="0101") THENIF(SEC11<"1001")THENSEC11<=SEC11+1;ELSE SEC11<="0000";SEC22<="0000";MIN11<="0000";MIN22<="0000";HOU R11<=HOUR11+1;END IF;END IF;END IF;END IF;ELSIF(HOUR11="1001")THENIF(MIN22<"0101")THENIF(MIN11<"1001")THENIF(SEC22<"0101")THENIF(SEC11<"1001")THENSEC11<=SEC11+1;ELSE SEC11<="0000";SEC22<=SEC22+1;END IF;ELSIF(SEC22="0101") THENIF(SEC11<"1001")THENSEC11<=SEC11+1;ELSE SEC11<="0000";SEC22<="0000";MIN11<=MIN11+1;END IF;ELSIF(MIN11="1001")THENIF(SEC22<"0101")THENIF(SEC11<"1001")THENSEC11<=SEC11+1;ELSE SEC11<="0000";SEC22<=SEC22+1;END IF;ELSIF(SEC22="0101") THENIF(SEC11<"1001")THENSEC11<=SEC11+1;ELSE SEC11<="0000";SEC22<="0000";MIN11<="0000";MIN22<=MIN22+1;END IF;END IF;END IF;ELSIF(MIN22="0101")THENIF(MIN11<"1001")THENIF(SEC22<"0101")THENIF(SEC11<"1001")THENSEC11<=SEC11+1;ELSE SEC11<="0000";SEC22<=SEC22+1;END IF;ELSIF(SEC22="0101") THENIF(SEC11<"1001")THENSEC11<=SEC11+1;ELSE SEC11<="0000";SEC22<="0000";MIN11<=MIN11+1;END IF;END IF;ELSIF(MIN11="1001")THENIF(SEC22<"0101")THENIF(SEC11<"1001")THENSEC11<=SEC11+1;ELSE SEC11<="0000";SEC22<=SEC22+1;END IF;ELSIF(SEC22="0101") THENIF(SEC11<"1001")THENSEC11<=SEC11+1;ELSE SEC11<="0000";SEC22<="0000";MIN11<="0000";MIN22<="0000";HOU R11<="0000";HOUR22<=HOUR22+1;END IF;END IF;END IF;END IF;END IF;ELSIF(HOUR22="0010")THEN -----20--23 hoursIF(MIN22<"0101")THENIF(MIN11<"1001")THENIF(SEC22<"0101")THENIF(SEC11<"1001")THENSEC11<=SEC11+1;ELSE SEC11<="0000";SEC22<=SEC22+1;END IF;ELSIF(SEC22="0101") THENIF(SEC11<"1001")THENSEC11<=SEC11+1;ELSE SEC11<="0000";SEC22<="0000";MIN11<=MIN11+1;END IF;END IF;ELSIF(MIN11="1001")THENIF(SEC22<"0101")THENIF(SEC11<"1001")THENSEC11<=SEC11+1;ELSE SEC11<="0000";SEC22<=SEC22+1;END IF;ELSIF(SEC22="0101") THENIF(SEC11<"1001")THENSEC11<=SEC11+1;ELSE SEC11<="0000";SEC22<="0000";MIN11<="0000";MIN22<=MIN22+1;END IF;END IF;END IF;ELSIF(MIN22="0101")THENIF(MIN11<"1001")THENIF(SEC22<"0101")THENIF(SEC11<"1001")THENSEC11<=SEC11+1;ELSE SEC11<="0000";SEC22<=SEC22+1;END IF;ELSIF(SEC22="0101") THENIF(SEC11<"1001")THENSEC11<=SEC11+1;ELSE SEC11<="0000";SEC22<="0000";MIN11<=MIN11+1;END IF;END IF;ELSIF(MIN11="1001")THENIF(SEC22<"0101")THENIF(SEC11<"1001")THENELSE SEC11<="0000";SEC22<=SEC22+1;END IF;ELSIF(SEC22="0101") THENIF(SEC11<"1001")THENSEC11<=SEC11+1;ELSE SEC11<="0000";SEC22<="0000";MIN11<="0000";MIN22<="0000";HOUR11<=HOUR11+1;END IF;END IF;END IF;END IF;ELSIF(HOUR11="0100")THEN------------------------------------20--23HOURSIF(MIN22<"0101")THENIF(MIN11<"1001")THENIF(SEC22<"0101")THENIF(SEC11<"1001")THENSEC11<=SEC11+1;ELSE SEC11<="0000";SEC22<=SEC22+1;END IF;ELSIF(SEC22="0101") THENIF(SEC11<"1001")THENSEC11<=SEC11+1;ELSE SEC11<="0000";SEC22<="0000";MIN11<=MIN11+1;END IF;END IF;ELSIF(MIN11="1001")THENIF(SEC22<"0101")THENIF(SEC11<"1001")THENSEC11<=SEC11+1;ELSE SEC11<="0000";SEC22<=SEC22+1;END IF;ELSIF(SEC22="0101") THENIF(SEC11<"1001")THENSEC11<=SEC11+1;ELSE SEC11<="0000";SEC22<="0000";MIN11<="0000";MIN22<=MIN22+1;END IF;END IF;END IF;ELSIF(MIN22="0101")THENIF(MIN11<"1001")THENIF(SEC22<"0101")THENIF(SEC11<"1001")THENELSE SEC11<="0000";SEC22<=SEC22+1;END IF;ELSIF(SEC22="0101") THENIF(SEC11<"1001")THENSEC11<=SEC11+1;ELSE SEC11<="0000";SEC22<="0000";MIN11<=MIN11+1;END IF;END IF;ELSIF(MIN11="1001")THENIF(SEC22<"0101")THENIF(SEC11<"1001")THENSEC11<=SEC11+1;ELSE SEC11<="0000";SEC22<=SEC22+1;END IF;ELSIF(SEC22="0101") THENIF(SEC11<"1001")THENSEC11<=SEC11+1;ELSE SEC11<="0000";SEC22<="0000";MIN11<="0000";MIN22<="0000";HOUR11<="0000";HOUR22<="0000";END IF;END IF;END IF;END IF;END IF;END IF;ELSE SEC11<="0000";SEC22<="0000";MIN11<="0000";MIN22<="0000";HOUR11<="0000";HOUR22<="0000";END IF;END IF;ELSE------------------------------------------进行手动调整IF(RES='0')THENIF(JIA_SEC1'EVENT AND JIA_SEC1='1')THEN------------------调整秒1IF(SEC11<"1001")THENSEC11<=SEC11+1;ELSE SEC11<="0000";END IF;END IF;IF(JIA_SEC2'EVENT AND JIA_SEC2='1')THEN------------------调整秒2IF(SEC22<"0101")THENSEC22<=SEC22+1;ELSE SEC22<="0000";END IF;END IF;IF(JIA_MIN1'EVENT AND JIA_MIN1='1')THEN------------------调整分1IF(MIN11<"1001")THENMIN11<=MIN11+1;ELSE MIN11<="0000";END IF;END IF;IF(JIA_MIN2'EVENT AND JIA_MIN2='1')THEN------------------调整分2IF(MIN22<"0101")THENMIN22<=MIN22+1;ELSE MIN22<="0000";END IF;END IF;IF(JIA_HOUR1'EVENT AND JIA_HOUR1='1')THEN----------------调整时1IF(HOUR11<"1001")THENHOUR11<=HOUR11+1;ELSE HOUR11<="0000";END IF;END IF;IF(JIA_HOUR2'EVENT AND JIA_HOUR2='1')THEN----------------调整时2IF(HOUR22<"0010")THENHOUR22<=HOUR22+1;ELSE HOUR22<="0000";END IF;END IF;ELSE SEC11<="0000";SEC22<="0000";MIN11<="0000";MIN22<="0000";HOUR11<="0000";HOUR22<="0000";END IF;END IF;END PROCESS;PROCESS(SEC11,SEC22,MIN11,MIN22)BEGINIF(MIN11="0000" AND MIN22="0000")THENIF(SEC11<"1010" AND SEC22<"0011")THENCOUT<='1';ELSE COUT<='0';END IF;ELSIF(MIN11="0000" AND MIN22="0011")THENIF(SEC11<"1010" AND SEC22<"0011")THENCOUT<='1';ELSE COUT<='0';END IF;ELSE COUT<='0';END IF;END PROCESS;HOUR2<=HOUR22;HOUR1<=HOUR11;SEC1<=SEC11;SEC2<=SEC22;MIN1<=MIN11;MIN2<=MIN22;END;。

基于fpga的多功能万年历

基于FPGA的多功能万年历1. 绪论现代科技在不断进步电子技术在不断发展,电子产品设计复杂程度也在不断增加。

而且电子产品的更新换代也越来越快,现在只靠传统的纯硬件的设计方法已经不能满足现代人们的要求。

EDA就是典型的硬件设计软件化的设计平台。

EDA是一项非常先进的技术,它有许多别的技术没有的优点:像单片机需要先画出硬件图再编写相对应的程序,而EDA是先编好程序再画图的,而且模块化的编程还会在软件中生成相应的封装元件,使最后画原理图变的更加简单;可以编好程序就直接仿真,程序出现错误可以在源文件内部直接改;并且设计好的总系统可以集成在一个体积小、功耗低、可靠性高的芯片上。

本设计采用VHDL语言,VHDL语言是一种全方位的数字系统设计和测试的硬件描述。

它支持原理图输入方法以及传统的文件输入方。

对于前者适用于小规模的数字集成电路,并进行模拟仿真。

而对于大规模的、复杂的系统,如果用纯原理图设计方法的话的,由于种种条件和环境制约,会导致工作效率底而且容易出错的等缺点。

在信息技术的今天,集成电路逐渐的趋向于系统化、微尺寸化、低功耗高集成化,因此,高密度可编程逻辑器件和VHDL越来越得到设计者的青睐。

它具有极强的描述能力,支持结构、数据流、行为三种描述形式的混合的设计方式,描覆盖面广、抽象能力强。

它能支持系统行为级、逻辑门级和寄存器传输级三个不同层次的设计。

在本设计中用到的FPGA是特殊的ASIC芯片,ASIC是一种带有逻辑处理的加速处理器的专用的系统集成电路。

它具有功耗低、速度快、集成度、设计制造成本低等优点。

本设计是研究基于FPGA的多功能万年历的设计,主要实现以下功能:能够显示年、月、日、时、分、秒,时间采用24小时制。

当时间不准确时还可以手动校准。

本系统还能实时的显示当前的温度,扩展了万年历的功能。

我采用的是数字温度传感器DS18B20和FPGA组成的温度采集系统,此系统具有硬件电路简单,抗干扰能力强等优点。

基于FPGA的多功能电子万年历设计

一、电子万年历简介 (1)二、电子万年历的工作原理 (1)三、多功能电子万年历各功能模块实现 (3)3.1时钟问题 (3)3.2电子万年历的控制系统 (5)3.3主控制模块maincontrol (6)3.4时间及其设置模块time_auto_and_set (7)3.3时间显示动态位选模块time_disp_select (12)3.4显示模块disp_data_mux (13)3.5秒表模块stopwatch (14)3.6日期显示与设置模块date_main (15)3.7闹钟模块alarmclock (17)3.8分频模块fdiv (18)四、附录 (20)附录一电子万年历系统的Verilog HDL语言程序 (20)一、电子万年历简介钟表的数字化给人们生产生活带来了极大的方便,而且大大地扩展了钟表原先的报时功能,诸如定时自动报警、按时自动打铃、时间程序自动控制、定时广播、定时启闭路灯等。

所有这些,都是以钟表数字化为基础的。

因此,研究电子万年历及扩大其应用,有非常现实的意义。

数字钟是一种用数字电路技术实现时、分、秒计时的装置,与机械式时钟相比具有更高的准确性和直观性,且无机械装置,具有更长的使用寿命,因此得到了广泛的使用。

电子万年历从原理上讲是一种典型的数字电路,其中包括了组合逻辑电路和时序电路。

本次所设计的电子万年历能显示日期、星期、时间,具有闹钟功能。

二、电子万年历的工作原理◆功能键用来选择不同的工作模式:时间正常显示功能、时间调整与显示、秒表功能、闹钟设置与查看、日期显示、日期调整与设置。

◆调整键1:主要用于闹钟设置、日期显示与调整、秒表、时间调整与设置中的位置选择按钮,与功能键配合使用。

●2号键功能模式,即时间调整与设置时,用作时、分、秒的移位,按一下,将会实现“时-分-秒”的依次移位,便于在特定位置进行调整;●4号键功能模式,即闹钟设置与查看时,同样用作时、分、秒的移位,按一下,将会实现“时-分-秒”的依次移位,便于在特定位置进行调整;●6号键功能模式,即日期调整与设置时,用作月、日的移位,按一下,将会实现“月-日”的依次移位,便于在特定位置进行调整。

基于FPGA的数字日历设计

基于FPGA的数字日历设计刘娟花;厉谨【摘要】A design scheme of digital calendar based on FPGA is introduced. VHDL programming language is used to de-sign the digital calendar,which has functions of displaying theyear,month,day,week,hour,minute,second,time adjust-ment and the Hourly chime. The input method of the scheme is in combination VHDL and block diagram. The design,compiling and simulation are completed under Quartus Ⅱ development environment. The designed file is accomplished and downloaded into FPGA chip EP1C3T144-3 to verify the results. The experiment results verify that the design scheme is workable,and can pro-vide references for the application of FPGA and the design of digital calendar.%介绍了一种基于FPGA的数字日历设计方案,采用VHDL语言编程设计了一个具有年、月、日、星期、时、分、秒计时显示功能,时间调整功能和整点报时功能的数字日历。

采用VHDL和原理图相结合的设计输入方式,在Quartus Ⅱ开发环境下完成设计、编译和仿真,并下载到FPGA芯片EP1C3T144-3上进行结果验证。

FPGA万年历报告

FPGA-CPLD原理及应用课程设计报告题目:基于SOPC设计万年历一、摘要设计从系统硬件出发,由CPU、总线、RAM、外接设备等构成SOPC Builder 的硬件系统,通过Nios II DE2开发的嵌入式软件编写并嵌入SOPC Builder的硬件中实现万年历的整体开发。

通过应用SoPC Builder开发工具,设计者可以摆脱传统的、易于出错的软硬件设计细节,从而达到加快项目开发、缩短开发周期、节约开发成本的目的并具有高集成度、设计灵活和可移植性较好。

关键词:万年历SOPC SOPC Builder Nios II DE2二、设计要求用Nios II DE2 开发板的LCD显示电子钟的日期和时间。

LCD分两行显示,第1行显示年、月、日;第2行显示时、分、秒。

用输入BUTTON[0]来控制LCD 行的修改,同时让Nios II DE2开发板上的绿色发光二极管亮灭来表示这个选择。

当BUTTON[0]按一下后,LEDG3亮,可以修改年、月和日的数字;再按一下BUTTON[0]后,LEDG3灭,可以修改时、分和秒的数字。

另外用输入按钮BUTTON[3]来控制日期和时间的修改,当处于日期修改方式时,每次按动一次BUTTON[3],依次更换“年”、“月”和“日”的修改。

当处于时间修改方式时,每次按动一次BUTTON[3],依次更换“时”、“分”和“秒”的修改。

修改对象被选中后,按动BUTTON[2]输入按钮可以增加显示的数字;按动BUTTON[1]输入按钮可以减少显示的数字。

三、设计内容1、按键信息BUTTON[3]:“年”、“月”、“日”或“时”、“分”、“秒”切换键BUTTON[2]:+键BUTTON[1]:-键BUTTON[0]:“年”、“月”、“日”与“时”、“分”、“秒”切换键显示信息LCD_Line1:显示“年”、“月”、“日”LCD_Line1:显示“时”、“分”、“秒”2、SOPC Builder 硬件建立SOPC Builder是在Quartus II里的SOPC Builder进行的,先建立工程,在SOPC Builder里添加硬件,包括CPU ,jtag_uart ,RAM,LCD,PIO,按键,LED,以及LCD_ON。

万年历的设计与实现

学校代码 ***** 学号 ******** 分类号 TP 密级公开本科毕业论文(设计)学院、系鄂尔多斯学院电子信息工程系专业名称自动化年级 2011 级学生姓名张文博指导教师王俊林2013年 6月 8 日万年历的设计与实现摘要本设计为一个多功能的万年历,具有年、月、日、时、分、秒计数显示功能,以24小时循环计数,具有校对功能。

本设计采用EDA 技术,以硬件描述语言verilog HDL和VHDL为系统逻辑描述手段设计文件,在Quartus II工具软件环境下,采用自顶向下的设计方法,由各个基本模块共同构建了一个基于KH-310开发工具的万年历。

系统主芯片采用EP1C12Q240C8,由主程序和BCD模块组成。

经编译和仿真所设计的程序,在可编程逻辑器件上下载验证,本系统通过控制能够完成年、月、日和时、分、秒的分别显示,由按键输入进行数字钟的校时、切换、扫描功能。

关键字:VHDL Verilog HDL EDA 万年历目录1绪论 (1)1.1选题背景 (1)1.2课题相关技术的发展 (1)1.3课题研究的必要性 (2)1.4课题研究的内容 (3)2 EDA技术 (4)2.1 EDA概述 (4)2.2什么是EDA (4)2.3 EDA的特点 (5)3 FPGA简介 (7)3.1 FPGA概述 (7)3.2 FPGA开发编程原理 (7)3.3FPGA基本结构 (8)3.4 FPGA系统设计流程 (10)4万年历设计方案 (14)4.1万年历的原理 (14)4.2 实验程序 (14)4.3 实验连接 (34)4.4 实验仿真与实现 (36)5实验结论与研究展望 (38)5.1实验结论 (38)5.2研究展望 (38)致谢 (39)参考文献 (40)内蒙古大学本科实训论文(设计)1绪论1.1选题背景20世纪末,数字电子技术飞速发展,有力的推动了社会生产力的发展和社会信息化的提高。

在其推动下,数字技术的应用已经渗透到人类生活的各个方面。

基于fpga的LCD显示万年历..

接着我的上一篇博文,终于完善好了,前几天太忙了,没有及时上传,呵呵,今天晚上刚比较早刚好凌晨,及时上传一下,实现了从0000---9999年的时钟,其实万年历和十万年历,都是差不多,等到地球能转到9999年再改代码也不迟,哈哈!!我这里有顶层和底层文件,顶层主要是调用模块和做按键处理,具体按键防抖动原理,参见偶的以前的博文,我写完这个万年历的代码,还没来得及优化,占用了太多了逻辑门,可以进一步优化。

大致思路是:第一次按下KEY1 的时候,所有计时停止,再按KEY1,年就闪烁,按下KEY2和KEY3 进行加减。

再按KEY1,月就闪烁,按下KEY2和KEY3 进行加减........依次为调年-月-日-星期-时分秒,再次按一下KEY1,进入正常运行模式。

好了先上顶层模块module LCD(rst,clk,rw,rs,en,data,key1,key2,key3);input clk,rst;input key1,key2,key3;output rs,en,rw;output [7:0] data;reg key1_out,key2_out,key3_out;wire clk,rst;wire rs,en,rw;wire [7:0] data;disp U1(.clk(clk),.rst(rst),.rs(rs),.en(en),.rw(rw),.data(data),.key1(key1_out),.key2(key2_out),.key3(key3_out));//=============key1,key2,key3 按键防抖动================// reg key1_reg1,key1_reg2;reg key2_reg1,key2_reg2;reg key3_reg1,key3_reg2;reg [31:0] count;always @(posedge clk)begincount<=count+1;if(count==500000)begincount<=0;key1_reg1<=key1;key2_reg1<=key2;key3_reg1<=key3;endkey1_reg2<=key1_reg1;key2_reg2<=key2_reg1;key3_reg2<=key3_reg1;key1_out <= key1_reg2 & (!key1_reg1);key2_out <= key2_reg2 & (!key2_reg1);key3_out <= key3_reg2 & (!key3_reg1);endendmodule底层模块:module disp(rst,clk,rw,rs,en,data,key1,key2,key3);input clk,rst;input key1,key2,key3;output rs,en,rw;output [7:0] data;reg rs,en_sel;reg [7:0] data;reg [14:0] year;reg [7:0] shi,fen,miao,month,dat;reg [31:0]count,count1; //LCD CLK 分频计数器reg lcd_clk;//2行32个数据寄存器reg [7:0]one_1,one_2,one_3,one_4,one_5,one_6,one_7,one_8,one_9,one_10,one_11,one_12,on e_13,one_14,one_15,one_16;reg [7:0]two_1,two_2,two_3,two_4,two_5,two_6,two_7,two_8,two_9,two_10,two_11,two_12,two_ 13,two_14,two_15,two_16;reg [7:0] next;parameter state0 =8'h00, //设置8位格式,2行,5*7 8'h38;state1 =8'h01, //整体显示,关光标,不闪烁8'h0C 闪烁8'h0estate2 =8'h02, //设定输入方式,增量不移位8'h06state3 =8'h03, //清除显示8'h01state4 =8'h04, //显示第一行的指令80Hstate5 =8'h05, //显示第二行的指令80H+40Hscan =8'h06,nul =8'h07;parameter data0 =8'h10, //2行32个数据状态data1 =8'h11,data2 =8'h12,data3 =8'h13,data4 =8'h14,data5 =8'h15,data6 =8'h16,data7 =8'h17,data8 =8'h18,data9 =8'h19,data10 =8'h20,data11 =8'h21,data12 =8'h22,data13 =8'h23,data14 =8'h24,data15 =8'h25,data16 =8'h26,data17 =8'h27,data18 =8'h28,data19 =8'h29,data20 =8'h30,data21 =8'h31,data22 =8'h32,data23 =8'h33,data24 =8'h34,data25 =8'h35,data26 =8'h36,data27 =8'h37,data28 =8'h38,data29 =8'h39,data30 =8'h40,data31 =8'h41;initialbegin//第一行显示年-月-日星期//Mon Tue Wed Thur Fri Sat Sunone_1<=" "; one_2<=" "; one_3<=" "; one_4<=" "; one_5<="-"; one_6<=" "; one_7<=" "; one_8<="-";one_9<=" ";one_10<=" ";one_11<=" ";one_12<=" ";one_13<=" ";one_14<="";one_15<=" ";one_16<=" ";//第二行显示Clock:00-00-00two_1<="C"; two_2<="l"; two_3<="o"; two_4<="c"; two_5<="k"; two_6<=":"; two_7<=" "; two_8<=" ";two_9<="-";two_10<=" ";two_11<=" ";two_12<="-";two_13<=" ";two_14<="";two_15<=" ";two_16<=" ";shi<=8'd0;fen<=8'd0;miao<=8'd0;end//======================产生LCD 时序脉冲=========================== always @ (posedge clk ) //获得LCD时钟begincount<=count+1;if(count==32'd50000)begincount<=32'b0;lcd_clk<=~lcd_clk;endend//=====================产生闪烁扫描时钟===========================reg [31:0] count2;reg scan_flag;always @ (posedge clk or negedge rst) //获得校准时间选中闪烁状态beginif(!rst)beginscan_flag<=1'b0;endelsebegincount2<=count2+1;if(count2==32'd1*******)begincount2<=32'b0;scan_flag<=~scan_flag;endendend//====================产生按键标志位================================= reg [3:0] flag;always @ (posedge clk or negedge rst )beginif(!rst)beginflag<=4'b0;endelseif(key1)beginflag<=flag+1'b1;if(flag==4'b1000)flag<=4'b0000;endend//===================计时以及校准=======================================reg[3:0] week;reg[7:0] dat_flag;always @ (posedge clk or negedge rst ) //时钟计数器beginif(!rst)begin //初始化显示第一行2012-05-19 Sat 第二行:Clock:00-00-00 shi<=8'b0;fen<=8'b0;miao<=8'b0;month<=8'd5;dat<=8'd19;year<=16'd2012;week<=4'd5;count1<=1'b0;two_7<= (shi/8'd10)+8'b00110000;two_8<= (shi%8'd10)+8'b00110000;two_10<=(fen/8'd10)+8'b00110000;two_11<=(fen%8'd10)+8'b00110000;two_13<=(miao/8'd10)+8'b00110000;two_14<=(miao%8'd10)+8'b00110000;one_1<=(year/16'd1000)+8'b00110000;one_2<=((year%16'd1000)/16'd100)+8'b00110000;one_3<=((year%16'd100)/8'd10)+8'b00110000;one_4<=(year%8'd10)+8'b00110000;one_6<=(month/8'd10)+8'b00110000;one_7<=(month%8'd10)+8'b00110000;one_9<=(dat/8'd10)+8'b00110000;one_10<=(dat%8'd10)+8'b00110000;endelsebegintwo_7<= (shi/8'd10)+8'b00110000;two_8<= (shi%8'd10)+8'b00110000;two_10<=(fen/8'd10)+8'b00110000;two_11<=(fen%8'd10)+8'b00110000;two_13<=(miao/8'd10)+8'b00110000;two_14<=(miao%8'd10)+8'b00110000;one_1<=(year/16'd1000)+8'b00110000;one_2<=((year%16'd1000)/16'd100)+8'b00110000;one_3<=((year%16'd100)/8'd10)+8'b00110000;one_4<=(year%8'd10)+8'b00110000;one_6<=(month/8'd10)+8'b00110000;one_7<=(month%8'd10)+8'b00110000;one_9<=(dat/8'd10)+8'b00110000;one_10<=(dat%8'd10)+8'b00110000;// 判断是否为31天的月份if(month==8'd1||month==8'd3||month==8'd5||month==8'd7||month==8'd8||month==8'd10|| month==8'd12)dat_flag<=8'd31;// 判断是否为30天的月份else if(month==8'd4||month==8'd6||month==8'd9||month==8'd11)dat_flag<=8'd30;// 判断是否为闰年和平年else if(month==8'd2)beginif(year % 4 == 0 && year % 100 != 0 || year % 400 == 0)dat_flag<=28;else dat_flag<=27;endcase (week)//星期//Mon Tue Wed Thu Fri Sat Sun4'b0000 : //1beginone_13<="M";one_14<="o";one_15<="n";end4'b0001 : //2beginone_13<="T";one_14<="u";one_15<="e";end4'b0010 : //3beginone_13<="W";one_14<="e";one_15<="d"; end4'b0011 : //4beginone_13<="T";one_14<="h";one_15<="u"; end4'b0100 : //5beginone_13<="F";one_14<="r";one_15<="i"; end4'b0101 : //6beginone_13<="S";one_14<="a";one_15<="t"; end4'b0110 : //7beginone_13<="S";one_14<="u";one_15<="n"; endendcasecase(flag)4'b0000 :beginen_sel<=1'b1;count1<=count1+1'b1;if(count1==32'd4*******)begincount1<=1'b0;miao<=miao+1'b1;if(miao==8'd59)beginmiao<=1'b0;fen<=fen+1'b1;if(fen==8'd59)beginfen<=1'b0;shi<=shi+1'b1;if(shi==8'd23)beginshi<=1'b0;dat<=dat+1'b1;week<=week+1'b1;if(week==4'b0110)week<=1'b1;if(dat==dat_flag)begindat<=8'd1;month<=month+1'b1;if(month==8'd12)beginmonth<=8'd1;year<=year+1'b1;if(year==16'd9999)year<=16'd0; //可以计1万年endendendendendendend4'b0001 :begincount1<=32'b0;//shi<=shi;fen<=fen;miao<=miao;year<=year;month<=month;dat<=dat;week<=week;end4'b0010 : //调年begincase(scan_flag)1'b0:begincount1<=32'b0; //shi<=shi;fen<=fen;miao<=miao;one_1<=8'd20;one_2<=8'd20;one_3<=8'd20;one_4<=8'd20;end1'b1:begincount1<=32'b0; //shi<=shi;fen<=fen;miao<=miao;endendcaseif(key2) //加数beginyear<=year+1'b1;if(year==16'd9999)year<=16'd0;endif(key3) //减数beginyear<=year-1'b1;if(year==16'd0)year<=16'd9999;endend4'b0011 : //调月begincase(scan_flag)1'b0:begincount1<=32'b0; //shi<=shi;fen<=fen;miao<=miao;one_6<=8'd20;one_7<=8'd20;end1'b1:begincount1<=32'b0; //shi<=shi;fen<=fen;miao<=miao;endcaseif(key2) //加数beginmonth<=month+1'b1;if(month==8'd12)month<=8'd0;endif(key3) //减数beginmonth<=month-1'b1;if(month==8'd0)month<=8'd12;endend4'b0100 : //调日begincase(scan_flag)1'b0:begincount1<=32'b0; //shi<=shi;fen<=fen;miao<=miao;one_9<=8'd20;one_10<=8'd20;end1'b1:begincount1<=32'b0; //shi<=shi;fen<=fen;miao<=miao;endendcaseif(key2) //加数begindat<=dat+1'b1;if(dat==dat_flag)dat<=8'd0;endif(key3) //减数dat<=dat-1'b1;if(dat==8'd0)dat<=dat_flag;endend4'b0101 : //调星期begincase(scan_flag)1'b0:begincount1<=32'b0; //shi<=shi;fen<=fen;miao<=miao;one_13<=8'd20;one_14<=8'd20;one_15<=8'd20;end1'b1:begincount1<=32'b0; //shi<=shi;fen<=fen;miao<=miao;endendcaseif(key2) //加数beginweek<=week+1'b1;if(week==4'd6)week<=4'd0;endif(key3) //减数beginweek<=week-1'b1;if(week==4'd0)week<=4'd7;endend4'b0110 : //调时begincase(scan_flag)begincount1<=32'b0; //shi<=shi;fen<=fen;miao<=miao;two_7<= 8'd20;two_8<= 8'd20;end1'b1:begincount1<=32'b0; //shi<=shi;fen<=fen;miao<=miao;endendcaseif(key2) //加数beginshi<=shi+8'b00000001;if(shi==8'd23)shi<=8'b0;endif(key3) //减数beginshi<=shi-8'b00000001;if(shi==8'b0)shi<=23;endend4'b0111 : //调分begincase(scan_flag)1'b0:begincount1<=32'b0; //shi<=shi;fen<=fen;miao<=miao;two_10<=8'd20;two_11<=8'd20;end1'b1:begincount1<=32'b0; //shi<=shi;fen<=fen;miao<=miao;endendcaseif(key2) //加数beginfen<=fen+8'b00000001;if(fen==8'd59)fen<=8'b0;endif(key3) //减数beginfen<=fen-8'b00000001;if(fen==8'b0)fen<=59;endend4'b1000 : //调秒begincase(scan_flag)1'b0:begincount1<=32'b0; //shi<=shi;fen<=fen;miao<=miao;two_13<=8'd20;two_14<=8'd20;end1'b1:begincount1<=32'b0; //shi<=shi;fen<=fen;miao<=miao;endendcaseif(key2) //加数beginmiao<=miao+8'b00000001;if(miao==8'd59)miao<=8'b0;endif(key3) //减数beginmiao<=miao-8'b00000001;if(miao==8'b0)miao<=59;endendendcaseendendalways @(posedge lcd_clk )begincase(next)state0 :begin rs<=1'b0; data<=8'h38; next<=state1; endstate1 :begin rs<=1'b0; data<=8'h0e; next<=state2; endstate2 :begin rs<=1'b0; data<=8'h06; next<=state3; endstate3 :begin rs<=1'b0; data<=8'h01; next<=state4; endstate4 :begin rs<=1'b0; data<=8'h80; next<=data0; end //显示第一行data0 :begin rs<=1'b1; data<=one_1; next<=data1 ; enddata1 :begin rs<=1'b1; data<=one_2; next<=data2 ; enddata2 :begin rs<=1'b1; data<=one_3; next<=data3 ; enddata3 :begin rs<=1'b1; data<=one_4; next<=data4 ; enddata4 :data5 :begin rs<=1'b1; data<=one_6; next<=data6 ; enddata6 :begin rs<=1'b1; data<=one_7; next<=data7 ; enddata7 :begin rs<=1'b1; data<=one_8; next<=data8 ; enddata8 :begin rs<=1'b1; data<=one_9; next<=data9 ; enddata9 :begin rs<=1'b1; data<=one_10; next<=data10 ; enddata10 :begin rs<=1'b1; data<=one_11; next<=data11 ; enddata11 :begin rs<=1'b1; data<=one_12; next<=data12 ; enddata12 :begin rs<=1'b1; data<=one_13; next<=data13 ; enddata13 :begin rs<=1'b1; data<=one_14; next<=data14 ; enddata14 :begin rs<=1'b1; data<=one_15; next<=data15 ; enddata15 :begin rs<=1'b1; data<=one_16; next<=state5 ; endstate5:begin rs<=1'b0;data<=8'hC0; next<=data16; end //显示第二行data16 :begin rs<=1'b1; data<=two_1; next<=data17 ; enddata17 :begin rs<=1'b1; data<=two_2; next<=data18 ; enddata18 :begin rs<=1'b1; data<=two_3; next<=data19 ; enddata19 :begin rs<=1'b1; data<=two_4; next<=data20 ; enddata20 :data21 :begin rs<=1'b1; data<=two_6; next<=data22 ; enddata22 :begin rs<=1'b1; data<=two_7; next<=data23 ; enddata23 :begin rs<=1'b1; data<=two_8; next<=data24 ; enddata24 :begin rs<=1'b1; data<=two_9; next<=data25 ; enddata25 :begin rs<=1'b1; data<=two_10; next<=data26 ; end data26 :begin rs<=1'b1; data<=two_11; next<=data27 ; end data27 :begin rs<=1'b1; data<=two_12; next<=data28 ; end data28 :begin rs<=1'b1; data<=two_13; next<=data29 ; end data29 :begin rs<=1'b1; data<=two_14; next<=data30 ; end data30 :begin rs<=1'b1; data<=two_15; next<=data31 ; end data31 :begin rs<=1'b1; data<=two_16; next<=scan ; endscan : //交替更新第一行和第二行数据beginnext<=state4;enddefault: next<=state0;endcaseendassign en=lcd_clk && en_sel;assign rw=1'b0;endmodule。

基于FPGA的万年历程序

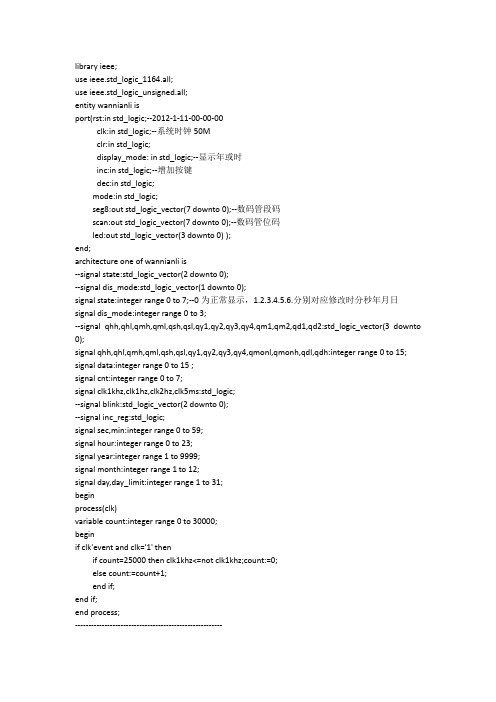

use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;entity wannianli isport(rst:in std_logic;--2012-1-11-00-00-00clk:in std_logic;--系统时钟50Mclr:in std_logic;display_mode: in std_logic;--显示年或时inc:in std_logic;--增加按键dec:in std_logic;mode:in std_logic;seg8:out std_logic_vector(7 downto 0);--数码管段码scan:out std_logic_vector(7 downto 0);--数码管位码led:out std_logic_vector(3 downto 0) );end;architecture one of wannianli is--signal state:std_logic_vector(2 downto 0);--signal dis_mode:std_logic_vector(1 downto 0);signal state:integer range 0 to 7;--0为正常显示,1.2.3.4.5.6.分别对应修改时分秒年月日signal dis_mode:integer range 0 to 3;--signal qhh,qhl,qmh,qml,qsh,qsl,qy1,qy2,qy3,qy4,qm1,qm2,qd1,qd2:std_logic_vector(3 downto 0);signal qhh,qhl,qmh,qml,qsh,qsl,qy1,qy2,qy3,qy4,qmonl,qmonh,qdl,qdh:integer range 0 to 15; signal data:integer range 0 to 15 ;signal cnt:integer range 0 to 7;signal clk1khz,clk1hz,clk2hz,clk5ms:std_logic;--signal blink:std_logic_vector(2 downto 0);--signal inc_reg:std_logic;signal sec,min:integer range 0 to 59;signal hour:integer range 0 to 23;signal year:integer range 1 to 9999;signal month:integer range 1 to 12;signal day,day_limit:integer range 1 to 31;beginprocess(clk)variable count:integer range 0 to 30000;beginif clk'event and clk='1' thenif count=25000 then clk1khz<=not clk1khz;count:=0;else count:=count+1;end if;end if;end process;-------------------------------------------------------variable cnte:integer range 0 to 30000000;beginif clk'event and clk ='1' thenif cnte=25000000 then clk1hz<=not clk1hz; cnte:=0;else cnte:=cnte+1;end if ;end if ;end process ;-----------------------------------------------------process (clk)variable cnt2:integer range 0 to 25000000;beginif clk'event and clk='1' thenif cnt2=12500000 then clk2hz<=clk2hz;cnt2:=0;else cnt2:=cnt2+1;end if ;end if ;end process;-----------------------------------------------------process(clk)variable cnnt:integer range 0 to 600000;beginif clk'event and clk='1' thenif cnnt=500000 then clk5ms<=clk5ms;cnnt:=0;else cnnt:=cnnt+1;end if ;end if ;end process;-----------------------------------------------------------------------------------------process(display_mode , clk1hz)beginif display_mode'event and display_mode='0' then dis_mode<=dis_mode+1;if dis_mode=1 thendis_mode<=0;end if;end if;end process;-------------------------------------------beginyear<=year;month<= month;day<=day;hour<=hour;min<=min;sec<=sec;end process;-----------------------------------------process(mode , clr,clk1hz)beginif clr='0' thenstate<=0;elsif mode'event and mode='0' thenstate<=state+1;if state=6 thenstate<=0;end if;end if ;end process;-----------------------------------------------------------------------------------process(clk1hz,state,dis_mode,inc,dec,clr,hour,sec,min,rst,year,month,day) beginif rst='0' thenyear<=2012;month<=1;day<=11;hour<=0;min<=0;sec<=0;--state<=0;--dis_mode<=0;elsif clr='0' thenhour<=23;min<=59;sec<=55;year<=2013;month<=1;day<=12;elsif clk1hz'event and clk1hz='1' thencase state iswhen 0 =>led<="0000";if((month=1)or(month=3)or(month=5)or(month=7)or(month=8)or(month=10)or(month=12)) thenday_limit<=31;end if;if month=2 then----if((year%4==0&&year%100!=0)||(year%400==0))if ((((year rem 4)=0) and ((year rem 100)/=0)) or ((year rem 400=0))) thenday_limit<=29;elseday_limit<=28;end if;end if;if((month=4)or(month=6)or(month=9)or(month=11)) thenday_limit<=30;end if;sec<=sec+1;if sec=59 thensec<=0;min<=min+1;if min=59 thenmin<=0;hour<=hour+1;if hour =23 thenhour<=0;day<=day+1;if day=day_limit thenday<=1;month<=month+1;if month=12 thenmonth<=1;year<=year+1;if year=9999 thenyear<=1;end if;end if;end if;end if;end if;end if;--if sec=59 then sec<=0;--if min=59 then min<=0;--if hour=23 then hour<=0;--else--hour<=hour+1;--end if;--else--min<=min+1;--end if;--else--sec<=sec+1;--end if;when 1=> led<="0001";if inc='0' thenif hour=23 thenhour<=0;else hour<=hour+1;end if;elsif dec='0' thenif hour=0 thenhour<=23;else hour<=hour-1;end if;end if;when 2=>led<="0010" ;if inc='0' thenif min=59 thenmin<=0;elsemin<=min+1;end if;elsif dec='0' thenif min=0 thenmin<=59;elsemin<=min-1;end if;end if;when 3=>led<="0011" ;if inc='0' thenif sec=59 thensec<=0;elsesec<=sec+1;end if;elsif dec='0' thenif sec=0 thensec<=59;elsesec<=sec-1;end if;end if;when 4 =>led<="0100";if inc='0' thenif year=9999 thenyear<=1;elseyear<=year+1;end if;elsif dec='0' thenif year=1990 thenyear<=2020;elseyear<=year-1;end if;end if;when 5=> led <="0101";if inc='0' thenif month=12 thenmonth<=1;elsemonth<=month+1;end if;elsif dec='0' thenif month=0 thenmonth<=12;elsemonth<=month-1;end if;end if;when 6 =>led <="0110";if inc='0' thenif day=day_limit thenday<=1;elseday<=day+1;end if;elsif dec='0' thenif day=0 thenday<=day_limit;elseday<=day-1;end if;end if;when others =>null;end case;end if;--end if;end process;----------------------------------------------------------------------process(sec)begincase sec iswhen 0|10|20|30|40|50 => qsl<=0;when 1|11|21|31|41|51 => qsl<=1;when 2|12|22|32|42|52 => qsl<=2;when 3|13|23|33|43|53 => qsl<=3;when 4|14|24|34|44|54 => qsl<=4;when 5|15|25|35|45|55 => qsl<=5;when 6|16|26|36|46|56 => qsl<=6;when 7|17|27|37|47|57 => qsl<=7;when 8|18|28|38|48|58 => qsl<=8;when 9|19|29|39|49|59 => qsl<=9;when others =>null;end case;case sec iswhen 0|1|2|3|4|5|6|7|8|9 => qsh<=0;when 10|11|12|13|14|15|16|17|18|19 => qsh<=1;when 20|21|22|23|24|25|26|27|28|29 => qsh<=2;when 30|31|32|33|34|35|36|37|38|39 => qsh<=3;when 40|41|42|43|44|45|46|47|48|49 => qsh<=4;when 50|51|52|53|54|55|56|57|58|59 => qsh<=5;when others =>null;end case;end process;--------------------------------------------------------------------process(min)begincase min iswhen 0|10|20|30|40|50 => qml<=0;when 1|11|21|31|41|51 => qml<=1;when 2|12|22|32|42|52 => qml<=2;when 3|13|23|33|43|53 => qml<=3;when 4|14|24|34|44|54 => qml<=4;when 5|15|25|35|45|55 => qml<=5;when 6|16|26|36|46|56 => qml<=6;when 7|17|27|37|47|57 => qml<=7;when 8|18|28|38|48|58 => qml<=8;when 9|19|29|39|49|59 => qml<=9;when others =>null;end case;case min iswhen 0|1|2|3|4|5|6|7|8|9 => qmh<=0;when 10|11|12|13|14|15|16|17|18|19 => qmh<=1;when 20|21|22|23|24|25|26|27|28|29 => qmh<=2;when 30|31|32|33|34|35|36|37|38|39 => qmh<=3;when 40|41|42|43|44|45|46|47|48|49 => qmh<=4;when 50|51|52|53|54|55|56|57|58|59 => qmh<=5;when others =>null;end case;end process;-----------------------------------------------------------------------process(hour)begincase hour iswhen 0|10|20 => qhl<=0;when 1|11|21 => qhl<=1;when 2|12|22 => qhl<=2;when 3|13|23 => qhl<=3;when 4|14 => qhl<=4;when 5|15 => qhl<=5;when 6|16 => qhl<=6;when 7|17 => qhl<=7;when 8|18 => qhl<=8;when 9|19 => qhl<=9;when others =>null;end case;case hour iswhen 0|1|2|3|4|5|6|7|8|9 => qhh<=0;when 10|11|12|13|14|15|16|17|18|19 => qhh<=1;when 20|21|22|23 => qhh<=2;when others => null;end case;end process;---------------------------------------------------------------process(year)beginqy1<=year/1000;qy2<=(year rem 1000)/100;qy3<=((year rem 1000)rem 100)/10;qy4<=((year rem 1000)rem 100) rem 10;--qy1<=year/1000;--qy2<=(year rem 1000)/100;--qy3<=((year-(year/1000)*1000)-((year-(year/1000)*1000)/100)*100)/10;--qy4<=((year rem 1000)rem 100)rem 10;end process;----------------------------------------------------------------process(month)beginqmonh<=month/10;qmonl<=month rem 10;end process;-----------------------------------------------------------------process(day)beginqdh<=day/10;qdl<=day rem 10;end process;----------------------------------------------------------------process(clk1khz)beginif clk1khz'event and clk1khz='1' thenif cnt=7 thencnt<=0;else cnt<=cnt+1;end if;end if;end process;----------------------------------------------------------process (cnt,qhh,qhl,qmh,qml,qsh,qsl,dis_mode)begincase dis_mode iswhen 0 => case cnt iswhen 0 => data<=qsl; scan<="11111110";when 1 => data<=qsh; scan<="11111101";when 2 => data<=15 ; scan<="11111111";when 3 => data<=qml; scan<="11110111";when 4 => data<=qmh; scan<="11101111";when 5 => data<=15; scan<="11111111";when 6 => data<=qhl; scan<="10111111";when 7 => data<=qhh; scan<="01111111";when others => null;end case;when 1=> case cnt iswhen 0 => data<=qdl; scan<="11111110";when 1 => data<=qdh; scan<="11111101";when 2 => data<=qmonl ; scan<="11111011";when 3 => data<=qmonh; scan<="11110111";when 4 => data<=qy4; scan<="11101111";when 5 => data<=qy3; scan<="11011111";when 6 => data<=qy2; scan<="10111111";when 7 => data<=qy1; scan<="01111111";when others =>null;end case;when others => null;end case;end process;----------------------------------------------------------------------------------process(data)begincase data iswhen 0 =>seg8<="11000000";when 1 =>seg8<="11111001";when 2 =>seg8<="10100100";when 3 =>seg8<="10110000";when 4 =>seg8<="10011001";when 5 =>seg8<="10010010";when 6 =>seg8<="10000010";when 7 =>seg8<="11111000";when 8 =>seg8<="10000000";when 9 =>seg8<="10010000";when others =>seg8<="11111111";end case ;end process;end;。

基于FPGA的多功能电子万年历毕业设计说明

毕业设计中期报告题目名称:基于FPGA的万年历设计院系名称:电气学院班级:应电学号:0832100589学生:梁启超指导教师:金凤2011年06月目录一、多功能电子万年历及FPGA简介 (1)1.1电子万年历的发展 (1)1.2 FPGA简介 (1)1.3 电子万年历的工作原理 (2)二、多功能电子万年历各功能模块实现 (4)2.1 时钟问题 (4)2.1.1 全局时钟 (4)2.1.2 门控时钟 (4)2.1.3 多级逻辑时钟 (5)2.1.4 波动式时钟 (5)2.2 电子万年历的控制系统 (6)2.3 主控制模块 maincontrol (7)2.4 时间及其设置模块 time_auto_and_set (8)2.2.1 时间模块 timepiece_main (8)2.2.2 时间设置模块 timeset (9)2.2.3 时间数据与时间设置数据多路选择模块 time_mux (11)2.3 时间显示动态位选模块 time_disp_select (13)2.4 显示模块 disp_data_mux (14)2.5 秒表模块 stopwatch (15)2.6 日期显示与设置模块 date_main (16)2.6.1 日期自动工作模块 autodate (17)2.6.2 日期设置模块 setdate (17)2.7 闹钟模块alarmclock (18)2.8 分频模块 fdiv (19)2.9 顶层模块图 (21)三、附录 (23)电子万年历系统的Verilog HDL语言程序设计部分代码 (23)3.1主控制模块 (23)3.2秒自动计时子模块 (25)3.3时间自动工作控制 (25)3.4时间数据与时间设置数据多路选择模块 (26)3.5时间及其设置模块 (27)3.6时间显示动态位选模块 (28)3.7秒表模块 (29)3.8分频模块 (29)参考文献 (31)1 引言1.1 选题意义钟表的数字化给人们生产生活带来了极大的方便,而且大扩展了钟表原先的报时功能,诸如定时自动报警、按时自动打铃、时间程序自动控制、定时广播、定时启闭路灯等。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

基于Verilog HDL的万年历设计与总结报告题目名称:基于Verilog HDL的万年历研究设计报告人:___________________________________________ 院系/年级/专业:________________________指导教师:________________________________________ 制作日期:_____________________________基于Verilog HDL的万年历摘要基于Verilog HDL的万年历设计,主要完成的任务是使用Verilog语言,在Quartus2上完成电路设计,程序开发模拟,基于功能是能够显示/修改年月日时分秒。

电路设计模块:分频、控制、时间显示调整、时分秒、年月日、显示控制、译码器。

各个模块完成不同的任务,合在一起就构成了万年历电路设计。

软件模拟直接在Quartus2上进行。

随着科学技术的发展,时间观念越来越重,但是老式的钟表以及日历等时间显示工具已不合时宜。

对此,数字钟表的设计有了用武之地。

基于Verilog的万年历设计,采用软件开发模拟,开发成本低,而且在功能设计上有了很大的灵活度。

同时,该设计的精度远远超过钟表,并且不需要维修。

综上所述,本设计具有设计方便、功能多样、电路简洁、成本低廉等优点。

符合社会发展趋势,前景广阔。