SPICE错误提示信息

AD06中英文错误提示对照表

Ⅰ、Error Reporting 错误报告A:Violations Associated with Buses 有关总线电气错误的各类型(共12项)◆bus indices out of range 总线分支索引超出范围◆Bus range syntax errors 总线范围的语法错误◆Illegal bus range values 非法的总线范围值◆Illegal bus definitions 定义的总线非法◆Mismatched bus label ordering 总线分支网络标号错误排序◆Mismatched bus/wire object on wire/bus 总线/导线错误的连接导线/总线◆Mismatched bus widths 总线宽度错误◆Mismatched bus section index ordering 总线范围值表达错误◆Mismatched electrical types on bus 总线上错误的电气类型◆Mismatched generics on bus (first index) 总线范围值的首位错误◆Mismatched generics on bus (second index) 总线范围值末位错误◆Mixed generics and numeric bus labeling 总线命名规则错误B:Violations Associated Components 有关元件符号电气错误(共20项)◆Component Implementations with duplicate pins usage 元件管脚在原理图中重复被使用◆Component Implementations with invalid pin mappings 元件管脚在应用中和PCB封装中的焊盘不符◆Component Implementations with missing pins in sequence 元件管脚的序号出现序号丢失◆Component contaning duplicate sub-parts 元件中出现了重复的子部分◆Component with duplicate Implementations 元件被重复使用◆Component with duplicate pins 元件中有重复的管脚◆Duplicate component models 一个元件被定义多种重复模型◆Duplicate part designators 元件中出现标示号重复的部分◆Errors in component model parameters 元件模型中出现错误的的参数◆Extra pin found in component display mode 多余的管脚在元件上显示◆Mismatched hidden pin component 元件隐藏管脚的连接不匹配◆Mismatched pin visibility 管脚的可视性不匹配◆Missing component model parameters 元件模型参数丢失◆Missing component models 元件模型丢失◆Missing component models in model files 元件模型不能在模型文件中找到◆Missing pin found in component display mode 不见的管脚在元件上显示◆Models found in different model locations 元件模型在未知的路径中找到◆Sheet symbol with duplicate entries 方框电路图中出现重复的端口◆Un-designated parts requiring annotation 未标记的部分需要自动标号◆Unused sub-part in component 元件中某个部分未使用C:violations associated with document 相关的文档电气错误(共10项)1conflicting constraints 约束不一致的2duplicate sheet symbol name 层次原理图中使用了重复的方框电路图3duplicate sheet numbers 重复的原理图图纸序号4missing child sheet for sheet symbol 方框图没有对应的子电路图5missing configuration target 缺少配置对象6missing sub-project sheet for component 元件丢失子项目7multiple configuration targets 无效的配置对象8multiple top-level document 无效的顶层文件9port not linked to parent sheet symbol 子原理图中的端口没有对应到总原理图上的端口10sheet enter not linked to child sheet 方框电路图上的端口在对应子原理图中没有对应端口D:violations associated with nets 有关网络电气错误(共19项)1adding hidden net to sheet 原理图中出现隐藏网络2adding items from hidden net to net 在隐藏网络中添加对象到已有网络中3auto-assigned ports to device pins 自动分配端口到设备引脚4duplicate nets 原理图中出现重名的网络5floating net labels 原理图中有悬空的网络标签6global power-objects scope changes 全局的电源符号错误7net parameters with no name 网络属性中缺少名称8net parameters with no value 网络属性中缺少赋值9nets containing floating input pins 网络包括悬空的输入引脚10nets with multiple names 同一个网络被附加多个网络名11nets with no driving source 网络中没有驱动12nets with only one pin 网络只连接一个引脚13nets with possible connection problems 网络可能有连接上的错误14signals with multiple drivers 重复的驱动信号15sheets containing duplicate ports 原理图中包含重复的端口16signals with load 信号无负载17signals with drivers 信号无驱动18unconnected objects in net 网络中的元件出现未连接对象19unconnected wires 原理图中有没连接的导线E:Violations associated with others有关原理图的各种类型的错误(3项)1No Error 无错误2Object not completely within sheet boundaries 原理图中的对象超出了图纸边框3Off-grid object原理图中的对象不在格点位置F:Violations associated with parameters 有关参数错误的各种类型1same parameter containing different types 相同的参数出现在不同的模型中2same parameter containing different values 相同的参数出现了不同的取值Ⅱ、Comparator 规则比较A:Differences associated with components 原理图和PCB上有关的不同(共16项) ◆Changed channel class name 通道类名称变化◆Changed component class name 元件类名称变化◆Changed net class name 网络类名称变化◆Changed room definitions 区域定义的变化◆Changed Rule 设计规则的变化◆Channel classes with extra members 通道类出现了多余的成员◆Component classes with extra members 元件类出现了多余的成员◆Difference component 元件出现不同的描述◆Different designators 元件标示的改变◆Different library references 出现不同的元件参考库◆Different types 出现不同的标准◆Different footprints 元件封装的改变◆Extra channel classes 多余的通道类◆Extra component classes 多余的元件类◆Extra component 多余的元件◆Extra room definitions 多余的区域定义B:Differences associated with nets 原理图和PCB上有关网络不同(共6项)◆Changed net name 网络名称出现改变◆Extra net classes 出现多余的网络类◆Extra nets 出现多余的网络◆Extra pins in nets 网络中出现多余的管脚◆Extra rules 网络中出现多余的设计规则◆Net class with Extra members 网络中出现多余的成员C:Differences associated with parameters 原理图和PCB上有关的参数不同(共3项)◆Changed parameter types 改变参数类型◆Changed parameter value 改变参数的取值◆Object with extra parameter 对象出现多余的参数。

spice仿真

spice仿真Spice仿真引言Spice (Simulation Program with Integrated Circuit Emphasis) 是一种电路仿真程序,它可以模拟各种电路的性能和行为。

历经多年的发展,Spice已经成为电子设计领域中最为常用和广泛认可的仿真工具之一。

本文将介绍Spice仿真的基本原理、应用领域以及使用方法,帮助读者更好地了解和应用这一强大的工具。

一、Spice仿真的基本原理Spice仿真基于电路的数学模型和电路分析方法,通过求解一组线性或非线性的代数和微分方程来模拟电路的行为。

Spice可以对各种类型的电路进行仿真,包括模拟电路、数字电路以及混合信号电路。

它考虑了电路中各个元件的电性能,并基于电流和电压的关系对电路进行建模和分析。

Spice程序需要用户提供电路的拓扑结构以及各个元件的参数。

通过这些输入,Spice可以根据预定义的电路分析方法和解算器来计算电路中各个节点和元件上的电压、电流以及功率等参数。

通过对电路的相应参数进行实时仿真和分析,Spice可以为设计者提供准确的电路行为信息,帮助他们对电路性能进行优化和改进。

二、Spice仿真的应用领域Spice仿真在电子设计和电路分析中有广泛的应用。

以下列举了几个常见的应用领域:1.模拟电路设计:Spice可以用于模拟电路的设计和验证,帮助设计者检查电路的性能和稳定性。

通过Spice仿真,设计者可以预测电路的频率响应、幅频特性以及相位延迟等参数,从而改进电路的设计方案。

2. 数字电路分析:Spice可以模拟数字电路中的逻辑门、触发器和时序电路等元件,帮助设计者验证电路的正确性和稳定性。

通过仿真结果,设计者可以找出可能存在的逻辑错误和电路延迟,并及时进行优化和调整。

3.射频电路分析:Spice也可以用于射频电路的仿真和分析。

射频电路中经常涉及到高频信号的传输和耦合问题,通过对射频电路进行Spice仿真,设计者可以预测电路中的信号衰减、失真以及噪声等问题,从而优化电路的性能。

SetupErrorGNDSpi...

SetupErrorGNDSpi...

解决之道

在用Protel99作仿真分析时出问题,提示如下:

Setup Error: GND Spice Reference Net (specified in Analog Options) is not in the schematic

我在网上找了很久,都没有找到有效的解决之道,后来自己无意中解决了,现跟大家分享。

画了一个电路图,设置了两个分析点(或者说网络标号,标号,观察点等等都是一个意思),一个为in,一个为out。

当然,GND接地也是设了的。

但是在运行仿真时出错,提示如上。

左看右看,发现out和GND处于短路状态,会不会跟这个有关?修改电路图,在out和GND之间加一电阻,使它们俩不再处于短路状态,重新运行访真,一次成功,问题解决!

现在看来,出现这个问题的跟本原因就是GND和分析点处于短路状态。

知道原因了,解决方法就有了:

第一种:把跟GND短路的分析点放到其它地方去,这是最好方法。

第二种:就像我前边所做的,在GND和分析点之间加一个元器件,如电阻或者保险丝等等。

祝大家进步!。

pspice暂态仿真+交流仿真辅导讲义 附常见错误提示

电路的暂态分析(TRAN分析)一、暂态分析语句暂态分析也称瞬态分析,是PSpice仿真分析中运用最多、最复杂、最耗时的分析。

暂态分析是一种非线性时域分析,它可以在暂态分析电源被设置后(或没有暂态分析电源,只是利用储能元件的初值),计算出电路的各输出变量(节点电压、支路电流等)随时间变化的规律。

在暂态分析中,需要计算暂态偏置点。

计算暂态偏置点的方法与计算直流偏置点的方法不同,直流偏置点被看作固定偏置点。

对于固定偏置点(无交流信号)的分析计算,电路电压的初值对于偏置点和线性参数没有影响,而且电路中的电容被看成开路,电感被看成短路。

但对于暂态偏置点(有交流小信号),在计算偏置点和非线性元件的小信号参数时,节点电压和支路电流的初值也考虑在内。

因此有初值的电容和电感也被看作是电路的一部分而保留下来。

暂态分析语句格式:输出偏置点数据(</OP>):.TRAN语句中带有可选项“/OP”后缀时,输出有关暂态偏置点的详细数据,这是因为在暂态分析时计算的偏置点数据和直流的数据是不同的,暂态分析的数据包含电路的初始条件。

输出分析数据的间隔(print-step value):打印或绘图输出的时间增量。

由于暂态分析是变步长计算,故输出的数据量是很大的,合理地选择输出分析数据的间隔能够使合适的数据输出到输出文件。

暂态分析终止时间(final-time-value):该时间即为暂态分析终止时间。

输出数据开始时间(<no-print value>):该项是输出数据(打印或绘图)的开始时间,即从此时间到“暂态分析终止时间”这段时间内输出数据。

若缺省该项,则程序默认开始时间为0.0。

注意,无论“输出数据开始时间”为多少,暂态分析都从时间为零开始,只不过在时间为零到输出数据开始时间这段时间间隔里没有数据输出而已,而且这段时间间隔内的暂态分析数据也没被存储起来。

分析步长上限(<step ceiling value>):该项是分析计算时的最大步长,该项缺省时其默认值为(final-time-value —no-print value)/50.0和print-step-value值中的较小值。

PSpice常见错误提示

电路描述文件和PSpice运行中常见错误提示如下:

提示

解释

“fs” is not a model parameter name

“fs”不是模型参数名

Missing primitive type

丢失数字原型

Mismatched parentheses

括号错配对

Can’t find library

错误—子电路X2中调用的ua741没有定义

Expression must fit on one line

表达式必须一行写完

Expression---use previously defined parameter only

表达式—应使用以前定义的参数

Invalid device

无效元器件

Invalid model type

无效模型类型

Invalid number

无效数字

Invalid specification

无效说明

Invalid sweep type

无效扫描类型

Less than 2 connection at node 3

节点3少于2个连接

Missing model

丢失模型

Missing node

丢失节点

Missing or invalid expression

找不到元件库

Circuit has errors ---run aborted see output files for details

电路有错误—运行中断,详情见输出文件

Duplicate name

重名

Error--- Node 2 is floating

错误--节点2是悬浮节点

Altium 的电路仿真功能

一、电路仿真功能介绍Altium Designer的混合电路信号仿真工具,在电路原理图设计阶段实现对数模混合信号电路的功能设计仿真,配合简单易用的参数配置窗口,完成基于时序、离散度、信噪比等多种数据的分析。

Altium Designer 可以在原理图中提供完善的混合信号电路仿真功能,除了对XSPICE 标准的支持之外,还支持对Pspice模型和电路的仿真。

Altium Designer中的电路仿真是真正的混合模式仿真器,可以用于对模拟和数字器件的电路分析。

仿真器采用由乔治亚技术研究所(GTRI)开发的增强版事件驱动型XSPICE仿真模型,该模型是基于伯克里SPICE3代码,并于且SPICE3f5完全兼容。

SPICE3f5模拟器件模型:包括电阻、电容、电感、电压/电流源、传输线和开关。

五类主要的通用半导体器件模型,如diodes、BJTs、JFETs、MESFETs和MOSFE Ts。

XSPICE模拟器件模型是针对一些可能会影响到仿真效率的冗长的无需开发局部电路,而设计的复杂的、非线性器件特性模型代码。

包括特殊功能函数,诸如增益、磁滞效应、限电压及限电流、s域传输函数精确度等。

局部电路模型是指更复杂的器件,如用局部电路语法描述的操作运放、时钟、晶体等。

每个局部电路都下在*.ckt文件中,并在模型名称的前面加上大写的X。

数字器件模型是用数字SimCode语言编写的,这是一种由事件驱动型XSPICE模型扩展而来专门用于仿真数字器件的特殊的描述语言,是一种类C语言,实现对数字器件的行为及特征的描述,参数可以包括传输时延、负载特征等信息;行为可以通过真值表、数学函数和条件控制参数等。

它来源于标准的XSPICE代码模型。

在SimCode中,仿真文件采用ASCII码字符并且保存成.TXT后缀的文件,编译后生成*.scb模型文件。

可以将多个数字器件模型写在同一个文件中。

Altium Designer 可实现如下功能:1、仿真电路建立及与仿真模型的连接AD 中由于采用了集成库技术,原理图符号中即包含了对应的仿真模型,因此原理图即可直接用来作为仿真电路,而99SE中的仿真电路则需要另行建立并单独加载各元器件的仿真模型。

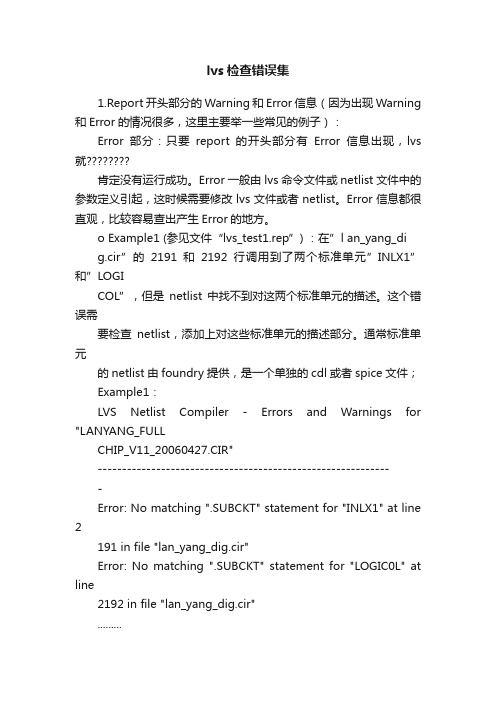

lvs检查错误集

lvs检查错误集1.Report开头部分的Warning和Error信息(因为出现Warning 和Error的情况很多,这里主要举一些常见的例子):Error部分:只要report的开头部分有Error信息出现,lvs 就肯定没有运行成功。

Error一般由lvs命令文件或netlist文件中的参数定义引起,这时候需要修改lvs文件或者netlist。

Error信息都很直观,比较容易查出产生Error的地方。

o Example1 (参见文件“lvs_test1.rep”) :在”l an_yang_dig.cir”的2191和2192行调用到了两个标准单元”INLX1”和”LOGICOL”,但是netlist中找不到对这两个标准单元的描述。

这个错误需要检查netlist,添加上对这些标准单元的描述部分。

通常标准单元的netlist由foundry提供,是一个单独的cdl或者spice文件;Example1:LVS Netlist Compiler - Errors and Warnings for "LANYANG_FULLCHIP_V11_20060427.CIR"-------------------------------------------------------------Error: No matching ".SUBCKT" statement for "INLX1" at line 2191 in file "lan_yang_dig.cir"Error: No matching ".SUBCKT" statement for "LOGIC0L" at line2192 in file "lan_yang_dig.cir"..................Warning部分:warning不会影响lvs的运行,但是经常会导致结果的不正确。

Quartus错误大全

Quartus常见错误分析1 Warning: VHDL Process Statement warning at random.vhd(18): signal reset is in statement, but is not in sensitivity list----没把singal放到process()中2 Warning: Found pins ing as undefined clocks and/or memory enables Info: Assuming node CLK is an undefined clock-=-----可能是说设计中产生的触发器没有使能端3 Error: VHDL Interface Declaration error in clk_gen.vhd(29): interface object "clk_scan" of mode out cannot be read. Change object mode to buffer or inout.------信号类型设置不对,out当作buffer来定义4 Error: Node instance "clk_gen1" instantiates undefined entity "clk_gen" -------引用的例化元件未定义实体--entity "clk_gen"5 Warning: Found 2 node(s) in clock paths which may be acting as ripple and/or gated clocks -- node(s) analyzed as buffer(s) resulting in clock skewInfo: Detected ripple clock "clk_gen:clk_gen1/clk_incr" as buffer Info: Detected ripple clock "clk_gen:clk_gen1/clk_scan" as buffer6 Warning: VHDL Process Statement warning at ledmux.vhd(15): signal or variable "dataout" may not be assigned a new in every possible path through the Process Statement. Signal or variable "dataout" holds its previous in every path with no new assignment, which may create a combinational loop in the current design.7 Warning: VHDL Process Statement warning at divider_10.vhd(17): signal "cnt" is read inside the Process Statement but isn''t in the Process Statement''s sensivitity list-----缺少敏感信号8 Warning: No clock transition on"counter_bcd7:counter_counter_clk/q_sig[3]" register9 Warning: Reduced register "counter_bcd7:counter_counter_clk/q_sig[3]" with stuck clock port to stuck GND10 Warning: Circuit may not operate. Detected 1 non-operational path(s) clocked by clock "class[1]" with clock skew larger than data delay. See Compilation Report for details.11 Warning: Circuit may not operate. Detected 1 non-operational path(s) clocked by clock "sign" with clock skew larger than data delay. See Compilation Report for details.12 Error: VHDL error at counter_clk.vhd(90): actual port "class" of mode "in" cannot be associated with formal port "class" of mode "out"------两者不能连接起来13 Warning: Ignored node in vector source file. Can''t find corresponding node name "class_sig[2]" in design.------没有编写testbench文件,或者没有编辑输入变量的值 testbench里是元件申明和映射14 Error: VHDL Binding Indication error at freqdetect_top.vhd(19): port "class" in design entity does not have std_logic_vector type that is specified for the same generic in the associated component---在相关的元件里没有当前文件所定义的类型15 Error: VHDL error at tongbu.vhd(16): can''t infer register for signal "gate" because signal does not hold its outside clock edge16 Warning: Found clock high time violation at 1000.0 ns on register "/fcounter/lpm_counter:temp_rtl_0/dffs[4]"17 Warning: Compiler packed, optimized or synthesized away node "temp[19]". Ignored vector source file node.---"temp[19]"被优化掉了18 Warning: Reduced register "gate~reg0" with stuck data_in port to stuck GND19 Warning: Design contains 2 input pin(s) that do not drive logic Warning: No output dependent on input pin "clk"Warning: No output dependent on input pin "sign"------输出信号与输入信号无关,20 Warning: Found clock high time violation at 16625.0 ns on register "/impulcomp/gate1"21 Error: VHDL error at impulcomp.vhd(19): can''t implement clock enable condition specified using binary operator "or"22 Error: VHDL Association List error at period_counter.vhd(38): actual parameter assigned to formal parameter "alarm", but formal parameter is not declared-------连接表错误,形参"alarm"赋值给实参,形参没定义,可能是形参与实参的位置颠倒了,规定形参在实参之前。

刚开始用PSPICE仿真的时候容易遇到的问题

刚开始用PSPICE仿真的时候容易遇到的问题刚开始用PSPICE仿真的时候容易遇到的问题刚开始用PSPICE仿真的时候容易遇到的问题真正的压力是自己给的,而不是别人;同样,你得到的成果也完全是你的,谁也拿不去。

——winston1:元件到哪里去找?元件当然是库里,但不是Capturer的库,而是PSpice的库。

最好的办法是重新建一个PROJECT,建的时候选择那个模拟和混合仿真的,然后建一个新的SCH,这时加载元件库的时候加载的是PSPICE的库而不是Capture的库了。

路径:Capture\Library\pspice。

重新加载库,重新Place元件。

直接从Capture中直接Copy过来,是不行的,那些元件都是没有模型的,RUN的时候会在该元件的一个角上出现一个绿色的小圆圈,点击它,会出现这样的错误提示:No PSpiceTemplate for U3, ignoring。

就是没模型。

下面是官方的说法,不动手做一正步还真不好理解:调用的器件必须有PSpice 模型。

首先,调用OrCAD软件本身提供的模型库,这些库文件存储的路径为Capture\Library\pspice,此路径中的所有器件都有提供PSpice模型,可以直接调用。

其次,若使用自己的器件,必须保证*.olb、*.lib 两个文件同时存在,而且器件属性中必须包含PSpice Template属性。

2:激励源怎么加?一般是这样,建一个GND,从这里引出一个电流源或者电压源,然后引出一个NET,和原理图上NET响应。

这样做的好处是不破坏原理图,而且看起来方便。

注意:PSPICE和CAPTURE的电源是不一样的,它长得和MULTISIM的差不多,是一个实体,而不是CAPTURE中的逻辑概念。

3:怎么老提示FLOATING PIN?SCH NET中一定要有一个网络地,并且其名称一定要为“0”。

如果没有,那么你连的再好,也总提示有N多引脚悬空。

SPICE错误提示信息

*ERROR*: UNKNOWN SUBCIRCUITNAME: SUBname

在电路程序描述中没有X语句调用的名为 在电路程序描述中没有 语句调用的名为SUBname 语句调用的名为 的子电路。 的子电路。

*ERROR*: .ENDS CARD MISSING

每一个子电路程序描述语句由一个一ENDS结束。在 结束。 每一个子电路程序描述语句由一个一 结束 整个程序结束的.END语句前,.ENDS个数与子电路 语句前, 整个程序结束的 语句前 个数与子电路 个数相同。 个数相同。

*ERROR*: NODE NUMBERS ARE MISSING

这个信息规定不符。例如,程序对于MOSFET规 的节点数与规定不符。例如,程序对于 规 定为4个节点 除了将衬底与地连接的情况外, 个节点, 定为 个节点,除了将衬底与地连接的情况外,都要 定义第四个节点。 定义第四个节点。

这个信息很少出现,它重复了前面的信息。 这个信息很少出现,它重复了前面的信息。对于 程序规定元件关键字以外的元件不能执行分析。 程序规定元件关键字以外的元件不能执行分析。

*ERROR*: NEGATIVE NODE NUMBER FOUND

这个信息跟随在输入语句后面, 这个信息跟随在输入语句后面,该语句出现了负 的节点号码。 的节点号码。

线性折线电源(PWL)的时间值系列必须是增长的。 的时间值系列必须是增长的。 线性折线电源 的时间值系列必须是增长的

§ 10. 3. 4 元器件模型错误

*ERROR*: VALUE IS MISSING OR IS NONPOSITIVE

这个信息跟随在元件定义语句之后, 这个信息跟随在元件定义语句之后,指出元件 没有赋值或元件值是负数。 没有赋值或元件值是负数。Spice程序对下列元件值 程序对下列元件值 规定必须是正数:电阻、电容、电感、 规定必须是正数:电阻、电容、电感、互感和受控 半导体器件的某些几何参数(如面积、宽度w、 源。半导体器件的某些几何参数(如面积、宽度 、 长度L等 出现负值时,也会引出这一错误信息。 长度 等)出现负值时,也会引出这一错误信息。

吉林大学pspice快速入门

附表1 几种主要的独立源描述

类型名 电源类型 参数设置 应用场合 举 例

DC

直流源

DC直流信号值

直流分析 (DC Sweep)

交流分析 (AC Sweep)

DC=5V

AC

交流源

AC 交流幅值

AC=10mV

SIN

调幅正弦信 号源

Voff直流偏置 瞬态分析 Vampl幅度(单峰 (tran) 值) Freq频率 TD 延迟时间 DF阻尼 因子 Phase相移

Transient 瞬态分析

程序自动设置

输出结果在输出文件*.out 中给出

Output Variable输出变量 Input Source输入电源名

输出变量是输出节点标号 或输出节点名称,必须与 电路输出文件定义一致。

Print Step打印间隔 Final Time 分析结束时间 No-Print Delay 初始延迟打印时间 Step Ceiling 开始保存分析数据的时间 Detailed Bias Pt. 给出详细输出偏置点的信 息

输出波形横轴为选中的扫描变量,扫描变量名必须 与电路已有的相符。 如:Voltage Source Name V1,V1必须存在 如:Model Name Q2N2222 BF(Q2N2222三极管必须存在 )

0

V1 BF

Bias Point Detail 静态工作点 分析 Transfer Function 小信号传递函 数分析

1.电路输入文件

• PSpice程序待仿真电路有两种输入方式,文本输入和图形输入。 文本输入方式是用PSpice编程语言编程,保存为扩展名cir (*.cir) 的文本文件。图形输入方式是在绘图编辑器(Schematic Editor) 中直接绘制电路图,计算机直接保存为扩展名sch图形文件。 • 绘图:打开Schematics窗口,从菜单Draw中选取Get New Part 命令,即打开元器件的符号库(*.slb),选取元器件符号图,放 (place)在绘图版面,连线,完成电路原理图绘制。 ①元件管脚不能重叠。 ②输出端不能悬空。任意节点对地要有直流通路。 ③元件旋转CTRL+R 镜像CTRL+F,在Edit菜单中,可以选 取对元件旋转和编辑的命令。 ④零伏电压源相当于电流表,串接电路中,求静态工作点。 ⑤文件名、路径必须英文,输入文件(*.cir)和(*.sch)必 须保存于英文路径和英文名称。

spice使用简介

(1)电路图的绘制。绘制电路图,激 励为电压脉冲源,选用Source.olb库 中的VPULSE。

分别键入下面参数的名称和数值: V1=0V(初始值) TR=0.4μ s(上升时间) V2=5V(幅值) TF=0.5μ s(下降时间) TD=0(延迟时间) PER=20ms(周期) PW=10ms(脉冲宽度)

表9-2 各标尺(快捷方式)的功能

快捷方式

名称

Display Freeze Peak Trough

含义

启动游标 关闭游标 定位光标在下一个最高点 定位光标在下一个最低点

Slope

Min Max

定位光标在下一个最大斜率点

定位光标在最低点 定位光标在最高点

PCommands…

(2)创建新仿真文件,注意分析参数设 置方法如图所示。

(3)执行PSpice分析程序,结果波形见图所示。 其中脉冲波是输入的矩形脉冲,输出电压 波形仍是矩形波,而电流波形是一个尖顶 波如图所示。此时R1=100 τ =RC=100×10×10-6=1ms<<T=20ms。

当R1=2K(或者大于2K)此时 τ=RC= 2000×10×10-6=20ms(或>20ms)

(2)扩库 :

(3)再入

下次再进入此Project的电路图界 面,须点界面左上角快捷键中 Open document键打开文档,按存 放此Project的路径查获。

2.画电路图

进行仿真: 选择PSpise / New Simulation Profile功能选项, 打开New Simulation对话框,在Name:栏输 入本仿真参数文件的名称RC。

用View\Output File 功能选项来观察执 行偏置点分析后的结果,

Altium Designer中的电路仿真92568

Altium Designer中的电路仿真今天看了下Altium Designer的电路仿真功能,发现它还是蛮强大的,按着help里面的文档《TU0106 Defining & running Circuit Simulation analyses.PDF》跑了一下,觉得还行,所以就把这个文档翻译下。

其中包含了仿真功能的介绍,元件仿真模型的添加与修改,仿真环境的设置,等等。

本人对SPICE仿真了解的不多,里面涉及到SPICE的文件如果有什么错误,欢迎提出!一、电路仿真功能介绍Altium Designer的混合电路信号仿真工具,在电路原理图设计阶段实现对数模混合信号电路的功能设计仿真,配合简单易用的参数配置窗口,完成基于时序、离散度、信噪比等多种数据的分析。

Altium Designer 可以在原理图中提供完善的混合信号电路仿真功能,除了对XSPICE 标准的支持之外,还支持对Pspice模型和电路的仿真。

Altium Designer中的电路仿真是真正的混合模式仿真器,可以用于对模拟和数字器件的电路分析。

仿真器采用由乔治亚技术研究所(GTRI)开发的增强版事件驱动型XSPICE仿真模型,该模型是基于伯克里SPICE3代码,并于且SPICE3f5完全兼容。

SPICE3f5模拟器件模型:包括电阻、电容、电感、电压/电流源、传输线和开关。

五类主要的通用半导体器件模型,如diodes、BJTs、JFETs、MESFETs和MOSFETs。

XSPICE模拟器件模型是针对一些可能会影响到仿真效率的冗长的无需开发局部电路,而设计的复杂的、非线性器件特性模型代码。

包括特殊功能函数,诸如增益、磁滞效应、限电压及限电流、s域传输函数精确度等。

局部电路模型是指更复杂的器件,如用局部电路语法描述的操作运放、时钟、晶体等。

每个局部电路都下在*.ckt文件中,并在模型名称的前面加上大写的X。

数字器件模型是用数字SimCode语言编写的,这是一种由事件驱动型XSPICE模型扩展而来专门用于仿真数字器件的特殊的描述语言,是一种类C语言,实现对数字器件的行为及特征的描述,参数可以包括传输时延、负载特征等信息;行为可以通过真值表、数学函数和条件控制参数等。

关于Pspice仿真中出错时的问题对策

关于Pspice仿真中出错时的问题对策:

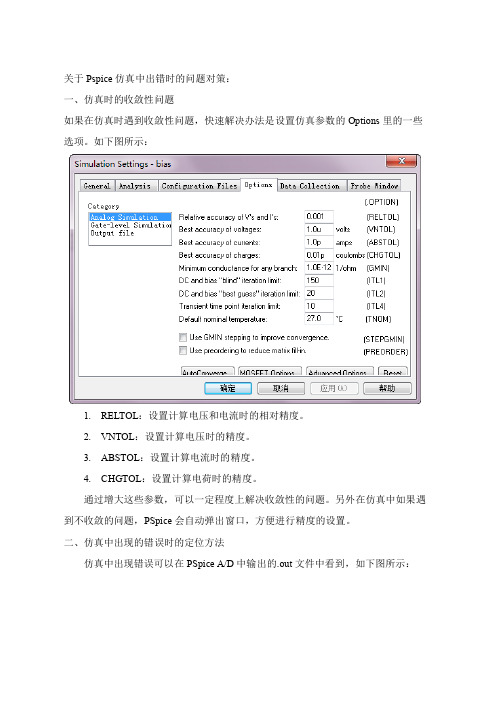

一、仿真时的收敛性问题

如果在仿真时遇到收敛性问题,快速解决办法是设置仿真参数的Options里的一些选项。

如下图所示:

1.RELTOL:设置计算电压和电流时的相对精度。

2.VNTOL:设置计算电压时的精度。

3.ABSTOL:设置计算电流时的精度。

4.CHGTOL:设置计算电荷时的精度。

通过增大这些参数,可以一定程度上解决收敛性的问题。

另外在仿真中如果遇到不收敛的问题,PSpice会自动弹出窗口,方便进行精度的设置。

二、仿真中出现的错误时的定位方法

仿真中出现错误可以在PSpice A/D中输出的.out文件中看到,如下图所示:

通过点击窗口左侧的也可以打开看到.out文件。

图中可以看见文件中显示了元件的网表,每一个元件的引脚都有相应的编号,L1的有N00166和N00180。

通过

这些提示就可以定位出错的元件,以便排除错误。

三、元件库的设置

有时在仿真时使用了非软件自带元件二在仿真时,出现了类似ERROR

–Subcircuit XXX used by X_U1 is undefined.的错误。

这个错误出现的原因是原理图中

所调用的元器件的PSpice模型没有添加到Library路径中。

解决方法是在PSpice仿真设置中的Configuration Files界面下的Library进行配置添加。

如下图所示:

这就是我在仿真中学到的一些知识,在这与大家分享。

有错误的地方欢迎指正。

pispice使用方法

1 PSPICE软件的简介与使用1.1 PSPICE的发展与现状根据实际电路(或系统)建立模型,通过对模型的计算机分析、研究和试验以达到研制和开发实际电路(或系统)的目的,这一过程,称为计算机仿真(Simulation)的高效、高精度、高经济性和高可靠性,因此倍受业界喜爱。

在设计或分析各类开关电源时,计算机仿真起了重要的作用。

数字仿真手段可用以检验设计的系统是否满足性能要求。

应用数字仿真可以减少电路实验的工作,与电路实验相比,计算机仿真所需时间要少得多,并可以更全面、更完整地进行,以期改进设计质量。

目前流行的许多著名软件如PSpice、Icape等,它们各自都有其本身的特点。

而随着Windows的全面普及,PSpice推出了Windows版本,用户不用象DOS版那样输入数据网表文件,而是图形化,只需选择相应的元器件的图标代号,然后使用线连接就可以自动生成数据网表文件,整个过程变得直观简单。

因此它已广泛应用于电力电子电路(或系统)的分析中。

用于模拟电路仿真的SPICE(Simulation Program with Integrated Circuit Emphasis)软件于1972年由美国加州大学伯克利分校的计算机辅助设计小组利用FORTRAN语言开发而成,主要用于大规模集成电路的计算机辅助设计。

SPICE 的正式实用版SPICE 2G在1975年正式推出,但是该程序的运行环境至少为小型机。

1985年,加州大学伯克利分校用C语言对SPICE软件进行了改写,1988年SPICE被定为美国国家工业标准。

与此同时,各种以SPICE为核心的商用模拟电路仿真软件,在SPICE的基础上做了大量实用化工作,从而使SPICE成为最为流行的电子电路仿真软件。

PSPICE则是由美国Microsim公司在SPICE 2G版本的基础上升级并用于PC 机上的SPICE版本,其中采用自由格式语言的5.0版本自80年代以来在我国得到广泛应用,并且从6.0版本开始引入图形界面。

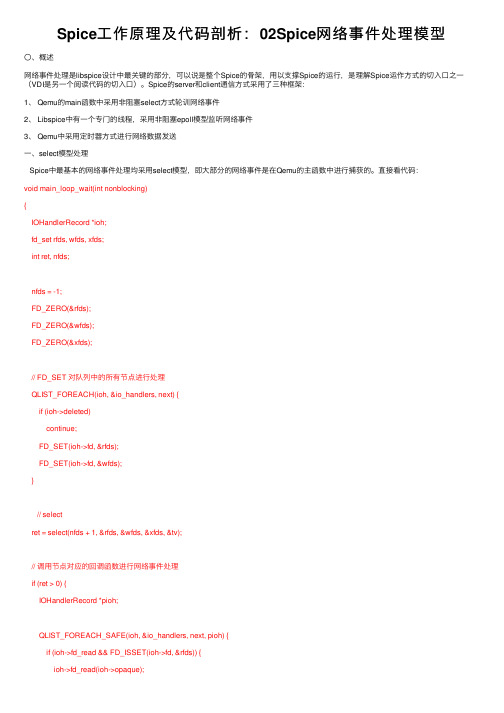

Spice工作原理及代码剖析:02Spice网络事件处理模型

Spice⼯作原理及代码剖析:02Spice⽹络事件处理模型〇、概述⽹络事件处理是libspice设计中最关键的部分,可以说是整个Spice的⾻架,⽤以⽀撑Spice的运⾏,是理解Spice运作⽅式的切⼊⼝之⼀(VDI是另⼀个阅读代码的切⼊⼝)。

Spice的server和client通信⽅式采⽤了三种框架:1、 Qemu的main函数中采⽤⾮阻塞select⽅式轮训⽹络事件2、 Libspice中有⼀个专门的线程,采⽤⾮阻塞epoll模型监听⽹络事件3、 Qemu中采⽤定时器⽅式进⾏⽹络数据发送⼀、select模型处理Spice中最基本的⽹络事件处理均采⽤select模型,即⼤部分的⽹络事件是在Qemu的主函数中进⾏捕获的。

直接看代码:void main_loop_wait(int nonblocking){IOHandlerRecord *ioh;fd_set rfds, wfds, xfds;int ret, nfds;nfds = -1;FD_ZERO(&rfds);FD_ZERO(&wfds);FD_ZERO(&xfds);// FD_SET 对队列中的所有节点进⾏处理QLIST_FOREACH(ioh, &io_handlers, next) {if (ioh->deleted)continue;FD_SET(ioh->fd, &rfds);FD_SET(ioh->fd, &wfds);}// selectret = select(nfds + 1, &rfds, &wfds, &xfds, &tv);// 调⽤节点对应的回调函数进⾏⽹络事件处理if (ret > 0) {IOHandlerRecord *pioh;QLIST_FOREACH_SAFE(ioh, &io_handlers, next, pioh) {if (ioh->fd_read && FD_ISSET(ioh->fd, &rfds)) {ioh->fd_read(ioh->opaque);}if (ioh->fd_write && FD_ISSET(ioh->fd, &wfds)) {ioh->fd_write(ioh->opaque);}}}qemu_run_all_timers();}以上代码遵循了select模型的基本处理步骤:FD_SET、select、process,所以⾮常容易理解。

如何使用LTspice为LED驱动器生成波特图

如何使用LTspice为LED驱动器生成波特图拥有(昂贵)设备和相应经验的工厂专家应进行适当的控制回路相位和增益测量。

对于那些无法访问其中一个或任何一个的人,还有另一种选择。

闭环增益和相位图是用于确定开关稳压器中控制环路稳定性的常用工具。

正确进行增益和相位测量时,需要访问和熟悉精美的网络分析仪。

测量包括断开控制环路、注入噪声以及在频率扫描中测量所得增益和相位(参见图 1)。

这种测量控制回路的做法很少应用于 LED 驱动器。

LED 驱动器控制环路相位和增益测量需要不同的方法(参见图 1)——偏离典型的电阻分压器路径到 GND 稳压器注入和测量点。

在这两种情况下,台式控制环路相位和增益测量是保证稳定性的最佳方式,但并非每个工程师都可以轻松获得所需的设备并访问经验丰富的工厂应用程序团队。

这些工程师是做什么的?一种选择是构建 LED 驱动器并查看它如何响应瞬变。

瞬态响应观察需要应用板和更常见的台式设备。

瞬态分析的结果缺少波特图基于频率的增益和相位数(可用于保证稳定性),但它们可以作为一般控制回路稳定性和速度的指标。

大信号瞬态可用于检查绝对偏差和系统响应时间。

瞬态干扰的形状表示相位或增益裕度,因此可用于了解一般环路稳定性。

例如,临界阻尼响应可能表示 45°到 60°的相位裕度。

或者,瞬态期间的大尖峰可能表明需要更多的 COUT 或更快的环路。

较长的建立时间可能表明需要加快环路的带宽(和交叉频率)。

这些相对简单的系统检查能够对开关稳压器的控制环路进行动态表征,但需要增益和相位波特图进行更深入的分析。

LTspice 仿真可用于在组装或制造电路之前生成开关稳压器输出瞬态和波特图。

这有助于粗略了解控制回路的稳定性——补偿元件选择和输出电容器尺寸的起点。

根据Mi ddlebrook 在 1975 年的最初建议使用 LTspice 的过程有充分的记录(请参阅“ LTspice:生成 SMPS 波特图的基本步骤”)。

te unexpected error

"Unexpected error" 是一个通用的错误提示,表示在程序运行过程中遇到了一个未被预期或未被特定处理的问题。

这种问题可能源于多种原因,包括但不限于以下几种情况:

1.程序文件受损:如“添加或删除程序”的相关文件受损,这可能导致系统无法正常运行某些功能。

2.系统或软件更新问题:例如,Windows XP Service Pack 2中的某些补丁可能与系统不兼容,或者某些记录硬件的文件可能已丢失。

3.硬件问题:如内存松动或接触不良,或者主板上的散热芯片接触不好,这些都可能导致系统出现错误。

4.代码或逻辑错误:在程序设计或开发过程中,可能存在一些难以避免的编码错误或逻辑问题,这些问题在特定条件下可能被触发,导致程序崩溃

或报错。

为了解决“unexpected error”,可以尝试以下方法:

1.检查系统日志:查看系统或应用程序的日志,了解错误发生的具体环境和条件,有助于定位问题。

2.更新或修复软件:如果是某个特定软件的错误,尝试更新到最新版本或修复安装可能有助于解决问题。

3.检查硬件:如果怀疑是硬件问题,可以尝试重新插拔内存条,检查散热设备等,确保硬件工作正常。

4.代码审查和优化:如果是自己开发的程序出现这个错误,进行代码审查,增强代码的健壮性,添加错误处理机制等可以帮助减少这类错误的发生。

5.寻求专业帮助:如果以上方法都不能解决问题,可能需要寻求专业的技术支持或咨询相关领域的专家。

AltiumDesigner中地电路仿真

Altium Designer中的电路仿真今天看了下Altium Designer的电路仿真功能,发现它还是蛮强大的,按着help里面的文档《TU0106 Defining & running Circuit Simulation analyses.PDF》跑了一下,觉得还行,所以就把这个文档翻译下。

其中包含了仿真功能的介绍,元件仿真模型的添加与修改,仿真环境的设置,等等。

本人对SPICE仿真了解的不多,里面涉及到SPICE的文件如果有什么错误,欢迎提出!一、电路仿真功能介绍Altium Designer的混合电路信号仿真工具,在电路原理图设计阶段实现对数模混合信号电路的功能设计仿真,配合简单易用的参数配置窗口,完成基于时序、离散度、信噪比等多种数据的分析。

Altium Designer 可以在原理图中提供完善的混合信号电路仿真功能,除了对XSPICE 标准的支持之外,还支持对Pspice模型和电路的仿真。

Altium Designer中的电路仿真是真正的混合模式仿真器,可以用于对模拟和数字器件的电路分析。

仿真器采用由乔治亚技术研究所(GTRI)开发的增强版事件驱动型XSPICE仿真模型,该模型是基于伯克里SPICE3代码,并于且SPICE3f5完全兼容。

SPICE3f5模拟器件模型:包括电阻、电容、电感、电压/电流源、传输线和开关。

五类主要的通用半导体器件模型,如diodes、BJTs、JFETs、MESFETs和MOSFETs。

XSPICE模拟器件模型是针对一些可能会影响到仿真效率的冗长的无需开发局部电路,而设计的复杂的、非线性器件特性模型代码。

包括特殊功能函数,诸如增益、磁滞效应、限电压及限电流、s域传输函数精确度等。

局部电路模型是指更复杂的器件,如用局部电路语法描述的操作运放、时钟、晶体等。

每个局部电路都下在*.ckt文件中,并在模型名称的前面加上大写的X。

数字器件模型是用数字SimCode语言编写的,这是一种由事件驱动型XSPICE模型扩展而来专门用于仿真数字器件的特殊的描述语言,是一种类C语言,实现对数字器件的行为及特征的描述,参数可以包括传输时延、负载特征等信息;行为可以通过真值表、数学函数和条件控制参数等。

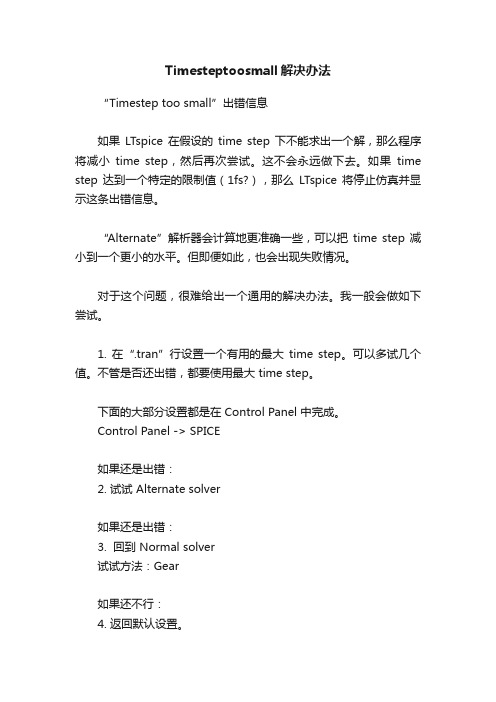

Timesteptoosmall解决办法

Timesteptoosmall解决办法“Timestep too small”出错信息如果LTspice 在假设的time step 下不能求出一个解,那么程序将减小time step,然后再次尝试。

这不会永远做下去。

如果time step 达到一个特定的限制值(1fs?),那么LTspice 将停止仿真并显示这条出错信息。

“Alternate”解析器会计算地更准确一些,可以把time step 减小到一个更小的水平。

但即便如此,也会出现失败情况。

对于这个问题,很难给出一个通用的解决办法。

我一般会做如下尝试。

1. 在“.tran”行设置一个有用的最大time step。

可以多试几个值。

不管是否还出错,都要使用最大 time step。

下面的大部分设置都是在 Control Panel 中完成。

Control Panel -> SPICE如果还是出错:2. 试试 Alternate solver如果还是出错:3. 回到 Normal solver试试方法:Gear如果还不行:4. 返回默认设置。

尝试在“.TRAN”设置中使用“startup”。

如果还不行:5. 返回默认设置。

试着设置 Gmin,但不要小于 1e-10还不行:6. 恢复默认设置。

试设置 Reltol=0.01还不行:7. 恢复默认设置。

试着用6 和7 的组合(罗亩按,此处不明白是何意,仍设为Reltol=0.01?)还不行:8. 恢复默认设置。

试设置 .options Tseed=maxtimestep/10还不行:9. 有元件的真实值吗?在电容器(ESR)或电感器中串一个电阻器。

还不行:10. 试设置 .ic 和 .nodeset还不行:11. 试设置 .options gshunt=... 和/或 .options cshunt=...还不行:12. 再问问别人吧。

:)不要低估了第11条提示。

下面是我在一次仿真中做的最多的一次设置复位 SPICE 设置:Control Panel -> SPICE在 Control Panel 中设置特殊 GMIN 选项如下:Control Panel -> Hacks Add GMIN across current sources设置一个最大 time step。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

*WARNING*: THE VALUE OF LAMBDA FOR MOSFET MODE, MODname,IS UNUSUALLY LARGE AND MIGHT , CAUSE NONCONVERGENCE

MOSFET模型的值大于正常值,可能引起不收敛。 模型的值大于正常值,可能引起不收敛。 模型的值大于正常值

*ERROR*: UNKNOWN SUBCIRCUITNAME: SUBname

在电路程序描述中没有X语句调用的名为 在电路程序描述中没有 语句调用的名为SUBname 语句调用的名为 的子电路。 的子电路。

*ERROR*: .ENDS CARD MISSING

每一个子电路程序描述语句由一个一ENDS结束。在 结束。 每一个子电路程序描述语句由一个一 结束 整个程序结束的.END语句前,.ENDS个数与子电路 语句前, 整个程序结束的 语句前 个数与子电路 个数相同。 个数相同。

子电路定义两个终端节点有相同号码。 子电路定义两个终端节点有相同号码。

*ERROR*:NONPOSITIVE NODE NUMBER FOUND IN SUBCIRCUIT DEFINITION

子电路所有的节点号必须为正。 子电路所有的节点号必须为正。

*ERROR*: SUBCIRCUITNAME ห้องสมุดไป่ตู้ISSING

在子电路定义中包含一个X调用语句, 在子电路定义中包含一个 调用语句,该语句调用的 调用语句 是该子电路。 是该子电路。

*WARNING*s ABOVE LINE NOT ALLOWED WITHIN SUBCIRCUIT-IGNORED

子电路里不允许有上一行语句,可以忽略。 子电路里不允许有上一行语句,可以忽略。

这个信息后面跟随一个以数字开始的输入语句。 这个信息后面跟随一个以数字开始的输入语句。 这可能是由于语句太长,同一语句另起一行 同一语句另起一行, 这可能是由于语句太长 同一语句另起一行,忘记加 一个+ 这是一个致命错误。 一个+号,这是一个致命错误。

*ERROR*: unknown data card: Name

*ERROR*:UNKNOWN SOURCE FUNCTION: source_function

时变电源的功能应该指定,检查时变电源的类型和 时变电源的功能应该指定, 缩写。 缩写。

*ERROR*:ELEMENT Name PIECEWISE LINEAR : SOURCE TABLE NOTINCREASING IN TIME

*WARNING*: IN DIODE MODEL MODname IBV INCREASED TO value TORESOLVE INCOMPATIBILITY WITH SPECIH IED IS

二极管模型中的参数IBV增长到 增长到value值时,与给定的 值时, 二极管模型中的参数 增长到 值时 is参数不兼容。 参数不兼容。 参数不兼容

传输线的延迟时间TD或频率值 必须给出其中一个。 传输线的延迟时间 或频率值F必须给出其中一个。 或频率值 必须给出其中一个

§ 10. 3. 3 电源元件的错误

*ERROR*: VOLTAGE SOURCE NOT FOUND ON ABOVE LINE

电流受控源需要的控制电压源名字没有给出。 电流受控源需要的控制电压源名字没有给出。电 流受控源的节点号后面必须跟随控制电源的名字。 流受控源的节点号后面必须跟随控制电源的名字。

在这个模型中没有这一参数的合法定义。 在这个模型中没有这一参数的合法定义。

*WARNING*: MINIMUM BASE RESISTANCE (RBM) IS LESS THAN TOTAL (RB) FOR MODEL MODname RBM SET EQUAL TO RB

基极电阻的最小值RBM应小于 应小于RB,模型中 模型中RBM设置 基极电阻的最小值 应小于 模型中 设置 为等于RB。 为等于 。

*ERROR*: .END CARD MISSING

这个信息告诉你,遗漏了 语句。 这个信息告诉你,遗漏了.END语句。 语句

*ERROR*: ILLEGAL NUMBER SCAN STOPPED AT COLUMN number

这个信息语句给出的数字超出了PSpice程序的规 程序的规 这个信息语句给出的数字超出了 定,绝对值在1035-1031之间。 绝对值在 之间。

*WARNING*:ATTEMPT TO REFERENCE UNDEFINED NODE number-NODE RESET TO 0

试将不确定的参考节点(number)重新设置为 。 重新设置为0。 试将不确定的参考节点 重新设置为

§ 10. 3. 6 子电路定义错误

*ERROR*:SUBCIRCUTT DEFBYTFION DUPLICATES NODE number

互感的偶合系数超过了1.0,程序继续分析,自动 互感的偶合系数超过了 ,程序继续分析, 将系数设置为1.0。 将系数设置为 。

*ERROR*: ZO MUST BE SPECIFIED

传输线的阻抗特性值必须给出. 传输线的阻抗特性值必须给出.这是一个致命 错误。 错误。

*ERROR*: EITHER TD OR F MUST BE SPECIFIED

这个信息指出:语句给出的元件名字的第一个 这个信息指出: 字母,必须是程序规定的关键字。 字母,必须是程序规定的关键字。也有可能在同一 电路里同一元件名用了两次。 电路里同一元件名用了两次。

*ERROR*: ELEMENT TYPE NOT YET IMPLEMENTED

这个信息很少出现,它重复了前面的信息。 这个信息很少出现,它重复了前面的信息。对于 程序规定元件关键字以外的元件不能执行分析。 程序规定元件关键字以外的元件不能执行分析。

线性折线电源(PWL)的时间值系列必须是增长的。 的时间值系列必须是增长的。 线性折线电源 的时间值系列必须是增长的

§ 10. 3. 4 元器件模型错误

*ERROR*: VALUE IS MISSING OR IS NONPOSITIVE

这个信息跟随在元件定义语句之后, 这个信息跟随在元件定义语句之后,指出元件 没有赋值或元件值是负数。 没有赋值或元件值是负数。Spice程序对下列元件值 程序对下列元件值 规定必须是正数:电阻、电容、电感、 规定必须是正数:电阻、电容、电感、互感和受控 半导体器件的某些几何参数(如面积、宽度w、 源。半导体器件的某些几何参数(如面积、宽度 、 长度L等 出现负值时,也会引出这一错误信息。 长度 等)出现负值时,也会引出这一错误信息。

*ERROR*: NEGATIVE NODE NUMBER FOUND

这个信息跟随在输入语句后面, 这个信息跟随在输入语句后面,该语句出现了负 的节点号码。 的节点号码。

*ERROR*: NODE NUMBERS ARE MISSING

这个信息跟随在输入语句后面, 这个信息跟随在输入语句后面,该语句中元件 的节点数与规定不符。例如,程序对于MOSFET规 的节点数与规定不符。例如,程序对于 规 定为4个节点 除了将衬底与地连接的情况外, 个节点, 定为 个节点,除了将衬底与地连接的情况外,都要 定义第四个节点。 定义第四个节点。

*ERROR*: X name HAS DIFFERENT NUMBER OF NODES THAN SUBname

X调用语句的节点数与所调用的子电路节点数必须相 调用语句的节点数与所调用的子电路节点数必须相 且一一对应。 同,且一一对应。

*EPROR*: SUBCIRCUIT SUBname IS DEFINED RECURSIVELY

*WARNING*:UNABLE TO MATCH FORWARD AND REVERSE DIODE REGIONS,BV=valuel AND IBV=value2

当BV=valuel和IB V=value2时,二极管的正向和反向 和 时 区域不匹配。 区域不匹配。

§ 10. 3. 5 电路拓扑结构错误

*ERROR*: VALUE IS ZERO

这个信息产生是由于电路里有零值电阻。 这个信息产生是由于电路里有零值电阻。Spice 程序解电路节点方程时,不允许出现零值电阻, 程序解电路节点方程时,不允许出现零值电阻,零 值电阻导致电导无穷大,引起运算不收敛。建议电 值电阻导致电导无穷大,引起运算不收敛。 阻值大于1M 。 阻值大于

在MODEL语句中必须有模型类型名 语句中必须有模型类型名

*ERROR*: UNKNOWN MODEL TYPE: model_type

模型类型名必须是Spice程序承认的 个类型之一 程序承认的8个类型之一 模型类型名必须是 程序承认的

*ERROR*: UNKNOWN MODEL PARAMETER: Name

*ERROR*: MODEL NAME IS MISSING

在二极管、晶体管 在二极管、晶体管DJT、结型场效应管 、结型场效应管JFET和 和 MOSFET等器件语句中,模型名应跟随节点之后。 等器件语句中, 等器件语句中 模型名应跟随节点之后。

*ERROR*: MODEL TYPE IS MISSING

*ERROR*: CIRCUIT HAS NO NODES

除了地节点外,电路至少还需要另一个节点。 除了地节点外,电路至少还需要另一个节点。

*ERROR*: LESS THAN 2 CONNECTIONS AT NODE number

任何一个节点必须连接两个元件。 任何一个节点必须连接两个元件。

*FUROR*:NO DC PATH TO GROUND FROM NODE number

为进行直流(DC)分析,每一个节点必须有对地的通 分析, 为进行直流 分析 即不能出现电容环路。 路,即不能出现电容环路。

*ERROR*: INDUCTOR/VOLTAGE SOURCE LOOP FOUND, CONTAINING Vname