STM32中断优先级彻底讲解

STM32 中断优先级理解

CM3 内核支持256 个中断,其中包含了16 个内核中断和240 个外部中断,并且具有256级的可编程中断设置。

但STM32 并没有使用CM3 内核的全部东西,而是只用了它的一部分。

STM32 有84 个中断,包括16 个内核中断和68 个可屏蔽中断,具有16 级可编程的中断优先级。

而我们常用的就是这68 个可屏蔽中断,但是STM32 的68 个可屏蔽中断,在STM32F103 系列上面,又只有60 个(在107 系列才有68 个)。

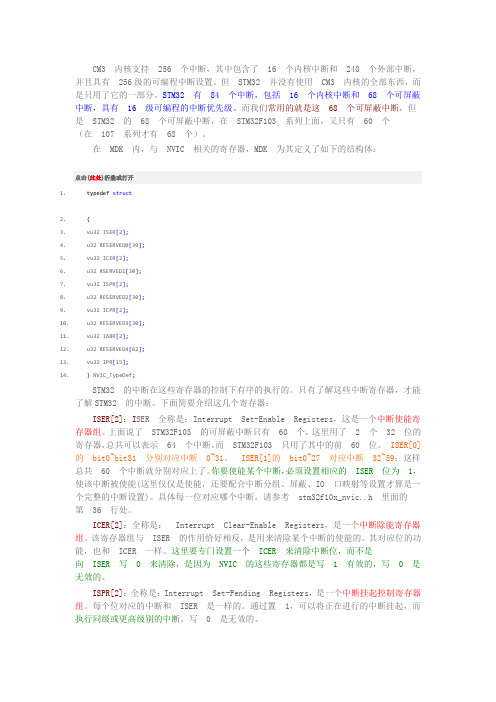

在MDK 内,与NVIC 相关的寄存器,MDK 为其定义了如下的结构体:点击(此处)折叠或打开1.typedef struct2.{3.vu32 ISER[2];4.u32 RESERVED0[30];5.vu32 ICER[2];6.u32 RSERVED1[30];7.vu32 ISPR[2];8.u32 RESERVED2[30];9.vu32 ICPR[2];10.u32 RESERVED3[30];11.vu32 IABR[2];12.u32 RESERVED4[62];13.vu32 IPR[15];14.} NVIC_TypeDef;STM32 的中断在这些寄存器的控制下有序的执行的。

只有了解这些中断寄存器,才能了解STM32 的中断。

下面简要介绍这几个寄存器:ISER[2]:I SER 全称是:Interrupt Set-Enable Registers,这是一个中断使能寄存器组。

上面说了STM32F103 的可屏蔽中断只有60 个,这里用了 2 个32 位的寄存器,总共可以表示64 个中断。

而STM32F103 只用了其中的前60 位。

ISER[0]的bit0~bit31 分别对应中断0~31。

ISER[1]的bit0~27 对应中断32~59;这样总共60 个中断就分别对应上了。

你要使能某个中断,必须设置相应的ISER 位为1,使该中断被使能(这里仅仅是使能,还要配合中断分组、屏蔽、IO 口映射等设置才算是一个完整的中断设置)。

STM32F4——NVIC中断优先级及外部中断

STM32F4——NVIC中断优先级及外部中断NVIC 中断优先级一、简介:CM4 内核可以支持256 个中断,包括16 个内核中断和240 个外部中断,256 级的可编程中断设置。

对于STM32F4 没有用到CM4 内核的所有东西,只是用到了一部分,对于STM32F40 和41 系列共有92 个中断,其中有10 个内核中断和82 个可屏蔽中断,常用的为82 个可屏蔽中断。

二、相关寄存器:ISER[8]中断使能寄存器组,用来使能中断,每一位控制一个中断,由于上面已经说明了控制82 个可屏蔽的中断,因此利用ISER[0~2]这三个32 位寄存器就够了。

一下的几个寄存器同理。

ICER[8]中断除能寄存器组,用来消除中断。

ISPR[8]中断挂起控制寄存器组,用来挂起中断。

ICPR[8]中断解挂控制寄存器组,用来解除挂起。

IABR[8]中断激活标志寄存器组,对应位如果为1 则表示中断正在被执行。

IP[240]中断优先级控制寄存器组,它是用来设置中断优先级的。

我们只用到了IP[0]~IP[81],每个寄存器只用到了高4 位,这4 位又用来设置抢占优先级和响应优先级(有关抢占优先级和响应优先级后面会介绍到),而对于抢占优先级和响应优先级各占多少位则由AIRCR 寄存器控制,相关设置如下图所示:关于抢占优先级和响应优先级的理解,可以将它们简单的理解为两个级别,抢占优先级的级别要比响应优先级的级别高,简单的理解为一个为长辈的一个为晚辈的,晚辈要让着长辈,因此抢占优先级的中断可以打断响应优先级的中断,而同级别的中断就得有个先来后到的了,先来的先执行。

三、相关库函数应用1、中断优先级分组函数:voidNVIC_PriorityGroupConfig(uint32_t NVIC_PriorityGroup),用来设置设置中断优。

STM32的中断优先级别理解20210524

STM32的中断优先级别理解20210524

理解:

1、STM32 总共有4个bit⽤来描述中断的种类,4个bit⼀共有5种组合【抢占式优先级别+副优先级(响应优先级)】,分组就决定了抢占优先级占⽤的bit数。

组0也就是表⽰0个bit为抢占优先级。

2、抢占式优先级别⾼的可以打断低优先级别的⼯作,相同抢占优先级的不能相互打断。

3、副优先级⾼的中断来临是,序号低的优先处理【响应】。

前提条件1:组别优先顺序(第0组优先级最强,第4组优先级最弱):

NVIC_PriorityGroup_0>NVIC_PriorityGroup_1>NVIC_PriorityGroup_2>NVIC_PriorityGroup_3>NVIC_PriorityGroup_4

前提条件2:“组”优先级别>“抢”占优先级别>“副”优先级别

前提条件3:同⼀组优先级别中,不同的抢占级别之间,其中⼀抢占级别正在做事,另外抢占级别不能打断他;(即”同⼀组优先级下的中断源间,没有中断嵌套“)

前提条件4:不同组优先级别间,依据优先级强弱,优先级别⾼的组的中断源可以打断优先级别低的组的正在做的事情;(即:不同组优先级间,可以中断嵌套)

对于上⾯的理解:

STM32中,每个设备都可以配置不同的中断组,抢占优先级,响应优先级。

具体举例:

项⽬需要2个串⼝,但是不是两个串⼝同时使⽤,只是随机使⽤其中⼀个,程序对2个串⼝的优先级需要配置;

要求两个串⼝⼯作的时候不能相互打断,最好也不鞥你被其他程序打断,那么可以把2个串⼝都设置成 NVIC_PriorityGroup_0 分组0【0个bit表⽰抢占优先级】,副优先级可以分别设置为1,2。

STM32日记之1——NVIC优先级概念

STM32(Cortex-M3)中的优先级概念STM32(Cortex-M3)中有两个优先级的概念——抢占式优先级和响应优先级,有人把响应优先级称作'亚优先级'或'副优先级',每个中断源都需要被指定这两种优先级。

具有高抢占式优先级的中断可以在具有低抢占式优先级的中断处理过程中被响应,即中断嵌套,或者说高抢占式优先级的中断可以嵌套低抢占式优先级的中断。

当两个中断源的抢占式优先级相同时,这两个中断将没有嵌套关系,当一个中断到来后,如果正在处理另一个中断,这个后到来的中断就要等到前一个中断处理完之后才能被处理。

如果这两个中断同时到达,则中断控制器根据他们的响应优先级高低来决定先处理哪一个;如果他们的抢占式优先级和响应优先级都相等,则根据他们在中断表中的排位顺序决定先处理哪一个。

既然每个中断源都需要被指定这两种优先级,就需要有相应的寄存器位记录每个中断的优先级;在Cortex-M3中定义了8个比特位用于设置中断源的优先级,这8个比特位可以有8种分配方式,如下:所有8位用于指定响应优先级最高1位用于指定抢占式优先级,最低7位用于指定响应优先级最高2位用于指定抢占式优先级,最低6位用于指定响应优先级最高3位用于指定抢占式优先级,最低5位用于指定响应优先级最高4位用于指定抢占式优先级,最低4位用于指定响应优先级最高5位用于指定抢占式优先级,最低3位用于指定响应优先级最高6位用于指定抢占式优先级,最低2位用于指定响应优先级最高7位用于指定抢占式优先级,最低1位用于指定响应优先级这就是优先级分组的概念。

-------------------------------------------------------------------------------- Cortex-M3允许具有较少中断源时使用较少的寄存器位指定中断源的优先级,因此STM32把指定中断优先级的寄存器位减少到4位,这4个寄存器位的分组方式如下:第0组:所有4位用于指定响应优先级第1组:最高1位用于指定抢占式优先级,最低3位用于指定响应优先级第2组:最高2位用于指定抢占式优先级,最低2位用于指定响应优先级第3组:最高3位用于指定抢占式优先级,最低1位用于指定响应优先级第4组:所有4位用于指定抢占式优先级可以通过调用STM32的固件库中的函数NVIC_PriorityGroupConfig()选择使用哪种优先级分组方式,这个函数的参数有下列5种:NVIC_PriorityGroup_0 => 选择第0组NVIC_PriorityGroup_1 => 选择第1组NVIC_PriorityGroup_2 => 选择第2组NVIC_PriorityGroup_3 => 选择第3组NVIC_PriorityGroup_4 => 选择第4组接下来就是指定中断源的优先级,下面以一个简单的例子说明如何指定中断源的抢占式优先级和响应优先级:// 选择使用优先级分组第1组NVIC_PriorityGroupConfig(NVIC_PriorityGroup_1);// 使能EXTI0中断NVIC_InitStructure.NVIC_IRQChannel = EXTI0_IRQChannel;NVIC_InitStructure.NVIC_IRQChannelPreemptionPriority = 1; // 指定抢占式优先级别1NVIC_InitStructure.NVIC_IRQChannelSubPriority = 0; // 指定响应优先级别0NVIC_InitStructure.NVIC_IRQChannelCmd = ENABLE;NVIC_Init(&NVIC_InitStructure);// 使能EXTI9_5中断NVIC_InitStructure.NVIC_IRQChannel = EXTI9_5_IRQChannel;NVIC_InitStructure.NVIC_IRQChannelPreemptionPriority = 0; // 指定抢占式优先级别0NVIC_InitStructure.NVIC_IRQChannelSubPriority = 1; // 指定响应优先级别1NVIC_InitStructure.NVIC_IRQChannelCmd = ENABLE;NVIC_Init(&NVIC_InitStructure);-------------------------------------------------------------------------------- 要注意的几点是:1)如果指定的抢占式优先级别或响应优先级别超出了选定的优先级分组所限定的范围,将可能得到意想不到的结果;2)抢占式优先级别相同的中断源之间没有嵌套关系;3)如果某个中断源被指定为某个抢占式优先级别,又没有其它中断源处于同一个抢占式优先级别,则可以为这个中断源指定任意有效的响应优先级别。

STM32中断优先级

STM32抢占优先级、响应优先级的详细讲解说明:stm32的优先级以寄存器的4位数据来表示的,因此2^4=16只能表示16级中断嵌套。

如上图所示:NVIC_PriotityGroup_0:即4位全部用于响应优先级(子优先级);因此,抢占优先级0级中断嵌套;响应优先级共有16即0—15级中断嵌套;NVIC_PriotityGroup_1:即1位用于响应优先级,3位用于响应优先级;因此,抢占优先级0下面共有2^3=8级中断嵌套;抢占优先级1下面共有2^3=8级中断嵌套;NVIC_PriotityGroup_2:即2位用于响应优先级,2位用于响应优先级;因此,抢占优先级总共有2^2=4个分别为:抢占优先级0至3且每个抢占优先级下面都有2^2=4个响应优先级。

NVIC_PriotityGroup_3:即3位用于响应优先级,1位用于响应优先级;因此,抢占优先级总共有2^3=8个分别为:抢占优先级0至7且每个抢占优先级下面都有2^1=2个响应优先级。

类似的,NVIC_PriotityGroup_4:即4位用于响应优先级,0位用于响应优先级;因此,抢占优先级16即0—15优先级中断嵌套;响应优先级共有0级中断嵌套;注意:响应优先级相等时,抢占优先级越小,中断级别越高抢占优先级相等时,响应优先级越小,中断级别越高举个栗子:void NVIC_Config(void){NVIC_InitTypeDef NVIC_InitStructure;NVIC_PriorityGroupConfig(NVIC_PriorityGroup_2);//NVIC_PriorityGroup_2即表明抢占优先级可有0—3级中断嵌套;响应优先级可设0—3级中断嵌套。

NVIC_InitStructure.NVIC_IRQChannel = USART1_IRQn;//配置串口中断NVIC_InitStructure.NVIC_IRQChannelPreemptionPrior ity = 0;//0即表明抢占优先级0;即为NVIC_PriorityGroup_2抢占优先0—3级中级别最高的优先级NVIC_InitStructure.NVIC_IRQChannelSubPriority = 0;//0即表明响应优先级0;即为NVIC_PriorityGroup_2响应优先0—3级中级别最高的优先级NVIC_InitStructure.NVIC_IRQChannelCmd = ENABLE;NVIC_Init(&NVIC_InitStructure);}总结:如上程序中串口1中断抢占优先级0,响应优先级0;其即为NVIC_PriorityGroup_2中中断优先级别最高,能够打断其它正在执行的中断。

STM32中断中设置的先占式优先级与从优先级

STM32中断中设置的先占式优先级与从优先级STM32(Cortex-M3)中有两个优先级的概念——抢占式优先级和响应优先级,有人把响应优先级称作'亚优先级'或'副优先级',每个中断源都需要被指定这两种优先级。

具有高抢占式优先级的中断可以在具有低抢占式优先级的中断处理过程中被响应,即中断嵌套,或者说高抢占式优先级的中断可以嵌套低抢占式优先级的中断。

当两个中断源的抢占式优先级相同时,这两个中断将没有嵌套关系,当一个中断到来后,如果正在处理另一个中断,这个后到来的中断就要等到前一个中断处理完之后才能被处理。

如果这两个中断同时到达,则中断控制器根据他们的响应优先级高低来决定先处理哪一个;如果他们的抢占式优先级和响应优先级都相等,则根据他们在中断表中的排位顺序决定先处理哪一个。

既然每个中断源都需要被指定这两种优先级,就需要有相应的寄存器位记录每个中断的优先级;在Cortex-M3中定义了8个比特位用于设置中断源的优先级,这8个比特位可以有8种分配方式,如下:所有8位用于指定响应优先级最高1位用于指定抢占式优先级,最低7位用于指定响应优先级最高2位用于指定抢占式优先级,最低6位用于指定响应优先级最高3位用于指定抢占式优先级,最低5位用于指定响应优先级最高4位用于指定抢占式优先级,最低4位用于指定响应优先级最高5位用于指定抢占式优先级,最低3位用于指定响应优先级最高6位用于指定抢占式优先级,最低2位用于指定响应优先级最高7位用于指定抢占式优先级,最低1位用于指定响应优先级这就是优先级分组的概念。

--------------------------------------------------------------------------------Cortex-M3允许具有较少中断源时使用较少的寄存器位指定中断源的优先级,因此STM32把指定中断优先级的寄存器位减少到4位,这4个寄存器位的分组方式如下:第0组:所有4位用于指定响应优先级第1组:最高1位用于指定抢占式优先级,最低3位用于指定响应优先级第2组:最高2位用于指定抢占式优先级,最低2位用于指定响应优先级第3组:最高3位用于指定抢占式优先级,最低1位用于指定响应优先级第4组:所有4位用于指定抢占式优先级可以通过调用STM32的固件库中的函数选择使用哪种优先级分组方式,这个函数的参数有下列5种: NVIC_PriorityGroup_0 => 选择第0组NVIC_PriorityGroup_1 => 选择第1组NVIC_PriorityGroup_2 => 选择第2组NVIC_PriorityGroup_3 => 选择第3组NVIC_PriorityGroup_4 => 选择第4组接下来就是指定中断源的优先级,下面以一个简单的例子说明如何指定中断源的抢占式优先级和响应优先级:// 选择使用优先级分组第1组NVIC_PriorityGroupConfig(NVIC_PriorityGroup_1);// 使能EXTI0中断NVIC_InitStructure.NVIC_IRQChannel=EXTI0_IRQChannel;NVIC_InitStructure.NVIC_IRQChannelPreemptionPriority = 1; // 指定抢占式优先级别1NVIC_InitStructure.NVIC_IRQChannelSubPriority = 0; // 指定响应优先级别0NVIC_InitStructure.NVIC_IRQChannelCmd = ENABLE;NVIC_Init(&NVIC_InitStructure);// 使能EXTI9_5中断NVIC_InitStructure.NVIC_IRQChannel=EXTI9_5_IRQChannel;NVIC_InitStructure.NVIC_IRQChannelPreemptionPriority = 0; // 指定抢占式优先级别0NVIC_InitStructure.NVIC_IRQChannelSubPriority = 1; // 指定响应优先级别1NVIC_InitStructure.NVIC_IRQChannelCmd =ENABLE;NVIC_Init(&NVIC_InitStructure);--------------------------------------------------------------------------------要注意的几点是:1)如果指定的抢占式优先级别或响应优先级别超出了选定的优先级分组所限定的范围,将可能得到意想不到的结果;2)抢占式优先级别相同的中断源之间没有嵌套关系;3)如果某个中断源被指定为某个抢占式优先级别,又没有其它中断源处于同一个抢占式优先级别,则可以为这个中断源指定任意有效的响应优先级别。

STM32中断优先级彻底讲解

STM32中断优先级彻底讲解stm32目前支持的中断共为84个(16个内核+68个外部),16级可编程中断优先级的设置(仅使用中断优先级设置8bit中的高4位)和16个抢占优先级(因为抢占优先级最多可以有四位数)。

二:优先级推论stm32(cortex-m3)中有两个优先级的概念——抢占式优先级和响应优先级,有人把响应优先级称作'亚优先级'或'副优先级',每个中断源都需要被指定这两种优先级。

具备低抢占市场式优先级的中断可以在具备高抢占市场式优先级的中断处理过程中被积极响应,即为中断嵌套,或者说低抢占市场式优先级的中断可以嵌套高抢占市场式优先级的中断。

当两个中断源的抢占式优先级相同时,这两个中断将没有嵌套关系,当一个中断到来后,如果正在处理另一个中断,这个后到来的中断就要等到前一个中断处理完之后才能被处理。

如果这两个中断同时到达,则中断控制器根据他们的响应优先级高低来决定先处理哪一个;如果他们的抢占式优先级和响应优先级都相等,则根据他们在中断表中的排位顺序同意先处置哪一个。

三:优先级分组既然每个中断源都须要被选定这两种优先级,就须要存有适当的寄存器位记录每个中断的优先级;在cortex-m3中定义了8个比特位用作设置中断源的优先级,这8个比特位在nvic应用领域中断与登位掌控递丛器(aircr)的中断优先级分组域中,可以存有8种分配方式,如下:所有8位用于指定响应优先级最低1十一位用作选定抢占市场式优先级,最高7十一位用作选定积极响应优先级最低2十一位用作选定抢占市场式优先级,最高6十一位用作选定积极响应优先级最低3十一位用作选定抢占市场式优先级,最高5十一位用作选定积极响应优先级最低4十一位用作选定抢占市场式优先级,最高4十一位用作选定积极响应优先级最低5十一位用作选定抢占市场式优先级,最高3十一位用作选定积极响应优先级最低6十一位用作选定抢占市场式优先级,最高2十一位用作选定积极响应优先级最低7十一位用作选定抢占市场式优先级,最高1十一位用作选定积极响应优先级这就是优先级分组的概念。

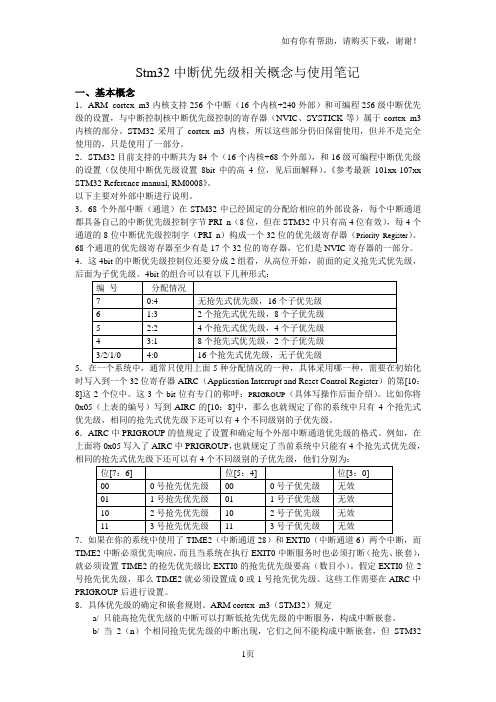

Stm32中断优先级相关概念与使用笔记

Stm32中断优先级相关概念与使用笔记一、基本概念1.ARM cortex_m3内核支持256个中断(16个内核+240外部)和可编程256级中断优先级的设置,与中断控制核中断优先级控制的寄存器(NVIC、SYSTICK等)属于cortex_m3内核的部分。

STM32采用了cortex_m3内核,所以这些部分仍旧保留使用,但并不是完全使用的,只是使用了一部分。

2.STM32目前支持的中断共为84个(16个内核+68个外部),和16级可编程中断优先级的设置(仅使用中断优先级设置8bit中的高4位,见后面解释)。

《参考最新101xx-107xx STM32 Reference manual, RM0008》。

以下主要对外部中断进行说明。

3.68个外部中断(通道)在STM32中已经固定的分配给相应的外部设备,每个中断通道都具备自己的中断优先级控制字节PRI_n(8位,但在STM32中只有高4位有效),每4个通道的8位中断优先级控制字(PRI_n)构成一个32位的优先级寄存器(Priority Register)。

68个通道的优先级寄存器至少有是17个32位的寄存器,它们是NVIC寄存器的一部分。

4.这4bit的中断优先级控制位还要分成2组看,从高位开始,前面的定义抢先式优先级,5.在一个系统中,通常只使用上面5种分配情况的一种,具体采用哪一种,需要在初始化时写入到一个32位寄存器AIRC(Application Interrupt and Reset Control Register)的第[10:8]这2个位中。

这3个bit位有专门的称呼:PRIGROUP(具体写操作后面介绍)。

比如你将0x05(上表的编号)写到AIRC的[10:8]中,那么也就规定了你的系统中只有4个抢先式优先级,相同的抢先式优先级下还可以有4个不同级别的子优先级。

6.AIRC中PRIGROUP的值规定了设置和确定每个外部中断通道优先级的格式。

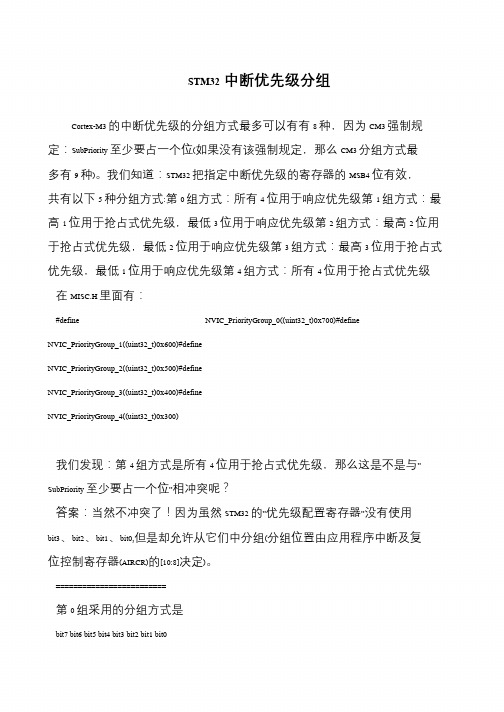

STM32中断优先级分组

STM32中断优先级分组Cortex-M3 的中断优先级的分组方式最多可以有有8 种,因为CM3 强制规定:SubPriority 至少要占一个位(如果没有该强制规定,那么CM3 分组方式最多有9 种)。

我们知道:STM32 把指定中断优先级的寄存器的MSB4 位有效,共有以下5 种分组方式:第0 组方式:所有4 位用于响应优先级第1 组方式:最高1 位用于抢占式优先级,最低3 位用于响应优先级第2 组方式:最高2 位用于抢占式优先级,最低2 位用于响应优先级第3 组方式:最高3 位用于抢占式优先级,最低1 位用于响应优先级第4 组方式:所有4 位用于抢占式优先级在MISC.H 里面有:#define NVIC_PriorityGroup_0((uint32_t)0x700)#define NVIC_PriorityGroup_1((uint32_t)0x600)#defineNVIC_PriorityGroup_2((uint32_t)0x500)#defineNVIC_PriorityGroup_3((uint32_t)0x400)#defineNVIC_PriorityGroup_4((uint32_t)0x300)我们发现:第4 组方式是所有4 位用于抢占式优先级,那么这是不是与”SubPriority 至少要占一个位”相冲突呢?答案:当然不冲突了!因为虽然STM32 的”优先级配置寄存器”没有使用bit3、bit2、bit1、bit0,但是却允许从它们中分组(分组位置由应用程序中断及复位控制寄存器(AIRCR)的[10:8]决定)。

=========================第0 组采用的分组方式是bit7 bit6 bit5 bit4 bit3 bit2 bit1 bit0。

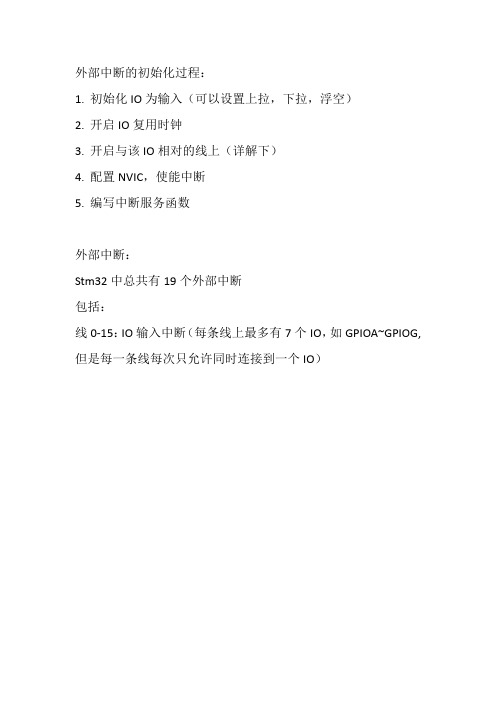

STM32外部中断以及中断优先级

外部中断的初始化过程:1.初始化IO为输入(可以设置上拉,下拉,浮空)2.开启IO复用时钟3.开启与该IO相对的线上(详解下)4.配置NVIC,使能中断5.编写中断服务函数外部中断:Stm32中总共有19个外部中断包括:线0-15:IO输入中断(每条线上最多有7个IO,如GPIOA~GPIOG,但是每一条线每次只允许同时连接到一个IO)线16:PVD线17:RTC线18:USB关于优先级:CM3中内核支持256个中断(16个内核+240外部)和可编程256级中断优先级的设置Stm32目前支持84个中断(16个内核+68个外部,注:不是指68个外部中断),16级可编程优先级(优先级设置寄存器中使用了4位)注意:其中外部中断5-9和中断10-15向量存放在一起优先级:数值低的优先级要高于数值高的!!!!!!上电复位后,系统默认使用的是组0;一个系统只能使用一组优先级组,不可使用多个,优先级的设置不能超过组的范围,否则会产生不可预计的错误1.高抢先级的中断可以打断低优先级的中断响应,构成中断嵌套2.相同抢先级的中断不可以构成嵌套,系统会优先响应子优先级高的3.当2(n)个相同抢先优先级和相同子优先级的中断出现,STM32首先响应中断通道所对应的中断向量地址低的那个中断4.0号抢先优先级的中断,可以打断任何中断抢先优先级为非0号的中断;1号抢先优先级的中断,可以打断任何中断抢先优先级为2、3、4号的中断;……;构成中断嵌套。

5.所有外部中断通道的优先级控制字PRI_n也都是0,68个外部中断通道的抢先优先级都是0号,没有子优先级的区分。

不会发生任何的中断嵌套行为,谁也不能打断当前正在执行的中断服务。

当多个中断出现后,则看它们的中断向量地址:地址越低,中断级别越高,STM32优先响应。

stm32中断抢占优先级和响应优先级有什么区别

stm32中断抢占优先级和响应优先级有什么区别

与51不同,stm32的中断分类更灵活。

51只是按先后顺序⼤⼩排列互相打断。

stm32中多了响应优先级这⼀概念。

stm32的中断分为 1.抢占(占先)优先级。

2.响应优先级。

1.抢占优先级。

抢占优先级⾼的中断,可以打断抢占优先级低的中断。

2.响应优先级。

抢占优先级相同的中断,响应优先级⾼的可以优先执⾏。

也许会有疑问:抢占优先级相同的中断,响应优先级⾼的不可以打断响应优先级低的中断。

两个中断肯定是谁先来了就相应谁,两个中断不可能同时来。

响应优先级⼜有何⽤呢。

其实,响应优先级主要给出了⼀种响应的优先队列。

假设中断的抢占优先级都相同。

如果有多个相同抢占优先级的中断来了,那么他们不会互相打断,但是他们后续的排队会按照响应优先级排队。

也就是说,在第⼀个中断没有执⾏完的期间内,后续的最⾼级的响应优先级是被安排到最⾼等待位处理的。

这为原⼦操作提供了可能,也就是不可被打断的操作。

有何正误,请指!。

STM32-NVIC中断优先级分组-中断优先级设置

STM32-NVIC中断优先级分组-中断优先级设置STM32-中断优先级管理NVIC1.NVIC中断优先级分组NVIC的全称是Nested vectoredinterrupt controller,即嵌套向量中断控制器。

STM32F中⽂参考⼿册中搜索向量表可以找到相应的中断说明。

CM4/CM7 内核⽀持256个中断,其中包含了16个内核中断和240个外部中断,并且具有256级的可编程中断设置。

STM32F4/F7并没有使⽤CM4内核的全部东西,⽽是只⽤了它的⼀部分。

STM32F40xx/STM32F41xx总共有92个中断。

10个内核中断,82个可屏蔽中断。

STM32F42xx/STM32F43xx则总共有97个中断。

10个内核中断,87个可屏蔽中断。

STM32F76x总共118个中断,10个内核中断,108个可屏蔽中断。

STM32具有16级可编程的中断优先级,⽽我们常⽤的就是这些可屏蔽中断。

⼏⼗个中断,怎么管理?⾸先,对STM32中断进⾏分组,组0~4。

同时,对每个中断设置⼀个抢占优先级和⼀个响应优先级值。

分组配置是在寄存器SCB->AIRCR中配置: IP bit[7:4]有4位,2^4=16,所以说它们的优先级可以有16个值,这时候如果是2位抢占优先级,那么它的值可能为0、1、2、3。

也就是抢占优先级可以取0到3 。

⾸先进⾏分组来决定⼏位抢占优先级、⼏位响应优先级。

数越⼩它的优先级越⾼。

组AIRCR[10:8]IP bit[7:4]分配情况分配结果01110:40位抢占优先级,4位响应优先级11101:31位抢占优先级,3位响应优先级21012:22位抢占优先级,2位响应优先级31003:13位抢占优先级,1位响应优先级40114:04位抢占优先级,0位响应优先级抢占优先级 & 响应优先级区别:⾼优先级的抢占优先级是可以打断正在进⾏的低抢占优先级中断的。

抢占决定了是否能打断别⼈。

STM32中断优先级与相关使用概念

STM32中断优先级与相关使用概念在STM32中,中断是一种特殊的程序执行方式,可以在系统中其中一事件发生时启动一个中断服务程序执行特定任务。

中断优先级是指在多个中断同时到达时,系统根据中断优先级决定哪一个中断先被响应。

在STM32中,中断优先级的设置非常重要,可以通过设置中断优先级来确保系统顺利运行。

在STM32中,每个中断都有自己的优先级,具体的中断优先级位数取决于具体的芯片型号。

一般来说,中断优先级可以分为主优先级和次优先级两部分。

主优先级用来决定不同中断之间的相对执行顺序,次优先级用来确定相同优先级的中断响应顺序。

在STM32中,中断优先级是通过NVIC(Nested Vectored Interrupt Controller)寄存器来设置的。

NVIC寄存器包括NVIC_IPR0-NVIC_IPR7等寄存器,用来设置各个中断通道的优先级。

在设置中断优先级时,要根据具体的中断要求和系统的实际情况进行设置,以确保系统的稳定性和性能。

设置中断优先级时,通常遵循以下几个原则:1.主优先级高的中断优先级高于次优先级高的中断。

即主优先级相同的情况下,主优先级高的中断先被响应。

2.同一个主优先级下,次优先级高的中断先被响应。

3.多级中断时,根据中断嵌套的层级关系来设置不同优先级。

4.保留一定的中断处理时间,避免因优先级设置不当导致一些低优先级的中断得不到响应。

5.不同的中断优先级设置要根据具体的系统实际需求进行调整,避免出现死锁和优先级反转等问题。

在实际应用中,中断优先级的设置要根据具体的系统需求和硬件环境进行合理调整。

在STM32中,中断优先级的设置可以通过CubeMX工具或直接在代码中修改来实现。

在CubeMX中,可以通过配置器界面来设置中断优先级,也可以通过用户手册来了解每个中断源的优先级设置规则。

总的来说,中断优先级的设置是STM32系统中非常重要的一环,合理的中断优先级设置可以提高系统的实时性和稳定性。

STM32中断优先级与相关使用概念

STM32中断优先级与相关使用概念

一、STM32中断优先级

STM32中断优先级由4位数定义,其中高4位为组优先级(group priority),低4位为子优先级(subpriority),如果两个中断具有相同的组优先级,其中断服务函数将按子优先级的先后顺序进行调度,优先级最高的中断先服务,中断优先级的从高到低分别为:

1.最高优先级:组优先级0位,子优先级0位,实际码值为0X00(其中断服务函数将不受其他的中断影响);

2.高优先级:组优先级1位,子优先级7位,实际码值为0X87;

3.中上优先级:组优先级2位,子优先级6位,实际码值为0X86;

4.中下优先级:组优先级3位,子优先级5位,实际是码值0X85;

5.低优先级:组优先级4位,子优先级4位,实际码值为0X84;

6.最低优先级:组优先级7位,子优先级1位,实际码值为0X81(此类中断服务函数将受其他的中断影响)。

(1)中断优先级的决定

不同的中断有不同的优先级,中断优先级由MCU的硬件决定的,而不是由程序代码来控制的,只有通过程序才能使中断具有不同的优先级。

(2)中断嵌套

对于STM32系列中断系统,在处理中断层次时,中断可以嵌套,即在正在处理的中断服务函数中,又产生新的中断,新产生的中断,如果具有更高的优先级。

STM32用FreeRTOS时任务优先级和中断优先级说明

STM32⽤FreeRTOS时任务优先级和中断优先级说明下⾯对 FreeRTOS 优先级相关的⼏个重要知识点进⾏下说明,这些知识点在以后的使⽤中务必要掌握牢固。

FreeRTOS 中任务的最⾼优先级是通过 FreeRTOSConfig.h ⽂件中的 configMAX_PRIORITIES 进⾏配置的,⽤户实际可以使⽤的优先级范围是 0 到 configMAX_PRIORITIES – 1。

⽐如我们配置此宏定义为 5,那么⽤户可以使⽤的优先级号是 0,1,2,3,4,不包含 5,对于这⼀点,初学者要特别的注意。

⽤户配置任务的优先级数值越⼩,那么此任务的优先级越低,空闲任务的优先级是 0。

建议⽤户配置宏定义 configMAX_PRIORITIES 的最⼤值不要超过 32,即⽤户任务可以使⽤的优先级范围是0到31。

因为对于CM内核的移植⽂件,⽤户任务的优先级不是⼤于等于32的话, portmacro.h⽂件中的宏定义configUSE_PORT_OPTIMISED_TASK_SELECTION会优化优先级列表中要执⾏的最⾼优先级任务的获取算法(对于 CM 内核的移植⽂件,此宏定义默认是使能的,当然,⽤户也可以在FreeRTOSConfig.h ⽂件中进⾏配置)。

相⽐通⽤的最⾼优先级任务获取算法,这两种⽅式的对⽐如下: 通⽤⽅式,没有优化---配置宏定义 configUSE_PORT_OPTIMISED_TASK_SELECTION 为 0: 所有平台的移植⽂件都可以配置为 0,因为这是通⽤⽅式。

纯 C 编写,⽐专⽤⽅式效率低。

可⽤的优先级数量不限制。

专⽤⽅式,进⾏优化---配置宏定义 configUSE_PORT_OPTIMISED_TASK_SELECTION 为为 1: 部分平台⽀持。

这些平台架构有专⽤的汇编指令,⽐如 CLZ(Count Leading Zeros)指令,通过这些指令可以加速算法执⾏速度。

STM32中断控制及优先级设置

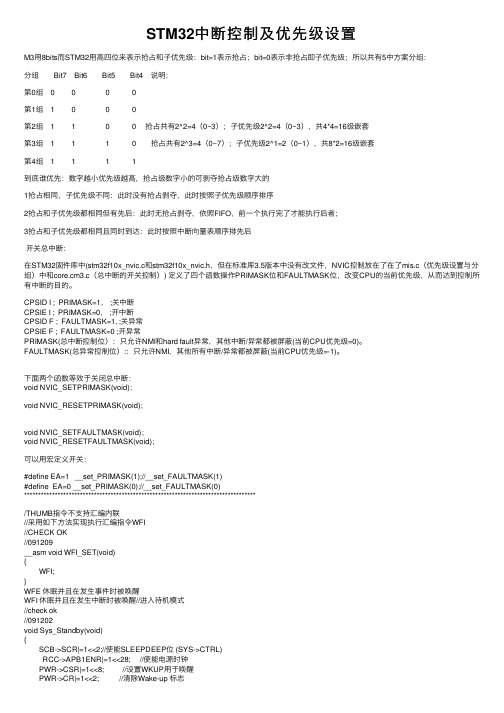

STM32中断控制及优先级设置M3⽤8bits⽽STM32⽤⾼四位来表⽰抢占和⼦优先级:bit=1表⽰抢占;bit=0表⽰⾮抢占即⼦优先级;所以共有5中⽅案分组:分组 Bit7 Bit6 Bit5 Bit4 说明:第0组 0 0 0 0第1组 1 0 0 0第2组 1 1 0 0 抢占共有2^2=4(0~3);⼦优先级2^2=4(0~3),共4*4=16级嵌套第3组 1 1 1 0 抢占共有2^3=4(0~7);⼦优先级2^1=2(0~1),共8*2=16级嵌套第4组 1 1 1 1到底谁优先:数字越⼩优先级越⾼,抢占级数字⼩的可剥夺抢占级数字⼤的1抢占相同,⼦优先级不同:此时没有抢占剥夺,此时按照⼦优先级顺序排序2抢占和⼦优先级都相同但有先后:此时⽆抢占剥夺,依照FIFO,前⼀个执⾏完了才能执⾏后者;3抢占和⼦优先级都相同且同时到达:此时按照中断向量表顺序排先后开关总中断:在STM32固件库中(stm32f10x_nvic.c和stm32f10x_nvic.h,但在标准库3.5版本中没有改⽂件,NVIC控制放在了在了mis.c(优先级设置与分组)中和core.cm3.c(总中断的开关控制)) 定义了四个函数操作PRIMASK位和FAULTMASK位,改变CPU的当前优先级,从⽽达到控制所有中断的⽬的。

CPSID I ; PRIMASK=1, ;关中断CPSIE I ; PRIMASK=0, ;开中断CPSID F ; FAULTMASK=1, ;关异常CPSIE F ; FAULTMASK=0 ;开异常PRIMASK(总中断控制位):只允许NMI和hard fault异常,其他中断/异常都被屏蔽(当前CPU优先级=0)。

FAULTMASK(总异常控制位)::只允许NMI,其他所有中断/异常都被屏蔽(当前CPU优先级=-1)。

下⾯两个函数等效于关闭总中断:void NVIC_SETPRIMASK(void);void NVIC_RESETPRIMASK(void);void NVIC_SETFAULTMASK(void);void NVIC_RESETFAULTMASK(void);可以⽤宏定义开关:#define EA=1 __set_PRIMASK(1);//__set_FAULTMASK(1)#define EA=0 __set_PRIMASK(0);//__set_FAULTMASK(0)***********************************************************************************/THUMB指令不⽀持汇编内联//采⽤如下⽅法实现执⾏汇编指令WFI//CHECK OK//091209__asm void WFI_SET(void){WFI;}WFE 休眠并且在发⽣事件时被唤醒WFI 休眠并且在发⽣中断时被唤醒//进⼊待机模式//check ok//091202void Sys_Standby(void){SCB->SCR|=1<<2;//使能SLEEPDEEP位 (SYS->CTRL)RCC->APB1ENR|=1<<28; //使能电源时钟PWR->CSR|=1<<8; //设置WKUP⽤于唤醒PWR->CR|=1<<2; //清除Wake-up 标志PWR->CR|=1<<1; //PDDS置位WFI_SET(); //执⾏WFI指令}。

STM32中断

STM32中断可能对于刚接触抢占式优先级和响应优先级的⼈来说学习STM32的中断优先级有点障碍,这⾥先介绍下优先级:具有⾼抢占式优先级的中断可以在具有低抢占式优先级的中断处理过程中被响应,即中断嵌套,或者说⾼抢占式优先级的中断可以嵌套低抢占式优先级的中断。

当两个中断源的抢占式优先级相同时,这两个中断将没有嵌套关系,当⼀个中断到来后,如果正在处理另⼀个中断,这个后到来的中断就要等到前⼀个中断处理完之后才能被处理。

如果这两个中断同时到达,则中断控制器根据他们的响应优先级⾼低来决定先处理哪⼀个;如果他们的抢占式优先级和响应优先级都相等,则根据他们在中断表中的排位顺序决定先处理哪⼀个。

STM32 可以⽀持的 68 个外部中断通道,已经固定的分配给相应的外部设备。

每个中断通道都具备⾃⼰的中断优先级控制字节 PRI_n(8 位,但在 STM32 中只使⽤ 4 位,⾼ 4 位有效),每 4 个通道的 8 位中断优先级控制字(PRI_n)构成⼀个 32 位的优先级寄存器(PriorityRegister)。

68 个通道的优先级控制字⾄少构成 17 个 32 位的优先级寄存器,它们是 NVIC寄存器中的⼀个重要部分。

5.对于这 4bit 的中断优先级控制位还必须分成 2 组看:从⾼位开始,前⾯是定义抢先式优先级的位,后⾯⽤于定义⼦优先级。

4bit 的分组组合可以有以下⼏种形式:第0组:所有4位⽤于指定响应优先级第1组:最⾼1位⽤于指定抢占式优先级,最低3位⽤于指定响应优先级第2组:最⾼2位⽤于指定抢占式优先级,最低2位⽤于指定响应优先级第3组:最⾼3位⽤于指定抢占式优先级,最低1位⽤于指定响应优先级第4组:所有4位⽤于指定抢占式优先级由于我们使⽤STM32的库函数,所以这⾥介绍如何使⽤库函数设置需要的优先级可以通过调⽤STM32的固件库中的函数NVIC_PriorityGroupConfig()选择使⽤哪种优先级分组⽅式这个函数在帮助⽂件的标准外设驱动的CMSIS\CMSIS_Expord_Function下;这个函数的参数有下列5种:NVIC_PriorityGroup_0 => 选择第0组NVIC_PriorityGroup_1 => 选择第1组NVIC_PriorityGroup_2 => 选择第2组NVIC_PriorityGroup_3 => 选择第3组NVIC_PriorityGroup_4 => 选择第4组这⾥要注意的是,在系统复位初始化之后,默认使⽤的是第0组优先级分组接下来就是指定中断源的优先级,下⾯以⼀个简单的例⼦说明如何指定中断源的抢占式优先级和响应优先级:如果应⽤程序储存在ROM中,并且不需要改变异常服务程序,则我们可以把整个向量表编码到ROM的起始区域(从0 地址开始的那段)。

stm32中断优先级的处理原则

STM32中断优先级的处理原则1. 引言在嵌入式系统中,中断是一种常用的机制,用于在特定事件发生时打断CPU的正常执行流程,转而执行特定的中断处理程序。

STM32系列微控制器提供了丰富的中断控制功能,并支持多个优先级的中断。

正确设置中断优先级是确保系统稳定性和可靠性的重要步骤。

本文将介绍STM32中断优先级处理原则,包括如何设置优先级、不同类型中断之间的关系以及注意事项等内容。

2. 中断优先级概述STM32微控制器支持多个优先级的中断,其中数字越小表示优先级越高。

当多个中断同时发生时,只有具有最高优先级的中断会被响应。

其他低优先级的中断将被挂起,等待当前正在处理的高优先级中断完成后再进行处理。

每个STM32微控制器都有一个向量表(Vector Table),其中存储了各个中断向量及其对应的ISR(Interrupt Service Routine)。

在初始化过程中,需要将需要使用到的ISR函数指针写入向量表相应位置。

3. 中断优先级设置原则在STM32微控制器上配置和设置各个外设的中断优先级时,需要遵循以下原则:3.1 高优先级中断的响应时间高优先级中断的响应时间应尽量短,以确保系统对紧急事件的及时响应。

通常情况下,系统启动和初始化过程中会配置一些必要的高优先级中断,如系统滴答定时器(SysTick)等。

3.2 低优先级中断的执行时间低优先级中断可能会被高优先级中断打断,在高优先级中断执行期间无法得到处理。

因此,低优先级中断的执行时间应尽量短,以减少对系统性能和实时性的影响。

STM32微控制器支持不同外设之间和相同外设内部的中断嵌套。

在设置嵌套中断时,需要注意以下原则: - 外设之间:不同外设之间的中断嵌套顺序应根据具体需求和业务逻辑进行设置。

- 外设内部:在具有多个可触发相同类型中断源的外设上,需要根据业务需求设置不同源之间的触发次序。

3.4 中断抢占与屏蔽STM32微控制器支持中断的抢占和屏蔽功能。

STM32单片机优先级的定义

STM32单片机优先级的定义前言:1.要想学习STM32中断,要先掌握STM32对优先级的定义;2.有51单片机开发经验会比较容易理解中断优先级;3.本篇博文基于STM32F103ZET6芯片和3.5.0标准库编写;4.本篇博文从寄存器入手,最终实现编程的步骤;一基础知识1. cortex-m3支持256个中断,其中包含了16个内核中断,240个外部中断。

(本博文只介绍60个外部可屏蔽中断)2. STM32只有84个中断,包括16个内核中断和68个可屏蔽中断3. stm32f103上只有60个可屏蔽中断,f107上才有68个中断4.先占优先级也就是抢占优先级,概念等同于51单片机中的中断。

假设有两中断先后触发,已经在执行的中断先占优先级如果没有后触发的中断先占优先级更高,就会先处理先占优先级高的中断。

也就是说又有较高的先占优先级的中断可以打断先占优先级较低的中断。

这是实现中断嵌套的基础。

次占优先级,也就是响应优先级,只在同一先占优先级的中断同时触发时起作用,先占优先级相同,则优先执行次占优先级较高的中断。

次占优先级不会造成中断嵌套。

如果中断的两个优先级都一致,则优先执行位于中断向量表中位置较高的中断。

NVIC是什么?嵌套向量中断控制器;用于为中断分组,从而分配抢占优先级和响应优先级;分组的方式有两种:(1)Cortex-m3内核提供了一种3位宽度的PRIGROUP数据区,用于指示一个8位数据序列中的小数点的位置,从而表示中断优先级的分组。

见下表:(2)而实际上STM32并没有用到这么多中断,所以在分组上只分了5个组,并且表示方法有所不同;见下表:我们在应用当中只会用到STM32的分组(5组)方式,所以下面着重于5组分组方式;二中断向量表(STM32F10x系列)(图片来自STM32使用手册,只需看,不需要熟记,知道大概这么多中断就好)三配置中断相关寄存器/*cortex-m3内核分组方式(8组)结构体表达方式:*/typedefstruct{__IOuint32_tISER[8];中断使能设置寄存器/*!《偏移量:0x000InterruptSetEnableRegister*/uint32_tRESERVED0[24];__IOuint32_TICER[8];中断清除使能寄存器/*!《偏移量:0x080InterruptClearEnableRegister*/uint32_tRSERVED1[24];__IOuint32_TISPR[8];中断挂起设置寄存器/*!《偏移量:0x100InterruptSetPendingRegister*/uint32_tRESERVED2[24];__IOuint32_TICPR[8];中断清除挂起寄存器/*!《偏移量:0x180InterruptClearPendingRegister*/uint32_tRESERVED3[24];__IOuint32_TIABR[8];中断激活状态位寄存器/*!《偏移量:0x200InterruptActivebitRegister*/uint32_tRESERVED4[56];__IOuint8_tIP[240];中断优先级寄存器/*!《偏移量:0x300InterruptPriorityRegister (8Bitwide)*/uint32_tRESERVED5[644];软件触发方式寄存器__Ouint32_tSTIR;/*!《偏移量:0xE00SoftwareTriggerInterruptRegister*/}NVIC_Type;12345678910111213141516171819/*STM32分组(5组)方式结构体表达方式typedefstruct{vu32ISER[2];u32RESERVED0[30];vu32ICER[2];u32RSERVED1[30];vu32ISPR[2];u32RESERVED2[30];vu32ICPR [2];u32RESERVED3[30];vu32IABR[2];u32RESERVED4[62];vu32IPR [15];}NVIC_TypeDef;*/1234567891011121314151617以上寄存器介绍:对一些概念的解释:1. 挂起:当置位中断挂起寄存器的时候,相应的中断将会被挂起,这是这个中断将不会立即执行,而是等待可执行的时候再执行;比如高低级别的中断同时产生,就先挂起低级别的中断,等高级别的中断执行完毕,解除并执行低级中断;2. 对中断优先级控制寄存器的解释四编程步骤(1)选择优先级分组/*1. 此函数在库文件misc.h文件下;2. 参数可参照下面图片:3. 功能:选择分组方式;*/void NVIC_PriorityGroupConfig(uint32_t NVIC_PriorityGroup);栗子:NVIC_PriorityGroupConfig(NVIC_PriorityGroup_2);//抢占优先级可选0~3,响应优先级可选0~3;(2)选择,配置,并使能中断NVIC_InitStructure.NVIC_IRQChannel = EXTI2_IRQn; //选择EXTI2中断NVIC_InitStructure.NVIC_IRQChannelPreemptionPriority = 0x02; //抢占优先级为2NVIC_InitStructure.NVIC_IRQChannelSubPriority = 0x02; //响应优先级为2NVIC_InitStructure.NVIC_IRQChannelCmd = ENABLE; //使能EXTI2中断;NVIC_Init(//初始化以上参数;(3)写出相应中断函数栗子:void EXTI2_IRQHandler(void){//逻辑代码;EXTI_ClearITPendingBit(EXTI_Line2); }。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

STM32中断优先级彻底讲解

一:综述

STM32 目前支持的中断共为 84 个(16 个内核+68 个外部), 16 级可编程中断优先级

的设置(仅使用中断优先级设置 8bit 中的高 4 位)和16个抢占优先级(因为抢占优先级最多可以有四位数)。

二:优先级判断

STM32(Cortex-M3)中有两个优先级的概念——抢占式优先级和响应优先级,有人把响应优先级称作'亚优先级'或'副优先级',每个中断源都需要被指定这两种优先级。

具有高抢占式优先级的中断可以在具有低抢占式优先级的中断处理过程中被响应,即中断嵌套,或者说高抢占式优先级的中断可以嵌套低抢占式优先级的中断。

当两个中断源的抢占式优先级相同时,这两个中断将没有嵌套关系,当一个中断到来后,如果正在处理另一个中断,这个后到来的中断就要等到前一个中断处理完之后才能被处理。

如果这两个中断同时到达,则中断控制器根据他们的响应优先级高低来决定先处理哪一个;如果他们的抢占式优先级和响应优先级都相等,则根据他们在中断表中的排位顺序

决定先处理哪一个。

三:优先级分组

既然每个中断源都需要被指定这两种优先级,就需要有相应的寄存器位记录每个中断的优先级;在Cortex-M3中定义了8个比特位用于设置中断源的优先级,这8个比特位在NVIC应用中断与复位控制寄丛器(AIRCR)的中断优先级分组域中,可以有8种分配方式,如下:

所有8位用于指定响应优先级

最高1位用于指定抢占式优先级,最低7位用于指定响应优先级

最高2位用于指定抢占式优先级,最低6位用于指定响应优先级

最高3位用于指定抢占式优先级,最低5位用于指定响应优先级

最高4位用于指定抢占式优先级,最低4位用于指定响应优先级

最高5位用于指定抢占式优先级,最低3位用于指定响应优先级

最高6位用于指定抢占式优先级,最低2位用于指定响应优先级

最高7位用于指定抢占式优先级,最低1位用于指定响应优先级

这就是优先级分组的概念。

Cortex-M3允许具有较少中断源时使用较少的寄存器位指定中断源的优先级,因此STM32把指定中断优先级的寄存器位减少到4位(AIRCR高四位),这4个寄存器位的分组方式如下:

第0组:所有4位用于指定响应优先级

第1组:最高1位用于指定抢占式优先级,最低3位用于指定响应优先级

第2组:最高2位用于指定抢占式优先级,最低2位用于指定响应优先级

第3组:最高3位用于指定抢占式优先级,最低1位用于指定响应优先级

第4组:所有4位用于指定抢占式优先级

可以通过调用STM32的固件库中的函数NVIC_PriorityGroupConfig()选择使用哪种优先级分组方式,这个函数的参数有下列5种:

NVIC_PriorityGroup_0 => 选择第0组

NVIC_PriorityGroup_1 => 选择第1组

NVIC_PriorityGroup_2 => 选择第2组

NVIC_PriorityGroup_3 => 选择第3组

NVIC_PriorityGroup_4 => 选择第4组

中断优先级分组是为了给抢占式优先级和响应优先级在中断优先级寄丛器的高四位分配各个优先级数字所占的位数。

在一个程序中只能设定一次

四:中断源的优先级

接下来就是指定中断源的优先级,中断源优先级是在中断优先级寄存器中设置的,只能设置及高四位,必须根据中断优先级分组中设置好的位数来在该寄存器中设置相应的数值。

假如你选择中断优先级分组的第3组:最高3位用于指定抢占式优先级,最低1位用于指定响应优先级,那么抢占式优先级就有000-111共八种数据选择,也就是有八个中断嵌套,而响应优先级中有0和1两种,总共有8*2=16种优先级。

中断源优先级具体的设置了该中断源的优先级别

在一个程序中可以设定多个(最多16个)

优先级,每个中断源只能设定的一个。

每写一个关于中断优先级的程序必须包含下列两个函数:

(1)void NVIC_PriorityGroupConfig(u32 NVIC_PriorityGroup)中断分组设置

(2)void NVIC_Init(NVIC_InitTypeDef* NVIC_InitStruct)中断优先级设置。