南邮微机原理第5章课件

合集下载

微机原理课件第五章存储器暗灰

铁电存储器的缺点

耐久性有限、数据保持时间较短等。

磁性随机存取存储器(MRAM)

01

总结词

磁性随机存取存储器是一种基 于磁隧道结的存储器,利用磁 性材料的磁化方向来存储数据 。

02

详细描述

MRAM利用磁隧道结中的磁性 材料在磁场作用下的磁化方向 来存储数据,通过读取磁隧道 结的电阻值来确定存储的数据 。MRAM具有非易失性、高速 读写、低功耗等优点。

紫外线擦除可编程只读存储器(EPROM)

总结词

一种可重复编程的存储器,通过紫源自线擦除 数据。详细描述紫外线擦除可编程只读存储器是一种可重复 编程的只读存储器。用户可以根据需要将数 据写入存储器中,写入后可以通过紫外线照 射来擦除数据,然后重新编程。这种存储器 适用于需要频繁更新数据的场合,如实验设 备、测试仪器等。

低功耗要求

嵌入式系统通常需要长时 间运行,因此存储器需要 具备低功耗特性,以降低 系统能耗。

其他领域的应用

通信领域

存储器用于存储通信协议 、控制信息等,保证通信 系统的稳定性和可靠性。

航空航天领域

存储器用于存储飞行控制 程序、导航数据等关键信 息,保证航空航天器的安 全运行。

物联网领域

存储器用于存储传感器数 据、设备配置信息等,实 现物联网设备的远程监控 和管理。

高可靠性、低功耗、快速读取 速度、可重复编程等。

写入速度较慢、写入周期有限 制等。

铁电存储器(FRAM)

总结词

铁电存储器是一种非易失性随机存取存储器,利用铁电材 料的特殊性质来存储数据。

铁电存储器的优点

高速读写、低功耗、非易失性等。

详细描述

铁电材料具有电滞回线特性,能够通过改变材料内部的极 化状态来存储数据。FRAM的读写速度与RAM相近,但 具有非易失性,能够在断电后保持数据。

耐久性有限、数据保持时间较短等。

磁性随机存取存储器(MRAM)

01

总结词

磁性随机存取存储器是一种基 于磁隧道结的存储器,利用磁 性材料的磁化方向来存储数据 。

02

详细描述

MRAM利用磁隧道结中的磁性 材料在磁场作用下的磁化方向 来存储数据,通过读取磁隧道 结的电阻值来确定存储的数据 。MRAM具有非易失性、高速 读写、低功耗等优点。

紫外线擦除可编程只读存储器(EPROM)

总结词

一种可重复编程的存储器,通过紫源自线擦除 数据。详细描述紫外线擦除可编程只读存储器是一种可重复 编程的只读存储器。用户可以根据需要将数 据写入存储器中,写入后可以通过紫外线照 射来擦除数据,然后重新编程。这种存储器 适用于需要频繁更新数据的场合,如实验设 备、测试仪器等。

低功耗要求

嵌入式系统通常需要长时 间运行,因此存储器需要 具备低功耗特性,以降低 系统能耗。

其他领域的应用

通信领域

存储器用于存储通信协议 、控制信息等,保证通信 系统的稳定性和可靠性。

航空航天领域

存储器用于存储飞行控制 程序、导航数据等关键信 息,保证航空航天器的安 全运行。

物联网领域

存储器用于存储传感器数 据、设备配置信息等,实 现物联网设备的远程监控 和管理。

高可靠性、低功耗、快速读取 速度、可重复编程等。

写入速度较慢、写入周期有限 制等。

铁电存储器(FRAM)

总结词

铁电存储器是一种非易失性随机存取存储器,利用铁电材 料的特殊性质来存储数据。

铁电存储器的优点

高速读写、低功耗、非易失性等。

详细描述

铁电材料具有电滞回线特性,能够通过改变材料内部的极 化状态来存储数据。FRAM的读写速度与RAM相近,但 具有非易失性,能够在断电后保持数据。

微机原理与接口技术课件第五章

微机原理与接口技术 课件第五章

目录

• 微机原理概述 • 接口技术基础 • 微机中的常见接口 • 微机中的总线技术 • 微机原理与接口技术的应用

01

微机原理概述

微机的基本概念

01

02

03

微机

微型计算机的简称,是一 种体积小、结构紧凑、性 能接近于大型计算机的计 算机。

特点

具有高性能、低价格、易 扩展、易维护等特点,广 泛应用于工业控制、自动 化、办公自动化等领域。

接口的分类方式多样,常见的有按数据传 输方式、按连接方式等分类,不同类型的 接口结构也不同。

并行接口和串行接口。并行接口传输速度 快,但线路复杂;串行接口传输速度较慢 ,但线路简单。

按连接方式分类

按功能分类

内置接口和外设接口。内置接口直接集成 在主板上,如IDE接口;外设接口则需要通 过电缆连接,如USB接口。

总线的定义

总线是计算机各功能部件之间传输信息的公共通信干线,它 由一组传输线组成,负责传输地址、数据和控制信号。

总线的分类

根据功能和传输速率的不同,总线可以分为地址总线、数据 总线和控制总线。地址总线用于传输地址信号,数据总线用 于传输数据信号,控制总线用于传输控制信号。

总线的通信协议

总线通信协议的定义

串行接口通常用于连接低速外 设,如鼠标、调制解调器等。

串行接口的数据传输速率较低 ,但只需要一条数据线,因此

Hale Waihona Puke 成本较低。串行接口的常见标准包括RS232和USB。

中断控制器接口

中断控制器接口是微机中用于管理中断的接口。

输标02入题

中断是指微机在执行程序过程中遇到突发事件时,暂 时停止当前程序的执行,转去处理突发事件,处理完 毕后再返回原程序继续执行的过程。

目录

• 微机原理概述 • 接口技术基础 • 微机中的常见接口 • 微机中的总线技术 • 微机原理与接口技术的应用

01

微机原理概述

微机的基本概念

01

02

03

微机

微型计算机的简称,是一 种体积小、结构紧凑、性 能接近于大型计算机的计 算机。

特点

具有高性能、低价格、易 扩展、易维护等特点,广 泛应用于工业控制、自动 化、办公自动化等领域。

接口的分类方式多样,常见的有按数据传 输方式、按连接方式等分类,不同类型的 接口结构也不同。

并行接口和串行接口。并行接口传输速度 快,但线路复杂;串行接口传输速度较慢 ,但线路简单。

按连接方式分类

按功能分类

内置接口和外设接口。内置接口直接集成 在主板上,如IDE接口;外设接口则需要通 过电缆连接,如USB接口。

总线的定义

总线是计算机各功能部件之间传输信息的公共通信干线,它 由一组传输线组成,负责传输地址、数据和控制信号。

总线的分类

根据功能和传输速率的不同,总线可以分为地址总线、数据 总线和控制总线。地址总线用于传输地址信号,数据总线用 于传输数据信号,控制总线用于传输控制信号。

总线的通信协议

总线通信协议的定义

串行接口通常用于连接低速外 设,如鼠标、调制解调器等。

串行接口的数据传输速率较低 ,但只需要一条数据线,因此

Hale Waihona Puke 成本较低。串行接口的常见标准包括RS232和USB。

中断控制器接口

中断控制器接口是微机中用于管理中断的接口。

输标02入题

中断是指微机在执行程序过程中遇到突发事件时,暂 时停止当前程序的执行,转去处理突发事件,处理完 毕后再返回原程序继续执行的过程。

微机原理PPT课件

06.08.2020

7

微机原理及应用 吴丽娟

5.1.2 86系列 CPU的寻址方式

为什么要设置多种寻址方式? 希望用最短的指令长度访问尽可能大的存储器空间 希望给多样的程序设计技术和数据结构对数据访问的灵 活性和有效性提供支持 变址寻址便于处理表格和矩阵 相对寻址便于编制浮动的、可重入的程序

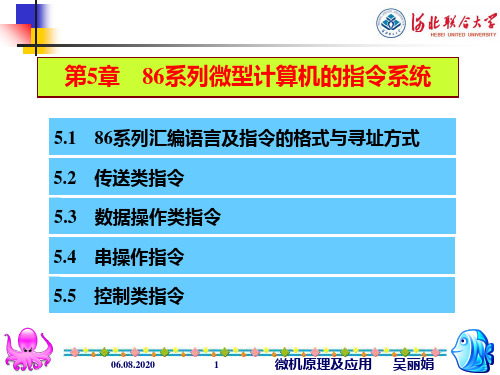

第5章 86系列微型计算机的指令系统

5.1 86系列汇编语言及指令的格式与寻址方式 5.2 传送类指令 5.3 数据操作类指令 5.4 串操作指令 5.5 控制类指令

06.08.2020

1

微机原理及应用 吴丽娟

指令是让计算机完成某种操作的命令, 指令的集合称作 指令系统, 不同系列计算机有不同的指令系统。

5.1.1 86系列汇编语言指令语句格式

任何一种汇编语言的指令语句都是与机器指令一一对应的, 它通过汇编程序将其翻译成机器指令代码 (目标代码), 让CPU 执行某种操作。86系列汇编语言指令语句格式如图 5.1 所示。 图中由前向后的箭头表示是可选项, 由后向前的箭头表示是重 复项, 圆头方框表示是语句中的关键字。

下面主要以MOV指令为例, 介绍86系列CPU的寻址方式。

06.08.2020

8

微机原理及应用 吴丽娟

MOV指令的功能 格式:MOV 目的操作数(dest) , 源操作数(src)

06.08.2020

9

微机原理及应用 吴丽娟

1. 立即数寻址

8086 CPU指令系统中, 有一部分指令所用的8位或16位操作

06.08.2020

3

微机原理及应用 吴丽娟

(1) 标号是给该指令所在地址取的名字, 必须后跟冒号“:”, 它可 以缺省, 是可供选择的标识符。86系列汇编语言中可使用的标 识符必须遵循下列规则:

南邮数电第5章6序列信号发生器.ppt

Q3 Q2 Q1 状态转移路线 模数 1 01

0 10 1 00 0 00

M=4 ×

0 01

0 10

需增加一个触发器! 取n=4,重新列状态转移表

Q4 Q3 Q2 Q1 状态转移路线 模数

101 0

010 0 100 0

M=6

000 1

√

001 0

010 1

101 0

(3) 求激励函数

Qn4 Qn3 Qn2 Qn1 Qn4+1 Qn3+1 Qn2+1 Qn+11 D1

解:方法一:用小规模器件实现 (1)设计M=8的计数器,方法同前面的同 步(异步)计数器的设计。 本解取n=3 的异步二进制加法计数器 (2)设计组合电路

组合电路真值表为:

Q3

Q2

Q1 F

0

0

01

0

0

11

0

1

01

0

1

11

1

0

00

1

0

11

1

1

00

1

1

11

用卡诺图化简得到:F=Q3+Q1

逻辑图为:

5

的n位码就是起跳状态。

表 2-4线译码器的真值表

Q2

Q1

Y0

Y1

Y2

Y3

0

0

1

0

0

0

0

1

0

1

0

0

1

0

0

0

1

0

1

1

0

0

0

1

Q2

Q1

1J

1J

C1

C1

1K

1K

最新南邮微机原理课件第5章备课讲稿

定位参数,链接参数,‘分类名’

பைடு நூலகம்为段定义语句的3个属性参数,可以选用1~3个,也可以全部省略。

属性参数的功能: 为源程序的汇编、链接提供必要的信息。

(1) 定位参数 定位参数通知链接程序,逻辑段的目标代码在存储器中如何存放。

① BYTE字节地址:表明该逻辑段的目标代码可以从任意地址开始依次存放;

② WORD 字地址:表示该逻辑段的目标代码,从偶地址开始依次存放;

.486

;方式定义

DATA SEGMENT USE16

;定义数据段

MESG DB ‘HELLO’,0DH,0AH,’$’

CS

DATA ENDS

CODE BEG: LAST:

CODE

SEGMENT USE16

ASSUME CS:CODE,DS:DATA

MOV

AX,DATA

MOV

DS,AX

MOV CX,10

(2) 链接参数 链接又称组合,链接参数通知链接程序如何将不同模块中的同名逻辑段组合 成一个段

① PUBLIC:通知链接程序,把不同模块中具有PUBLIC属性的同名段,在 满足定位方式前提下,按照指定的链接顺序进行链接,组成一个逻辑段;

② MEMORY:实验证明 MEMORY属性和 PUBLIC属性是等价的; ③ COMMON:通知链接程序,把不同模块中,具有 COMMON 属性的同名 段,根据指定的链接顺序,按照 “覆盖” 方式组合成一个逻辑段。组合之后 的逻辑段体积,等于链接之前具有 COMMON 属性同名段中最大的段体;

南邮微机原理课件第5章

5.1 宏汇编语言的开发过程

编辑程序

Edit 等

. ASM 文件

汇编程序

微机原理课件 Chapter 5

5

Principle and System Design of Microcomputer Xidian University

5.1 Simple Interface and Interface Chips

• Latch

• 74LS373 (Octal latch with 3-state outputs, level triggered)

• • • • Two Groups (Group A and Group B) Each group contains one 8-bit port and one 4-bit control/data port. The 8-bit data port can be either input or output. Both inputs and outputs are latched. The 4-bit port is used for control and status of the 8-bit port.

15

Principle and System Design of Microcomputer Xidian University

5.2 Programmable Parallel Interface Chip 8255

• 5.2.2 Operating Mode • Mode 0 - Basic Input/Output

4

Principle and System Design of Microcomputer Xidian University

5.1 Simple Interface and Interface Chips

• Latch

• 74LS273 (Octal latch without 3-state outputs)

微机原理第五次课ppt

16 Z y1 = ±ε = = 4 2p 2×2

y = yk = 1

—电机拖动基础—

—电机拖动基础—

(1)先画16根等长、等距的实线,代表各槽上层元件边,再画16 根等长等距的虚线,代表各槽下层元件边。实际上一根实线和 一根虚线代表一个槽,依次把槽编上号,如图所示; (2)根据 y1 ,画出第一个元件的上下层边(1~5槽),令上层边 所在的槽号为元件号; (3)接上换向片,1、2片之间对准元件中心线,之后等分换向器, 定出换向片号; (4)画出第二个元件,上层边在第2槽,与第一个元件的下层边联 接;下层边在第6槽与3号换向联接。按此规律,一直把16个元 件全部联起来。

2.单叠绕组电路图: 为了进一步说明单叠绕组各个元件的联接 次序及其电动势分布情况,按单叠绕组展开图中 元件的联接顺序,可得到如下图所示的绕组电路 图。从图可以看出,每个极下的元件组成 一条 支路,这就是说,单叠绕组的并联支路数正好等 于电机的极数,即 a = p( a 为并联支路对数)。 这是单叠绕组的重要特点之一。

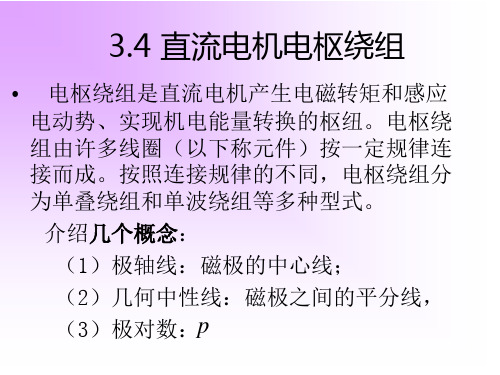

3.4 直流电机电枢绕组

•

电枢绕组是直流电机产生电磁转矩和感应 电动势、实现机电能量转换的枢纽。电枢绕 组由许多线圈(以下称元件)按一定规律连 接而成。按照连接规律的不同,电枢绕组分 为单叠绕组和单波绕组等多种型式。 介绍几个概念 几个概念: 几个概念 (1)极轴线:磁极的中心线; (2)几何中性线:磁极之间的平分线, (3)极对数:p

3.4.1 元件与节距

元件(线圈):是绕组的一个基本单元,可为单匝,也可为多 匝,元件的两个出线端分别接到两片换向片上,并与其他元件相 连。一个元件边放在槽的上层,另一边放在另一槽的下层,因此, 一个槽里总有上下层两个线圈边,称为双层绕组。

1.上元件边 2.下元件边 3.端接部分 4.端接部分 1.槽楔 2.槽壁 3.上元件边 4.隔断 5.槽壁 6.隔断

y = yk = 1

—电机拖动基础—

—电机拖动基础—

(1)先画16根等长、等距的实线,代表各槽上层元件边,再画16 根等长等距的虚线,代表各槽下层元件边。实际上一根实线和 一根虚线代表一个槽,依次把槽编上号,如图所示; (2)根据 y1 ,画出第一个元件的上下层边(1~5槽),令上层边 所在的槽号为元件号; (3)接上换向片,1、2片之间对准元件中心线,之后等分换向器, 定出换向片号; (4)画出第二个元件,上层边在第2槽,与第一个元件的下层边联 接;下层边在第6槽与3号换向联接。按此规律,一直把16个元 件全部联起来。

2.单叠绕组电路图: 为了进一步说明单叠绕组各个元件的联接 次序及其电动势分布情况,按单叠绕组展开图中 元件的联接顺序,可得到如下图所示的绕组电路 图。从图可以看出,每个极下的元件组成 一条 支路,这就是说,单叠绕组的并联支路数正好等 于电机的极数,即 a = p( a 为并联支路对数)。 这是单叠绕组的重要特点之一。

3.4 直流电机电枢绕组

•

电枢绕组是直流电机产生电磁转矩和感应 电动势、实现机电能量转换的枢纽。电枢绕 组由许多线圈(以下称元件)按一定规律连 接而成。按照连接规律的不同,电枢绕组分 为单叠绕组和单波绕组等多种型式。 介绍几个概念 几个概念: 几个概念 (1)极轴线:磁极的中心线; (2)几何中性线:磁极之间的平分线, (3)极对数:p

3.4.1 元件与节距

元件(线圈):是绕组的一个基本单元,可为单匝,也可为多 匝,元件的两个出线端分别接到两片换向片上,并与其他元件相 连。一个元件边放在槽的上层,另一边放在另一槽的下层,因此, 一个槽里总有上下层两个线圈边,称为双层绕组。

1.上元件边 2.下元件边 3.端接部分 4.端接部分 1.槽楔 2.槽壁 3.上元件边 4.隔断 5.槽壁 6.隔断

微机原理与接口技术-第5章ppt课件

.

9

§5-1 存储器分类

二、按性质分类 :随机存取存储器、只读存储器

1. RAM随机存取存储器(Random Access Memory)

CPU能将数据随机地写入或读出RAM 。断电所存数据全 部丢失。通常所说的内存容量大小,是指RAM存储器的容量。

⑴SRAM--静态RAM(Static RAM) :

速度非常快,不断电内容不自动消失。集成度相对较低, 功耗也较大,高速缓冲存储器(Cache memory)用它组成。

⑵DRAM--动态RAM(Dynamic RAM):

DRAM的内容在10-3或l0-6秒之后自动消失,必须周期性的 在内容消失之前进行刷新(Refresh)。集成度高,成本较低,耗 电 少 , 但 需 要 刷 新 电 路 。 DRAM 运 行 速 度 较 慢 , SRAM 比 DRAM要快2~5倍,一般,PC机的标准存储器都采用DRAM组 成。

存储器是用来存放程序和数据的部件 存储器的容量和存取速度是决定计算机性能

的重要指标。 存储器的容量越大,记忆的信息也就越多,

计算机的功能也就越强。

2020/4/23

.

4

§5-1 存储器分类 ——概述

地址译码器 地址总线

地址

内容

0000H 0001H 0002H

XXXXH

读写控制总线

数据总线

存储器的逻辑结构示意图

8086系统,20条地址总线,可以寻址内存空间为1M字节; 80386系统,32条地址总线,可以寻址4GB字节。 存放内容:系统软件(系统引导程序、监控程序或者操作系统 中的ROM BIOS等)以及当前要运行的应用软件。

2020/4/23

.

7

§5-1 存储器分类

南京邮电大学电路分析基础_第5章1

4 .电容是储能元件

电压电流参考方向关联时,电容吸收功率 p(t) u(t)i(t) u(t)C du dt

p 可正可负。当 p > 0 时,电容吸收 功率(吞),储存电场能量增加;当p

< 0时,电容发出功率(吐),电容放 出存储的能量。

任意时刻t得到的总能量为

t

t

wC (t)

p( )d

i +

uS/mV + 10

uS -

Lu -

0

-10

(a)

1 2 3t (b)

解: 当0<t1s时,u(t)=10mV,

i(t) 1

t

u( )d

L

i(0) 2102

t

10

2

d

0

2t

A

2t

A

0

当 t 1s 时 i(1) 2A

当1s<t2s时,u(t)=-10mV

i(t)

,

i(1)

2. 电感是惯性元件

di

u 有限时,电流变化率 dt 必然有限; 电流只能连续变化而不能跳变。

3.电感是记忆元件

i(t) 1

t

u( )d

L

电感电流i有“记忆”电压全部历史

的作用。取决于电压(, t )的值。

i(t) 1

t

u( )d

L

1

t0 u()d 1

t

u( )d

L

L t0

上式也可以理解为什么电容电压不 能轻易跃变,因为电压的跃变要伴随 储能的跃变,在电流有界的情况下, 是不可能造成电场能发生跃变和电容 电压发生跃变的。

例1 C =4F,其上电压如图(b),试求

微机原理第5版(周荷琴)第五章.pptx

例 5.4 用1K×4的SRAM芯片2114构成4K×8的存储器。 先作位扩展, 2 片 2114并接成一组 1KB存储器;再对 4 组作字扩展,用24译码器对这4组进行片选。

3. 形成片选信号的三种方法 1)线选法

用某1位高位地址做片选,低位地址与芯片地址线相连

实现片内寻址。电路简单但空间浪费大,因部分地址 线未参与译码,会地址重叠和地址不连续。 例5.5 有2块2764 EPROM芯片,用线选法对它们进行寻 址。画出译码电路示意图,并列出地址范围。 2764 容 量 8KB=23×210=213 字 节 , 共 有 13 根 地 址 线 A12A0。可在地址总线A19A13中任选2根作线选译码 信号,当然地址范围会不同。 CE 让A13、A14接芯片1、2的片选 端,A12A0接芯片1、 2的地址线A12A0 ,就实现了线选法寻址。 这样, A13=0 选中 2764(1) , A14=0 选中 2764(2) 。它们 不能同时选中。A12A0从000H变到FFFH,就能顺序 访问被选中芯片中的8K个字节。

2)字扩展

芯片位数已符合,只要增加地址范围,即字扩展增加

字数或容量。 例5.3 用16K×8芯片字扩展为64K×8存储器。 用4个芯片,A13A0、D7 D0、WE 线均并联,设计1 个24译码器,为各芯片提供片选信号 CS3 CS0 。

3)字位扩展

存储器芯片的容量和位数都需要进行扩展。

§5.4 存储器与CPU的连接

5.4.1 设计接口应考虑的问题

5.4.2 存储器接口设计

5.4.2 存储器接口设计

1. 地址译码器

存储器由多个芯片构成,CPU进行读/写操作时,

首先应选中特定的芯片,称为片选,然后从该芯 片中选择所要访问的存储单元。片选和访存的信 息,来源于CPU执行存储器读/写指令时,送到地 址总线上的地址信息,其中的高位用来生成片选 信号,低位直接连到芯片的地址线上,去实现片 内寻址。 用高位地址信息实现片选的电路称为地址译码器, 有门电路译码器、 N中取一译码器和 PLD( Programmable Logic Device,可编程逻辑器件)译码 器等几种。如果用 FPGA 设计硬件系统,还可用 FPGA芯片的一部分来实现地址译码。 74LS138是常用的8中取1译码器。

微机原理课件0 Contents

微机原理与应用—课程目录

第0章 课程介绍

第0讲 性质、作用与教学计划

第1章 计算机基础

第1讲 计算机概述 第2讲 计算2讲 存储器组织和I/O组织 第3讲 引脚及其功能 第4讲 系统组织与工作时序

第3章 指令系统

第1讲 寻址方式 第2 讲 数据传送指令 第3讲 运算与移位指令 第4讲 串操作与控制转移指令

第4章 汇编语言程序设计

第1讲 宏汇编语言基本语法 第2讲 伪指令与宏指令 第3讲 DOS功能调用与程序调试 第4讲 汇编语言程序设计方法

第5章 微机存储器系统

第1讲 存储器概述 第2讲 存储器与CPU的连接

第6章 基本输入输出接口 第7章 中断控制接口

第1讲 8086中断系统 第2讲 可编程中断控制器8259A

第8章 并行通信接口 第9章 串行通信接口 第10章 定时计数控制接口

北京工业大学 电子信息与控制工程学院

第0章 课程介绍

第0讲 性质、作用与教学计划

第1章 计算机基础

第1讲 计算机概述 第2讲 计算2讲 存储器组织和I/O组织 第3讲 引脚及其功能 第4讲 系统组织与工作时序

第3章 指令系统

第1讲 寻址方式 第2 讲 数据传送指令 第3讲 运算与移位指令 第4讲 串操作与控制转移指令

第4章 汇编语言程序设计

第1讲 宏汇编语言基本语法 第2讲 伪指令与宏指令 第3讲 DOS功能调用与程序调试 第4讲 汇编语言程序设计方法

第5章 微机存储器系统

第1讲 存储器概述 第2讲 存储器与CPU的连接

第6章 基本输入输出接口 第7章 中断控制接口

第1讲 8086中断系统 第2讲 可编程中断控制器8259A

第8章 并行通信接口 第9章 串行通信接口 第10章 定时计数控制接口

北京工业大学 电子信息与控制工程学院

微机原理-第5版(周荷琴)-第五章-(4)PPT课件

CPU总线的负载能力

总线直接驱动负载的能力超过后会影响信号逻辑电 平。例如8086能驱动5个74LS系列TTL逻辑元件,或 10个74HC系列CMOS逻辑元件。应在总线和负载间 接缓冲器或驱动器,如74LS244、74LS245等,增大 CPU负载能力,即减小信号电平变化时加到总线的 电流值,不至影响信号逻辑电平。

CPU时序与存储器存取速度间的配合

CPU要对存储器频繁读/写,选芯片时要考虑其存取 速度能否与CPU读/写时序匹配。

2021

中国科学技术大学

5.4 存储器连接

5.4.1 设计接口应考虑的问题

第5章 存储器

存储器的地址分配和片选

设计时,首先根据所用CPU特点和系统需求,确 定内存总量,然后布局,为存储器分配地址范围。 由于每块芯片存储容量有限,一个存储器系统由 多块芯片组成,要重点考虑容量的扩充方案和片 选信号的形成。

个24译码器,为各芯片提供片选信号CS3 CS0 。

2021

中国科学技术大学

5.4 存储器连接

第5章 存储器

3)字位扩展

存储器芯片的容量和位数都需要进行扩展。 例 5.4 用1K×4的SRAM芯片2114构成4K×8的存储器。 ➢ 先作位扩展,2片2114并接成一组1KB存储器;再对4组

作字扩展,用24译码器对这4组进行片选。

2021

中国科学技术大学

5.4 存储器连接

第5章 存储器

A19A15未参与译码,可以是0000011111中任意编码,图 中是A19A15=00000时的地址范围。

这 5 位 有 25=32 个 编 码 , 会 形 成 许 多 地 址 重 叠 区 , 例 如 8400085FFFH 、 C4000C5FFFH 等 地 址 都 会 选 中 芯 片 2764(1)。

总线直接驱动负载的能力超过后会影响信号逻辑电 平。例如8086能驱动5个74LS系列TTL逻辑元件,或 10个74HC系列CMOS逻辑元件。应在总线和负载间 接缓冲器或驱动器,如74LS244、74LS245等,增大 CPU负载能力,即减小信号电平变化时加到总线的 电流值,不至影响信号逻辑电平。

CPU时序与存储器存取速度间的配合

CPU要对存储器频繁读/写,选芯片时要考虑其存取 速度能否与CPU读/写时序匹配。

2021

中国科学技术大学

5.4 存储器连接

5.4.1 设计接口应考虑的问题

第5章 存储器

存储器的地址分配和片选

设计时,首先根据所用CPU特点和系统需求,确 定内存总量,然后布局,为存储器分配地址范围。 由于每块芯片存储容量有限,一个存储器系统由 多块芯片组成,要重点考虑容量的扩充方案和片 选信号的形成。

个24译码器,为各芯片提供片选信号CS3 CS0 。

2021

中国科学技术大学

5.4 存储器连接

第5章 存储器

3)字位扩展

存储器芯片的容量和位数都需要进行扩展。 例 5.4 用1K×4的SRAM芯片2114构成4K×8的存储器。 ➢ 先作位扩展,2片2114并接成一组1KB存储器;再对4组

作字扩展,用24译码器对这4组进行片选。

2021

中国科学技术大学

5.4 存储器连接

第5章 存储器

A19A15未参与译码,可以是0000011111中任意编码,图 中是A19A15=00000时的地址范围。

这 5 位 有 25=32 个 编 码 , 会 形 成 许 多 地 址 重 叠 区 , 例 如 8400085FFFH 、 C4000C5FFFH 等 地 址 都 会 选 中 芯 片 2764(1)。

南邮微机原理课件第5章

④ STACK: 具有STACK属性的逻辑段是堆栈段,链接程序将把不同模块中 具有STACK属性的同名段链接成一个大的堆栈段。链接后的堆栈空间是链 接前各模块预留的堆栈空间之和。 程序装入后,DOS自动给SS寄存器赋值,使之等于堆栈段段基址,自动给SP赋 值,使之等于堆栈空间的字节数,使 SS:SP自动指向栈顶。 链接程序要求:EXE文件的汇编源程序,必须有堆栈段,否则链接时发出警告 信息:

③ PARA (或者缺省) 节地址:表示该逻辑段的目标代码,从一个能被16整除 的地址开始依次存放;

④ PAGE 页地址:表示该逻辑段的目标代码,从一个能被256整除的地址开 始依次存放。

注意:

链接程序对于不同模块中的同名段进行链接时,对于有BYTE属性的段,总 是紧接着前一段存放,不留空闲单元。对于有WORD属性的段,也是紧接前一 段存放,最多留出一个空闲单元。

INT 21H

LOOP LAST

MOV AH,4CH

INT 21H

;返回DOS

CODE ENDS

END BEG

;汇编结束

•

1、有时候读书是一种巧妙地避开思考 的方法 。20.1 2.1220. 12.12Sa turday, December 12, 2020

•

2、阅读一切好书如同和过去最杰出的 人谈话 。12:4 0:4612: 40:4612 :4012/ 12/2020 12:40:46 PM

定位参数,链接参数,‘分类名’

为段定义语句的3个属性参数,可以选用1~3个,也可以全部省略。

属性参数的功能: 为源程序的汇编、链接提供必要的信息。

(1) 定位参数 定位参数通知链接程序,逻辑段的目标代码在存储器中如何存放。

① BYTE字节地址:表明该逻辑段的目标代码可以从任意地址开始依次存放;

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

南邮微机原理第5章

(2) 链接参数 链接又称组合,链接参数通知链接程序如何将不同模块中的同名逻辑段组合 成一个段

① PUBLIC:通知链接程序,把不同模块中具有PUBLIC属性的同名段,在满 足定位方式前提下,按照指定的链接顺序进行链接,组成一个逻辑段;

② MEMORY:实验证明 MEMORY属性和 PUBLIC属性是等价的; ③ COMMON:通知链接程序,把不同模块中,具有 COMMON 属性的同名 段,根据指定的链接顺序,按照 “覆盖” 方式组合成一个逻辑段。组合之后的逻 辑段体积,等于链接之前具有 COMMON 属性同名段中最大的段体;

南邮微机原理第5章

1. 方式选择伪指令

功能: 通知汇编程序,当前的源程序指令是哪一种CPU指令,经过汇编链接之后生成的目 标程序在哪一种CPU机型上运行。 不属于选定CPU的指令均为非法指令。80486指令集是在8086、8088、80286、 80386基础上逐步发展起来的,很显然,80486的某些指令在早期的80X86系列是没有 的,为了使汇编程序能够识别,在高版本的汇编程序中,对应于每一种CPU的指令系统, 都有一个目标指令的集合。

② WORD 字地址:表示该逻辑段的目标代码,从偶地址开始依次存放;

③ PARA (或者缺省) 节地址:表示该逻辑段的目标代码,从一个能被16整除 的地址开始依次存放;

④ PAGE 页地址:表示该逻辑段的目标代码,从一个能被256整除的地址开始 依次存放。

注意:

链接程序对于不同模块中的同名段进行链接时,对于有BYTE属性的段,总 是紧接着前一段存放,不留空闲单元。对于有WORD属性的段,也是紧接前一 段存放,最多留出一个空闲单元。

南邮微机原理第5章

④ STACK: 具有STACK属性的逻辑段是堆栈段,链接程序将把不同模块中具 有STACK属性的同名段链接成一个大的堆栈段。链接后的堆栈空间是链接 前各模块预留的堆栈空间之和。

程序装入后,DOS自动给SS寄存器赋值,使之等于堆栈段段基址,自动给SP赋 值,使之等于堆栈空间的字节数,使 SS:SP自动指向栈顶。

南邮微机原理第5章

指令以句号开头, 格式和功能如下:

· 8086

;只汇编8086、8088指令。

· 286或 ·286C ;只汇编8086、8088及80286实模式指令

· 286P

;只汇编8086、8088及80286全部指令

· 386或 ·386C ;同·286,且汇编80386实模式指令

· 386P

21H

LOOP LAST

MOV AH,4CH

INT

21H

;返回DOS

ENDS END BEG

南邮微机原理第5章;汇编结束

‘H’ ‘E’ ‘L’ ‘L’

‘O’ DS

0D 0A ‘$’

1. 方式选择伪指令 2. 段定义语句 3. 段约定语句 4. 过程定义语句 5. 汇编结束语句 6.返回DOS语句 这类语句是与程序结构密切相关的基本语句,用来说明 MPU类型、段结构与寻址方式的段约定、目标块的定位和 源程序结束。

链接程序要求:EXE文件的汇编源程序,必须有堆栈段,否则链接时发出警告 信息:

Warning no stack segment 这行信息仅仅是提醒用户注意,并不表示源程序有什么错误。

南邮微机原理第5章

⑤ AT 表达式: 该属性表明:逻辑段在定位时,其段基址等于表达式给出的值。

AT属性常和 ORG伪指令配合

CS

DATA ENDS

CODE BEG: LAST:

CODE

SEGMENT USE16

;定义代码段

ASSUME CS:CODE,DS:DATA ;说明段约定

MOV AX,DATA MOV DS,AX

;BEG为启动地址 MESG

MOV CX,10

MOV AH,9

MOV DX,OFFSET MESG

INT

如: DATA SEGMENT AT 0040H

ORG 0017H

KEYFLAG DB ?

DATA

南邮微机原理第5章

定位参数,链接参数,‘分类名’

为段定义语句的3个属性参数,可以选用1~3个,也可以全部省略。

属性参数的功能: 为源程序的汇编、链接提供必要的信息。

南邮微机原理第5章

(1) 定位参数 定位参数通知链接程序,逻辑段的目标代码在存储器中如何存放。

① BYTE字节地址:表明该逻辑段的目标代码可以从任意地址开始依次存放;

;同·286P,且汇编80386全部指令

· 486或 ·486C ;同·386,且汇编80486实模式指令

· 486P

;同·386P,且汇编80486全部指令

通常,方式选择伪指令放在程序的头部,做为源程序的第一条语句。不设置方式选 择伪指令与设置·8086是等价的。

南邮微机原理第5章

2. 段定义语句 功能:

器类型; 用段定义语句定义每一个逻辑段; 用过程定义语句定义每一个子程序; 用ASSUME语句说明段约定; 用汇编结束语句说明源程序结束; 程序在完成预定功能之后,应能安全返回DOS。

南邮微机原理第5章

.486

;方式定义

DATA SEGMENT USE16

;定义数据段

MESG DB ‘HELLO’,0DH,0AH,’$’

是逻辑段的定界语句,源程序中每一个逻辑段都必须用段定义语句定界。

段定义语句格式如下:

段名 SEGMENT 定位参数 链接参数 ‘分类名’ 段长度 段体

段名 ENDS

SEGMENT/ENDS

是一对段定义语句,一个逻辑段从SEGMENT语句开始,到ENDS语句结束。 段名 命名规则和变量名及标号名一样,它不能代表段体的性质,但为了 阅读方便,习惯上总是根据段体的性质起一个适当的段名。通常用DATA做 为数据段的段名,用STACK做为堆栈段的段名,CODE为代码段的段名。

第5章 宏汇编语言

5.1 宏汇编语言的开发过程 5.2 宏汇编语言基本语句

南邮微机原理第5章

5.1 宏汇编语言的开发过程

编辑程序

Edit 等

. ASM 文件

汇编程序

TMASM

. OBJ 文件

Байду номын сангаас

连接程序

TLINK

. EXE 文件

南邮微机原理第5章

5.2 宏汇编语言基本语句

5.2.1 源程序的结构

一个完整的源程序在结构上必须做到: 用方式选择伪指令说明执行该程序的微处理

(2) 链接参数 链接又称组合,链接参数通知链接程序如何将不同模块中的同名逻辑段组合 成一个段

① PUBLIC:通知链接程序,把不同模块中具有PUBLIC属性的同名段,在满 足定位方式前提下,按照指定的链接顺序进行链接,组成一个逻辑段;

② MEMORY:实验证明 MEMORY属性和 PUBLIC属性是等价的; ③ COMMON:通知链接程序,把不同模块中,具有 COMMON 属性的同名 段,根据指定的链接顺序,按照 “覆盖” 方式组合成一个逻辑段。组合之后的逻 辑段体积,等于链接之前具有 COMMON 属性同名段中最大的段体;

南邮微机原理第5章

1. 方式选择伪指令

功能: 通知汇编程序,当前的源程序指令是哪一种CPU指令,经过汇编链接之后生成的目 标程序在哪一种CPU机型上运行。 不属于选定CPU的指令均为非法指令。80486指令集是在8086、8088、80286、 80386基础上逐步发展起来的,很显然,80486的某些指令在早期的80X86系列是没有 的,为了使汇编程序能够识别,在高版本的汇编程序中,对应于每一种CPU的指令系统, 都有一个目标指令的集合。

② WORD 字地址:表示该逻辑段的目标代码,从偶地址开始依次存放;

③ PARA (或者缺省) 节地址:表示该逻辑段的目标代码,从一个能被16整除 的地址开始依次存放;

④ PAGE 页地址:表示该逻辑段的目标代码,从一个能被256整除的地址开始 依次存放。

注意:

链接程序对于不同模块中的同名段进行链接时,对于有BYTE属性的段,总 是紧接着前一段存放,不留空闲单元。对于有WORD属性的段,也是紧接前一 段存放,最多留出一个空闲单元。

南邮微机原理第5章

④ STACK: 具有STACK属性的逻辑段是堆栈段,链接程序将把不同模块中具 有STACK属性的同名段链接成一个大的堆栈段。链接后的堆栈空间是链接 前各模块预留的堆栈空间之和。

程序装入后,DOS自动给SS寄存器赋值,使之等于堆栈段段基址,自动给SP赋 值,使之等于堆栈空间的字节数,使 SS:SP自动指向栈顶。

南邮微机原理第5章

指令以句号开头, 格式和功能如下:

· 8086

;只汇编8086、8088指令。

· 286或 ·286C ;只汇编8086、8088及80286实模式指令

· 286P

;只汇编8086、8088及80286全部指令

· 386或 ·386C ;同·286,且汇编80386实模式指令

· 386P

21H

LOOP LAST

MOV AH,4CH

INT

21H

;返回DOS

ENDS END BEG

南邮微机原理第5章;汇编结束

‘H’ ‘E’ ‘L’ ‘L’

‘O’ DS

0D 0A ‘$’

1. 方式选择伪指令 2. 段定义语句 3. 段约定语句 4. 过程定义语句 5. 汇编结束语句 6.返回DOS语句 这类语句是与程序结构密切相关的基本语句,用来说明 MPU类型、段结构与寻址方式的段约定、目标块的定位和 源程序结束。

链接程序要求:EXE文件的汇编源程序,必须有堆栈段,否则链接时发出警告 信息:

Warning no stack segment 这行信息仅仅是提醒用户注意,并不表示源程序有什么错误。

南邮微机原理第5章

⑤ AT 表达式: 该属性表明:逻辑段在定位时,其段基址等于表达式给出的值。

AT属性常和 ORG伪指令配合

CS

DATA ENDS

CODE BEG: LAST:

CODE

SEGMENT USE16

;定义代码段

ASSUME CS:CODE,DS:DATA ;说明段约定

MOV AX,DATA MOV DS,AX

;BEG为启动地址 MESG

MOV CX,10

MOV AH,9

MOV DX,OFFSET MESG

INT

如: DATA SEGMENT AT 0040H

ORG 0017H

KEYFLAG DB ?

DATA

南邮微机原理第5章

定位参数,链接参数,‘分类名’

为段定义语句的3个属性参数,可以选用1~3个,也可以全部省略。

属性参数的功能: 为源程序的汇编、链接提供必要的信息。

南邮微机原理第5章

(1) 定位参数 定位参数通知链接程序,逻辑段的目标代码在存储器中如何存放。

① BYTE字节地址:表明该逻辑段的目标代码可以从任意地址开始依次存放;

;同·286P,且汇编80386全部指令

· 486或 ·486C ;同·386,且汇编80486实模式指令

· 486P

;同·386P,且汇编80486全部指令

通常,方式选择伪指令放在程序的头部,做为源程序的第一条语句。不设置方式选 择伪指令与设置·8086是等价的。

南邮微机原理第5章

2. 段定义语句 功能:

器类型; 用段定义语句定义每一个逻辑段; 用过程定义语句定义每一个子程序; 用ASSUME语句说明段约定; 用汇编结束语句说明源程序结束; 程序在完成预定功能之后,应能安全返回DOS。

南邮微机原理第5章

.486

;方式定义

DATA SEGMENT USE16

;定义数据段

MESG DB ‘HELLO’,0DH,0AH,’$’

是逻辑段的定界语句,源程序中每一个逻辑段都必须用段定义语句定界。

段定义语句格式如下:

段名 SEGMENT 定位参数 链接参数 ‘分类名’ 段长度 段体

段名 ENDS

SEGMENT/ENDS

是一对段定义语句,一个逻辑段从SEGMENT语句开始,到ENDS语句结束。 段名 命名规则和变量名及标号名一样,它不能代表段体的性质,但为了 阅读方便,习惯上总是根据段体的性质起一个适当的段名。通常用DATA做 为数据段的段名,用STACK做为堆栈段的段名,CODE为代码段的段名。

第5章 宏汇编语言

5.1 宏汇编语言的开发过程 5.2 宏汇编语言基本语句

南邮微机原理第5章

5.1 宏汇编语言的开发过程

编辑程序

Edit 等

. ASM 文件

汇编程序

TMASM

. OBJ 文件

Байду номын сангаас

连接程序

TLINK

. EXE 文件

南邮微机原理第5章

5.2 宏汇编语言基本语句

5.2.1 源程序的结构

一个完整的源程序在结构上必须做到: 用方式选择伪指令说明执行该程序的微处理