第九章基于DSP应用系统的硬件设计举例

dsp硬件系统设计

LF240x/240xA DSP数据总线驱动能力为4mA,地址总线 驱动能力为2mA。在总线负载较重的情况下,应使用 总线缓冲器增强驱动能力。

总线驱动电路

74LVTH245驱 动能力可达32mA

八、总线驱动及I/O接口电路扩充设计

I/O接口电路扩充设计: 方法: 1、采用TTL电路或CMOS电路的三态缓冲器、触发器和 锁存器等构成简单I/O口 2、采用通用I/O集成芯片或可编程逻辑器件构成外部I/O 口 在进行简单设计时,应遵循“输入三态、输出锁存”与 总线相连的设计原则,即输入口可使用三态缓冲器或 带有三态输出的锁存器,而输出口只能使用锁存器, 否则将无法保留所送信号。

1频率2信号电平3时钟的沿特性4驱动能力5采用有源晶振还是无源晶振用户布线时应确保由时钟走线芯片以及旁路电容组成的回路区域尽可能地小时钟走线尽可能地短且直以减少电磁干扰同时避免高频噪声的干扰复位电路设计tms320lf240x240xa系列dsp为低电平复位tms320lf2407a内部带有复位电路因此可以直接在rs复位引脚外面接一个10k的上拉电阻

十、DSP与A/D、D/A的接口

3、电平问题 4、原理图设计 5、设计印制电路板图(PCB)

二、3.3V和5V混合逻辑系统设计

1、各种电平转换标准

二、3.3V和5V混合逻辑系统设计

2、3.3V和5V器件接口的四种情况

三、电源转换电路设计

TMS320LF240x/240xA系列DSP为低功耗系列,所有引脚 中除VCCP引脚在对Flash编程时接5V电压外,其他供 电电源引脚供电电压均为3.3V。这些供电电源分成三部 分: 1、PLL供电电压PLLVccA 2、ADC模块模拟供电电压VccA 3、数字逻辑和I/O缓冲器电源电压VDD/VDD0 模拟电压与数字电压要分开供电,模拟地与数字地也要分 开,

(DSP处理器原理与应用)第9章DSP系统硬件设计

本章将介绍DSP处理器硬件设计的基本概念,包括DSP芯片的特点和功能, DSP硬件系统的架构设计,和DSP芯片的初始设置和配置。

模块化设计与DSP硬件系统

设计原则

模块化设计提高可维护性和可重用性,减少错误和开发时间。

案例研究

通过实际案例分析模块化设计在DSP系统中的应用和优势。

最佳实践

探讨如何合理划分模块并实现模块之间的通信和数据传输。

DSP系统时钟与定时器设计

1 时钟源选择

讨论选择合适的时钟源以满足DSP系统的时序和性能要求。

2 时钟稳定性

详解外部时钟源的频率和稳定性的要求以及如何保证。

3 定时器设计

介绍DSP系统中定时器的功能和设计方法。

强大的DSP输入/输出接口

功率分配

讨论如何合理分配和管理DSP系 统中的功率。

2

存储器容量和速度

讨论如何根据DSP系统的需求,选择合适的存储器容量和速度。

3

存储器优化

提供存储器布局和访问优化的技巧和方法。

外设接口设计与优化

串行接口

• I2C • SPI • UART

并行接口

• GPIO • PCI • ISA

高速接口

• USB • Ethernet • HDMI

中断系统的设计与实现

输入接口设计

深入探Байду номын сангаасDSP系统输入接口的设 计原则和常见的输入接口类型。

输出接口设计

讨论DSP系统输出接口的设计方 案和常用的输出接口类型。

显示接口设计

介绍DSP系统显示接口的设计要 求和实现方法。

高效的DSP存储器设计

1

MS320C55x DSP应用系统设计PPT课件

如300MHz的C55x与120MHz的

C54x相比,C55x的处理速度比

C54x提高了5倍,功耗降到只有

C54x的1/6。

24

表1-1 C55x与C54x的比较

C54x

C55x

MAC 累加器 读总线 写总线 程序提取 地址总线 程序字长 数据字长 辅助寄存器ALU ALU 辅助寄存器 数据寄存器 存储器空间

高度集成化

模间拟只混有合66式uSD。SP芯片已有较大的发展和应用。 D具SP有的较字完长善从的8位软已件增和加硬到件6开4位发,工累具加,器如的:长软度件也仿真

增器加Si到mu4l0a位to,r、从在而线提仿高真了器运E算mu精la度to。r、同C时编,译采器用和集

运算精度和动态超成长范开字发围指环令境字CC(S等VL,IW给)开结发构应和用高带性来能很的大浮方点便运。算C,CS

第三阶段,DSP的完善阶段(2000年以后)

➢ 信号处理能力更加完善,而且使系统开发更加方便 、程序编辑调试更加灵活、功耗进一步降低、成本 不断下降

➢ 各种通用外设集成到片上,大大地提高了数字信号 处理能力

➢ DSP运算速度可达到单指令周期10ns左右,可在 Windows 下用C语言编程,使用方便灵活

实现数字信号处理算法的微处理器芯片

1.2 DSP芯片简介

DSP芯片的发展历史、现状和趋势 DSP芯片的特点 DSP芯片的分类 DSP芯片的应用领域 选择DSP芯片考虑的因素

8

1.2.1 DSP芯片的发展历史、现状和趋势

发展历史

诞生于20世纪70年代末 第一阶段,DSP的雏形阶段(1980年前后)

为16位定点整数 DSP处理器 迄今已有三代产品,即:

TMS320C5x、TMS320C 54x和TMS320C55x 同代产品具有相似的CPU结构和不同的片上存储器和

基于DSP的嵌入式数字硬盘录像机的硬件设计

邓 贤 君 朱 志 亮

科

基于 D P的嵌入式数字硬盘录像机的硬件设计 S

(、 1 南华大学通信工程 系. 南 衡 阳 4 10 2 温 州大学物理 与电子信息工程学院, 湖 201 、 浙江 温州 3 53 ) 2 0 5

摘 要: 本文提 出了基 于 T 3 0 M6 8的数 字硬盘录像机的设计方案 , S 2 D 4 详细介绍 了嵌入式数字硬盘录像机硬件设计。本 系统经 多次现场测 试。 效果 良好 , 符合 实际应用的需要 。 关 键 词 :3 2 1A; 字 硬 盘 录像 机 ; MS 2 D 4 ; 频 监 控 ¥ C 50 数 T 3 0 M6 8

1 述 概 频、 网络 、 信号处理环境。 数字硬盘录像机 , 英文名称为 Dg a Vdo 目前 D 6 8可应 用 于 i t i il e M4 R cre, eodr简称 D R, V 它是视频监控系统中重要的 I 频 电 话 ( d P P视 Vie I o 设备, P oe、 O ( ie n hn )V D Vd O o mad 、 机。 前l盘录鬃乩 牛 目 匝 架构 E 分主要分为工控 De n ) 机 顶 盒 式硬盘录像机( 或者工控硬盘录像机或者 P 式硬 (e U oe)视 频 监 C St pB xs、 — 盘录像机 ) ^式硬盘录像机, 、 嵌 从压缩算法来分有 控数字录像机等开发系 小波压缩 。J E MP G ,I 4等。目前工控式 统 ,I M P G, E 4I - 26 T 公司提供了相应的 图 1 主控 制模 块 设 计 框 图 硬盘录像机和嵌入式硬盘录像机所占市场比重差 船 D 4 8 留了 M6 保 不多,由于嵌 人 式硬盘录像机的稳定性及易维护 C X 4 6 原有的内核结构 , 工作频率由内 部倍频器设 口 出。 性, 选择嵌 入 式硬盘录像机的用户会越来越多, 市 置 , 可以达 到 7 0 H 、 0 H 或 90 H , 2 M z 0 M z 0 M z相应 8 T P 4 V 5 5 A具有 4 1 个通道 , 每个通道均为具 场前景非常大。基于这种应用背景, 本文提出了 嵌 的时钟周期为 19 s1 5 s 1 s每秒可执行 有可编程多态换算器 ( l o h a r的独立 3 n、2 n 或 .1 , 1n p y r i s l) om p c c e 人武融 录像机的设计 思路和实现方案。 指令数 5 6 、4 o 7 0 MIS 7 06 o 和 2 0 P 。此外 D 4 8片 解码器, 萌 M6 可j 过嵌 入 式同步模块将 N S 、A T C P L或 2系统 总 体方案 上带有 5 个双通道( B两通道 ) A、 数字视频 口( P S C v E AM视频信号转换成 8位 IU R B . 6格 — T 5 r 6 2 . 1技术指标 口)可同时处理多路数字视频流, 匕 , 片 带有多通道 式 , 或使用分立同步模块使输出格式为 8位 4 : 2 "。 2 本系统的主要技术指标如下 : 串行音频接口,可同时处理 l 路立体声输入, O 输 5P B设 计 C 视频输 入:6路复合视频输 入P LN S 1 A /TC 出音 . 号。 f 言 本系统的主频高达 1 M z 属于高频系统 , 6 H, 6 视 频输 出 : 复 合视 频输 出 P I T C 2路 A s 4{J 块原理设计 亥 所以在进行 P B的设计时, 保证信号的完整, C 为了 (N B C接 口,. p P 5 ) 1V -, n 0 7 可以划分以下 在设计的时候采用了如下方法: 音频输出:6路音频输 ^2 — 0 mv0 1 0 10 lK .= 『 L : 主控制模块 ;视音频采集 、 a h 压缩 5 . D AM 的时钟线, 1对 DR 尽量走短线 , 而且 模块;视 预 览、 c 回放模块; 块( 电源、 存 到两个 D R M 的长度尽量做到相等; n CA ) DA 音频 输 出 : 2路音 频输 出 ,0 10 v Kn 储器扩展 、 2—0m, l 网络传输、 逻辑控制等) 。 5 L S 等其f夕 不要直接与数据和地 2F A H 电 } C ) A 本文详细介绍主控制模块和视频处理模块的 址 总 线 连 接 ,而 是 通 过 缓 冲 芯 片 ( 如 2 2设计方案 设 计。 S 7 L T 6 4 B 连授 ; N 4V 1251 根据系统要求的技术指标 , 本文没计的 l 路 6 4 . 1主控制模块 5 3高速总线 E 串人了小阻值电阻 阻值大小 嵌入式 D R系统硬件部分采用了主从式双 C U V P 对整个系统任 通过 Po l r e软件仿真得到, t 同时对线路 进行了阻抗 架构模式。主 C U选用 了AR 处理器 , P M9 具体型 务的运行进行分配与调度 。¥ C 50 3 2 1 A本身内置 限制 。 号为三星半导体的 ¥ C 5O , C U选用 D P P I 3 2 A 从 P I S C 控制器 , 5个 P I 口可分别和 2 C接 个音 , 视频 6结论 处理器具 体型号为美国德州仪器( I T) 的多媒体处 压缩模块, 个图象预览,回放模块, 个数据存储 1 2 本系统最主要的创新点有以下两点: 理芯 片 T 3 0 M6 8 MS 2 D 4 。主从 C U之间 通过 P I 模块连接; P C 再加上它已有的串口, S U B接 口, 网络接 61 .在系统硬件架构上, 采用了主从C U的架 P 总线进行通讯。 口,O等组成整个系统的控制模块。 I / 它的 路 构 , C U和从 C U分工明确 , 主 P P 充分的发挥 了它 所示 。 整个系统的工作流程设计女下:系统上电或 如图 l _t l 们各 自的处理优势; 复位后, C U¥ C 5 0 主 P 3 2 1A从 Fah加载程序, l s 完 4 视音频采集 , . 2 压缩模块 视音频处理方面 , 选用了 耵最新推出的数 成对芯片的初始化和外围硬件的配置, 之后从 C U P 视音频信号处理的流程如下 :模拟视频信号 字多媒体处理器 T S2D 68采用高效率的 H M 30 M , 4 T s2D 68 M 3 O M 4 便开始进行图像采集。从 C U通 先经视频解码器 T P 14 P V 5 5 A转换成 8位 Y V数 2 4 U 6 压缩标准,实现了多通道的视音频数据处理, 过I 2 对系统中的 C口 视频解 码芯片进行控制, 将从 字视频信号 再送至 D 6 8 M 的视频输入接 口 可以充分的满足市场需要 ; 4 . 摄像头采集到的模拟视频信号转换为数字视频信 模拟音频信号经音频 A D转换器 P M10 转换 C 81 参考文献 号, 送人 D 4 M6 8的视频通道 P端 口)同步采集到 为 I ; 2 S格式的音频数据, 进人多媒体压缩芯片的 [ m u g Eet nc o d 3 2 1A 3 一 1 sn lc ois CLt  ̄a r .¥ C 5 0 2 DM 4 T S C R0C S ES OR ER US 的漠 拟音频信号 经过音频编解码器模 / 数转换后 , 音频输入接 口, 6 8将原始的视频和音频数据 BI RI C MI R0P 送人 D 6 8 ̄ M 4 I (c S 端口 。 M 4 将 分别进行压缩, M AP )D 6 8 再把压缩视频流和压缩音频流进 MANUA12 03 ,0 . 接收到的数字视频信号和数字音频信号数据分别 行 同步 复 合 ,产生 I24 视频 复 合 流 .一 片 [tx nt m nsIcroae T 3 0 M6 8 -6 I . E ea Is u e t noprtLMS 2 D 4 / s r c 进行压缩, 再把压缩视频流和压缩音频流进行同 D 4 8可以同时产生 8个视 , M6 音频通道的 H2 Di a d a Pr c s o,0 7 2 0 . . 4 6 st Me i o e s r 0 - 0 9 l 2 步复合, 产生 I2 4视频复合流 , -6 1 . 再通过 P I C 总线 复合数据流. M 4 把每个视 / D 68 音频通道的复合 f苏东. AR 3 】 主流 M嵌入式 系统设计技术与实例精 上传给主 C U 主 C U P , P 将从 P I C 接口收到的数据 视频数据在片外 D R M的数据缓冲区中排列成 解帆 北京: DA 电子工业出版社 以文件的格式存储到本地硬盘 , 日 供 后调用 ; 同步 固定长度的数据包. 当缓冲区内的数据量超过一 f王 跃 宗.MS 2 D 4 S 用 系统设 计 与开 4 ] T 3 0 M6 2D P应 将复合数据流传送给图象预览芯片进行显示。 定 的阀值, 它就通过 P I C 中断向主 C U发 出请 发 北京: P 人民邮电 ̄ d 2 0 , & 0 91 . 3 M 30 M 4 数字信号处理器简介 S2D 68 T 求, 当中断被响应时, C U 从包缓冲区内将数 主 P 作者简介 : 邓贤君(9 1)男, 18一 , 湖南郴州, 南华 T 30 M6 8 耵 公司于 2 o MS 2 D 4 是 0 7年推出的 据取走。 大学电气工程学院通信工程系, 讲师。 主 要研究方 款高性能的 3 位定点 D P主要面向数字媒体 2 S, D 68具有 5 M 4 个视频端口, 支持多种分辨率 向为嵌入式应用, 移动通信技术, P应用。 Ds 应用, 属于 C 0 0 60 系列 D P 此款芯片带有丰富的 和标准, C I 6 1Iu 6 6B .12 So 如 C R 0 、 —B 5 、T 0等, T 1 朱志亮(9 2 )男, 18 ̄ , 浙江温州, 温州大学物理 视音频硬件资源,具有网口、C 接 口、 P 接口、 每个端口为 2 bt PI HI 0 i位宽, 可以被灵活的配置为—个 与电子信. r 学院, g_ 4 ̄ 讲师。主 要研究方向为信号 1C接 口、 2 串行 口等多种接 口, 可广泛应用于视音 2 /6 i或两个 1/bt 01bt 08i通道。同时, 每个端口都 与信 息处理 。

DSP应用系统设计实例教学设计

DSP应用系统设计实例教学设计一、设计背景数字信号处理(DSP)在现代通信和信息处理领域中起着非常重要的作用。

DSP 应用系统设计实例教学针对的是EDA(Electronic Design Automation)领域,通过教学设计,培养学生的设计能力和创新能力,使学生在毕业后具备独立开发DSP 应用设计的实践能力。

二、教学目标1.掌握DSP应用系统设计的基础知识和技能,包括DSP系统结构、编程语言、算法、架构设计等;2.培养学生的应用实践能力,让学生能够运用所学知识实际上机进行设计和开发;3.提高学生的创新能力,鼓励学生自主思考和创新;4.培养学生的团队合作意识和能力,让学生学会沟通、协作和分享。

三、教学方法1.讲授与实践相结合:教师通过讲授基本理论和原理,并结合实例进行演示操作,让学生更加深入地理解和掌握知识点;2.实践与考核相结合:学生将在课程中完成一系列的设计任务,检验学生的实践能力和对知识点的理解;3.小组讨论与展示相结合:学生将分为若干小组,每个小组有不同的设计任务,小组成员之间进行交流和讨论,最后进行展示并进行评分。

四、教学内容1.DSP基础知识–DSP系统结构和基本原理–DSP编程语言–DSP算法2.DSP应用开发–DSP应用需要的硬件和软件环境的搭建–DSP应用的开发流程3.DSP应用系统设计实例–声音信号的DSP处理–图像和视频信号的DSP处理–实时控制系统的DSP处理五、教学评估1.作业评估:根据学生提交的作业进行评估,重点考察学生实际应用能力;2.实验报告评估:针对学生完成的实验报告进行评估,重点考察学生对知识点的理解程度;3.课堂表现评估:通过学生的课堂出勤率和表现进行评估,重点考察学生的学习态度和团队合作能力;4.期末项目评估:最终项目是课程的重要评估指标,考察学生的实际应用能力、创新能力和团队协作能力。

六、教学成果通过这门课程,学生将掌握DSP应用系统设计的基础知识和技能,具备实际开发DSP应用设计的能力和独立思考的创新能力。

DSP硬件系统的设计

5 DSP硬件系统的设计本方案是完成对三分量地震动信号采集和处理的硬件系统。

采用TI公司的TMS320C5409作为中央处理芯片,运用其高速的运算性能,完成对信号的实时处理。

5.1系统简介课题的研究对象为地面车辆的地震动信号,由前面介绍的三轴地震动检波器进行采集。

采集到的目标信号很微弱,通常只有几个至几十个微伏。

如此小的信号必须先经过前置放大和预处理后才能进行后续处理。

另外由于原始信号的这种微弱性,很容易被噪声淹没,所以一种低噪声、高增益放大电路也是本系统的重要组成部分之一。

为了能有效抑制干扰,对此测量电路应满足以下基本要求:(1)高输入阻抗,以减轻信号源的负载效应和抑制传输网络电阻不对称引入的误差;(2)高共模抑制比,以抑制各种共模干扰引入的误差;(3)零点的时间稳定性和温度稳定性要高,零位可调,或者能自动较零;(4)具有优良的动态特性。

基于以上要求,并满足三路信号的同时采集,本系统中采用的电路为三个单片的MAX4094组成多运放仪用放大电路,增益约为104,可单电源+2.7V~+6.0V 工作,功能可靠,性能稳定,达到了系统期望的要求。

在信号经过前置放大和预处理以后,就可以进行分析处理了。

本系统中采用DSP进行信号的分析与识别,由于DSP所能处理的信号为数字信号,所以在分析处理之前,必须将模拟信号转化成数字信号,也就是A/D转换。

针对于DSP芯片的数据接收特点,采用串行SPI方式进行数据接收,并要求三通道同时采集。

本系统采用MAX1246,该芯片为四通道串行数据传输、12位精度、低功耗ADC。

采用尾对尾连接方式,完全能够和DSP不加附加电路直接连接,从而简化电路的设计。

考虑到本系统的可调试方便,系统的电源使用独立变压器的+5V直流电源,它能够提供给系统稳定的电源保证,由于DSP有两种工作电压要求,一个是+1.8 V,一个是+3.3V。

所以本系统采用电源芯片为TI公司的TPS767D318。

同时考虑到模拟器件(主要是信号放大电路部分)和数字器件(主要是DSP和DSP周边器件)的干扰问题,采用电源芯片MAX860以及电压参考芯片MAX6030和断续放大器ICL7652,为系统提供双向电源3V。

DSP器件及其应用DSP的硬件结构PPT学习教案

单个周期内计算40位累加器中数值的指数。

双地址生成器,包括8个辅助寄存器和2个辅助寄存器算术运算

单元(ARAU)。

34

第33页/共90页

TMS320C54x的硬件结构

1 TMS320C54x的内部结构和主要特性

1.2 TMS320C54x的主要特性

2.存储器 16位192K字的可寻址存储空间(64K字的程序存储空间、

立的地址总线和数据总线,取指和 读数可以同时进行,从而提高速度, 目前的水平已达到90亿次浮点运算 /秒(9000MFLOPS)

MIPS--Million Instruction Per

Second

第3页/共90页

MFLOPS--Million Floating

DSP芯片的特点

哈佛结构

程序 存储器

35

第34页/共90页

TMS320C54x的硬件结构

1 TMS320C54x的内部结构和主要特性

1.2 TMS320C54x的主要特性

3.片外设

软件可编程等待状态发生器。 可编程分区切换逻辑电路。 带有内部振荡器或用外部时钟源的片内锁相环时钟发生器。 支持全双工操作的串行口,可进行8位或16位串行通信。 片内的串行口根据型号不同可分为4种:单通道同步串行口

❖ DSP的CPU设置硬件乘法器,可以在单 周期内完成乘法和累加

基于DSP的永磁同步电机控制系统硬件设计

基于DSP的永磁同步电机控制系统硬件设计胡宇;张兴华【摘要】以小功率永磁同步电机(PMSM)为研究对象,结合数字信号处理器TMS320F2812功能特点,给出了一套PMSM驱动控制系统硬件设计方案.详细阐述了功率驱动主电路、反馈信号检测电路以及供电电路的设计,介绍了主要元器件选型和参数计算方法.基于设计的硬件平台,对PMSM调速控制系统进行了测试.试验结果表明,所设计的控制系统硬件设计可靠、性能稳定、控制精度高.%Based on the controlled object of small power permanent magnet synchronous motor (PMSM),combined with the main features of digital signal processor TMS320F2812,an overall hardware design scheme had been put forward for the PMSM drive control system.Design of the power driven main circuit had illustrated,signal detection circuit and power supply circuit in detail,meanwhile introduced the main components selection and parameters calculation method.Based on the designed hardware platform,the control system of PMSM had been performed a functional test.Experimental results showed that the hareware design of control system had good reliability with stable performance and high control precision.【期刊名称】《电机与控制应用》【年(卷),期】2017(044)012【总页数】7页(P19-24,80)【关键词】永磁同步电机;功率驱动主电路;信号检测电路【作者】胡宇;张兴华【作者单位】南京工业大学电气工程与控制科学学院,江苏南京211816;南京工业大学电气工程与控制科学学院,江苏南京211816【正文语种】中文【中图分类】TM351永磁同步电机(Permanent Magnet Synchronous Motor,PMSM)因其体积小、损耗低、功率密度高和效率高等优点,在机械制造、工业控制、航空航天等领域得到广泛应用[1]。

DSP系统硬件设计

A0~A16

MSTRB

16245电平转换实际连接图

DSP存储器及I/O扩展

数据运算量大,存储容量要求高的系统 DSP芯片本身存储及I/O资源有限 需要进行存储器和I/O扩展

了解DSP片上存储资源和I/O空间资源 根据实际应用需求进行扩展

ROM和RAM ROM:EPROM、EEPROM(E2PROM)、FLASH RAM:SRAM、DRAM和SDRAM、DDR RAM…

依据选定的扩展存储器读写时序,确定DSP 访问时的逻辑控制时序

读写

片选

程序存储器工作方式

读操作

程序存储器的内容在通常情况下不能改写; 片选和输出使能信号同时有效时,地址线所选中

的地址单元内容出现在数据总线

维持操作

片选无效时,处于维持状态:地址和数据线为高

阻状态,存储器相当于悬空

其中

IOH: 输出高电平电流;

IOL: 输出低电平电流; IIH: 输入高电平电流; IIL: 输入低电平电流; VOH: 输出高电平下限电压; VOL: 输出低电平上限电压; VIH: 输入高电平下限电压; VIL: 输入低电平上限电压;

3.3v与5v接口的四种形式

⑴ 5v TLL器件驱动3.3v TTL器件

H/TOUT

HOLDA MSTRB

IOSTRB READY

N C

CIN/X2 TOUT0

BFSX0 BFSR0

HOLD EMU0 8 0

BDX0 BDR0 TRST

N C

MSC TDO

TMS TCK R/W IAQ

TDI

D X P

I

S S

S 1

VC5402

《DSP应用系统设计》课件

DSP应用系统广泛应用于通信、多媒体、 工业控制等领域。

DSP应用系统的设计需要考虑到性能、成 本、功耗等多个因素。

DSP应用系统的特点

高性能:处理速度快,计 算能力强

灵活性:可编程,可定制, 可扩展

实时性:实时处理数据, 响应速度快

稳定性:可靠性高,抗干 扰能力强

应用广泛:应用于通信、 信号处理、图像处理等领 域

01 02

03 04

05

DSP芯片的分类:根据应用领域和功能,可以分为通用型DSP芯片、 专用型DSP芯片和混合型DSP芯片。

通用型DSP芯片:具有较高的灵活性和可编程性,适用于多种应用 领域。

专用型DSP芯片:针对特定应用领域进行优化设计,具有较高的性 能和效率。

混合型DSP芯片:结合了通用型和专用型DSP芯片的优点,具有较 高的灵活性和性能。

常用数字信号处理算法

快速傅里叶变换(FFT):用于信号频谱分析 离散小波变换(DWT):用于信号去噪和压缩 自适应滤波器:用于信号处理和系统辨识 卡尔曼滤波器:用于信号估计和预测 神经网络:用于模式识别和预测 遗传算法:用于优化问题和参数估计

算法设计流程与优化

确定算法目标:明确算法需要解决的问题和性能要求

应用实例:包括图像处理、信号处 理、语音识别等

调试与测试方法

单元测试:对每个模块进行独立测试,确保其功能正确

集成测试:将各个模块集成在一起进行测试,确保系统整体功能正确

压力测试:对系统进行高负载测试,确保系统在高负载情况下仍能正常 运行

性能测试:对系统的性能进行测试,确保系统满足性能要求

稳定性测试:对系统进行长时间运行测试,确保系统在长时间运行下仍 能保持稳定

硬件设计需要遵循一定的规 范和标准,如IEEE、ISO等

基于DSP的音频信号处理系统设计

基于DSP的音频信号处理系统设计一、导言随着数字信号处理(DSP)技术的不断发展和成熟,其在音频信号处理领域的应用也越来越广泛。

基于DSP的音频信号处理系统不仅可以实现高质量的音频处理和增强,也可以满足不同应用场景下的需求,如音频通信、娱乐、音频分析等。

本文将针对基于DSP的音频信号处理系统进行设计,从系统结构、信号处理算法、硬件平台等方面进行介绍和分析。

二、系统结构设计基于DSP的音频信号处理系统的设计首先需要确定系统的结构框架。

一般来说,这个结构包括了输入模块、DSP处理模块、输出模块和控制模块。

输入模块用于接收音频信号,可以是来自麦克风、音乐播放器、电视等各种音频设备。

DSP处理模块是音频信号处理的核心部分,其中包括了各种信号处理算法和算法的实现。

输出模块用于将处理后的音频信号输出到扬声器、耳机等输出设备中,以供用户听取。

控制模块可以用来控制和调节系统参数、算法选择、音频效果等。

三、信号处理算法音频信号处理系统的设计离不开各种信号处理算法的选择和实现。

常见的音频信号处理算法包括了滤波、均衡器、混响、压缩、编码解码等。

滤波算法用于去除音频信号中的杂音和干扰,使音频信号更加清晰;均衡器算法可以调节音频信号的频谱特性,使音频输出更加平衡;混响算法用于模拟不同的音频环境和效果;压缩算法可以调节音频信号的动态范围,使音频输出更加均衡;编码解码算法用于音频信号的数字化和解码处理。

在实际应用中,根据不同场景和需求,可以选择不同的信号处理算法,并通过DSP处理模块进行实现和调节。

四、硬件平台设计在基于DSP的音频信号处理系统的设计中,硬件平台的选择和设计也是非常重要的一部分。

常见的DSP芯片有TI的TMS320系列、ADI的Blackfin系列、Freescale的i.MX系列等。

在选择DSP芯片的还需要考虑到外围设备的选择和接口设计,如ADC(模数转换器)、DAC(数模转换器)、存储器、通信接口等。

为了提高系统的性能和稳定性,还需要考虑到功耗、体积、散热等方面的问题。

基于DSP变频调速系统的硬件设计

性 能控 制 。L 2 O A 作 为 2 0 D P家 族 的新 成 F47 4x S 员, 在处 理性 能及 其 片 内外设 上有 了很 大 的改进 ,

主要 包括 算 术逻 辑单 元 ( U—Ar h t o i AL i mei L g— t c cl i) a Unt ,寄 存 器 单 元 、 助 算 术 逻 辑 单 元 辅

器 , 法 移 位 器 , 个 功 能 强大 的事 件 管理 器 , 加 两 外

的发 展 , 频 调 速 技 术 取 得 了 巨大 的 技 术 进 步 。 变 电气传 动控 制在 现代 化 建设 中起 着极 为 重要 的作

围存 储 器扩展 接 口单 元 , AN 总 线 接 口单 元 , C 通 用 IO 口单元 , / 时钟 锁 相 环 电路 , 内部 A/ D转 换 器, 串行 口 , 串行 外 设 接 口等 部 分 。 L 2 0 A 的 F 47 推出, 为交 流调 速 装 置 控 制 器 的设 计 提供 了新 的

以其 特 有 的 优 点 正 逐 步 取 代 传 统 的 直 流 调 速 , 电 气 传 动 领 域 中扮 演 着 重 要 的 角 色 。本 文 以 此 为 背 景 对 基 于 D P变 频 在 S

调 速 系 统 进 行 了 研 究 。实 现 了 既节 能 , 低 耗 材 的 目的 , 保 证 了 安 全 生 产 。 降 又

方案。

用 , 了满足 高性 能 、 能 和 环保 的要 求 , 流 调 为 节 交

速 控制 系统 以其 特有 的优 点正 逐 步取 代传 统 的直 流 调速 , 电气传 动 领域 中扮 演着 重要 的 角色 。 在

本 文 从 节 能 的 角 度 出 发 ,以 TI公 司 的

基于DSP的车载音频系统设计

基于DSP的车载音频系统设计随着汽车产业的不断进步和发展,车载音频系统在普及和质量上都有了很大的提升。

而车载音频系统的核心,在于数字信号处理(DSP)技术的应用。

本文将从基本概念、硬件设计、软件设计和音效处理四个方面,探讨一下基于DSP的车载音频系统的设计。

基本概念数字信号处理(DSP)是一种将模拟信号转换为数字信号,再用数字电路处理信号的技术。

由于汽车所处嘈杂的交通环境中,很难获取准确的模拟信号,所以数字信号处理在车载音频系统中显得尤为重要。

硬件设计车载音频系统的硬件设计包括采样芯片、数字信号处理器、功率放大器、音频解码器和音箱等,其中数字信号处理器是整个系统的核心。

数字信号处理器需要具备高计算速度和稳定性能,以确保信号的处理精度和音质的清晰度。

DSP的选型时需要综合考虑其性能和成本,常用的DSP芯片有德州仪器的TMS320系列、ADI的SHARC系列、XMOS的XS1系列等。

这些芯片具有不同的性能水平和应用范围,可以根据不同的需求进行选择。

在设计音频解码器时需要等到车载音频系统支持多种音频格式播放,如MP3、WAV、FLAC、APE等。

此外,车载音频系统基于DSP的硬件设计还需要考虑音频输入的方式、电源管理、防干扰等因素,以保证音质的稳定和可靠性。

软件设计车载音频系统的软件设计也是基于DSP的。

如果采用高效的DSP算法,就能够提升音质和效果,并且具备高的可扩展性和灵活性。

软件设计需要涉及DSP芯片的代码编写和程序调试,采用C语言、汇编语言等开发语言,调试工具等以及适当的优化,使得程序代码高效、紧凑。

音效处理在车载音频系统的设计中,音效处理是非常重要的。

通过DSP技术处理,可以实现各种音效效果,比如卡拉OK唱歌的混响滤波器、3D环绕音效等。

汽车所处交通环境嘈杂,对于车载音频系统来说,去噪、残声抑制等技术尤为关键。

DSP 技术可以使得车载音频系统在不同场景下,自动调整音效效果,并且实现声音的均衡和混合处理,给人以舒适、自然的感觉。

基于DSP可重构运动控制器的硬件设计

30 7 ) 00 2

要 :针 对 当 前 运 动 控 制 器 不 能 满 足 柔 性 化 制 造 的 要 求 ,提 出 了一 种 基 于 T 30 2 1 S MS2 C 82D P、可 编 程 逻 辑 器 件

CL P D和 F G P A的 高 性 能 运 动控 制器 硬 件 的设 计 方 法 。考 虑 到 D P P D和 F G 的 特 点 ,采 用 模 块 化 设 计 ,应 用 S 、C L PA

FP GA s c p o e s r t o lt n e sv ac lto a o r c s o o c mp ee i tn ie c l u ain. An h e o fg r b e d sg s d o he FPGA d t e rc n u a l e in ba e n t i

Absr c t a t:I r e o me t h e uie n s o e i e ma u a t rn n o d r t e te r q r me t ff xbl n f cu i g,a h r wa e d sg i g meho fa l a d r e in n t d o

sr cu e c mp ee y me t h e u s fr a・i e c n r l n tu t r o lt l es te r q e to e lt o tol g,a d i i e o fg r b e m i n t s r c n u a l . i

Ke o d y W r s:Moi n c n r l to o to ;DS P;Re o fg r b e;CPLD;FPGA c n ua l i

0 引 言

柔 性化 制造 是指 能 够 根 据 制 造任 务 和生 产 品 种 变化 而迅速进 行 调 整 的 自动 化制 造 系 统 ,数 控 系 统 是 自动 化制造 系统 的 核 心 ,运 动控 制 器 是 数 控 系 统 的核心 ,其反 映 速度 和 精 度 直接 影 响数 控 系 统 的性

DSP应用技术-工程应用实例

20 K

30 k

3C11

RXB

RX B

14

CLKFLTA D

1u CL K FL TA D 3

4

A V CC

AVCC 3R8

13 V+

IN CL K V-

ou t 11

op ou t op in

5 6

GND 12

3R9

20 K

2

3 3R10

+2 .5 V

U10 MA X 29 5EW E

31R020

NC NC

7 GND 16

AGND 27 AGND

3R3 10 k

3R6 10 k

15 D0 14 D1 13 D2 12 D3 11 D4 10 D5 9 D6 6 D7 5 D8 4 D9 3 D10 2 D11 1 28

TI

T

I

TQ

T

Q

D [0..1 1] D [0..1 1]

图7.7 模拟输入/输出通道电路

工程应用实例

1. 信号流程

(1) 接收信号流程 由射频部分送来的基带DQPSK调制信号 (f0=7.2 kHz),进入带通滤波器MAX295EWE,滤除带外噪声, 然后进入运算放大器(TL084)放大至适当电平(0~3 V变化范围)。 放大后的信号由模数转换器AD7862进行量化,量化后的数据进 入DSP芯片,通过软件编程进行DQPSK解调、维特比译码和解 交织等,得到原始信息码。DSP将该信息码送给Intel8251A,转 化成9.6 kb/s的UART数据流,最后经MAX232EESE转变成RS232电平(±12 V)送往数据终端。

7.6 DSP

工程应用实例

图

主 系 统 及 部 分 外 围 电 路

基于DSP的全数字永磁交流伺服系统的硬件设计

本文详细论述基于 D P芯片 T S 2F 8 2的永磁电机数字交流 S M 302 1 3 逆 变器 主 电路 。 3 . 1 图 是 ! 伺服控制系统的硬件设计 ,主要包括控制系统总体电路 、功率驱动 回 逆变器主电路。逆变电路是变 路、 速度和位置检测电路以及系统保护电路设计。 频器主要部分之一。起作用是 1系统硬件的总体结构 在控制电路的控制下将直流电 L G - N_ 。_ 图1 所示为系统硬件结构框图。 硬件电路可 以分为三部分 : 主控电 路输出的直流电压转换成所需 T :0 I C K 9 1 路、 功率驱动电路和电源电路。主控电路以 D P为核心 , S 外围电路主要 频 率 的交 流 电压 。逆变 器 主 电 ! _ _ _ 包括 : 仿真接 口电路、 电平转换电路、 外部存储器扩展电路。功率驱动电 路包括市电整流 、 滤波和三相桥 路包括逆变器主电路、 电流检测 电路、 转子位置速度检测电路和故障保 式逆变电路。整流 由普通二极 护 电路等。电源 电路为系统提供多路不同等级的直流电源。 管整流桥实现。三菱公 司的智 图 2J A 电路 T G 能功璋i 模块( M)M2 c J6 I P 0 s0 O P 为功率变换装置。 IM 模块 内部 集成 了六 个 P I B 作为功率开关元件 , G T 同时 集成了驱动电路 ,并设计有过 电压 、 过电流 、 过热 、 电压等 欠 故障检测保 护电路。由于 IM P 模块的智能化 、模块化 、集成 化 、 价 比高 、 护 功 能 全 、 性 保 控 制驱动简单等特点 ,使整个 电 路设计更简洁, 成本降低。D P S 输 出六路 P WM信号驱动 IM P 图 1系统硬件结构框图 工作输 出三相电流给电机定子 2 主控 电路 绕组, 使电机运转。 2 S _ D P控制核心。本系统采用 T 公司的高性能 的 D P控制器 1 I S 在 IM 接 口电路 中 , 对 P 针 T 20 21 MS 3 F 8 2作为控制核心 ,MS 2 F 82采用高性 能静态 C S IM所 需 相 应设 置 D P T 30 2 1 MO P S ,同时 图 3 逆变主 电路 技术 , 具有 10 z6 7s 5 MH (. n 周期时间 ) 6 的时钟频率 , 低功耗设计( 内核 在 D P和 IM之间应该使用高速光耦隔离。P S P IM需要 四路隔离的+ 5 1V 1 V, 3 V) . 哟 . ,支持 J A 8 3 T G技术。片内集成 了一个 山l 3 陛能 2位 C U 供电, P 上三桥臂各用—个 , 下三桥臂共用—个, 由电源模块 J 18 S 5 提供。 ( Ms 2 c 8 )止 夕 , T 3 0 2 x。 匕 该器件带有支持 4 个外设中断的外设中断扩展 5 3 - 2电流检测 电路 。为了满足商 性能伺服系统的要求, 提高系统电 ( I 模块 , 个 3 位 C U定时器。 PE) 3 2 P 电机控制外设包括两个事件管理器 流环响应速度 , 必须进行电流检测。电流检测模块就是把交流感应电机 (V E B , E A,V )同时与 2 0 设备兼容。5 个独立可编程 , 4x 6 多路通用输入/ 的三相定子电流转换成相应的二进制代码, 以方便 D P处理。 S 由于本课 输 出( P0 管脚 。 G T) 高级仿真 陛能包括 : 分析和断点功能 、 硬件实时调试。 题研究的是三} 平衡系统 :十 = , i i 0 因此只要检测其 中两路电流 , A 就可 2 S . D P外围电路 。( )A 2 1T G仿真接 口。2 x P 8C U的仿真逻辑包括 以得 到三 相 电流 。 有: 调试和测试直接存取存储器 , 调试器可以不使用指令流水线循环周 根据电动机 的数学模型可知,定子电流检测的精度和实时f 生是整 期, 而通过控制存储器接 口直接得到寄存器或存储器的内容。 仿真逻辑 个矢量控制系统精度的关键 , 因此对 电流检测要求精度高和速度快 , 设 允许在 2 x 8 和调试器之间对存储器 内容进行初始化操作,内含完成基 计中采用 H ny e 公司的霍耳传感器 C N 1 1 10 运放采用 T 公 o ew l l S E 5— 0 。 I 准测试程序的计数器及具有多重调试事件。目标层次的 T 调试接 口使 司的商l I 生能双运算放大器 T C 22 L 2 7 。比目前常用的 C S MO 运放有更好 用5 个标准的 IE l 9 ( A  ̄- T S 、C 、MST I T O) 的噪声 、 E E1 .J G) 号( R TT K T 、D 和 D 和 4 IT 功耗和输入失调电压陛能, 非常适宜用于诸如 电压/ 电流传感器 两个 T 扩展 口( Mu 、 MU ) I E 0E 1。通过结合 T 的集成开发环境( c ) I c s与 之类的小信号的计算 、 放大。 采集 的模拟信号需经 AD转换成数字信号 / JA T G接 口, 以很方便地进行实时在线调试 以及程序的下载。接口电 才能被 D P 可 S 处理。 MS 2 F 8 2内部提供了两个 1 位 AD转换模块 , T 302 1 2 / 路如图 2所示 。( ) 2电源电平转换 电路 。T S 2F 8 2的核心电压是 可实现最多 1 路模拟信号的采集 。两个 AD模块可以同时进行转换 , M 302 1 6 / 1 V Ⅳ】 . ,(口电压是 3 V。为保证芯片正常工作 , 8 . 3 必须进行电源转换提供 保 证 了被采 集 的两相定 子 电流 的 同相 位 。 这两种工作电压。 线形稳压芯片是 一种最简单的电源转换芯片 , 基本上 3 速度检测。本文采用的是电机 自带的光电编码器 , - 3 它有三相输 不要外围元件。但是传统的线形稳压器 , 7 X 如 8 X系列都要求输入 电压 出, 分别为 A, , , B z相 利用 z相和 A, B相的相对位置可以精确定位电 要 比输出电压高 2 3 V以上 , ~. 3 否则不能正常工作 , 但是 5 V到 3 v的 机 的磁极位置 。T S 2 F 8 2 . 3 M 3 0 2 1 事件管理模块具有正交解码脉 冲电路 电压差只有 1 V . ,所以 7 X 7 8 X系列 已经不能够满足 3 v电源设计要 ( E . 3 Q P电路) 。当该电路被使能后 , 引脚 C P/E I C P /E Z接收 A I P 和 A ZQ P Q 求。面对这类需求 , 许多电源芯片公司推出了 L w rpuR g l o低 脉冲信号。正交解码脉冲电路可用于连接光电编码器以获得电机转子 o D oo teua r t 压 差 稳 压 器 。可 以实 现 5 V转 3 W1 V 的要 求 1 公 司生 产 的 的位置及速度信 息,电机轴上的光电码盘输出的正交编码脉冲经接 口 . . 3 8 r I T S6D P 7 7 3 1 8电源芯片进行电压转换。 电路输入到正交解码脉冲输入电路 , 接口电路用来完成脉冲的隔离 、 整 3 功率 驱动 电路 形 功能 。 ( 转 2 9页 ) 下 4

基于DSP的音频信号处理系统设计

基于DSP的音频信号处理系统设计【摘要】本文介绍了基于DSP的音频信号处理系统设计。

在文章概述了背景介绍、研究目的和研究意义。

在详细讨论了DSP在音频信号处理中的应用、音频信号处理系统设计原理、DSP系统设计流程、DSP系统硬件设计和DSP系统软件设计。

在总结了基于DSP的音频信号处理系统设计的优势,并探讨了未来研究方向。

通过本文的研究,读者可以更加深入地了解基于DSP的音频信号处理系统设计,并了解其在实际应用中的优势和未来发展方向。

【关键词】关键词:DSP、音频信号处理、系统设计、应用、原理、流程、硬件设计、软件设计、优势、未来研究方向、总结1. 引言1.1 背景介绍音频信号处理是数字信号处理领域的一个重要应用方向,随着数字信号处理技术的不断发展,其在音频领域的应用越来越广泛。

传统的音频信号处理系统往往采用模拟信号处理技术,但是由于模拟处理存在精度不足、易受干扰等问题,随着数字信号处理技术的不断改进和发展,基于DSP的音频信号处理系统逐渐成为主流。

DSP技术具有处理速度快、精度高、灵活性强等优点,能够实现复杂的音频信号处理功能,如滤波、时域变换、频谱分析等。

基于DSP的音频信号处理系统设计可以满足不同应用场景对音频处理的要求,如音乐录制、语音识别、音频增强等。

本文旨在探讨基于DSP的音频信号处理系统设计原理和流程,从硬件设计到软件设计进行详细介绍,希望能够为大家对音频信号处理技术有一个更深入的了解,并为未来的研究和应用提供一定的参考。

1.2 研究目的本文旨在通过对基于DSP的音频信号处理系统设计进行深入研究,探讨其在音频领域的应用和发展趋势。

具体来说,研究目的主要包括以下几点:1. 探究DSP在音频信号处理中的优势和特点,分析其在音频处理中的具体应用和效果。

通过深入了解DSP技术在音频信号处理中的作用,可以为音频领域的技术发展提供更深入的理解。

2. 研究音频信号处理系统设计原理,探讨DSP系统在音频处理中的工作原理和设计思路。

DSP系统设计及应用实例.

确定硬件方案 器件选型

原理图设计

PCB图设计

ቤተ መጻሕፍቲ ባይዱ

第五步:硬件调试;

硬件调试

TMS320C54x的硬件设计

DSP系统的基本设计

一个完整的DSP系统通常是由DSP芯片和其他 相应的外围器件构成。 本节主要以TMS320C54x系列芯片为例,介 绍DSP硬件系统的基本设计,包括: 电源电路 复位电路

TMS320C54x的硬件设计

硬件设计概述

第二步:器件的选择;

⑦ 人机接口 常用的人机接口主要有键盘和显示器。 通过与其他单片机的通信构成; 与DSP芯片直接构成。 ⑧ 电源的选择 主要考虑电压的高低和电流的大小。 既要满足电压的匹配,又要满足电流容量的要求。

TMS320C54x的硬件设计

硬件设计概述

第三步:原理图设计; 原理图设计包括: 系统结构设计 可分为单DSP结构和多DSP结构、并行结构和串 行结构、全DSP结构和DSP/MCU混合结构等; 模拟数字混合电路的设计 主要用来实现DSP与模拟混合产品的无逢连接。 包括信号的调理、A/D和D/A转换电路、数据缓 冲等。

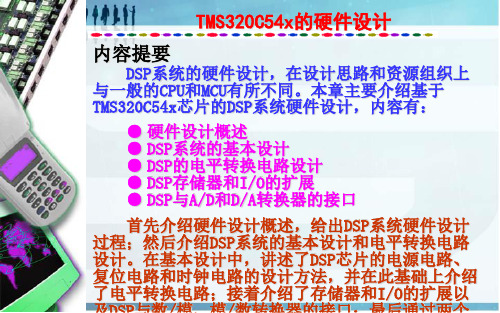

TMS320C54x的硬件设计

TMS320C54x的硬件设计 内容提要

DSP系统的硬件设计,在设计思路和资源组织上 与一般的CPU和MCU有所不同。本章主要介绍基于 TMS320C54x芯片的DSP系统硬件设计,内容有: ● 硬件设计概述 ● DSP系统的基本设计 ● DSP的电平转换电路设计 ● DSP存储器和I/O的扩展 ● DSP与A/D和D/A转换器的接口 首先介绍硬件设计概述,给出DSP系统硬件设计 过程;然后介绍DSP系统的基本设计和电平转换电路 设计。在基本设计中,讲述了DSP芯片的电源电路、 复位电路和时钟电路的设计方法,并在此基础上介绍 了电平转换电路;接着介绍了存储器和I/O的扩展以

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

9.4.1 DSP控制电路

图9-2 DSP56805电路

9.4.2 GA电路

图9-3 FPGA及外围电路

9.4.3信号调理及模/数转换电路

经模拟通道后的被测信号首先进行调理,再分 别送高速A/D转换电路和信号整形电路进行处 理。高速A/D转换器可采用TI的TLC5580。其 分辨率为8位,转换速率可根据需要调整,最 高为80MHz。A/D转换的数据结果送FPGA内的 FIFO缓存。整形电路用高速比较器TLC3016, 将任意形状的模拟信号转换为标准的矩形脉冲 信号,送FPGA的频率电路进行频率/周期的测 量。

DSP芯片的选择

DSP芯片的运算速度 1)按样点处理 2)按帧处理 DSP芯片的价格 DSP芯片的硬件资源 DSP芯片的运算速度 DSP芯片的开发工具 DSP 芯片的功耗 其他的因素,如封装的形式、质量标准、生命 周期等

ADELANTE 科技公司的Saturn系列 AGERE系统公司的 DSP16XXX 模拟器件公司的 ADSP-21XX 模拟器件公司的 ADSP-21XXX SHARC 系列 模拟器件公司的 ADSP-215XX BLACKFIN 系列 模拟器件公司的 ADSP-TS101 TIGERSHARC 系列 CHIPWRIGHTS公司的 CW4011和CW451 CIRRUS LOGIC 公司的 CS494XX DSP 体系结构公司的 DSP24 日立半导体公司的 SH-DSP 系列和 SH3-DSP 系列 LSI 逻辑公司的 ZSP400、LSI402ZX 和 LSI403LP LSI 逻辑公司的 ZSP500 LSI 逻辑公司的 ZSP600

9.4.4 软件结构

图9-4 示波表软件结构

DSP器件还提供了高度专业化的指令集,提高 了FFT快速傅里叶变换和滤波器的运算速度。

DSP芯片一般具有如下一些主要特征: 硬件乘法累加操作(MACs) 具有哈佛结构 零消耗循环控制 特殊寻址模式 执行时间的可预测性 可以并行执行多个操作 具有在单周期内操作的多个硬件地址产生器 支持流水线操作

DSP的典型应用如下: 通用数字信号处理;

9.2.2 DSP应用系统的低功耗设计

合理选择DSP处理器器件 让DSP以适当的速度运行 在软件设计中降低功耗 存储器类型对功耗的影响 正确处理外围电路

9.3 DSP芯片的选择及其介绍

按基础特性分 这是根据DSP芯片的工作时钟和 指令类型来分类的。 按数据格式分 这是根据DSP芯片工作的数据格 式来分类的。数据以定点格式工作的DSP芯片称 之为定点DSP芯片。以浮点格式工作的称为DSP 芯片 按用途分 可分为通用型DSP芯片和专用型的 DSP芯片。通用型DSP芯片适合普通的DSP应用, 如TI公司的一系列DSP芯片。专用型DSP芯片是为 特定的DSP运算而设计,更适合特殊的运算,如 数字滤波、卷积和FFT等。

DSP系统处理的模拟带宽。 实时性要求。 算法的复杂度。 DSP系统处理精度要求。 成本要求。 可靠性要求。 方便开发和使用。

2. DSP算法的验证与模拟

DSP处理系统所选 用的算法无非是各种通用算 法的组合和改进,DSP系统设计师应尽量选用成 熟可靠、经过时间考验的算法,而支持各种通用 算法的DSP模拟软件市场上已有不少。 SPW工作站 Matlab工具包 Dalisp软件

通信;

声音/语音信号处理; 图形/图像信号处理 ; 控制,包括:磁盘/光盘伺服控制、激光打印机伺 服控制、机器人控制、发动机控制、卡尔曼滤波 等;

仪器,包括:频谱分析、函数发生、波形发生、 数据采集、暂态分析、模态分析、石油/地质助 探、飞行器风洞试验等;

医学电子学;

军事; 计算机和消费电子。

DSP在通信设备领域的应用: 1.数字式蜂房系统

◆语音合成、语音压缩与编码 ◆纠错编码 ◆基带调制与解调 2.软件电台(Software rideo) 3.均衡和信道估计 4.语音和字符识别算法 5.调制解调器(Modem) 6.综合业务数字网(ISDN) 7.多媒体

9.2 DSP系统的总体设计

图9-1 典型的DSP系统

1. DSP系统的功能需求分析

9.4 DSP应用系统硬件电路设计

以Motorola的DSP56805芯片为例,介绍其在数 字示波表中的应用。 硬件电路主要由Motorola的数字信号处理芯片 DSP56805、XILINX的现场可编程门阵列XC2S50 、GSI的静态存储器GS71116、TI的高速模/数 转换芯片TLC5580、Microtips的MTG-F32240液 晶显示器和其他辅助器件组成。

第九章 基于DSP应用系统的 硬件设计举例

9.1 DSP介绍及其应用

与单片机相比,DSP器件具有较高的集成度。 DSP具有更快的CPU,更大容量的存储器,内 置有波特率发生器和FIFO缓冲器。提供高速、 同步串口和标准异步串口。有的片内集成了 A/D和采样/保持电路,可提供PWM输出。

DSP器件采用改进的哈佛结构,具有独立的 程序和数据空间,允许同时存取程序和数据。 内置高速的硬件乘法器,增强的多级流水线, 使DSP器件具有高速的数据运算能力。DSP器 件比16位单片机单指令执行时间快8~10倍, 完成一次乘加运算快16~30倍。

3. DSP开发工具的选择

ASM/LINK 汇编/链接器; JTAG硬件仿真器,可全透明地访问DSP的所有 资源而不占用用户任何资源; Debugger调试器; 其他选件还有:C编译器、实时操作系统和算 法库。

4. DSP系统调试

认真处理好复位和时钟信号; 在DSP电路中,对所有的输入信号必须有明确 的处理,不能悬浮和置之不理; 模拟电路和数字电路独立布线,最后单点连接 电源和地。软件设计则应严格按照软件工程的 方法进行管理。