基于fpga的eeprom设计

毕业设计(论文)-基于fpga的sdram控制器的实现(软件部分)[管理资料]

![毕业设计(论文)-基于fpga的sdram控制器的实现(软件部分)[管理资料]](https://img.taocdn.com/s3/m/0426a5c767ec102de3bd8968.png)

毕业设计(论文)机械与电气工程学院电气工程及其自动化专业毕业设计(论文)题目基于FPGA的SDRAM控制器的实现(软件部分)学生姓名班级电气工程及其自动化学号指导教师完成日期2012 年 6 月 6 日基于FPGA的SDRAM控制器的实现(软件部分)The realization of SDRAM controller based on FPGA (software)总计毕业设计(论文) 41 页表格 6 个插图 21 幅摘要文中介绍了FPGA的开发流程、硬件开发语言及其开发环境QuartusII和SDRAM的结构特点和工作原理,根据SDRAM的工作原理、控制时序和指令特点,设计一种基于FPGA的SDRAM控制器的方案。

SDRAM控制器的设计主要由主控制模块、信号产生模块、数据路径模块和参数模块组成。

本设计解决SDRAM控制复杂、不方便的问题,并用Verilog给予仿真结果。

仿真结果表明使用该方法设计实现的控制器能够使系统方便,可靠的对SDRAM进行操作。

关键字:SDRAM控制器FPGA 控制模块软件仿真AbstractThis paper introduces the development process and FPGA hardware development language and the development environment of SDRAM QuartusII and structural characteristics and working principle, according to the working principle of SDRAM, sequence control and instruction characteristics, a scheme based on FPGA SDRAM controller is designed. SDRAM controller design mainly by the master control module, signal module, data path module and parameter module composition. This design solved a problem about the controlling complexity of SDRAM controller, and gives the simulation results by using Verilog. The simulation results show that using this method to design the controller can realize the system is convenient, reliable operation of SDRAM.Key words: SDRAM controller FPGA Control module Software simulation目录摘要 (I)Abstract (II)第一章绪论 (1)课题背景 (1)课题研究的意义 (1)第二章FPGA与Quartus II软件简介 (2)FPGA简介 (2)FPGA背景 (2)FGPA结构原理 (2)Quartus II软件简介 (3)硬件描述语言Verilog (4)FPGA开发过程 (5)第三章SDRAM的技术介绍 (6) (6)SDRAM简介 (6)SRAM和DRAM (6)SDRAM发展过程 (7)SDRAM工作原理和基本操作 (8)SDRAM存储的工作原理 (9)SDRAM 的引脚信号 (9)SDRAM基本命令 (10)SDRAM初始化 (10)SDRAM读、写操作 (11)终止操作 (12)第四章 SDRAM控制器设计 (12)SDRAM控制器 (13)主控制模块 (14)信号产生模块 (16)参数模块 (18)数据通路模块 (19)第五章SDRAM的读、写仿真 (19)SDRAM控制器时序仿真 (20)Quartus II (20)读仿真时序 (20)写仿真时序 (21)仿真结果分析 (22)结论 (24)参考文献 (25)致谢 (26)附录 (27)第一章绪论课题背景伴随着电子信息技术的飞速发展和其在通讯、工业、商业、医疗等方面的广泛应用,人们对信息的需求逐渐向着更快、更多、更准确发展。

FPGA读写EEPROM

FPGA读写EEPROMFPGA读写EEPROMmodulei2c(clk,rst,data_in,scl,sda,wr_input,rd_input,lowbit,en,seg_data);input clk,rst;output scl;//I2C时钟线inout sda;//I2C数据线input[3:0] data_in;//拨码开关输入想写入EEPROM的数据input wr_input;//要求写的输入input rd_input;//要求读的输入output lowbit; //输出一个低电平给矩阵键盘的某一行output[1:0] en;//数码管使能output[7:0] seg_data;//数码管段数据reg[7:0] seg_data;reg scl;reg[1:0] en;reg[7:0] seg_data_buf;reg[11:0] cnt_scan;reg sda_buf;//sda输入输出数据缓存reg link; //sda输出标志reg phase0,phase1,phase2,phase3;//一个scl时钟周期的四个相位阶段,将一个scl周期分为4段//phase0对应scl的上升沿时刻,phase2对应scl的下降沿时刻,phase1对应从scl高电平的中间时刻,phase2对应从scl低电平的中间时刻,reg[7:0] clk_div;//分频计数器reg[1:0] main_state;reg[2:0] i2c_state;//对i2c操作的状态reg[3:0] inner_state;//i2c每一操作阶段内部状态reg[19:0] cnt_delay;//按键延时计数器reg start_delaycnt;//按键延时开始reg[7:0] writeData_reg,readData_reg;//要写的数据的寄存器和读回数据的寄存器reg[7:0] addr;//被操作的EEPROM字节的地址parameter div_parameter=100;// 分频系数,AT24C02最大支持400K时钟速率parameter start=4'b0000, //开始first=4'b0001, //第1位second=4'b0010,//第2位third=4'b0011, //第3位fourth=4'b0100, //第4位fifth=4'b0101, //第5位sixth=4'b0110, //第6位seventh=4'b0111, //第7位eighth=4'b1000, //第8位ack=4'b1001, //确认位stop=4'b1010; //结束位parameter ini=3'b000, //初始化EEPROM状态sendaddr=3'b001, //发送地址状态write_data=3'b010, //写数据状态?read_data=3'b011, //读数据状态read_ini=6'b100; //发送读信息状态assign lowbit=0;assign sda=(link)? sda_buf:1'bz;always@(posedge clk or negedge rst) beginif(!rst)cnt_delay<=0;else beginif(start_delaycnt) beginif(cnt_delay!=20'd800000)cnt_delay<=cnt_delay+1;elsecnt_delay<=0;endendendalways@(posedge clk or negedge rst) begin if(!rst) beginclk_div<=0;phase0<=0;phase1<=0;phase2<=0;phase3<=0;endelse beginif(clk_div!=div_parameter-1)clk_div<=clk_div+1;elseclk_div<=0;if(phase0)phase0<=0;else if(clk_div==99)phase0<=1;if(phase1)phase1<=0;else if(clk_div==24)phase1<=1;if(phase2)phase2<=0;else if(clk_div==49)phase2<=1;if(phase3)phase3<=0;else if(clk_div==74)phase3<=1;endend///////////////////////////EEPROM操作部分///////////// always@(posedge clk or negedge rst) beginif(!rst) beginstart_delaycnt<=0;main_state<=2'b00;i2c_state<=ini;inner_state<=start;scl<=1;sda_buf<=1;link<=0;writeData_reg<=5;readData_reg<=0;addr<=10;endelse begincase(main_state)2'b00: begin //等待读写要求writeData_reg<=data_in;scl<=1;sda_buf<=1;link<=0;inner_state<=start;i2c_state<=ini;if((cnt_delay==0)&&(!wr_input||!rd_input)) start_delaycnt<=1;else if(cnt_delay==20'd800000) beginstart_delaycnt<=0;if(!wr_input)main_state<=2'b01;else if(!rd_input)main_state<=2'b10;endend2'b01: begin //向EEPROM写入数据if(phase0) scl<=1;else if(phase2)scl<=0;case(i2c_state)ini: begin //初始化EEPROM case(inner_state)start: beginif(phase1) beginlink<=1;sda_buf<=0;endif(phase3&&link) begininner_state<=first;sda_buf<=1;link<=1;endendfirst:if(phase3) beginlink<=1;inner_state<=second; end second:if(phase3) beginsda_buf<=1;link<=1;inner_state<=third; end third:if(phase3) beginsda_buf<=0;link<=1;inner_state<=fourth; end fourth:if(phase3) beginsda_buf<=0;link<=1;inner_state<=fifth; end fifth:if(phase3) beginsda_buf<=0;link<=1;inner_state<=sixth; end sixth:if(phase3) beginsda_buf<=0;link<=1;inner_state<=seventh; end seventh:if(phase3) beginlink<=1;inner_state<=eighth; endeighth:if(phase3) beginlink<=0;inner_state<=ack;endack: beginif(phase0)sda_buf<=sda;if(phase1) beginif(sda_buf==1)main_state<=3'b000;endif(phase3) beginlink<=1;sda_buf<=addr[7];inner_state<=first;i2c_state<=sendaddr;endendendcaseendsendaddr: begin //送相应字节的地址case(inner_state) first:if(phase3) beginlink<=1;sda_buf<=addr[6]; inner_state<=second; end second:if(phase3) beginlink<=1;sda_buf<=addr[5]; inner_state<=third; end third:if(phase3) beginlink<=1;sda_buf<=addr[4]; inner_state<=fourth; end fourth:if(phase3) beginlink<=1;sda_buf<=addr[3];inner_state<=fifth; endfifth:if(phase3) beginlink<=1;sda_buf<=addr[2]; inner_state<=sixth; end sixth:if(phase3) beginlink<=1;sda_buf<=addr[1]; inner_state<=seventh; end seventh:if(phase3) beginlink<=1;sda_buf<=addr[0]; inner_state<=eighth; end eighth:if(phase3) beginlink<=0;inner_state<=ack;endack: beginif(phase0)sda_buf<=sda;if(phase1) beginif(sda_buf==1)main_state<=3'b000;endif(phase3) beginlink<=1;sda_buf<=writeData_reg[7]; inner_state<=first;i2c_state<=write_data;endendendcaseendwrite_data: begin //写入数据case(inner_state) first:if(phase3) beginlink<=1;sda_buf<=writeData_reg[6]; inner_state<=second; endsecond:if(phase3) beginlink<=1;sda_buf<=writeData_reg[5]; inner_state<=third; endthird:if(phase3) beginlink<=1;sda_buf<=writeData_reg[4]; inner_state<=fourth; endfourth:if(phase3) beginlink<=1;sda_buf<=writeData_reg[3]; inner_state<=fifth; endfifth:if(phase3) beginlink<=1;sda_buf<=writeData_reg[2]; inner_state<=sixth; endsixth:if(phase3) beginlink<=1;sda_buf<=writeData_reg[1]; inner_state<=seventh; endseventh:if(phase3) beginlink<=1;sda_buf<=writeData_reg[0]; inner_state<=eighth; endeighth:if(phase3) beginlink<=0;inner_state<=ack;endack: beginif(phase0)sda_buf<=sda;if(phase1) beginif(sda_buf==1)main_state<=2'b00; endelse if(phase3) begin link<=1;sda_buf<=0;inner_state<=stop; endendstop: beginif(phase1)sda_buf<=1;if(phase3)main_state<=2'b00; endendcasedefault:main_state<=2'b00; endcaseend2'b10: begin //读EEPROMif(phase0)scl<=1;else if(phase2)scl<=0;case(i2c_state)ini: begin //初始化EEPROM case(inner_state) start: beginif(phase1) beginlink<=1;sda_buf<=0;endif(phase3&&link) begin inner_state<=first; sda_buf<=1;link<=1;endfirst:if(phase3) beginsda_buf<=0;link<=1;inner_state<=second; end second:if(phase3) beginsda_buf<=1;link<=1;inner_state<=third; end third:if(phase3) beginsda_buf<=0;link<=1;inner_state<=fourth; end fourth:if(phase3) beginsda_buf<=0;link<=1;inner_state<=fifth; end fifth:if(phase3) beginsda_buf<=0;link<=1;inner_state<=sixth; end sixth:if(phase3) beginsda_buf<=0;link<=1;inner_state<=seventh; endseventh:if(phase3) beginsda_buf<=0;link<=1;inner_state<=eighth; end。

基于FPGA的PCIe设计

基于FPGA的PCIe设计————————————————————————————————作者:————————————————————————————————日期:ﻩ基于FPGA的PCIe设计1. PCIe简介1.1. PCIe基本架构PCIe的优势以其复杂性为代价。

PCIe是基于分组的串行连接协议,估计比PCI并行总线复杂10倍以上。

这种复杂性部分源于在千兆赫速率所要求的并行到串行的数据转换以及转向基于分组的实现。

PCIe保持了PCI基于加载存储的基本架构,包括对PCI-X增加的对分割事务的支持。

此外,它引进了一系列底层信息传送要件来管理链接(如链路层流量控制)以模仿传统并行总线的边带线,且提供了更高水平的robustness和功能。

该规范定义了许多特性、能同时支持当今的需求和未来的扩展需要,且同时与PCI保持了软件兼容。

PCI Express的先进特性包括:主动电源管理;先进的错误报告;通过端对端循环冗余校验(ECRC)支持的端对端的可靠性;支持热插拔以及服务质量(QoS)流通类。

一个简化系统的拓扑结构包括四个功能类型,根联合体根联合体(root com plex)、交换器(switch)、端点(multiple Endpoints)和桥(bridge)。

1.ROOT Complex:根联合体对整个PCIe建构实施初始化并配置各链路。

它通常把中央处理单元(CPU)与其它三个功能中的一或多个——PCIe交换器、PCIe端点和PCIe到PCI桥——连接起来;2.Endpoint:端点通常位于终端应用内,它负责连接应用与系统内的PCIe网络。

端点要求并完成PCIe事务传输。

一般来说,系统内的端点比任何其他类型的PCIe部件都要多;(1)Legacy Endpoint;(2)PCI Express Endpoint;(3)Root Complex Integrated Endpoint;3.Switch:PCIe交换器把数据路由至下游多个PCIe端口,并分别从其中每个端口路由到上游唯一一个根联合体。

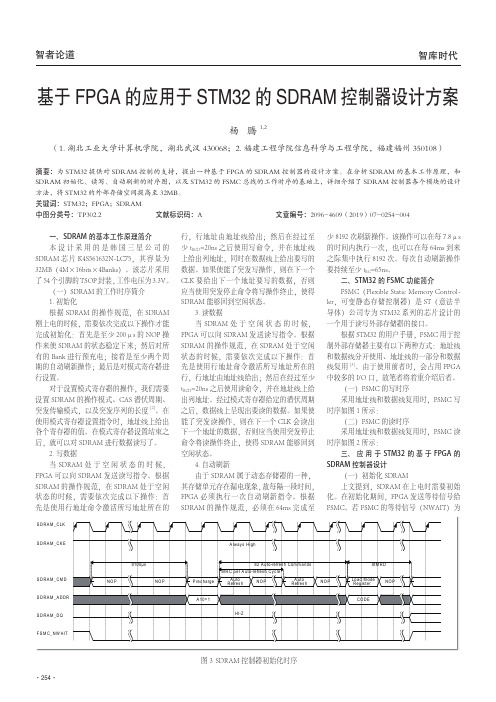

基于FPGA的应用于STM32的SDRAM控制器设计方案

·254·基于FPGA 的应用于STM32的SDRAM 控制器设计方案杨 腾1,2(1.湖北工业大学计算机学院,湖北武汉 430068;2.福建工程学院信息科学与工程学院,福建福州 350108)摘要:为STM32提供对SDRAM 控制的支持,提出一种基于FPGA 的SDRAM 控制器的设计方案。

在分析SDRAM 的基本工作原理,和SDRAM 初始化、读写、自动刷新的时序图,以及STM32的FSMC 总线的工作时序的基础上,详细介绍了SDRAM 控制器各个模块的设计方法,将STM32的外部存储空间提高至32MB。

关键词:STM32;FPGA;SDRAM 中图分类号:TP302.2文献标识码:A文章编号:2096-4609(2019)07-0254-004一、SDRAM 的基本工作原理简介本设计采用的是韩国三星公司的SDRAM 芯片K4S561632N-LC75,其容量为32MB(4M×16bits×4Banks)。

该芯片采用了54个引脚的TSOP 封装,工作电压为3.3V。

(一)SDRAM 的工作时序简介1.初始化根据SDRAM 的操作规范,在SDRAM 刚上电的时候,需要依次完成以下操作才能完成初始化:首先是至少200μs 的NOP 操作来使SDRAM 的状态稳定下来;然后对所有的Bank 进行预充电;接着是至少两个周期的自动刷新操作;最后是对模式寄存器进行设置。

对于设置模式寄存器的操作,我们需要设置SDRAM 的操作模式、CAS 潜伏周期、突发传输模式,以及突发序列的长度[2]。

在使用模式寄存器设置指令时,地址线上给出各个寄存器的值。

在模式寄存器设置结束之后,就可以对SDRAM 进行数据读写了。

2.写数据当SDRAM 处于空闲状态的时候,FPGA 可以向SDRAM 发送读写指令。

根据SDRAM 的操作规范,在SDRAM 处于空闲状态的时候,需要依次完成以下操作:首先是使用行地址命令激活所写地址所在的行,行地址由地址线给出;然后在经过至少t RCD =20ns 之后使用写命令,并在地址线上给出列地址,同时在数据线上给出要写的数据。

FPGA的eMMC嵌入式阵列存储系统设计

该 阵 列 系统 主 要 在 Xilinx公 司 的 Virtex 6系 列 FP— GA 芯 片 XC6VI X240 中 实 现 控 制 器 模 块 ,生 成 各 级 FIFO,以及 为 控 制 器 、FIFO、eMMC芯 片 提 供 各 种 需 求 的 时 钟 电路 。 同时 ,该 阵 列 系 统 使 用 GTX 收 发 器 作 为 数 据 传 输 的T 具 ,使 得 系统 具 备 高 传 输 速 率 的特 点 。

Abstract:In the paper,an em bedded array storage system is proposed.The design uses eM M C em bedded m ultim edia card as the storage medium which has the advantages of volum e,perform ance and price,and it uses the hardw are logic based on FPG A to im plem ent the read and write controller.The software sim ulation and hardware testing are given in the paper.Eight m em ory chips are used to extend the ca~ pacity,and the G TX high-speed transceiver is used to im prove the speed.Com pared with the single chip storage system ,the design has the characteristics of m ass storage,high—speed reading and w riting. Key words:FPG A ;eM M C ;GTX high—speed transceiver;array storage system ;read and w rite controller

基于FPGA的DDR2 SDRAM控制器设计

基于FPGA的DDR2SDRAM控制器设计钱素琴,刘晶华(东华大学信息科学与技术学院,上海,201600)摘要:基于高速数据传输与存储的数据釆集记录仪对缓存模块高性能的需求,选择了读写速度快、低成本、大容量、运行稳定的DDR2SDRAM作为本地存储器,在其存储寻址原理和IP核的读写控制逻辑的基础上,借助硬件描述语言设计了一个DDR2存储控制器方案。

在Intel的FPGA Cyclone IV系列开发板上进行了整体方案的功能验证,完成了用户接口和控制器之间的多数据宽度、多突发长度的高效数据传输和读写操作,在166.7MHz时钟频率下实现了稳定读写的目标。

关键词:FPGA;DDR2SDRAM;IP核Design of DDR2SDRAM controller based on FPGAQian Suqin,Liu Jinghua(College of information science and technology,Donghua University,Shanghai,201600) Abstract;Based on the requirement of high-speed data transmission and storage data acquisition recorder for high performance of cache module,DDR2SDRAM with high read-write speed,low cost, large capacity and stable operation is selected as the local memory.Based on its storage addressing principle and the read-write control logic of IP core,a DDR2storage controller scheme is designed with the help of hardware description language.The functional verifiestion of the overall scheme is carried out on the FPGA cyclone IV series development board of Intel.The efficient datQ transmission and read-write operation of multipie data widths and burst lengths between the user interface and the cont r oller are comple t ed.The st a ble read-wr ite t a rge t is achieved a/t166.7MHz clock frequency. Keywords:FPGA;DDR2SDRAM;IP coreo引言随着数据采集系统的发展,应用于图像采集和数据传输等领域的产品对存储器的速度要求越来越高。

FPGA片内RAM模拟EEPROM的优化方法

FPGA片内RAM模拟EEPROM的优化方法简介FPGA(现场可编程门阵列)提供了一种灵活且可定制的硬件平台,广泛应用于各种领域。

在FPGA中,片内RAM(Random Access Memory)主要用于存储数据。

在某些应用中,我们需要将片内RAM模拟为EEPROM(Electrically Erasable Programmable Read-Only Memory),以提供非易失性存储。

本文将介绍一种优化方法,以实现FPGA片内RAM的EEPROM模拟。

方法在传统的片内RAM模拟EEPROM方法中,通常使用了多个RAM单元来实现较大的EEPROM存储容量,并通过控制电路模拟EEPROM的读写操作。

然而,这种方法会占用大量的FPGA资源,并且在存储容量较大时会导致性能下降。

为了优化FPGA片内RAM的EEPROM模拟,我们可以采用如下方法:1. 压缩存储空间:通过采用合适的编码方法对数据进行压缩,可以减小存储容量。

例如,使用Huffman编码等压缩算法可以将数据存储在更少的RAM单元中,节省FPGA资源。

2. 分时访问:将RAM划分为多个部分,并采用分时访问的方式,可以提高访问效率。

这样,即使存储容量较大,但每次只需访问其中一部分,减小了读写操作的延迟。

3. 数据预取:通过在RAM中预取常用的数据,可以减少对EEPROM模拟的需求。

例如,将频繁读取的数据存储在RAM中,可以避免每次都去模拟EEPROM进行读取操作,提高性能。

4. 数据缓存:在读取数据时,可以使用数据缓存来提高读取速度。

将最近读取的数据暂时存储在缓存中,下次读取时首先从缓存中获取,减少对EEPROM模拟的需求。

通过以上优化方法,我们可以有效提高FPGA片内RAM模拟EEPROM的性能和资源利用率,实现更优化的设计。

结论本文介绍了一种优化FPGA片内RAM模拟EEPROM的方法。

通过压缩存储空间、分时访问、数据预取和数据缓存等策略,我们可以提高性能并节省FPGA资源。

基于FPGA的外部存储器设计

基于FPGA的外部存储器设计

随着雷达技术的进一步发展,对雷达信号处理的要求越来越高,在实时信号处理过程中有大量数据需要存储,由于FPGA本身的存储器容量非常小,根本满足不了雷达信号处理过程中的需求,为解决这一问题,通过查询资料,引入SDRAM和FLASH作为FPGA的外部存储器。

SDRAM存储器以其快速、方便和价格相对便宜,因而,常被用在雷达信号实时处理上。

选择SDRAM而没有SRAM是因为SRAM价格太贵,SDRAM相对便宜。

没有选择DDR SDRAM的原因是因为在实际的雷达信号处理中并不需要那幺高burst率,SDRAM足以满足实际需求。

SDRAM主要作用:在MTI处理时作为周期延迟器件、动态杂波图的存储和数据暂存等功能。

虽然SDRAM有存储容量大、价格相对便宜等优点,但是其断电所有数据丢失的缺点,使其仅在FPGA外部连接SDRAM作为外部存储器件显然是不能满足设计需求的,因此,在设计过程中考虑到FLASH存储。

在设计中用FLASH存储一些断电不能丢失的数据,如:脉冲压缩处理时的匹配滤波器系数、MTI处理时杂波加权系数、CFAR处理时的对数表以及一些函数求值等。

1 存储电路设计。

基于FPGA的SDRAM控制器设计

基于FPGA的SDRAM控制器设计摘要:介绍了SDRAM的特点和工作原理,提出了一种基于FPGA的SDRAM控制器设计方法,采用Verilog语言完成的控制器的设计,可以很方便地对SDRAM进行操作。

控制器在大容量数据记录仪扩展缓存得到了很好的应用。

关键字:FPGA;SDRAM;V erilog;1 引言在进行高速数据记录仪的开发中,由于硬盘固有的寻道延时,不能实现外部数据实时写入。

采用固态硬盘成本又比较高,所以在设计中考虑外加大容量数据缓存。

在各种随机存储器件中,SRAM的价格低,设计简单,但容量一般都不大;DDR速度快、容量大,但硬件和软件设计都比较复杂。

SDRAM具价格低、体积小、速度快、容量大的优点,是满足高速数据记录设计带宽的理想器件。

但是,与SRAM相比较,SDRAM的控制逻辑复杂,接口方式与普通的存储器差异很大。

为了解决这个矛盾,需要设计专用的SDRAM控制器,本文中提出了SDRAM控制器的FPGA设计,FPGA内部采用状态机的方式。

该设计采用了Altera公司的CycloneII系列EP2C35F484C8N作为主控芯片。

系统工作时钟为75M。

2 SDRAM工作原理简介本设计采用SDRAM芯片选用Winbond公司的W982516,4M×4BANKS×16BIT,两片并成32位数据总线,突发读写速度可达到300Mbytes/s。

W982516采用了54引脚的TSOP封装,工作电压为3.3V,并且采用同步接口方式(所有的信号都是时钟信号的上升沿触发),与系统时钟同步运行。

W982516行地址数目是13,列地址数目是9。

与各种SDRAM 一样,这种SDRAM具有以下几个特点:(1)采取行列地址复用原则,SDRAM的地址线在不同的命令下提供不同的地址,行列地址复用13根地址线。

(2)需要定时刷新。

(3)在进行读写时,需先激活行。

换页读写时要预充关闭的行,然后再激活新的行进行读写。

eeprom

1 引言由于FPGA的出现,使得我们不需要承担较大风险和较高的流片费用将小规模的或处于研发阶段的芯片制成ASIC芯片了。

而基于FPGA的SOC——SOPC(可编程片上系统),由于其可编程性,按照用户特定需要构建的SOPC是一个在某种程度上替代SOC的较好方案。

Altera公司为其FPGA开发了第二代软核嵌入式处理器NiosII,同时开发了用以构建基于NiosII处理器的SOPC Builder,使得用户可以通过自定义逻辑的方法方便地开发基于NiosII的SOPC系统。

SOPC Builder集成在EDA工具QuartusII中,提供了N iosII处理器及一些常用外设接口,如DMA控制器, SDRAM控制器,SPI接口以及锁相环PLL等等,对于一些库中没有提供的模块用户可以自己定义添加。

在实际应用中,具有I2C接口的EEPROM有着广泛的运用,本文就是在基于NiosII的SOPC中设计了一个EEPROM Controller Core,用Verilog HDL描述硬件逻辑部分,同时编写相关驱动,下载到Stratix系列的FPGA中实现了对片外EEPROM AT24C02的读写。

2 基于NiosII的Controller CoreSOPC中的各模块通过Altera公司开发的Avalon总线互连。

任何一个挂接在Avalon总线上的模块都必须符合Avalon总线规范,即包含特定的信号类型clk,reset,chipselect,write,writedata等,并满足一定建立保持时间和等待周期的读写模式。

一个典型模块的Controller Core由硬件和驱动软件两部分构成。

2.1硬件构成基于NiosII的Controller Core是用于构建SOPC的基本组件,它由HDL语言描述其硬件逻辑,一个典型的Controller Core由task logic(行为模块),register file(寄存器),interface(总线接口)三部分组成,它们在逻辑上的关联关系如图1所示:图1Controller Core在逻辑上的关联关系interface是顶层模块,与Avalon总线的直接接口;register file:通信模块,对模块内部寄存器读写的通道;task logic:行为模块,实现模块逻辑功能的核心部分。

基于fpga的eeprom设计

二线制I2C CMOS 串行EEPROM 的FPGA设计姓名:钱大成学号:080230114院系:物理院电子系2011年1月1日一、课程设计摘要:(1)背景知识:A、基本介绍:二线制I2C CMOS 串行EEPROM AT24C02/4/8/16 是一种采用CMOS 工艺制成的串行可用电擦除可编程只读存储器。

B、I2C (Inter Integrated Circuit)总线特征介绍:I2C 双向二线制串行总线协议定义如下:只有在总线处于“非忙”状态时,数据传输才能被初始化。

在数据传输期间,只要时钟线为高电平,数据线都必须保持稳定,否则数据线上的任何变化都被当作“启动”或“停止”信号。

图1 是被定义的总线状态。

①总线非忙状态(A 段)数据线SDA 和时钟线 SCL 都保持高电平。

②启动数据传输(B 段)当时钟线(SCL)为高电平状态时,数据线(SDA)由高电平变为低电平的下降沿被认为是“启动”信号。

只有出现“启动”信号后,其它的命令才有效。

③停止数据传输(C 段)当时钟线(SCL)为高电平状态时,数据线(SDA)由低电平变为高电平的上升沿被认为是“停止”信号。

随着“停在”信号出现,所有的外部操作都结束。

④数据有效(D 段)在出现“启动”信号以后,在时钟线(SCL)为高电平状态时数据线是稳定的,这时数据线的状态就要传送的数据。

数据线(SDA)上的数据的改变必须在时钟线为低电平期间完成,每位数据占用一个时钟脉冲。

每个数传输都是由“启动”信号开始,结束于“停止”信号。

⑤应答信号每个正在接收数据的EEPROM 在接到一个字节的数据后,通常需要发出一个应答信号。

而每个正在发送数据的EEPROM 在发出一个字节的数据后,通常需要接收一个应答信号。

EEPROM 读写控制器必须产生一个与这个应答位相联系的额外的时钟脉冲。

在EEPROM 的读操作中,EEPROM 读写控制器对EEPROM 完成的最后一个字节不产生应答位,但是应该给EEPROM 一个结束信号。

基于FPGA的外部存储器设计

基于FPGA的外部存储器设计FPGA是一种可编程逻辑设备,可以被重新编程用于实现不同的功能。

在计算机系统中,外部存储器是一种用于保存数据的设备,例如硬盘、固态硬盘(SSD)和闪存。

在本文中,我们将探讨如何设计基于FPGA的外部存储器。

外部存储器在计算机系统中起着至关重要的作用,它可以保存大量的数据,并且在计算机断电后,数据仍然可以保持完整。

外部存储器的性能和容量对计算机系统的整体性能具有重要影响。

在大数据应用和高性能计算中,对外部存储器的需求越来越高。

在设计基于FPGA的外部存储器时,我们需要考虑以下几个方面:1.存储介质选择:选择适合的存储介质对于设计外部存储器非常重要。

常见的存储介质包括硬盘、固态硬盘(SSD)和闪存。

每种存储介质都具有不同的性能和容量特性,我们需要根据具体的应用场景进行选择。

2.存储器控制器设计:存储器控制器是FPGA与外部存储器之间的接口。

它负责实现数据的读写操作,以及处理错误检测和纠正功能。

存储器控制器还需要支持各种不同的存储介质和接口标准。

3.存储器接口设计:存储器接口是FPGA与外部存储器之间的物理连接。

常见的存储器接口包括SATA、PCIe和USB。

我们需要根据具体的应用场景选择适合的存储器接口,并确保接口带宽满足数据传输的需求。

4.数据传输优化:在设计外部存储器时,我们需要考虑如何优化数据传输的性能。

这可以通过使用数据缓存、并行数据传输和数据压缩等技术来实现。

优化数据传输可以提高存储器的访问速度和效率。

5.容量扩展性:外部存储器的容量通常是根据应用需求选择的。

在设计存储器时,我们需要考虑到容量的扩展性,以便将来能够方便地增加存储容量。

6.可靠性和可用性:对于外部存储器来说,可靠性和可用性是非常重要的。

我们需要设计一种容错机制,以确保即使在存储设备出现故障的情况下,数据仍然可以安全地存储和恢复。

7.能耗和成本:在设计外部存储器时,我们需要考虑到能耗和成本的限制。

通过采用低功耗设计和选择适当的存储介质,我们可以有效地减少能耗和成本。

基于FPGA的SDRAM控制器设计

基于FPGA的SDRAM控制器设计西南交通大学电气工程学院宋一鸣雷娟李春茂(610031)摘要:本文介绍了SDRAM的结构和控制时序特点,介绍了基于FPGA的SDRAM控制器设计的关键技术,并引入仲裁机制,从而可以快速高效地控制SDRAM。

关键词:SDRAM,FPGA,Verilog,状态机,仲裁机制。

引言SDRAM是新一代的高速、高容量动态存储器,与SRAM相比,不仅容量大得多,并且价格也很便宜。

特别是目前的PCI总线已取代ISA总线成为控制系统总线的主流,随之而来的是对数据访问需求量的增大,SRAM的速度和容量已远远不能满足这些系统的需要。

目前市场上有一些通用的SDRAM控制器,但设置复杂,并且由于是通用的,无法针对特定的系统,因此性能不能发挥到最好,这在很大程度上抵消了使用SDRAM的优势。

因此,我们提出使用可编程逻辑器件平台并通过使用硬件描述语言,针对特定的系统定制自己需要的SDRAM控制器,不仅可以节省系统资源,而且可以最大限度地发挥SDRAM的作用,从而提升系统的性能。

本在一项图像处理系统中采用Verilog语言在FPGA上实现了SDRAM控制器的设计,成功地使SDRAM通过PCI接口与PC机内存之间完成可靠的数据交换。

本文分为三部份,第一部份以Micron公司的128Mb的SDRAM芯片为例介绍SDRAM控制的时序,第二部份介绍基于FPGA的SDRAM控制器设计的关键技术,第三部份介绍以上设计的实现和仿真结果。

SDRAM的控制时序SDRAM需要正确的上电逻辑和模式设置来进入期望的工作模式。

访问特定的逻辑单元必须先激活相应的存储块,并锁定对应的行列地址。

另外,必须有定时的刷新逻辑保持数据不丢失,SDRAM有多种操作模式,由引脚CS#、RAS#、CAS#、WE#和地址信号的不同状态来决定,SDRAM控制器必须为SDRAM提供满足时序要求的这些控制信号,以准确地控制SDRAM的各种不同操作。

基于FPGA的通用存储器控制器的系统设计与实现的开题报告

基于FPGA的通用存储器控制器的系统设计与实现的开题报告一、选题背景及意义FPGA(Field Programmable Gate Array)是一种硬件可编程芯片,它可以通过开发工具对其逻辑、配置、功能等进行编程,实现不同的应用。

随着硬件设计的复杂度和算法的不断变化,FPGA已经广泛应用于许多领域,如数字信号处理、图像处理和通信等领域。

在这些应用中,存储是一个核心问题,因此需要一个强大的存储器控制器来实现数据的读写和管理。

本文将基于FPGA实现一个通用存储器控制器,该控制器可以对各种存储器进行控制,如RAM、Flash、EEPROM等。

通过实现该控制器,可以为FPGA的应用提供更加强大的存储管理能力,提高系统的性能和可靠性。

二、选题内容及研究思路该项目的主要内容是设计和实现一个基于FPGA的通用存储器控制器,支持多种存储器类型。

该控制器需要具备以下特点:1. 支持多种存储器类型:RAM、Flash、EEPROM等;2. 具有强大的存储器管理能力,包括读写操作、地址解码和数据缓存等;3. 具备接口和协议的灵活性,可以适应不同的应用场景,如数据存储、图像处理等;4. 具有高效的存储器读写速度和性能,满足实时性和低延迟的需求。

在实现通用存储器控制器的过程中,需要通过以下步骤来完成:1. 确定控制器的基本功能和性能要求;2. 设计控制器的硬件电路,包括存储器管理模块、地址解码模块、数据缓存模块等;3. 编写控制器的软件代码,实现控制器的接口和协议;4. 对控制器进行验证和测试,验证控制器的性能和稳定性。

三、研究目标和预期成果该项目的研究目标是实现一个高效、灵活和可靠的基于FPGA的通用存储器控制器。

预期的成果包括:1. 设计和实现一个通用存储器控制器的硬件电路和软件代码;2. 验证和测试控制器的性能和稳定性,包括存储器读写速度、响应时间、数据准确性等指标;3. 发表相关论文和技术报告,推广和应用控制器的技术成果。

(完整版)基于FPGA的数字电子钟系统设计毕业论文

基于FPGA的数字电子钟系统设计摘要随着电子技术的飞速发展,现代电子产品渗透到了社会的各个领域,并有力地推动着社会生产力的发展和社会信息化程度的提高。

在现代电子技术中,可编程器无疑是扮演着重要角色。

现场可编程门阵列(FPGA)是近年来迅速发展起来的新型可编程器,其灵活的可编程逻辑可以方便的实现高速数字信号处理。

它突破了并行处理、流水级数的限制,具有反复的可编程能力,从而有效的地利用了片上资源,加上高效的硬件描述语言(VHDL),从而为数字系统设计提供了极大的方便。

本文较系统地介绍了FPGA的基本结构、基本原理、功能特点及其应用;阐述了数字系统设计的基本思想及设计流程,同时,也概述了FPGA在数字系统设计中的作用,基于FPGA的数字系统设计方法和流程;简要介绍了VHDL语言的发展历程,VHDL语言的功能特点等。

本文的主要内容是根据上述原理和方法设计一个电子钟系统,目的在于通过该系统的功能,体现出FPGA在数据处理中的应用。

该电子钟系统功能齐全,设计思路清晰。

系统程序基于VHDL语言,采用模块化设计方法。

系统设计包含8个子程序模块:分频组件、六十进制计数器组件、二十四进制计数器组件、闹钟设定组件、校时组件、i60BCD组件、i24BCD组件、以及二进制转换成七段码组件。

每个子程序均经过EDA 工具仿真,并附有仿真图,最后将各模块组装为一个整体——电子钟。

-关键词电子设计自动化;现场可编程门阵列;硬件描述语言;电子钟-Digital Electronic Clock DesignBased on Technology of FPGAAbstractWith the rapid development of electronic technology, modern electronic products , also increased. In modern electronic technology, the programmable logic devices play a key role.Field programmable gate arrays (FPGA), a new type of programmable device, is developing rapidly recent years.It introduced the concept of flexible programmable logic, which can realize -chip resources, coupled with efficient language VHDL, so as to design digital systems conveniently. This article introduces a system of the basic structure of the FPGA, the basic principle of features and applications; expounded on the basic design of digital systems thinking and design process, at the same time, also outlined the FPGA in the design of digital systems, FPGA-based digital system design methods and processes; gave a briefing on the development of VHDL language, VHDL language and other features.The main work is based on the principles and methods, design an electronic clock system to the adoption of the system, embodied in the FPGA data processing of applications. The electronic clock system is fully functional, designed clear ideas. Based on VHDL system procedures, The system is modular in design methods. It includes 8 sub-system design process modules:frequency division system, 60 M counter system,24 M-counter system,Alarm clock settings system, timing system, i60BCD system, i24BCD system, and convert binary into Seven-Segment code system. each subroutine simulated by EDA tools, with a simulation map. The modules will be the final assembly as a whole - the electronic clock.Key words EDA;FPGA; VHDL; Electronic clock-目录摘要 (I)Abstract (II)第1章绪论 (1)1.1课题背景和意义 (1)1.2可编程器件的发展历程 (1)1.2.1早期的可编程器件——PLD (2)1.2.2高级可编程器件FPGACPLD (3)1.3国内外研究现状 (4)1.4本文主要内容 (5)第2章FPGA基本结构及数字系统设计原理 (6)2.1 FPGA的基本结构及工作原理 (6)2.1.1基于查找表结构的FPGA (8)2.1.2查找表结构的FPGA逻辑实现原理 (8)2.1.3 FPGA的工作原理 (9)2.2数字系统设计概述 (9)2.2.1数字系统的组成 (10)2.2.2数字系统设计方法 (10)2.2.3数字系统设计的一般过程 (11)2.3本章小结 (12)-第3章数字电子钟功能模块设计 (13)3.1数字系统设计中的FPGA (13)3.1.1 FPGA在数字系统设计中的作用 (13)3.1.2基于FPGA的应用系统设计 (13)3.2数字系统设计的重要工具——VHDL (16)3.2.1 VHDL语言的特点 (16)3.2.2基于VHDL的系统设计流程 (17)3.3电子钟主要功能模块设计 (18)3.3.1分频模块 (18)3.3.2六十进制计数器模块 (19)3.3.3二十四进制计数器模块 (20)3.3.4校时模块 (22)3.3.5 BCD七段显示译码器 (23)3.4本章小结 (23)第4章电子钟模拟仿真及其分析 (24)4.1系统设计的总体思路 (24)4.2各功能模块仿真分析 (25)4.2.1 分频组件 (25)4.2.2 六十进制计数器组件 (25)4.2.3 二十四进制计数器组件 (26)4.2.4 闹钟设定组件 (26)4.2.5 校时组件 (27)4.2.6 i60BCD组件 (28)4.2.7 i24BCD组件 (29)4.2.8 二进制转换成七段码组件 (30)4.3数字电子钟功能仿真图 (30)4.4采用FPGA设计优势分析 (33)4.5本章小结 (34)结论 (35)致谢 (36)参考文献 (37)附录A (38)附录B (43)附录C (47)附录D (48)第1章绪论1.1课题背景和意义20世纪70年代,随着中小规模集成电路的开发应用,传统的手工制图设计印刷电路板和集成电路的方法已无法满足设计的精度和效率的要求。

基于高云FPGA的I2C读写EEPROM

基于高云 FPGA的 I2C读写 EEPROM摘要:无线通信设备设计中,需要对功率平坦度进行调试,所以需要将每个频点的数控衰减值存储于EEPROM,以便设备在正常工作中,使用该衰减值,达到功率输出一致的要求。

同时由于无线通信设备的硬件差异性和环境影响,使得无线通信设备的正反向功率等参数不一致,所以需要EEPROM存储每个设备的基准值,已达到无线通信设备的一致性。

本文主要选用国产芯片使用VHDL语言实现EEPROM的读写,来实现数控衰减值和基准值的存储和读出,广东高云半导体FPGA芯片GW2A-LV55PBGA484C8/I7作为主机,成都华微电子EEPROm芯片HWD24C512作为为从机。

关键词:FPGA;I2C;EEPROM1 引言I2C总线(I2C bus,Inter-IC bus)是一个双向的两线连续总线,提供集成电路之间的通信线路,它是一种串行扩展技术,即就是完成集成电路或功能单元之间的信息交换的规范或者协议[1]。

I2C总线采用一条数据(SDA:串行数据线Serial data line),加一条时钟线(SCL:串行时钟线Serial clock line)来完成数据的传输及外围器件的扩展。

I2C在芯片的配置中应用很广泛,比如摄像头、VGA转HDMI转换芯片[2]。

无线通信设备设计中,需要对功率平坦度进行调试。

即就是对其所有工作频点进行功率校准,使设备处于发射状态时,所有工作频点下输出功率基本一致并且在特定的范围内,否则会出现状态不一致甚至烧坏其他部件的情况。

本文通过改变每个频点下的数控衰减值,以达到功率一致,并将每个频点的数控衰减值存储于EEPROM,以便设备在正常工作中,使用该衰减值,达到功率输出一致的要求。

无线通信设备设计中,由于硬件差异性和环境影响,使得无线通信设备的一致性不同,为了使得控制一致,所以需要EEPROM存储每个设备的基准值,已达到无线通信设备的一致性。

本文以实际项目中用于存储参数的EEPROM的读写设计为实例。

基于FPGA的存储解决方案

基于FPGA的存储解决方案——片内存储器片内存储器是基于FPGA的嵌入系统可使用的最简单的存储器。

由于存储是在FPGA内部完成,电路板上无需外部连线。

可以简单地选择SOPC builder中System Contents-> On-Chip Memory选项,来完成设计中的片内存储器。

也可以根据需求定义片内存储器的大小、带宽、种类、及特殊的片内存储器性质,如DDR等。

优点片内存储器在基于FPGA的嵌入系统可使用的存储器中是具有最高吞吐量和最低反应延时的。

它的反应延时通常仅为一个时钟周期。

通过存储处理管道化,可以使吞吐量达到每个时钟周期进行一次处理。

有些片内存储器被设计成可以在DDR模式下进行存取,其中读和写是分别进行操作的。

DDR模式能够有效地实现双倍存储带宽,允许存储器在一个通道进行写入,同时在另一个通道进行读取。

片内存储器的另一个好处是,由于它是在FPGA上直接实现的,它无需在板上或电路中进行写入。

使用片内存储器可以节省开发时间和成本。

一些片内存储器可以在FPGA配置时自动初始化。

这种存储器可以被用来保持小数据量的启动代码或重启动所需的LUT数据。

缺点尽管速度很快,片内存储器在一定程度上会受到其容量的限制。

FPGA可用的片内存储器的数量由使用的特定FPGA器件决定,容量范围从最小的Cyclone II device中15KB到最大的Stratix III device中近2MB。

因为多数片内存储器都是易失性的,它在断电后丢失数据。

然而,某些片内存储器可以在FPGA配置时自动初始化,相当于提供了一种非易失性的功能。

最佳应用场合以下是片内存储器适宜的一些应用。

缓存由于其具有低反应延时,片内存储器在微处理器中作为缓存表现良好。

Nios II处理器使用片内存储器作为引导和数据缓存。

片内存储器有限的容量作为缓存通常不是一个问题,因为缓存本身都相对很小。

点到点的缓存能够在低反应时间下进行存取也使得片内存储器适用于做器件间的缓存,即点到点的缓存,它是指处于正常的寻址空间,但与微处理器有专用接口的存储器。

用EEPROM对大容量FPGA芯片数据实现串行加载

用EEPROM对大容量FPGA芯片数据实现串行加载自大规模现场可编程规律器件问世以来,先后浮现了两类器件,一类是基于SRAM体系结构的系列,如XILINX公司的4000系列和最新的Virtex 系列;另一类是基于faxtFLASH技术的器件,如XILINX公司的9500系列和Lattice公司的ispLSxx系列芯片。

FPGA具有容量大、设计资源丰盛、片内ROM及RAM设计灵便等特点1,但是它们需要在每次上电时举行数据加载。

目前实现加载的办法有以下三种:①采纳PROM并行加载;②采纳专用SROM串行加载;③采纳控制实现加载。

第一种方式需要占用较多的FPGA管脚资源,虽然这些管脚在加载完成后可用作普通I/O口,但在加载时不允许这些管脚有其他任何外来信号源;另外数据存储器PROM与FPGA之间的大量固定连线如8位数据线以及大量拜访PROM的地址线等,使得设计不便。

但是第一种方式有一个有利的方面,即PROM的容量较大、简单购置、价格低、技术支持(编程器)较好。

其次种方式状况刚好与第一种方式相反,即占用资源少、PCB布板便利,但是容量小、价格较高、兼容性差。

第三种方式采纳单片机控制,由PROM中读取并行数据,然后再串行送出。

因为涉及到单片机编程,对于开发者来说较为不便;另外,假如单片机仅用来实现该任务,较为铺张硬件资源。

CPLD的一个最大优点是采纳计算机专用开发工具,通过JTAG口挺直一次性实现编程数据加载,并永远保留,除非举行再次编程(与GAL器件相像)。

该类器件比较适合在试验室内举行现场调试,但是因为其数据的加载必需通过计算机,因此对于从事野外作业者来说会产生不便。

通过上述比较,并结合实际工作状况,我们认为采纳串行数据加载比较便利、牢靠(这种牢靠性得益于FPGA与SROM之间较少的接口线)。

但随着FPGA规模的不断升级,其CONFIG数据量越来越大,截止到本文写作时,CONFIG数据量最大已到6MBIT,虽然XILINX公司有相关的XC17X系列SROM提供用法,但皆为一次性芯片?2、开发成本较高、代理商供货周期长、价格较高,这给FPGA的应用及普及带来很大的障碍。

基于FPGA的外部存储器设计

基于FPGA的外部存储器设计邓志清【摘要】In order to improve the processing speed for mass data storage of radar signals, a high-speed external memory based on FPGA was designed. The feasibility of the design method was verified. The high-speed external memory can effectively improve the data storage speed and shorten the read-write time. This memory makes full use of the design convenience of FPGA, and the high-speed read-write superiority of SDRAM and FLASH to meet the high-speed and real-time signal processing requirements. It also has the advantages of low cost, good compatibility and easy engineering realization.%为了提高雷达海量数据的处理速度,采用FPGA设计了一种高速外部存储器,通过多次实验,验证了设计方法的可行性.高速外部存储器可以有效地提高数据存储速度,节约读/写时间,从而满足信号处理的高速实时的要求.这种方法充分利用FPGA设计方便,SDRAM和FLASH的存储读写速度快的优势,具有成本低廉,兼容性强,易于工程实现的特点.【期刊名称】《现代电子技术》【年(卷),期】2011(034)014【总页数】4页(P131-134)【关键词】雷达信号处理;FPGA;SDRAM;FLASH;存储器设计【作者】邓志清【作者单位】江苏科技大学电子信息学院,江苏,镇江,212003【正文语种】中文【中图分类】TN911-340 引言随着雷达技术的进一步发展,对雷达信号处理的要求越来越高,在实时信号处理过程中有大量数据需要存储[1],由于FPGA本身的存储器容量非常小,根本满足不了雷达信号处理过程中的需求,为解决这一问题,通过查询资料[2-4],引入SDRAM和FLASH作为FPGA的外部存储器。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

二线制I2C CMOS 串行EEPROM 的FPGA设计姓名:钱大成学号:080230114院系:物理院电子系2011年1月1日一、课程设计摘要:(1)背景知识:A、基本介绍:二线制I2C CMOS 串行EEPROM AT24C02/4/8/16 是一种采用CMOS 工艺制成的串行可用电擦除可编程只读存储器。

B、I2C (Inter Integrated Circuit)总线特征介绍:I2C 双向二线制串行总线协议定义如下:只有在总线处于“非忙”状态时,数据传输才能被初始化。

在数据传输期间,只要时钟线为高电平,数据线都必须保持稳定,否则数据线上的任何变化都被当作“启动”或“停止”信号。

图1 是被定义的总线状态。

·①总线非忙状态(A 段)数据线SDA 和时钟线 SCL 都保持高电平。

②启动数据传输(B 段)当时钟线(SCL)为高电平状态时,数据线(SDA)由高电平变为低电平的下降沿被认为是“启动”信号。

只有出现“启动”信号后,其它的命令才有效。

③停止数据传输(C 段)当时钟线(SCL)为高电平状态时,数据线(SDA)由低电平变为高电平的上升沿被认为是“停止”信号。

随着“停在”信号出现,所有的外部操作都结束。

④数据有效(D 段)在出现“启动”信号以后,在时钟线(SCL)为高电平状态时数据线是稳定的,这时数据线的状态就要传送的数据。

数据线(SDA)上的数据的改变必须在时钟线为低电平期间完成,每位数据占用一个时钟脉冲。

每个数传输都是由“启动”信号开始,结束于“停止”信号。

⑤应答信号每个正在接收数据的EEPROM 在接到一个字节的数据后,通常需要发出一个应答信号。

而每个正在发送数据的EEPROM 在发出一个字节的数据后,通常需要接收一个应答信号。

EEPROM 读写控制器必须产生一个与这个应答位相联系的额外的时钟脉冲。

在EEPROM 的读操作中,EEPROM 读写控制器对EEPROM 完成的最后一个字节不产生应答位,但是应该给EEPROM 一个结束信号。

C、3. 二线制I2C CMOS 串行EEPROM读写操作① EEPROM 的写操作(字节编程方式)所谓EEPROM 的写操作(字节编程方式)就是通过读写控制器把一个字节数据发送到EEPROM 中指定地址的存储单元。

其过程如下:EEPROM 读写控制器发出“启动”信号后,紧跟着送4 位I2C 总线器件特征编码1010 和3 位EEPROM 芯片地址/页地址XXX 以及写状态的R/W 位(=0),到总线上。

这一字节表示在接收到被寻址的EEPROM 产生的一个应答位后,读写控制器将跟着发送1 个字节的EEPROM 存储单元地址和要写入的1 个字节数据。

EEPROM 在接收到存储单元地址后又一次产生应答位以后,读写控制器才发送数据字节,并把数据写入被寻址的存储单元。

EEPROM 再一次发出应答信号,读写控制器收到此应答信号后,便产生“停止”信号。

字节写入帧格式如图2 所示:②二线制I2C CMOS 串行EEPROM 的读操作所谓EEPROM 的读操作即通过读写控制器读取EEPROM 中指定地址的存储单元中的一个字节数据。

串行EEPROM 的读操作分两步进行:读写器首先发送一个“启动”信号和控制字节(包括页面地址和写控制位)到EEPROM,再通过写操作设置EEPROM 存储单元地址(注意:虽然这是读操作,但需要先写入地址指针的值),在此期间EEPROM 会产生必要的应答位。

接着读写器重新发送另一个“启动”信号和控制字节(包括页面地址和读控制位R/W = 1),EEPROM 收到后发出应答信号,然后,要寻址存储单元的数据就从SDA 线上输出。

读操作有三种:读当前地址存储单元的数据、读指定地址存储单元的数据、读连续存储单元的数据。

在这里只介绍读指定地址存储单元数据的操作。

读指定地址存储单元数据的帧格式如图3:(2)实现功能及设计思路:EEPROM是要实现接收来自信号源模型产生的读信号、写信号、并行地址信号、并行数据信号,并把它们转换为相应的串行信号发送到串行EEPROM(AT24C02/4/8/16)的行为模型中去的功能,同时它还发送应答信号(ACK)到信号源模型,以便让信号源来调节发送或接收数据的速度以配合EEPROM模型的接收(写)和发送(读)数据。

其基本设计思路是利用同步有限状态机的设计方法实现,根据串行EEPROM的读写特性,用五个状态时钟完成写操作,用七个状态时钟完成读操作,通过编写EEPROM读写器的模块以及随机读写数据模块,再加上信号产生模块,最终封装在一块完成初步的设计。

二、系统设计部分(1)整体设计的组织结构(2)子单元设计结构:①EEPROM 的行为模型为了设计这样一个电路我们首先要设计一个EEPROM 的Verilog HDL 模型,而设计这样一个模型我们需要仔细地阅读和分析EEPROM 器件的说明书,因为EEPROM 不是我们要设计的对象,而是我们验证设计对象所需要的器件,所以只需设计一个EEPROM 的行为模型,而不需要可综合风格的模型,这就大大简化了设计过程。

下面的Verilog HDL 程序就是这个EEPROM(AT24C02/4/8/16)能完成一个字节数据读写的部分行为模型。

这里只对在操作中用到的信号线进行模拟,对于没有用到的信号线就略去了。

对EEPROM用于基本总线操作的引脚SCL和SDA说明如下:SCL,串行时钟端,这个信号用于对输入和输出数据的同步,写入串行EEPROM的数据用其上升沿同步,输出数据用其下降沿同步;SDA,串行数据(/地址)输入/输出端。

EEPROM的行为模型如下://---------------eeprom.v文件开始-----------------`define timeslice 100module EEPROM(scl,sda);input scl;inout sda;reg out_flag;reg[7:0] memory[2047:0];reg[10:0] address;reg[7:0] memory_buf;reg[7:0] sda_buf;reg[7:0] shift;reg[7:0] addr_byte;reg[7:0] ctrl_byte;reg[7:0] State;integer i;//------------------------------------------parameter r7= 8'b10101110, w7= 8'b10101110, //main7 r6= 8'b10101101, w6= 8'b10101100, //main6 r5= 8'b10101011, w5= 8'b10101010, //main5 r4= 8'b10101001, w4= 8'b10101000, //main4 r3= 8'b10100111, w3= 8'b10100110, //main3 r2= 8'b10100101, w2= 8'b10100100, //main2 r1= 8'b10100011, w1= 8'b10100010, //main1 r0= 8'b10100001, w0= 8'b10100000; //main0 //---------------------------------------------assign sda =(out_flag == 1) ? sda_buf[7] : 1'bz;//---------------------寄存器和存储器初始化--------initialbeginaddr_byte = 0;ctrl_byte = 0;out_flag = 0;sda_buf = 0;State = 2'b00;memory_buf = 0;address = 0;shift = 0;for(i=0;i<2047;i=i+1)memory[i] = 0;end//--------------启动信号-----------------------always@(negedge sda)if(scl == 1)beginState = State + 1;if(State == 2'b11)disable write_to_eeprm;end//----------------主状态机----------------------always@(posedge sda)if(scl == 1)stop_W_R;elsebegincasex(State)2'b01:/******************************************************************************************************/beginread_in;if(ctrl_byte == w7 || ctrl_byte == w6 || ctrl_byte == w5|| ctrl_byte == w4 || ctrl_byte == w3 || ctrl_byte == w2 || ctrl_byte == w1 || ctrl_byte == w0 )beginState = 2'b10;write_to_eeprm;endelseState = 2'b00;end2'b11:read_from_eeprm;default:State=2'b00;endcaseend//------------------------操作停止----------------------task stop_W_R;beginState = 2'b00;addr_byte = 0;ctrl_byte = 0;out_flag = 0;sda_buf = 0;endendtask//--------------------读进控制字和存储单元地址--------------task read_in;beginshift_in(ctrl_byte);shift_in(addr_byte);endendtask//--------------------EEPROM的写操作-----------------------task write_to_eeprm;beginshift_in(memory_buf);address ={ctrl_byte[3:1],addr_byte};memory[address] =memory_buf;$display("eeprm-----memory[%0h]=%0h",address,memory[address]); State =2'b00;endendtask//----------------------EEPROM的读操作--------------------task read_from_eeprm;beginshift_in(ctrl_byte);if(ctrl_byte == r7 || ctrl_byte == r6 || ctrl_byte == r5|| ctrl_byte == r4 || ctrl_byte == r3 || ctrl_byte == r2|| ctrl_byte == r1 || ctrl_byte == r0)beginaddress ={ctrl_byte[3:1],addr_byte};sda_buf = memory[address];shift_out;State = 2'b00;endendendtask//---SDA数据线上的数据存入寄存器,数据在SCL的高电平有效---------- task shift_in;output[7:0]shift;begin@(posedge scl) shift[7] = sda;@(posedge scl) shift[6] = sda;@(posedge scl) shift[5] = sda;@(posedge scl) shift[4] = sda;@(posedge scl) shift[3] = sda;@(posedge scl) shift[2] = sda;@(posedge scl) shift[1] = sda;@(posedge scl) shift[0] = sda;@(negedge scl)begin#`timeslice ;out_flag =1;sda_buf =0;end@(negedge scl)#`timeslice out_flag = 0;endendtask//---EEPROM存储器中的数据通过SDA数据线输出,数据在SCL低电平时变化-------task shift_out;beginout_flag = 1;for(i=6;i>=0;i=i-1)begin@(negedge scl);#`timeslice;sda_buf = sda_buf<<1;end@(negedge scl) #`timeslice sda_buf[7] = 1;@(negedge scl) #`timeslice out_flag = 0;endendtaskendmodule//-----------------eeprom.v文件结束----------------------------②EEPROM读写器的可综合的Verilog HDL模型下面的程序是一个串行EEPROM读写器的可综合的Verilog HDL模型,它接收来自信号源模型产生的读信号、写信号、并行地址信号、并行数据信号,并把它们转换为相应的串行信号发送到串行EEPROM(AT24C02/4/8/16)的行为模型中去;它还发送应答信号 (ACK)到信号源模型,以便让信号源来调节发送或接收数据的速度以配合EEPROM模型的接收(写)和发送(读)数据。