单片机数字钟设计实习报告

数字钟实习报告总结

实习报告总结:数字钟设计与实现一、实习背景与目的随着现代电子技术的快速发展,数字钟作为一种常见的电子设备,已经被广泛应用于日常生活和工业领域。

本次实习的主要目的是学习和掌握数字钟的设计与实现方法,培养自己的实际动手能力和创新思维能力。

二、实习内容与过程1. 数字钟的设计原理在实习初期,我首先学习了数字钟的设计原理,包括数字电路的基本组成、时钟信号的产生与处理、显示电路的设计等。

通过学习,我了解了数字钟的工作原理和设计思路,为后续的实际操作奠定了基础。

2. 硬件设计在硬件设计方面,我选择了常用的微控制器AT89S52作为数字钟的控制核心。

通过编程,实现了时钟信号的产生、分秒的计数和显示等功能。

同时,我还设计了按键输入电路,以便进行时间设置和调整。

3. 软件编程在软件编程方面,我使用了C语言进行编程。

通过编写程序,实现了数字钟的计时、显示等功能。

在程序设计过程中,我充分运用了所学的算法和编程技巧,提高了自己的编程能力。

4. 系统调试与优化在系统调试阶段,我通过不断测试和调整,发现并解决了数字钟运行中出现的问题。

同时,我对程序进行了优化,提高了数字钟的运行效率和稳定性。

三、实习收获与总结通过本次实习,我收获颇丰。

首先,我掌握了数字钟的设计原理和实现方法,为自己的实际工作积累了宝贵的经验。

其次,我在硬件设计和软件编程方面提高了自己的实际动手能力,为今后的职业发展打下了基础。

最后,我在实习过程中培养了团队协作意识和创新思维能力,对自己的人生发展具有积极意义。

同时,我也认识到自己在本次实习中存在的不足。

例如,在硬件焊接和调试过程中,我对一些细节处理不够到位,导致数字钟运行不稳定。

在今后的工作中,我将更加注重细节,提高自己的动手能力。

总之,本次实习使我受益匪浅。

通过学习和实践,我掌握了数字钟的设计与实现方法,提高了自己的实际动手能力和创新思维能力。

在今后的学习和工作中,我将继续努力,不断提高自己,为实现自己的职业目标奋斗。

单片机设计数字钟实验报告

单片机实验报告——数字钟设计班级:学号:姓名:时间:一.实验目的1、进一步熟悉C的语法知识和keil环境;2、熟练掌握一些常用算法;3、熟悉keil的编写、下载、调试过程;4、了解单片机的工作原理和电路图;5、熟悉单片机的外围电路功能模块、LED灯、数码管模块以及键盘;6、熟练焊接技术。

二.实验器件三.数字钟设计原理数字钟实际是对标准频率计数的电路,由于计数的起始时间不可能与标准时间一致,故需要在电路上加一个校时电路,同时标准的时间信号必须做到准确稳定。

通常使用石英晶体振荡电路构成数字钟。

数字钟电子钟由以下几部分组成:按键开关部分,振荡电路部分,89c51单片机控制器,4位数码管显示部分,7407数码管驱动部分。

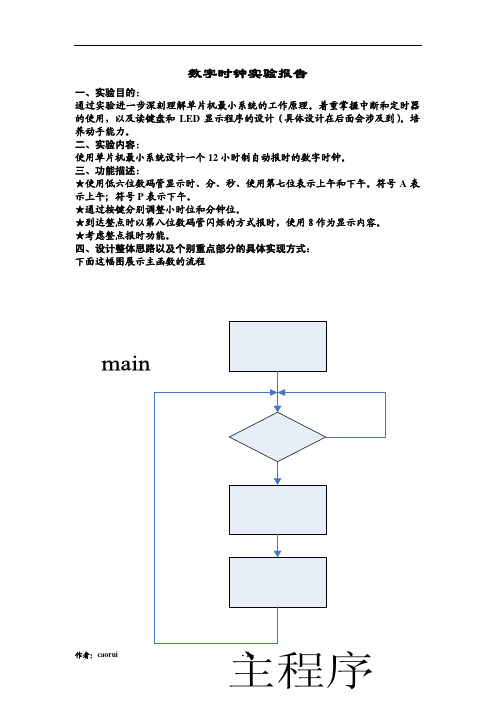

按键开关振荡电路89C51单片机控制器4位数码管显示7407列驱动四.流程图主程序流程图如图2.3所示,定时器T0中断服务程序流程图如2.4所示。

返回五.51单片机系统的硬件连接1、STC单片机最小系统硬件电路图如下2、硬件电路的设计该电路采用AT89C51单片机最小化应用,采用共阴7段LED数码管显示器,P2.4~P2.7口作为列扫描输出,P0口输出段码数据,P1.2,P1.1口接2个按钮开关,用于调时及功能误差,采用12Mhz晶振,可提高秒计时的精确度。

六.程序设计HOUR EQU 3AH ;赋值伪指令MIN EQU 3BHSEC EQU 3CHBUFF EQU 3DHORG 0000HAJMP MAINORG 000BH ;主程序入口AJMP PTF0ORG 0033H ;跳转到标号PTF0执行;**************************************************************;主程序MAIN: MOV HOUR, #00H ;时,分,秒,标记清零MOV MIN, #00HMOV SEC, #00HMOV BUFF, #00HMOV SP, #0EFH ;设堆栈指针MOV TH0, #0ECH ;定时器赋初值MOV TL0, #78HMOV 40H, #100 ;设循环次数MOV 41H, #2MOV TMOD , #1 ;写TMODMOV IP, #2 ;写IPMOV IE, #82HMOV R5,#0;开中断SETB TR0 ;启动定时器PTF0: SETB P1.2MOV TH0, #0ECHMOV TL0, #78HINC R5MOV R6,BUFFCJNE R6,#00H,BBMOV DPTR,#TAB1LJMP LOOP0BB:MOV DPTR,#TABLOOP0: CJNE R5,#1,LOOP1ACALL LOP0AJMP JKLOOP1:CJNE R5,#2,LOOP2ACALL LOP1AJMP JKLOOP2:CJNE R5,#3,LOOP3ACALL LOP2AJMP JKLOOP3:ACALL LOP3MOV R5,#0JK: DJNZ 40H, PTFORXRL BUFF, #0FFHMOV 40H, #100JNB P1.1, JFJNB P1.2, JSMOV R7, 41HCJNE R7, #1, AAAA: DJNZ 41H, PTFORMOV 41H,#2MOV A, SEC ;秒加1ADD A, #1DA AMOV SEC, ACJNE A, #60H, PTFORMOV SEC, #0 ;秒清零JF: MOV A, MIN ;分加1ADD A, #1DA AMOV MIN, ACJNE A, #60H,PTFORMOV MIN, #0 ; 分清零ACALL LEDJS: MOV A,HOURADD A,#1DA AMOV HOUR,A ;时加1CJNE A, #24H,PTFOR ;时加到24时否?是,清零MOV HOUR, #0PTFOR:RETILOP0: MOV A, MIN ;显示分钟的个位ANL A, #0FHMOVC A, @A+DPTRMOV P0,AMOV P2,#0F0HCLR P2.4CLR P0.4RETLOP1:MOV A, MIN ;显示分钟的十位SWAP AANL A, #0FHMOVC A, @A+DPTRMOV P0, AMOV P2, #0F0HCLR P2.5CLR P0.4RETLOP2: MOV A, HOUR ;显示时钟的个位ANL A, #0FHMOVC A, @A+DPTRMOV P0, AMOV P2, #0F0HCLR P2.6RETLOP3:MOV A, HOUR ;显示时钟的十位SWAP AANL A, #0FHMOVC A, @A+DPTRMOV P0, AMOV P2, #0F0HCLR P2.7CLR P0.4RETTAB: DB 3FH,06H,5BH,4FH,66H,6DH,7DH,07H,7FH,6FH ;不带小数点的字型码TAB1:DB 0BFH,86H,0DBH,0CFH,0E6H,0EDH,0FDH,87H,0FFH,0EFH ;带小数点的字型码END七.系统调试及结果分析硬件调试硬件电路板中器件连接好后,先用万用表测试电路中有无虚焊短接之处,测试无误后,将板子通电,进行静态调试。

51单片机数字钟设计实习报告

51单片机数字钟设计实习报告目录一.设计方案: (3)二.设计内容: (3)三.相关总线及芯片介绍: (3)1.SPI总线: (3)2.74LS595芯片: (4)3. 实验箱电路图: (6)四.系统软件程序设计: (6)五.设计程序: (8)六.程序调试及显示: (11)七.实习心得: (12)八.参考文献: (13)一.设计方案:通过单片机内部的计数/定时器,采用软件编程来实现时钟计数,一般称为软时钟,这种方法的硬件线路简单,系统的功能一般与软件设计相关,通常用在对时间精度要求不高的场合。

二.设计内容:这里采用应用广泛的C51作为时钟控制芯片,利用单片机内部的定时/计数器T0 实现软时钟的目的。

首先将T0设定工作于定时方式,对机器周期计数形成基准时间(50ms),然后用另一个定时/计数器T1对基准时间计数形成秒,秒计60次形成分,分计60形成小时,小时计到12或者24。

通过外部中断实现12进制与24进制的切换。

最后通过数码管把它们的内容在相应的位置显示出来,达到时、分、秒计时的功能。

三.相关总线及芯片介绍:1.SPI总线:SPI(Serial Peripheral Interface--串行外设接口)总线系统是一种同步串行外设接口,它可以使MCU与各种外围设备以串行方式进行通信以交换信息。

外围设置FLASHRAM、网络控制器、LCD显示驱动器、A/D转换器和MCU等。

SPI 总线系统可直接与各个厂家生产的多种标准外围器件直接接口,该接口一般使用4条线:串行时钟线(SCK)、主机输入/从机输出数据线MISO、主机输出/从机输入数据线MOSI和低电平有效的从机选择线SS(有的SPI接口芯片带有中断信号线INT或INT、有的SPI接口芯片没有主机输出/从机输入数据线MOSI)。

由于SPI系统总线一共只需3~4位数据线和控制即可实现与具有SPI总线接口功能的各种I/O器件进行接口,而扩展并行总线则需要8根数据线、8~16位地址线、2~3位控制线,因此,采用SPI总线接口可以简化电路设计,节省很多常规电路中的接口器件和I/O口线,提高设计的可靠性。

单片机数字时钟实验报告

数字时钟实验报告一、实验目的:通过实验进一步深刻理解单片机最小系统的工作原理。

着重掌握中断和定时器的使用,以及读键盘和LED显示程序的设计(具体设计在后面会涉及到)。

培养动手能力。

二、实验内容:使用单片机最小系统设计一个12小时制自动报时的数字时钟。

三、功能描述:★使用低六位数码管显示时、分、秒、使用第七位表示上午和下午。

符号A表示上午;符号P表示下午。

★通过按键分别调整小时位和分钟位。

★到达整点时以第八位数码管闪烁的方式报时,使用8作为显示内容。

★考虑整点报时功能。

四、设计整体思路以及个别重点部分的具体实现方式:下面这幅图展示主函数的流程下面描述的是调用T0中断时所进行的动作显示更新的函数具体见下面这幅图我们还一个对键盘进行扫描以获得有效键盘值,其具体的实现见下面这幅图● 要实现时钟的运行和时间的调整,我的设计思路是这样的:由于T0中断的时间间隔是4ms,那么我可以设置一个计数器i,在每次进入中断时进行加一调整,当i计满面250时就将时钟我秒的低位加一。

然后根据进位规则,对其后的各位依次进行调整。

●要实现整点报时功能,则可以根据时位是否为0判断是否要闪烁显示字符8。

至于闪烁的具体实现方式,见源程序。

至此,本实验的设计思路己基本介绍完毕。

下面就是本次实验的源程序代码。

/*********************************************************//** 数字时钟程序**//** **//*********************************************************/#include <absacc.h>#include <reg51.h>#define uchar unsigned char#define uint8 unsigned char#define uint16 unsigned int#define LED1 XBYTE [0xA000] //数码管地址#define LED2 XBYTE [0xA001]#define LED3 XBYTE [0xA002]#define LED4 XBYTE [0xA003]#define LED5 XBYTE [0xA004]#define LED6 XBYTE [0xA005]#define LED7 XBYTE [0xA006]#define LED8 XBYTE [0xA007]#define KEY XBYTE [0xA100] //键盘地址bit ap=0;//上下午int i=0;//计数器uchar data clock[7]={0,0,0,0,0,0,0};/*扫描键盘使用的变量 */sbit first_row = P1^4; //键盘第一行控制sbit second_row = P1^3; //键盘第二行控制bit first_getkey = 0,control_readkey = 0; //读键盘过程中的标志位bit getkey = 0; //获得有效键值标志位等于1时代表得到一个有效键值bit keyon = 0; //防止按键冲突标志位uchar keynum = 0; //获得的有效按键值寄存器/*数码管显示使用的变量和常量*/uchar lednum = 0; //数码管显示位控制寄存器uchar led[8] = {0,0,0,0,0,0,0,0}; //数码管显示内容寄存器uchar code segtab[18] = {0xc0,0xf9,0xa4,0xb0,0x99,0x92,0x82,0xf8,0x80,0x90,0x88,0x83,0xc6,0xa1,0x86,0x8e,0x8c,0xff}; //七段码段码表// "0", "1", "2", "3", "4", "5", "6", "7", "8", "9", "A", "B", "C", "D","E", "F", "P" ,"black"void leddisp(void); //数码管显示函数void readkey(void); //读键盘函数void intT0() interrupt 1 //T0 定时中断处理函数{TH0 = -2720/256; //定时器中断时间间隔 4msTL0 = -2720%256;if((clock[2]==0)&&(clock[3]==0)&&(i==125)&&(clock[5]<=5)&&(clock[4]==0))led[7]=17;if((clock[2]==0)&&(clock[3]==0)&&(i==0)&&(clock[5]<=5)&&(clock[4]==0))led[7]=8;i=i+1;if(i==250){if((clock[2]==0)&&(clock[3]==0)&&(clock[4]==0)&&(clock[5]==0)&&(clock[6]==0)){ap=!ap;if(ap==0)led[6]=10;if(ap==1)led[6]=16;}clock[5]=clock[5]+1;i=0;}if(clock[5]==10){clock[5]=0;clock[4]=clock[4]+1;}if(clock[4]==6){clock[4]=0;clock[3]=clock[3]+1;}if(clock[3]==10){clock[3]=0;clock[2]=clock[2]+1;}if(clock[2]==6){clock[2]=0;clock[6]=clock[6]+1;}if(clock[6]==12){clock[6]=0;}clock[0]=clock[6]/10;clock[1]=clock[6]%10;led[5]=clock[0];led[4]=clock[1];led[3]=clock[2];led[2]=clock[3];led[1]=clock[4];led[0]=clock[5];leddisp(); //每次定时中断显示更新一次if(control_readkey == 1) //每两次定时中断扫描一次键盘{readkey();}c ontrol_readkey = !control_readkey;}void main(void){TMOD = 0x01; //TH0 = -2720/256; //定时器中断时间间隔 4msTL0 = -2720%256;TCON = 0x10;ET0 = 1;EA = 1;while(1){if(getkey == 1) //判断是否获得有效按键{getkey = 0;switch(keynum) //判断键值,对不同键值采取相应的用户定义处理方式{case 0x01: //当按下第一行第二列键时,分加一clock[3]=clock[3]+1;break;case 0x02: ////当按下第一行的第三列键时,分减一clock[3]=clock[3]-1;break;case 0x03://当按下第一行的第四列时,时加一clock[6]=clock[6]+1;break;case 0x04:clock[6]=clock[6]-1; //当按下第一行的第五列时,时减一break;default:break;}}}}/***************************************************键盘扫描函数原型: void readkey(void);功能: 当获得有效按键时,令getkey=1,keynum为按键值****************************************************/void readkey(void){uchar M_key = 0;second_row = 0;M_key = KEY;if(M_key != 0xff) //如果有连续两次按键按下,认为有有效按键按下。

单片机实验报告-数字时钟设计报告

单片机实验报告-数字时钟设计报告一、实验目的1、掌握单片机的主要原理及相关的功能和特点。

2、熟悉单片机测试与调试的一般步骤与操作。

3、掌握定时/计数功能在单片机系统中的实现方法。

4、领会单片机实验模块设计思想。

二、实验内容本次实验主要是利用STC89C52单片机实现数字时钟设计,实验从硬件电路组成和单片机编程两个部分来实现数字时钟的设计。

(1)硬件电路设计该系统的硬件电路设计主要包括PCB板的设计、电源的设置、单片机与外设的连接以及时钟芯片的接入。

利用Altium Designer软件来进行电路板设计,将STC89C52芯片与时钟模块(DS1302)以及屏幕连接,整个电路如图1所示。

图1 数字时钟使用STC89C52的电路图(2)单片机程序设计本实验使用keil软件对单片机程序进行编程,主要的部分如下:(2.1)定义单片机IO口首先定义单片机IO口,其定义方式如下:#include<reg52.h>sbit Row0=P1^0; //定义P1.0作为数码管的Row0控制端sbit Row1=P1^7; //定义P1.7作为数码管的Row1控制端sbit Row2=P1^1; //定义P1.1作为数码管的Row2控制端sbit Row3=P2^0; //定义P2.0作为数码管的Row3控制端sbit Col0=P1^2; //定义P1.2作为数字管的Col0控制端sbit Col1=P1^3; //定义P1.3作为数字管的Col1控制端sbit Col2=P1^4; //定义P1.4作为数字管的Col2控制端sbit Col3=P1^5; //定义P1.5作为数字管的Col3控制端sbit Col4=P1^6; //定义P1.6作为数字管的Col4控制端(2.2)定义LED数码管数据和定义变量//定义LED数码管数据unsigned char codetable[10]={0xc0,0xf9,0xa4,0xb0,0x99,0x92,0x82,0xf8,0x80,0x90};unsigned char i,j,k,m,n,s;(2.3)调用初始化函数再调用初始化函数,用于完成I/O口、定时器0/1及外部中断的初始化,代码如下:void init (void){TMOD=0x01; //定时器0的模式1TH0=0x3c; //定时器0赋初值TL0=0xb0;EA=1; //外部总中断开启ET0=1; //允许定时器0中断ET1=0; //不允许定时器1中断TR0=1; //开启定时器0TR1=1; //关闭定时器1}(2.4)主函数最后我们考虑到,应该实现的LED点阵的显示函数和定时更新时钟的函数,本实验的核心代码如下:void main(){init(); //调用初始化函数while(1){display(); //调用LED点阵显示函数number_refresh(); //调用定时更新时钟函数}}(2.5)LED点阵显示函数为保证LED点阵的正常工作,可利用多次延时函数,定义LED点阵显示函数,每次显示一位数字,实现数字从左往右以及从右往左的滚动移动显示,具体实现如下:void display (int ){P2=0xfe; //定义P2这一行位先低电平,控制第一位显示P0=table[m]; //将得到的数字m 显示在第一位数码管Delay_1ms(2); //延时1msP2=0xfd; //定义P2这一行位先低电平,控制第二位显示P0=table[n]; //将得到的数字n 显示在第二位数码管Delay_1ms(2); //延时1msP2=0xfb; //定义P2这一行位先低电平,控制第三位显示P0=table[s]; //将得到的数字s 显示在第三位数码管Delay_1ms(2); //延时1msP2=0xf7; //定义P2这一行位先低电平,控制第四位显示P0=table[i]; //将得到的数字i 显示在第四位数码管Delay_1ms(2); //延时1msP2=0xef; //定义P2这一行位先低电平,控制第五位显示P0=table[j]; //将得到的数字j 显示在第五位数码管Delay_1ms(2); //延时1msP2=0xdf; //定义P2这一行位先低电平,控制第六位显示P0=table[k]; //将得到的数字k 显示在第六位数码管Delay_1ms(2); //延时1ms}(2.6)定时更新时钟函数本部分,利用定时器0的中断功能实现定时更新LED点阵时间,定义定时器0中断函数,实现每隔一秒更新一次,更新变量m、n、s、i、j、k,代码如下:ㄖ/Timer 0中断函数void Timer0() interrupt 1{TH0=0x3c; //定时器0赋初值TL0=0xb0;m++; //每秒,m值加1if(m>9) //当m的值大于9时,n值加1{n++;m=0;}if(n>9) //当n的值大于9时,s值加1{s++;n=0;}if(s>5) //当s的值大于5时,i值加1{i++;s=0;}if(i>9) //当i的值大于9时,j值加1{j++;i=0;}if(j>5) //当j的值大于5时,k值加1{k++;j=0;}if(k>9) //当k的值大于9时,m值加1{k=0;m=0;}}三、实验结果本次实验让我深入理解单片机及一些外设的工作原理,掌握定时/计数机制,以及实现数字时钟设计的思维过程。

单片机数字钟实习报告

一、实习目的随着电子技术的飞速发展,单片机作为一种重要的电子元件,在工业、医疗、通讯等领域得到了广泛的应用。

为了更好地掌握单片机的原理和应用,提高动手能力,我们选择了单片机数字钟作为实习项目。

通过本次实习,我们旨在掌握单片机的编程、调试、硬件连接等方面的知识,实现数字时钟的显示与控制。

二、实习内容1. 单片机数字钟硬件设计(1)选用AT89C51单片机作为核心控制单元,具有丰富的片上资源,方便编程和调试。

(2)采用LCD1602液晶显示屏,显示时间、日期等信息。

(3)使用DS1302实时时钟芯片,实现时间的存储和更新。

(4)选用按键作为输入设备,实现时间的调整和设置。

(5)选用蜂鸣器作为报警设备,实现定时报警功能。

2. 单片机数字钟软件设计(1)编写主程序,实现系统初始化、时间显示、按键扫描、时间调整等功能。

(2)编写中断服务程序,实现DS1302时钟芯片的读写、按键消抖等功能。

(3)编写子程序,实现时间的计算、格式化、显示等功能。

3. 单片机数字钟调试与测试(1)连接电路,检查各个模块的连接是否正确。

(2)编写程序,将程序烧录到单片机中。

(3)调试程序,确保程序运行正常。

(4)测试各个功能模块,如时间显示、按键调整、定时报警等。

三、实习过程1. 硬件设计(1)根据设计要求,绘制电路原理图。

(2)购买所需元器件,进行焊接。

(3)组装电路板,连接各个模块。

2. 软件设计(1)编写程序,采用C语言进行编程。

(2)使用Keil软件进行编译、烧录。

(3)在仿真软件Proteus中进行仿真,验证程序的正确性。

3. 调试与测试(1)连接电路,检查各个模块的连接是否正确。

(2)编写程序,将程序烧录到单片机中。

(3)调试程序,确保程序运行正常。

(4)测试各个功能模块,如时间显示、按键调整、定时报警等。

四、实习总结1. 通过本次实习,我们掌握了单片机的编程、调试、硬件连接等方面的知识。

2. 学会了使用LCD1602液晶显示屏、DS1302实时时钟芯片、按键等元器件。

单片机实验报告数字时钟设计报告

单片机实验报告数字时钟设计报告一、实验目的本次单片机实验的目的是设计并实现一个基于单片机的数字时钟。

通过该实验,深入了解单片机的工作原理和编程方法,掌握定时器、中断、数码管显示等功能的应用,提高综合运用知识解决实际问题的能力。

二、实验原理1、单片机选择本次实验选用了常见的 51 系列单片机,如 STC89C52。

它具有丰富的资源和易于编程的特点,能够满足数字时钟的设计需求。

2、时钟计时原理数字时钟的核心是准确的计时功能。

通过单片机内部的定时器,设定合适的定时时间间隔,不断累加计时变量,实现秒、分、时的计时。

3、数码管显示原理采用共阳或共阴数码管来显示时间数字。

通过单片机的 I/O 口控制数码管的段选和位选信号,使数码管显示相应的数字。

4、按键控制原理设置按键用于调整时间。

通过检测按键的按下状态,进入相应的时间调整模式。

三、实验设备与材料1、单片机开发板2、数码管3、按键4、杜邦线若干5、电脑及编程软件(如 Keil)四、实验步骤1、硬件连接将数码管、按键与单片机开发板的相应引脚通过杜邦线连接起来。

确保连接正确可靠,避免短路或断路。

2、软件编程(1)初始化单片机的定时器、中断、I/O 口等。

(2)编写定时器中断服务程序,实现秒的计时。

(3)设计计时算法,将秒转换为分、时,并进行进位处理。

(4)编写数码管显示程序,将时间数据转换为数码管的段选和位选信号进行显示。

(5)添加按键检测程序,实现时间的调整功能。

3、编译与下载使用编程软件将编写好的程序编译生成可执行文件,并下载到单片机中进行运行测试。

五、程序设计以下是本次数字时钟设计的主要程序代码片段:```cinclude <reg52h>//定义数码管段选码unsigned char code SEG_CODE ={0xC0, 0xF9, 0xA4, 0xB0, 0x99, 0x92, 0x82, 0xF8, 0x80, 0x90};//定义数码管位选码unsigned char code BIT_CODE ={0x01, 0x02, 0x04, 0x08, 0x10,0x20, 0x40, 0x80};//定义时间变量unsigned int second = 0, minute = 0, hour = 0;//定时器初始化函数void Timer_Init(){TMOD = 0x01; //定时器 0 工作在方式 1 TH0 =(65536 50000) / 256; //定时 50ms TL0 =(65536 50000) % 256;EA = 1; //开总中断ET0 = 1; //开定时器 0 中断TR0 = 1; //启动定时器 0}//定时器 0 中断服务函数void Timer0_ISR() interrupt 1{TH0 =(65536 50000) / 256;TL0 =(65536 50000) % 256;second++;if (second == 60){second = 0;minute++;if (minute == 60){minute = 0;hour++;if (hour == 24){hour = 0;}}}}//数码管显示函数void Display(){unsigned char i;for (i = 0; i < 8; i++)P2 = BIT_CODEi;if (i == 0){P0 = SEG_CODEhour / 10;}else if (i == 1){P0 = SEG_CODEhour % 10;}else if (i == 2){P0 = 0xBF; //显示“”}else if (i == 3){P0 = SEG_CODEminute / 10;else if (i == 4){P0 = SEG_CODEminute % 10;}else if (i == 5){P0 = 0xBF; //显示“”}else if (i == 6){P0 = SEG_CODEsecond / 10;}else if (i == 7){P0 = SEG_CODEsecond % 10;}delay_ms(1);//适当延时,防止闪烁}}//主函数void main(){Timer_Init();while (1){Display();}}```六、实验结果与分析1、实验结果将程序下载到单片机后,数字时钟能够正常运行,准确显示时、分、秒,并且通过按键可以进行时间的调整。

单片机数字钟实习报告

单片机数字钟实习报告一、实习目的和意义随着计算机科学与技术的飞速发展,计算机的应用已经渗透到国民经济与人们生活的各个角落,而单片机技术作为计算机技术中的一个独立分支,具有性价比高、集成度高、体积小、可靠性高、控制功能强大、低功耗、低电压等特点,因此在各个领域得到了广泛的应用。

本次实习旨在通过设计一款数字钟,使学生掌握单片机的原理及其应用,提高实际动手能力和创新能力。

数字钟作为一种典型的数字电路,包括组合逻辑电路和时序电路。

通过设计制作数字钟,可以让学生了解数字钟的原理,学会制作数字钟,并进一步了解各种中小规模集成电路的作用及实用方法。

同时,通过数字钟的制作,可以让学生进一步学习与掌握各种组合逻辑电路与时序电路的原理与使用方法。

二、实习内容和要求1. 设计一款基于单片机的数字钟,能显示时、分、秒。

2. 数字钟具有校时功能,能以24小时为一个周期循环显示时间。

3. 掌握单片机的原理及其编程方法,熟悉LCD1602液晶显示屏的使用。

4. 了解数字钟的原理,学会制作数字钟,并掌握各种组合逻辑电路与时序电路的原理与使用方法。

三、实习过程1. 首先,我们对单片机的原理进行了学习,了解了单片机的内部结构、工作原理及其编程方法。

同时,我们还学习了LCD1602液晶显示屏的使用,掌握了如何将单片机与LCD1602液晶显示屏进行连接。

2. 接下来,我们开始了数字钟的设计。

首先,我们设计了数字钟的电路原理图,包括了单片机、LCD1602液晶显示屏、按键、时钟芯片等元件。

然后,我们进行了电路板的焊接,焊接过程中,我们严格遵循电路焊接规范,确保了电路板的质量和稳定性。

3. 焊接完成后,我们开始了数字钟的程序编写。

我们编写了相应的程序,实现了数字钟的时、分、秒显示功能以及校时功能。

在编程过程中,我们深入理解了单片机的编程原理,掌握了Keil编程软件的使用。

4. 最后,我们对数字钟进行了调试和测试。

我们通过观察数字钟的显示效果,分析了可能存在的问题,并针对问题进行了改进。

数字时钟的设计实习报告

数字时钟的设计实习报告一、实习目的本次实习旨在通过设计一个数字时钟,使学生掌握数字电路的设计方法,熟悉集成电路的使用,提高对单片机的学习和应用能力,培养学生的软硬件开发能力。

二、实习内容1. 设计一个数字时钟,能够显示时分秒。

2. 掌握数字时钟的设计方法。

3. 熟悉集成电路的使用方法。

4. 培养学习、设计、开发软、硬的能力。

三、实习过程1. 首先,我们对数字时钟的设计进行了需求分析,明确了数字时钟的功能和要求。

数字时钟应能够显示时分秒,采用24小时标准计时制。

2. 接下来,我们进行了数字时钟的设计方案制定。

数字时钟主要由单片机、LED数码管、按键等部分构成。

单片机负责控制整个系统,LED数码管用于显示时间,按键用于调整时间。

3. 然后,我们进行了数字时钟的硬件设计。

我们选择了AT89C52单片机作为核心控制器,6个共阳极的高亮度LED数码管用于显示时间,还选择了两个按键用于调整时间。

4. 在硬件设计的基础上,我们进行了数字时钟的软件设计。

我们编写了程序,使单片机能够控制LED数码管显示时间,并能够通过按键调整时间。

5. 最后,我们对数字时钟进行了测试和调试,确保其功能的正确性和稳定性。

四、实习心得通过本次实习,我们掌握了数字时钟的设计方法,熟悉了集成电路的使用方法,提高了对单片机的学习和应用能力。

我们在设计过程中,学会了如何分析需求、制定方案、设计硬件和软件,并通过测试和调试,确保设计的正确性和稳定性。

此外,我们还学会了如何协作和沟通,提高了团队协作能力。

在设计过程中,我们遇到了很多问题,但通过互相讨论和请教老师,我们逐一解决了问题,取得了实习的成功。

五、实习成果本次实习,我们成功设计了一个数字时钟,能够显示时分秒,并具有时间调整功能。

数字时钟的硬件电路稳定运行,软件程序正确无误。

六、实习展望在今后的学习和工作中,我们将继续深入学习数字电路和单片机的相关知识,提高自己的设计能力和开发水平。

我们还将把在实习中学到的知识和技能应用到实际项目中,为我国电子行业的发展做出贡献。

单片机数字钟设计总结

单片机数字钟设计总结第一篇:单片机数字钟设计总结单片机数字钟设计总结经过一周的课程设计,我收获颇多,有深刻的心得体会。

实训让我们受益匪浅。

首先是关于单片机方面的。

我们学到了许多关于单片机系统开发的知识,从最开始选题到最后的结题,更使我们得到了充分的锻炼。

其次,它让我体会到了什么才是teamwork spirit。

一如:团队管理的经验、团队意识的提升和协调能力等等,这些都会让我们终身受益。

通过此次课程设计,使我更加扎实的掌握了有关电子线路单片机方面的知识,在设计过程中虽然遇到了一些问题,但经过一次又一次的思考,一遍又一遍的检查我终于找出了问题所在,也暴露出了前期我在这方面的知识欠缺和经验不足。

实践才能出真知,实践才是检验真理的唯一标准,唯有通过亲自动手制作,才能令我们掌握的知识不再是一些纸上谈兵的东西。

在这次的课程设计中,我们遇到了很多困难,过程很艰难,但是我们都克服了,这是对我们自己的肯定。

我们不断发现错误,不断改正,不断领悟,不断获取。

我们也曾灰心,也曾茫然,也曾不知所措,从一开始的自信满满,到最后的紧张繁杂,所有的这些都令我们回味无穷,这已经成为了我们人生的一个宝藏。

我想今后的学习和工作也是这样的,汗水见证着成功,我想十年过后,但我们都已经走入了社会,在某个阳光明媚的夏日,午后醒来,突然想起大学经历的时候,最先映入脑海里的就是这门课程吧,就是这些为了一个共同的目标,相互合作,共同奋斗的日子吧。

不可否认,单片机是一门比较难的专业学科。

但是经过这一学期的学习,我们觉得单片机这门课很好,让我们在设计中掌握课程,具有很强的实用性。

在社会上,单片机也应用极其广泛。

通过这次课程设计,我掌握了常用元件的识别和测试;熟悉了常用仪器、仪表;了解了电路的连线方法;以及如何提高电路的性能等等。

我相信在接下来的日子里,我会更深刻地去研究它,发掘它。

在这次的实训里,我觉得过得很充实。

实训,不仅培养了我们独立思考、动手操作的能力,在各种其它能力上也都有了提高。

单片机设计时钟实训报告

一、引言随着科技的不断发展,单片机技术在电子领域得到了广泛的应用。

为了提高学生的实践能力,培养实际工程应用能力,我们进行了单片机设计时钟实训。

本实训以AT89C51单片机为核心,通过学习时钟电路的设计、编程和调试,使学生掌握单片机在时钟设计中的应用,提高学生的动手能力和创新思维。

二、实训目的1. 掌握单片机的基本原理和编程方法;2. 熟悉时钟电路的设计和调试;3. 培养学生的实际工程应用能力和创新思维;4. 提高学生的团队协作能力和沟通能力。

三、实训内容1. 硬件设计(1)单片机选型:选用AT89C51单片机作为核心控制单元;(2)时钟电路:采用晶振电路作为时钟源,实现1Hz的基准时钟;(3)显示电路:采用LCD1602液晶显示屏,实现时间、日期和星期等信息显示;(4)按键电路:设计4个按键,分别用于设置时间、日期、星期和闹钟功能;(5)复位电路:采用上电复位和按键复位两种方式,保证系统稳定运行。

2. 软件设计(1)系统初始化:初始化单片机,设置波特率、定时器等;(2)时间显示:通过读取实时时钟芯片(如DS1302)的数据,显示时间、日期和星期;(3)按键处理:根据按键输入,实现时间、日期、星期和闹钟的设置与修改;(4)闹钟功能:当设定的时间到达时,通过蜂鸣器发出提示音。

3. 调试与优化(1)调试方法:使用Proteus软件进行仿真调试,观察程序运行状态,分析故障原因;(2)优化方法:针对仿真过程中出现的问题,优化程序代码,提高程序运行效率。

四、实训过程1. 硬件制作(1)按照设计图纸,焊接电路板;(2)连接晶振、LCD显示屏、按键和蜂鸣器等元器件;(3)调试电路,确保各元器件正常工作。

2. 软件编写(1)使用Keil C51软件编写程序,实现时钟显示、按键处理和闹钟功能;(2)编译程序,生成HEX文件。

3. 调试与优化(1)使用Proteus软件进行仿真调试,观察程序运行状态;(2)针对仿真过程中出现的问题,优化程序代码,提高程序运行效率;(3)将优化后的程序烧录到单片机中,进行实际运行测试。

数字钟电子实习报告

实习报告实习时间:2023年7月1日至2023年7月31日实习单位:XX科技有限公司实习内容:数字钟的设计与制作一、实习目的通过本次实习,我希望能够掌握数字钟的设计原理,了解数字钟的制作流程,提高自己的实际操作能力,培养自己的创新意识和团队协作能力。

二、实习要求1. 熟悉数字钟的设计原理和制作流程。

2. 能够独立完成数字钟的设计和制作。

3. 了解常用电子元器件的性能和使用方法。

4. 具备一定的电路调试和故障排除能力。

三、实习过程1. 设计阶段:在实习的第一周,我们学习了数字钟的设计原理,包括时钟芯片的使用、显示模块的连接、电路图的设计等。

在导师的指导下,我们独立完成了数字钟的设计方案,并进行了讨论和修改。

2. 制作阶段:在实习的第二周,我们开始着手制作数字钟。

我们按照设计方案,选择了合适的电子元器件,进行了电路连接和焊接。

在制作过程中,我们遇到了一些问题,如电路连接错误、元器件损坏等,但在导师的帮助下,我们逐一解决了这些问题。

3. 调试阶段:在实习的第三周,我们开始对制作的数字钟进行调试。

我们使用了调试工具,如万用表、示波器等,对电路进行了检测和调整。

通过不断的调试,我们成功地使数字钟运行起来,并进行了功能测试。

4. 总结与改进:在实习的最后一周,我们对制作的数字钟进行了总结和评估。

我们发现了一些不足之处,如显示模块的亮度不够、时钟精度不够高等。

我们讨论了改进的方法,并提出了一些改进方案,如使用更亮的显示模块、调整时钟频率等。

四、实习收获通过本次实习,我掌握了数字钟的设计原理和制作流程,提高了自己的实际操作能力。

我学会了如何选择合适的电子元器件,进行电路连接和焊接,掌握了调试工具的使用方法,能够对电路进行检测和调整。

在制作过程中,我学会了如何解决问题和团队合作,培养了自己的创新意识和团队协作能力。

五、实习体会通过本次实习,我深刻体会到了理论与实践相结合的重要性。

只有在实际操作中,我们才能真正理解和掌握所学知识。

单片机数码时钟实训报告

一、实训目的本次单片机数码时钟实训旨在通过实际操作,让学生了解单片机的应用,掌握单片机数码时钟的设计与实现方法,提高学生的实践操作能力和创新思维。

二、实训内容1. 硬件设计(1)单片机:选用AT89C51单片机作为核心控制器。

(2)显示模块:采用4位数码管,实现时分秒的显示。

(3)时钟模块:采用12MHz晶振作为时钟源,通过单片机的定时器/计数器实现秒、分、时的计时。

(4)按键模块:设计启动/停止按钮、设置按钮、清零按钮等,实现对时钟的控制和设置。

(5)电源模块:采用5V电源适配器为系统供电。

2. 软件设计(1)主程序:初始化单片机,设置定时器/计数器,实现时分秒的计时。

(2)中断服务程序:实现按键控制、时间设置、清零等功能。

(3)显示程序:将计时的时分秒数据转换为数码管显示的格式。

三、实训过程1. 硬件搭建(1)按照电路图连接AT89C51单片机、数码管、晶振、按键等元件。

(2)检查电路连接是否正确,确保无短路、断路等现象。

2. 软件编写(1)编写主程序,初始化单片机,设置定时器/计数器,实现时分秒的计时。

(2)编写中断服务程序,实现按键控制、时间设置、清零等功能。

(3)编写显示程序,将计时的时分秒数据转换为数码管显示的格式。

3. 调试与测试(1)将编写好的程序烧录到单片机中。

(2)打开电源,观察数码管显示的时分秒是否正确。

(3)测试按键控制功能,包括启动/停止、设置、清零等。

(4)测试时间设置功能,包括小时、分钟、秒的设置。

四、实训结果1. 硬件方面:成功搭建了单片机数码时钟的硬件电路,包括单片机、数码管、晶振、按键等元件。

2. 软件方面:成功编写了单片机数码时钟的程序,实现了时分秒的计时、按键控制、时间设置等功能。

3. 功能实现:数码时钟能够正常显示时分秒,并通过按键控制实现启动/停止、设置、清零等功能。

五、实训总结1. 通过本次实训,使学生掌握了单片机数码时钟的设计与实现方法,提高了学生的实践操作能力和创新思维。

数字钟课程设计实习报告

数字钟课程设计实习报告一、实习目的与要求本次数字钟课程设计实习旨在让同学们熟悉数字电路的设计与实践,掌握集成电路的引脚安排、各芯片的逻辑功能及使用方法,了解面包板结构及其接线方法,培养同学们动手实践能力和问题解决能力。

实习要求设计并制作一个数字电子钟,具体要求如下:1. 显示时、分、秒,时间以24小时为一个周期;2. 具有校时功能,可以分别对时、分进行单独校正;3. 计时过程具有报时功能,当时间到达整点前5秒进行蜂鸣报时;4. 保证计时的稳定及准确,须由晶体振荡器提供表针时间基准信号。

二、实习过程1. 设计原理及其框图数字钟的构成实际上是一个对标准频率(1HZ)进行计数的计数电路。

由于计数的起始时间不可能与标准时间(如北京时间)一致,故需要在电路上加一个校时电路,同时标准的1HZ时间信号必须做到准确稳定。

通常使用石英晶体振荡器电路构成数字钟,其一般构成框图如下:图1 数字钟的组成框图2. 电路设计本次实习采用32768HZ晶振产生振荡脉冲,然后经过CD4060分频后得到2HZ脉冲,再经过74LS74(D触发器)2分频得到1HZ脉冲,由74HC161计数器计数再经CD4511译码器译码后产生驱动数码显示器的信号,使数码显示器呈现出时、分、秒对应的计时数字。

电路还增加了校正电路和整点报时电路,时、分、秒都可手动按键校正,使其准确的工作,在整点的时候发出警报,在每个整点前鸣叫五次低音(500Hz),整点时再鸣叫一次高音(1000Hz)。

3. 元器件及参数选择本次实习所需元器件及参数如下:(1)石英晶体振荡器:32768HZ;(2)CD4060:分频系数为1024;(3)74LS74:D触发器;(4)74HC161:十进制计数器;(5)CD4511:BCD至七段译码器;(6)数码显示器:7段LED;(7)晶体管:放大报警声音;(8)蜂鸣器:报警声音输出。

4. 电路仿真与调试在电路设计完成后,使用Multisim软件进行电路仿真,验证电路功能的正确性。

单片机数字时钟实训报告

一、实训目的本次实训旨在通过设计和实现单片机数字时钟,使学生掌握单片机的基本原理和应用技术,提高学生的动手能力和实践技能。

通过实训,使学生熟悉单片机的硬件结构、编程方法和调试技巧,了解数字时钟的设计原理和实现方法,培养学生的创新意识和团队协作能力。

二、实训内容1. 硬件设计(1)单片机选型:MSP430F5529(2)显示模块:OLED显示屏(3)按键模块:4个按键(4)蜂鸣器模块:蜂鸣器(5)电源模块:电源电路2. 软件设计(1)系统初始化:设置系统时钟、初始化OLED显示屏、按键扫描、蜂鸣器控制等(2)实时时钟(RTC)实现:通过MSP430F5529的RTC模块获取当前时间(3)时间显示:在OLED显示屏上显示年、月、日、时、分、秒等信息(4)整点报时:在整点时刻通过蜂鸣器播放音乐进行报时(5)按键控制:通过按键实现时间的设置、闹钟的设定等功能三、实训过程1. 硬件搭建(1)根据设计图纸,连接MSP430F5529单片机、OLED显示屏、按键、蜂鸣器等元器件(2)搭建电源电路,为单片机和显示屏提供稳定的电源(3)检查连接是否正确,确保电路安全可靠2. 软件编写(1)使用C语言编写程序,实现系统初始化、实时时钟获取、时间显示、整点报时、按键控制等功能(2)编写程序代码,实现各个功能模块的代码(3)调试程序,确保程序运行正确3. 系统调试(1)将程序烧录到MSP430F5529单片机中(2)连接OLED显示屏、按键、蜂鸣器等模块(3)检查系统运行情况,确保各个功能正常(4)调整程序参数,优化系统性能四、实训结果与分析1. 系统功能实现本次实训成功实现了单片机数字时钟的功能,包括时间显示、整点报时、按键控制等。

系统运行稳定,各项功能正常。

2. 系统性能分析(1)实时时钟获取:通过MSP430F5529的RTC模块获取当前时间,精度较高(2)时间显示:OLED显示屏显示清晰,信息完整(3)整点报时:在整点时刻通过蜂鸣器播放音乐进行报时,声音清晰(4)按键控制:通过按键实现时间的设置、闹钟的设定等功能,操作方便3. 系统优化(1)优化程序代码,提高程序运行效率(2)改进显示效果,提高用户体验(3)增加闹钟功能,实现定时提醒五、实训总结1. 通过本次实训,使学生掌握了单片机的基本原理和应用技术,提高了学生的动手能力和实践技能2. 学生学会了如何使用MSP430F5529单片机设计数字时钟,了解了数字时钟的设计原理和实现方法3. 学生培养了创新意识和团队协作能力,为今后的学习和工作打下了良好的基础4. 实训过程中,学生遇到了各种问题,通过查阅资料、讨论和请教老师,最终解决问题,提高了学生的解决问题的能力5. 本次实训使学生认识到理论知识与实践相结合的重要性,激发了学生的学习兴趣,为今后的学习和工作奠定了基础。

数字钟实习报告

实习报告:数字钟设计与实现一、实习目的本次实习的主要目的是通过设计和实现一个数字钟,深入理解数字电路的基本原理和应用,提高自己的实际操作能力和解决问题的能力。

同时,通过实习过程,了解电子钟表的工作原理,掌握数字电路的设计方法和流程。

二、实习内容1. 数字钟的设计:以单片机为核心,设计一个具有小时、分钟、秒数显示功能的数字钟。

2. 数字电路的实现:使用数字电路元件,如电阻、电容、二极管、三极管等,搭建数字钟的电路。

3. 程序编写:编写程序代码,实现数字钟的功能。

4. 系统调试:对数字钟进行调试,确保其正常运行。

三、实习过程1. 设计阶段:在老师的指导下,学习数字电路的基本原理,了解数字钟的设计方法。

通过查阅资料,确定数字钟的显示方式、时钟源等参数。

2. 实现阶段:根据设计方案,购买所需元件,搭建数字钟的电路。

在搭建过程中,遇到一些问题,如电路连接错误、元件损坏等,通过请教老师和同学,逐步解决问题。

3. 编程阶段:学习单片机的编程语言,如C语言,编写数字钟的程序代码。

在编程过程中,遇到一些难题,如时序问题、数据处理等,通过查阅资料、请教老师和同学,克服困难,完成编程。

4. 调试阶段:对数字钟进行调试,发现一些问题,如显示不稳定、时间误差等,分析原因,修改程序和电路,直至数字钟正常运行。

四、实习收获1. 理论知识:通过实习,掌握了数字电路的基本原理和单片机编程技术,为今后的学习和工作奠定了基础。

2. 实际操作能力:在实习过程中,学会了使用电子工具,如万用表、示波器等,提高了自己的实际操作能力。

3. 团队协作能力:在实习过程中,与同学们共同解决问题,分工合作,培养了团队协作能力。

4. 解决问题能力:在实习过程中,遇到许多问题,如电路连接错误、编程难题等,通过请教老师、查阅资料和与同学讨论,逐步解决问题,提高了自己的解决问题的能力。

五、实习总结通过本次实习,我对数字电路和单片机编程有了更深入的了解,提高了自己的实际操作能力和解决问题的能力。

单片机数字钟设计报告

XXXX学院课程设计(实训)报告学院 XXXXXXXXX 专业 XXXXXXXXXX班级 XXXXXXXXX 学号 XXXXXXXXX 姓名 XXXXXXXXX 课题数字钟指导教师 XXXXXXXXX 报告成绩______________ 日期:2013 年 3 月22 日摘要近年来随着计算机在社会领域的渗透和大规模集成电路的发展,单片机的应用正在不断地走向深入,由于它具有功能强,体积小,功耗低,价格便宜,工作可靠,使用方便等特点,因此特别适合于与控制有关的系统,越来越广泛地应用于自动控制,智能化仪器,仪表,数据采集,军工产品以及家用电器等各个领域,单片机往往是作为一个核心部件来使用,在根据具体硬件结构,以及针对具体应用对象特点的软件结合,以作完善。

本次设计中以单片机的发展过程和发展方向为背景,应用了定时器/计数器、中断、片内外存贮器、I/O口、串行口通讯,数码管的使用,蜂鸣器的使用。

本次做的数字钟是以单片机(AT89C51)为核心,结合相关的元器件:共阴极LED数码显示器,再配以相应的软件,是它具有万年历,闹钟,秒表的功能,并且相互之间还可以调整。

此次设计电子数字钟是为了进一步复习及,从而学会运用单片机知识,以此制作电子数字钟。

而且通过电子数字钟的制作进一步的了解各种在制作中用到的中小规模集成电路的作用及实用方法。

通过它可以进一步学习与掌握单片机原理与使用方法。

关键字:单片机,数字时钟目录一、课程设计目的 (4)二、课程设计任务与要求 (4)2.1 课程设计题目........................................ 错误!未定义书签。

2.2 课程设计要求........................................ 错误!未定义书签。

三、设计题目原理分析 (4)3.1 多功能数字钟实现的功能 (4)3.2 按键控制 (4)四、硬件设计内容.............................................. 错误!未定义书签。

单片机数字电子钟课程设计实训报告

第一章设计概要设计要求:1、用单片机及6位LED数码管显示时、分、秒00时00分00秒——23时59分59秒循环运行2、整点提醒0,1…23时短蜂鸣3、用按键实现时、分、秒调整*4、省电功能(关闭显示)*5、定时设定提醒如设定08时15分00秒长蜂鸣*6、秒表功能显示××分××秒. ××健复位从00分00秒00开始计时启动从00分00秒00开始计时停止显示实际计时××分××秒××第二章硬件设计方案2.1设计框架图2.2总体设计方案说明设计框架图如图2.1所示总共分为5小部分:时间显示部分,键盘控制部分,单片机部分,闹钟部分,电源部分。

本设计各部分由统一电源集中供电,外加被用电源确保主电源断电时备用电源及时供电避免时间的丢失.采用12MHZ晶振为单片机提供时钟。

显示部分采用容易购买的LED八段数码显示管,利用单片机输出高低电平实现数码管的刷新显示。

LED具有显示明亮,容易识别,价格便宜等优点,特别适合时间的显示。

按键部分采用普通的按建开关,使用查询方式从而节约元件。

12.3数码显示管设计部分.图3.1-1数码显示部分采用八块共阳极八段数码显示管分别对时,分,秒进行显示。

将第三块和第六块显示横杠,可以使时间显示更美观.显示部分采用刷新显示方案.具体如下:当p2口输出第一块的三极管导通,u1数码管被选中,然后p0口输出数字的数码管编码。

如p0口输出时u1数码管就输出数字0。

当循环右移一位是u2被选通显示。

依次类推u1-u8数码管显示完成,再循环显示。

由于单片机的刷新速度很快所以8个数码管看起来就像同时显示的一样。

2.4 键盘控制电路键盘部分采用普通的按键进行设计,使用软件延时消除开关抖动.2.5 闹铃电路闹铃电路通过p1.7口输出1HZ脉冲使蜂鸣器发出间隔为一秒的蜂鸣声.32.6电源电路2.7 总体电路图设计图3.4-15第三章软件设计方案3.1 程序流程图3.2 总体程序设计//主程序ORG 0000HAJMP MAINORG 000BHAJMP TZPORG 0030HMAIN: MOV SP,#60HMOV R4,#00HMOV TMOD,#02hMOV TH0,#06HMOV TL0,#06HSETB EASETB ET0SETB TR0//初始化MOV R2,#3MOV R1,#30HLOOP: MOV @R1,#00HINC R1DJNZ R2,LOOPLCALL RINGPI//7LOOP2: MOV R2,#6MOV R1,#30HLCALL DPZP// 开启节能功能JB P1.0,XWJNJB P1.0,$//// 闹钟设置入口ZWJN: JB P1.1,XPP1LCALL RINGPLCALL RELAY////调时入口XPP1: JB P1.3,XPP2LCALL ZPP1XPP2: JB P1.2,ZPPLCALL ZPP2ZPP: AJMP LOOP2////定时器0中断TZP: PUSH 00HPUSH 03HINC R4 // 软件-硬件延时1秒CJNE R4,#40,ENDIMOV R4,#0INC R5CJNE R5,#100,ENDI //结束MOV R5,#0ZP: MOV R0,#30HMOV R3,#3MOV DPTR,#TCOUNTLCALL TTZPLCALL RINGENDI: POP 03HPOP 00HRETI//定时器0中断返回//软中断1ZPP1: MOV A,31HADD A,#1DA AMOV 31H,ACJNE A,#60H,END1MOV 31H,#00HEND1: LCALL RELAYRET////软中断2ZPP2: MOV A,32H9ADD A,#1DA AMOV 32H,ACJNE A,#24H,END2MOV 32H,#00HEND2: LCALL RELAYRET////延时显示程序RELAY: MOV R6,#255REP: MOV R7,#4REEE: MOV R2,#6MOV R1,#30HLCALL DPZPDJNZ R7,REEEDJNZ R6,REPRET//延时显示程序结束//显示子程序DPZP: MOV P0,#0FFH // 显示横杠MOV P2,#0DBHMOV P0,#0BFH // END DPZP1: MOV P0,#0FFHMOV DPTR,#CHART //P3partMOV A,R2MOVC A,@A+DPTRMOV P2,A //MOV DPTR,#LEDMOV A,@R1JNB F0,DPZPSINC R1SWAP ADPZPS: ANL A,#0FHMOVC A,@A+DPTRMOV P0,ACPL F0DJNZ R2,DPZP1RET//显示子程序结束//不规则循环加一子程序TTZP: MOV A,@R0ADD A,#1DA AMOV @R0,AMOV A,R3MOVC A,@A+DPTRCLR CSUBB A,@R011JNC RTTZPMOV @R0,#0INC R0DJNZ R3,TTZP RTTZP: RET// 响铃程序RING: MOV R0,#34HMOV 24H,#6 RRING: MOV A,31HSUBB A,@R0JNZ ERINGINC R0MOV A,32HSUBB A,@R0DEC R0JNZ ERINGCPL P1.7RETERING: MOV A,R0ADD A,#3MOV R0,ADJNZ 24H,RRINGSETB P2.1RET//// 闹钟调整程序RINGP: MOV 20H,#33HMOV 21H,#6MOV R3,#20MOV 22H,#5LPRP: LCALL RELAY1JB P1.1,LPRP1MOV R3,#20MOV A,20HADD A,#3MOV 20H,ADJNZ 22H,LPRPRETLPRP1: JB P1.3,LPRP2MOV R3,#20HMOV A,20HADD A,#1MOV R0,AMOV A,@R0ADD A,#1MOV @R0,ADA ACJNE A,#60H,LPRP21MOV @R0,#00H13LPRP21: LCALL RELAY1 LPRP2: JB P1.2,LPRP3MOV R3,#20HMOV A,20HADD A,#2MOV R0,AMOV A,@R0ADD A,#1DA AMOV @R0,ACJNE A,#24H,LPRP31MOV @R0,#00H LPRP31: LCALL RELAY1 LPRP3: DJNZ R3,LPRP LPRPEND: RET////闹钟组初始化程序(共5组) RINGPI: MOV R2,#5MOV R1,#41H LPRPI: MOV @R1,#00HDEC R1MOV @R1,#00HDEC R1MOV A,#00HORL A,#0A0HADD A,R2MOV @R1,ADEC R1DJNZ R2,LPRPIRET////延时显示程序1RELAY1: MOV R6,#255REP1: MOV R7,#4REEE1: MOV R2,21HMOV R1,20HLCALL DPZPDJNZ R7,REEE1DJNZ R6,REP1RET//延时显示程序结束//数据表LED: DB0c0H,0f9H,0a4H,0b0H,099H,092H,82H,0f8H,80H,90H,8EH,0A8H//0,1,2,3,4,5,6,7,8,9,F,n CHART: DB 0FEH,0FEH,0FDH,0F7H,0EFH,0BFH,7FHTCOUNT: DB 0,23H,59H,59HEND15第四章心得体会4.1心得体会在整个课程设计完后,总的感觉是:有收获。

单片机数字钟实训报告

单片机数字钟实训报告摘要:本实训项目旨在设计并实现一个基于单片机的数字钟。

通过对单片机的学习和应用,我们成功地完成了数字钟的设计与制作。

本报告将从设计目标、硬件电路、软件程序以及实际操作等方面进行详细介绍和分析,以期对读者有所启发和帮助。

一、设计目标数字钟是一款常见而实用的电子设备,它能够精准地显示当前的时间,并具备闹钟和定时器等功能。

我们的设计目标是实现一个简洁、易用且功能齐全的数字钟,具备时钟、闹钟和定时器三种模式,并能够通过按键进行切换和设置。

二、硬件电路我们采用了8051系列单片机作为核心控制器,并搭配数码管、按键和蜂鸣器等外围电路。

其中,数码管用于显示时间和设置参数,按键用于切换模式和设置时间,蜂鸣器用于报警。

通过合理的连接和布局,我们成功地搭建了数字钟的硬件电路。

三、软件程序为了实现数字钟的各项功能,我们根据设计目标编写了相应的软件程序。

程序主要包括时钟模式、闹钟模式和定时器模式的切换与设置,时间的显示和更新等功能。

通过对按键的扫描和状态判断,我们能够根据用户的操作进行相应的响应和处理。

在程序的编写过程中,我们注重代码的可读性和可维护性,使其具备良好的扩展性和稳定性。

四、实际操作在完成硬件电路和软件程序的设计后,我们进行了实际的操作测试。

首先,我们通过按键进行模式的切换和时间的设置,验证了数字钟的基本功能。

其次,我们通过调整定时器的参数,测试了数字钟的定时器功能。

最后,我们设置了闹钟并验证了其报警功能。

实际操作的结果表明,我们的数字钟设计达到了预期的效果,并且具备了稳定可靠的性能。

五、总结与展望通过本次实训项目,我们深入学习了单片机的原理和应用,并成功地设计和制作了一个数字钟。

通过实际操作的过程,我们对数字钟的功能和性能有了更深入的了解。

然而,我们也意识到数字钟仍有一些不足之处,比如显示方式的改进和功能的扩展等。

因此,我们对未来的工作进行了展望,并提出了一些改进的建议,以期进一步完善和优化数字钟的设计。

单片机制作时钟实训报告

随着科技的不断发展,单片机作为一种集计算机技术、微电子技术和自动控制技术于一体的综合性技术,已经在各个领域得到了广泛的应用。

为了提高我们的实践能力和创新意识,我们选择了单片机制作时钟这一实训项目,通过实际操作来深入了解单片机的应用和编程技巧。

二、实训目的1. 熟悉单片机的基本原理和结构。

2. 掌握单片机的编程方法和技巧。

3. 学会使用常用电子元器件,如数码管、按键等。

4. 培养团队合作精神和动手能力。

三、实训内容1. 硬件设计(1)选用MCS-51单片机作为核心控制器;(2)使用8位LED数码管显示时间,包括时、分、秒;(3)设计按键模块,实现时间设置、闹钟设定等功能;(4)设计电源模块,保证系统稳定运行。

2. 软件设计(1)编写时钟计数程序,实现时间的精确计数;(2)编写按键扫描程序,实现时间设置、闹钟设定等功能;(3)编写显示控制程序,实现时间信息的实时显示。

3. 系统调试(1)对硬件电路进行连接和调试,确保电路正常运行;(2)对软件程序进行调试,修正错误,优化性能;(3)进行功能测试,验证系统功能的正确性和稳定性。

1. 需求分析根据实训要求,分析时钟功能,确定硬件和软件设计方案。

2. 硬件选型与电路设计根据需求分析,选择合适的单片机、数码管、按键等元器件,并设计电路图。

3. 软件编程使用C语言编写时钟计数、按键扫描、显示控制等程序。

4. 实物制作与调试按照电路图焊接电路板,组装元器件,进行实物制作。

然后对硬件电路和软件程序进行调试,确保系统正常运行。

5. 功能测试与优化对系统进行功能测试,验证时钟的准确性、按键功能的可靠性、显示的清晰度等。

根据测试结果对系统进行优化,提高性能。

五、实训成果1. 成功制作了一款基于单片机的电子时钟,具有实时显示、时间设置、闹钟设定等功能;2. 掌握了单片机的基本原理和编程方法,提高了实践能力;3. 学会了使用常用电子元器件,为以后的学习和工作打下了基础。

六、实训总结通过本次单片机制作时钟实训,我们深入了解了单片机的应用和编程技巧,提高了实践能力和创新意识。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

51单片机数字钟设计实习报告实用文档目录一.设计方案: (3)二.设计内容: (3)三.相关总线及芯片介绍: (4)1.SPI总线: (4)2.74LS595芯片: (7)3. 实验箱电路图: (10)四.系统软件程序设计: (10)五.设计程序: (13)六.程序调试及显示: (21)七.实习心得: (23)实用文档八.参考文献: (25)一.设计方案:通过单片机内部的计数/定时器,采用软件编程来实现时钟计数,一般称为软时钟,这种方法的硬件线路简单,系统的功能一般与软件设计相关,通常用在对时间精度要求不高的场合。

二.设计内容:这里采用应用广泛的C51作为时钟控制芯片,利用单片机内部实用文档的定时/计数器T0 实现软时钟的目的。

首先将T0设定工作于定时方式,对机器周期计数形成基准时间(50ms),然后用另一个定时/计数器T1对基准时间计数形成秒,秒计60次形成分,分计60形成小时,小时计到12或者24。

通过外部中断实现12进制与24进制的切换。

最后通过数码管把它们的内容在相应的位置显示出来,达到时、分、秒计时的功能。

三.相关总线及芯片介绍:1.SPI总线:SPI(Serial Peripheral Interface--串行外设接口)总线系统是一种同步串行外设接口,它可以使MCU与各种外围设备以串行方式进行通信以交换信息。

外围设置FLASHRAM、网络控制器、LCD显示驱动器、A/D转换器和MCU等。

SPI总线系统可直接与各个厂家生产的多种标准外围器件直接接口,该接口一般使用4条线:串行时钟线(SCK)、主机输入/从机输出数据线MISO、主机输出/从机输入数据线MOSI和低电平有效的从机选择线SS(有的SPI接口芯片带有中断信号线INT或INT、有的SPI接口芯片没有主机输出/从机实用文档输入数据线MOSI)。

由于SPI系统总线一共只需3~4位数据线和控制即可实现与具有SPI总线接口功能的各种I/O器件进行接口,而扩展并行总线则需要8根数据线、8~16位地址线、2~3位控制线,因此,采用SPI总线接口可以简化电路设计,节省很多常规电路中的接口器件和I/O口线,提高设计的可靠性。

由此可见,在MCS51系列等不具有SPI接口的单片机组成的智能仪器和工业测控系统中,当传输速度要求不是太高时,使用SPI总线可以增加应用系统接口器件的种类,提高应用系统的性能。

利用SPI总线可在软件的控制下构成各种系统。

如1个主MCU 和几个从MCU、几个从MCU相互连接构成多主机系统(分布式系统)、1个主MCU和1个或几个从I/O设备所构成的各种系统等。

在大多数应用场合,可使用1个MCU作为控机来控制数据,并向1个或几个从外围器件传送该数据。

从器件只有在主机发命令时才能接收或发送数据。

其数据的传输格式是高位(MSB)在前,低位(LSB)在后。

当一个主控机通过SPI与几种不同的串行I/O芯片相连时,必须使用每片的允许控制端,这可通过MCU的I/O端口输出线来实现。

但应实用文档特别注意这些串行I/O芯片的输入输出特性:首先是输入芯片的串行数据输出是否有三态控制端。

平时未选中芯片时,输出端应处于高阻态。

若没有三态控制端,则应外加三态门。

否则MCU的MISO端只能连接1个输入芯片。

其次是输出芯片的串行数据输入是否有允许控制端。

因此只有在此芯片允许时,SCK脉冲才把串行数据移入该芯片;在禁止时,SCK对芯片无影响。

若没有允许控制端,则应在外围用门电路对SCK进行控制,然后再加到芯片的时钟输入端;当然,也可以只在SPI总线上连接1个芯片,而不再连接其它输入或输出芯片。

对于不带SPI串行总线接口的MCS-51系列单片机来说,可以使用软件来模拟SPI的操作,包括串行时钟、数据输入和数据输出。

对于不同的串行接口外围芯片,它们的时钟时序是不同的。

对于在SCK 的上升沿输入(接收)数据和在下降沿输出(发送)数据的器件,一般应将其串行时钟输出口P1.1的初始状态设置为1,而在允许接收后再置P1.1为0。

这样,MCU在输出1位SCK时钟的同时,将使接口芯片串行左移,从而输出1位数据至MCS-51单片机的P1.3口(模拟MCU的MISO线),此后再置P1.1为1,使MCS-51系列单片机从P1.0(模拟MCU的MOSI线)输出1位数据(先为高位)实用文档至串行接口芯片。

至此,模拟1位数据输入输出便宣告完成。

此后再置P1.1为0,模拟下1位数据的输入输出……,依此循环8次,即可完成1次通过SPI总线传输8位数据的操作。

对于在SCK的下降沿输入数据和上升沿输出数据的器件,则应取串行时钟输出的初始状态为0,即在接口芯片允许时,先置P1.1为1,以便外围接口芯片输出1位数据(MCU接收1位数据),之后再置时钟为0,使外围接口芯片接收1位数据(MCU发送1位数据),从而完成1位数据的传送。

2.74LS595芯片:74595的数据端:QA--QH: 八位并行输出端,可以直接控制数码管的8个段。

QH': 级联输出端。

我将它接下一个595的SI端。

SI: 串行数据输入端。

74595的控制端说明:实用文档/SCLR(10脚): 低点平时将移位寄存器的数据清零。

通常我将它接V cc。

SCK(11脚):上升沿时数据寄存器的数据移位。

QA-->QB-->QC-->... -->QH;下降沿移位寄存器数据不变。

(脉冲宽度:5V时,大于几十纳秒就行了。

我通常都选微秒级)RCK(12脚):上升沿时移位寄存器的数据进入数据存储寄存器,下降沿时存储寄存器数据不变。

通常我将RCK置为低点平,当移位结束后,在RCK端产生一个正脉冲(5V时,大于几十纳秒就行了。

我通常都选微秒级),更新显示数据。

/G(13脚): 高电平时禁止输出(高阻态)。

如果单片机的引脚不紧张,用一个引脚控制它,可以方便地产生闪烁和熄灭效果。

比通过数据端移位控制要省时省力。

注:1)74164和74595功能相仿,都是8位串行输入转并行输出移位寄存器。

74164的驱动电流(25mA)比74595(35mA)的要小,14脚封装,体积也小一些。

实用文档2)74595的主要优点是具有数据存储寄存器,在移位的过程中,输出端的数据可以保持不变。

这在串行速度慢的场合很有用处,数码管没有闪烁感。

3)595是串入并出带有锁存功能移位寄存器,它的使用方法很简单,在正常使用时SCLR为高电平,G为低电平。

从SER每输入一位数据,串行输595是串入并出带有锁存功能移位寄存器,它的使用方法很简单,如下面的真值表,在正常使用时SCLR为高电平,G为低电平。

从SER每输入一位数据,串行输入时钟SCK上升沿有效一次,直到八位数据输入完毕,输出时钟上升沿有效一次,此时,输入的数据就被送到了输出端。

入时钟SCK上升沿有效一次,直到八位数据输入完毕,输出时钟上升沿有效一次,此时,输入的数据就被送到了输出端。

实用文档3.实验箱电路图:图1.实验箱电路四.系统软件程序设计:1.主程序:先对显示单元和定时器/计数器初始化,然后重复调用数码管显示模块和中断处理模块,当有外部中断按下时,则转入相应的功能程序。

2.数码管显示模块:实用文档本实验有8个数码管,从右到左为时、横线、分、横线、秒。

在本系统中数码管显示利用SPI总线进行传输显示。

3.定时器/计数器T0中断服务程序:T0用于计时,选中方式一,重复定时,定时时间设为50ms,定时时间到则中断,在中断服务程序中用一个计数器对50ms计数,计20次则对秒单元加一。

秒单元加到60则对分单元加一,同时秒单元清0;分单元加到60则对时单元加一,同时分单元清0;时单元加到12则对时单元清0,标志一天时间计满。

在对各单元计数的同时,把他们的值放到存储器单元的指定位置。

4.外部中断服务程序:对小时进行12进制与24进制切换。

5.流程图如下:实用文档图2. 主程序 图3.中断处理程序1图4.数据显示模块图5.外部中断处理程序五.设计程序:ENA EQU P2.0实用文档ENB EQU P2.1ENC EQU P2.2CLK EQU P1.0DIN EQU P1.1COUNT EQU 0FHCISHU EQU 2EHORG 0000HAJMP MAINORG 0003HAJMP INT0ORG 000BHAJMP I0MAIN: MOV COUNT,#0MOV CISHU,#12CALL L2WAIT: LCALL INLCALL XIANSHI实用文档SJMP WAITL2: MOV R3,#0AHMOV R4,#55MOV R5,#59MOV R6,#11MOV TMOD,#11HMOV TH0,#03CHMOV TL0,#0B0HSETB IT0SETB EX0SETB ET0SETB EASETB TR0RETIN:MOV A,R6MOV B,#0AH实用文档DIV ABMOV DPTR,#TABMOVC A,@A+DPTRMOV 6FH,AMOV A,BMOV DPTR,#TABMOVC A,@A+DPTRMOV 6EH,AMOV A,#0BFHMOV 70H,AMOV A,R5MOV B,#0AHDIV ABMOV DPTR,#TABMOVC A,@A+DPTRMOV 72H,AMOV A,B实用文档MOV DPTR,#TABMOVC A,@A+DPTRMOV 71H,AMOV A,#0BFHMOV 73H,AMOV A,R4MOV B,#0AHDIV ABMOV DPTR,#TABMOVC A,@A+DPTRMOV 75H,AMOV A,BMOV DPTR,#TABMOVC A,@A+DPTRMOV 74H,ARETXIANSHI:实用文档CLR ENASETB ENBSETB ENCMOV R1,6EHLOOP3:MOV A,@R1MOV R0,#08HLOOP2:LCALL LOOPINC R1CJNE R1,#76H,LOOP3SETB ENARETI0: DJNZ R3,LOOP1MOV R3,#14HINC R4CJNE R4,#60,LOOP1实用文档MOV R4,#0INC R5CJNE R5,#60,LOOP1INC R6MOV R5,#0MOV A,R6CJNE A,CISHU,LOOP1MOV R6,#0LOOP1:MOV TH0,#03CHMOV TL0,#0B0HSETB TR0RETILOOP: RLC AMOV DIN,CNOPNOP实用文档SETB CLKNOPNOPCLR CLKDJNZ R0,LOOPRETINT0:INC COUNTMOV A,COUNTMOV B,#2DIV ABMOV A,BCJNE A,#0,L3L1: MOV CISHU,#12RETIL3: MOV CISHU,#24RETI实用文档TAB:DB 0C0H,0F9H,0A4H,0B0H,99H,92H,82H,0F8H,80H,90H END六.程序调试及显示:1.输入源程序输入源程序时,应以西文方式输入字母和符号,且中文注释前要加分号。