(完整word版)1.测试1位全加器的仿真

实验一 1位全加器电路设计知识分享

实验一1位全加器电路设计实验一 1位全加器电路的设计一、实验目的1、学会利用Quartus Ⅱ软件的原理图输入方法设计简单的逻辑电路;2、熟悉利用Quartus Ⅱ软件对设计电路进行仿真的方法;3、理解层次化的设计方法。

二、实验内容1、用原理图输入方法设计完成一个半加器电路。

并进行编译与仿真。

2、设计一个由半加器构成1位全加器的原理图电路,并进行编译与仿真。

3、设计一个由1位全加器构成4位加法器的原理图电路,并进行编译与仿真。

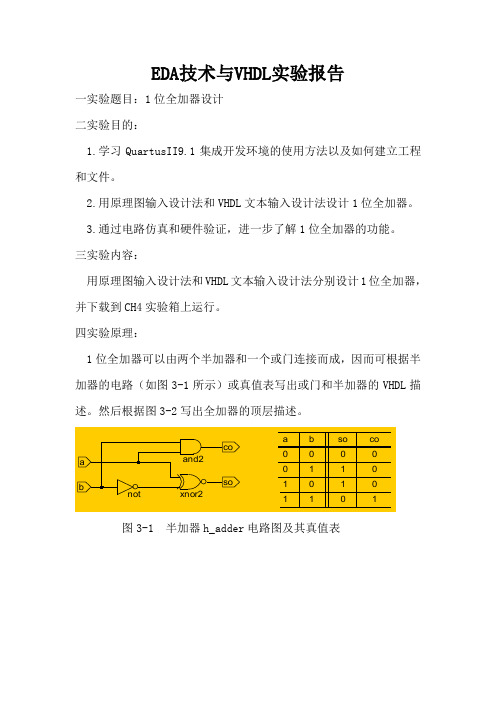

三、实验步骤1. 使用Quartus建立工程项目从【开始】>>【程序】>>【ALtera】>>【QuartusII6.0】打开Quartus软件,界面如图1-1示。

仅供学习与交流,如有侵权请联系网站删除谢谢2图1-1 Quartus软件界面在图1-1中从【File】>>【New Project Wizard...】新建工程项目,出现新建项目向导New Project Wizard 对话框如图1-2所示。

该对话框说明新建工程应该完成的工作。

在图1-2中点击NEXT进入新建项目目录、项目名称和顶层实体对话框,如图1-3 所示,顶层实体名与项目名可以不同,也可以不同。

输入项目目录如E:\0512301\ first、工程项目名称和顶层实体名同为fadder。

仅供学习与交流,如有侵权请联系网站删除谢谢3图1-2 新建工程向导说明对话框图1-3 新建工程目录、项目名、顶层实体名对话框仅供学习与交流,如有侵权请联系网站删除谢谢4接着点击NEXT进入新建添加文件对话框如图1-4所示。

这里是新建工程,暂无输入文件,直接点击NEXT进入器件选择对话框如图1-5所示。

这里选择Cyclone系列的EP1C6Q240C8。

图1-4 新建添加文件对话框仅供学习与交流,如有侵权请联系网站删除谢谢5图1-5器件选择对话框点击NEXT进入添加第三方EDA开发工具对话框如图1-6所示。

实验五1位全加器的文本输入(波形仿真应用)

实验五 1位全加器的文本输入(波形仿真用)1.实验目的通过此实验让学生逐步了解、熟悉和掌握FPGA开发软件Quartus II的使用方法及VHDL 的编程方法。

学习电路的仿真方法。

2.实验内容本实验的内容是建立一个1位全加器。

在实验箱上的按键KEY1~KEY3分别为A、B 和Cin,并通过LED1~LED3指示相应的状态。

输出Sum和Cout通过LED7和LED8指示。

3.实验原理1位全加器的真值表如下所示。

表1位全加器逻辑功能真值表4.实验步骤(1) 启动Quartus II,建立一个空白工程,然后命名为full_add.qpf。

(2) 新建full_add.vhd源程序文件,编写代码。

然后进行综合编译。

若在编译过程中发现错误,则找出并更正错误,直到编译成功为止。

也可采用原理图文件的输入方式,建立半加器,然后在组成1位全加器。

原理图如下所示半加器设计1位全加器设计(3) 波形仿真步骤如下:① 在Quartus II 主界面中选择File → New 命名,打开新建文件对话框,从中选择V ector Waveform File ,如下图所示。

单击OK 建立一个空的波形编辑窗口。

选择File →Saveas 改名为full_add.vwf。

此时会看到窗口内出现如下图所示。

图 新建文件对话框 图 新建波形文件界面② 在上图所示的Name 选项卡内双击鼠标左键,弹出如图 所示的对话框。

在该对话框中单击Node Finder 按钮,弹出如图 所示的对话框。

图 添加节点对话框③ 按照下图所示进行选择和设置,先按下“list ”按钮,再按下“>>”按钮添加所有节点,最后按下“ok ”按钮。

图添加节点④波形编辑器默认的仿真结束时间为1us,根据仿真需要可以设置仿真文件的结束时间。

选择Edit→ End Time命令可以更改。

这里采用默认值不需更改。

图添加完节点的波形图⑤编辑输入节点的波形。

编辑时将使用到波形编辑工具栏中的各种工具。

实验一 1位全加器的设计(修改后)

• 步骤三:编辑全加器的原理图: 步骤三:编辑全加器的原理图:

• 由file->new,打开原理图文件Block Diaoram/Schematic File,并存盘为full_adder.bdf

左键双击原理图编辑窗空白处,弹出如下窗口

• 调入 1)半加器:half_adder, 2)二输入或门:2or, 3)输入,输出引脚

实验一 1位全加器的设计 位全加器的设计

一位全加器的原理分析

• 一位全加器可由两个一位半加器与一个或 门构成,其原理图如下图。

该设计利用层次结构描述法, • 首先设计半加器电路,将其打包为半加器 模块; • 然后在顶层调用半加器模块 半加器模块和ALTERA提供 半加器模块 的二输入或门 输入或门组成全加器电路; 输入或门 • 最后将全加器电路编译下载到实验箱,

输入是 两个加数:ain,bin, 一个进位:cin 这三个输入数据是1位(1bit),可由DE2的 SW0,SW1,SW2提供 为了显示更加清楚,可以将ain,bin,cin的输出引 出到DE2上的红色发光二极管显示,可选用 LEDR0,LEDR1,LEDR2. 输出是: 输出是: 和:sum 进位:cout 输出可由DE2的绿色发光二极管显示,可选用 LEDG0,LEDG1

• 步骤一:建立full_adder的工程 (project)

新建立full_adder工程(project)

设置project相关参数

• 设置project放置的位置及其名称,随后按 Next继续

• 添加文件到工程(project)中,在无相关文件需要 添加的情况下,按Next继续

• 选择FPGA目标器件,根据DE2的平台情况,选 择cyclone II系列的EP2C35F672C6,继续

1.测试1位全加器的仿真

可编程逻辑器件设计实验报告实验名称: 测试1位全加器的仿真 实验目的: 使用modelsim 编写test bench 代码实现测试1位全加器的仿真,并得到输出波形实验时间: 年 月 日 地点:实验室学生姓名: 学号:实验名称: 测试1位全加器的仿真1、 实验步骤1. 创建工程文件,并命名为full_adder_test 。

2. 将已存在的full_adder 的verilog HDL File 添加到工程文件中,并创建modelsim 仿真文件,命名为full_adder_tb 。

3. 在modelsim 仿真文件中输入代码,并编译。

2、 VerilogHDL 代码module full_adder_1(ina,inb,ci,co,sum);input ina,inb,ci;output co,sum;assign {co,sum}=ina+inb+ci;endmodule3、Test bench 仿真代码:`timescale 1ns/1nsmodule full_adder_tb;reg a,b,c;wire co,sum;integer i,j;parameter delay=100;装订 线full_adder_1 U1(a,b,c,co,sum);initialbegina=0;b=0;c=0;for(i=0;i<2;i=i+1)for(j=0;j<2;j=j+1)begina=i;b=j;c=0;#delay;endfor(i=0;i<2;i=i+1)for(j=0;j<2;j=j+1)begina=i;b=j;c=1;#delay;endendendmodule4、RTL视图5、仿真结果。

一位全加器实验报告

实验题目

实验报告正文一律使用A4打印纸打印或手写,页眉上标明“《XXXX》课程实验”字样。

页面设置上边距2.5cm,下边距2 cm,右边距2 cm(左装订),多倍行距1.25倍。

正文用宋体5号字,页眉和页脚同宋体小5号字并居中。

1、实验内容

用MAX+plus II 10.1设计一位全加器

2、实验目的与要求

设计一位全加器,并且熟悉MAX+plus II 10.1使用环境。

3、实验环境

MAX+plus II 10.1

4、设计思路分析(包括需求分析、整体设计思路、概要设计)

用两个半加器和一个或门,设计一位全加器。

5、详细设计

一位全加器可以用两个半加器和一个或门连接而成,半加器由一个与门,一个非门,同或门来实现。

在MAX+plus II 10.1环境操作步骤如下:

1、半加器的设计

2、全加器的设计

3、分配管脚

4、编译

5、仿真

6、下载

7、观察结果

6、实验结果与分析

半加器原理图

半加器波形图

全加器原理图

全加器波形图

7、实验体会与建议

通过这次实验课的学习,我学会了MAX+plus 的使用。

了解了半加器和全加器的设计原理和在MAX+plus中的实现方法。

在操作过程中虽然遇到了很多的困难,但在同学的帮助下都克服了。

同学的帮助在学习的过程中是很重要的。

实验一1 1位全加器的设计

实验一1位全加器的设计一、实验目的1.熟悉ISE软件的使用;2.熟悉下载平台的使用;3.掌握利用层次结构描述法设计电路。

二、实验原理及说明由数字电路知识可知,一位全加器可由两个一位半加器与一个或门构成,其原理图如图1所示。

该设计利用层次结构描述法,首先设计半加器电路,将其打包为半加器模块;然后在顶层调用半加器模块组成全加器电路;最后将全加器电路编译下载到实验板,其中a,b,cin 信号可采用实验箱上SW0,SW1,SW2键作为输入,输出sum,cout信号采用发光二极管LED3,LED2来显示。

图1 全加器原理图三、实验步骤1.在ISE软件下创建一工程,工程名为full_adder,工程路径在E盘,或DATA盘,并以学号为文件夹,注意不要有中文路径,注意:不可将工程放到默认的软件安装目录中。

芯片名为Spartan3E系列的XC3S500E-PQG2082.新建Verilog HDL文件,首先设计半加器,输入如下源程序;module half_adder(a,b,s,co);input a,b;output s,co;wire s,co;assign co=a & b;assign s=a ^ b;endmodule3.保存半加器程序为half_adder.v,通过HDL Bench画仿真波形,获得仿真用激励文件,随后进行功能仿真、时序仿真,验证设计的正确性,观察两种仿真波形的差异。

4.在Design窗口中,选择Design Utilities→Create Schematic Symbol创建半加器模块;5.新建一原理图(Schematic)文件,在原理图中调用两个半加器模块、一个或门模块,按照图1所示连接电路,并连接输入、输出引脚。

完成后另保存full_adder.sch。

6.对设计进行综合,如出现错误请按照错误提示进行修改。

7.HDL Bench画仿真波形,获得仿真用激励文件,分别进行功能与时序仿真,验证全加器的逻辑功能,观察两类波形的差异。

实验一1位二进制全加器的设计

实验一1位二进制全加器的设计(共6页)--本页仅作为文档封面,使用时请直接删除即可----内页可以根据需求调整合适字体及大小--龙岩学院实验报告班级学号姓名同组人实验日期室温大气压成绩实验题目:基于原理图输入法的1位二进制全加器的设计一、实验目的1、学习、掌握QuartusⅡ开发平台的基本使用。

2、学习基于原理图输入设计法设计数字电路的方法,能用原理图输入设计法设计1位二进制半加器、1位二进制全加器。

3、学习EDA-V型实验系统的基本使用方法。

二、实验仪器装有QuartusⅡ软件的计算机一台、EDA系统实验箱、导线若干三、实验原理半加器只考虑两个1位二进制数相加,而不考虑低位进位数相加。

半加器的逻辑函数为式中A和B是两个相加的二进制数,S是半加和,C是向高位的进位数。

表1为半加器真值表。

表1A B C S0000010110011110显然,异或门具有半加器求和的功能,与门具有进位功能。

其逻辑图跟逻辑符号如下图:全加器除了两个1位二进制数相加以外,还与低位向本位的进位数相加。

表2为全加器的真值表。

表2A iB iC I-1C i S0000000101010010111010001101101101011111由真值表可得出逻辑函数式式中,A i和B i是两个相加的1为二进制数,C i-1是由相邻低位送来的进位数,S I是本位的全加和,C I是向相邻高位送出的进位数。

其逻辑图跟逻辑符号如下图所示:四、实验内容1、根据1位二进制半加器、1位二进制全加器的真值表,设计并画出1位二进制半加器的原理框图,由半加器及门电路设计并画出1位二进制全加器的原理框图(最终设计的是1位二进制全加器)。

2、用QuartusⅡ原理图输入输入法输入1位二进制半加器的原理框图,并进行编译。

如有输入错误,修改后再进行编译。

4、根据1位二进制半加器的工作原理,选择输入合适的输入信号和波形及其输出信号,进行仿真,得到器件的输入与输出波形,验证设计是否正确。

一位全加器(1)

u3:or2a PORTMAP(a=>d,b=>f,c=>cout);

END ARCHITECTURE fd1;

引脚分配:

端口名

端口模式

引脚

ain

Input

Pin_66

bin

Input

Pin_64

cin

Input

END ENTITYh_adder;

ARCHITECTURE fht;=NOT(a XOR(NOT b));

co<=a AND b;

END ARCHITECTURE fh1;

(2)或门逻辑描述:

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

Pin_62

cout

Out

Pin_51

sum

Out

Pin_52

五实验过程:

半加器的VHDL描述

或门的VHDL描述

1位二进制全加器顶层VHDL描述

引脚设定

六实验结果:

输出波形图

3.通过电路仿真和硬件验证,进一步了解1位全加器的功能。

三实验内容:

用原理图输入设计法和VHDL文本输入设计法分别设计1位全加器,并下载到CH4实验箱上运行。

四实验原理:

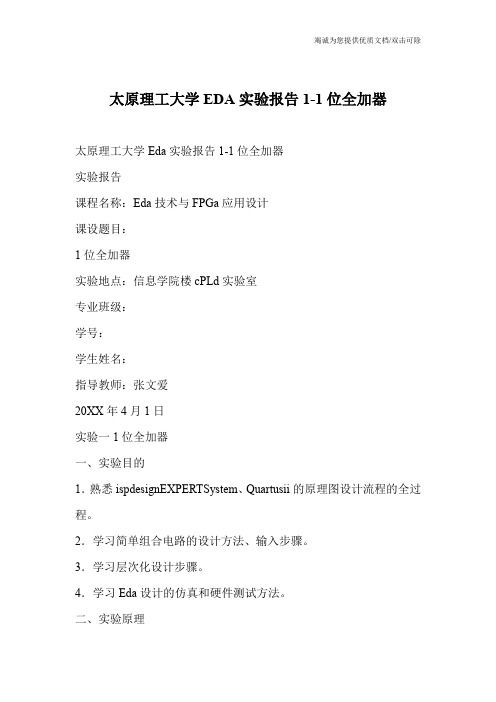

1位全加器可以由两个半加器和一个或门连接而成,因而可根据半加器的电路(如图3-1所示)或真值表写出或门和半加器的VHDL描述。然后根据图3-2写出全加器的顶层描述。

图3-1 半加器h_adder电路图及其真值表

图3-2 全加器f_adder电路图及其实体模块

EDA之1位全加器

EDA技术实验教案实验一1位全加器原理图输入设计一、实验目的1、熟悉MAX+plusII软件的基本使用方法。

2、熟悉GW48-ES EDA实验开发系统的基本使用方法。

3、了解原理图输入设计方法。

二、实验内容设计并调试好一个1位二进制全加器,并用GW48-ES EDA实验开发系统(拟采用的实验芯片的型号为EPF10K20TC144-4或EP1K30TC144-3)进行系统仿真、硬件验证。

设计1位二进制全加器时要求先用基本门电路设计一个1位二进制半加器,再由基本门电路和1位二进制半加器构成1位二进制全加器。

三、实验条件1、开发条件:MAX+plusII2、实验设备:GW48-ES EDA实验开发系统、联想电脑3、拟用芯片:EPF10K20TC144-4或EP1K30TC144-3四、实验设计半加器(h_adder.gdf)全加器(f_adder.gdf)实验结果半加器仿真波形半加器引脚锁定实验芯片:EPF10K20TC144-4选用模式:模式5设计实体I/O标识I/O来源/去向结构图上的信号名芯片引脚号a 键1 PIO0 8b 键2 PIO1 9so 二极管D1 PIO8 20co 二极管D2 PIO9 21 全加器仿真波形全加器引脚锁定实验芯片:EPF10K20TC144-4选用模式:模式5设计实体I/O标识I/O来源/去向结构图上的信号名芯片引脚号ain 键1 PIO0 8bin 键2 PIO1 9cin 键3 PIO2 10sum 二极管D1 PIO8 20cout 二极管D2 PIO9 21全加器真值表ain 0 1 0 1 0 1 0 1 bin 0 0 1 1 0 0 1 1 cin 0 0 0 0 1 1 1 1 sum 0 1 1 0 1 0 0 1 cout 0 0 0 1 0 1 1 1实验二1位全加器VHDL文本输入设计一、实验目的1、熟悉MAX+plusII软件的基本使用方法。

太原理工大学EDA实验报告1-1位全加器

太原理工大学EDA实验报告1-1位全加器

太原理工大学Eda实验报告1-1位全加器

实验报告

课程名称:Eda技术与FPGa应用设计

课设题目:

1位全加器

实验地点:信息学院楼cPLd实验室

专业班级:

学号:

学生姓名:

指导教师:张文爱

20XX年4月1日

实验一1位全加器

一、实验目的

1.熟悉ispdesignEXPERTSystem、Quartusii的原理图设计流程的全过程。

2.学习简单组合电路的设计方法、输入步骤。

3.学习层次化设计步骤。

4.学习Eda设计的仿真和硬件测试方法。

二、实验原理

1.位全加器可以用两个半加器及一个或门连接而成。

图1.半加器原理图

图2.全加器原理图

三、实验任务

1.用原理图输入方法设计半加器电路。

2.建立顶层原理图电路。

3.对全加器电路进行引脚锁定、硬件测试。

四、实验内容

1.用原理图输入方法设计半加器电路

图3.半加器电路图

2.半加器经封装后作为一个元件为全加器电路使用,调用半加器设计全加器:

图4.全加器电路图

五、实验结果

六、实验感想

通过本次试验我熟悉了ispdesignEXPERTSystem、Quartusii的原理图设计流程的全过程。

学习了简单组合电路的设计方法、输入步骤以及Eda设计的仿真和硬件测试方法。

学会了使用FPGa设计的顶层设计的简单实验,通过设计半加器完成全加器的设计。

对所学的知识得到很好的实践和检验。

()。

数字电路实验报告-组合逻辑电路的设计:一位全加器

Si

Ci

0

0

0

0

0

0

0

1

1

0

0

1

0

1

0

0

1

1

0

1

1

0

0

1

0

1

0

1

0

1

1

1

0

0

1

1

1

1

1

1

描述

一位全加器的表达式如下:

Si=Ai⊕Bi⊕Ci-1

实验仪器

1.电子技术综合实验箱

2.芯片74LS86、74LS08、74LS32

实验内容及步骤

各芯片的管脚图如下图所示:

一位全加器逻辑电路图如下所示:

1.按上图连线

电学实验报告模板

电学虚拟仿真实验室

实验名称

组合逻辑电路的设计:一位全加器

实验目的

1.学习组合逻辑电路的设计方法

2.掌握组合逻辑电路的调试方法

实验原理

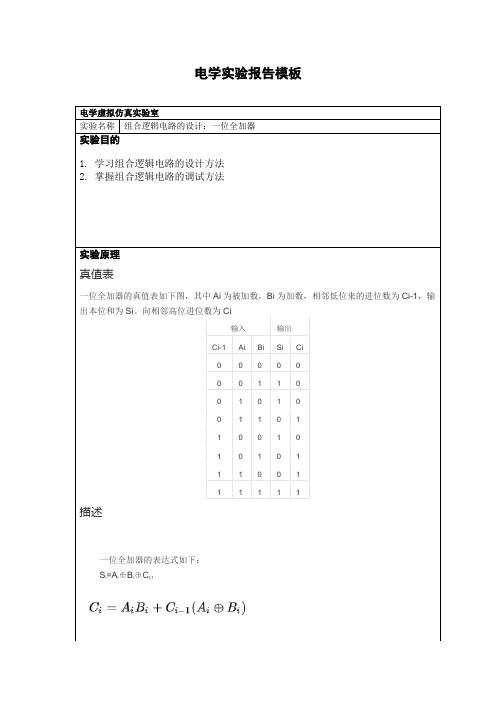

真值表

一位全加器的真值表如下图,其中Ai为被加数,Bi为加数,相邻低位来的进位数为Ci-1,输出本位和为Si。向相邻高位进位数为Ci

输入

输出

Ci-1

Ai

2.测试其逻辑功能,并记录数据

实验结果及分析

实验数据:

Ci-1

Ai

Bi

Si

Ci

0

0

0

0

0

0

0

1

1

0

0

1

0

1

0

0

1

1

0

1

10010 Nhomakorabea1

0

1

0

1

实验一 1位全加器电路设计

实验一 1位全加器电路的设计一、实验目的1、学会利用Quartus Ⅱ软件的原理图输入方法设计简单的逻辑电路;2、熟悉利用Quartus Ⅱ软件对设计电路进行仿真的方法;3、理解层次化的设计方法。

二、实验内容1、用原理图输入方法设计完成一个半加器电路。

并进行编译与仿真。

2、设计一个由半加器构成1位全加器的原理图电路,并进行编译与仿真。

3、设计一个由1位全加器构成4位加法器的原理图电路,并进行编译与仿真。

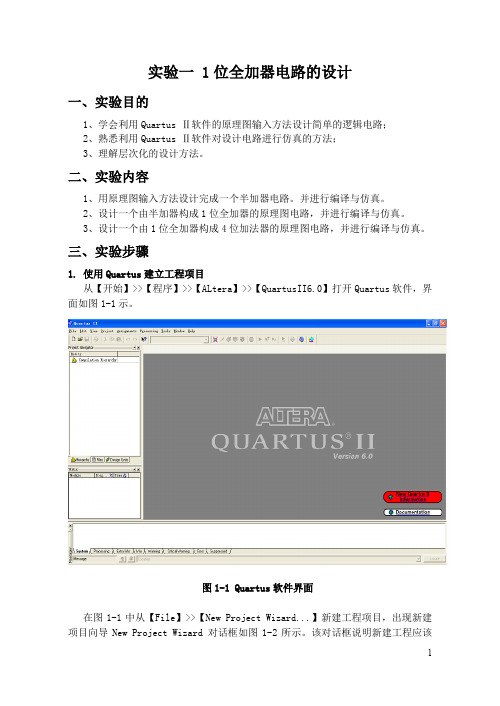

三、实验步骤1. 使用Quartus建立工程项目从【开始】>>【程序】>>【ALtera】>>【QuartusII6.0】打开Quartus软件,界面如图1-1示。

图1-1 Quartus软件界面在图1-1中从【File】>>【New Project Wizard...】新建工程项目,出现新建项目向导New Project Wizard 对话框如图1-2所示。

该对话框说明新建工程应该完成的工作。

在图1-2中点击进入新建项目目录、项目名称和顶层实体对话框,如图1-3 所示,顶层实体名与项目名可以不同,也可以不同。

输入项目目录如E:\0512301\ first、工程项目名称和顶层实体名同为fadder。

图1-2 新建工程向导说明对话框图1-3 新建工程目录、项目名、顶层实体名对话框接着点击进入新建添加文件对话框如图1-4所示。

这里是新建工程,暂无输入文件,直接点击进入器件选择对话框如图1-5所示。

这里选择Cyclone 系列的EP1C6Q240C8。

图1-4 新建添加文件对话框图1-5器件选择对话框点击进入添加第三方EDA开发工具对话框如图1-6所示。

图1-6 添加第三方EDA开发工具对话框本实验只利用Quartus集成环境开发,不使用其它EDA开发工具,进入工程信息报告对话框如图1-7所示。

点击完成新建工程项目的建立如图1-8示。

图1-7工程信息报告对话框图1-8工程项目建立完成界面2、新建半加器原理图文件在图1-8中从【File】>>【New.】打开新建文件对话框如图1-9所示。

电工一位全加器实验报告

课程名称:1504010320

实验项目:一位全加器实验

姓名:吴雅惠

专业:计算机科学与技术

班级: 3

学号:1504010320

计算机科学与技术学院

实验教学中心

2016 年 4 月26 日

一、实验内容:①设计一个二进制具有低位进位的一位加法器(全加器)。

②利用Multisim10软件,对一位全加器电路进行逻辑仿真。

二、实验材料:。

计算机、 Multisim10仿真软件。

三、实验步骤:⑴在U盘上建一个文件夹:数字电路与逻辑。

⑵打开Multisim10软件,点击文件→新建→原理图。

⑶点击文件→另存为,选择U盘→数字电路与逻辑文件夹,文件名→全加器。

⑷点击主菜单中的元器件,放入所需元件、仪表并连线,调整参数进行仿真。

实验提示:

(1)点击“放置信号源”按钮,POWER_SOURCES中可选信号源、电源、地线。

(2)点击“放置基础元件”按钮,可放置变压器、电阻、电解电容、电容、开关。

(3)点击“放置二极管”按钮,可放置整流二极管、稳压二极管、整流桥。

(4)点击“放置杂项元件”按钮,可放置整流桥、保险管。

(4)点击“放置数字元件”按钮,可放置与门、或门、异或门、非门等。

(4)点击“放置显示元件”按钮,可放置逻辑测试指示器、指示灯泡。

(5)调整元件;点击元件→点击右键→替换元件;调整元件方向;Ctrl+R

四、实验结果(要求抓图)。

实验一 1位全加器

实验一1位全加器一、实验目的1.掌握QuartusⅡ设计的基本流程;2.熟悉QuartusⅡ编译、仿真;3.掌握QuartusII的引脚分配和下载验证。

二、实验内容1.利用QuartusⅡ完成Verilog HDL文本输入和编译等步骤;2.设置合适的参数,进行功能仿真和时序仿真;3.对引脚进行配置并下载到FPGA芯片中验证全加器的功能。

三、实验步骤1.创建工程1)在D盘中新建文件夹,取名为full_adder,路径为D:\full_adder。

注意:●文件夹名字不能用中文,也不能包含空格,建议用英文、数字和下划线,最好以英文字母开头,长度在8个字符以内。

●工程文件夹不要设在计算机已有的安装目录中,也不要建立在“桌面”上,更不要将其直接放在安装目录中。

●不同的设计项目最好放在不同的文件夹中,而同一工程的所有文件都必须放在同一文件夹中。

2)利用向导创建项目芯片选择Cyclone III中的EP3C40Q240C8。

2.输入Verilog HDL文件注意:文件名和模块名要一致3.编译设计文件选择菜单Processing—Start Compilation或单击启动完全编译。

4.仿真1)建立波形文件选择菜单File—New,在New窗口中选择Vector Waveform File选项,单击OK,出现波形编辑窗口。

2)输入信号节点选择菜单Edit—Insert Node or Bus—Node Finder,在Filter框中选择Pin:all,再单击List按钮,可在Nodes Founder对话框中将所需节点添加进去。

3)设置波形参量选择菜单Edit—End time在弹出的窗口中设置仿真结束时间(通常为50us)4)编辑输入信号使用波形编辑器窗口中的赋值快捷键编辑激励波形。

5)保存波形文件6)运行仿真器1)功能仿真在“Assignments”菜单中选择“Setting...”,选择“Simulator Settings”,在“Simulation mode”(仿真模式)列表中选择“Functional”,单击“OK”按钮即可进行功能仿真。

EDA技术与FPGA应用设计实验报告--1位全加器的设计(可编辑修改word版)

本科实验报告

课程名称:EDA 技术与FPGA 应用设计实验项目: 1 位全加器的设计

实验地点:跨越机房

专业班级:学号:

学生姓名:

指导教师:

2012 年6 月20 日

一、实验目的:

1.熟悉 ispDesignEXPERT System 原理图设计流程的全过程。

2.学习简单组合电路的设计方法、输入步骤。

3.学习层次化设计步骤。

4.学习 EDA 设计的仿真和硬件测试方法。

二、实验原理:

1.位全加器可以用两个半加器及一个或门连接而成。

三、实验任务:

1.用原理图输入方法设计半加器电路。

2.建立顶层原理图电路。

3.对全加器电路进行仿真分析、引脚锁定、硬件测试。

四、实验内容:

1.用原理图输入方法设计半加器电路

2.调用半加器设计全加器:

五、仿真波形:

六、加法器的延时情况:

七、心得体会:

通过本实验让我对原理图方法设计有了一定的认识,让我初步掌握了 ispDesignEXPERT System 软件,在构建原理图时,我们可以使用巧妙的办法搭建出最简便的原理图,初次实验,有些生疏,不过还是很完美的做完了实验,希望今后能有更多的机会去实践,去巩固,去提高。

武大电气数电仿真实验报告

数电仿真实验报告一、实验目的1. 掌握Quartus II 8.0软件使用流程。

2. 初步掌握Verilog 的编程方法。

二、 实验原理1sum a b C ∧∧=&|(^b)&C1Ch a b a =三、实验内容 1.编程代码如下:module fulladder(a,b,cl,ch,sum); input a,b,cl; output ch,sum; reg ch,sum;always@(a or b or cl) beginsum=a^b^cl;ch=a&b|(a^b)&cl; end endmodule2.时序仿真图一、实验目的1.掌握图形层次设计方法;2.熟悉Quartus II 8.0软件的使用及设计流程;3.掌握全加器原理,能进行多位加法器的设计。

二、实验原理加法器是数字系统中的基本逻辑器件。

例如:为了节省资源,减法器和硬件乘法器都可由加法器来构成。

但位宽加法器的设计是很消耗资源的,因此实际的设计和相关系统的开发中需要注意资源的利用率和进位速度等两方面的问题。

多位加法器的构成有两种方式:并行进位和串行进位方式。

并行进位加法器设有并行进位产生逻辑,运行速度快;串行进位方式是将全加器级联构成多位加法器。

通常,并行加法器比串行加法器占用更多的资源,并且随着位数的增加,相同位数的并行加法器比串行加法器的资源占用差距也会越来越大。

四位加法器可以采用四个一位全加器级联成串行进位加法器。

无法胜任高速运算。

三、实验内容1.程序代码module full4adder(A,B,Cin,Sum,Cout);input [3:0]A,B;input Cin;output [3:0]Sum;output Cout;assign{Cout,Sum}=A+B+Cin;endmodule2.时序仿真图实验三三输入与门、三输入或门一、实验目的1.理解简单组合电路的设计方法。

2.掌握基本门电路的应用。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

可编程逻辑器件设计实验报告

实验名称: 测试1位全加器的仿真 实验目的: 使用modelsim 编写test bench 代码实现测试1位全加器的仿真,并得到

输出波形 实验时间: 年 月 日 地点:实验室 学生姓名: 学号:

实验名称: 测试1位全加器的仿真

1、 实验步骤

1. 创建工程文件,并命名为full_adder_test 。

2. 将已存在的full_adder 的verilog HDL File 添加到工程文件中,并创建modelsim 仿真文件,命名为full_adder_tb 。

3. 在modelsim 仿真文件中输入代码,并编译。

2、 VerilogHDL 代码

module full_adder_1(ina,inb,ci,co,sum);

input ina,inb,ci;

output co,sum;

assign {co,sum}=ina+inb+ci;

endmodule

3、Test bench 仿真代码:

`timescale 1ns/1ns

module full_adder_tb;

reg a,b,c;

wire co,sum;

integer i,j; parameter delay=100;

装

订 线

full_adder_1 U1(a,b,c,co,sum);

initial

begin

a=0;b=0;c=0;

for(i=0;i<2;i=i+1)

for(j=0;j<2;j=j+1)

begin

a=i;b=j;c=0;

#delay;

end

for(i=0;i<2;i=i+1)

for(j=0;j<2;j=j+1)

begin

a=i;b=j;c=1;

#delay;

end

end

endmodule

4、RTL视图

5、仿真结果。