APU并行编程

如何利用超级计算技术进行高效的并行编程

如何利用超级计算技术进行高效的并行编程随着科技的快速发展,超级计算机已经成为解决复杂问题的重要工具。

并行编程技术的应用使得超级计算机能够更高效地处理大规模计算任务。

本文将介绍如何利用超级计算技术进行高效的并行编程,以优化计算性能。

首先,了解并行计算的基本概念是非常重要的。

并行编程是指将一个大型任务分解成多个小的子任务,并通过同时执行这些小任务来加快整体计算速度。

在超级计算机中,每个任务可以在多个处理器核心上同时执行,以实现更快的计算速度。

因此,了解如何划分任务、将任务分配给核心和协调任务之间的通信是必不可少的。

其次,选择合适的并行编程模型对于高效的并行编程至关重要。

目前,最常用的并行编程模型包括消息传递接口(MPI)和共享内存模型(OpenMP)。

MPI适用于分布式内存计算机集群,它通过通信传递消息来实现不同处理器核心之间的数据交换。

OpenMP则适用于共享内存系统,它允许多个线程共享同一个内存空间。

选择适合你的计算环境的并行编程模型是非常重要的,以确保最佳的计算性能。

在编写并行程序时,合理地划分任务是至关重要的。

任务划分策略的好坏直接影响着并行程序的性能。

一般来说,任务应该被划分为相互独立且工作量均衡的子任务。

这样可以避免一些核心空闲等待其他任务完成并提高计算效率。

可以通过任务图、负载均衡算法或启发式算法来分析和划分任务。

另外,高效的任务调度和通信机制对于并行编程也是至关重要的。

任务调度的目标是使得多个任务分配给不同的核心,以减少任务等待的时间和提高计算效率。

常见的任务调度算法有贪心算法、动态调度算法等。

此外,合理地设置通信机制,避免通信频繁和通信量过大是保证高效并行编程的关键。

可以使用非阻塞通信和集合通信等技术来优化通信效率。

与并行编程相关的性能调优也是提高计算效率的重要步骤。

性能调优可以在代码层面、算法层面和系统层面进行。

在代码层面,可以通过优化数据结构和算法、减少数据依赖等方式来提高计算效率。

掌握并行编程充分利用多核处理器

掌握并行编程充分利用多核处理器随着科技的不断发展和进步,计算机的处理能力也在不断提高。

单核处理器已经不能满足人们对计算性能的需求,多核处理器成为现在计算机的主流选择。

然而,要充分利用多核处理器的强大计算能力,我们就需要掌握并行编程。

一、多核处理器的优势多核处理器具有以下优势:1. 提高计算性能:多核处理器可以同时处理多个任务,充分利用处理器的计算能力,大大提高计算速度。

2. 加快程序运行速度:将一个程序拆分成多个子任务,分配给不同的核心进行并行计算,可以在相同的时间内完成更多的工作。

3. 处理复杂任务:在处理大规模数据、图形渲染、模拟等复杂任务时,多核处理器可以将任务分解成多个子任务,分配给各个核心同时进行,从而提高整体的处理能力。

二、并行编程概念并行编程是指将程序中可以并行执行的任务拆分成多个子任务,在多个处理单元上同时执行,以达到加速运算的目的。

并行编程包括以下关键概念:1. 线程:是程序的最小执行单位,每个线程独立运行,拥有自己的寄存器和堆栈。

2. 进程:是执行中的程序的一个实例。

一个程序可以同时有多个进程在运行。

3. 并发:是指两个或多个任务可以在重叠的时间段内执行,无需等待。

4. 同步:是指控制多个线程的执行顺序和时机,保证线程之间的数据一致性。

三、并行编程工具为了更好地利用多核处理器的优势,我们可以使用以下并行编程工具:1. OpenMP:是一种并行编程接口,可以在C、C++和Fortran等编程语言中使用。

通过添加一些指令和注释,可以将串行代码转化为并行代码。

2. MPI:是一种消息传输接口,用于在多核处理器上进行分布式并行计算。

3. CUDA:是一种并行计算平台和编程模型,用于利用NVIDIA图形处理器的并行计算能力。

四、掌握并行编程的方法要熟练掌握并行编程,充分利用多核处理器,可以从以下几个方面入手:1. 学习并行编程语言:如OpenMP、MPI和CUDA等,并理解其原理和使用方法。

嵌入式开发中的并行编程

嵌入式开发中的并行编程在嵌入式系统的开发中, 并行编程是一项非常重要的技术。

并行编程允许多个任务同时执行,提高系统的性能和响应速度。

本文将介绍嵌入式开发中的并行编程技术以及其应用。

一、嵌入式系统并行编程的背景嵌入式系统具有资源有限、功耗低、实时性要求高等特点。

针对这些特点,传统的串行编程方式显然无法满足需求。

因此,并行编程技术应运而生。

二、常见的并行编程模型在嵌入式开发中,有多种并行编程模型可供选择。

下面将介绍一些常见的模型及其特点。

1. 任务并行任务并行是最常见的并行编程模型,在该模型中,程序被分为若干个任务,这些任务可以并行执行。

任务之间可以通过消息传递或者共享内存进行通信。

2. 数据并行数据并行是指将大规模数据集分成若干个子数据集,在各个处理器上进行并行处理。

每个处理器对自己的子数据集进行计算,最后将结果进行合并。

3. 流水线并行流水线并行是指将处理过程分为若干个阶段,不同的处理器同时进行不同阶段的计算,最后将结果传递给下一个阶段进行处理。

流水线并行可以加速处理过程。

三、嵌入式开发中的并行编程技术在嵌入式系统的开发中,常用的并行编程技术有以下几种。

1. 线程和进程线程和进程是实现并行编程的常见手段。

线程是进程内的一个执行单元,可以独立运行。

通过多线程的方式,可以在同一个进程中实现并行计算。

2. 任务调度任务调度是指将多个任务安排在不同的处理器上执行,以实现并行计算。

任务调度需要考虑任务的依赖关系和任务的优先级等因素,以保证任务能够顺利执行。

3. 并行算法在嵌入式系统的开发中,使用并行算法可以加速计算过程。

并行算法可以将一个复杂的计算问题分解为多个子问题,并在多个处理器上同时进行计算,最后将结果进行合并。

四、嵌入式开发中的并行编程应用并行编程在嵌入式系统的开发中有着广泛的应用。

下面将介绍几个常见的应用场景。

1. 图像处理在嵌入式系统中,图像处理通常需要大量的计算资源。

通过并行编程,可以将图像处理过程分解为多个子任务,在多个处理器上同时进行处理,提高图像处理的速度。

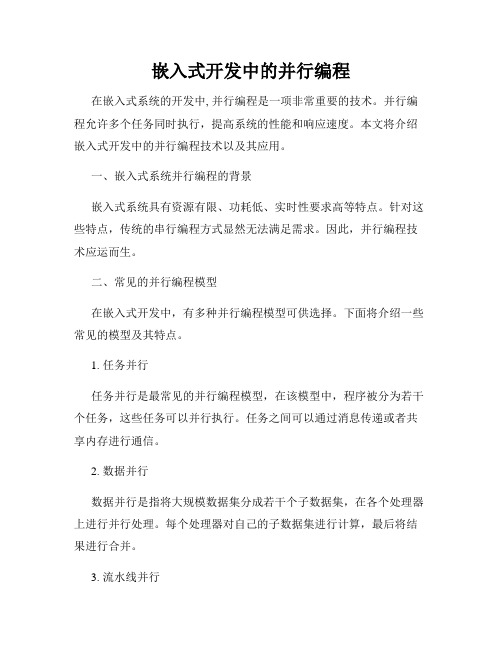

多核计算机上的并行计算

表 1用算法 2进行求和并行计算 的加速 比和效率

双核

P

l 2

四核

, %) r I ( P

1 2

ts ()

05l . 5 O

.

S p

ts ()

"

S p

19 3 "9

m( ) %

9 6 9. 4

o r ut n + C f d ci ( :C) ; re o

3 结语

通过 以上算例在各种 环境 下的运行 结果可 以看 出,拥 有 多核 C U的计算 机实际上是并行计算机 ,串行程序 只使 用 了 P

多核 C U的一个核 ,由于多核 C U拥有共享 主存 ,因此 对于 P P

变 ,由于设计理 念的不 同 ,在单 核 C U上运行 良好 的软件或 P 者传统 的算法不 能使多核 C U发挥其 最大效 能 ,要想 高效利 P 用 多核 C U,就必 须将 编程 思想从 “ P 串行 ”转 变 到 “ 行 ” 并 上 ,改进 原有 的程序 和算法 。

算法 2 ( 使用 O e MP的归约求 和算法) pn

得满意的多核并行效果 。

k n + ) C[ D + < ;k + i 】 =a[ 【】 ] i k 】 b【】 D; k 】}

算法 4 (p n O eMP环境下矩阵乘积并行算法)

# n l d o .> i c u e< mph

m i an 0

{ o p stn m tra s ( po ); # rg a o p p rl l m — e u _h e d N rc _ pa m m aa e l

fr ( l <= ;i + s m= u i o i ;i n + ) u s m+ ; = }

计算空气动力学并行编程基础

计算空气动力学并行编程基础

空气动力学并行编程基础是指在进行空气动力学模拟和计算时,使用

并行编程技术来提高计算效率和准确性的基础知识和技能。

以下是空气动

力学并行编程基础的主要内容:

1.并行计算的原理和方法:了解并行计算的基本原理和方法,掌握基

于多核CPU、GPU等硬件加速器的并行计算方法。

2. 数值计算库的使用:掌握数值计算库(如OpenFOAM、ANSYS

Fluent等)的使用方法,能够将计算工作划分为多个任务进行并行处理。

3. MPI编程:学习使用MPI(Message Passing Interface)进行并

行编程,能够完成基于MPI的并行化计算程序的设计和开发。

4. 多线程编程:学习使用多线程技术进行并行编程,能够编写基于OpenMP或CUDA等多线程编程工具的程序。

5.分布式计算:学习使用分布式计算技术进行并行计算,了解如何搭

建分布式计算环境和编写基于分布式计算框架的程序。

6.网格划分与负载均衡:了解空气动力学计算中网格的划分和负载均

衡问题,能够设计和实现均衡的网格划分和负载均衡算法。

7.性能优化:了解空气动力学计算中的性能优化技术,如算法优化、

数据结构优化、计算资源调度等,能够优化计算程序的性能。

通过学习和掌握上述基础知识和技能,能够有效地利用并行计算技术

进行空气动力学计算和模拟,提高计算效率和准确性。

如何利用超级计算技术进行高效的并行编程

如何利用超级计算技术进行高效的并行编程高效的并行编程是当今计算机科学领域的热门话题之一。

随着处理器核心数量的增加和超级计算机的发展,利用超级计算技术进行高效的并行编程已经成为一个关键技能。

本文将探讨如何利用超级计算技术进行高效的并行编程,以提高计算效率和性能。

首先,为了实现高效的并行编程,必须了解并行计算和超级计算技术的基本概念。

并行计算是指将大型计算任务分解成多个较小的子任务,并在多个处理器上同时执行,以提高计算效率。

超级计算技术是指利用多核处理器、分布式计算和高速网络等技术,实现高性能计算和大规模并行处理的技术。

在进行高效的并行编程之前,需要进行任务分解和调度。

任务分解是将大型计算任务划分成若干较小的子任务,以便并行执行。

任务调度是指将这些子任务分配给可用的处理器,并管理它们的执行顺序和资源分配。

良好的任务分解和调度可以最大程度地利用处理器的并行能力。

接下来,选择合适的并行编程模型也是至关重要的。

常见的并行编程模型包括共享内存模型和消息传递模型。

共享内存模型使用共享数据结构,不同的线程可以通过读写共享内存来进行通信和同步。

消息传递模型则通过消息的发送和接收来进行通信。

根据具体的应用场景和需求,选择合适的并行编程模型可以提高编程效率和性能。

在进行高效的并行编程时,合理使用线程和进程间的通信和同步机制也是必不可少的。

通过线程间的通信和同步,可以实现子任务之间的数据传输和共享,以及对资源的访问控制。

常用的线程间通信和同步机制包括互斥锁、条件变量、信号量等。

合理利用这些机制可以确保线程之间的数据一致性和并行执行的正确性。

此外,高效的并行编程还需要考虑任务负载的均衡和任务并行度的优化。

任务负载的均衡是指将子任务尽可能均匀地分配给处理器,以避免任务之间的负载不平衡导致性能下降。

任务并行度的优化是指根据系统资源和任务特性,选择适当的并行度来提高计算效率。

通过分析和调整任务负载的均衡和任务并行度,可以使并行编程更加高效。

了解编程技术中的并行计算和并行编程方法

了解编程技术中的并行计算和并行编程方法在当今信息技术高速发展的时代,计算机在各个领域的应用越来越广泛。

为了提高计算机的性能和效率,人们开始研究并行计算和并行编程方法。

并行计算是指同时执行多个任务,而并行编程则是为了实现并行计算而采用的一种编程方式。

本文将介绍并行计算和并行编程的基本概念、方法和应用。

一、并行计算的基本概念并行计算是指在多个处理器上同时执行多个任务,从而提高计算机系统的处理能力和效率。

与之相对的是串行计算,即在单个处理器上按照顺序执行任务。

并行计算的主要目的是通过任务的分解和分配,实现任务的并行执行,从而加快计算速度和提高系统的吞吐量。

二、并行计算的方法1. 任务并行任务并行是指将一个大任务分解成多个小任务,然后分配给多个处理器同时执行。

每个处理器独立地执行自己分配到的任务,最后将结果合并得到最终的结果。

任务并行的优点是可以充分利用多个处理器的计算能力,提高计算速度和系统的吞吐量。

2. 数据并行数据并行是指将大规模的数据分成多个子集,然后分配给多个处理器进行计算。

每个处理器独立地计算自己分配到的数据子集,最后将计算结果合并得到最终的结果。

数据并行的优点是可以充分利用多个处理器的存储空间和计算能力,提高计算速度和系统的吞吐量。

3. 流水线并行流水线并行是指将一个任务分解成多个子任务,并通过多个处理器按照一定的顺序进行处理。

每个处理器负责执行自己分配到的子任务,并将结果传递给下一个处理器进行处理。

流水线并行的优点是可以充分利用多个处理器的计算能力和存储空间,提高计算速度和系统的吞吐量。

三、并行编程的方法并行编程是为了实现并行计算而采用的一种编程方式。

在传统的串行编程中,程序按照顺序执行,而在并行编程中,程序需要考虑任务的分解和分配,以及任务之间的通信和同步。

常见的并行编程方法包括共享内存编程和消息传递编程。

1. 共享内存编程共享内存编程是指多个处理器共享同一块内存空间,并通过读写共享内存来实现任务之间的通信和同步。

[DOCIN]基于异构多核平台的优化编程研究

![[DOCIN]基于异构多核平台的优化编程研究](https://img.taocdn.com/s3/m/67f6f5c927fff705cc1755270722192e453658bd.png)

华中科技大学博士学位论文摘要过去几十年来,代表CPU性能的主频在不断的提高,但由于生产工艺、功耗以及架构设计等原因使得主频之路已经走到了尽头。

在无法进一步提高处理器主频的情况下,CPU进入了多核时代。

对于计算密集型的应用,由若干个完全相同处理器核心构成的同构多核CPU并不是最好的方案。

因此,出现了以通用CPU加专用加速核心构成的异构计算平台,并且逐渐成为高性能计算领域的主流架构。

这种底层硬件架构的革新也给在它上面的程序开发带来重大改变。

而目前的异构多核平台都面临着性能调优困难和编程复杂的问题。

如何简化编程,如何充分发挥异构多核平台的性能是程序开发方面不得不面临的挑战。

在异构多核计算平台上,专用加速核心是提供计算能力的主要部件,如何挖掘加速核心的处理能力是影响整体性能的关键。

本研究提出了基于异构多核平台的多粒度并行优化策略,基于该模型实现的应用能最大限度地使用专用加速核心硬件计算资源,由此,总结出在异构多核平台上的专用加速核心端进行性能调优的一般规律。

现代异构计算平台的异构多核架构中,加速核心通常用于计算,但平台上的多核CPU的计算能力同样很强大。

为了利用CPU的计算能力,针对数据并行应用,提出了异构数据并行模型,该异构数据并行模型通过对CPU和加速核心间负载的合理划分,使得CPU和专用计算核心间的负载达到均衡。

在利用专用加速核心计算能力的同时,充分发挥多核CPU的计算能力,从而提高系统整体的性能。

同样是为了利用多核CPU的计算性能,对于一些流式数据并行计算的应用,提出了流式计算模型,该模型是由CPU、加速核心以及它们之间的数据通信组成一条三阶段的流水线。

CPU端对输入数据进行初步处理,过滤掉部分无需APU处理的数据,这样做一方面减少了CPU与加速核心之间的巨大的通信延迟;另一方面也降低专用加速核心的负载。

通过调整CPU端的过滤的精度来协调CPU和专用加速核心之间的负载,使流水线处于充盈状态,以达到整体的性能最优。

并行编程原理及程序设计

并行编程原理及程序设计并行编程是一种编程方法,通过同时执行多个计算任务来提高计算机程序的性能和效率。

在传统的串行编程中,计算机程序按照顺序执行指令,只有一个计算任务在运行。

而并行编程可以同时运行多个计算任务,并利用多核处理器、并发技术和分布式系统来实现。

并行编程的核心原则是任务分解和任务调度。

首先,需要将一个大的计算任务分解为多个小的子任务,这些子任务可以并行执行。

然后,通过合理的任务调度算法将这些子任务分配给不同的处理器或计算节点进行执行。

最后,将子任务的计算结果合并得到最终的计算结果,完成整个并行计算过程。

并行编程的程序设计需要考虑以下几个方面:1.并行算法的设计:针对不同的并行计算问题,需要设计符合并行计算模型的算法。

并行算法通常包括任务分解、任务调度、数据通信等关键步骤。

合理的算法设计可以充分利用并行计算资源,提高程序的速度和效率。

2.数据共享与同步:在并行编程中,多个计算任务可能需要共享数据。

数据共享的正确性和一致性是保证并行程序正确运行的关键。

为了避免数据竞争和死锁等并发问题,需要使用同步机制,如锁、信号量、条件变量等来确保数据访问的顺序和正确性。

3.并行性调度:并行编程中,任务调度的策略对程序的性能和效率有着重要影响。

任务调度算法应根据任务的性质、数据依赖关系和计算资源的情况进行合理的调度决策,以最大程度地提高并行任务的并发度和执行效率。

4.数据分布和通信:在分布式并行编程中,不同的计算节点之间需要进行数据交换和通信。

数据分布的合理性和通信开销的减少是影响分布式并行程序性能和效率的关键因素。

合理的数据分布和高效的通信机制可以减少通信开销,提高程序的性能和可扩展性。

5. 调试和优化:并行编程中,bug 的调试和性能的优化具有一定的挑战性。

并行程序的错误可能涉及到多个计算任务和多个计算节点,调试过程相对复杂。

而性能优化则需要通过有效的算法设计、数据分布和通信机制来减少资源竞争,提高并行任务的并发度和执行效率。

超级计算技术中的并行编程模型介绍

超级计算技术中的并行编程模型介绍超级计算机被设计用于解决复杂问题,大规模数据处理和模拟计算等高性能计算任务。

为了充分利用超级计算机的计算能力和处理大规模数据的需求,高效的并行编程模型至关重要。

本文将介绍超级计算技术中常见的并行编程模型,以帮助读者更好地理解并应用这些模型。

1. SIMD(单指令多数据)模型SIMD模型是一种将一个操作应用于多个数据元素的并行编程模型。

在该模型中,计算任务被分为多个数据并行的操作,每个操作都被应用于大量的数据元素。

这样可以通过向量化指令集或并行处理器来加速计算。

SIMD模型适用于需要对大规模数据进行相同操作的计算任务,如图像处理和数值模拟。

2. MIMD(多指令多数据)模型MIMD模型是一种将多个独立的指令应用于不同的数据元素的并行编程模型。

在该模型中,计算任务被分为多个并行的子任务,每个子任务都是独立执行的,可以分配给不同的处理器或计算节点。

MIMD模型可以同时处理不同的计算任务,适用于解决大规模、复杂的问题,如分布式计算和并行算法。

3. SPMD(单指令多线程)模型SPMD模型是一种将相同指令应用于多个并行线程的并行编程模型。

在该模型中,计算任务被分为多个线程,每个线程都执行相同的指令序列,但可能处理不同的数据。

SPMD模型适用于数据密集型计算任务,其中每个线程可以独立执行不同的计算操作,例如在图像和视频处理中的像素级操作。

4. 数据并行模型数据并行模型是一种将计算任务分为多个数据部分并以数据为中心进行并行处理的编程模型。

在该模型中,数据被分为不同的分块、分配给不同的处理器或计算节点,然后进行并行计算。

数据并行模型适用于某些科学和工程应用中的数组操作和矩阵运算。

5. 任务并行模型任务并行模型是一种将计算任务划分为不同的子任务并以任务为中心进行并行处理的编程模型。

在该模型中,每个子任务独立执行,可以分配给不同的处理器或计算节点,之后通过消息传递或共享内存进行通信和同步。

高性能计算技术的并行编程技巧

高性能计算技术的并行编程技巧随着科学技术的不断发展,对计算机性能的要求也越来越高。

高性能计算技术在科学研究、工程仿真、天气预报等领域中起着至关重要的作用。

而并行计算是提升计算机性能的重要手段之一。

本文将介绍高性能计算技术的并行编程技巧,帮助读者更好地利用并行计算来提升计算效率。

首先,要理解并行计算的基本概念。

并行计算是指将一个计算任务分解成多个子任务,并在多个处理器上同时执行这些子任务。

每个子任务都是独立的,可以并行执行,最后再将它们的结果合并起来得到最终结果。

并行计算的核心思想是任务的分解与合并,通过合理地分解任务并将计算负载均衡地分配给不同的处理器,可以充分发挥多处理器系统的计算能力。

在并行编程中,最常用的并行编程模型是共享内存和消息传递。

共享内存模型中,所有的处理器共享同一个内存地址空间,它们通过读写共享变量来进行通信和同步。

而消息传递模型中,每个处理器都有自己的私有内存空间,并通过发送消息和接收消息的方式来进行通信。

共享内存模型适用于在单机上运行并行程序,而消息传递模型适用于在多机集群上运行并行程序。

在编写并行程序时,要注意以下几点:第一,任务的分解要合理。

合理的任务分解可以使得每个子任务的计算量尽可能均衡,并且能够充分利用处理器的计算能力。

分解出的子任务应该尽量减少对共享变量的访问,从而避免对内存的竞争,提高程序的效率。

第二,要注意数据的局部性。

在并行计算中,数据的传输是一个非常耗时的操作。

因此,要尽量减少数据的传输量,提高数据的局部性。

可以利用缓存来减少对大量数据的读写操作,从而提高程序的运行效率。

第三,要合理地选择并行算法和数据结构。

不同的算法和数据结构具有不同的并行性能。

在选择并行算法和数据结构时,要充分考虑各种因素,包括任务的划分、通信和同步的代价等。

合理地选择并行算法和数据结构可以大大提高程序的运行效率。

第四,要合理地利用并行编程工具。

并行编程工具可以简化并行程序的开发过程,提高开发效率。

如何利用超级计算技术进行高效的并行编程

如何利用超级计算技术进行高效的并行编程在当今科技快速发展的时代,超级计算技术在解决复杂问题和加快计算速度方面扮演着重要角色。

并行编程技术则是发挥超级计算机性能的关键。

本文将介绍如何利用超级计算技术进行高效的并行编程,以提高计算速度和效率。

首先,了解并行计算的基础是必要的。

并行计算是指将计算任务分成若干个子任务,然后同时运行在多个处理器上,以加快整体计算速度。

而在这个过程中,需要考虑到任务的分解和调度,以及数据传输和同步等问题。

其次,选择合适的并行编程模型也是至关重要的。

有多种并行编程模型可供选择,如共享内存模型和分布式模型等。

选择合适的模型取决于问题的属性和计算机架构。

对于多核处理器的共享内存系统,OpenMP是一种流行的并行编程模型。

而对于分布式内存的多机系统,MPI (Message Passing Interface)则是一种常用的并行编程模型。

进一步说,合理地利用并行编程模型的指令和功能也是提高并行计算效率的关键。

在OpenMP中,可以使用#pragma omp指令将串行代码转化为并行代码。

通过使用并行循环和并行区域,可以将循环和过程并行化,充分发挥多核处理器的潜力。

而在MPI中,则需要合理地进行进程的划分与通信。

合理地选择消息传递方式,减少消息传递的次数和数据量,可以减少通信开销并提高计算效率。

此外,利用高级编程语言和工具也是提高并行编程效率的关键。

高级编程语言如C++、Fortran和Python等提供了丰富的并行编程库和函数,可以简化并行编程的工作。

例如,C++的STL库提供了各种并行算法,如并行排序、并行查找等,可以更加方便地进行并行编程。

同时,一些高级工具如Intel的TBB (Threading Building Blocks)和OpenACC (Open Accelerators)等,提供了更高层次的抽象和自动化,可以进一步简化并行编程的过程。

除了选择合适的并行编程模型和利用高级语言和工具,优化并行算法也是提高并行计算效率的重要部分。

超级计算技术中的并行程序设计与优化

超级计算技术中的并行程序设计与优化并行程序设计与优化在超级计算技术中的重要性随着科技的不断发展,超级计算机已成为处理海量数据和复杂计算的基石。

并行程序设计与优化是超级计算技术中的关键环节,能够提高计算机性能,实现高效的数据处理和计算。

在超级计算机中,程序设计需要优先考虑并行性,以利用并行处理的优势。

并行程序设计是指将任务分解成多个子任务,分别在不同的处理器或计算核心上并行执行,以加快计算速度。

它能够充分利用计算机的多核心架构,提高系统的整体性能。

并行程序设计涉及到多个层面的优化。

首先,需要将问题分解为适度大小的任务,以保证负载均衡和并行任务的粒度合适。

过大的任务会导致处理器负荷不均衡,而过小的任务会导致过多的通信开销。

其次,需要设计有效的通信机制,以实现不同子任务之间的数据交流和同步。

通信的开销对程序性能有重要影响,合理设计通信机制可以减少通信开销,提高计算速度。

此外,还需要充分利用数据局部性,通过合理的数据分配和访问方式,减少数据传输和存储开销,提高程序效率。

在并行程序设计的过程中,合理选择并行编程模型也是至关重要的。

常用的并行编程模型有MPI和OpenMP。

MPI是消息传递接口,适用于分布式内存系统,可以处理大规模并行计算。

它通过发送和接收消息来实现多个处理器之间的通信。

OpenMP是一种共享内存并行编程模型,适用于共享内存系统。

它通过使用指令指定并行区域,将任务分布到不同的线程上并行执行。

根据问题的性质和计算资源的情况,选择适合的并行编程模型,可以更好地发挥计算机的性能。

在超级计算机中,程序优化是不可忽视的一部分。

通过对程序进行优化,可以提高计算速度和性能。

首先,需要进行算法优化。

选择合适的算法和数据结构,可以减少计算量和时间复杂度,提高程序效率。

其次,需要进行并行性的优化。

通过合理的任务划分、通信机制和数据局部性优化,可以减少并行程序中的通信开销和数据传输开销。

此外,还可以通过性能分析工具进行性能调优,找出程序中的瓶颈并进行改进。

二维椭圆型方程普通 4 阶格式及其并行程序设计

二维椭圆型方程普通 4 阶格式及其并行程序设计

第一章 引言

1.1 泊松方程概述

二维 Poisson 方程的基本形式为

2 u ( x, y ) 2 u ( x, y ) f ( x, y ) ,他是最简单 x 2 y 2

也是最典型的椭圆形偏微分方程,其描述了处于稳定或者是平衡状态下的物理 量,在物理学中我们经常可以见到 Poisson 方程、拉普拉斯方程,如在静电场、 引力场、流体力学、压力传导等中。在地球物理学中,重力位、磁位、电位等的 运动方程中均满足了 Poisson 方程。比如在流体力学中描述速度矢和势函数之间 的关系: 2 D 是一个 Poisson 方程,由它可知势函数与速度矢之间的互求 关系,当 D=0 时该方程又称为 Laplace 方程或者调和方程。

第二章

Poisson 方程的差分离散 ............................................................ 4

2.1 五点格式的建立 ............................................................................................. 4 2.2 九点格式的建立 ............................................................................................. 6 2.3 编制程序求解方程及其几种迭代格式 ............................................................ 8

第三章

Poisson 方程的 MPI 并行程序设计 ...........................................12

提高超级计算技术并行计算能力的编程技巧指南

提高超级计算技术并行计算能力的编程技巧指南超级计算机是一种将成千上万个处理器集合起来以进行高性能计算的超级计算技术。

随着技术的不断发展,超级计算机的并行计算能力日益提高,这为科学、工程和商业领域的各种复杂问题的解决提供了巨大的潜力。

然而,要充分发挥超级计算机的潜力,需要掌握一些编程技巧和指南。

本文将介绍一些提高超级计算技术并行计算能力的编程技巧指南。

首先,要充分利用超级计算机的并行计算能力,我们需要将问题划分成更小的子问题,并使用适当的并行算法来处理这些子问题。

并行算法是一种将问题分解为多个可同时执行的子任务的算法。

通过并行化算法,我们可以更有效地利用超级计算机的处理器中心,从而提高计算效率。

其次,我们需要选择合适的并行计算模型来实现并行计算。

并行计算模型是一种描述如何组织和执行并行计算的框架。

常用的并行计算模型包括:共享内存模型、分布式内存模型和混合内存模型。

选择合适的并行计算模型可以更好地适应超级计算机的体系结构,从而提高并行计算能力。

在编写并行计算程序时,我们需要提高代码的可伸缩性。

可伸缩性是指在增加处理器数量时,程序的性能能够线性或接近线性地提高。

为了提高代码的可伸缩性,我们可以使用一些技术,如减少通信开销、优化数据布局、避免数据竞争等。

通过优化代码的可伸缩性,我们可以更好地利用超级计算机的并行计算能力。

此外,合理地利用超级计算机的存储层次结构也是提高并行计算能力的关键。

超级计算机具有多级存储器层次结构,包括:寄存器、高速缓存、主存和磁盘等。

合理地利用存储层次结构可以减少数据传输延迟,提高计算效率。

例如,将数据局部化到高速缓存中,可以减少对主存的访问次数,从而提高计算速度。

最后,我们还可以利用一些高级编程工具和技术来提高超级计算技术的并行计算能力。

例如,使用多线程编程模型可以将计算任务分配给不同的线程来并行执行,从而提高计算效率。

使用并行调试工具可以帮助我们检测和解决并行程序中的错误和性能问题。

数控编程中的并行计算与并行程序设计

数控编程中的并行计算与并行程序设计近年来,随着科技的不断进步和发展,数控编程在制造业中的应用越来越广泛。

数控编程作为一种基于计算机的控制技术,通过编写程序来指导机床进行加工操作,提高了生产效率和产品质量。

而在数控编程中,如何利用并行计算和并行程序设计技术,进一步提升加工效率和精度,成为了研究的热点之一。

并行计算是指将一个大问题划分成多个小问题,并通过多个处理器同时进行计算,最后将结果进行合并的计算方式。

在数控编程中,通过并行计算,可以将复杂的加工任务分解成多个子任务,由多个处理器同时进行计算,从而提高加工效率。

例如,在进行复杂曲面加工时,可以将曲面分割成多个小面,由多个处理器分别计算,最后将结果合并得到最终的加工路径。

这种并行计算的方式,不仅能够提高加工效率,还能够减少计算时间,提高程序的响应速度。

而要实现并行计算,就需要进行并行程序设计。

并行程序设计是指将一个大程序划分成多个小程序,并通过多个处理器同时执行这些小程序的设计方式。

在数控编程中,通过并行程序设计,可以将复杂的加工任务分解成多个子任务,由多个处理器同时执行,从而实现并行计算。

例如,在进行多轴联动加工时,可以将不同轴的运动控制分别编写成独立的子程序,由多个处理器同时执行,从而实现多轴的并行控制。

这种并行程序设计的方式,不仅能够提高加工效率,还能够减少程序的复杂度,提高程序的可读性和可维护性。

然而,并行计算和并行程序设计在数控编程中的应用也面临着一些挑战和难题。

首先,如何合理地划分加工任务和设计程序,是一个需要解决的问题。

在进行并行计算和并行程序设计时,需要将加工任务和程序划分成多个子任务和子程序,但如何划分才能最大限度地提高并行计算的效果,是需要仔细考虑的。

其次,如何协调和管理多个处理器之间的计算和通信,也是一个需要解决的问题。

在进行并行计算时,多个处理器之间需要进行计算结果的合并和通信,如何保证计算的正确性和效率,是需要进行深入研究的。

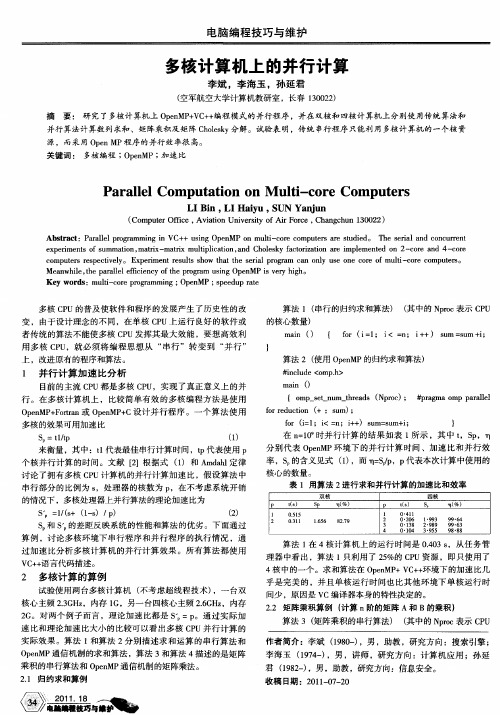

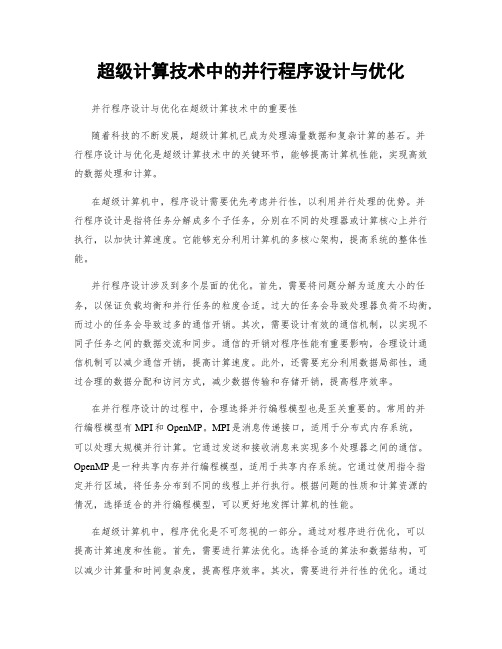

APU是什么

APU是什么?未来?今天的主角不是CPU,而是APU。

那么APU是什么?APU的英文全称是“Accelerated Processing Units”,意为加速处理器,她是一款融聚了AMD先进技术的产品。

实际上在今年的1月份我们就已经接触过APU——AMD在2011年1月召开了主题为“I Love APU”的盛大发布会,而当时所发布的产品为Brazos E350,也就是APU的入门型号,在之前我们已经对E350平台做过详细评测。

在等待了近半年之后,AMD终于发布其主流定位的APU型号,也就是本文的主角A系列,而在A 系列APU发布之时,我们也将对这套被网友期待了半年之久的平台做详细评测,让我们体验一下APU所带来的异构计算的魅力。

其实早在去年(2010年)的2月,AMD技术部高级副总裁 Chekib Akrout 就已经给我们带来了APU的消息,用Chekib Akrout先生的话来形容APU就是“最好的CPU和最好的GPU组成了APU”,在这一方面AMD是占有巨大优势的——目前AMD方面具备CPU和GPU这两颗PC最重要核心的研发实力,在其并购ATI之后的时间里AMD推出了一系列占据明显优势的集显产品,而APU又将是一款超越之前所有作品的大作,其内部的独显核心将带来比以往都更强的加速性能,更重要的是,新的32纳米制程将带来更低的功耗和更为紧密的融合,这是一次全面的进步。

产品:A8-3800AMD CPU融聚的产物—1+1大于2的APU◇融聚的产物—1+1大于2的APU在此前我们和AMD高层沟通的过程中,“融聚”这个词出现的几率非常高,为什么?因为APU的特点就是融聚,APU将是融合了传统CPU核心以及独显核心的全新产品,这是由AMD研发团队带来的超时代产物——最好的CPU和最好的GPU 组成了APU,AMD技术部高级副总裁 Chekib Akrout 的原话正是如此。

AMD高级副总裁兼技术事业部总经理Chekib Akrout向记者介绍APU事实上在6月成功举办的ComputeX 2011(2011年台北电脑展)上,APU就已经获得了ComputeX展会委员会的认可并授予了ComputeX 2011最佳选择奖,而将这一奖项赠予一款CPU类产品是不多见的,可见IT官方组织对于APU的高度认可,而AMD全球高级副总裁、大中华区总裁邓元鋆也说过:“APU作为无缝融合架构的加速处理器,在视频图像上有着非常大的优势,将标清变身为高清等等功能让APU赋予了更大的潜力及市场。

基于OpenACC编程模型的逆时偏移多级并行的设计与优化

基于OpenACC编程模型的逆时偏移多级并行的设计与优化赵虎;武泗海;尹成;唐泽凯;贾鹏【摘要】OpenCL和CUDA等GPU并行编程模型在波场数值模拟、偏移成像等领域已经得到广泛应用,但二者都破坏原有的串行代码而重新设计并行算法,会增加并行实现的难度和工作量.本文将一种新的GPU并行编程模型OpenACC应用于逆时偏移计算,通过添加编译指令实现节点间/节点内的进程/线程级的多级并行方案,是一种更便捷、高效的异构并行技术.对多级并行的数据通信进行优化,实现了叠前偏移成像的多级异构并行加速.数值实验结果表明文中多级并行方案可以有效地解决逆时偏移计算量大和存储量大的问题;经过数据通信的优化后,可以显著提高逆时偏移的计算效率.【期刊名称】《石油地球物理勘探》【年(卷),期】2018(053)006【总页数】8页(P1307-1313,1325)【关键词】GPU编程;OpenACC;逆时偏移;多级并行【作者】赵虎;武泗海;尹成;唐泽凯;贾鹏【作者单位】西南石油大学地球科学与技术学院,四川成都610500;西南石油大学天然气地质四川省重点实验室,四川成都610500;西南石油大学地球科学与技术学院,四川成都610500;西南石油大学天然气地质四川省重点实验室,四川成都610500;西南石油大学地球科学与技术学院,四川成都610500;西南石油大学天然气地质四川省重点实验室,四川成都610500;中国石油东方地球物理勘探公司西南物探分公司,四川成都610213;中国石油东方地球物理勘探公司西南物探分公司,四川成都610213【正文语种】中文【中图分类】P6311 引言地震勘探的发展与高性能计算息息相关,勘探新技术的推广离不开高性能计算,特别是在叠前深度偏移、逆时偏移和全波形反演等方面,庞大的计算量在一定程度上制约了上述技术的应用。

目前,常规的CPU加速技术是基于消息传递的MPI编程模型和共享存储的OpenMP编程模型实现的混合并行[1]。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

11 | The Programmer’s Guide to the APU Galaxy | June 2011

FUSION SYSTEM ARCHITECTURE – AN OPEN PLATFORM

Open Architecture, published specifications – FSAIL virtual ISA – FSA memory model – FSA dispatch ISA agnostic for both CPU and GPU

Single-thread Performance

Throughput Performance

we are here Time (Data-parallel exploitation)

Time

Time (# of processors)

9 | The Programmer’s Guide to the APU Galaxy | June 2011

AMD Fusion System Architecture

Roadmap Software evolution A visual view of the new command and data flow

3 | The Programmer’s Guide to the APU Galaxy | June 2011

Multi-Core Era

Enabled by: Moore’s Law SMP architecture

Heterogeneous Systems Era

Enabled by: Abundant data parallelism Power efficient GPUs Temporarily Constrained by: Programming models Comm.overhead

DirectX®

8 | The Programmer’s Guide to the APU Galaxy | June 2011

A NEW ERA OF PROCESSOR PERFORMANCE

Single-Core Era

Enabled by: Moore’s Law Voltage Scaling Constrained by: Power Complexity

THE PROGRAMMER’S GUIDE TO THE APU GALAXY

Phil Rogers, Corporate Fellow AMD

THE OPPORTUNITY WE ARE SEIZING

Make the unprecedented processing capability of the APU as accessible to programmers as the CPU is today.

CUDA™, Brook+, etc

See Herb Sutter’s Keynote tomorrow for a cool example of plans for the architected era!

2002 - 2008

2009 - 2011

2012 - 2020

10 | The Programmer’s Guide to the APU Galaxy | June 2011

COMMITTED TO OPEN STANDARDS AMD drives open and de-facto standards – Compete on the best implementation Open standards are the basis for large ecosystems Open standards always win over time – SW developers want their applications to run on multiple platforms from multiple hardware vendors

3rd Generation Unified Video Decoder

PCIe® Gen2

Single-channel DDR3 @ 1066 6W TDP w/ Local Hardware Thermal Control

Performance:

Up to 8.5GB/s System Memory Bandwidth Suitable for sealed, passively cooled designs

EVOLUTION OF HETEROGENEOUS COMPUTING

Architected Era Excellent Architecture Maturity & Programmer Accessibility Standards Drivers Era OpenCL™, DirectCompute Driver-based APIs AMD Fusion System Architecture GPU Peer Processor

Quality of Service Common Manufacturing Technology Bi-Directional Power Mgmt between CPU and GPU Fully coherent memory between CPU & GPU

Extend to Discrete GPU

4 | The Programmer’s Guide to the APU Galaxy | June 2011

LOW POWER E-SERIES AMD FUSION APU: “ZACATE”

E-Series APU

2 x86 Bobcat CPU cores Array of Radeon™ Cores

Performance:

Up to 8.5GB/s System Memory Bandwidth Up to 90 Gflop of Single Precision Compute

5 | The Programmer’s Guide to the APU Galaxy | June 2011

TABLET Z-SERIES AMD FUSION APU: “DESNA”

Z-Series APU

2 x86 “Bobcat” CPU cores Array of Radeon™ Cores

Discrete-class DirectX® 11 performance 80 Stream Processors

Poor

Expert programmers C and C++ subsets Compute centric APIs , data types Multiple address spaces with explicit data movement Specialized work queue based structures Kernel mode dispatch

Array of Radeon™ Cores

Discrete-class DirectX® 11 performance

3rd Generation Unified Video Decoder Blu-ray 3D stereoscopic display PCIe® Gen2 Dual-channel DDR3 45W TDP

6 | The Programmer’s Guide to the APU Galaxy | June 2011

MAINSTREAM A-SERIES AMD FUSION APU: “LLANO”

A-Series APU

Up to four x86 CPU cores

AMD Turbo CORE frequency acceleration

Mainstream programmers Full C++ GPU as a co-processor Unified coherent address space Task parallel runtimes Nested Data Parallel programs User mode dispatch Pre-emption and context switching

APU: ACCELERATED PROCESSING UNIT

The APU has arrived and it is a great advance over previous platforms

Combines scalar processing on CPU with parallel processing on the GPU and high bandwidth access to memory How do we make it even better going forward? – Easier to program – Easier to optimize – Easier to load balance – Higher performance – Lower power

Integrate CPU & GPU in silicon

GPU Compute C++ support

Unified Address Space for CPU and GPU

Unified Memory Controller

User mode scheduling

GPU uses pageable system memory via CPU pointers

FSA FEATURE ROADMAP

Physical Integration