MOS场效应晶体管

白底+9第9章MOS场效应晶体管

结论:导电因子由工艺参数 K’和设计参数 W/L 决定。

VLSI CAD, CHP.0 37

9-1-1 MOS晶体管的基本结构

• MOS晶体管--- MOSFET,金属-氧化物-半 导体场效应晶体管 • 基本结构:源区,漏区,沟道区,图1-1-2, 图1-1-1, • 主要结构参数:

– – – –

2000-9-20

沟道长度(1-1-2,栅极图形沟道长度poly,实际沟道长度S-D) 沟道宽度W (1-1-3, W= W1 +W2 +W3) 栅氧化层厚度tox 源漏区结深 Xj (见图1-1-1 )

• 9-4- 1 MOS晶体管的本征电容 – 定义:由沟道区内的耗尽层电荷和反型层电荷随外 电压变化引起的电容。 • 9-4- 2 MOS晶体管的寄生电容 – 源漏区PN结电容:CjSB、CjDB,图1-4-6 – 覆盖电容: CGS、CGD, 图1-4-9, CGB,图1-4-9, • 9-4- 3 MOS晶体管瞬态分析的等效电路*

27

夹断现象

2000-9-20

VLSI CAD, CHP.0

28

9-3-3 饱和区沟道长度调制效应

• 现象:图1-3-9,实际I—V特性饱和区电流不饱和 • 原因:图1-3-8 • 对电流方程的修正:在下式中

W off Cox

Leff

Leff L ΔL (1.3.26)

ΔL λVDS L

• 美国,R.M.Warner, • 电子工业出版社

前言, 2

9-1 MOS晶体管工作原理

• • • • 9-1-1 MOS晶体管的结构特点和基本原理 9-1-2 MOS晶体管的阈值电压分析 9-1-3 MOS晶体管的电流方程 920

mos管的作用功能

MOS管(金属-氧化物-半导体场效应晶体管)具有多种功能,主要包括放大器、电子开关、时钟电路和射频放大器等。

放大器:MOS管可以放大模拟电信号,例如音频信号,使得音乐声音更加清晰、有力。

电子开关:MOS管可以作为电子开关,在电路中开启或关闭电路,从而实现电路的控制。

时钟电路:MOS管可用于制作时钟电路,例如计数器、时序电路等。

可以对输入信号进行处理,从而实现时钟信号的发生和计数。

射频放大器:MOS管可以作为射频放大器,放大无线电信号,从而增强信号的传输距离和质量。

转换数字电信号:MOS管可以将输入的模拟电信号转换成数字电信号或将数字电信号转换回模拟电信号。

在实际应用中,MOS管的多种功能使其在许多领域中得到广泛应用,例如音频放大、电源管理、通信等。

MOS场效应管

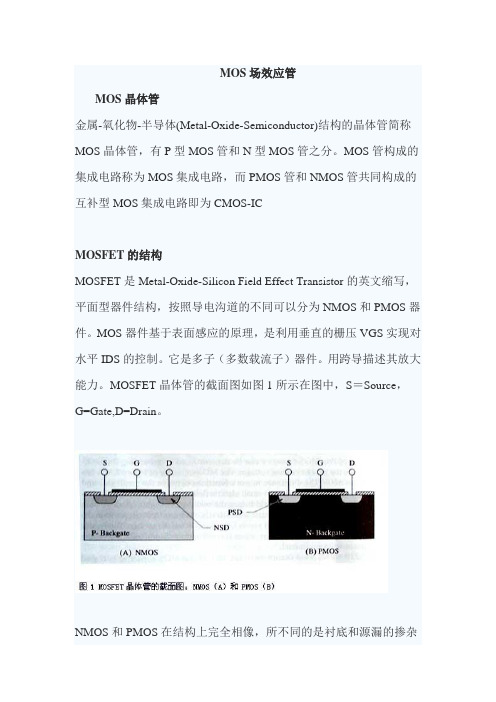

MOS场效应管MOS晶体管金属-氧化物-半导体(Metal-Oxide-Semiconductor)结构的晶体管简称MOS晶体管,有P型MOS管和N型MOS管之分。

MOS管构成的集成电路称为MOS集成电路,而PMOS管和NMOS管共同构成的互补型MOS集成电路即为CMOS-ICMOSFET的结构MOSFET是Metal-Oxide-Silicon Field Effect Transistor的英文缩写,平面型器件结构,按照导电沟道的不同可以分为NMOS和PMOS器件。

MOS器件基于表面感应的原理,是利用垂直的栅压VGS实现对水平IDS的控制。

它是多子(多数载流子)器件。

用跨导描述其放大能力。

MOSFET晶体管的截面图如图1所示在图中,S=Source,G=Gate,D=Drain。

NMOS和PMOS在结构上完全相像,所不同的是衬底和源漏的掺杂类型。

简单地说,NMOS是在P型硅的衬底上,通过选择掺杂形成N 型的掺杂区,作为NMOS的源漏区;PMOS是在N型硅的衬底上,通过选择掺杂形成P型的掺杂区,作为PMOS的源漏区。

如图所示,两块源漏掺杂区之间的距离称为沟道长度L,而垂直于沟道长度的有效源漏区尺寸称为沟道宽度W。

对于这种简单的结构,器件源漏是完全对称的,只有在应用中根据源漏电流的流向才能最后确认具体的源和漏。

器件的栅电极是具有一定电阻率的多晶硅材料,这也是硅栅MOS器件的命名根据。

在多晶硅栅与衬底之间是一层很薄的优质二氧化硅,它是绝缘介质,用于绝缘两个导电层:多晶硅栅和硅衬底,从结构上看,多晶硅栅-二氧化硅介质-掺杂硅衬底(Poly-Si--SiO2--Si)形成了一个典型的平板电容器,通过对栅电极施加一定极性的电荷,就必然地在硅衬底上感应等量的异种电荷。

这样的平板电容器的电荷作用方式正是MOS器件工作的基础。

MOS管的模型MOS管的等效电路模型及寄生参数如图2所示。

图2中各部分的物理意义为:(1)LG和RG代表封装端到实际的栅极线路的电感和电阻。

mos管工艺流程

mos管工艺流程MOS管(金属氧化物半导体场效应晶体管)是一种常用的场效应晶体管,广泛应用于集成电路中。

MOS管的制造需要经过一系列的工艺流程,下面将详细介绍MOS管的制造流程。

首先,制作MOS管的第一步是准备硅基片。

硅基片是制造集成电路的基础材料。

它通过切割硅单晶材料得到,然后经过多次的研磨和抛光,使得硅基片表面光洁平整。

接下来,将硅基片进行清洗,以去除表面的杂质和污染物。

清洗过程中使用一系列溶液和超声波来清洗硅基片。

清洗后,硅基片需要进行干燥,以确保表面干净无尘。

然后,在硅基片上生长一层绝缘层。

绝缘层可以是氧化硅(SiO2)或氮化硅(Si3N4),它起到隔离和保护MOS管的作用。

生长绝缘层的方法有热氧化和化学气相沉积(CVD)。

热氧化是将硅基片放入高温氧气中,使硅表面与氧气反应生成氧化硅。

化学气相沉积则是通过化学反应在硅表面沉积氮化硅。

接下来是制作栅极。

首先,在绝缘层上涂覆一层光刻胶,然后使用曝光设备将光刻胶曝光。

曝光后,用显影液去除未曝光的光刻胶,形成栅极的图案。

然后,将栅极材料(通常是多晶硅或金属)沉积在图案上,形成栅极。

然后是离子注入。

离子注入是将掺杂物注入硅基片中,以改变硅基片的导电性能。

掺杂物可以是硼(B)或磷(P),硼用于形成P型区,而磷用于形成N型区。

注入时,利用离子注入设备将掺杂物离子加速并注入硅基片,形成掺杂层。

接下来是退火步骤。

退火是将硅基片加热到高温,以恢复掺杂区的结构,并消除离子注入中的缺陷。

退火还帮助栅极材料与硅基片结合更牢固。

最后是接触孔刻蚀和金属沉积。

这一步是将接触孔刻蚀在绝缘层上,并在接触孔中沉积金属,以形成电极。

接触孔的刻蚀可以使用干法刻蚀或湿法刻蚀,金属的沉积可以使用物理气相沉积(PVD)或化学气相沉积(CVD)。

通过以上工艺流程,MOS管的制造完成。

最后,还需要进行电气测试和封装等步骤,以确保MOS管的质量和可靠性。

总之,MOS管制造的流程复杂且涉及多个步骤,每个步骤都需要精确控制和严格的质量检测。

第八章 MOS场效应晶体管

VT

MS

TOX

OX

QOX

TOX

OX

QAD 2FB

e) 氧化层中的电荷面密度 QOX

QOX 与制造工艺及晶向有关。MOSFET 一般采用(100) 晶面,并在工艺中注意尽量减小 QOX 的引入。在一般工艺条 件下,当 TOX = 150 nm 时:

QOX 1.8 ~ 3.0 V COX

以VGS 作为参变量,可以得到不同VGS下的VDS ~ID 曲线族, 这就是 MOSFET 的输出特性曲线。

非

饱

饱

和

和

区

区

将各条曲线的夹断点用虚线连接起来,虚线左侧为非饱和区, 虚线右侧为饱和区。

5、MOSFET的类型 P 沟 MOSFET 的特性与N 沟 MOSFET 相对称,即: (1) 衬底为 N 型,源漏区为 P+ 型。 (2) VGS 、VDS 的极性以及 ID 的方向均与 N 沟相反。 (3) 沟道中的可动载流子为空穴。 (4) VT < 0 时称为增强型(常关型),VT > 0 时称为耗尽型

MS

QOX COX

K

2FP VS VB

1

2 2FP VS

注意上式中,通常 VS > 0,VB < 0 。 当VS = 0 ,VB = 0 时:

VT

MS

QOX COX

K

2 FP

1 2

2FP

这与前面得到的 MOS 结构的 VT 表达式相同。

同理可得 P 沟 MOSFET的 VT 为:

电势差,等于能带弯曲量除以 q 。COX 表示单位面积的栅氧化

层电容,COX

OX

TOX

,TOX 为氧化层厚度。

(3)实际 MOS结构当 VG = VFB 时的能带图

电子管,晶体管,三极管,场效应管,MOS以及CMOS的区别和联系

电子管,晶体管,三极管,场效应管,MOS以及CMOS的区别和联系

电子管:一种在气密性封闭容器中产生电流传导,利用电场对真空中的电子流的作用以获得信号放大或振

荡的电子器件,常用于早期电子产品中。

晶体管(transistor):一种固体半导体器件,可以用于检波、整流、放大、开关、稳压、信号调制和许多其它功能。

晶体管作为一种可变开关,基于输入的电压,控制流出的电流,因此晶体管可做为电流的开关,和一般机械开关(如Relay、switch)不同处在于晶体管是利用电讯号来控制,而且开关速度可以非常

之快,在实验室中的切换速度可达100GHz以上。

电子管与晶体管代表了电子元器件发展过程中的两个阶段:电子管——晶体管——集成电路。

电子管可分为电子二极管,电子三极管等,晶体管也分为半导体二极管,半导体三极管等。

三极管:半导体三极管的简称,是一种电流控制型半导体器件,由多子和少子同时参与导电,也称双极型

晶体管(BJT)或晶体三极管。

场效应管(FET):Field Effect Transistor,一种电压控制型半导体器件,由多数载流子参与导电,也称为单极

型晶体管。

MOS:场效应管的一种。

CMOS:互补金属氧化物半导体,是一种类似MOS管设计结构的多MOS结构组成的电路,是一种由无数

电子元件组成的储存介质。

mos场效应晶体管

mos场效应晶体管

Mos场效应晶体管是一种由晶体管和一组极性电极组成的可控制的电晶体元件,它的构造有着三个基本构元:主要是活塞片,源极和漏极。

Mos场效应晶体管是半导体电子器件中的重要一部分,它由两个栅极桥式构成,由垂直排列的源极,漏极,活塞片和双栅极构成,通过改变活塞片的位移来改变电路参数,以实现对电路的控制,是工业等领域应用十分广泛的半导体元件。

它具有较低的截止电压,低风险,高稳定性,低功耗,高可靠性等优点,适用于低功耗、放大、抑制、调节等电路应用。

场效应晶体管的工作原理

由于栅极与P 区相连,所以,两个PN结都加上了反向电压,只有极微小电流流出栅极。由于漏极和源极都和N区相连,漏、源极之间加正向电压之后,在栅极电压负值不大时,源极之间有漏极电流,D流过,它是由N区中多数载流子(电子)形成的。

当PN结施加反向电压时(P接负极,N接正极),耗尽区就会向半导体内部扩展,使耗尽变宽,使耗尽区里的空间电荷增多。这种扩展,如果N区杂质浓度高于P区,主要在P区进行晶体管的工作原理如图73所示。它是在一块低掺杂的N型区两边扩散两个高掺杂的P型区,形成两个PN结,一般情况下N区比较薄。N区两端的两个电极分别叫做漏极(用字母D表示)和源极(用字母S表示),P 区引出的电极叫做栅极(用字母G表示)。

场效应晶体管的工作原理

场效应晶体管是受电场控制的半导体器件,而普通晶体管的工作是受电流控制的。场效应晶体管主要有结型场效应晶体管和金属氧化物半导体场效应晶体管(通常称MOS型)两种类型。两种管子工作原理不同,但特性相似。

1.结型场效应晶体管的工作原理

与普通结型晶体管一样,结型场效应晶体管的基本结构也是PN结。N型半导体与P型半导体形成PN结时,N区电子很多,空穴很少,而P区空穴很多,电子很少,因此在PN结交界处,N区电子跑向P区,P区空穴跑向N区。这样,在N区留下的是带正电的施主离子,在P区留下的是带负电的受主离子。这一区域内再也没有自由电子或空穴了,故称为“耗尽区”或“耗尽层”,又称空间电荷区

更多电子元件资料

由于P N结的耗尽区大部分在N区,当加上反向电压时,耗尽区主要向N区扩展。电压愈高,两个耗尽区之间电流可以通过的通道(常称为沟道)就愈窄,所以加在栅极与源极之间的负电压越大,两个耗尽区变得越厚,夹在中间的沟道就越薄,从而使沟道的电阻增大,漏电流ID减小;反之ID增大。漏极电流ID的大小会随栅、源之间的电压UGS大小而变,也就是说,栅、源电压US能控制漏电流ID,这就是结型场效晶体管的工作原理。需要着重指出的是,它是用电压来控制管子工作的。前面讲的是两个P 区夹着一个薄的N区形成的结型场效应晶体管,称为N沟道结型场效应晶体管。同样,用两个矿区夹着一个薄的P区就形成P沟道结型场效应晶体管,但是它的正常电压与N区沟道管子相反。

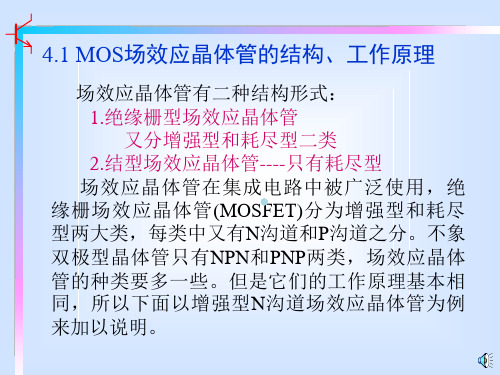

4.1MOS场效应晶体管结构工作原理

绝缘栅型场效应三极管MOSFET( Metal Oxide Semiconductor FET)。分为

增强型 N沟道、P沟道 耗尽型 N沟道、P沟道

N沟道增强型MOSFET 的结构示意图和符号见图 4.1。其中: D(Drain)为漏极,相当c; G(Gate)为栅极,相当b; S(Source)为源极,相当e。

在。

S GD

IDSS

ID /m A

6

D

5 IDSS

+++++++++

SiO2

夹断电压

4

N+

N+

G

B

3

2

P 型衬底

S

1

B

4 3 2 1 U G S (off)

0

U GS/V

当UGS=0时,对应的漏极电流用IDSS表示。当UGS>0时,将使ID进一 步增加。UGS<0时,随着UGS的减小漏极电流逐渐减小,直至ID=0。对 应ID=0的UGS称为夹断电压,用符号UGS(off)表示,有时也用UP表示。N沟 道耗尽型MOSFET的转移特性曲线如右上图所示。

从N型区引出电极,一个是漏极

D,一个是源极S。

D

D

在源极和漏极之间的绝缘层上镀

一层金属铝作为栅极G。

G

B G

B

N沟道增强型MOSFET的符号如

左图所示。左面的一个衬底在内部与

S

S

源极相连,右面的一个没有连接,使

用时需要在外部连接。 动画2-3

2 N沟道增强型MOSFET的工作原理

对N沟道增强型MOS场效应三极管的工作原理,分两个方面进行

可变I电D/ 阻m A区

MOS管参数详解和驱动电阻选择

MOS管参数详解和驱动电阻选择MOS管,全名金属氧化物半导体场效应晶体管(Metal-Oxide-Semiconductor Field-Effect Transistor),是一种广泛应用于电子电路中的晶体管。

它具有低功耗、高开关频率、低电压驱动、高噪声抑制等特点,常被用作功率放大器和开关。

下面将详细解析MOS管的一些重要参数及其影响,以及驱动电阻的选择。

1. 阈值电压(Threshold Voltage):阈值电压是指当MOS管工作在放大区时,控制电压达到的临界值。

它决定了MOS管的导通条件,越小表示MOS管对控制电压的敏感度越高。

2. 栅极电容(Gate Capacitance):栅极电容是指栅极和源极之间的电容。

它是MOS管的核心特性之一,决定了MOS管的响应速度。

栅极电容越小,MOS管的开关速度越快。

3. 输出电容(Output Capacitance):输出电容是指输出端和源极之间的电容。

它是MOS管的另一个重要特性,影响MOS管的开关频率和功耗。

输出电容越大,MOS管的开关频率越低,功耗越大。

4. 导通电阻(On-Resistance):导通电阻是指MOS管导通时的电阻值。

它是MOS管的一个重要参数,影响功率损耗和效率。

导通电阻越小,MOS管的功率损耗和热量损失越小。

5. 驱动电阻(Drive Resistance):驱动电阻是指用于驱动MOS管的电路中的电阻。

驱动电阻的选择对MOS管的性能和可靠性至关重要。

一般来说,驱动电阻不能过大,以保证MOS管在短时间内能够迅速充放电,提高开关速度;同时也不能过小,以避免过大的电流流过驱动电路,降低效率。

在选择驱动电阻时,需要考虑以下几个因素:1.驱动电压:驱动电阻的阻值应根据MOS管的驱动电压来确定。

一般来说,驱动电阻的阻值应小于MOS管的输入电阻,以确保能够提供足够的电流来驱动MOS管。

2.驱动能力:驱动电阻应具有足够的驱动能力,即能够提供足够的电流来驱动MOS管的栅极。

mos管欧姆区,饱和区,截止区

mos管欧姆区,饱和区,截止区

MOS管是金属氧化物半导体场效应晶体管的简称,它是一种重

要的半导体器件。

MOS管的工作可以分为三个区域,欧姆区、饱和

区和截止区。

首先,让我们来谈谈欧姆区。

在MOS管中,当栅极对终端施加

一个电压时,如果电压不足以形成漏极和源极之间的导通通道,此

时MOS管处于欧姆区。

在欧姆区,MOS管的导通电阻很大,电流流

动受到限制。

其次是饱和区。

当栅极电压增加,足以形成漏极和源极之间的

导通通道时,MOS管就进入了饱和区。

在饱和区,MOS管的导通电阻

较小,电流可以自由地通过MOS管。

最后是截止区。

当栅极电压继续增加,达到一定数值时,MOS

管就会进入截止区。

在截止区,MOS管完全关闭,导通电阻非常大,电流无法通过MOS管。

总的来说,MOS管的欧姆区、饱和区和截止区分别对应着不同

的工作状态,这些状态取决于栅极电压和漏极-源极之间的电压。

了

解MOS管的这三个区域对于理解MOS管的工作原理和应用具有重要意义。

希望这些信息能够帮助你更好地理解MOS管的工作原理。

mos管并联二极管

mos管并联二极管

MOS管(金属氧化物半导体场效应晶体管)和并联二极管是电子电路中常用的元件,它们在不同的应用中具有各自的特点和作用。

当这两者并联时,可以发挥一些独特的功能。

1. MOS管(金属氧化物半导体场效应晶体管):

MOS管是一种半导体器件,它由金属氧化物层和半导体材料组成。

它具有较高的输入阻抗、低的输出阻抗和较大的放大能力。

MOS 管适用于信号放大、开关和数字电路等应用。

2. 并联二极管:

并联二极管是将两个或多个二极管连接在一起形成并联电路。

这种连接方式可以改变整体电性能,并提供更大的电流和低于单个二极管的电阻值。

并联二极管广泛应用于电源、市电修正、电压稳定器等电路中。

当MOS管和并联二极管相互连接时,有以下几种常见的应用:

3. 稳压电路:

MOS管可以通过调节其栅极电压来实现对并联二极管的控制,从而实现稳压功能。

当负载电压变化时,MOS管的栅极电压相应调节,以保持输出电压的稳定性。

4. 整流电路:

将MOS管和并联二极管相结合的整流电路可以实现高效的电压整流功能。

通过MOS管的控制,可以改变二极管的通断状态,从而实现有效的电压转换和整流效果。

5. 开关电路:

结合MOS管和并联二极管可以构建可靠的开关电路。

MOS管负责控制电路的通断状态,而并联二极管则起到辅助稳定电流和保护元件的作用。

总体而言,将MOS管和并联二极管结合可以实现多种电路功能,如稳压、整流和开关等。

通过合理的电路连接和控制,可以充分利用它们各自的特点,实现电子电路中的各种需求。

二维mos场效应晶体管的结构

二维mos场效应晶体管(二维MOSFET)作为一种重要的半导体器件,具有结构简单、成本低廉、功耗小、速度快等优点,在电子行业得到广泛应用。

其结构设计和制造工艺对器件性能有着重要的影响。

本文将介绍二维MOSFET的结构设计及相关特点。

二、二维MOSFET的结构1. 二维MOSFET的基本结构二维MOSFET是由衬底、栅极、绝缘层和沟道层组成的。

衬底通常为p型或n型半导体材料,而栅极通常是金属或多晶硅制成的。

绝缘层位于衬底上,用于隔离栅极与衬底,常见的材料包括氧化硅或氮化硅。

沟道层是二维材料,如石墨烯或硅基石墨烯,用于传输载流子。

2. 二维MOSFET的工作原理当在栅极上施加正电压时,栅极下方的绝缘层中会形成正电荷,吸引衬底中的自由电子或空穴移动至沟道层,形成导通通道。

当施加负电压或不施加电压时,形成截至通道,器件关闭。

三、二维MOSFET的特点1. 尺寸小由于二维MOSFET采用了二维材料作为沟道层,其尺寸相比传统MOSFET得到了极大的缩小,可实现微米甚至纳米级的尺寸。

二维材料具有高载流子迁移率,使得二维MOSFET具有较快的开关速度和传输速度,适合高频应用。

3. 低功耗由于二维MOSFET的结构精简,功耗较低,可有效降低设备使用过程中的能量消耗。

4. 制造成本低制备二维材料的成本相对较低,而且制造工艺相对简单,使得二维MOSFET的制造成本大大降低。

4. 对二维材料的要求二维MOSFET对沟道层的材料要求严格,需要具有高载流子迁移率、较大电子迁移长度等特性。

目前广泛应用的二维材料包括石墨烯和硅基石墨烯。

五、结论二维MOSFET作为一种新型的场效应晶体管,具有结构简单、速度快、功耗低等优点,成为未来半导体器件行业的研究热点之一。

在实际应用中,对二维材料的研究和制备工艺的不断改进将进一步推动二维MOSFET技术的发展。

二维MOSFET的结构设计和制造工艺对其性能具有重要影响。

随着二维材料领域的不断创新和发展,相信二维MOSFET将在未来的电子器件领域大放异彩。

场效应管和mos管的区别综述

功率场效应晶体管MOSFET1.概述MOSFET的原意是:MOS(Metal Oxide Semiconductor金属氧化物半导体),FET(Field Effect Transistor场效应晶体管),即以金属层(M)的栅极隔着氧化层(O)利用电场的效应来控制半导体(S)的场效应晶体管。

功率场效应晶体管也分为结型和绝缘栅型,但通常主要指绝缘栅型中的MOS型(Metal Oxide Semiconductor FET),简称功率MOSFET(Power MOSFET)。

结型功率场效应晶体管一般称作静电感应晶体管(Static Induction Transistor——SIT)。

其特点是用栅极电压来控制漏极电流,驱动电路简单,需要的驱动功率小,开关速度快,工作频率高,热稳定性优于GTR,但其电流容量小,耐压低,一般只适用于功率不超过10kW的电力电子装置。

2.功率MOSFET的结构和工作原理功率MOSFET的种类:按导电沟道可分为P沟道和N沟道。

按栅极电压幅值可分为;耗尽型;当栅极电压为零时漏源极之间就存在导电沟道,增强型;对于N(P)沟道器件,栅极电压大于(小于)零时才存在导电沟道,功率MOSFET主要是N沟道增强型。

2.1功率MOSFET的结构功率MOSFET的内部结构和电气符号如图1所示;其导通时只有一种极性的载流子(多子)参与导电,是单极型晶体管。

导电机理与小功率MOS管相同,但结构上有较大区别,小功率MOS管是横向导电器件,功率MOSFET大都采用垂直导电结构,又称为VMOSFET (Vertical MOSFET),大大提高了MOSFET器件的耐压和耐电流能力。

按垂直导电结构的差异,又分为利用V型槽实现垂直导电的VVMOSFET和具有垂直导电双扩散MOS结构的VDMOSFET(Vertical Double-diffused MOSFET),本文主要以VDMOS 器件为例进行讨论。

MOS场效应晶体管ppt课件

16

2. MOS管的基本工作原理

MOS 场效应晶体管的工作原理示意图

17

4.2.2 MOS 场效应晶体管的转移特性

MOS 场效应晶体管可分为以下四种类型:N沟增强型、 N沟耗尽型、P沟增强型、P沟耗尽型。 1. N沟增强型MOS管及转移特性

18

2. N沟耗尽型MOS管及转移特性 3.P沟增强型MOS管及转移特性

理想 MOS 二极管不同 偏压下的能带图及 电荷分布

a) 积累现象 b) 耗尽现象 c) 反型现象

3

2.表面势与表面耗尽区 下图给出了P型半导体MOS结构在栅极电压UG>>0情况 下更为详细的能带图。

4

在下面的讨论中,定义与费米能级相对应的费米势为

F

(Ei

EF )体内 q

因此,对于P型半导体, F

如图所示,当漏源电压UDS增高到某一值时,漏源电流 就会突然增大,输出特性曲线向上翘起而进入击穿区。 关于击穿原因,可用两种不同的击穿机理进行解释:漏 区与衬底之间PN结的雪崩击穿和漏-源之间的穿通。

41

1. 漏区-衬底之间的PN结击穿 在MOS晶体管结构中,栅极金属有一部分要覆盖在漏极上。 由于金属栅的电压一般低于漏区的电位,这就在金属栅极 与漏区之间形成附加电场,这个电场使栅极下面PN结的耗 尽区电场增大,如下图,因而使漏源耐压大大降低。

a) N 沟 MOS b) P 沟 MOS

29

3. 衬底杂质浓度的影响

衬底杂质浓度对阀值电压的影响

30

4. 功函数差的影响

功函数差也将随衬底杂质浓度的变化而变化。但实验证明, 该变化的范围并不大。 从阀值电压的表示式可知,功函数越大,阀值电压越高。 为降低阀值电压,应选择功函数差较低的材料,如掺杂多 晶体硅作栅电极。

MOS 场效应晶体管

工作原理

mosfet通过在金属-氧化物-半导 体结构上施加电压,控制电子流动, 实现信号放大和开关作用。

结构

mosfet由栅极、源极、漏极和半导 体层组成,具有对称的结构。

mos 场效应晶体管的应用

集成电路

mosfet是集成电路中的基本元件, 广泛应用于数字电路和模拟电路 中。

工作原理概述

电压控制

导电通道的形成与消失

mos场效应晶体管是一种电压控制器 件,通过在栅极施加电压来控制源极 和漏极之间的电流流动。

随着栅极电压的变化,导电通道的形 成与消失,从而控制源极和漏极之间 的电流流动。

反型层

当在栅极施加正电压时,会在半导体 表面产生一个反型层,使得源极和漏 极之间形成导电通道。

电压与电流特性

转移特性曲线

描述栅极电压与漏极电流之间关 系的曲线。随着栅极电压的增加, 漏极电流先增加后减小,呈现出

非线性特性。

跨导特性

描述源极电压与漏极电流之间关 系的曲线。跨导反映了mos场效

应晶体管的放大能力。

输出特性曲线

描述漏极电压与漏极电流之间关 系的曲线。在一定的栅极电压下, 漏极电流随着漏极电压的增加而

增加,呈现出线性特性。

Part

03

mos 场效应晶体管的类型与 特性

nmos 场效应晶体管

总结词

NMOS场效应晶体管是一种单极型晶体管,其导电沟道由负电荷主导。

详细描述

NMOS场效应晶体管通常由硅制成,其导电沟道由负电荷主导,因此被称为 NMOS。在NMOS中,电子是主要的载流子,其源极和漏极通常为n型,而衬 底为p型。

制造工艺中的挑战与解决方案

1 2 3

mos管体效应

mos管体效应

回答:

MOS管是一种常用的场效应晶体管,其主要特点是具有高输入阻抗、低噪声、低失真等优点。

MOS管的体效应是指在MOS管的工作过程中,由于沟道中的电子密度变化而引起的电场效应。

MOS管的结构包括一个金属栅极、一个绝缘层和一个半导体沟道。

当栅极施加正电压时,栅极和沟道之间的电场会引起沟道中的电子密度变化。

由于沟道中的电子密度变化,沟道中的电场也会发生变化,从而影响MOS管的输出特性。

MOS管的体效应主要包括两个方面:沟道长度调制效应和沟道宽度调制效应。

沟道长度调制效应是指在MOS管的工作过程中,由于沟道长度的变化而引起的电场效应。

当栅极施加正电压时,沟道中的电子密度会发生变化,从而引起沟道长度的变化。

沟道长度的变化会影响沟道中的电场分布,从而影响MOS管的输出特性。

沟道宽度调制效应是指在MOS管的工作过程中,由于沟道宽度的变化而引起的电场效应。

当栅极施加正电压时,沟道中的电子密度会发生变化,从而引起沟道宽度的变化。

沟道宽度的变化会影响沟道中的电场分布,从而影响MOS管的输

出特性。

MOS管的体效应对MOS管的输出特性有很大的影响。

在MOS管的设计和制造过程中,需要考虑体效应的影响,以提高MOS管的性能和可靠性。

mos场效应管制作工艺的基本步骤

一、介绍mos场效应管MOS场效应管(Metal-Oxide-Semiconductor Field-Effect Transistor,简称MOSFET)是一种常用的场效应晶体管,被广泛应用于集成电路和功率放大器中。

它具有高输入电阻、低噪声系数、高频率特性和较高的可靠性,因此在电子行业中拥有广泛的应用。

二、MOS场效应管的制作工艺1. 基础工艺准备MOS场效应管的制作首先需要准备硅衬底,通常是n型或p型硅衬底。

在准备硅衬底之前,需要对硅片进行清洗、抛光和去除常见的杂质和附着物,以确保硅衬底表面的光洁度和平整度。

2. 渗透层制备接下来是为了增强氧化层和MOS栅极的定位而形成的渗透层的制备。

渗透层主要由P型或N型多晶硅薄膜组成,其厚度通常在200-300nm之间。

3. 氧化层生长氧化层的生长通常使用干法氧化或湿法氧化的方法。

干法氧化是通过高温下氧化气体的作用,在硅表面生长出氧化层;湿法氧化则是在加热的气氛中,采用水蒸气和氧气混合气体生长氧化层。

氧化层的厚度通常在20-300nm之间。

4. 光刻工艺在氧化层上,在所需要的位置上,通过光刻胶技术进行图案设计,然后投射紫外光,再通过显影和蚀刻等工艺将所需的图案转移到氧化层上。

5. 栅极制备在光刻工艺过程中形成的图案将作为掩膜,用于栅极的形成。

通常使用富勒烯等材料来用于栅极的制备。

6. 接触沟槽制备通过刻蚀技术,形成MOSFET的接触沟槽。

接触沟槽是用于源漏掺杂(通常为N+或P+掺杂)的区域。

7. 接触金属制备在接触沟槽中形成接触金属,通常使用铝或金属合金作为接触金属。

这一步骤需要经过金属蒸发或其他金属沉积工艺。

8. 清洗和退火对制备好的MOSFET晶体管进行清洗和热退火处理,来确保晶体管的结构完整和性能稳定。

三、总结MOS场效应管的制作工艺是一个复杂而精细的过程,需要多种材料和工艺的结合。

它的制备包括了硅片准备、渗透层制备、氧化层生长、光刻工艺、栅极制备、接触沟槽制备、接触金属制备和清洗和退火等基本步骤。

半导体器件物理_chapter5_MOS场效应晶体管讲解

MOS场效应晶体管是四端器件。

D(Drain)为漏极,相当c; G(Gate)为栅极,相当b; S(Source)为源极,相当e。 B(substrate),衬底极。 通常接地,有时为了控制电流或由

于电路结构的需要,在衬底和源之 间也加一个小偏压(VBS)。 若栅极材料用金属铝,则称“铝栅”器件;

当VG较小时,表面处的能带 只是略微向下弯曲,使表面费 米能级EF更接近本征费米能级 Ei,空穴浓度减少,电子浓度 增加,但与电离受主的空间电 荷相比仍较少,可忽略。

VG继续增大,使表面费米能级 EF与本征费米能级Ei时,表面电 子浓度开始要超过空穴浓度,

表面将从P型转为N型,称为

“弱反型”。发生弱反型时,

2、MIS结构

(1) 表面空间电荷层和反型层 表面空间电荷层和反型层实际上属于半导体表面

的感生电荷。 MIS结构上加电压后产生感生电荷的四种情况。

以P半导体的MIS结构为例。

• 当栅上加负电压,所产生的感生电荷是被吸引到表面的多子 (空穴),在半导体表面形成积累层。

• 当栅上加正电压,电场的作用使多数载流子被排斥而远离表 面,从而在表面形成由电离受主构成的空间电荷区,形成耗 尽层。此时,虽然有少子(电子)被吸引到表面,但数量很 少。这一阶段,电压的增加只是使更多的空穴被排斥走,负 空间电荷区加宽。

• 随着正电压的加大,负电荷区逐渐加宽,同时被吸引到表面 的电子也随着增加。当电压达到某一“阈值”时,吸引到表 面的电子浓度迅速增大,在表面形成一个电子导电层,即反 型层。反型层出现后,再增加电极上的电压,主要是反型层 中的电子增加,由电离受主构成的耗尽层电荷基本不再增加。

(2) 形成反型层的条件

式中QB为强反型时表面区的耗尽层电荷密度,Cox为MIS结构 中一绝缘层为电介质的电容器上的单位面积的电容:

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

Slide 6-14

6.3.3 HEMT, High Electron Mobility Transistor

N-GaAlAs

source

N

+

metal gate

drain

N

+

….......

Modern Semiconductor Devices for Integrated Circuits (C. Hu)

Slide 6-13

6.3.2 GaAs MESFET

source

+

gate

metal N-channel

drain

+

N

N

GaAs

Semi-insulating substrate

MESFET IV characteristics are similar to MOSFET’s but does not require a gate oxide. Question: What is the advantage of GaAs FET over Si FET?

Terms: depletion-mode transistor, enhancement-mode transistor

Modern Semiconductor Devices for Integrated Circuits (C. Hu)

Slide 6-5

6.2 MOSFETs Technology

Polysilicon gate and 1.2nm SiO2

•1.2 nm SiO2 used in production. Leakage current through the oxide limits further thickness reduction.

Chapter 6 MOSFET

The MOSFET (MOS Field-Effect Transistor) is the building block of Gb memory chips, GHz microprocessors, analog, and RF circuits. Match the following MOSFET characteristics with their applications: • small size • high speed • low power • high gain

Modern Semiconductor Devices for Integrated Circuits (C. Hu)

Slide 6-16

6.4 Vt and Body Effect

How to Measure the Vt of a MOSFET

A B

•Method A. Vt is measured by extrapolating the Ids versus Vgs curve to Ids = 0. W I dsat = Coxe (Vgs - Vt ) m nsVds Vgs - Vt •Method B. The Vg at which Ids =0.1mA W/L

(b)

NFET

N+

0V (c) • basic layout of a CMOS inverter

Modern Semiconductor Devices for Integrated Circuits (C. Hu)

Slide 6-9

6.3 Surface Mobilities and High-Mobility FETs

From Gauss’s Law,

Eb = – Qdep/es

Vt = V fb st - Qdep / Coxe

Therefore,

Eb = Coxe

es

(Vt - V fb - st ) Coxe (Vgs - Vt ) C 1 Et ) = oxe (Vgs Vt - 2V fb - 2 st ) ( Eb 2e s 2 =

Modern Semiconductor Devices for Integrated Circuits (C. Hu)

Slide 6-7

CMOS (Complementary MOS) Inverter

Vd d

PFET S D D S NFET 0V

Vin

Vo ut C:

capacitance (of interconnect, 0 V etc.)

Wd max

Qinv = -Coxe (Vgs - Vt ) CdepVsb

Coxe

= -Coxe (Vgs - (Vt

• Redefine Vt as

Cdep Coxe

Vsb ))

Cdep

Vt (Vsb ) = Vt 0

Cdep Coxe

Vsb = Vt 0 Vsb

Modern Semiconductor Devices for Integrated Circuits (C. Hu)

Et = -(Qdep Qinv ) / e s = Eb - Qinv / e s = Eb = Coxe

es

es

(Vgs - V fb - st )

Coxe (Vgs Vt 0.2 V) 2e s Vgs Vt 0.2 V

6Toxe

Slide 6-11

Modern Semiconductor Devices for Integrated Circuits (C. Hu)

A CMOS inverter is made of a PFET pull-up device and a (a) NFET pull-down device. Vout = ? if Vin = 0 V.

Modern Semiconductor Devices for Integrated Circuits (C. Hu)

Modern Semiconductor Devices for Integrated Circuits (C. Hu)

Slide 6-6

6.2 Complementary MOSFETs Technology

NFET PFET

When Vg = Vdd , the NFET is on and the PFET is off. When Vg = 0, the PFET is on and the NFET is off.

Modern Semiconductor Devices for Integrated Circuits (C. Hu)

Slide 6-15

6.3.4 JFET

source

+

P+ gate

drain

+

N

N-channel

N

P-Si

•The gate is a P+N junction.

•The FET is a junction field-effect transistor (JFET).

6.3.1 Surface Mobilities

Vg = Vdd , Vgs = Vdd

Vds > 0

Ids

How to measure the surface mobility:

I ds = W × Qinv × v = WQinv m nsE = WQinv m nsVds / L = WCoxe (Vgs - Vt ) m nsVds / L

Modern Semiconductor Devices for Integrated Circuits (C. Huon the Field-Effect Transistor

In 1935, a British patent was issued to Oskar Heil. A working MOSFET was not demonstrated until 1955. Using today’s terminology, what are 1, 2, and 6?

Slide 6-18

MOSFET Vt and the Body Effect

• Body effect: Vt is a function of Vsb. When the source-body junction is reverse-biased, Vt increases.

Slide 6-8

CMOS (Complementary MOS) Inverter

Vdd

Contact P+

Vin 0V

P+ N+

Vout

N+ P+

V dd

P+ N+

N-well

PFET

N-well

Vin Vout

P-substrate

• NFET and PFET can be fabricated on the same chip.

Modern Semiconductor Devices for Integrated Circuits (C. Hu)

Slide 6-1

6.1 Introduction to the MOSFET

Basic MOSFET structure and IV characteristics

+

+

Modern Semiconductor Devices for Integrated Circuits (C. Hu)

(Vgs Vt 0.2) / 6Toxe = 1.5 V / 1210-7 cm = 1.25 MV/cm