模拟cmos集成电路设计(拉扎维)第2章MOS器件物理基础PPT课件

模拟集成电路课件 第2章CMOS技术

无源元件的温度特性通常用温度比例系数 TCF来表示

X是无源元件的电阻或电容 通常温度比例系数乘106,用每度百万分之几(即ppm/℃)为单 位 MOS器件的特性与温度之间的关系由公式可以看出,

vGS vT 0 0 vDS vGS VT 0 vGS VT vDS

Bi-CMOS工艺

Bi-CMOS同时包括双极和MOS晶体管的集成电路,它结 合了双极器件的高跨导、强驱动能力和CMOS器件的高 集成度、低功耗的优点,使它们互相取长补短、发挥 各自优点,制造高速、高集成度、性能好的 VLSI。

第2章CMOS技术

1.CMOS制造工艺 2.MOS器件的工作原理 3.MOS无源元件 4.CMOS技术的其他考虑

特点:寄生参量小,精度高。

金属-氧化物-多晶硅

第2章CMOS技术

1.CMOS制造工艺 2.MOS器件的工作原理 3.MOS无源元件 4.CMOS技术的其他考虑

4.CMOS技术的其他考虑

CMOS电路的闩锁(Latch-up)效应 MOS器件的温度特性 噪声

背栅效应 沟道长度调制效应 亚阈值特性 短沟效应

MOS管的阈值电压

VT是MOS晶体管的一个极其重要的参数

VT可在制造过程中加以控制

阈值电压大小取决于: 栅极材料 栅极绝缘材料 栅极绝缘层厚度

沟道掺杂浓度 源极与衬底之间电压 环境温度:随温度升高而降低 调节阈值电压大小方法: 用离子注入法改变沟道掺杂浓度 采用不同栅极绝缘材料

源/漏离子注入电阻

薄层电阻Rs在500—2000Ω/口 绝对误差精度土15% 相对误差2%(5μm)0.15%( 50 μm ) 温度系数400ppm/℃ 电压系数800ppm/V

南邮拉扎维模拟cmos前两章课件

其中, 2qsi Nsub / COX ,称为体效应系数

沟道长度调制效应

描述: 当栅漏之间的电压差增大时,实际的反型沟道长度逐渐减小。

由式

ID

1 2

nCOX

W L

(VGS

VTHΒιβλιοθήκη )2可知,L是

VDS

的函数

,即上述的沟道长度调制效应

若定义 L L L(L 较小)且L / L 和VDS 之间的关系是线性的,则

ID

1 2

nCOX

W L

(VGS

VTH

)2 (1 VDS )

是沟道长度调制系数,表示给定的 VDS 增量所引起的沟道长度的相对变化量

COX W (VGS VTH )

(b) VDS 0

时,源漏存在电压差,因此,

沿沟道x点处的电荷密度为

Qd (x) COX W (VGS VTH V (x))

I D WC OX [VGS VTH V (x)]

ID

WCOX [VGS

VTH

V (x)]n

dV (x) dx

对应的边界条件为 V (0) 0,V (L) VDS ,两边积分得

• 模拟电路对噪声、串扰和其他干扰比数字电路要敏感的多。

• 器件的二级效应对模拟电路的影响比数字电路要严重的多。

• 高性能模拟电路的设计很少能自动完成,而许多数字电路都 是自动综合和布局的。

• 模拟电路的许多效应的建模和仿真仍然存在问题,模拟设计 需要设计者利用经验和直觉来分析仿真结果。

拉扎维模拟CMOS集成电路设计(前十章全部课件)

重邮光电工程学院

考虑沟道调制效应后的跨导gm

λ ∝1/L ∂ID/∂VDS∝ λ /L∝1/L2

W gm nCox (VGS VTH )(1 VDS) L gm 2nCox W L I D

(1 VDS)

2 ID , (unchanged) gm VGS VTH

重邮光电工程学院

模拟CMOS集成电路设计

[美] 理查德· 拉扎维 著

西安交通大学出版社

©2003

重邮光电工程学院

第一章

模拟集成电路设计绪论

模拟集成电路设计绪论 Ch.1# 2

重邮光电工程学院

自然界信号的处理

高速、高精度、低功耗ADC的设 计是模拟电路设计中的难题之一

高性能放大器和滤波器 设计也是热点研究课题

沟道未夹断条件

边界条件:V(x)|x=0=0, V(x)|x=L=VDS

模拟集成电路设计绪论 Ch. 1 # 9

重邮光电工程学院

NMOS沟道电势示意图(2)

dq(x) CoxWdx[vGS v (x) VTH ]

边界条件:V(x)|x=0=0, V(x)|x=L=VDS

模拟集成电路设计绪论 Ch. 1 # 10

传送端 接收端

模拟集成电路设计绪论 Ch.1# 5

重邮光电工程学院

磁盘驱动电子学

存储数据

恢复数据

硬盘存储和读出后的数据

模拟集成电路设计绪论 Ch.1# 6

重邮光电工程学院

无线接受机

无线接收天线接收到的信号(幅度只有几微伏)和噪声频谱 接收机放大低电平信号时必须具有极小噪 声、工作在高频并能抑制大的有害成分

模拟设计困难的原因是什么(1)?

模拟集成电路设计ch2 MOS器件物理基础

Ch. 2 # 7

Design of Analog CMOS Integrated Circuits

例:判断制造下列电路的衬底类型

Ch. 2 # 8

2.2.1 NMOS器件的阈值电压VTH

(a)栅压控制的MOSFET,栅 和衬底形成一个电容器

(b) VG 增大,P衬底中的空穴被赶离 栅区而留下负离子,形成耗尽区

当VG大到一定程 度时,电子被吸引到 界面处,形成导电沟 道(反型层) (c)反型的开始 (d)反型层的形成 VTH定义为表面电子浓度等于衬底多子浓度时的VG Ch. 2 # 11

Ch. 2 # 12

Design of Analog CMOS Integrated Circuits

阈值电压VTH的调整

MOS管导通,VGS>VTH,若 VTH=0,则MOS不关断

在器件制造过程中,通过向沟 道区注入杂质来调整阈值电压 VTH0 ,即改变氧化层界面附近 衬底的掺杂浓度。 但工艺确定后,VTH0确定,设 计者无法改变

Design of Analog CMOS Integrated Circuits

2.1.3 MOS符号

四端器件,模拟设计中 常用,需明确B端连接

当B、S短接时,省掉B端

数字电路用,只需 区别MOS管类型

NMOS器件B接地,PMOS器件B接VDD MOS器件具有高输入阻抗 一般源漏对称,怎样区分?

推导时沟道未夹断:

VGD =VGS -VDS≥VTH ⇒ VDS≤VGS -VTH

Ch. 2 # 23

拉扎维模拟cmos集成电路课件Lecture_2

diff

0

I dx W Dn

0

L

Q dQCS dx W dx

QD

kT q dQC

QC QS

I D I0 e

VGS q kT

There is no “simple” expression for the “moderate inversion” region.

4

In weak inversion, the diffusion term dominates over the drift term.

I diff W Dn

dQC kT dQ W C dx q dx

In weak inversion

L

QC exp(qV GB VCB / kT )

7

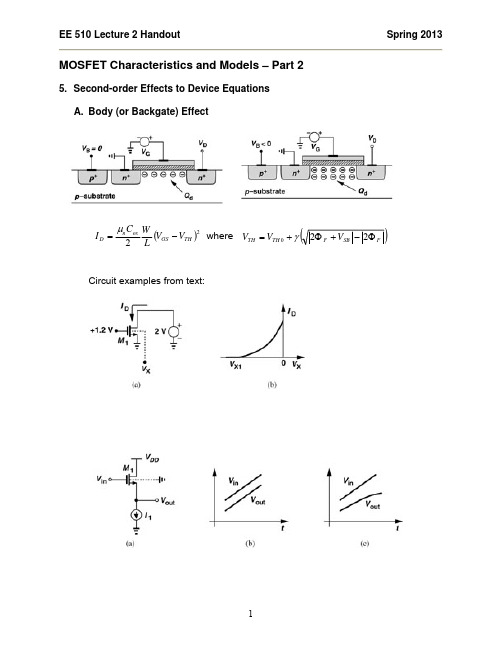

EE 510 Lecture 2 Handout

Spring 2013

For the output resistance in saturation

i gO D vDS

gO ID

Q

2 W VGS VTH 1 gO n Cox 2 L

1 VDS

ID

For saturation operation:

i gm D vGS

Q

1 W vGS VTH iD n Cox 1 vDS L 2

2

1 V 2I D 2 W VGS VTH DS n Cox W I D gm nCox 1 V DS L L VGS VTH

EE 510 Lecture 2 Handout D. Short (deep submicron)-channel Effects (Note: Chapter 16 topic of your textbook.)

CMOS模拟集成电路的设计ch2器件物理课件

CMOS模拟集成电路的设计ch2器件物理

16

怎么判断MOSFET处在什么工作区?

方法一: 比较源漏电压 Vds和过饱和电 压Vsat的高低

方法二: (源极电压不 方便算出时) 比较栅极Vg和 漏端Vd的电压 高低

管 子 导 通 ,且 V D S V G S V T H 时 , 则 管 子 进 入 线 性 区 相 反 是 饱 和 区

模拟CMOS集成电路设 计

第 2 章 MOS器件物理基础

CMOS模拟集成电路的设计ch2器件物理

1

2.1 基本概念

漏(D: drain)、 栅(G: gate)、

G

源(S: source)、衬底(B: bulk)

S

MOSFET:一个低功耗、高效率的开关

CMOS模拟集成电路的设计ch2器件物理

2

MOS符号

变化的能力。反映了器件的灵敏度

——VGS对ID的控制能力CMO。S模拟集成电路的设计ch2器件物理

14

gm ID VGSVDScontsant

nCoxW L(VGSVTH)

2nCox

W L

ID

2ID VGS VTH

CMOS模拟集成电路的设计ch2器件物理

15

到此为止,我们已经学习了MOSFET的三种用途:

17

思考题 图中MOS管的作用是什么?应该工作在什么工作区?

CMOS模拟集成电路的设计ch2器件物理

18

即NMOS开关不能传递最高电位,仅对低电位是比较理想的开关 相对的,PMOS开关不能传递最低电位,仅对高电位是比较理想的开关

CMOS模拟集成电路的设计ch2器件物理

19

拉扎维模拟CMOS集成电路设计第二章作业答案详解完整版PPT课件

1 2

nCOX

W L

[2

0.2(VX

1) (VX

1)2

]

1 2

nCOX

W L

(1.4 VX )(VX

1)

gm

nCOX

W L

VDS

nCOX

W L

(Vx

1)

第8页/共37页

③ 当VX≥1.2V时,MOS管工作在饱和区

IX

+

IX

1 2

nCOX

W L

(VGS

VTH )2

1 2

nCOX

W L

(0.2)2

1.9V

+ VX

-

第14页/共37页

2.7 对于图2.44的每个电路,画出Vout关于

M1

Vin的函数曲线草图。Vin从0变化到

解(右aV:)图DλD=中=γ3=,V0。M, VOTSH管=0源.7V-漏极交换

Vin +

1V -

M1

• 当Vin<0.7V时,M1工作在截止区,

Vin

Vout=0

• 当0.7<Vin≤1.7V时,M1工作在饱和区,则

10k

gmro 1.96 103 10 103 19.6

第3页/共37页

• 2.3 导出用ID和W/L表示的gmro的表达式。画出以L

为参数的gmro~ID的曲线。注意λ∝L

解:

gm

2Cox

W L

ID

ro

1

ID

gmro

2Cox

W L

ID

1

ID

A

WL ID

第4页/共37页

2.4 分别画出MOS晶体管的ID~VGS曲线。a) 以VDS作

模拟CMOS集成电路设计(毕查德·拉扎维著,陈贵灿等译,西安交通大学出版社) 绪论课件

模拟CMOS集成电路设计教材n模拟CMOS集成电路设计,毕查德.拉扎维著,陈贵灿等译,西安交通大学出版社参考资料n半导体集成电路,朱正涌,清华大学出版杜n CMOS模拟电路设计(英文),P.E.Allen,D.R.Holberg,电子工业出版社n模拟集成电路的分析与设计,P.R.Gray等著,高等教育出版社半导体集成电路发展历史n1947年BELL实验室发明了世界上第一个点接触式晶体管(Ge NPN)半导体集成电路发展历史n1948年BELL 实验室的肖克利发明结型晶体管n1956年肖克利、布拉顿和巴丁一起荣获诺贝尔物理学奖n50年代晶体管得到大发展(材料由Ge→Si)半导体集成电路发展历史n1958年TI公司基尔比发明第一块简单IC。

n在Ge晶片上集成了12个器件。

n基尔比也因此与赫伯特·克勒默和俄罗斯的泽罗斯·阿尔费罗夫一起荣获2000年度诺贝尔物理学奖。

半导体集成电路发展历史n19世纪60年代美国仙童公司的诺依斯开发出用于IC的平面工艺技术,从而推动了IC制造业的大发展。

半导体集成电路发展历史n60年代TTL、ECL出现并得到广泛应用n1966年MOS LSI发明(集成度高,功耗低)n70年代MOS LSI得到大发展(出现集成化微处理器,存储器)n80年代VLSI出现,使IC进入了崭新的阶段。

n90年代ASIC、ULSI和巨大规模集成GSI等代表更高技术水平的IC 不断涌现,并成为IC应用的主流产品。

n21世纪SOC、纳米器件与电路等领域的研究已展开n展望可望突破一些先前认为的IC发展极限,对集成电路IC的涵义也将有新的诠释。

集成电路用半导体工艺,或薄膜、厚膜工艺(或这些工艺的组合),把电路的有源器件、无源元件及互连布线以相互不可分离的状态制作在半导体或绝缘材料基片上,最后封装在一个管壳内,构成一个完整的、具有特定功能的电路、组件、子系统或系统。

模拟集成电路n1967年国际电工委员会(IEC)正式提出模拟集成电路的概念,它包括了除逻辑集成电路以外的所有半导体集成电路。

CMOS模拟集成电路设计ch2器件物理 共42页

ID =0

6

2. 线性区 triode or linear region

当 V G S V T H ,且 V D S V G S V T H 时 MOSFET 处于线性区

7

Derivation of I/V Characteristics

I Qd v Q d W o(V x C G S V T)H Q d ( x ) W o ( V x G C V S ( x ) V T )H

1

ID

2L

25

亚阈值导电性(弱反型)

在初步分析MOSFET的时候,我们假设当VGS < VTH时, 器件会突然关断,即ID会立即减小到零;但实际上当VGS 略小于VTH 时,有一个“弱”的反型层存在,ID大小随

VGS下降存在一个“过程”,与VGS呈指数关系:

26

2.4 MOS器件电容

分析高频交流特性时 必须考虑寄生电容的影响 根据物理结构,可以把 MOSFET的寄生电容分为:

模拟CMOS集成电路设计

第 2 章 MOS器件物理基础

2.1 基本概念

漏(D: drain)、 栅(G: gate)、

G

源(S: source)、衬底(B: bulk)

S

MOSFET:一个低功耗、高效率的开关

D

2

MOS符号

模拟电路中常用符号

数字电路中常用

MOSFET是一个四端器件

3

2.2 MOS的I/V特性

2. 右图中MOSFET的过饱和电压是多少?管子处于什么工 作区?

R

Vb=1V

Vds=0.5V

40

3. 如图所示,Vin随时间线性增加。在不考虑沟调效应,需考 虑体效应的前提下,画出Vout随时间的曲线。

CMOS模拟集成电路设计 拉扎维课件

1st 代:MOS1,MOS2,MOS3; 2nd代:BSIM,HSPICE level=28,BSIM2 3rd代:BSIM3,MOS model9,EKV(Enz-Krummenacher-Vittoz)

目前工艺厂家最常提供的MOS SPICE模型为BSIM3v3 (UC Berkeley)

CMOS模拟集成电路设计

绪论、MOS器件物理基础

王永生 Harbin Institute of Technology Microelectronics Center

2009-1-16

提纲

2

提纲

1、绪论 2、MOS器件物理基础

HIT Microelectronics

王永生

2009-1-16

2.3.1体效应

对于NMOS,当VB<VS时,随VB下降,在没反型前, 耗尽区的电荷Qd增加,造成VTH增加,也称为“背栅 效应”

其中,γ为体效应系数

HIT Microelectronics

VTH 0

VTH

王永生

2009-1-16

MOS器件物理基础

15

2.3.2 沟道长度调制效应

当沟道夹断后,当VDS增大时,沟道长度逐渐减小, 即有效沟道长度L’是VDS的函数。

定义L’=L-ΔL, ΔL/L=λVDS

λ为沟道长度调制系数。

HIT Microelectronics

王永生

2009-1-16

MOS器件物理基础

16

2.3.3亚阈值导电性

当VGS≈VTH时和略小于VTH ,“弱”反型层依然存在, 与VGS呈现指数关系。当VDS大于200mV时,

这里ζ>1,VT=kT/q

模拟CMOS集成电路设计第2章MOS器件物理基础

MOS管的开启电压VT及体效应

V T H = V T H 0 + γ2 Φ F + V S B -2 Φ F,γ =2 q ε s i N s u b C o x

体效应系数, VBS=0时,=0

源极跟随器 无体效应 有体效应 一般,体效应使设计复杂化

MOS器件物理基础 Ch. 2 # 29

第二章 MOS器件物理基础

MOS器件物理基础 Ch. 2 # 1

MOSFET的结构

MOS器件物理基础 Ch. 2 # 2

MOSFET的结构

Ldrawn:沟道总长度 LD:横向扩散长度

衬底 (bulk、body)

Leff:沟道有效长度, Leff= Ldrawn-2 LD

MOS器件物理基础 Ch. 2 # 3

对于 的典型值,在室温下,要使I D 下降一个数量级,VGS 必须下降M约OS8器0件mC物Vh.理。2基# 3础7

NMOS管的电流公式

ID 0 截至区,Vgs<VTH

ID=n C 2 o L xW [2 (V G S-V T H )V D S-V D S 2]

线性区,Vgs >VTH VDS< Vgs - VTH

ID= nC 2o L xW(VG S-VTH)2

饱和区,Vgs >VTH VDS >Vgs - VTH

寄生二极管

MOS器件物理基础 Ch. 2 # 5

例:判断制造下列电路的衬底类型

MOS器件物理基础 Ch. 2 # 6

NMOS器件的阈值电压VTH

(a)栅压控制的MOSFET (c)反型的开始

(b)耗尽区的形成

(d)反型层的形成

模拟CMOS集成电路设计 拉扎维 ——复旦大学课件

参杂半导体

• 掺入三家获五价原子,提供一个载流子。

• N型:掺入五价元素,如磷(P)、砷(As),

提供一个电子,电子导电。

若:ND 是参杂浓度,D代表施主浓度 多子(电子)浓度: nn = ND

少子(空穴)浓度:

Pn

=

n

2 i

/

ND

• P型:掺入三价元素,如硼(B),

提供一个空穴,空穴导电。

若:NA 是参杂浓度,A代表施主浓度 多子(空穴)浓度: Pp = NA

参数化模块/单元 layout

宏模型 Matlab…

器件

器件特性

版图描述 design rule

器件模型 spice model

模拟集成电路的应用

• 模拟电路本质上是不可替代的

– 自然界是“模拟”的

• 集成传感器、显示驱动 • 模数和数模转换

– 数字信号经过传输后à模拟信号

• 无线和有线通讯 • 磁盘驱动

单极点低通Gm-C滤波器

Gm由偏置电流或电压确定,易受工艺、温度和电源 电压变化的影响

磁盘驱动器中的模块电路(2)

• 模数转换器(ADC)

– 6位ADC, – 由VCO提供采样时钟。采样频率由数字时钟恢复电路控

制。 – 偏移控制:采集63个比较器的失调电压,反馈到输入

端,抵消由此引起的失真。

• 数字信号处理

dQn dVR

=

ε 0ε si 2 ΦB

qN D + VR

1

2

=

Cj0

1

1

+

VR ΦB

2

C j0

=

ε

0ε si qN 2Φ B

D

2

= ε0εsi xn

拉扎维模拟CMOS集成电路设计第二章作业答案 ppt课件 (2)

p 100cm2 /V / s LD 0.09106 m

p 0.2V 1 tox 9 109 m

ID

1 2

pCox

W Leff

(VGS

VTH )2 (1 p 3)

ID 4.8103 (VSG 0.8)2

0 8.854 1012 F / m sio2 3.9

Cox

0 sio2 3.837 103 F / m2

W L

ID

3.66

mA /V

ro

1

n ID

1 0.1 0.5103

20k

gmro 3.66 103 20103 73.2

2)PMOS p 100cm2 /V / s

pCox 3.835105 F /V / s

gm

2PCox

W L

ID

1.96

mA /V

ro

1

P ID

1 0.2 0.5103

数;b)以VBS为参数,并在特性曲线中标出夹断点

解:以NMOS为例

+

当VGS<VTH时,MOS截止,则ID=0

+

VGS

-

+ VDS

VBS

--

ID当VTH<VGS<VDS+VTH时, MOS工斜率作正在比于饱VDS和区

ID

1

ID 2

C WL V V n ox

VSB=0GS

2 VSTB>H0

当VGS>VDS+VTH时,MOS工作在三极管区(线性区)

第二章 作业答案

1 ppt课件

2.1、W/L=50/0.5,假设|VDS|=3V,当|VGS|从0上升到 3V时,画出NFET和PFET的漏电流VGS变化曲线

模拟CMOS集成电路设计精粹ppt 第二章

只要L和C串联损耗阻抗为0,L和C就不产生noise,在无源器件中,只有电阻产生额外的noise。电路 中加入了L就会使得gm和输出电阻都与f有关。如果不含串联的R or L,输入阻抗ZinL是容性的,现在 则变成了纯阻性的,其值为gmLS/CGS,或LSω T,原因是输入CGS被电感抵消了。这样输入电阻可以很容 易地被设计成50 ,从而与50传输线(同轴电缆,天线等)相匹配。这种方法可设计出一个超高f低 noise放大器。

采用两种相同的电流偏置,但右边电路(2)中M2和M1并联,哪一种更好呢?(2)放大器中,输出电 阻较大,∴增益相对较高,相应的带宽窄一些。可用另一个晶体管构成电流源,这个晶体管是PMOST 器件,它的栅极与参考电压相连,产生直流偏置电流。还存在下面两种电路形式。

第一种放大器有一个恒定的直流偏置电流,∵作为电流源的M2的栅极与一个直流参考电压相连。低f 情况下,负载CL不起作用, 此时,M1和M2的直流电流不随信号电平而变化。被定义为A类放大器。第 二种,连接并同时驱动两个管的栅极,结果完全不同。根据所输入信号电平的不同,流过两个管的电 流变化非常大。这就是AB类放大器。实际上,在数字输入信号和模拟输入信号中都有可能采用第二种 放大器。

实现这样一种串联反馈电阻的一个简单方法是采用一个nMOST管,让其工作在线性区。但只有当VDS2很 小,在100mV~200mV之间才有可能。两个晶体管的VGS也不同。 MOST M1工作在饱和区,包含一个参数 K‘,而M2是作为一个电阻使用,包含参数KP,它们的参数n不同,n本身也是一个不确定的值

在增益表达式中,保留输出电阻,能较好地理解同样的输出电阻是怎样来决定输出极点或者带宽的。 在计算GBW时,这个输出电阻被消去,这和单管情况一样。但GBW变成了2倍,∵单管的跨导增大了2倍, ∴这是电流复用的一个简单例子。GBW是最重要的技术指标,它表明在任意f下,可以获得多大的电压 增益。它通过gm取决于电流。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

Q d ( x ) W o ( V x G C V S ( x ) V T )H

西电微电子学院-董刚-模拟集成电路设计

16

I/V特性—推导I(VDS,VGS)

I D W o [ V G x C V S ( x ) V T ] v H

Givv E ea nn E (x d ) d(x V ) dx d(x V )

数字电路设计师一般不需要进入器件内 部,只把它当开关用即可

AIC设计师必须进入器件内部,具备器 件物理知识

❖MOS管是AIC的基本元件 ❖MOS管的电特性与器件内部的物理机制密

切相关,设计时需将两者结合起来考虑

器件级与电路级联系的桥梁?

❖器件的电路模型

西电微电子学院-董刚-模拟集成电路设计

5

本讲

基本概念

I D n C o W L ( x V G V T S ) V D H , V D S 2 S ( V G V T S )

等效为一个线性电阻

RONnCoxW L(V 1GSVTH)

在AIC设计中会用到

西电微电子学院-董刚-模拟集成电路设计

深三极管区

19

I/V特性—当VDS>VGS-VTH时?

与电源无关、与温度无关、PTAT电流、 恒Gm、速度与噪声

西电微电子学院-董刚-模拟集成电路设计

2

上一讲

研究模拟电路的重要性 模拟电路设计的难点 研究AIC的重要性 研究CMOS AIC的重要性 电路设计一般概念

❖抽象级别 ❖健壮性设计 ❖符号

西电微电子学院-董刚-模拟集成电路设计

3

上一讲

数字电路无法完全取代模拟电路,模拟 电路是现代电路系统中必不可少的一部 分

提供载流子的端口为源,收集载流子的端口为漏

最重要的工作区域? 受VG控制的沟道区

西电微电子学院-董刚-模拟集成电路设计

9

MOS管的结构

独享一个阱的 MOS管在AIC设 计中有特殊应用

衬底电压要保证源漏PN结反偏,对阈值电压有影响

同一衬底上的NMOS和PMOS管(体端不同)

西电微电子学院-董刚-模拟集成电路设计

❖简化模型-开关 ❖结构 ❖符号

I/V特性

❖阈值电压 ❖I-V关系式 ❖跨导

二级效应

❖体效应、沟道长度调制效应、亚阈值导电性

器件模型

❖版图、电容、小信号模型等

西电微电子学院-董刚-模拟集成电路设计

6

本讲的目的

从AIC设计者角度,看器件物理;本讲 只讲授MOS器件物理基础知识

理解MOS管工作原理

定性分析、定量分析、共模响应、吉尔伯特单元

基本/共源共栅/有源电流镜 弥勒效应、极点与节点关系、各类单级放大 器频率特性分析 统计特性、类型、电路表示、各类单级放 大器噪声分析、噪声带宽 特性、四种反馈结构、负载影响、对噪声的影响

性能参数、一级运放、两级运放、各指标分析

多极点系统、相位裕度、频率补偿

基于原理,掌握电路级的器件模型

❖直流关系式-I/V特性 ❖交流关系式-小信号电路中的参数

西电微电子学院-董刚-模拟集成电路设计

7

MOS管简化模型

简化模型——开关 由VG控制的一个开关

西电微电子学院-董刚-模拟集成电路设计

8

MOS管的结构

Bulk(body)

源漏在物理结构上是完全对称的,靠什么区分开?

ID n C oW x L[V (G SV T)H V D S1 2V D2]S

是否仍按抛物线 变化?

公式不再适用

推导时是针对反型 沟道区上的长度和 电压差进行积分

沟道区两端的电压 差不再等于VDS, 保持为VGS-VTH

西电微电子学院-董刚-模拟集成电路设计

10

MOS管的符号

? 电流方向

四端器件

省掉B端

数字电路用

AIC设计中一般 应采用该符号?

在Cadence

analogLib库

中,当B、S端短接时

需明确体端连接

只需区别 开MOS管 类型即可

西电微电子学院-董刚-模拟集成电路设计

11

本讲

基本念

❖简化模型-开关 ❖结构 ❖符号

I/V特性

❖阈值电压 ❖I-V关系式 ❖跨导

模拟电路设计的难点比数字电路不同

❖关注点、噪声和干扰、器件二阶效应、设计 自动化程度、建模和仿真、工艺、数模混合

AIC具有高速度、高精度、低功耗、大 批量时成本等优点

用CMOS工艺设计、加工AIC具有加工 成本低、易实现数模混合等优点,被广 泛采用

西电微电子学院-董刚-模拟集成电路设计

4

掌握器件物理知识的必要性

模拟集成电路设计

第2章 MOS器件物理基础

董刚

微电子学院

西电微电子学院-董刚-模拟集成电路设计

1

授课内容

绪论 器件物理基础 单级放大器

差动放大器 无源/有源电流镜 放大器的频率特性

噪声 反馈 运算放大器 稳定性和频率补偿 带隙基准源

重要性、一般概念

MOSFET结构、IV特性、二级效应、器件模型

共源、共漏、共栅、共源共栅

二级效应

❖体效应、沟道长度调制效应、亚阈值导电性

器件模型

❖版图、电容、小信号模型等

西电微电子学院-董刚-模拟集成电路设计

12

沟道电荷的产生

当VG大到一定 程度时,表面

势使电子从源

流向沟道区

VTH定义为表面 电子浓度等于衬 底多子浓度时的

VG

西电微电子学院-董刚-模拟集成电路设计

13

阈值电压

0 栅与衬底功函数差

COX

OX

TOX

常通过沟道注入把VTH0调节到合适值

工艺确定后,VTH0就固定了,设计者无法改变

西电微电子学院-董刚-模拟集成电路设计

14

I/V特性-沟道随VDS的变化

西电微电子学院-董刚-模拟集成电路设计

15

I/V特性—推导I(VDS,VGS)

IQd v

Q d W o(V x C G S V T)H

ID n C oW x L[V (G SV T)H V D S1 2V D2]S 过驱动电压

(VGSVTH)

三极管区 欧姆区 线性区

西电微电子学院-董刚-模拟集成电路设计

18

I/V特性—当VDS<<2(VGS-VTH)时?

ID n C oW L x[V ( G S V T)V H D S 1 2 V D 2 ]S

ID W o[V x C G S V (x ) V T]H n dx

L

VDS

ID d x WoC xn[V G SV (x)V T]H dV

x0

V0

ID n C oW L x[V ( G S V T)V H D S 1 2 V D 2 ]S

西电微电子学院-董刚-模拟集成电路设计

17

I/V特性—线性区