基于FPGA的FFT算法实现

采用FPGA实现FFT算法

采用FPGA实现FFT算法随着数字技术的快速发展,数字信号处理已深入到各个学科领域。

在数字信号处理中,许多算法如相关、滤波、谱估计、卷积等都可通过转化为离散傅立叶变换(DFT)实现,从而为离散信号分析从理论上提供了变换工具。

但DFT计算量大,实现困难。

快速傅立叶(FFT)的提出,大大减少了计算量,从根本上改变了傅立叶变换的地位,成为数字信号处理中的核心技术之一,广泛应用于雷达、观测、跟踪、高速图像处理、保密无线通信和数字通信等领域。

目前,硬件实现FFT算法的方案主要有:通用数字信号处理器(DSP)、FFT专用器件和现场可编程门阵列(FPGA)。

DSP具有纯软件实现的灵活性,适用于流程复杂的算法,如通信系统中信道的编译码、QAM映射等算法。

DSP完成FFT运算需占用大量DSP的运算时间,使整个系统的数据吞吐率降低,同时也无法发挥DSP软件实现的灵活性。

采用FFT专用器件,速度虽能够达到要求。

但其外围电路复杂,可扩展性差,成本昂贵。

随着FPGA发展,其资源丰富,易于组织流水和并行结构,将FFT实时性要求与FPGA器件设计的灵活性相结合,实现并行算法与硬件结构的优化配置,不仅可以提高处理速度,并且具有灵活性高。

开发费用低、开发周期短、升级简单的特点。

针对某OFDM系统中FFT运算的实际需要,提出了基于FPGA的设计来实现FFT算法,并以16位长数据,64点FFT为例,在Quartus Ⅱ软件上通过综合和仿真。

2 FFT原理及算法结构FFT是离散傅立叶变换(DFT)的快速算法。

对于N点离散的有限长时问序列x(n),其傅里叶变换为:完成N点的DFT需要N2次复数乘法和N(N-1)次复数加法。

点数大时,计算量也大,所以难以实现信号的实时处理。

FFT的基本思想是利用旋转因子WN的周期性、对称性、特殊性以及周期N的可互换性,将长度为N点的序列DFT运算逐次分为较短序列的DFT运算,合并相同项,大大减少了计算量。

基于FPGA的高速定点FFT算法的实现

基于FPGA的高速定点FFT算法的实现迅速傅里叶变换(FFT)作为计算和分析工具,在众多学科领域(如信号处理、图像处理、生物信息学、计算物理、应用数学等)有着广泛的应用。

在高速数字信号处理领域,如雷达信号处理,FFT的处理速度往往是囫囵系统设计性能的关键所在。

针对高速实时信号处理的要求,软件实现办法明显满足不了其需要。

近年来现场可编程门阵列()以其高性能、高灵便性、友好的开发环境、在线可编程等特点,使得基于FPGA的设计可以满足实时数字信号处理的要求,在市场竞争中具有很大的优势。

在FFT算法中,数据的宽度通常都是固定的宽度。

然而,在FFT的运算过程中,特殊是乘法运算中,运算的结果将不行避开地带来误差。

因此,为了保证结果的精确性,采纳定点分析是十分须要的。

1 FFT算法原理FFT算法的基本思想就是利用权函数的周期性、对称性、特别性及周期N的可互换性,将较长序列的DFT运算逐次分解为较短序列的DFT运算。

针对N=2的整数次幂,FFT算法有基-2算法、基-4算法、实因子算法和分裂基算法等。

这里,从处理速度和占用资源的角度考虑,选用基-4按时光抽取FFT算法 (DIT)。

对于N=4γ,基-4 DIT具有log4N=γ次迭代运算,每次迭代包含N/4个蝶形单元。

蝶形单元的运算表达式为:其信号流1。

式中:A,B,C,D和A′,B′,C′,D′均为复数据;W=e-j2π/N。

举行1次蝶形运算共需3次复乘和8次复加运算。

N=64 点的基-4DIT信号流其输入数据序列是按自然挨次罗列的,输出结果需经过整序。

64点数据只需举行3次迭代运算,每次迭代运算含有N/4=16个蝶形单元。

2 FFT算法的硬件实现2.1 流水线方式FFT算法的实现第1页共4页。

基于FPGA的并行实序列FFT算法研究与实现

基于FPGA的并行实序列FFT算法研究与实现随着科技的发展,要求越来越高的数据处理速度对计算技术提出了更高的要求。

离散傅立叶变换(Discrete Fourier Transform,简称DFT)是一种重要的信号处理技术,广泛应用于通信、图像处理等领域。

FFT (Fast Fourier Transform)是一种快速计算DFT的算法,大大提高了DFT的计算效率。

现在,越来越多的应用需要实时处理海量的数据,这对FFT算法提出了更高的要求。

然而,传统基于CPU的FFT算法在处理大规模数据时效率低下。

为了加速FFT算法,可以利用FPGA并行计算的特性。

FPGA(Field Programmable Gate Array)是一种集成电路,可以通过配置逻辑门来实现特定的功能。

相较于通用处理器,FPGA具有可编程性强、并行计算能力强等优点。

因此,利用FPGA进行并行实序列FFT算法的设计与实现,可以大大提高计算效率。

首先,需要了解并行实序列FFT算法的原理。

实序列FFT算法可以将输入序列分为偶数部分和奇数部分,然后通过FFT算法分别计算这两部分的DFT,最后将结果进行合并即可得到整个序列的DFT。

并行算法的设计思路是将这些计算任务分配给多个处理单元,并行计算。

在FPGA上实现并行实序列FFT算法,可以通过以下步骤:1.设计FPGA的结构:将输入序列分为偶数部分和奇数部分,并为每个处理单元分配计算任务。

2.对每个处理单元进行FFT计算:在每个处理单元内部,实现FFT算法,计算偶数部分和奇数部分的DFT。

3.合并计算结果:将各个处理单元计算得到的DFT结果进行合并,得到整个序列的DFT。

在设计并行实序列FFT算法时1.处理单元之间的通信:处理单元之间需要进行数据的传输和同步。

可以使用FPGA内部的通信接口来实现高速数据传输,保证各个处理单元的计算结果能够及时传输和合并。

2.数据存储:在FPGA上进行大规模数据的计算,需要合理设计数据存储结构,以提高计算效率。

基于FFT谱分析测频算法的FPGA实现

基于FFT谱分析测频算法的FPGA实现在FPGA实验中,主要是用FPGA来实现FFT,使其完成对信号的频谱分析。

实验中设计流水线结构FFT,主要是进行蝶形单元的设计;旋转参数生成;FFT 系统仿真测试。

标签:FPGA;QuartusⅡ;FFT处理器1 实验原理及步骤1.1 QuartusⅡ开发环境QuartusⅡ是Altera公司提供的FPGA/CPLD集成开发软件,在QuartusⅡ上可以完成设计输入、HDL综合、布新布局(适配)、仿真和选择以及硬件测试等流程,它提供了一种与结构无关的设计环境,使设计者能方便地进行设计输入、开始处理和器件编程。

QuartusⅡ具备仿真功能,同时支持第三方的仿真工具(如ModelSin)。

此外,QuartusⅡ与MATLAB和DSP Builder结合,可用进行基于FPAG 的DSP系统开发,是DSP硬件系统实现的工具EDA工具。

FFT算法种类很多,基本上可分为两大类:一类是针对N等于2的整数次幂的算法,如基2算法、基4算法和分裂基算法等;另一类是针对N不等于2的整数次幂的算法,以Winograd为代表,它们有重要的理论价值,但是不适于硬件实现。

基2算法结构简单,但运算量大。

基4算法相对于基2算法更为复杂,但是计算量减少了。

FFT算法按分解方式的不同又可以分为时域抽取算法(decimation in time,DIT)和频域抽取算法(decimation in frequency,DIF)两种。

这两种算法在本质上都是一种基于标号分解的算法,在运算量和复杂性等方面完全一样。

考虑到本设计FFT运算的点数不是太多,故选用了时域抽取基2算法(DIT)。

1.3 按时间抽取的基-2FFT算法(DIT-基2-FFT)原理FFT算法由多级蝶形运算构成,具体运算流图也有多种形式。

本设计选用了输入倒序、输出顺序的运算流图,图3所示为N=8点时的DIT-FFT运算流图。

这种运算流图是同址运算,其优点是:在同一级运算中,每个蝶形的两个输入数据只对计算本蝶形有用,而且蝶形的输入输出数据节点又同在一条水平线上,这就意味着计算完一个蝶形运算后,所得输出数据可以立即存入元出入数据所占用的存储器。

基于FPGA的FFT算法实现

毕业论文基于FPGA的FFT算法实现[摘要]快速傅立叶变换(FFT)作为时域和频域转换的基本运算,是数字谱分析的必要前提。

传统的FFT使用软件或DSP实现,高速处理时实时性较难满足。

FPGA是直接由硬件实现的,其内部结构规则简单,通常可以容纳很多相同的运算单元,因此FPGA在作指定运算时,速度会远远高于通用的DSP芯片。

FFT运算结构相对比较简单和固定,适于用FPGA进行硬件实现,并且能兼顾速度及灵活性。

本文介绍了一种通用的可以在FPGA上实现512点FFT变换的方法。

主要对quartus II中的ram,rom,fft,基本运算等宏模块进行调用。

并且通过vga控制模块,和键盘等控制模块,实现对信号的产生和频谱的测量和显示等工作。

实验果表明,设计完成的系统能够在保证运算精度和实现复杂度的同时,切实可行地完成设计的总体要求。

[关键词]FPGA;VGA ;FFT;ip核Implementation of FFT algorithm based on FPGA[Abstract]:Fast Fourier Transform (FFT) as a time domain and the frequency domain conversion of the basic operation, the digital spectrum analysis prerequisite. The traditional FFT implemented using software or DSP, real-time high-speed processing more difficult to meet. FPGA is a direct hardware implementation, and its internal structure rules are simple, you can usually accommodate many of the same arithmetic unit, thus making the assignment operator FPGA, the speed will be much higher than the general-purpose DSP chips. FFT operation is relatively simple and fixed structure, suitable for hardware implementation using FPGA and can both speed and flexibility. This paper describes a generic that can be implemented on FPGA 512-point FFT transform method. Mainly quartus II of ram, rom, fft, basic operations such as macro block calls. And through vga control module, and keyboard control module enables the signal generation and spectrum measurement and display work. Experimental results show that the design is completed the system to ensure the accuracy and computing implementation complexity while practicable to complete the design of the overall requirements.[Key words]: FPGA; VGA; FFT; ip nuclear目录1引言 (1)2设计原理 (3)2.1基2-FFT算法原理 (3)2.2基4-FFT算法原理 (8)2.3IP核实现原理 (8)3 FFT设计实现 (13)3.1总体结构设计 (13)3.2FFT IPC ORE的建立 (14)3.3测试信号的产生 (18)3.3.1 dds原理 (18)3.3.2 dds的实现 (18)3.3.3 测试信号的仿真 (19)3.4显示模块设计 (19)3.4.1 vga显示原理 (19)3.4.2 vga的实现 (22)3.4.3 vga的仿真测试 (23)3.5存储单元设计 (23)4系统调试 (25)4.1安装B YTE B LASTER II下载电缆 (25)4.1.1驱动程序安装 (25)4.1.2硬件下载 (26)4.1.3软件实现过程 (26)4.2FFT算法测试 (29)4.2.1正弦信号的FFT测试 (29)4.2.2 方波信号的FFT测试 (30)总结与展望 (32)致谢 (33)参考文献 (34)附录 (35)源程序...................................................... . (41)1引言在数字化高速发展的今天,对数字信号处理高速实时的要求也不断提高。

用FPGA实现FFT算法

用FPGA实现FFT算法引言DFT(Discrete Fourier Transformation)是数字信号分析与处理如图形、语音及图像等领域的重要变换工具,直接计算DFT的计算量与变换区间长度N的平方成正比。

当N较大时,因计算量太大,直接用DFT算法进行谱分析和信号的实时处理是不切实际的。

快速傅立叶变换(Fast Fourier Transformation,简称FFT)使DFT运算效率提高1~2个数量级。

其原因是当N较大时,对DFT进行了基4和基2分解运算。

FFT算法除了必需的数据存储器ram和旋转因子rom外,仍需较复杂的运算和控制电路单元,即使现在,实现长点数的FFT仍然是很困难。

本文提出的FFT 实现算法是基于FPGA之上的,算法完成对一个序列的FFT计算,完全由脉冲触发,外部只输入一脉冲头和输入数据,便可以得到该脉冲头作为起始标志的N点FFT输出结果。

由于使用了双ram,该算法是流型(Pipelined)的,可以连续计算N点复数输入FFT,即输入可以是分段N点连续复数数据流。

采用DIF(Decimation In Frequency)-FFT和DIT(Decimation In Time)-FFT对于算法本身来说是无关紧要的,因为两种情况下只是存储器的读写地址有所变动而已,不影响算法的结构和流程,也不会对算法复杂度有何影响。

算法实现的可以是基2/4混合基FFT,也可以是纯基4FFT和纯基2FFT运算。

傅立叶变换和逆变换对于变换长度为N的序列x(n)其傅立叶变换可以表示如下:N nkX(k)=DFT[x(n)] =Σ x(n)Wn=0式(1)其中,W=exp(-2π/N)。

当点数N较大时,必须对式(1)进行基4/基2分解,以短点数实现长点数的变换。

而IDFT的实现在DFT的基础上就显得较为简单了:式(2)由式(2)可以看出,在FFT运算模块的基础上,只需将输入序列进行取共轭后再进行FFT运算,输出结果再取一次共轭便实现了对输入序列的IDFT运算,因子1/N对于不同的数据表示格式具体实现时的处理方式是不一样的。

基于FPGA的FFT算法硬件实现

基于FPGA的FFT算法硬件实现引言:FFT是一种用于将时域信号转换为频域信号的算法,常用于信号处理和图像处理领域。

由于FFT的高计算复杂度,硬件实现可以提供更高的计算效率和并行处理能力。

本文将介绍基于FPGA的FFT算法硬件实现,并详细解释算法的原理和实现过程。

一、快速傅里叶变换(FFT)算法简介快速傅里叶变换(FFT)是一种将一个N点离散序列转换为频域离散序列的算法。

它的时间复杂度为O(NlogN),相比于传统的傅里叶变换算法的时间复杂度O(N^2),FFT算法具有更高的计算效率。

FFT算法的核心思想是将一个N点离散序列划分为其各个子序列,然后再分别计算各个子序列的傅里叶变换,并将结果通过一系列的蝶形运算合并得到最终的频域信号。

二、FFT算法的硬件实现原理基于FPGA的FFT算法实现可以充分发挥FPGA的并行计算能力和灵活性。

硬件实现的核心是设计一个包含多个计算单元的并行处理模块。

常见的FFT硬件实现架构包括基于蝶形运算的位递归FFT算法和基于矩阵运算的线性变换FFT算法。

1.基于蝶形运算的位递归FFT算法实现首先将输入序列分为奇数位和偶数位两个子序列,然后分别对这两个子序列进行FFT计算。

然后将得到的结果通过蝶形运算合并得到最终的频域信号。

在硬件实现中,可以设计一个包含多个蝶形运算单元的并行计算模块。

每个蝶形运算单元包括两个输入通道和两个输出通道,通过并行计算可以同时进行多个蝶形运算操作,提高计算效率。

2.基于矩阵运算的线性变换FFT算法实现线性变换FFT算法将FFT计算表示为矩阵运算的形式,可以充分利用FPGA的向量计算能力。

这种实现方法将输入序列表示为一个复数矢量,然后通过矩阵运算得到最终的频域信号。

在硬件实现中,可以设计一个包含多个矩阵运算单元的并行计算模块。

每个矩阵运算单元可以同时对多个输入进行矩阵运算,提高计算效率。

三、基于FPGA的FFT算法硬件实现步骤1.硬件资源规划:根据需要计算的样本点数N,确定所需的FPGA资源,包括DSP片上资源、BRAM资源和IO资源等。

基4FFT算法的FPGA实现

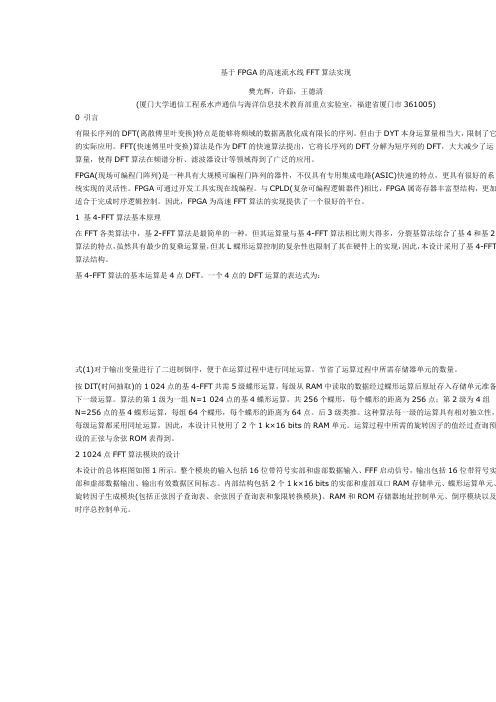

本文通过设计一种基于FPGA的基-4的FFT,探讨 FPGA在实现FFT算法中的应用。本文重点设计了采用 一种旋转因子存储器搭建基-4FFT蝶形模块,实现蝶 形运算单元。本系统最大的优势在于利用FPGA丰富逻 辑资源,及其灵活的可编程特性使运算速度较传统方 法有了很大提高。 用FPGA实现基-4FFT可以获得高性能,满足成本 要求,并享有快速有效地对新设计进行优化的灵活性。 这种基于用FPGA实现FFT算法,可以广泛应用在高速 信号处理中,并从此设计可以看出,前端的可编程数字 信号处理算法都可利用FPGA构建。但是与传统的基-2 相比较,虽然运算速度提高了,却使用了很多逻辑资源。

ROM因子 表

FFT输出标志

图 1-3

FFT实现框图

在图1-3中,运算模块为基-4运算模块,控制模块产生 所有的控制信号、存储器1和2的读写地址、写使能、 运算模块的启动信号因子表的读写地址等信号。

存储器1作为当前输入标志对应输入N点数据缓 冲器,存储器2作为中间变量结果存储器,用于 存 储 运 算 模 块 计 算 出 各 个 通 道 的 结 果 。

FFT硬件实现

1:旋转因子乘法器的实现 FFT设计一个旋转因子存储单元可以提高FFT的 计算速度,因此需要合理的设计旋转因子的存 储单元,在FFT硬件设计中占重要地位。本文采用 一种高效的算法来实现存储旋转因子。 设复数旋转因子乘法器R+ jI=(X+ jY) (C+ jS) 因为C、S可以预先计算的,并可以存储在一个表 中。所以我们可以存储下面三个系数: C、C+S、C-S

基-4算法的模块实现

FFT模块的构成: 1:旋转因子乘法器;2:基-4蝶形运算器; 3:地址产生器; 4:控制信号产生器 5:中间变量存放组 本文设计的FFT模块的划分图如图1-3,图中 各个模块在中央控制单元的管理下并行工作。

用FPGA实现FFT的方法

用FPGA实现FFT的方法使用FPGA(Field-Programmable Gate Array)实现FFT(Fast Fourier Transform)可以提供高性能的信号处理能力。

FFT是一种将时域信号转换为频域信号的算法,广泛应用于数字信号处理、通信系统、图像处理等领域。

下面将介绍一种常见的方法来使用FPGA实现FFT。

首先,需要了解FFT算法的基本原理。

FFT将长度为N的离散时间信号x(n)转换为N个频谱分量X(k),其中k=0,1,...,N-1、FFT算法的核心是蝶形运算,通过将信号分解成不同的频率分量并逐步组合来实现。

下面是使用FPGA实现FFT的具体步骤:1.设计数据缓存器:在FPGA内部设计一个数据缓存器用于存储输入信号x(n)和输出信号X(k)。

缓存器的宽度和深度取决于输入信号的采样位数和FFT的长度。

2. 数据采集与预处理:使用FPGA的输入模块采集外部信号,并通过FIFO(First In First Out)缓冲区将数据传输到数据缓存器中。

为了提高计算速度,可以使用预处理方法如窗函数、数据重排等来优化输入信号的质量。

3.蝶形运算模块设计:FFT算法的核心是蝶形运算。

在FPGA中,设计一个蝶形运算模块用于计算FFT算法中的每一个蝶形运算,即通过求解两个复数的乘积,并进行加法运算得到结果。

该模块需要实现乘法器和加法器,并对数据进行并行计算。

4.快速蝶形运算网络构建:将蝶形运算模块按照FFT算法中的乘积因子进行连接,并根据FFT的长度设计合适的网络结构。

可以使用串行-并行方式或并行-串行方式来实现FFT算法。

需要注意的是,为了减少延迟,可以采用流水线技术来提高运算速度。

5.数据输出与后处理:设计一个输出模块将计算得到的频域信号X(k)输出到外部。

可以通过FPGA的输出模块将数据传输到外部存储器、显示器或其他设备进行后续处理。

6. 时钟和时序设计:在FPGA中需要设计合适的时钟频率和时序来保证FFT算法的准确性和稳定性。

基于FPGA的计算整数FFT算法的设计及实现

基于FPGA的计算整数FFT算法的设计及实现近年来,FPGA技术得到了广泛的关注和应用,除了在数字电路设计和信号处理方面得到广泛的应用外,还可以使用FPGA实现计算整数FFT算法。

其中,FFT 算法是一种十分重要的数字信号处理方法,可以快速地计算离散傅里叶变换(DFT),常常被用于音频、图像和视频等领域。

在本文中,我将介绍基于FPGA的计算整数FFT算法的设计及实现,包括算法的原理、设计思路和实现过程等方面,旨在为对此感兴趣的读者提供一些参考和帮助。

一、FFT算法原理在介绍计算整数FFT算法的设计过程前,我们先来了解一下FFT算法的原理。

DFT是将一个有限长的序列映射到另一个有限长的序列的线性变换,它的表达式为:$$X(k)=\sum_{n=0}^{N-1}{x(n)e^{-j2\pi k n/N}}$$其中,$x(n)$为原始序列,$N$为序列长度,$k$为频率索引。

这个表达式说明了在时域上的一个序列可以通过傅里叶变换转换到频域上的一个序列。

但是,DFT的计算量很大,因此常常使用FFT算法来实现DFT计算。

FFT算法的核心思想是分治法,将DFT一次计算分解为多次小规模DFT,简化计算量,提高计算效率。

在此过程中,我们需要卷积(卷积是将两个函数进行叠加得到一个新的函数)和旋转因子的概念。

卷积可以通过以下公式来表示:$$(f * g)(n)=\sum_{k=0}^{N-1}{f(k)g(n-k)}$$其中,$*$表示卷积运算,$f(n)$和$g(n)$是两个序列。

这个公式表示的是,将$f(n)$和$g(n)$反转、平移后得到的两个函数的积的积分。

旋转因子是指:$$W_N=e^{-j2\pi/N}$$$$W_N^k=e^{-j2\pi k/N}$$这个公式是用来计算旋转角度的。

在FFT算法中,需要不断地计算角度,旋转因子起到了重要作用。

二、计算整数FFT算法设计思路在了解了FFT算法的原理后,我们可以开始设计计算整数FFT算法。

基于FPGA IP核的FFT实现与改进

基于FPGA IP核的FFT实现与改进摘要利用FPGA IP核设计了一种快速、高效的傅里叶变换系统。

针对非整数倍信号周期截断所导致的频谱泄露问题,提出了一种通过时输入信号加窗处理来抑制频谱泄露的方法。

利用Modelsim和Matlab对设计方案进行了仿真,同时在Altera公司的CycloneⅡ硬件平台上进行了验证。

验证结果表明,系统性能良好,改进效果明显。

FFT是离散傅里叶变换(DFT)的一种快速算法,被广泛应用于频谱分析、音频编码、图像处理等数字信号处理领域。

FFT运算复杂,需要大量的存储器和运算单元,其硬件实现平台多种多样。

DSP需要外置存储器和特定接口,限制了运算速度。

ASIC虽能满足速度要求,但其硬件电路复杂、可扩展性差、且价格昂贵。

FPGA具有陕速并行运算、高集成度、低功耗等特点,且具有丰富的IP核资源,方便调用,适合FFT算法的实现。

对于512点FFT处理器,如果该512个输入数据不是信号周期的整数倍,即非整数倍周期截断,则会出现频谱泄露现象。

窗函数处理的宗旨是减小频谱泄露。

常规的FFT硬件实现方法均不考虑由于非整数倍截断导致的频谱泄露问题。

针对以上问题,本文设计了一种基于Altera IP核的512点FFT系统,同时通过对输入信号的加窗处理,抑制了非整数倍信号周期截断所产生的频谱泄露。

1 原理概述1.1 FFT原理离散傅里叶变换(DFT)算法为FFT为DFT的快速算法,其方法多种多样,基本可以分为按时间抽取法和按频率抽取法两类。

此处介绍基-4频率抽取法。

令N=4M,对式(1)N点的DFT可按如下方法作按频率出抽取4个等式可定义为一个蝶形运算,蝶形运算可看作基-4FFT基本运算单元。

参与蝶形运算的4个节点是有规律的,分别为(n)、(n+N/4)、(n+2N/4)和(n+3N/4)。

接着再将X(4r)、X(4r+1)、X(4r+2)和X(4r+3)分别分解为4个长度为N/16的序列,基本结构是每一级的运算由N/4个蝶形运算构成,经过迭代log4N次后完成计算。

基于FPGA的FFT算法的实现

基于FPGA的FFT算法的实现摘要:信号处理在电力系统工作中应用广泛,其中快速傅里叶变换(FFT)在信号处理中是一种采用较多的方式。

现提出一种基于FPGA的快速傅里叶变化算法的实现方式,同时给出基于Modelsim的仿真结果与Matlab的计算结果进行对比。

关键词:FFT;FPGA;信号处理0 引言FFT是DFT的一种快速计算方式,能够将DFT运算的计算效率提高1~2个数量级[1]。

传统的快速傅里叶变化多采用单片机或者DSP进行实现,而单片机都采用循环的串行计算,当碰到高频信号需要较高的采样频率时,其计算结果的实时性无法得到保证。

FPGA(现场可编程门阵列)其并行运算的特性,能够进一步提高FFT计算的速度,拥有较高的实时性。

本文提出了一种基于FPGA的256点的FFT算法的实现。

1 FFT算法的原理对于一个N点有限长度的序列的,其DFT计算方式为:完成一次N点序列的DFT计算需要N2次复数乘法即N(N-1)次复数加法[2],最终需要经历4N2次实数乘法,2N(2N-1)次实数加法才能得到其计算结果,其计算量十分庞大。

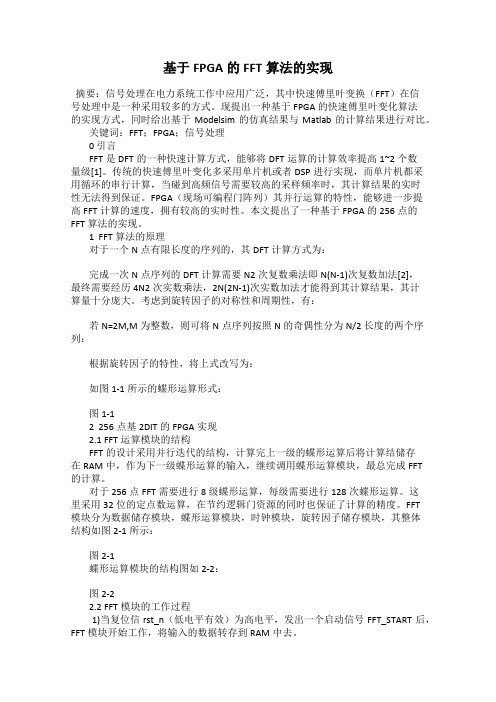

考虑到旋转因子的对称性和周期性,有:若N=2M,M为整数,则可将N点序列按照N的奇偶性分为N/2长度的两个序列:根据旋转因子的特性,将上式改写为:如图1-1所示的蝶形运算形式:图1-12 256点基2DIT的FPGA实现2.1 FFT运算模块的结构FFT的设计采用并行迭代的结构,计算完上一级的蝶形运算后将计算结储存在RAM中,作为下一级蝶形运算的输入,继续调用蝶形运算模块,最总完成FFT的计算。

对于256点FFT需要进行8级蝶形运算,每级需要进行128次蝶形运算。

这里采用32位的定点数运算,在节约逻辑门资源的同时也保证了计算的精度。

FFT模块分为数据储存模块,蝶形运算模块,时钟模块,旋转因子储存模块,其整体结构如图2-1所示:图2-1蝶形运算模块的结构图如2-2:图2-22.2 FFT模块的工作过程1)当复位信rst_n(低电平有效)为高电平,发出一个启动信号FFT_START后,FFT模块开始工作,将输入的数据转存到RAM中去。

基于FPGA的FFT算法硬件实现

基于FPGA的FFT算法硬件实现FFT(快速傅里叶变换)是一种非常重要的算法,在信号处理、图像处理、生物信息学、计算物理、应用数学等方面都有着广泛的应用。

在高速数字信号处理中,FFT 的处理速度往往是整个系统设计性能的关键所在。

FPGA(现场可编程门阵列)是一种具有大规模可编程门阵列的器件,不仅具有ASIC(专用集成电路)快速的特点,更具有很好的系统实现的灵活性。

基于FPGA 的设计可以满足实时数字信号处理的要求,在市场竞争中具有很大的优势。

因此,FPGA 为高速FFT 算法的实现提供了一个很好的平台。

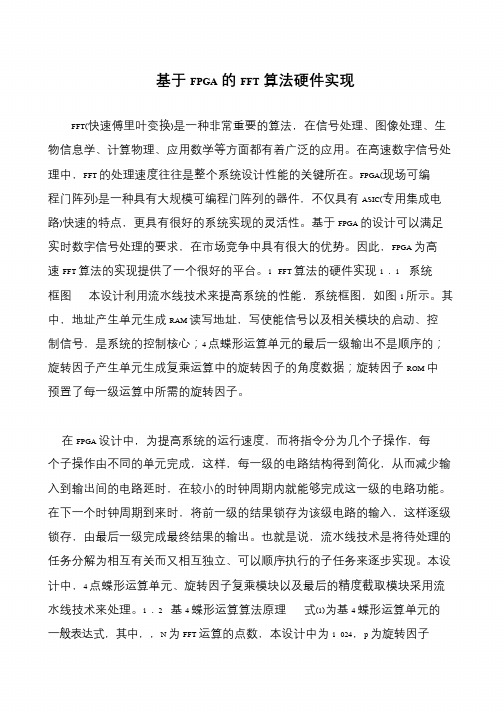

1 FFT 算法的硬件实现1.1 系统框图本设计利用流水线技术来提高系统的性能,系统框图,如图1 所示。

其中,地址产生单元生成RAM 读写地址,写使能信号以及相关模块的启动、控制信号,是系统的控制核心;4 点蝶形运算单元的最后一级输出不是顺序的;旋转因子产生单元生成复乘运算中的旋转因子的角度数据;旋转因子ROM 中预置了每一级运算中所需的旋转因子。

在FPGA 设计中,为提高系统的运行速度,而将指令分为几个子操作,每个子操作由不同的单元完成,这样,每一级的电路结构得到简化,从而减少输入到输出间的电路延时,在较小的时钟周期内就能够完成这一级的电路功能。

在下一个时钟周期到来时,将前一级的结果锁存为该级电路的输入,这样逐级锁存,由最后一级完成最终结果的输出。

也就是说,流水线技术是将待处理的任务分解为相互有关而又相互独立、可以顺序执行的子任务来逐步实现。

本设计中,4 点蝶形运算单元、旋转因子复乘模块以及最后的精度截取模块采用流水线技术来处理。

1.2 基4 蝶形运算算法原理式(1)为基4 蝶形运算单元的一般表达式,其中,,N 为FFT 运算的点数,本设计中为1 024,p 为旋转因子。

基于FPGA的高速流水线FFT算法实现

基于FPGA的高速流水线FFT算法实现樊光辉,许茹,王德清(厦门大学通信工程系水声通信与海洋信息技术教育部重点实验室,福建省厦门市361005)0 引言有限长序列的DFT(离散傅里叶变换)特点是能够将频域的数据离散化成有限长的序列。

但由于DYT本身运算量相当大,限制了它的实际应用。

FFT(快速傅里叶变换)算法是作为DFT的快速算法提出,它将长序列的DFT分解为短序列的DFT,大大减少了运算量,使得DFT算法在频谱分析、滤波器设计等领域得到了广泛的应用。

FPGA(现场可编程门阵列)是一种具有大规模可编程门阵列的器件,不仅具有专用集成电路(ASIC)快速的特点,更具有很好的系统实现的灵活性。

FPGA可通过开发工具实现在线编程。

与CPLD(复杂可编程逻辑器件)相比,FPGA属寄存器丰富型结构,更加适合于完成时序逻辑控制。

因此,FPGA为高速FFT算法的实现提供了一个很好的平台。

1 基4-FFT算法基本原理在FFT各类算法中,基2-FFT算法是最简单的一种,但其运算量与基4-FFT算法相比则大得多,分裂基算法综合了基4和基2算法的特点,虽然具有最少的复乘运算量,但其L蝶形运算控制的复杂性也限制了其在硬件上的实现,因此,本设计采用了基4-FFT 算法结构。

基4-FFT算法的基本运算是4点DFT。

一个4点的DFT运算的表达式为:式(1)对于输出变量进行了二进制倒序,便于在运算过程中进行同址运算,节省了运算过程中所需存储器单元的数量。

按DIT(时间抽取)的1 024点的基4-FFT共需5级蝶形运算,每级从RAM中读取的数据经过蝶形运算后原址存入存储单元准备下一级运算。

算法的第1级为一组N=1 024点的基4蝶形运算,共256个蝶形,每个蝶形的距离为256点;第2级为4组N=256点的基4蝶形运算,每组64个蝶形,每个蝶形的距离为64点。

后3级类推。

这种算法每一级的运算具有相对独立性,每级运算都采用同址运算,因此,本设计只使用了2个1 k×16 bits的RAM单元。

基4FFT算法的FPGA实现

基4FFT算法的FPGA实现基4FFT算法是一种优化的快速傅里叶变换(Fast Fourier Transform, FFT)算法,它能有效地将长度为4的离散序列转换为其频域表示。

在FPGA上实现基4FFT算法可以提高傅里叶变换的计算速度和效率,适用于音频处理、无线通信、图像处理等领域。

FPGA(Field Programmable Gate Array)是一种可编程逻辑设备,其灵活性和高度并行的特性使其成为FFT算法的理想硬件实现平台。

下面将从优化策略、架构设计和性能分析三个方面来讨论FPGA上基4FFT算法的实现。

一、优化策略基于FPGA的FFT算法实现的优化策略包括算法优化和硬件优化两个方面。

1.算法优化:基4FFT算法的关键特性是将长度为4的序列分解为两个长度为2的序列,再进行运算。

通过在算法级别上进行优化,可以减小计算量和存储量。

例如,采用切比雪夫多项式代替蝶形运算,减少乘法操作。

此外,使用采样点的对称性和周期性,可以进一步简化计算过程。

2.硬件优化:在FPGA的架构设计方面,可以采用流水线化和并行计算的方法来提高计算效率。

流水线化可以将计算过程划分为多个阶段,实现多个计算阶段的并行化,从而提高吞吐量。

并行计算可以通过使用多个处理单元来同时执行多个计算操作,进一步增加计算能力。

二、架构设计基于FPGA的基4FFT算法实现的架构设计主要包括数据存储和运算单元的设计。

1. 数据存储:基于FPGA的FFT算法实现中,需要使用存储单元来存储输入序列和中间结果。

常用的存储单元包括FIFO(First-in-First-out)队列和RAM(Random Access Memory)。

存储单元的设计需要考虑读写速度和存储容量。

2.运算单元:基于FPGA的FFT算法实现中,需要设计运算单元来进行乘法和加法运算。

运算单元的设计需要考虑乘法器的使用,乘法操作是FFT计算的关键部分,可以采用片上乘法器和并行乘法器来提高计算速度。

基于FPGA的FFT算法实现

基于FPGA的FFT算法实现摘要随着数字电子技术的发展,数字信号处理技术具有极其广泛的应用,比如视频压缩、数字机顶盒、有线调制解调器、数字多用盘、多媒体与无线通信、语音处理、传输系统、雷达成像、全球定位系统等等。

同时,信息技术领域是依赖于数字信号处理及其相应的专用集成电路的,所以对数字信号处理的要求越来越高。

因此对数字信号处理中涉及到的有关算法的改进也提出了更高的要求,其中快速傅立叶变换是数字信号处理的一种重要的算法研究。

现场可编程门阵列是近年来出现的一种新的可编程逻辑器件,它具有运行速度快、存储容量大、管脚多等特点。

本文研究的是利用现场可编程门阵列来实现快速傅立叶变换算法,快速傅立叶变换算法的实现,大大缩短了运算所需的时间,降低了因计算复杂而导致的计算误差。

随着超大规模集成电路技术的不断提高,现场可编程门阵列的规模和集成度越来越大,在电子系统的设计中发挥了更大的作用。

主要的设计内容包括现场可编程门阵列的结构与功能、VHDL语言的介绍、算法的实现过程等。

本文通过离散傅立叶变换引出快速傅立叶变换算法,提出了快速傅立叶变换的两种抽取方法,重点介绍了基2按时间抽取的快速傅立叶算法,对算法进行了MAX+PLUSⅡ的仿真,再利用现场可编程门阵列来实现,并对仿真结果进行了分析。

结果表明快速傅立叶变换的算法结果已达到了一定的精度,运算速度能够满足一般实时信号处理的要求。

关键词:现场可编程门阵列,VHDL,快速傅立叶变换,MAX+PLUSⅡAbstractWith the development of digital electronic technology , digital signal processing technology have an extremely wide range of applications ,such as video compression,digital set-top boxes ,cable modems ,digital multi-purpose tray ,multimedia and wireless communications ,voice processing ,transmission systems ,radar imaging ,global positioning systems and so on .Meanwhile ,information technology depend on the digital signal processing and its corresponding application specific integrated circuit ,so the demand of digital signal processing have become more and more .Therefore, the digital signal processing involved in the algorithm is also put forward higher requirements ,and fast Fourier transform digital signal processing is an important algorithm . Field programmable gate array emerged in recent years, and it is a new programmable logic devices .It has the operational speed, storage capacity, much more pins and so on.This paper studies the implementation of FFT based FPGA .The realization of Fast Fourier Transform algorithm greatly reduce the computation time which required to and decrease the computational complexity caused by calculation errors .As VLSI technology continues to improve , its size and growing integration play a bigger role on the design of electronic systems .And the main design elements include the structure and function of FPGA ,the description of VHDL language ,algorithm implementation processes and so on .According to the description of Fourier transform fast Fourier transform algorithm, leading to fast Fourier transform of the two extraction methods .And the paper especially studies the time taken by the base 2 Fast Fourier algorithm and uses MAX+PLUSⅡsimulate it ,meanwhile adopts FPGA to achieve ,and the simulation results are analyzed .The results show that the results of fast Fourier transform algorithm has reached a certain degree ,and its accuracy, computation speed can meet the general requirements of real-time signal processing .Keywords :FPGA,VHDL,FFT,MAX+PLUSⅡ目录第1章绪论 (1)1.1 FFT算法的研究现状及应用 (1)1.2 课题的提出 (1)1.3 FPGA实现FFT的优势 (2)1.4 本文的研究工作 (2)第2章可编程门阵列与VHDL (3)2.1 可编程门阵列 (3)2.1.1 FPGA的基本结构 (3)2.1.2 FPGA的基本特点 (3)2.1.3 FPGA的配置模式与功能 (4)2.2 VHDL的出现 (4)2.2.1 VHDL硬件描述语言 (4)2.2.2 VHDL的基本结构 (5)第3章 FFT算法研究 (6)3.1 傅立叶变换 (6)3.2 离散傅立叶变换 (6)3.3 FFT的基本思想 (6)3.4 快速傅立叶变换 (7)3.4.1 基于时选的快速傅立叶变换 (7)3.4.2 基于频选的快速傅立叶变换 (11)3.5 FFT算法的类型 (13)第4章FFT算法的软件设计与仿真 (15)4.1 FFT算法模块设计的层次划分 (15)4.2旋转因子 (15)4.2.1旋转因子模块 (15)4.2.2旋转因子复数乘法器算法研究 (15)4.3加/减法器 (16)4.3.1端口命名 (16)4.3.2加/减法器设计 (17)4.4乘法器 (18)4.4.1端口命名 (18)4.4.2乘法器设计 (18)4.5 基-2蝶形处理器 (19)小结 (20)致谢 (21)参考文献 (22)附录 (23)第1章绪论1.1 FFT算法的研究现状及应用数字信号处理是起源于十七和十八世纪数学的一个学科,当时加文(Garwin)在他的研究中极需要一个计算傅立叶变换的快速方法。

文献综述 -基于FPGA的FFT算法实现

毕业设计(论文)文献综述课题名称:基于FPGA的FFT算法实现学院:机电工程学院专业:电子信息工程年级:指导教师:学生姓名:学号:______起迄日期:__日一、前言DFT和卷积是信号处理中两个最基本也是最常用的运算,他们涉及到信号与系统的分析与综合这一广泛的信号处理领域。

卷积可以化为DFT来计算,实际上其他许多算法,如相关、滤波、谱估计等也都可以化为DFT来计算。

当然,DFT也可化为卷积来实现。

由后面的讨论可知,它们之间有着互通的关系。

对N 点序列x(n),要求出DFT变换对,就需要先求出N点X(k)需要N2次复数乘法,N(N-1)次复数加法。

众所周知,实现一次复数乘需要四次实数乘两次加法,实现一次复数加则需要两次实数加。

当N很大时,其计算量是相当可观的。

例如,若N=1024,则需要1048576次复数乘法,即4194304次实数乘。

所需要时间过长,难于“实时”实现。

对于2-D图像处理,所需要计算量更是大得惊人[1]。

又例如,在FIR滤波器设计中会遇到从h(n)求H(k)或由H(k)求h(n),这就需要计算DFT。

再有,信号的频谱分析对通信、图像传输、雷达、声纳等都是很重要的。

此外,在系统的分析、设计和实现中都会用到DFT的计算。

但是,在相当长的时间里,由于DFT的计算量太大,即使采用计算机也很难对问题进行实时处理,所以并没有得到真正的应用。

直到1965年库利在《计算数学》杂志上发表了著名的“及其计算傅里叶级数的一种算法”的文章,提出了DFT 的一种快速算法FFT,后来又有桑德和图基的快速算法FFT相继出现,情况才发生了变化[2]。

二、主题序列和线性时不变系统的频域特征是用Z变换和傅里叶变换来表示的。

对于有限长序列,可以导出另一种傅里叶变换表示式,即离散傅里叶变换(简称DFT——Discrete Fourier Transform),它是解决频谱离散化的有效方法,并因存在着计算DFT的高效算法——快速傅里叶变换FFT(Fast Fourier Transform),因而离散傅里叶变换不仅在理论上有重要意义,而且在各种数字信号处理的运算方法中起着重要的作用[3-4]。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

基于FPGA的FFT算法实现Based on the FPGA implementation of FFTalgorithm作者:张小艳 ZHANG XiaoYan(电子工程学院光信0901班)指导老师:常凌颖 CHANG LingYing 副研究员摘要:设计了一种基于FPGA的1024点16位FFT算法, 采用了基4蝶形算法和流水线处理方式, 提高了系统的处理速度, 改善了系统的性能。

提出了先进行前一级4点蝶形运算, 再进行本级与旋转因子复乘运算的结构, 合理地利用了硬件资源。

对系统划分的各个模块使用VerilogHDL进行编码设计。

对整个系统整合后的代码进行功能验证之后, 采用Quartus 与Matlab进行联合仿真, 其结果是一致的。

该系统既有DSP器件实现的灵活性又有专用FFT芯片实现的高速数据吞吐能力, 在数字信号处理领域有广泛应用。

关键字:现场可编程门阵列; 快速傅立叶变换; 基4蝶形运算; 硬件描述语言Implementation of FFT Algorithm Based on FPGALing MingtingAbstract: A 1024-point FPGA-based 16-bit FFT algorithm is designed which is using Radix-4 butterfly algorithm and pipeline operations to enhance the processing speed and improving the performance. A structure that the butterfly algorithm operation of the first level is made before the complex multiplication of the therotation factor of the second level is proposed, which using of the hardware resources reasonably. The system is divided into several modules in V erilogHDL. After testing the flexibility of DSP devices but also has the high speed data throughput of the dedicated FFT chips . This algorithm can be widely used in the field of digital signal processing.keywords : FPGA; FFT; radix-4 butterfly algorithm; V erilogHDL;硬件实现快速傅里叶变换(FFT)的方案包括:数字信号处理器(DSP)、专用集成电路(ASIC)和现场可编程门阵列(FPGA)。

其中DSP适合用于流程复杂的算法,例如在通信系统中信道的编码和解码,利用DSP进行FFT运算将占用大量DSP的运算时间,降低整个系统的数据吞吐率,也无法发挥DSP的灵活性;采用ASIC运行FFT运算完全能达到速度要求,但可扩展性差;FPGA具有可重构的特点,是适合于算法结构固定、运算量大的前端数字信号处理现在FPGA产品都采用多层布线结构,核心电压低、IO管脚丰富、容量可达到100K个逻辑单元,并且内置嵌入式RAM资源、集成多个数字锁相环和多个嵌入的硬件乘法器。

因此,FPGA在数字信号处理领域显示出自己特有的优势,并且也已经广泛应用近年来,国内也设计完成很多利用硬件方法处理FFT算法的实例,并且基于FPGA设备的方法也已经提出并正在实现但电子设备对速度的要求也越来越快,面对这种情况,针对目前所拥有的方法,设计出一种利用FPGA实现FFT运算的加速方案,并以1024点FFT为例,采用Quartus 与Matlab进行联合仿真。

1 算法及数据分析1.1 FFT 算法分析FFT 是DFT (离散傅里叶变换)的快速算法,而DFT 是数字信号处理中常用的一种算法,用来对信号频谱进行分析。

其基本公式是∑-===10)()]([)(N n nkN W n x n x DFT K X ; 式中旋转因子为e N jnk nk N Wπ2-=。

另外,x(n)表示时域信号,X(K)表示频域信号。

对于N 点DFT 需要N2log 级运算,每级需要N/2个蝶型运算单元。

一个FFT 运算单元如图1所示图1 蝶形运算符号Fig. 1 butterfly operation symbols其运算结果:BW A A +=',BW A B -='.而对于复信号而言,基本公式可以扩展为iXI(nXR(n)x(n)+= 因此,原式可以表示为 i nk n XR nk n XI nk n XI nk n XR W n x nk N )2sin()()2cos()([)2sin()()2cos()()(N-N +N +N -=ππππ 1.2 基4蝶形运算⎥⎥⎥⎥⎥⎦⎤⎢⎢⎢⎢⎢⎣⎡⎥⎥⎥⎥⎦⎤⎢⎢⎢⎢⎣⎡=⎥⎥⎥⎥⎦⎤⎢⎢⎢⎢⎣⎡P P P W X W X W X W X x x 3201111)3()1()2()0(j - 1- j 11- 1 1- 1j 1- j - 11 1 1 1)3()2()1(x (0)x (1) 式( 1)为基4蝶形运算单元的一般表达式。

其中,N j e W π2-=, N 为FFT 运算的点数, 本设计中为1024, p 为旋转因子W 的相位角。

X(0)、X(1)、X(2)、X(3)为原始数据,顺序输入RAM 后蝶形倒序输出, 与旋转因子复乘再进行4点蝶形运 A B 'A'BW-1算, 而(0)x 1、(1)x 1、(2)x 1、(3)x 1即为第1级蝶形运算的结果。

此时RAM 存储的原始数据已经清空, 将第1级蝶形运算结果再存回RAM 中, 按照一定的地址输出后, 与第2级的旋转因子复乘、4点蝶形运算, 得到第2级蝶形运算结果, 依此类推。

由于蝶形运算为同址操作, 所以第2级的RAM 写地址即为第一级的RAM 读地址。

2 算法的硬件实现2.1 系统框图本设计利用流水线技术来提高系统的性能, 系统框图, 如图2所示。

其中, 地址产生单元生成RAM 读写地址, 使信号以及相关模块启动、控制信号, 是系统的控制核心; 4点蝶形运算单元的最后一级输出不是顺序的; 旋转因子产生单元生成复乘运算中的旋转因子的角度数据; 旋转因子ROM 中预置了每一级运算中所需的旋转因子。

图2 系统框图Fig. 2 a diagram of the system在FPGA 设计中, 为提高系统的运行速度, 而将指令分为几个子操作, 每个子操作由不同的单元完成, 这样, 每一级的电路结构得到简化, 从而减少输入到输出间的电路延时, 在较小的时钟周期内就能够完成这一级的电路功能。

在下一个时钟周期到来时,将前一级的结果锁存为该级电路的输人, 这样逐级锁存, 由最后一级完成最终结果的输出。

也就是说, 流水线技术是将待处理的任务分解为相互有关而又相互独立、可以顺序执行的子任务来逐步实现。

本设计中, 4点蝶形运算单元、旋转因子复乘模块以及最后的精度截取模块采用流水线技术来处理。

2.2 算法原理1024点的基4- FFT 共需要5级蝶形运算, 每级需要计算256个蝶形, 其传输入数据旋转因子虚部ROM实部RAM虚部RAM 4点蝶形运算单元地址产生单元 旋转因子产生单元读地址写地址精度截取乘减器 乘加器旋转因子实部ROM统实现框图如图2所示。

图3 传统硬件FFT 实现框图Fig.3 traditional FFT hardware implementation block diagram考虑到第一级蝶形运算不需要旋转因子, 所以第一级的旋转因子复乘模块可以省略, 但本设计的硬件结构需要循环利用, 一般情况下, 可以对第一级数据进行!1运算, 再进行4点蝶形运算。

不过, 考虑到我们并不关心每一级蝶形运算后的结果, 本文提出了一种蝶形运算的新结构: 即先进行前一级的4点蝶形运算, 再进行本级的与旋转因子复乘运算, 如图3所示。

图4 本设计的FFT 硬件实现框图Fig. 4 FFT hardware realization diagram of this design可以看出, 图3减少了一个旋转因子复乘模块,不但节约了一次乘法运算时间, 也省略了第一级旋转因子, 更好地利用了硬件结构。

首先, 在Quartus 环境中对4点蝶形运算时序仿真, 采用流水线设计, 连续输入连续输出, 仿真结果如图4所示。

图5 四点蝶形运算仿真结果Fig.5 butterfly computation simulation results at four o 'clock第一级输入数据 四点蝶形运算 旋转因子相乘 ······ 四点蝶形运算旋转因子相乘 第五级输出数据第一级 第四级 四点蝶形运算 第五级第一级输入数据旋转因子复乘 四点蝶形运算 ······旋转因子复乘 四点蝶形运算 第五级输出数据 第一级 第五级由图4可以看出, 输出比输入延时6个时钟, 这在系统的控制核心地址产生单元的设计中需要考虑到。

2.3 地址产生与时序控制对于1024点基4FFT运算, 需要5级蝶形运算,每一级运算都要有写地址和读地址, 根据FFT同址运算的特点可知, 当前的写地址即是上一级蝶形运算的读地址。

因此完成FFT运算需要设计6级RAM地址。

其中第1级的写地址即是数据输入的顺序地址,不予讨论。

最后一级读地址为数据正序输出所需的地址。

其余4级为1024点数据对应的FFT蝶形运算。

第一级读取节点地址的顺序应该是: ( 0, 256, 512, 768), ( 1, 257, 513, 769),···, ( 255, 511, 767, 1023)。

易观察其读地址的规律如下:设读取次序的二进制编码为bit[ 9:0]; 则读地址的二进制编码为{ bit[ 1:0], bit[ 9:2] }, 并且依次可以推出第2、3、4级的读地址二进制编码分别为{bit[ 9:8], bit[ 1:0], bit[ 7:2] }, { bit[ 9:6],bit[ 1:0], bit [ 5:2] }、{ bit [ 9:4], bit [ 1:0],bit[ 3:2] }, 而最后一级输出数据的地址二进制编码则为: {bit[ 1:0], bit[ 3:2], bit[ 5:4], bit[ 7:6],bit[ 9:8] }。