DC基本问题

DC故障处理

精心整理H X D3C电力机车作业程序及常见故障处理操作方法常见应急故障处理行车故障应急处理前应注意以下事项1.故障处理前,必须将主手柄及换向手柄回“0”位,断开主断路器。

2.机车在运行途中断开下列开关或断路器均会造成机车惩罚制动:⑴电钥匙SA49(50)⑵微机控制1、2自动开关QA41(42)⑶制动机自动开关QA50⑷司机控制Ⅰ、Ⅱ自动开关QA43(44)⑸机车控制自动开关QA45⑹蓄电池自动开关QA61进行复位断蓄电池复位应按如下程序操作:司机控制手柄回零—换向手柄置零位—降弓—断主断—断开机车电钥匙—蓄电池自动开关QA61断开蓄电池30秒后,合蓄电池自动开关QA61再给机车电钥匙,升弓、合主断。

3.人为断开上述自动开关后,再重新闭合需要间隔30秒以上。

4.确认需要断开蓄电池自动开关QA61之前,应正确处理好监控装置的操作,并将列车停妥。

一、升不起弓1.某一端受电弓升不起,另一受电弓升弓正常则维持运行。

2.如果运行中某一受电弓频繁自动降下,(第一次自动降下时需观察是否发生刮弓)则为该受电弓管路漏风,关闭其气路控制板下方供风塞门(1端弓气路控制板在微机柜后方,2端弓气路控制板在制动柜后方),换另一台受电弓运行。

3.两台受电弓均不能升起(1)在空气柜检查升弓气路风压表应高于600kpa以上,如风压低,合升弓扳键,辅助压缩机将会自动打风,辅助风缸风压达到735kpa后,断开升弓扳键再次重合即可升弓;乘务员也可不合升弓扳键,在制动柜处按压右上方辅助压缩机按钮SB95,使用辅助空压机打风后再升弓。

(2)检查控制电器柜司机控制自动开关QA43或QA44应在闭合位,断合几次,防止假跳。

(3)检查空气柜蓝钥匙U99是否在开放位(垂直状态),检查空气柜升弓塞门U98是否在开放位。

(4)检查高压接地开关QS10是否在“运行”位。

二、途中刮弓(1)立即断主断降弓停车,迅速关闭制动柜控制风缸塞门U77存风,马上向列车调度员报告列车车次、机车号码、刮弓地点、司机姓名等有关内容,并申请停电,做好防溜防护。

简述dcdc转换器的故障排除流程

当处理一个曲折的DC—DC转换器时,关键是用侦探解决一个谜题的精准度处理故障排除过程。

第一个业务顺序是让小转换器彻底检查一次,检查任何物理损伤或发热脾气的迹象。

注意烧焦的斑点松散的连接物或多氯联苯上任何看上去像是在争吵的痕迹就像检查婴儿的温度一样,确保输入和输出在指定范围内发挥良好。

任何偏离电压和当前收视率的情况都会导致全面暴跌或全面崩溃!显示转换器一些爱和关注,让我们开始这个权力游戏的底部!

一旦我们给了转换器一次是时候用动力测试让它复活了我们将使用诸如示波器或多米器等微小工具,密切注视输入和输出电压,电流和波形。

这就像我们偷看转换器的心脏看看输出波形中是否有任何异常,如过度波纹或噪音。

这并不是全部,我们还将检查转换波形,以确保控制电路和动力半导体中的一切运行顺利。

等等,还有更多!我们甚至会用热成像相机来寻找转换器上的热点为什么?因为这些热点可能告诉我们里面的热量有点高说到用转换器的温度

如果最初的视觉和动力测试没有发现任何明显的打嗝,也许是时候把大炮打碎,潜入DC—DC转换器的世界。

我们说的是专门的测试设备来真正地把这些东西通过它们的脚步。

装入调节测试,效率测量,以及瞬态反应测试将告诉我们这些转换器如何处理不同的情况。

如果我们真的想到 nitty—gritty,我们可以检查输入和输出电容器的电容和ESR,或者给这些二极管和晶体管一个很好的老式测试,来除草任何麻烦制造者。

有了正确的工具和系统的方法,我们就能让这些转换器

在不远的时间内像一台油气良好的机器一样运行。

让我们潜入并释放测试的力量!。

DC综合问题总结

DC综合问题总结第一篇:DC综合问题总结DC综合以及后仿问题总结日期:2013.08.24 关于DC综合出现的一些warning以及解决方法:1)当出现这种unsign to signed warning出现的时候一般是代码中出现了一下两种不规范的写法:第一种:例如:wire data_A assign data_A=(判断条件)?1:0;即:定义一个wire类型的信号data_A,然后通过一个判断条件的真假来个data_A进行赋1或者0,那么这样的写法就会造成上面例句的warning,这是因为在verilog中直接写1或者0,那么verilog就会把1或者0默认为整型变量,而整型变量默认的是有符号数,而我们定义的data_A是一个无符号信号,那么正确的写法应该为wire data_A assign data_A=(判断条件)?1’b1:1’b0,这样写才是规范的写法。

第二种:这种情况warning主要出现在一些用到了有符号数运算的电路中,比如我们要计算两个8bit有符号数的加法、减法、乘法等,而其中一个有符号数要通过别的寄存器进行赋值,比如总线寄存器(即:要进行运算的数通过总线赋值),那么我们可能会这样写:wire signed [7:0] A;assign A=bus_data_reg[7:0],这样写verilog就会把bus_data_reg[7:0]默认为一个无符号数,可是我们的A要求是一个有符号数,故就会出现上面列举的warning,正确的写法应该是wire signed [7:0] A;assign A=$signed(bus_data_reg[7:0]);,总的来说就是,我们要给一个有符号数的信号赋值,那么我们就应该保证等号两边都是有符号数,verilog中可以用$signed将一个数定义成有符号数。

同样当出现signed to unsigned这样的warning后,我们用上面同样的方法进行分析就可以解决了2)当综合之后出现这种类型的warning时,说明你的代码中在实例化某个模块的时候你只把该信号的某几bit连接到了该模块的端口上,这种警告的出现是比较常见的,比如上图所示:这表明在代码中send_check_bus_addr是一个11bit的输入信号,它的第6~10bit没有连接到该模块的端口上,即:这样的警告的出现是正常的,对DC综合的结果没有太大的影响。

DC-DC转换器疑问2

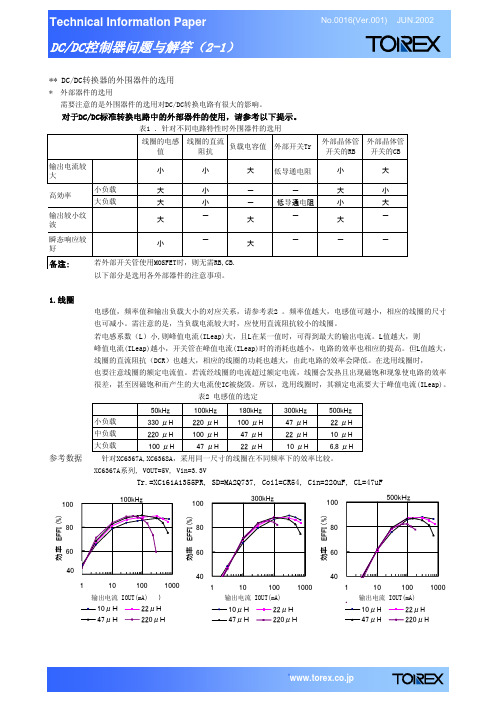

b: 并且请选用开关速度快的(导通时的延迟时间td(on)短,tr的上升时间短,关闭的延迟时间td(off)短) 功率MOSFET,因为开关速度快,电路的功率会提高。

c: 请选用栅极和源极之间的关闭电压Vgs(off)远低于输入电压的功率MOSFET。在IC的电源电压低于1.2V的 情况下,请选用晶体管。

10μH

22μH

47μH

220μH

'www.torex.co.jp

Technical Information Paper

No.0016(Ver.001) JUN.2002

DC/DC控制器问题与解答(2-2)

XC6368A系列, Vout=5V Vin=3.3V Tr.=XC161A1355PR, SD=MA2Q737, Coil=CR54, Cin=220uF, CL=47uF

当RB阻值较小(200--500Ω),输出电流会增大,小负载时,电路的效率会降低。 当RB阻值较大(750--2KΩ),输出电流会减小,小负载时,电路的效率会提高。

当Tr导通时,可由集电极电流ISW(Ic)求出RB的值。

ISW(Ic)=hFE x IB = Vout ÷ (RB + REXTH) RB ≦(Vout-0.7)×hFE ÷ ISW(Ic) - REXTH

5-2.晶体管Tr.

a: 请选用电流放大系数hFE为100--500的晶体管。但请注意,hFE若太大的话,基极电流会很小, 极间反向电流会很大。

b: 请选用开关速度快的(导通时的延迟时间td(on)短,tf的下降时间短,ts,tg的累积时间短)晶体管。 因为开关速度快,电路的效率会提高。请选用集电极的输出电容Cob(几十pF左右)较小的晶体管。

100kHz

DC-DC模块电源产品常见问题解答

0匸~0〔模块电源产品常见问题解答00-00模块电源是可以直接贴装在印刷电路板上的电源供应器,其特点是可为专用集成电路(入810、数 字信号处理器⑴^?)、微处理器、存储器、现场可编程门阵列斤?6入)及其他数字或模拟负载提供供电。

一般 来说,这类模块称为负载点(^^^)电源供应系统或使用点电源供应系统0现8》。

由于模块式结构的优点甚多,因此模块电源广泛用于交换设备、接入设备、移动通讯、微波通讯以及光传输、路由器等通信领域和汽车电子、航空航天等。

顺源科技作为国内资深模块电源技术应用研发生产厂家,根据多年的研发生产经验和技术服务工程 师广泛收集的工业现场各种不同环境下用户反馈宝贵意见,在对产品性能不受影响前提下逐步对各项技术指标进 行改进改善的同时,将工程师现场遇到的一些技术问题进行记录、收集整理,希望给广大用户提供一些技术参考 和现场应用解决方案的支持。

今后如收集到更多的技术问题解决方案,我们会及时更新信息。

欢迎用户在现场 应用中把遇到的问题或投诉建议发送到我公司的技术支持邮箱:8聊@8脏丫仙虹0爪:外8@8脏丫仙虹0爪小功率电源模块〔不包含训圆系列)客户常见问题解答1、顺源科技00-00电源模块有哪些系列?小功率电源模块〜3撕;0^6系列高电压输出的最大功率10撕〕包括①定电压输入,隔离非稳压输出系列:八/8/13系列……1(^八。

隔离、定电压输入非稳压输出已/卜系列…3^^六0隔离、定电压输入非稳压单7双输出0/6系列……6^乂八0高隔离、定电压输入非稳压输出/卩「系列…定压输入非稳压31^隔离短路保护巳狀系列…1…隔离、变送器两线制回路取样配电电源②定电压输入,隔离稳压输出有过载短路保护系列:I八厂旧乂0系列…1匕乂八匚隔离、定压输入稳压保护输出㈧卩户/卯卩已系列…36^隔离定压输入稳压短路保护输出③定电压输入,隔离稳压输出有过载短路和81^保护抗浪涌系列:㈧只叫/V[^系列…31^隔离、8心抗浪涌稳压保护输出㈧叫/㈧!^系列…6心隔离、抗浪涌稳压保护输出④定电压输入,非隔离高电压输出系列〔50〜600乂〉如下:6只8系列…高压输出短路保护、非隔离型宽电压输入2、00-00电源模块一般应用在哪些场合?顺源科技生产的00-00转换器,无需任何外围元件便可在一般的常规电路中直接使用。

DC-DC电源模块常见使用问题剖析与处理

DC-DC电源模块常见使用问题剖析与处理微功率DC-DC电源模块以高集成度、高可靠性、简化规划等多重优势,遭到许多电子规划者的喜爱。

电源模块尽管运用电路简略,操作简略,但往往在运用时仍是会遇到一些常见问题。

针对此本文对电源模块常见的运用问题以及怎么排除故障进行具体的剖析,期望对规划者的电源模块选型时有所协助。

常见问题一:输出纹波噪声偏大原因1:模块在运用时,负载为动态负载,使得模块输出电压峰峰值变大,但留意这不是纹波噪声。

当负载电流假如进行周期性骤变时,模块输出电压的峰峰值会变大。

这是一个瞬态量,但有时会被误以为是纹波噪声。

所以当运用一个电源模块给多个电路单元供电时,关于有周期性负载改动的电路,前级需求添加π型滤波,减小这部分电路的瞬态改动对其他电路的搅扰。

例如,下图中电路B由于负载巨细的改动,使得输入电压动摇。

为了减小电路B对电路A的搅扰,主张在电路B的输入端添加π型滤波。

图 1 电路链接框图原因2:示波器地线问题在测验电源输出的纹波噪声时,示波器的地线夹和地线、模块输出引脚构成一个环路,类似于天线接收器,会引进其他噪声。

假如测验的环境搅扰大,这种噪声也会由示波器引进,影响纹波噪声测验的成果。

且往常咱们购买的示波器探头的地与示波器内部的大地线相连,这种状况对工频搅扰的抗扰才能弱,简单引进搅扰噪声。

所以在运用中最好确保示波器探头浮地处理(阻隔开示波器的电源地,或许直接运用电池供电的示波器),削减引进的搅扰。

假如丈量目标的供电电源也是浮地,这样更好,这样就不会导致电路特性的改动,使模块输出噪声增大。

常见问题二:模块发动后,输出电压偏低原因1:输入端有防反接电路图 2 模块防反接链接框图举例:图2中的ZY_FKES-3W模块是定压输入非稳压输出模块,其输出电压会跟着输入电压和负载巨细的改动而改动的。

由于在电路规划时,在其输入侧添加了防反接二极管,所以这会导致到模块输入端的电压下降,然后输出电压变小。

DC基本知识问答

什么是DC?DC(Design Compiler)是Synopsys公司的logical synthesis工具,它根据design description和design constraints自动综合出一个优化了的门级电路。

它可以接受多种输入格式,如HDL、Schematics、Netlist等,并能生成多种性能report,在reducing design time的同时提高了设计的性能。

DC能接受多少种输入格式支持.db、.v、.vhd、.edif、.vgh、.lib等,.db一般是厂商的单元库;.v是veilog的后缀;.vhd是VHDL的后缀;.edif 和.vhd是两种形式的netlist。

DC提供多少种输出格式提供.db、.v、.vhd、edif、.vgh等,并可以输出sdc、sdf等相关格式文件。

DC的主要功能或者主要作用是什么DC是把HDL描述的电路综合为跟工艺相关的门级电路。

并且根据用户的设计要求,在timing、area、power上取得最佳的效果。

在floorplanning和placement和插入时钟树后返回DC进行时序验证。

如何寻找帮助帮助可以用3种求助方式:1. 使用SOLD,到文档中寻求答案2. 在命令行中用man+ DC命令(我最喜欢这种)3. 在命令行中用info+ DC命令如何找到SOLD文档SOLD文档可以在teminal中输入sold&执行。

$> sold&或者用命令which dc_shell找到dc的安装目录。

找到online目录。

如何配置DC综合设置提供必要的参数给DC,使工具能够知道进行综合时所需要的必要的信息,如:工艺库,目标库,标志库等等。

要在.上设置好这些参数。

而.要在三个目录下有说明,一个是synopsys的安装目录,一个是用户文件夹,最后一个是工程目录。

由后一个设置覆盖前一个文件。

具体参数包括:search_path, target_library, link_library, symbol_librarytarget_library 是指什么target_library是在synthesis的map阶段时需要的实际的工艺库。

DC-DC常见问题解答

流过电感的电流I PEAK 的大小由R LIM决定,而I PEAK 是选择电感的重要参数,I PEAK 越大,也意味着电磁干扰EMI越大;另外,从公式(1)我们也可看出I PEAK 对于这个DC/DC电路的效率的影响。

【关闭窗口】

-------------------------------------------------------------------------------

-

公司介绍 产品指南 方案推荐 客户服务 产品应用 设计与知识 新品速递 友情链接 返回主页

DC-DC常见问题解答

1. 为何DC-DC转换器的带载能力达不到给定的功率要求?

这种情况绝大多数出现在电感的指标未能满足要求,而对于应用于DC-DC中的功率电感来说,必须考虑以下指标:最大饱和电流值(饱和电流越大,功率输出能力越大)、电感值(在相同的开关峰值电流条件下,电感值越大,输出功率的能力越大)、频率特性(必须满足开关频率下的特性)、绕线电阻值(电阻越小,效率损失越小)和EMI(电感的电磁辐射干扰,决定是否需要选择低辐射或屏蔽的罐装电感)。如果输出功率达不到IC所能提供的额定值,通常与电感的前三个参数有关。解决步骤:1)保证电感的频率特性满足要求;2)保证电感的饱和电流值大于开关的峰值电流;3)在最大开关峰值电流不变的条件下,可以适当增大电感值,以提高功率输出能力。4)如果开关频率允许调节,则提高开关频率,将增大输出功率;5)如果开关峰值电流允许调节,则增大开关峰值电流,将增大输出功率。

2. 为何DC-DC转换器的输出纹波远远超出IC指标?

对于基于开关型的DC-DC转换器,其输出电压纹波与下列参数有关:1)开关频率,在电路其它条件不变的前提下,工作频率越高,输出电压的纹波越小;2)电感值,电感值越大,输出纹波越小;3)电容值,输出电容越大,输出纹波越小;4)电容的等效串联阻抗(ESR),ESR越小,输出纹波越小;5)电感的峰值电流,峰值电流越大,输出纹波越大。解决方法:一方面,根据负载电流要求,计算出合适的电感峰值电流,以选择合适的电感值;另一方面,在成本允许的范围内,尽量选择等效串联电阻较小的输出电容,当然,多个输出电容并联会进一步降低输出电容的串联等效电阻。此类电容一般选用低串联等效电阻的钽电容或电解电容,普通铝电解电容不能满足此项要求。另外,请注意:许多电容的等效串联电阻在温度低于0℃以后,其等效串联电阻会显著地增大,使电源输出纹波也随之变大。

DC综合基础

EDA实践

03 解读相关库

4 符号库(symbol_library) 定义了单元显示的图形库。 5 综合库(synthetic_library) 由Synopsys提供的designware库,包含很多IP核及运算单元,用来实现Verilog描述 的运算符。如果要Foundation的DesignWare,除了需要有DesignWare Foundation的 Licesen之外还需要在综合的时候设置synthetic_library。 set synthetic_library {dw_foundation.sldb} 调用designware里的ip核 Lappend link_library $dw_foundation.sldb lappend表示把某项添加到某列表 的末尾。

解读相关库

03 解读相关库

1 搜索路径(search_path) 指各种库的路径,包括库的路径和将要输入的代码文件的路径,设定后在下面设置 库时就不必添加库的绝对路径,DC会自动在输入的路径下搜索。

2 目标库(target_library) 即工艺库,在DC在编译(compile)时用来构成电路图的,将电路映射到具体单元上。 电路的延时信息从这里得到,根据各个单元延时、面积和驱动能力的不同选择合适 的单元 来优化电路。 3 链接库(link_library) 是算法库或者设计库,将设计连接到对应的库上,设置模块或者单元电路的引用, 对于所有DC可能用到的库,我们都需要在link_library中指定一般包含目标库、宏 单元、IP核等。 (库前的*说明当链接设计时,DC先搜寻已经调进DC memory的模块和单元电路,如 果在link library 中不包含’*’,DC就不会使用DC memory中已有的模块,因此, 会出现无法匹配的模块或单元电路的警告信息(unresolved design reference)。然 后再搜寻变量link_library中指定的其它库)

DC综合教程范文

DC综合教程范文DC(Direct Current,直流电)综合教程直流电(DC)是一种电流方向始终保持一致的电流。

在直流电综合教程中,我们将探讨直流电的基本概念、原理、应用以及如何进行直流电的测量和分析。

一、直流电的基本概念和原理1.直流电的定义:直流电是电流方向始终保持不变的电流。

相对于直流电,交流电(AC)的电流方向根据时间周期变化。

2.直流电的产生:直流电可以通过许多方式产生,最常见的方式是使用电池。

电池中的化学反应将化学能转化为电能,并在电路中产生直流电流。

3.直流电的电压和电流:直流电的电压是指电流在电路中的压力或能量。

电流是电荷在单位时间内通过导体的速率。

电压通过电压表或示波器进行测量,而电流可以通过电流表测量。

4.直流电的电路:直流电流通常通过电路中的导线、电阻、电容器和电感器等元件流动。

在电路中,电源提供电流,而负载消耗或利用电流。

5.直流电和交流电的差异:直流电和交流电有很多差异。

直流电的电流方向始终保持不变,而交流电的电流方向由于周期性的变化。

直流电的电压和电流大小在一段时间内保持恒定,而交流电的电压和电流大小会根据时间周期变化。

二、直流电的应用直流电在许多领域中都有广泛的应用,以下是几个常见的应用领域:1.电子设备:直流电被广泛应用于各种电子设备,如计算机、手机、平板电脑等。

电子设备通常使用直流电来供电。

2.电动机和发电机:直流电被用于驱动各种类型的电动机,如直流电动机、步进电动机等。

直流电也被用于发电机来产生电能。

3.太阳能电池板:太阳能电池板将太阳能转换为直流电。

这些直流电可用于供电家居设备、电动车辆等。

4.电解过程:直流电在电解过程中起着重要作用。

在电解过程中,电流通过电解质溶液,将化学物质分解为其组成元素。

5.电磁铁:直流电可以通过电磁铁产生电磁力,从而实现吸引和释放物体的目的。

这在电动门、电梯等设备中得到应用。

三、直流电的测量和分析测量和分析直流电是电子工程师和技术人员的常见任务之一、以下是几种常见的直流电测量和分析方法:1.电压测量:直流电的电压可以通过电压表测量。

DC-DC设计注意事项

反馈电路

• 输出电压可调的DC-DC, 反馈电阻必须是高精密的电阻。一般 DC-DC电路是靠反馈电压来调整工作模式, 反馈电压如果波动太 大, 则振荡的占空比也是一直变化。根据傅立叶分析方法, 占空比变 化将增加电压、电流的谐波分量, 对EMC测试就不利。

如何选择电解容

• 一般温度变化引起电视机不稳定的问题跟电容的特性有很大的关系 。常见的问题是低温噪波,干扰增加,甚至低温无法开机。一个很 主要的原因是我司的电容入库前并没有在不同温度下测试,同时, 不同厂家的电容共用一个编号。另一个更主要的原因是设计师本身 在最初设计时没有考虑这个问题,或者考虑到但没有条件测试。这 里有个比较简单可行的方法:在体积一样的条件下,选择耐压高, 容量大的电容(为什么? 自己思考);条件允许的情况下,选择高 纹波电容。以下是电解容的一些知识:

滤波电容

• 可分为输入电容和输出电容。实际应用中, 我们都选择电解电容作 为储能滤波电容, 但一定要在每个电解容傍边增加一个100nf的磁 介容来“保护”该电解容(原因请自己思考)。对于输入输出 电 容一般来说都是越大越好, 但应考虑过大的输入电容将增加前端电 路的压力(特别是前端是二极管+电容的稳压电路), 过小则起不 到储能作用, 一般470uF-680uF 为宜。对于输出电容一般也 是越 大越好, 但过大将导致上电慢, 对于有些CPU的上电可能无 法满足 要求, 过小则纹波电压大。一般选择470uf-1000uf.

输出的纹波电流哪里来?

• 输出电容的改变能改变流过该电容的纹波电流吗?

•

经过对比发现,对于电解电容,流过该电容的纹波电流几乎

不随不同的电容而改变,换句话说,电解电容上的纹波电流是由

电路本身决定! 为什么?

• 滤波电感可以改变纹波电流

DC经典入门问题

~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~ 在综合中,ungroup命令可以去除系统的层次,有利于减小面积。

我对比了在使用ungroup -all -flatten 命令前后的Total cell area。

在使用该命令之前Total cell area是102396,使用之后49663,减小了一半左右。

时序部分也没有变差。

那是不是综合脚本一般都要使用ungroup呢?请指教,谢谢。

ungroup -all当然是能达到最大的优化力度啊,整体timing最好,但是有时候会导致功能的变化,仿真没法过,比如某个hier boundary没了,因此只是有限度的ungroup,比如-level 3,全部ungroup打散后,没有boundary,一般功能是不会影响的,LEC来保证。

但是function 层次就没有了,比如对网表做一些verification,如STA时一些重要的点可能找不到了,如果还要debug的话几乎做不下去。

后端fix后某些点发现需要做function ECO,那么很可能也没法做了。

另外ungroup也分具体情况也不是所有情况下就一定明显减小面积,我们一般是有选择地对个别一些联系紧密的module会ungroup,不过目的是为了打掉boundary得到更好的timing不是面积。

纯属个人理解LEC是logical equivalent check,主要比较RTL和NETLIST,NETLIST和NETLIST的逻辑功能一致性。

通常来说,synthesis以后,会把RTL和综合得到的netlist 比较,以保证综合没有造成逻辑的错误。

PR以后,也会做同样的check。

DC-DC系列模块电源常见故障分析

3:实际负载过轻,轻于10%额定负载

采取措施:

1:将输入电压调准

2:确保模块工作时输出端至少有8%的额定负载。若实际电路工作中会有空载现象,就在输出端并接一个额定功率8%的假负载,确保电源模块实际负载至少达到额定负载的10%

三、上电后电源损坏

产生原因:

1:输入电源极性接反

2:输入电压远远高于标称电压

9:输出外接电容应小于技术手册规定的最大值,一般根据输出电流选电容值,原则是1uF/100mA(对于输出功率小于0.5W及输出电压高于20V的产品,建议不外接电容),如果需降低输出纹波,可先在输出端串联一个4.7-10uH电感后再并联一个电容组成LC型滤波电路。

二、输出电压高于标称值

产生原因:

1:输入电压偏高

3:输出外接电容太大或电容耐压不够

4:输出电路易引起短路

5:SMD产品输出空载

采取措施:

1:在输入端串联一个低压降的二极管作为防反接保护

2:重新设定输入电压

3:输出外接电容应小于技术手册规定的最大值,一般根据输出电流选电容值,原则是1uF/100mA(对于输出功率小于0.5W及输出电压高于20V的产品,建议不外接电容),如确需要降低输出纹波,可先在输出端串联一个4.7-10uH电感后再并联一个电容组成LC型滤波电路。电容耐压值至少要达到电源电压的1.5倍以上。

4:在输出端增加短路保护电路

5:输出端加至少10%的负载

四、系统运行中电源损坏

产生原因:

采取措施:

五、输出电压低于标称值

产生原因:

采取措施:

六、输出电压低于标称值

产生原因:

采取措施:

七、输出电压低于标称值

产生原因:

使用dc进行逻辑综合的基本步骤

使用dc进行逻辑综合的基本步骤该文档是本店铺精心编制而成的,希望大家下载后,能够帮助大家解决实际问题。

该使用dc进行逻辑综合的基本步骤该文档下载后可定制修改,请根据实际需要进行调整和使用,谢谢!本店铺为大家提供各种类型的实用资料,如教育随笔、日记赏析、句子摘抄、古诗大全、经典美文、话题作文、工作总结、词语解析、文案摘录、其他资料等等,想了解不同资料格式和写法,敬请关注。

文档下载说明Download tips: This document is carefully compiled by this editor. I hope that after you download it, it can help you solve practical problems. The document 使用dc进行逻辑综合的基本步骤can be customized and modified after downloading, please adjust and use it according to actual needs, thank you! In addition, this shop provides you with various types of practical materials, such as educational essays, diary appreciation, sentence excerpts, ancient poems, classic articles, topic composition, work summary, word parsing, copy excerpts, other materials and so on, want to know different data formats and writing methods, please pay attention!DC综合是数字电路设计过程中非常重要的一步,它将逻辑功能描述转换为对应的门级电路。

非凸优化的DC算法及其应用

问题的难点与挑战

非凸优化问题的求解非常困难,因为其最优解可能存在于一个多维空间中的局部最 优解集合中,而这个集合可能包含大量的局部最优解。

在求解非凸优化问题时,传统的优化算法往往不能找到全局最优解,而是只能找到 局部最优解。

非凸优化问题的DC解决方案案例二

总结词

DC算法在图像处理中的优势应用

VS

详细描述

DC算法在图像处理中也得到了广泛的应 用。例如,在图像去噪问题中,通过构建 一个包含噪声水平和目标图像的DC方程 ,DC算法能够实现快速且高效的去噪效 果。此外,DC算法在图像分割、特征提 取等任务中也具有优势应用。

非凸优化问题的DC解决方案案例三

• min f(x) = f1(x) - f2(x) - ... - fn(x)

优化目标的数学表达式如下 • 其中,f1(x), f2(x), ..., fn(x) 是二次函数。

DC算法的迭代过程

DC算法的迭代过程包括以下 几个步骤

• 初始化:选择一个初始点 x0,以及一个步长α。

• 迭代更新:在每一次迭代 中,根据当前点x和步长α ,计算下一个点x' = x + α * d,其中d是当前点的 梯度方向。

• 判断终止条件:如果达到 预设的迭代次数或者目标 函数值满足一定的精度要 求,则停止迭代,否则继 续进行迭代更新。

03

非凸优化问题的DC算法 设计

基于DC分解的算法设计

01

DCA算法

将非凸函数分解为两个凸函数之 差,采用分步迭代的方式逐步逼 近最优解。

DC规划

02

03

DC松弛

积分器dc偏移

积分器DC偏移在电子系统和信号处理中,积分器是一种基本而重要的元件,广泛应用于各种电路和系统设计中。

然而,在实际应用中,积分器可能会受到一种被称为DC偏移(DC Offset)的影响。

本文将详细探讨积分器DC偏移的现象、成因,以及针对这一问题的各种解决方案。

一、积分器与DC偏移概述积分器是一种将输入信号进行积分运算的电路或系统。

在理想情况下,积分器应能够对输入信号进行精确的积分,但在实际应用中,由于电路元件的非理想特性、环境因素等原因,积分器的输出可能会出现偏差,这种偏差就是DC偏移。

DC偏移是指在没有输入信号或输入信号为零时,积分器的输出并不为零,而是存在一个固定的偏移量。

这种偏移量会对积分器的性能和精度产生负面影响,特别是在需要高精度积分的应用中,如模拟计算、信号处理、控制系统等。

二、DC偏移的成因积分器DC偏移的成因是多方面的,主要包括以下几个方面:1. 运算放大器的非理想特性:实际运算放大器的输入失调电压、输入偏置电流等参数会导致输出存在DC偏移。

2. 电容的漏电:积分器中的电容器并非理想元件,会存在一定的漏电现象,导致电荷积累和输出电压的变化。

3. 温度漂移:随着温度的变化,电路元件的参数也会发生变化,从而导致DC偏移的产生。

4. 电源电压波动:电源电压的不稳定也会导致积分器输出的DC偏移。

三、DC偏移的影响积分器DC偏移会对系统的性能和精度产生显著影响,具体表现在以下几个方面:1. 积分精度下降:DC偏移会导致积分器的输出偏离真实值,从而降低积分精度。

2. 系统稳定性受损:在反馈系统中,DC偏移可能引发正反馈,导致系统不稳定。

3. 信号失真:DC偏移可能使信号在处理过程中发生失真,影响信号质量。

4. 动态范围减小:DC偏移会占用积分器的输出范围,从而减小系统的动态范围。

四、DC偏移的解决方案针对积分器DC偏移的问题,可以采取以下几种解决方案:1. 选用高性能运算放大器:具有低输入失调电压、低输入偏置电流等特性的运算放大器可以减小DC偏移。

dc电压输出的原理

DC电压输出的原理一、引言在电力电子技术和电子设备中,DC电压输出是一种常见的电源特性。

DC 电压输出指的是电源输出的电压为直流电压,这种输出方式与交流电压输出相对应。

DC电压输出在许多领域都有广泛的应用,如电池供电设备、电动汽车、电子仪器等。

本文将详细介绍DC电压输出的基本原理、工作方式、应用领域、优缺点及未来发展趋势。

二、DC电压输出的基本原理DC电压输出的基本原理基于电荷的累积和流动。

当电荷在一个电场中累积时,会在电场力的作用下产生电流。

DC电压输出就是通过一种称为整流的电路,将交流电转换为直流电的过程。

整流电路主要由二极管构成,利用二极管的单向导电性实现电流的整流,从而产生稳定的直流电压输出。

三、DC电压输出的工作方式DC电压输出的工作方式主要有以下几种:1.直接输出方式:DC电源直接提供直流电压输出,无需经过任何转换。

这种方式的优点是效率高、稳定性好,但输出电压的范围和稳定性取决于电源的内部结构和参数。

2.稳压输出方式:DC电源通过反馈电路控制输出电压的稳定性,使其保持在一定的范围内。

这种方式能够提供稳定的输出电压,但电路结构相对复杂,效率较低。

3.变换器输出方式:DC电源通过变压器和整流电路将交流电转换为直流电,以提供所需的电压输出。

这种方式适用于大功率电源,可以同时实现电压变换和电流控制。

四、DC电压输出的应用领域DC电压输出在以下领域中有着广泛的应用:1.电池供电设备:大多数便携式电子设备都采用电池供电,如手机、笔记本电脑等,这些设备中的电源管理芯片将电池的化学能转换为直流电能供设备使用。

2.电动汽车:电动汽车中的动力电池提供直流电能,通过逆变器将直流电转换为交流电驱动电机运转。

3.电子仪器:许多电子仪器需要稳定的直流电压才能正常工作,如示波器、信号发生器等。

4.工业控制:在工业控制领域中,直流电机、伺服电机等都需要直流电能来驱动,而直流电压输出为这些电机提供了稳定的能源供应。

5.通讯设备:通讯设备中的信号处理电路和射频模块都需要直流电压才能正常工作,DC电压输出为这些设备提供了可靠的能源支持。

都是DC惹的“祸” 细说DC

都是DC惹的“祸” 细说DC

DC-DC转换器

这里会详细讨论DC-DC转换器的抗干扰性这一主题,先简单聊聊DC-DC 转换器,自从电子学诞生以来,就流传着一句老话…“所有问题都是DC问题。

”

当然,DC指“直流”,即电路中穿过导体由A点至B点的单向电流。

我们知道,这里所说的“问题”意思很简单,就是…问题。

那幺,为什幺所有问题都是DC问题呢?

我们知道,电流和电子简单来说是完整电路系统中,各种导体和器件中的电流产生的能量。

因此,归根结底是一种能量转换。

能量是做功的能力,以两种形式存在:1)势能和2)动能。

势能是一种非活动状态的蓄能(如电池端子间的电压)。

动能是势能转变为活动状态时产生的能量(如电流穿过灯泡)。

电子学简单来说是通过控制各种导体中的电流,将势能(电压) 转变为动能(电流) 的科学! 欧姆‘DC定律’必须始终满足能量转换才能产生作用!因此,电路输入与输出之间的每一部分,无论是否具备AC功能,必须出色设计电路的DC结构,才能有效支持无论何种形式的能量转换。

换句话说,如果电路DC设计不良,不可能实现AC性能。

这种情况给设计师造成极大压力,需要在电源与接地之间“模拟设计”的基础上,掌握多学科领域高水平专业技术。

相对于各种输入信号,要想在各种电压条件下以低噪声转换直流(DC),首先需要选择正确的DC-DC转换器。

DC-DC转换器有各种尺寸和类型:转换器包括线性、开关模式和磁电等不同类型。

而且,升压(步升) 和降压(步降) 功能采用类型各异的能量转换电路。

正确了解这些电路类型,可以避免使用时性能下降。

后面,我们可以分。

DC基本知识问答

D C基本知识问答-标准化文件发布号:(9556-EUATWK-MWUB-WUNN-INNUL-DDQTY-KII1.1 什么是DC?DC(Design Compiler)是Synopsys公司的logical synthesis工具,它根据design description和design constraints自动综合出一个优化了的门级电路。

它可以接受多种输入格式,如HDL、Schematics、Netlist 等,并能生成多种性能 report,在reducing design time的同时提高了设计的性能。

1.2 DC能接受多少种输入格式?支持 .db、.v、.vhd、.edif、.vgh、.lib等,.db一般是厂商的单元库;.v是veilog的后缀;.vhd是VHDL的后缀;.edif 和 .vhd是两种形式的netlist。

1.3 DC提供多少种输出格式?提供 .db、.v、.vhd、edif、.vgh等,并可以输出sdc、sdf等相关格式文件。

1.4 DC的主要功能或者主要作用是什么? DC是把HDL描述的电路综合为跟工艺相关的门级电路。

并且根据用户的设计要求,在timing、area、power上取得最佳的效果。

在floorplanning和placement和插入时钟树后返回DC进行时序验证。

1.5 如何寻找帮助?帮助可以用3种求助方式:1. 使用SOLD,到文档中寻求答案2. 在命令行中用man+ DC命令(我最喜欢这种)3. 在命令行中用info+ DC命令1.6 如何找到SOLD文档? SOLD文档可以在teminal中输入sold&执行。

$> sold&或者用命令 which dc_shell找到dc的安装目录。

找到online目录。

1.7 如何配置DC?综合设置提供必要的参数给DC,使工具能够知道进行综合时所需要的必要的信息,如:工艺库,目标库,标志库等等。

dc里那些有趣的冷知识

dc里那些有趣的冷知识DC(Direct Current,直流电)是指电流方向始终保持不变的电流。

与之相对的是AC(Alternating Current,交流电),交流电的电流方向会不断变化。

冷知识一:直流电是直线传播的直流电在导体中的传播是直线传播,而交流电在导体中的传播是沿着导体表面传播的。

这是因为直流电的电流方向始终不变,电流会沿着导体内部的路径直线传播;而交流电的电流方向会不断变化,电流会沿着导体表面传播,这也是为什么高频交流电会在导体表面集中传播的原因。

冷知识二:直流电的电阻与电流方向无关在直流电中,电流的方向对电阻的大小并没有影响。

电阻是指导体对电流流动的阻碍程度,与电流方向无关。

这就意味着,无论电流是从正极到负极,还是从负极到正极,对于相同的导体而言,电阻都是一样的。

冷知识三:直流电可用于长距离输电由于直流电在导体中的传播是直线传播,相对于交流电而言,直流电在输电过程中的能量损耗更小。

因此,直流电可以用于长距离输电,减少能源的损耗。

这也是为什么在远距离的高压输电线路中,往往会采用直流输电的原因之一。

冷知识四:直流电有极性直流电在电路中有极性之分,分为正极和负极。

正极是电流流出的地方,负极是电流流入的地方。

在电路中,正极和负极之间会产生电压差,电流会从正极流向负极。

这与交流电不同,交流电没有极性之分。

冷知识五:直流电可用于电子设备由于直流电的特性,直流电可以更好地应用于电子设备中。

许多电子设备需要稳定的电压和电流,而直流电可以提供稳定的电流。

因此,在电子设备中,直流电经常被用于供电,如电脑、手机等。

冷知识六:直流电在电化学中的应用直流电在电化学中有广泛的应用,如电解、电镀等。

在电解过程中,直流电会使电解质分解成离子,从而产生化学反应。

在电镀过程中,直流电会使金属离子在电极上还原成金属层,实现金属的镀覆。

冷知识七:直流电与生活息息相关直流电在我们的日常生活中有着广泛的应用。

家用电池输出的电流就是直流电,用于给电子设备供电。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

1.14. translation这一步是用什么DC命令来实现的?

我们知道,DC综合过程包括3个步骤:translation + logic optimization + mapping

transition 对应命令为 read_verilog(read_vhdl等)

logic optimization 和 mapping 对应于 compile

1.15. 逻辑优化和映射(logic optimization + mapping)又是用什么DC命令来实现的?

logic optimization 和 mapping 均在compile命令完成,但是可以指定使用特殊的优化方法:structural 和flatten,建议大家在synthesis时同时生成structural 和flatten格式的netlist,然后打开看看到底有什么不同之处。

1.17. 基于路径的综合的意思是什么?

路径(path),是DC中的一个重要概念。

它包括4种路径方式:

1 input到FF的D端。

2 FF的clk到另一个FF的D端。

3 FF的clk到输出Q。

4 input到output。

基于路径的综合就是对这四种路径进行加约束,综合电路以满足这些约束条件。

1.24 reference 是指什么? 和cell 有什么区别?

当存在一个模块被多次例化,那么该模块就称为reference

1.25 如何读入一个design?

使用analyze + elaborate 或者 read_verilog、read -f verilog、

read_vhdl、read_file 命令。

1.26 analyze+ elaborate 和 read 命令有什么区别?

read_file 是可以读取任何synopsys支持格式的;analyze和eloborate 只支持verilog和VHDL两个格式,但是他们支持在中间过程中加入参数而且以便以后可以加快读取过程。

1.27 如何处理多个引用的问题?

方法一:使用 uniquify,就是把引用几次那么就在内存中换名引入多个子设计,适用于不同时序约束要求。

方法二:可以用dont_touch命令,先对多个引用的设计进行编译之后,设置为dont_touch,适用于基本相同的环境要求。

方法三:把两个引用进行 flatten(没有层级结构),然后进行综合。

1.28 link的作用是什么?

确定所有文件是否均存在并把它们链接到当前设计。

1.29 环境设置是指什么?

是指芯片物理上的参数,比如电压,温度等。

1.30 如何设置线载模型?

使用set_wire_load_model 命令,

如:set_wire_load_model -name KME -library libr

1.31 如何得知线载模型的种类?

读取库文件到DC中,使用report_lib看有多少可用的线载模型

1.32 如何设置工作环境变量?

使用set_operating_conditions

如:set_operating_conditions "WCCOM"

1.33 工作环境变量的类别可以分为哪几类?

一般可以分为最坏(worst case)、典型(typical)、最佳(best case)。

1.34 为什么要设置工作环境变量?

由于我们要做的是一颗要在实际环境中正常工作的芯片,而温度和环境对电路的性能有很大影响,因此为了尽可能地模拟芯片工作,设置合适的工作环境信息是非常必要的。

1.35 read 和 analyze + ealborate做了哪些工作?

语法检查,建立GETECH库(大家可以自己去搜索什么叫GETECH库)值得注意的是,read命令不自动执行link操作。

1.36 getech库是做何用途的?

GETCH库是由软宏(soft macros)组成的,是加法器,乘法器之类的东西,这些组件都是在DW里引用的。

1.32 如何设置工作环境变量?

使用set_operating_conditions

如:set_operating_conditions "WCCOM"

1.33 工作环境变量的类别可以分为哪几类?

一般可以分为最坏(worst case)、典型(typical)、最佳(best case)。

1.34 为什么要设置工作环境变量?

由于我们要做的是一颗要在实际环境中正常工作的芯片,而温度和环境对电路的性能有很大影响,因此为了尽可能地模拟芯片工作,设置合适的工作环境信息是非常必要的。

1.35 read 和 analyze + ealborate做了哪些工作?

语法检查,建立GETECH库(大家可以自己去搜索什么叫GETECH库)值得注意的是,read命令不自动执行link操作。

1.36 getech库是做何用途的?

GETCH库是由软宏(soft macros)组成的,是加法器,乘法器之类的东西,这些组件都是在DW里引用的。

2.13 DC是基于path的综合,那么在约束时如何体现?

我们知道,基于path会有四种路径形式,DC中提供

create_clock 定义寄存器和寄存器之间的路径;

set_input_delay 定义输入与寄存器之间的路径;

set_output_delay 定义寄存器与输出之间的路径;

set_max_delay 和 set_min_delay定义输入和输出的组合路径;

2.14 set_input_delay 的目的是什么?

定义输入延时,来约束设计中输入逻辑的时序

2.15 set_output_delay 的目的是什么?

定义输出延时,来约束设计中的输出逻辑的时序

2.16 如何对组合电路进行约束?

组合电路有set_max_delay 和set_min_delay进行约束

2.18 当一个组合电路超过了时钟周期约束,那么该如何处理?

加上set_max_delay重新约束,这样综合工具就会按照set_max_delay 的值尽量满足要求,不过这样会增加design的area,如果timing还是不能满足,那只能修改设计。

2.19 当出现环路电路时,如何约束电路?

对某一路径使用set_false_path

2.20 如何加强设计规则的约束?

DRC是电路必须满足的设计规则,使用

set_max_capcitance

set_max_fanout

set_max_tansition

2.21 在添加了4种路径约束后,那么在synthesis时如何为某些path移除约束,不作timing分析?

使用set_flase_path使得某些路径不进行timing check

2.22 对于某些路径需要在固定的几个周期内完成,如何对这些路径进行约束?

使用set_multicycle_path 对路径进行约束

2.23 在添加这些特殊的路径约束,如何恢复原来通用的时序约束?

使用reset_path

2.24 如何对三态门进行约束?

由于综合时,默认三态门是enable的,所以对某些路径要设置

set_false_path

2.25 如何对门控时钟进行约束,以保证功能正常?

对门控时钟电路进行setup和hold检查,使用set_gating_clock_check

2.26 设置对某些网络比如clock或者reset不进行添加buffer等操作,应该怎么约束?

使用set_dont_touch_network

4.1 如何看面积报告?

report_area

4.2 如何看时序报告?

report_timing,详细请man report_timing 这个命令,看看它的多种option 用法

4.3 想对单独的单元看面积报告, 用什么命令?

report_cell 但是缺省的report_cell只能看current_design下面的一级的cell的面积,因此就有两种方法解决这个问题:

1. 用report_cell [get_cells -hier *]可以看所有的cells面积

2. 用list_design列出所有的design, 然后改变current_design到你所想要看的那一级的cell, 然后直接用report_cell.

4.4 如何看设计环境和线载模型?

report_design

4.5 若设计规则和时序违反约束,如何查看?

使用report_constraint -all_violators

4.6 如何查看连线的扇入,扇出,负载,电容和跳变时间?

使用report_net

4.6 如何看整个综合后的网表中使用多少种类型的电路门?

使用report_hierarchy

4.7 如何查看timing exception的时序约束?

使用report_timing_requirements,请大家思考一下有哪些timing exceptions。